### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

Masters Theses Graduate School

5-2001

# A PLL frequency synthesizer for a 300 MHz high temperature transceiver realized in 0.5um SOS technology

Andrew Philip Moor

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

#### **Recommended Citation**

Moor, Andrew Philip, "A PLL frequency synthesizer for a 300 MHz high temperature transceiver realized in 0.5um SOS technology." Master's Thesis, University of Tennessee, 2001. https://trace.tennessee.edu/utk\_gradthes/9686

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Andrew Philip Moor entitled "A PLL frequency synthesizer for a 300 MHz high temperature transceiver realized in 0.5um SOS technology." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

James M. Rochelle, Major Professor

We have read this thesis and recommend its acceptance:

Britton, Bouldin

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

### To the Graduate Council:

I am submitting herewith a thesis written by Andrew Philip Moor entitled "A PLL Frequency Synthesizer for a 300 MHz High Temperature Transceiver Realized In 0.5um SOS Technology". I have examined the final copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

James M. Rochelle, Major Professor

We have read this thesis and recommend its acceptance:

Accepted for the council:

Interim Vice Provost and Dean of the Graduate School

### A PLL Frequency Synthesizer for a 300 MHz High Temperature Transceiver Realized In 0.5um SOS Technology

A Thesis Presented for the Master of Science Degree

The University of Tennessee, Knoxville

Andrew Philip Moor May 2001 Dedicated to my family and friends who have motivated and supported me throughout my college career.

### Acknowledgements

I sincerely appreciate the many people who offered me guidance and support during the course of my Master's program. First of all, I would like to thank my thesis committee, Dr. Rochelle, Dr. Britton, and Dr. Bouldin, for taking time to review and direct my thesis work. Special thanks to Dr. Rochelle for serving as my major professor and graduate advisor. In addition, I would like to thank each of my graduate professors for their excellent instruction and guidance.

I am grateful to the University of Tennessee, Oak Ridge National Laboratory, and their corporate partners for their support of the UT/ORNL Joint Program. I would especially like to thank Lucent Technologies for sponsoring my graduate summer internship in the Microelectronics Group and my research efforts at ORNL. Additionally, I extend my thanks to the many engineers at ORNL who offered their support during my thesis research. Special thanks to Dr. Britton for his insight and direction of my research.

Finally, I would like to thank the staff of the Co-op Engineering Program at UT for their continued support during my graduate studies. Special thanks to my friends and family, who have been with me throughout my undergraduate and graduate education at UT. It has been a tremendous amount of fun to be around so many bright, creative, and enthusiastic people, and I truly appreciate the unique contributions of support and encouragement that each one of you has made.

This work was funded by Halliburton Energy Systems (HES). In particular, I would like to thank Roger Schultz of HES for his support. This work was performed at the Oak Ridge National Laboratory managed by UT-Battelle, LLC for the U.S. Department of Energy under contract DE-AC05-00OR22725.

### **Abstract**

This thesis presents a study of the design of a phase-lock loop (PLL) system, including specific designs for a voltage-controlled oscillator and programmable frequency divider, implemented in a 0.5 m silicon-on-sapphire CMOS technology. The system is designed for use as a frequency synthesizer in a high-temperature transceiver. Several issues relating to high-temperature applications as well as the overall system architecture are presented. Principles of the PLL system are described, and critical design considerations are discussed. The designs of the VCO and programmable divider are described and analyzed in detail. A brief discussion of the design and analysis of other PLL components is presented. Prototyping and testing procedures are discussed and the results of the prototyped circuits are evaluated. Finally, a summary of the work is presented along with insights gained toward future research.

# Table of Contents

| Chapter 1: |                                                       | Overview                                                     |  |  |  |

|------------|-------------------------------------------------------|--------------------------------------------------------------|--|--|--|

|            | 1.1:                                                  | Introduction 1                                               |  |  |  |

|            | 1.2:                                                  | Overview of Phase-Locked Loop Functionality 3                |  |  |  |

|            | 1.3:                                                  | High Temperature System Considerations 4                     |  |  |  |

|            | 1.4:                                                  | Scope of Thesis                                              |  |  |  |

| Chapter 2: | Phas                                                  | e Locked Loop Design and Analysis 6                          |  |  |  |

| -          | 2.1:                                                  | PLL System Architecture 6                                    |  |  |  |

|            | 2.2:                                                  | Phase Detector and Charge Pump 7                             |  |  |  |

|            | 2.3:                                                  | Loop Filter 10                                               |  |  |  |

|            | 2.4:                                                  | Voltage Controlled Oscillator                                |  |  |  |

|            | 2.5:                                                  | Frequency Divider 12                                         |  |  |  |

|            | 2.6:                                                  | PLL Performance Issues                                       |  |  |  |

| Chapter 3: | Volta                                                 | ge-controlled Oscillator Design and Analysis 18              |  |  |  |

| •          | 3.1:                                                  | Specifications                                               |  |  |  |

|            | 3.2:                                                  | Architecture Considerations                                  |  |  |  |

|            | 3.3:                                                  | Topology Analysis and Design Considerations 20               |  |  |  |

|            |                                                       | 3.3.1: Tank Circuit                                          |  |  |  |

|            |                                                       | 3.3.2: Varactor Diodes                                       |  |  |  |

|            |                                                       | 3.3.3: Integration of Varactor Diodes in the Tank Circuit 25 |  |  |  |

|            |                                                       | 3.3.4: Quality Factor of Tank Circuit 26                     |  |  |  |

|            |                                                       | 3.3.5: Cross-coupled Differential Transistor Pair 28         |  |  |  |

|            |                                                       | 3.3.6: VCO Resonant Frequency and Quality Factor 30          |  |  |  |

|            |                                                       | 3.3.7: Biasing and Output Buffering                          |  |  |  |

|            | 0.4                                                   | 3.3.8: Noise Effects and Design Tradeoffs                    |  |  |  |

|            | 3.4:                                                  | High Temperature Considerations                              |  |  |  |

|            | 3.5:                                                  | Preliminary Design                                           |  |  |  |

|            | 3.6:                                                  | Simulation and Layout Techniques                             |  |  |  |

| Chapter 4: | Programmable Frequency Divider Design and Analysis 45 |                                                              |  |  |  |

|            | 4.1:                                                  | Specifications                                               |  |  |  |

|            | 4.2:                                                  | Architecture                                                 |  |  |  |

|            |                                                       | 4.2.1: Front End Design                                      |  |  |  |

|            |                                                       | 4.2.2: Programmability Considerations                        |  |  |  |

|            | 4.3:                                                  | High Temperature Considerations                              |  |  |  |

|            | 4.4:                                                  | Simulation, Synthesis and Optimization 50                    |  |  |  |

| Chapter 5:  | Prototype Testing and Evaluation |                                                    |      |

|-------------|----------------------------------|----------------------------------------------------|------|

| -           | 5.1:                             | Chip Layout Techniques                             |      |

|             | 5.2:                             | Chip Fabrication                                   | . 59 |

|             | 5.3:                             | Test Board Design                                  | . 64 |

|             | 5.4:                             | Test Board Modifications                           |      |

|             | 5.5:                             | VCO Test Procedures and Results                    | . 73 |

|             |                                  | 5.5.1: Tuning Range                                | . 73 |

|             |                                  | 5.5.2: Output Drive                                | . 77 |

|             |                                  | 5.5.3: Phase Noise                                 |      |

|             | 5.6:                             | Frequency Divider Test Procedures and Results      |      |

|             | 5.7:                             | Closed-loop PLL Test Procedures and Results        | . 89 |

|             |                                  | 5.7.4: Initial Testing                             |      |

|             |                                  | 5.7.5: Troubleshooting and Optimization            | . 91 |

|             |                                  | 5.7.6: Closed-loop Measurements                    | . 93 |

|             |                                  | 5.7.7: Small-signal Response                       | . 97 |

|             |                                  |                                                    |      |

| Chapter 6:  |                                  | usions and Future Improvements                     | . 99 |

|             | 6.1:                             | Conclusions                                        |      |

|             | 6.2:                             | Future Improvements                                | 101  |

| -           |                                  |                                                    | 400  |

| References  | • • • • •                        |                                                    | 103  |

| Annendix A: | Pre-la                           | yout HSPICE Simulation Files                       | 108  |

| Appoilant   | A.1:                             | VCO Pre-layout HSPICE Simulation File              |      |

|             | A.2:                             | Divider Pre-layout ViewSim Simulation Source File  |      |

|             | A.3:                             | Divider Pre-layout ViewSim Simulation Command File |      |

|             |                                  |                                                    |      |

| Appendix B: |                                  | ayout HSPICE Simulation Files                      | 114  |

|             | B.1:                             | VCO Post-layout HSPICE Simulation File             |      |

|             | B.2:                             | Divider Post-layout HSPICE Simulation File         | 11/  |

| Vita        |                                  |                                                    | 126  |

# List of Figures

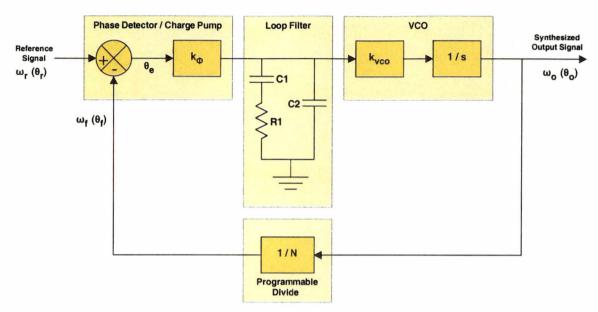

| Figure 2.1:  | PLL block diagram                                              | . 7 |

|--------------|----------------------------------------------------------------|-----|

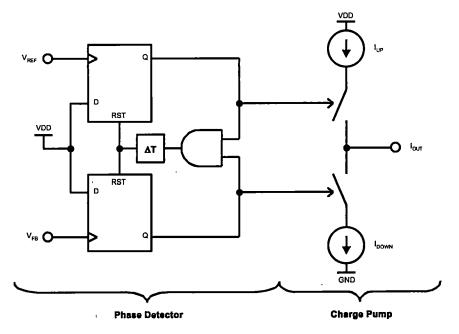

| Figure 2.2:  | Phase detector / charge pump diagram                           | . 8 |

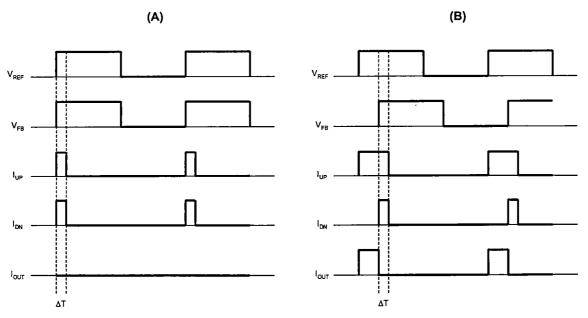

| Figure 2.3:  | Charge pump output comparison                                  | . 9 |

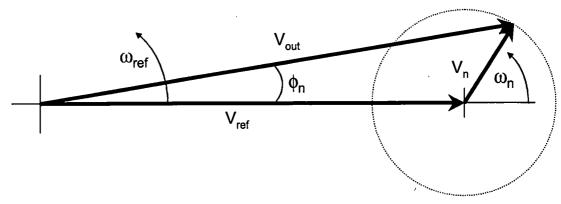

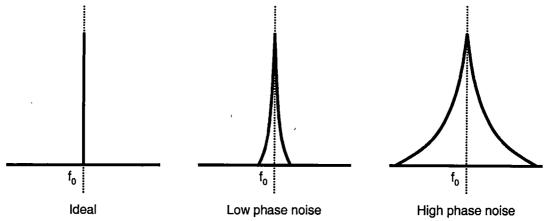

| Figure 2.4:  | Phasor representation of phase noise                           | 14  |

| Figure 2.5:  | Examples of phase noise in output signal spectrum              | 15  |

| Figure 2.6:  | Contributions to overall phase noise in a PLL                  |     |

| Figure 3.1:  | Schematic diagrams of typical oscillators                      | 18  |

| Figure 3.2:  | VCO Schematic                                                  |     |

| Figure 3.3:  | Varactor diode model                                           |     |

| Figure 3.4:  | Varactor diode performance data                                |     |

| Figure 3.5:  | Hybrid-Pi model for cross-coupled differential transistor pair | 29  |

| Figure 3.6:  | Equivalent impedance Hybrid-Pi model                           | 30  |

| Figure 3.7:  | Hybrid-Pi model for complete tank circuit                      | 31  |

| Figure 3.8:  | Comparison of phase noise models                               |     |

| Figure 3.9:  | VCO pre-layout simulation                                      |     |

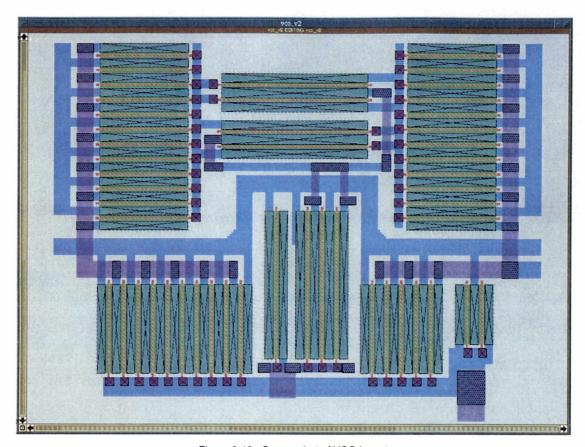

| Figure 3.10: | Screen shot of VCO layout                                      |     |

| Figure 3.11: | VCO post-layout simulation                                     | 43  |

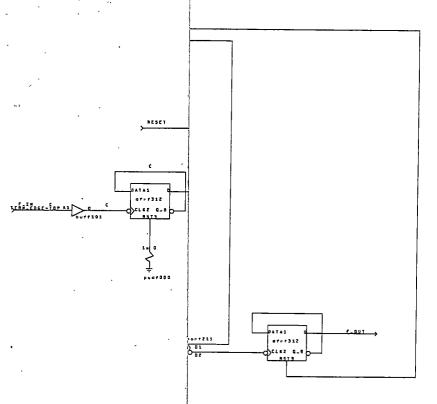

| Figure 4.1:  | Programmable divider schematic                                 | 46  |

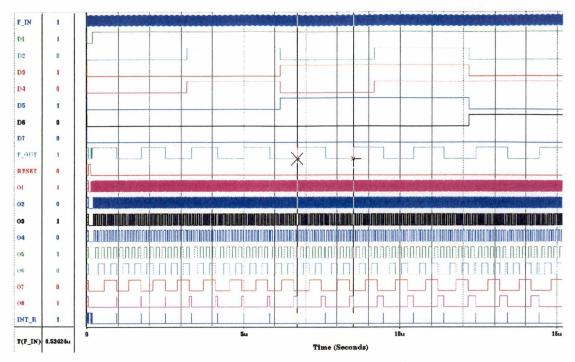

| Figure 4.2:  | Pre-layout simulation of programmable divider                  |     |

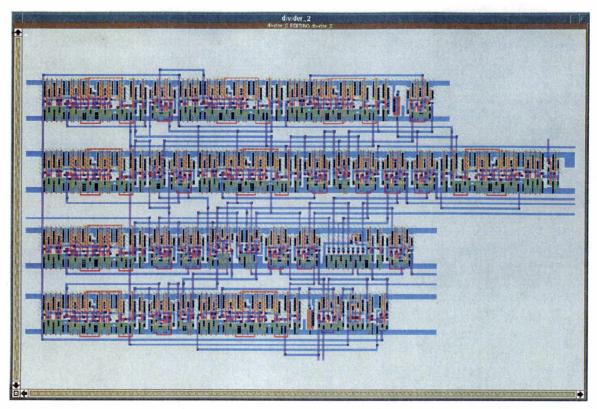

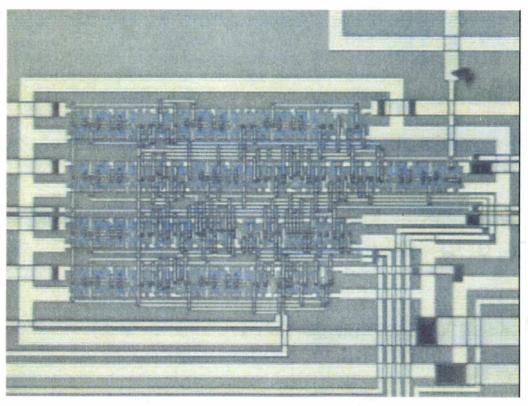

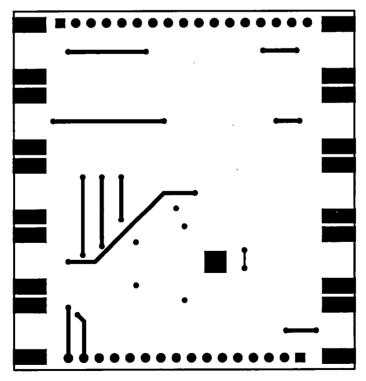

| Figure 4.3:  | Screen shot of programmable divider layout                     | 53  |

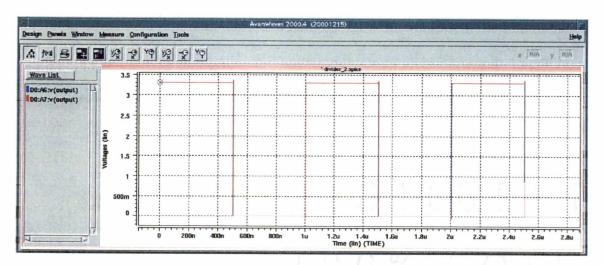

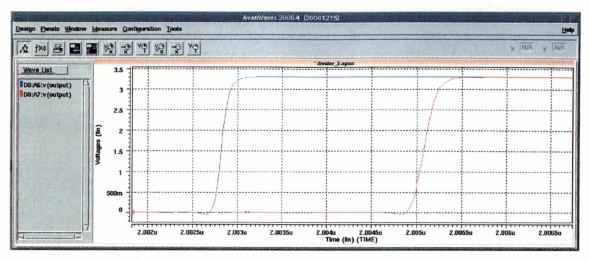

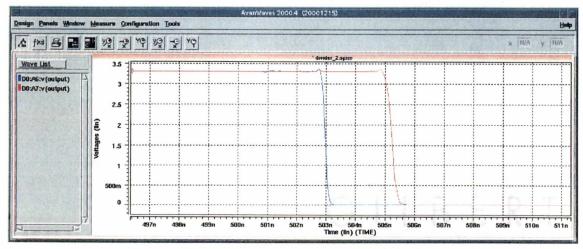

| Figure 4.4:  | Post-layout simulation of divider at 300 MHz                   |     |

| Figure 4.5:  | Post-layout simulation of divider at 300 MHz - rising edge     | 55  |

| Figure 4.6:  | Post-layout simulation of divider at 300 MHz - falling edge    | 55  |

| Figure 4.7:  | Post-layout simulation of divider at 260 MHz - falling edge    | 56  |

| Figure 4.8:  | Post-layout simulation of divider at 340 MHz - falling edge    |     |

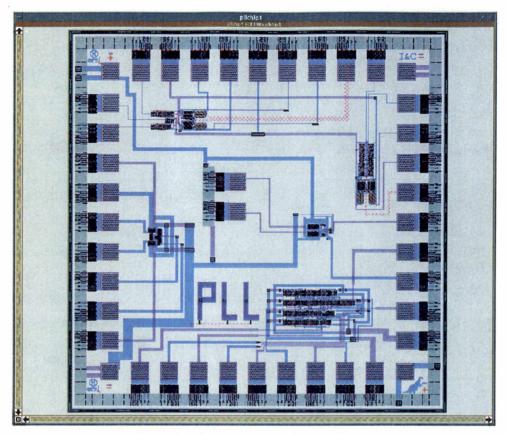

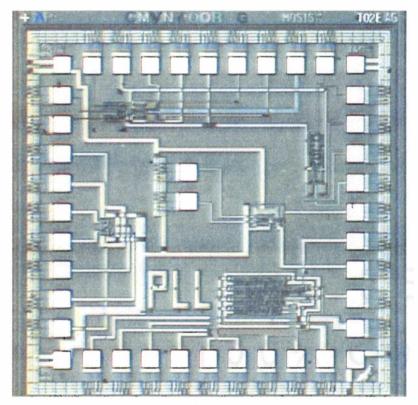

| Figure 5.1:  | Screen shot of complete chip layout                            | 59  |

| Figure 5.2:  | Traditional bulk silicon process cross-section                 | 60  |

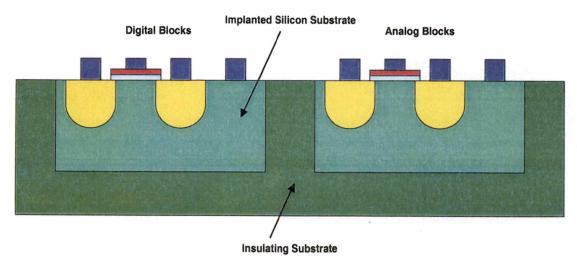

| Figure 5.3:  | Typical silicon-on-insulator (SOI) cross-section               |     |

| Figure 5.4:  | Microscope photo of PLLCHIP1 die                               |     |

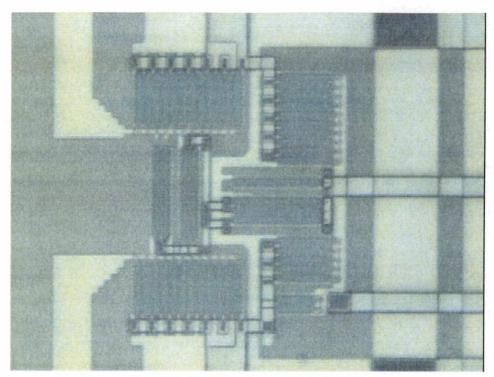

| Figure 5.5:  | Microscope photo of PLLCHIP1 VCO                               |     |

| Figure 5.6:  | Microscope photo of PLLCHIP1 divider                           |     |

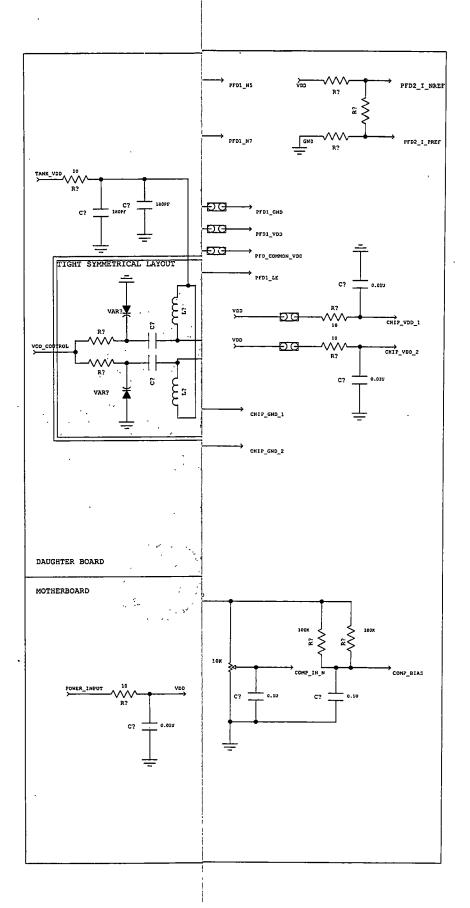

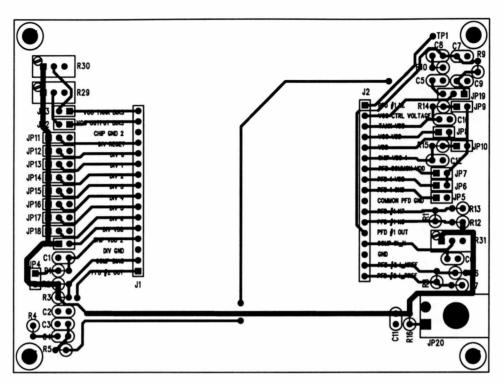

| Figure 5.7:  | PLLCHIP1 test board schematic                                  |     |

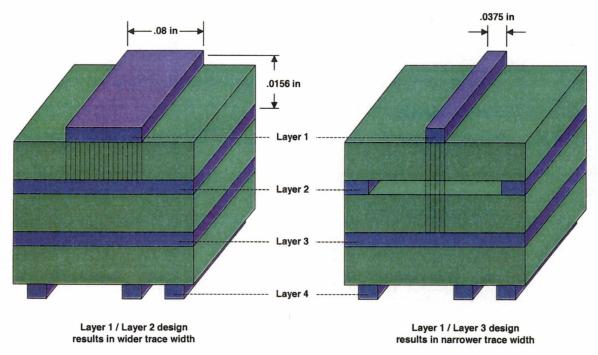

| Figure 5.8:  | Comparison of transmission line designs                        |     |

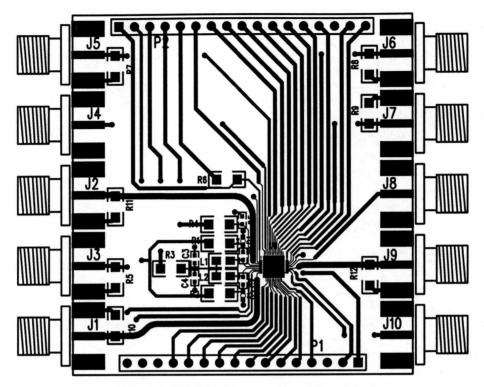

| Figure 5.9:  | PLLCHIP1A test board layout: layer 1 (top)                     | 68  |

|              | PLLCHIP1A test board layout: layer 2                           |     |

|              | PLLCHIP1A test board layout: layer 3                           |     |

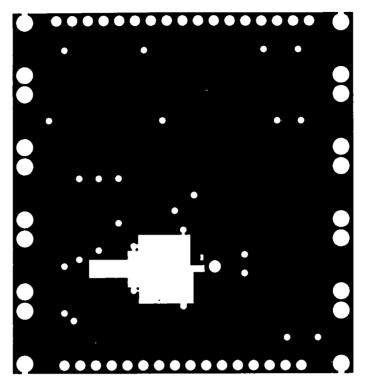

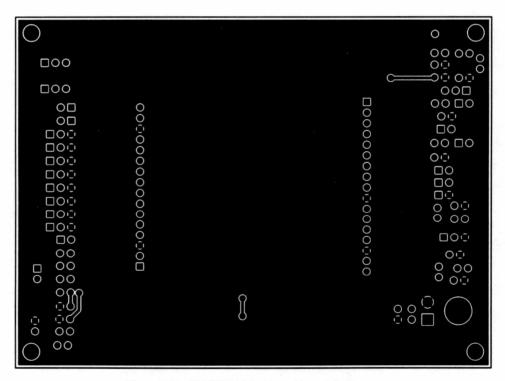

| Figure 5.12: | PLLCHIP1A test board layout: layer 4 (bottom)                  | 69  |

|              | PLLCHIP1B test board layout: top                               |     |

| Figure 5.14: | PLLCHIP1B test board layout: bottom                            | 70  |

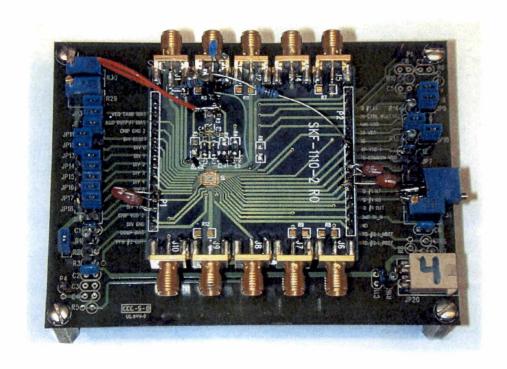

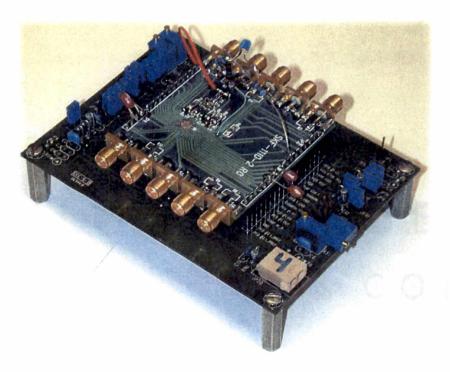

| Figure 5.15: | Test boards with modifications, top view                       | 72  |

|              | Test boards with modifications, isometric view                 |     |

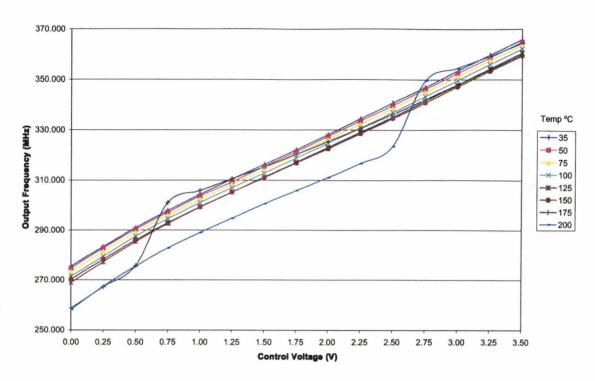

|              | VCO control voltage vs. frequency - Test board #1              |     |

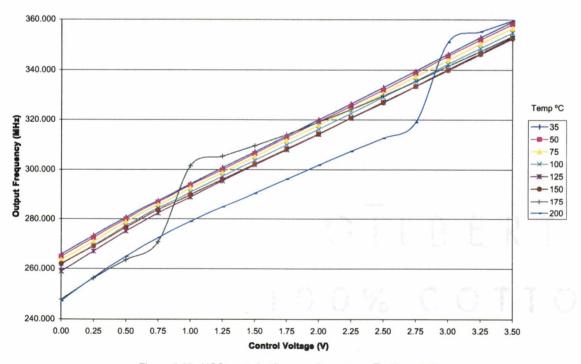

| Figure 5.18: | VCO control voltage vs. frequency - Test board #2              | 74  |

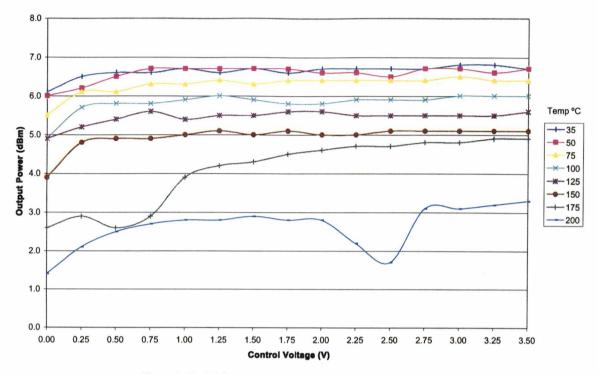

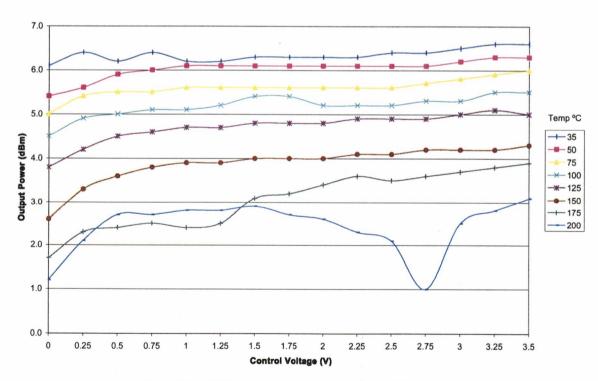

| Figure 5.19: | VCO output power vs. control voltage - Test board #1   | 78 |

|--------------|--------------------------------------------------------|----|

| Figure 5.20: | VCO output power vs. control voltage - Test board #2   | 78 |

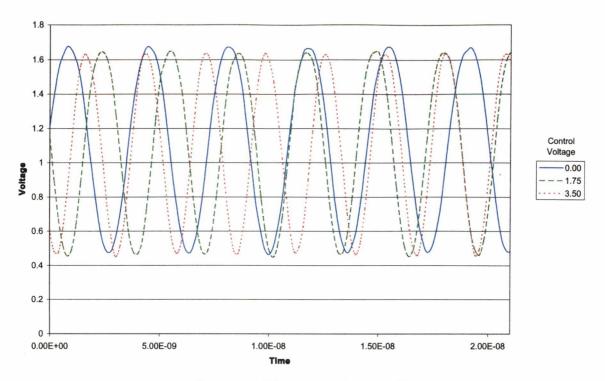

| Figure 5.21: | VCO output waveforms at 25 °C                          | 79 |

| Figure 5.22: | VCO output waveforms at 50 °C                          | 79 |

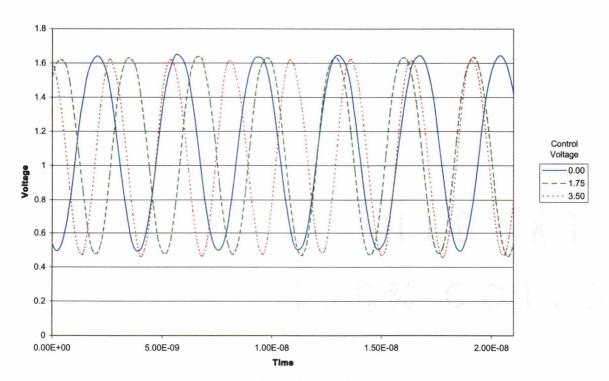

| Figure 5.23: | VCO output waveforms at 100 °C                         | 80 |

| Figure 5.24: | VCO output waveforms at 150 °C                         | 80 |

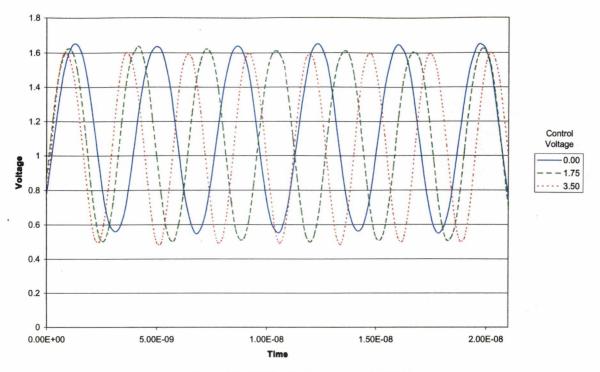

| Figure 5.25: | VCO output waveforms at 200 °C                         | 81 |

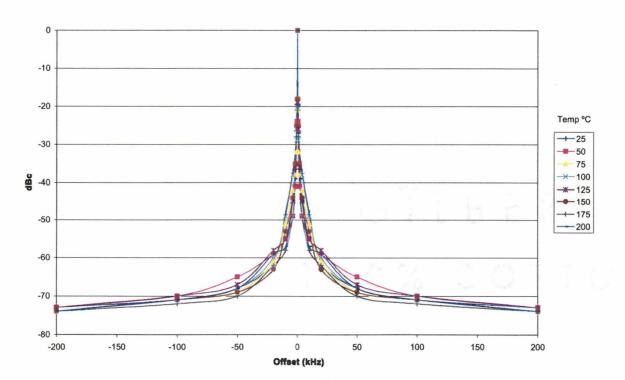

| Figure 5.26: | VCO output spectrum over temperature                   | 82 |

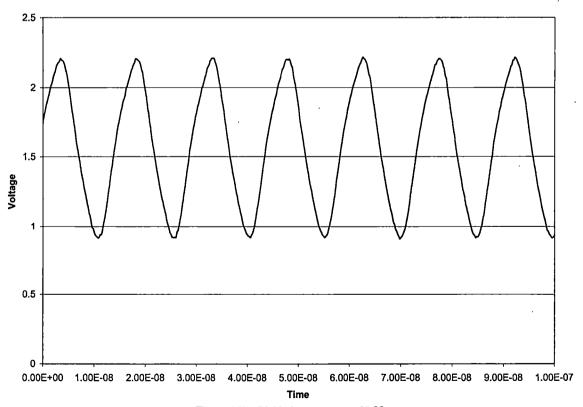

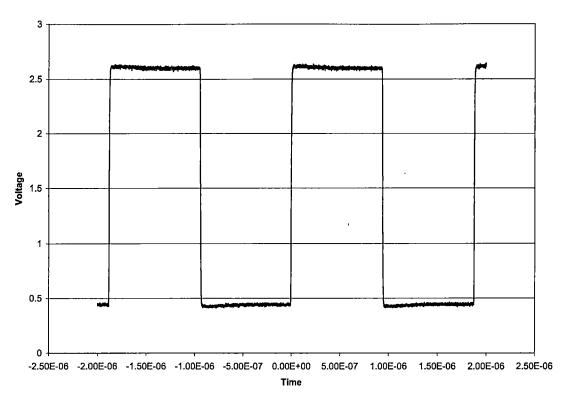

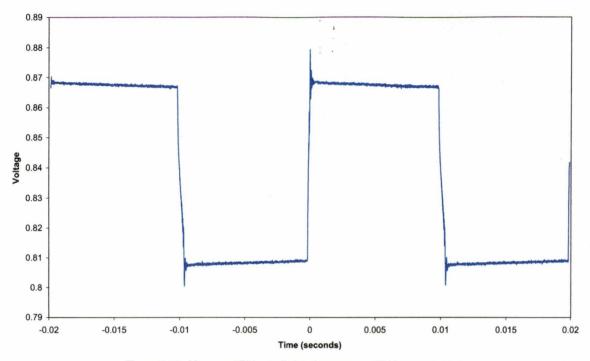

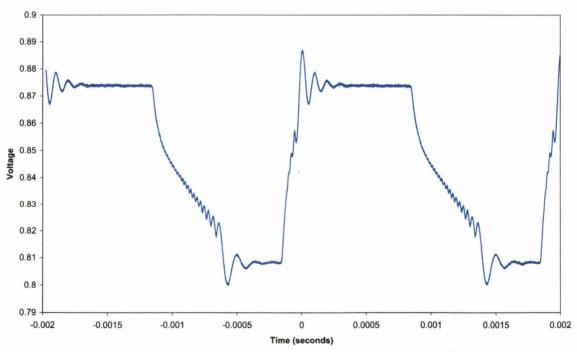

| Figure 5.27: | Divide-by-4 output at 25 °C                            | 85 |

| Figure 5.28: | Divide-by-512 output at 25 °C                          | 86 |

| Figure 5.29: | Divide-by-16 output at 25 °C                           | 86 |

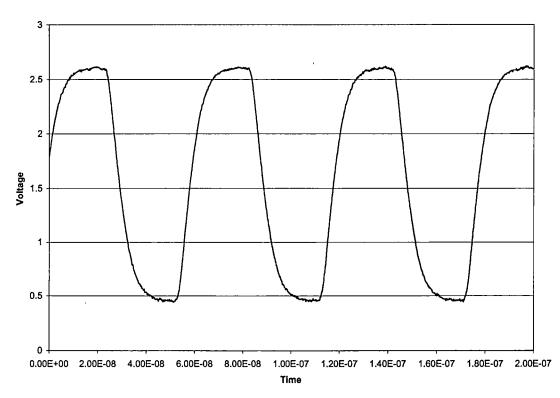

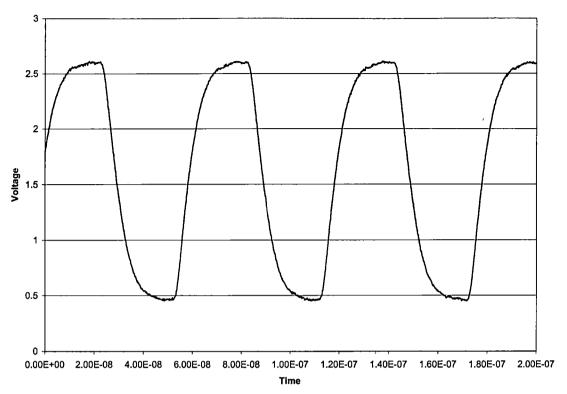

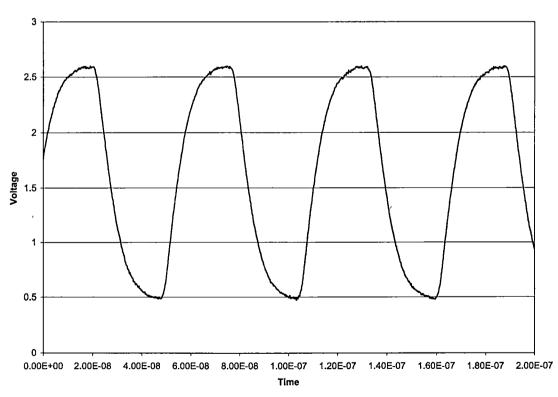

| Figure 5.30: | Divide-by-16 output at 75 °C                           | 87 |

| Figure 5.31: | Divide-by-16 output at 125 °C                          | 87 |

| Figure 5.32: | Divide-by-16 output at 175 °C                          | 88 |

| Figure 5.33: | Divide-by-16 output at 200 °C                          | 88 |

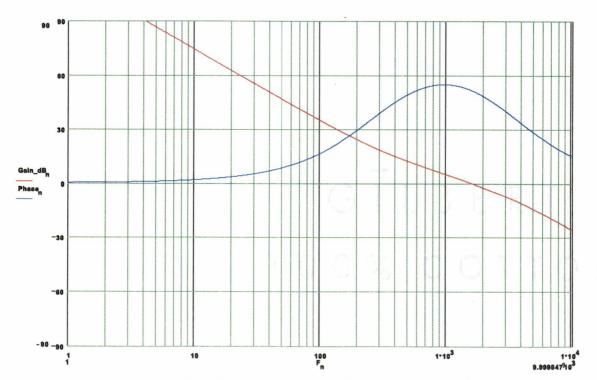

| Figure 5.34: | Simulated PLL transfer function characteristics        | 93 |

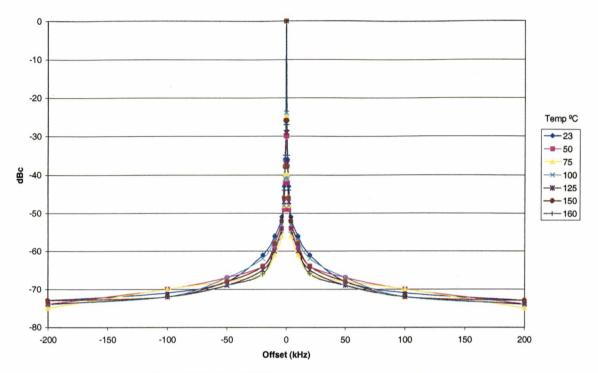

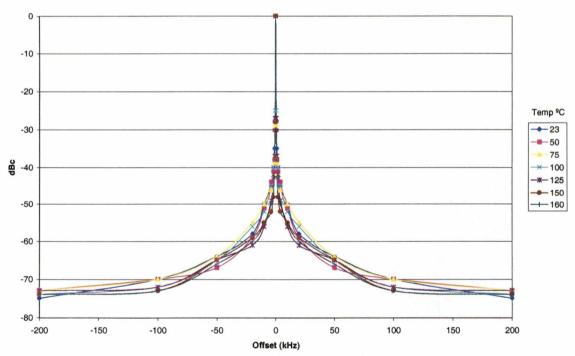

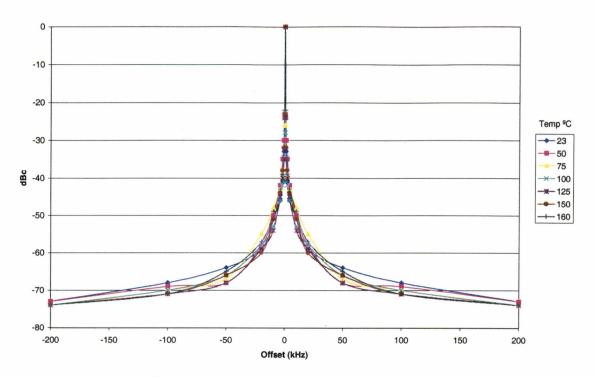

| Figure 5.35: | PLL 280 MHz output spectrum over temperature           | 95 |

| Figure 5.36: | PLL 300 MHz output spectrum over temperature           | 95 |

|              | PLL 320 MHz output spectrum over temperature           |    |

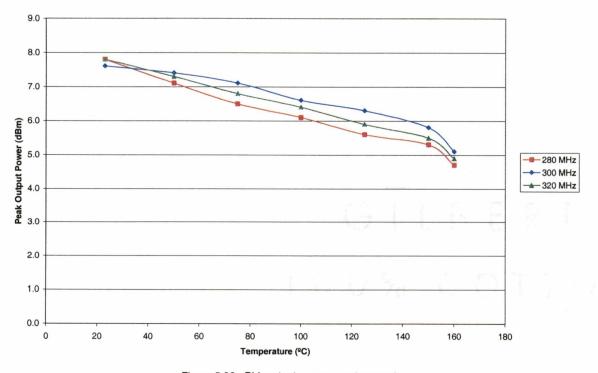

|              | PLL output power over temperature                      |    |

|              | Simulated PLL small-signal response                    |    |

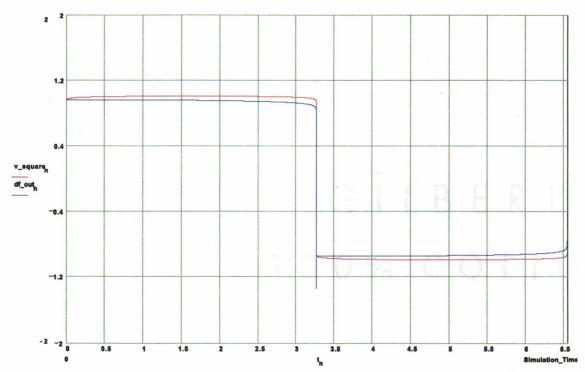

| Figure 5.40: | Measured PLL small signal response - 50 Hz square wave | 98 |

| Figure 5.41: | Measured PLL small signal response - 50 Hz square wave | 98 |

## List of Tables

| Table 3.1: | Varactor diode modeling parameters for SMV1236 | 24 |

|------------|------------------------------------------------|----|

| Table 3.2: | VCO tank circuit component values              | 38 |

| Table 3.3: | VCO pre-layout simulation results              | 40 |

| Table 3.4: | VCO post-layout simulation results             | 44 |

| Table 4.1: | Divider programming codes                      | 51 |

| Table 4.2: | Divider simulation results                     | 57 |

| Table 5.1: | Test board functions                           | 64 |

| Table 5.2: | VCO measured gain - Test board #1              | 75 |

| Table 5.3: | VCO measured gain - Test board #2              | 75 |

| Table 5.4: | Comparison of VCO gain and drift               | 75 |

| Table 5.5: | VCO open-loop phase noise measurements         | 82 |

| Table 5.6: | Divider measured results                       | 89 |

| Table 5.7: | Initial loop filter component values           | 90 |

| Table 5.8: | Final loop filter component values             | 93 |

### **Chapter 1**

### Overview

#### 1.1 Introduction

In many commercial and industrial environments, system engineers can easily obtain process measurements and information by connecting a test instrument directly to a sensor. In some cases, information from many different sensors can be combined and routed to a different location for centralized monitoring. However, difficulties can arise in situations where the sensor itself is too large to monitor the target process, or the process environment itself is considered 'hostile' to measurements, due to extremes in atmospheric conditions, chemical reactivity, or temperature. In these cases, specialized systems must be designed to meet the challenges of the hostile environment while providing accurate measurement capability of the target process.

The implementation of remote measurement and monitoring systems for hostile environments poses a significant challenge to system engineers. In many cases, the constraints make traditional measurement techniques impractical or even impossible. Integrated circuit (IC) technology offers several distinct advantages which can be leveraged to meet the demands of hostile environments requiring sensors that must be relatively small, and be capable of operating over a wide range of temperature.

First of all, IC technology provides the capability to produce small, durable, and relatively inexpensive devices. Thousands of transistors and many types of passive devices can

be easily manufactured on a very small chip. Secondly, these devices have the potential to operate more predictably at higher temperatures than an equivalent discrete-component implementation. Devices on an integrated circuit can be matched to a much higher precision, and the effects of temperature gradients can be minimized by using appropriate layout techniques. Finally, recent innovations in IC fabrication have spurred new developments in sensor technology, yielding the ability to incorporate many unique, specialized, and highly accurate sensors on a single silicon substrate. On-chip sensors are considerably smaller and more accurate than many of their discrete counterparts. These benefits make IC technology an obvious solution for remote measurement applications where a high degree of measurement precision is required, but size constraints or unusual operating temperature requirements cannot be avoided.

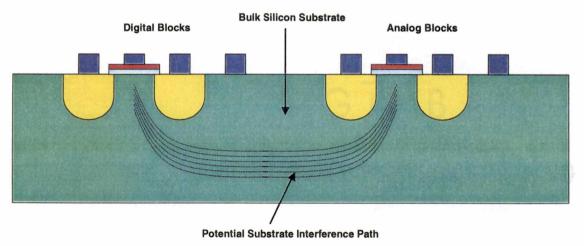

Many variations of IC processing technology exist, such as bulk CMOS, Silicon-Germanium, and Gallium-Arsenide. However, the use of Silicon-on-Sapphire (SOS) processing provides several distinct advantages compared to traditional processes. First of all, devices fabricated in SOS are effectively isolated, because the sapphire substrate is a very good insulator. This prevents substrate leakage current flow between devices, translating into reduced noise and reduced power consumption, and the ability to increase the packing density of devices on a single chip [1]. In fact, analog and digital circuits can be easily implemented on the same chip, compared to the cumbersome design techniques required to achieve mixed signal circuits in traditional processes. SOS circuits are also more resistant to radiation effects, making them ideal for use in radio transmitters for applications such as cellular phones and communications satellites [1]. Thermal effects of SOS circuits differ significantly from other processes, because the

sapphire substrate has a lower thermal conductivity than bulk silicon [2]. Another advanced application of SOS technology is optical networking, where signals from fiber-optic cables can be processed and routed on a single chip [3]. Of these advantages, the noise-reducing properties of the insulating substrate are the primary reason for the selection of SOS technology for the PLL.

This thesis describes the design and testing of a phase-locked loop (PLL) to be used as a frequency synthesizer in a high-temperature remote sensor system. An overview of the PLL is presented, along with a discussion of critical performance criteria. Subsequent chapters present the design and analysis of two major sub-components of the PLL: a voltage-controlled oscillator (VCO) and a frequency divider. Simulation results and prototype test results are compared, and the feasibility of the design is evaluated.

### 1.2 Overview of Phase-Locked Loop Functionality

The primary function of a PLL is to synchronize a controllable oscillator with a precision reference oscillator. The controllable oscillator can operate at a much higher frequency than the reference if a frequency divider is also included in the loop. This makes PLLs useful in applications such as local oscillators for radios, clock generation for digital circuitry, and data synchronization for communication systems [4]. In general, the PLL can be interpreted as a negative-feedback system, where the error between the phase (or frequency) of the reference signal and output (feedback) signal is converted into a voltage that drives the oscillator. The PLL architecture for this application is composed of several modules, including a voltage-controlled oscillator (VCO), programmable

frequency divider, phase detector, charge pump, and a loop filter. More details regarding the functions of each block are presented in Chapters 2-4.

### 1.3 High Temperature System Considerations

Because the PLL is required to operate in a high temperature environment, special consideration must be given to temperature effects on the devices used. Adverse effects of temperature include physical breakdown of solder joints, potentially uncorrelated drift of device parameters such as resistance and capacitance, and deviations in operating frequency, stability, and output power. The voltage-controlled oscillator topology used in the PLL offers a limited amount of flexibility in dealing with temperature effects. In addition, the architecture of the PLL itself provides some compensation of temperature effects through the negative feedback loop. Specific details of temperature effects and related design issues for each block are presented in the following chapters.

### 1.4 Scope of Thesis

This thesis presents the design, development, simulation, and characterization of the VCO and programmable frequency divider as components of the PLL. Chapter 2 contains a brief overview of the other components of the PLL, including the phase detector, charge pump, and loop filter. Chapter 3 presents a detailed analysis of the VCO, including high-temperature considerations. Chapter 4 describes the design of the programmable divider. Chapter 5 presents a discussion of prototype fabrication issues, as well as the testing and characterization of the prototyped components. Chapter 6 contains the conclusion and a brief discussion of ideas for future improvements. Appendix A contains all source files used in the simulation of the VCO and programmable

divider. Appendix B contains post-layout extracted parameter source files used to simulate the VCO and programmable divider.

### Chapter 2

### Phase Locked Loop Design and Analysis

This chapter discusses the design and analysis of the phase-locked loop (PLL). The specific architecture used in the PLL design is based on a digital phase-locked loop topology, making use of a digital frequency divider and a digital phase detector. Advantages of this approach include a wide lock range, fast acquisition time, and straightforward implementation in CMOS technology. The loop is capable of generating frequencies from 250 to 350 MHz using a precision reference oscillator.

### 2.1 PLL System Architecture

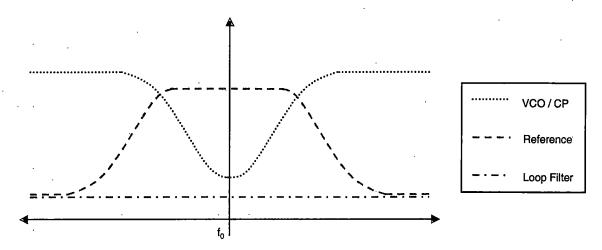

A phase-locked loop is composed of five major components: a precision frequency reference, a phase detector and charge pump, a loop filter, a voltage-controlled oscillator (VCO), and a frequency divider (see Figure 2.1). The loop can be analyzed as a negative feedback control system [5, 6]. The signal from the precision frequency reference has very low phase noise and jitter. This signal is compared with the feedback signal, and the phase difference is converted into a current pulse using a circuit commonly known as a charge pump. These current pulses have a width proportional to the difference in phase (a longer pulse is generated by a larger phase difference). The current pulses are passed to the loop filter to generate a voltage, which in turn drives the voltage-controlled oscillator.

Figure 2.1: PLL block diagram

The VCO output frequency changes proportionally to its control voltage. This output signal drives the output of the PLL, and is also connected to the input of the programmable divider to complete the negative feedback loop. The divider reduces the frequency of the signal so that it is approximately equal to the precision reference frequency. The difference between the reference signal and the feedback signal then adjusts the VCO control voltage, until the error between the two is minimized. In this manner, the negative feedback loop allows the PLL to precisely generate arbitrary output frequencies that are multiples of the precision reference frequency.

### 2.2 Phase Detector and Charge Pump

One of the fundamental requirements of any phase locked loop is the capability to detect and quantify a difference in phase or frequency between the precision reference signal and the feedback signal. This can be accomplished using several different circuit topologies [7]. However, one of the most common and easily implemented approaches is a digital phase comparator. This method uses two flip-flops, with one clocked by the reference signal and the other clocked by the feedback signal, as seen in Figure 2.2. [4]

The output of each flip-flop is connected through an AND gate and a delay element,  $\Delta T$ , back to the reset lines of the flip-flops, and also to a current switch that controls the flow of current into or out of the loop filter. If the feedback signal is perfectly in phase with the reference signal, then the flip-flops will be clocked at the same time, causing the output of the AND gate to be asserted. Once this signal passes the delay element, both flip-flops will be reset simultaneously. The net effect of this perfect synchronization is to close both current switches simultaneously, and a short time later, open them simultaneously. Thus, if the switching currents are matched, the total current delivered to the loop filter through  $I_{OUT}$  is 0, thus the output of the loop filter remains unchanged and the VCO continues to run at the same frequency.

Figure 2.2: Phase detector / charge pump diagram Adapted from: John Wetherell, "Phase Locked Loop Design and Analysis", 1997.

If, however, the feedback signal is out of phase with the reference signal, one of the two current switches will be closed before the other, depending on whether the feedback signal leads or lags the reference. The phase error between the two signals is translated into a current pulse delivered to (or pulled from) I<sub>OUT</sub>. This process effectively adds or removes charge from the loop filter, thus changing the loop filter output voltage and the VCO operating frequency. A comparison of the charge pump output for these cases is given in Figure 2.3. When the loop filter is properly adjusted, the closed-loop system can be stabilized to automatically synchronize the feedback signal to the reference signal. Using a divider in the feedback path allows the closed-loop PLL output frequency to be a precise multiple of the signals in the phase detector.

Figure 2.3: Charge pump output comparison Synchronized (A) and unsynchronized (B)

#### 2.3 Loop Filter

The purpose of the loop filter is to integrate the output of the charge pump, providing a voltage level to control the input of the VCO. Several types of loop filters are commonly used, including second and third-order filters. The selection of filter component values also controls what is commonly known as the loop bandwidth. This is the effective bandwidth of the signal present at the output of the charge pump. By reducing the loop bandwidth, the rejection of high-frequency transients is improved. However, the capture range becomes narrower, the lock time increases, and the overall loop phase margin is reduced [6]. The performance and stability of the entire PLL is therefore critically dependent on the loop filter.

Selection of appropriate loop filter component values is a somewhat open-ended process. One approach is to utilize the Laplace transform to derive an equivalent expression for the loop filter transfer function. Using the designations from Figure 2.1, the transfer function for the loop filter can be obtained [4].

$$F(s) = \frac{1 + RC_1 s}{s(C_1 + C_2)(1 + RC_1 \parallel C_2 s)}$$

2.1

The open-loop transfer function for the PLL can be found by incorporating the gain of the phase detector  $(K_0)$  and VCO  $(K_v)$ , and the division ratio (N).

$$A_{OL} = \frac{K_{\phi} K_{\nu} (1 + RC_{1}s)}{N(C_{1} + C_{2})s(1 + RC_{1} \parallel C_{2}s)}$$

2.2

Setting the open-loop transfer function equal to unity allows the unity-gain bandwidth to be determined [4].

$$1 = \frac{K_{\phi} K_{v} \sqrt{1 + (RC_{1} \omega_{u})^{2}}}{N(C_{1} + C_{2}) \omega_{u}^{2} \sqrt{1 + (RC_{1} \parallel C_{2} \omega_{u})^{2}}}$$

2.3

The loop filter component values can be expressed in terms of their relationship to the pole and zero in the transfer function. First, an appropriate value of the unity-gain bandwidth,  $\omega_u$ , should be determined. Various rules-of-thumb exist for choosing this value, with the goal of allowing a fast settling time while still filtering out spurs from the reference frequency. Finally, the locations of the pole and zero must be chosen to provide adequate phase margin for the system. A typical practice is to use a common factor to scale the unity-gain bandwidth, as in the following examples: [4]

$$\omega_Z = \frac{\omega_u}{\Delta} \qquad \qquad \omega_P = 4 \cdot \omega_u \qquad \qquad 2.4$$

Once these frequencies have been selected, the component values can be calculated using Equation 2.3, and are dependent only on the gain of the charge pump and VCO, the feedback division ratio, and the unity-gain bandwidth.

$$C_1 = \frac{4K_0 K_v}{N\omega_u^2} - C_2$$

2.5

$$C_2 = \frac{K_{\phi} K_{\nu}}{4N\omega_u^2} \tag{2.6}$$

$$R = \frac{4}{\omega_u C_1}$$

2.7

### 2.4 Voltage Controlled Oscillator

With respect to the operation of the PLL, the voltage-controlled oscillator functions as a gain block, with units of Hertz per volt. The VCO uses an L-C tank circuit as a resonator, and includes varactor diodes to tune the resonant frequency. Output buffers are included to provide the capability to drive a  $50-\Omega$  load. The VCO gain and the maximum tuning range are determined by the selection of devices within the tank circuit, and are constraints which affect the design of other components in the PLL. Further details of the VCO design are given in Chapter 3.

### 2.5 Frequency Divider

The primary purpose of the frequency divider is to allow the VCO to run at a higher frequency than the reference frequency. In principle, this allows the accurate synthesis of much higher frequency signals which are phase locked to a lower-frequency reference signal. When a precision reference signal is used, the negative feedback loop will force the VCO to track the reference signal with almost the same level of precision. In this application, the frequency divider is a digital module consisting of standard-cell blocks. Programmability is also included, which allows the division ratio to be altered. While certain divider architectures can allow division by non-integer ratios, this capability was not required for the PLL design, thus an integer-only architecture was used to reduce the overall system complexity. Using the programmable divider, the PLL can be configured to generate one of many possible signals, all of which are integer multiples of the reference signal frequency and phase-locked to the reference signal. Additional details of the programmable divider design are presented in Chapter 4.

#### 2.6 PLL Performance Issues

The performance of phase-locked loops is dependent on several design parameters. PLL systems are generally characterized according to their loop bandwidth, phase margin, and lock time. Loop bandwidth is the effective bandwidth of the signal at the output of the charge pump, and corresponds to the rate at which the VCO control voltage can vary (for example, due to FM modulation of the reference source) while maintaining the locked condition of the PLL. Phase margin relates to the stability of the PLL as a negative feedback system. Circuits with a low phase margin are subject to large overshoot and long settling time, and may exhibit a ringing response to a step input. Circuits with high phase margins are more stable, with little or no overshoot and a much shorter settling time. The lock time for a PLL is the time required for the loop to achieve phase lock after starting up. These system characteristics are somewhat mutually related, and are affected primarily by the design of the VCO, charge pump, and loop filter.

One of the most important goals in the design of a PLL is the minimization of phase noise. This type of noise is directly related to randomly occurring variations in the frequency of the PLL output signal. As an unavoidable condition in physical circuits, phase noise can best be understood using a phasor representation, as in Figure 2.4 [6, 7]. In this diagram, a small rotating phasor, with randomly-varying amplitude and frequency ( $V_n$  and  $\omega_n$ ) is superimposed on the phasor of an ideal oscillator, having a fixed amplitude and frequency ( $V_{ref}$  and  $\omega_{ref}$ ). The resultant vector ( $V_{out}$ ) has a randomly-fluctuating phase difference from the reference signal, represented by  $\phi_n$ . In relation to the frequency spectrum of the output signal, phase noise appears as a widening of the bandwidth of the

Figure 2.4: Phasor representation of phase noise

output signal. While an ideal sine wave would appear as an impulse in frequency space, a sine wave with phase noise would appear to have noise sidebands shaped like a concave-sided triangle, the width of which is proportional to the amount of phase noise present in the signal, as depicted in Figure 2.5 [7].

Phase noise can have a significant impact on the performance of systems which incorporate a PLL, such as RF transceivers. The sideband noise from the PLL can adversely affect both modulation and demodulation of signals using the PLL output as a carrier reference, resulting in a frequency-domain 'smearing' of the modulated signal. Depending on the amount of phase noise and the type of signal being modulated, the resulting output could be significantly degraded or even irrecoverable [8, 9]. In addition, government licenses for radio systems frequently specify spectral limitations that cannot be exceeded. Thus it is critical to minimize phase noise effects in the design of phase-locked loop systems [10, 11]

The majority of phase noise in a PLL can be attributed to one or more of the precision reference frequency source, the loop filter, and the VCO. The precision reference

Figure 2.5: Examples of phase noise in output signal spectrum

frequency source, by itself, has a certain amount of phase noise. When placed inside the PLL, this reference phase noise is multiplied by the loop gain (set by the division ratio). The PLL loop appears as a low-pass filter to the reference frequency, thus a significant amount of the close-in phase noise (that which is very close to the output frequency) of the PLL output can be attributed to the reference frequency. This implies that to reduce the phase noise contributions from the reference source, an extremely high precision, low noise frequency reference must be used, such as a temperature-compensated crystal oscillator.

Noise effects present in the loop filter also contribute to the phase noise of the PLL. Components in the loop filter generate some amount of noise, which is passed to the control voltage of the VCO. Intuitively, this noise on the control voltage will create random fluctuations in the frequency of the VCO output. The final effect is that the noise of the loop filter is multiplied by the gain of the VCO, and the resulting phase noise adds directly to the output phase noise of the entire PLL. The effects of loop filter noise can be minimized by using low-noise circuit designs and a lower VCO gain.

The voltage-controlled oscillator also contributes to the phase noise of the PLL. Noise effects in the VCO introduce random deviations in the output frequency, resulting in phase noise. The amount of phase noise generated is dependent on several aspects of the VCO design, including the selection of passive components for the L-C resonator, the size of the active devices used, and the topology of the circuit. In PLLs using a very high precision reference frequency, the VCO is often a dominant source of phase noise. Minimizing phase noise from the VCO requires optimizing the closed-loop PLL bandwidth, because the loop appears as a high-pass filter relative to the VCO [6, 12]. While a small loop bandwidth would minimize the overall output phase noise, the lock time of the PLL and the phase noise contributed by the VCO within the loop bandwidth would be increased. As a consequence, the design must balance these trade-offs to arrive at an optimum solution, in which the loop bandwidth is set to minimize the effect of VCO phase noise relative to the overall PLL phase noise [7].

The primary difference between the noise generated by the reference frequency, loop filter, and VCO is the physical origin of the noise itself. Reference frequency noise is due mainly to jitter in the crystal oscillator, while noise in the charge pump can be attributed to the nonlinearities in the active devices. Loop filter noise is primarily due to white noise in the passive components of the filter. Phase noise generated by the VCO stems from noise in both the active and passive devices, as well as the topology of the oscillator circuit. Figure 2.6 [7] shows the relative contributions of phase noise by the major components in the PLL.

Figure 2.6: Contributions to overall phase noise in a PLL.

Adapted from: R. K. Feeney and D. R. Hertling, "Fundamentals of Frequency Synthesis and Phase-Locked Loops", 1997.

An analysis of the overall phase noise of the PLL reveals that most of the close-in phase noise is due to the reference source and the charge pump, while the higher-frequency phase noise can be traced to the VCO. The loop filter noise, while still present, is not usually a dominant contributor to the output phase noise.

## **Chapter 3**

### Voltage-controlled Oscillator Design and Analysis

### 3.1 Specifications

The voltage-controlled oscillator (VCO) accepts a DC control voltage between 0 and 3.3 V and is capable of generating a sinusoidal output signal with a frequency between 250 and 350 MHz. The frequency of the output signal is regulated by the control voltage. Any changes in the control voltage produce a proportional change in the output frequency.

### 3.2 Architecture Considerations

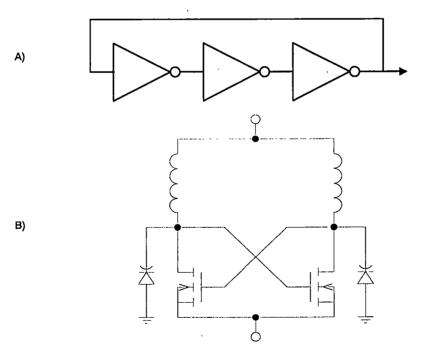

Two common VCO topologies were considered, including ring oscillators and negative-g<sub>m</sub> L-C oscillators (see Figure 3.1). A typical ring oscillator consists of several inverting

Figure 3.1: Schematic diagrams of typical oscillators Simple ring oscillator (A) and simple negative- $g_m$  L-C oscillator (B)

amplifiers, connected in series such that the total phase difference between the first stage and the last stage is 180 degrees. Ring oscillators are easily implemented using digital logic cells, and do not require passive components such as inductors and capacitors. They are commonly used in digital clock-recovery and clock-distribution circuits [13]. Unfortunately, this type of oscillator is plagued by poor phase noise performance, primarily because the transfer of energy within the circuit takes place during a transition between voltages, rather than at a minimum or maximum voltage [14]. In digital logic circuitry, this phase noise degradation may be of secondary concern, since other steps can be taken to assure synchronization of the clock throughout the chip. However, this limitation has prevented ring oscillators from being used in most RF applications, where good phase noise performance is required to meet spectral power limitation requirements.

A typical negative- $g_m$  L-C oscillator consists of a resonant tank circuit connected to a cross-coupled differential pair of transistors. The transistors act to restore energy that is lost to resistive elements in the tank circuit, where the oscillation takes place. By the nature of the circuit, more energy is restored to the resonator during peaks in the oscillation. This reduces the effects of amplitude noise being translated into phase shifts in the resonant signal, and results in far superior phase noise performance when compared to a ring oscillator [10]. For this reason, the negative- $g_m$  L-C oscillator is frequently used in RF applications. Many modern IC fabrication processes are capable of creating the necessary passive components on-chip, resulting in even better phase noise performance. Because of its good phase noise performance and stability, the negative- $g_m$  L-C oscillator topology was selected as the basis for the VCO design.

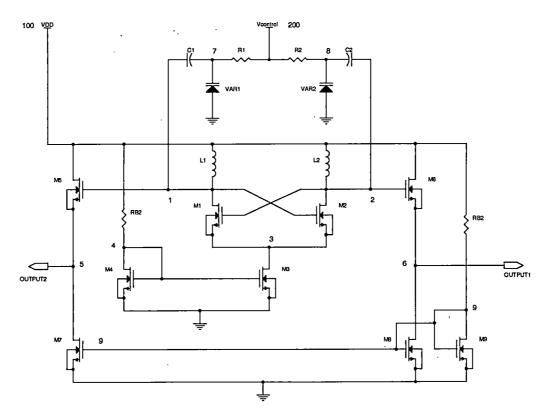

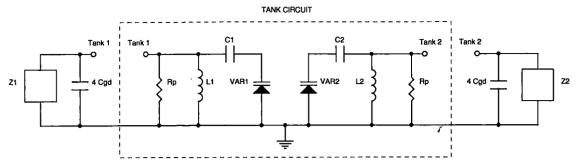

### 3.3 Topology Analysis and Design Considerations

The complete VCO design incorporates several features to improve performance and output drive capability. A schematic diagram of the VCO is presented in Figure 3.2. Detailed analyses of the topology, design considerations, and relevant performance issues are presented in the following sections.

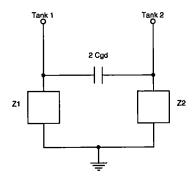

#### 3.3.1 Tank Circuit

The core of any negative-g<sub>m</sub> VCO is the tank circuit. This circuit is composed of the inductors, capacitors, and varactors, as well as the cross-coupled differential pair of NMOS transistors. The operating frequency and tuning range of the VCO are determined by these components. As a whole, the tank has a certain amount of inductance,

Figure 3.2: VCO Schematic

dominated by the off-chip discrete inductors (L1 and L2). A small amount of parasitic inductance is also introduced by the bond wires and board traces, although for the purposes of this design, the effects of parasitic inductance are negligible. The net tank capacitance is set by a combination of the varactor capacitances (VAR1 and VAR2) and the discrete chip capacitors (C1 and C2). In addition, there are several sources of stray capacitance which are accounted for. The chip, bond wires, and board traces all have a certain amount of parasitic capacitance. As a design parameter, the total capacitance due to these parasitic effects was estimated at 2 pF. The cross-coupled differential pair (M1 and M2) also have inherent capacitances, which were estimated at 0.5 pF per device. The total stray capacitance in the design was estimated at 3 pF.

The tank circuit also has a small amount of parasitic resistance, due to non-ideal effects of physical devices. For instance, the inductors have a small, but finite, series resistance in the wire, and the varactors and capacitors have similar resistances in the contacts and internal structure. Board traces and bond wires also contribute parasitic resistance. These parasitic resistances are precisely what the cross-coupled differential transistors are designed to offset. Energy lost in the parasitic resistance must be restored to maintain oscillation, and these transistors provide the means to do so.

#### 3.3.2 Varactor Diodes

To achieve the VCO design goal of having an output frequency controlled by an input voltage, a means must be provided to adjust or 'tune' the resonant frequency of the oscillator tank circuit. This implies changing either the inductance or capacitance, or both.

A simple approach to this task uses a varactor as the tuning element. This type of device

has a capacitance which varies as a function of its applied bias voltage. Depending on the specific type of varactor, the capacitance may or may not be linearly related to the bias voltage. Varactors are typically implemented as reverse-biased P-N junction diodes. In all P-N junction diodes, the depletion width of the junction is dependent on the bias voltage. Reverse-biasing a varactor diode causes the depletion width,  $w_d$ , to increase beyond the zero-bias value. Inherently, this also increases the charge in the depletion region. This fact means that the charge in the diode changes as a function of the reverse bias voltage, as shown in Equation 3.1 [15] where A is the cross-sectional area of the diode and  $N_A$  and  $N_D$  are the doping concentrations.

$$Q_n = q \left(\frac{N_A N_D}{N_A + N_D}\right) w_d A \tag{3.1}$$

The resulting capacitance can be expressed in terms of the zero-bias junction capacitance  $C_{j0}$ , the junction potential  $\phi_j$ , and the reverse bias voltage,  $v_R$ .

$$C_j = \frac{C_{j0}}{\sqrt{1 + \frac{v_R}{\phi_j}}}$$

3.2

The equation shows that the diode capacitance will be at a maximum when there is no reverse-bias voltage applied. The capacitance will decrease as the reverse-bias voltage increases. This provides a means of controlling the capacitance, and therefore the resonant frequency of the tank circuit, simply by altering the reverse-bias voltage on the varactors.

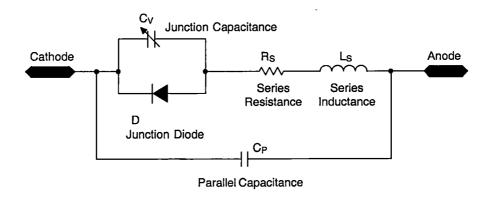

Modeling the non-ideal parasitic effects of varactors provides a more accurate estimation of actual performance. Most manufacturers provide a model which includes parasitic resistance, capacitance, and inductance. The particular varactors used in the VCO are the Alpha Industries SMV1236. The manufacturer's model, shown in Figure 3.3 [16], accounts for the parasitics mentioned above. In addition, the manufacturer provides a capacitance modeling equation [16], similar to Equation 3.2, which utilizes a set of process-extracted parameters.

$$C_V = \frac{C_{J0}}{\left(1 + \frac{V_R}{V_J}\right)^M} + C_P$$

3.3

The values  $V_J$ ,  $C_P$  and M are not representative of any physical quantities. They are merely curve-fitting parameters that allow the equation to more closely track the actual voltage-capacitance curve. The manufacturer's modeling parameters are presented in Table 3.1.

Figure 3.3: Varactor diode model

Source: Varactor SPICE Models for RF VCO Applications, Alpha Industries application note APN1004.

Table 3.1: Varactor diode modeling parameters for SMV1236

| C <sub>J0</sub> | 21.63 pF |

|-----------------|----------|

| VJ              | 8 V      |

| М               | 4.2      |

| C <sub>P</sub>  | 3.2 pF   |

| R <sub>S</sub>  | 0.5      |

| L <sub>S</sub>  | 1.7 nH   |

Some of the varactor parasitic values are quite important to the design, while others are negligible. For instance, the parasitic inductance is very small, and will not have a significant effect on the resonant frequency of the tank circuit unless the resonant frequency approaches the gigahertz range. The parasitic capacitance is also a very small percentage of the total tank capacitance, and can therefore be neglected. However, the parasitic resistance of the varactor cannot be easily overlooked. In fact, this resistance can have a significant effect on the quality factor of the tank circuit.

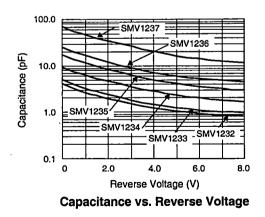

Additional information about the varactors can be obtained by inspecting the manufacturer's performance curves [17], shown in Figure 3.4. Using the capacitance vs. reverse voltage chart for the SMV1236 device, the measured characteristics of the varactor can be evaluated. These characteristics will be reflected in the tuning range of the tank circuit, as well as the gain of the VCO (Hz/volt). In addition, the series resistance vs. reverse voltage chart is useful in determining the anticipated parasitic resistance of the varactors, and in turn the effect on the quality factor of the tank. An important goal is to ensure that the series resistance remains fairly constant over the entire operating voltage, as this will maintain a relatively constant quality factor of the tank regardless of

the operating frequency. Lower parasitic resistances will also result in an increased quality factor.

### 3.3.3 Integration of Varactor Diodes in the Tank Circuit

Varactor diodes are included in the tank circuit to provide voltage-controlled adjustment of the resonant frequency of the tank. However, the varactors alone may not be sufficient to establish the desired resonant frequency, or the available tuning range of the tank may result in an unnecessarily large VCO gain. To compensate for these effects, additional fixed capacitors can be inserted in the tank, in series with the varactors. capacitors in series with the varactors will lower the effective capacitance of the tank, thus raising the center frequency of the VCO, and will also significantly increase the percentage change of tank capacitance contributed by the varactors, thus expanding the tuning range.

An added benefit of the additional capacitors is the isolation of the tank circuit from the cross-coupled transistors. The capacitors provide AC coupling between the varactor

@ 500 MHz

Figure 3.4: Varactor diode performance data Source: Hyperabrupt Tuning Varactors, Alpha Industries product data sheet SMV1232-SMV1237. diodes and the rest of the VCO. This allows the varactor tuning voltage to be referenced to ground instead of the bias voltage of the transistors, and facilitates the ability of other components in the PLL to drive the varactors. Additional problems are also avoided, such as inadvertent forward-biasing of the varactors. Without the series capacitors, the varactor bias voltage would be the difference between the tank circuit output and the control voltage, presenting the possibility of a forward-bias situation. Isolation resistors are included between the control voltage source and the varactors. Unlike the parasitic resistances in the tank, these resistors have no effect on the quality factor of the tank, provided that they are much larger than the equivalent parallel resistance of the tank.

#### 3.3.4 Quality Factor of Tank Circuit

The performance of resonant circuits can be characterized using a quantity known as quality factor. This dimensionless value has no direct correspondence with a physical property. Instead, it is a measure of the energy stored in a circuit relative to the energy lost in the circuit. The most common definition of quality factor, Q, is shown in the following equation [18]:

$$Q = \frac{\omega_0}{RW}$$

3.4

In this case,  $\omega_0$  is the center frequency, and BW is the -3 dB bandwidth of the circuit. A perfect tank circuit, composed of lossless inductors and capacitors, would have an infinitely large quality factor. In reality, all tank circuits contain parasitic resistances which degrade the quality factor. The amount of degradation is directly proportional to the

equivalent parallel tank resistance, as shown in Equation 3.5 [18].

$$Q = R_P \sqrt{\frac{L}{C}}$$

3.5

Both the inductors and capacitors contribute to the tank resistance. The parasitic resistances of these components, usually expressed as a series resistance by the manufacturer, can be represented with equivalent parallel resistances, R<sub>PL</sub> and R<sub>PC</sub> [18].

$$R_{PL} = \frac{\omega_0^2 \cdot L^2}{R_{SL}}$$

3.6

$$R_{PC} = \frac{1}{\omega_0^2 \cdot C^2 \cdot R_{SC}}$$

3.7

Since all the tank components are connected in parallel, these resistances can be combined to derive the net parallel tank resistance [18].

$$R_P = \left(\frac{1}{R_{PL}} + \frac{1}{R_{PC}}\right)^{-1} \tag{3.8}$$

$$R_P = \frac{L^2}{C \cdot L \cdot R_{SC} + \frac{R_{SL}}{\omega_0^2}}$$

3.9

The results of this analysis provide a degree of insight into the design principles for tank circuits. Equation 3.9 demonstrates that the parasitic resistance of the capacitor contributes significantly to the reduction of the quality factor of the tank. Noting that the

the equivalent parallel resistance of an ideal tank circuit is infinite (which yields the ideal infinite Q), the design of physical tank circuits must seek to maximize the equivalent parallel resistance. This can be achieved by reducing the parasitic resistance of the inductor and capacitor. The parasitic resistance of the inductor is dependent on several factors, including the particular physical structure and configuration used. Because most inductors are metallic, parasitic resistance is usually quite small, and further minimization may not be possible. In contrast, the parasitic resistance of a capacitor is related to its capacitance as well as its physical structure, and these observations imply that the net capacitance should be minimized when designing a tank circuit [19]. Unfortunately, the other requirements of the tank, such as tuning range, may impose a lower bound on the capacitance that can be used.

#### 3.3.5 Cross-coupled Differential Transistor Pair

The cross-coupled differential transistor pair (M1 and M2 in Figure 3.2) provide a means of restoring energy lost to parasitic resistances in the tank circuit. The transistors are biased from the positive rail voltage through the tank inductors (which have very small DC resistance) and a current mirror (M3 and M4 in Figure 3.2). The current mirror helps to establish the proper DC operating points to drive the output buffers.

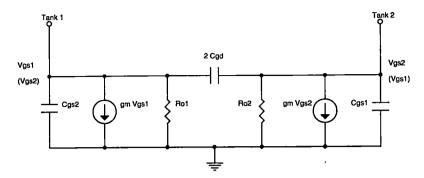

A detailed analysis of the AC characteristics of the differential pair can be derived through the use of the Hybrid-Pi model [20, 21]. This model accounts for the parasitic effects of the transistors, as well as the small signal gain. Because the goal of the differential pair is to present a negative impedance to the tank circuit, thereby restoring energy, it is useful to evaluate the Hybrid-Pi model in such a way that the input impedance can be obtained.

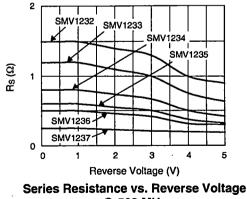

Figure 3.5: Hybrid-Pi model for cross-coupled differential transistor pair

The schematic in Figure 3.5 shows the circuit used for this evaluation. The Tank 1 and Tank 2 terminals represent the connections to the rest of the tank circuit. Each transistor is represented by an equivalent transconductance source, parasitic output resistance, and parasitic gate-source and gate-drain capacitances. Because the transistors are cross-coupled, the gate-drain capacitances appear in parallel with each other, thus doubling the capacitance between the transistors.

To analyze the input impedance seen by the tank circuit, the effects of each transistor can be represented as a single impedance block, Z1 and Z2, respectively, as seen in Figure 3.6. Assuming the transistors are well-matched, these impedances are equal, and can be obtained through the parallel combination of the transistor gate-source capacitance, transconductance, and output resistance.

$$Z_1 = Z_2 = \frac{1}{j\omega C_{gs}} \| \frac{1}{-g_m} \| r_o$$

3.10

$$= \left(j\omega C_{gs} - g_m + \frac{1}{r_o}\right)^{-1} \tag{3.11}$$

Figure 3.6: Equivalent impedance Hybrid-Pi model

$$Z_1 = Z_2 = \frac{r_o}{1 - g_m r_o + j\omega C_{gs} r_o}$$

3.12

The resulting impedance can then be combined with the parasitic gate-drain capacitances by employing the half-circuit technique. This additional capacitance is then in parallel with the gate-source capacitance. After combining all the parasitic effects of the differential transistor pair, the total input impedance seen by the tank circuit,  $Z_{in}$  is:

$$Z_{in} = \frac{2r_o}{1 - g_m r_o + j\omega r_o (C_{gs} + 4C_{gd})}$$

3.13

#### 3.3.6 VCO Resonant Frequency and Quality Factor

The remaining components of the tank circuit can be included in the Hybrid-Pi model to determine the complete characteristics of the VCO, as seen in Figure 3.7. At resonance, the energy contributed by the differential pair will exactly balance the energy lost in the tank due to the equivalent parallel resistance. The equivalent tank impedance can be found using the half-circuit technique, and includes the effects of all devices and parasitic

Figure 3.7: Hybrid-Pi model for complete tank circuit

effects in the tank circuit.

$$Z_{TANK} = \frac{j\omega L}{1 + j\omega L \left(\frac{1}{R_{p}} + \frac{1}{2r_{o}} - \frac{g_{m}}{2}\right) - \omega^{2}L\left(C_{gs} + 2C_{gd} + \frac{C \cdot C_{var}}{C + C_{var}}\right)}$$

3.14

Equation 3.14 reveals that if the negative impedance of the differential transistors is sufficiently large, it will cancel the loss due to the parasitic output resistance of the transistors and the equivalent parallel resistance of the tank. In fact, because the transconductance of the differential transistors directly controls their negative impedance, the condition for oscillation can be described in terms of a minimum  $g_m$  value:

$$g_m \ge \frac{1}{r_o} + \frac{2}{R_P} \tag{3.15}$$

This is an important result, demonstrating that the proper transconductance of the differential transistors will allow the impedance of the tank to become purely reactive, achieving a theoretically infinite quality factor.

The resonant frequency of the VCO can be obtained from Equation 3.14. The negative impedance of the transistors will cancel the first-order  $\omega$  term in the denominator. At the

resonant frequency, the second-order  $\omega$  term in the denominator is ideally equal to 1, which will result in an infinite parallel tank impedance. Using this information, the resonant frequency is therefore:

$$\omega_0 = \frac{1}{\sqrt{L \cdot \left(C_{gs} + 2C_{gd} + \left(\frac{C \cdot C_{var}}{C + C_{var}}\right)\right)}}$$

3.16

The quality factor of the circuit can also be obtained by evaluating Equation 3.14 if the transconductance is assumed to be less than the value required to completely cancel the parasitic resistances in the tank circuit.

$$g_m \le \frac{1}{r_o} + \frac{2}{R_P} \tag{3.17}$$

$$Q = \omega_0 \cdot \frac{C_{gs} + 2C_{gd} + \left(\frac{C \cdot C_{var}}{C + C_{var}}\right)}{\frac{1}{R_P} + \frac{1}{2r_o} - \frac{g_m}{2}}$$

3.18

Recalling from Equation 3.9 that the equivalent parallel tank resistance, R<sub>P</sub>, is significantly affected by the choice of capacitors for the tank circuit, it becomes apparent that these capacitors also affect the quality factor of the circuit. By maximizing the equivalent parallel tank resistance, the quality factor of the oscillator will also be maximized. This underscores the importance of selecting appropriate components for the tank circuit, balancing the requirements for operating frequency and tuning range against the need to minimize parasitic resistances.

#### 3.3.7 Biasing and Output Buffering

The tank circuit and differential transistors are biased through a current mirror (M3 and M4 in Figure 3.2). The use of a current mirror allows the differential output voltage to be current-limited with peak-to-peak voltages,  $V_{max}$ , in the range of

$$2I_{M3}R_P \le V_{mzx} \le 2V_{DD}$$

3.19

This range of peak-to-peak voltages is significantly higher than what would be achievable if the differential transistors were connected directly to ground, where  $V_{max} = V_{DD}$ . Current limiting occurs as long as the differential transistors are operating in the saturation region [22, 23]. If the output voltage drives these transistors into the linear region, the oscillation will stop because the transistors appear as resistors in parallel with the tank circuit. This condition is referred to as voltage limiting [22, 23].

To provide the capability to drive a 50- $\Omega$  load, the VCO incorporates source-followers to implement output buffering, allowing the output signals to be isolated from the tank circuit. This approach has two advantages. First of all, external adjustments can be made to the bias points of the differential transistor current mirror, as well as the output buffer current mirror, allowing the operation of the VCO to be optimized with respect to its current-limited and voltage-limited states. Secondly, the quality factor of the tank circuit is independent of the load on the output. Because the input impedance of the gate of a MOS device is quite large, there is no substantial reduction in the tank's equivalent parallel resistance. In fact, low-impedance loads connected directly to the tank output will greatly reduce the equivalent parallel resistance (and thus the Q of the tank circuit,

resulting in increased phase noise), and could potentially prevent the circuit from oscillating altogether [24].

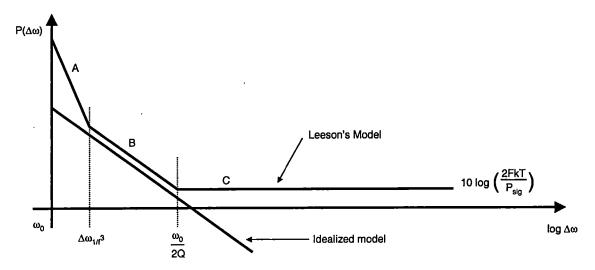

#### 3.3.8 Noise Effects and Design Tradeoffs

Several noise sources contribute to the overall output noise of the VCO, which is generally quantified in terms of phase noise. These include components in the tank circuit, the differential transistors, the output buffers, and the current mirrors. An ideal negative-g<sub>m</sub> oscillator, with noise effects due only to resistance in the tank, has an output noise spectrum described by the following equation, where k is Boltzmann's constant and T is the temperature in Kelvin [18]:

$$\frac{v^2}{\Delta f} = 4kTR_P \left(\frac{\omega_0}{2Q\Delta\omega}\right)$$

3.20

Inspection of this equation shows that the noise spectral density is not independent of frequency, due to the filtering of the tank circuit. This equation accounts for variations in both amplitude and phase of the output signal. Because all realizable circuits have some means of amplitude limiting, the amplitude variations are attenuated, leaving the phase variations as the dominant result of the tank noise. The equipartition theory of thermodynamics allows the assumption that without amplitude limiting, the tank noise energy splits equally between amplitude variations and phase variations [18]. Thus when amplitude limiting is applied, the total output noise is half of that expressed by Equation 3.20 [18]. By normalizing the output noise spectrum to the carrier power, a more

convenient expression for phase noise is obtained, where  $P_{\text{siq}}$  is the output carrier power

$$P(\Delta\omega) = 10 \cdot \log \left[ \frac{2kT}{P_{sig}} \cdot \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right]$$

3.21

The units of Equation 3.21 are dBc/Hz, specified at a given frequency offset from the carrier. Inspection of this equation shows that the phase noise will improve if the carrier power is increased, or if the quality factor is increased. The equation also demonstrates that the noise falls off in proportion to the inverse square of the frequency offset, yielding noise spectrums such as those presented in Figure 2.5.

While Equation 3.21 adequately describes the noise characteristics for an ideal oscillator, additional consideration must be given to the noise contributed by the active devices in the design, such as the differential transistors and output buffering. These additional effects are accounted for in Leeson's equation for phase noise, shown in Figure 3.8. The figure compares Leeson's model to the idealized model of Equation 3.21. Regions of specific interest are labeled A, B, and C in Figure 3.8. Leeson's model includes a scale factor F to account for additional noise in the  $1/(\Delta\omega)^2$  region (region B), a unity addition factor to account for the 'noise floor' (region C), and an additional scale factor to account for additional noise at frequency offsets very close to the carrier (region A) [18]. Leeson's equation for phase noise is:

$$P(\Delta\omega) = 10 \cdot \log \left\{ \frac{2FkT}{P_{sig}} \cdot \left[ 1 + \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right] \cdot \left( 1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|} \right) \right\}$$

3.22

The various scale factors associated with Leeson's model are not always related to a physical device characteristic, and thus are generally treated as curve-fitting parameters.

Figure 3.8: Comparison of phase noise models

Adapted from: Thomas H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge

University Press, 1998.

Other, more advanced models of phase noise, such as the Hajimiri model, take into account additional factors such as non-linearity and time-variance, both of which affect the phase noise of a real oscillator [10].

Leeson's model shows that noise generated by active devices in the circuit will cause phase noise in the output signal. For instance, noise associated with the differential transistor current mirror will be modulated to the resonant frequency of the oscillator. Effects such as this are observed in region A of Figure 3.8. Noise associated with the output buffers will add to the overall noise floor of the oscillator, as seen in region C. The additional phase noise resulting from these components presents an interesting design tradeoff. The current mirror allows an increase in the resonant tank peak-to-peak voltage, which helps to reduce phase noise. Likewise, the output buffers are required to prevent the tank circuit Q from being severely degraded. Therefore, the design must balance the

benefits of these additional devices against their potential effect on the output phase noise.

#### 3.4 High Temperature Considerations

The VCO is required to operate over a temperature range from room temperature (25 °C) up to 200 °C. This wide temperature range raises several important issues which must be addressed in the design of the VCO. First of all, the gain (Hz/volt) of the VCO should stay constant or nearly constant over the entire temperature range. This will ensure that the stability of the PLL will not be affected by a change in the VCO. Secondly, the passive components of the VCO should have minimal deviation over temperature [25]. This will maintain the Q of the tank, as well as keep the operating frequency constant for a fixed control voltage. Finally, the transistors used must continue to operate at high temperature, without compromising the output voltage swing requirements necessary to drive the rest of the PLL.

The majority of the design of the VCO was done using room-temperature parameters, allowing the design to be optimized with respect to its operating characteristics. After a suitable set of component values and transistor sizes was determined, the design was simulated over temperature using HSPICE [26] as discussed in Section 3.6. Because the simulator uses complex thermal models in its calculations, a relatively good prediction can be made about the operation of the circuit at a given temperature. In fact, the results of initial temperature simulations prompted a few adjustments, such as the sizing of the output buffer transistors, to optimize the performance of the VCO over the entire range of operating temperatures.

#### 3.5 Preliminary Design

The resonant tank components of the VCO were initially determined using hand calculations based on the formulas presented in Section 3.3.6. Because the varactor diodes control the tuning range of the VCO, the selection of an appropriate device was critical to achieving the 100 MHz tuning range. Secondary considerations involved the inductors and coupling capacitors, which predominantly control the center frequency of the VCO. Using a spreadsheet analysis, suitable component values were determined, and are listed in Table 3.2.

Approximate bias points for the circuit were obtained by first determining the  $g_m$  value necessary to achieve oscillation in the resonant tank. This value was calculated using Equation 3.15 with a calculated equivalent parallel tank resistance of 546 ohms at 300 MHz. The minimum  $g_m$  required for oscillation was calculated to be 3.68 mS. To establish this bias condition in the differential transistor pair, the bias current for each device was calculated to be approximately 500 uA. The transistors of the tank and the associated current mirror were sized to achieve the appropriate bias. To isolate the VCO output load from the resonant tank and provide increased output drive capability, the output buffer transistors were biased at a quiescent current of approximately 15 mA. The  $g_m$  of the source-following transistors was approximately 35 mS. Current mirrors

Table 3.2: VCO tank circuit component values

| Component | Value     |

|-----------|-----------|

| Inductor  | 18 nH     |

| Coupling  | 22 pF     |

| Capacitor |           |

| Varactor  | 9 - 28 pF |

associated with the output buffers were sized to handle the current requirements of the output load. Pre-layout simulations were used to refine the initial design.

#### 3.6 Simulation and Layout Techniques

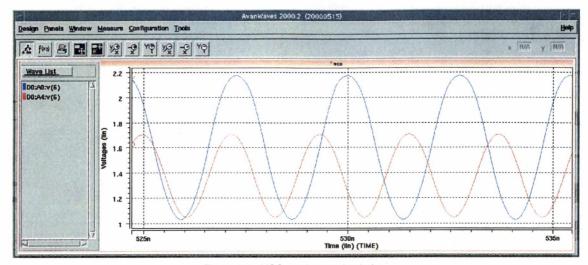

After the initial design of the VCO was completed, the circuit was simulated using HSPICE to evaluate its performance over the entire range of operating temperatures. The simulation accounted for anticipated parasitic effects to more accurately model the real-world circuit behavior. A subcircuit model was generated for the varactor diodes, according to the manufacturer's suggested parameters, as discussed in Section 3.3.2. The complete HSPICE file used for pre-layout simulations is included in Appendix A, and includes all device sizes. Low-threshold devices, available in the fabrication process, were used to improve the voltage range of the output. Results of the pre-layout simulation showed that the VCO would perform acceptably over the required operating parameters, including frequency range, output drive, and temperature. In addition, several preliminary design calculations were validated, including the g<sub>m</sub> value required to achieve oscillation (3.8 mS simulated as compared to 3.68 mS calculated).

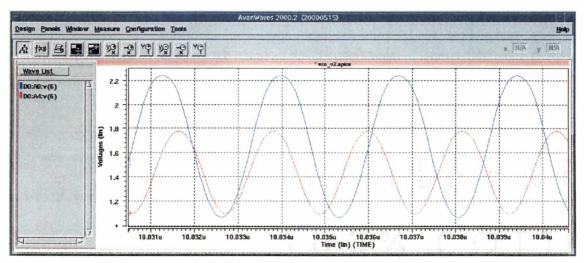

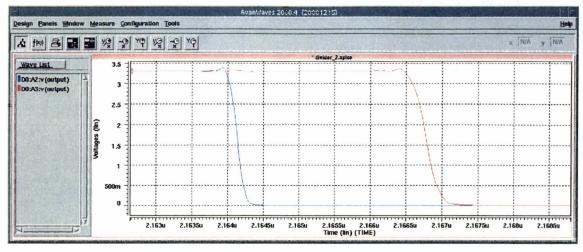

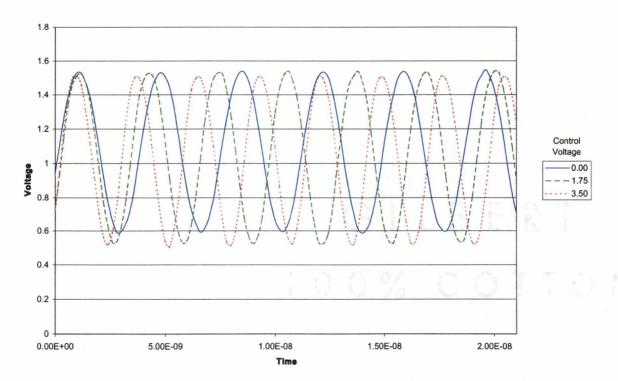

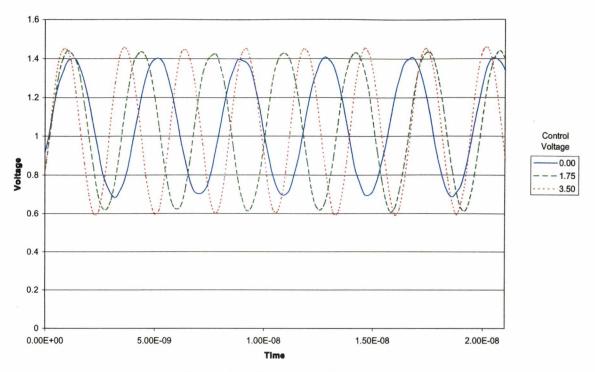

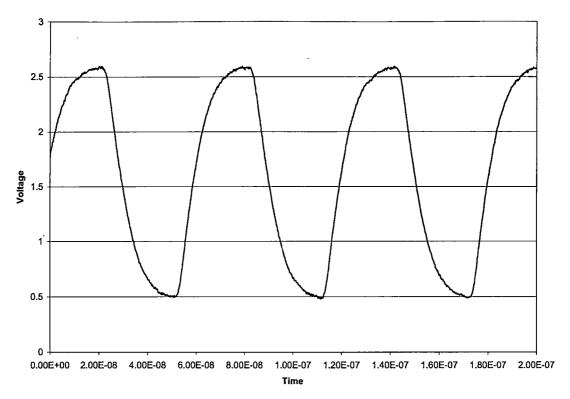

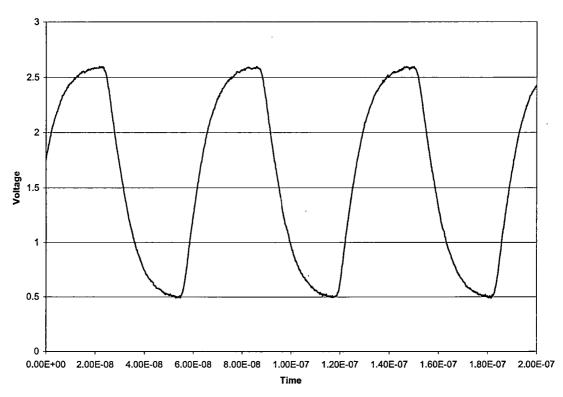

Figure 3.9 shows the results of a pre-layout simulation of the VCO over temperature. The blue trace reflects operation at 25 °C, while the red trace represents 200 °C. The control voltage in this simulation is 3.0 V, resulting in an oscillation frequency of approximately 357 MHz at 25 °C. Several effects of temperature are immediately obvious from the simulation, including a drop in output drive capability, as well as an increase in operating frequency by 25% to approximately 450 MHz. Both of these effects were anticipated, but do not pose a significant problem to the operation of the PLL. The VCO output is still

Figure 3.9: VCO pre-layout simulation Blue: 25 °C output, Red: 200 °C output Source file: Appendix A.1. Vdd = 3.3V, Vcontrol = 3.0V

capable of driving the 50-ohm load, and the tuning range of the VCO is sufficient to allow the PLL to correct for the shift in frequency. In addition, the simulation shows virtually no distortion of the output waveform at either of the two temperature extremes. This is a very valuable result, since distortion of the waveform would introduce additional phase noise in the PLL output. Further simulations revealed the tuning range of the VCO, shown in Table 3.3.

Layout of the VCO was done by hand using the MAGIC software package [27]. A 'foundry rules' technology file for the Peregrine technology was used. In this technology file, the minimum incremental size was 0.1 um, commonly referred to as 'lambda' ( $\lambda$ ). However, the minimum gate length in the process was 0.5 um, or 5 $\lambda$ . This contrasts to

Table 3.3: VCO pre-layout simulation results

| Parameter     | 25 °C   | 200 ºC  |

|---------------|---------|---------|

| Min frequency | 240 MHz | 290 MHz |

| Max frequency | 357 MHz | 440 MHz |

typical scalable-CMOS design rules, where the minimum gate length is  $2\lambda$ . Foundry rules provide the designer with a higher degree of precision, while SCMOS designs have the advantage of being easily translated and scaled between various processes.