#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

Masters Theses Graduate School

5-2000

# Development of a 6-bit 15.625 MHz CMOS two-step flash analogto-digital converter for a low dead time sub-nanosecond time measurement system

Brian Keith Swann

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

#### **Recommended Citation**

Swann, Brian Keith, "Development of a 6-bit 15.625 MHz CMOS two-step flash analog-to-digital converter for a low dead time sub-nanosecond time measurement system." Master's Thesis, University of Tennessee, 2000.

https://trace.tennessee.edu/utk\_gradthes/9497

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Brian Keith Swann entitled "Development of a 6-bit 15.625 MHz CMOS two-step flash analog-to-digital converter for a low dead time subnanosecond time measurement system." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

James M. Rochelle, Major Professor

We have read this thesis and recommend its acceptance:

T. Vaughn Black, Danny F. Newport, David M. Binkley

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

#### To the Graduate Council:

I am submitting herewith a thesis written by Brian Keith Swann entitled "Development of a 6-bit 15.625MHz CMOS Two-Step Flash Analog-to-Digital Converter for a Low Dead Time Sub-Nanosecond Time Measurement System." I have examined the final copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering

arrite,

Dr. James M. Rochelle, Major Professor

We have read this thesis and recommend its acceptance.

Dr. T. Vaughn Blalock

Dr. Danny F. Newport

Dr. David M. Binkley

Accepted for the Council:

Associate Vice Chancellor and Dean of The Graduate School

## Development of a 6-bit 15.625 MHz CMOS Two-Step Flash Analog-to-Digital Converter for a Low Dead Time Sub-Nanosecond Time Measurement System

A Thesis

Presented for the

Master of Science

Degree

The University of Tennessee, Knoxville

Brian Keith Swann May 2000

## **Dedication**

This thesis is dedicated to my parents Robert L. and Bertie L. Swann who have sacrificed much to give me unlimited opportunities in life which they never had and to my brother Rodger M. Swann who has always been there for me no matter what the circumstances.

#### **Acknowledgements**

I would like to thank many people who have made this work possible. First, I would like to thank the members of my committee, which include Drs. J. M. Rochelle, my major professor, D. M. Binkley, T. V. Blalock, and D. F. Newport. Special gratitude and recognition goes to Dr. Blalock who served on my committee as an emeritus faculty member. Also, I would like to thank and recognize Dr. E. J. Kennedy for teaching and providing me with a good foundation in analog electronics as an undergraduate student.

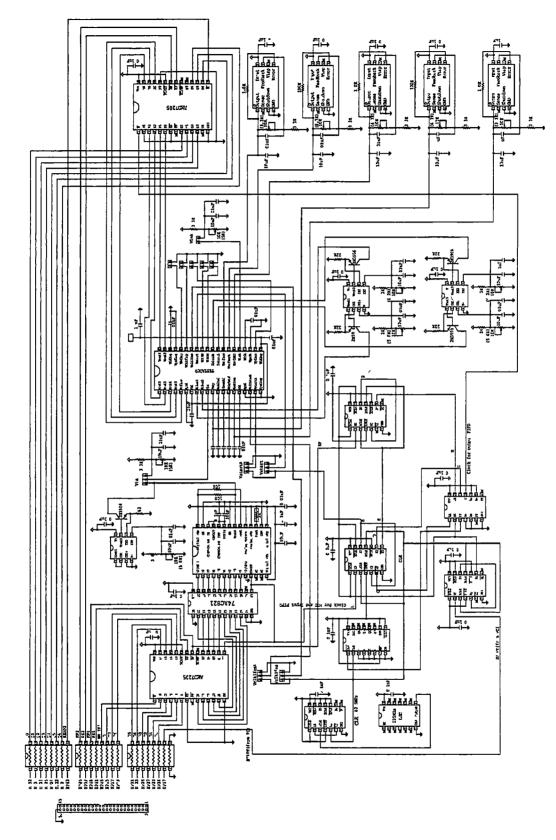

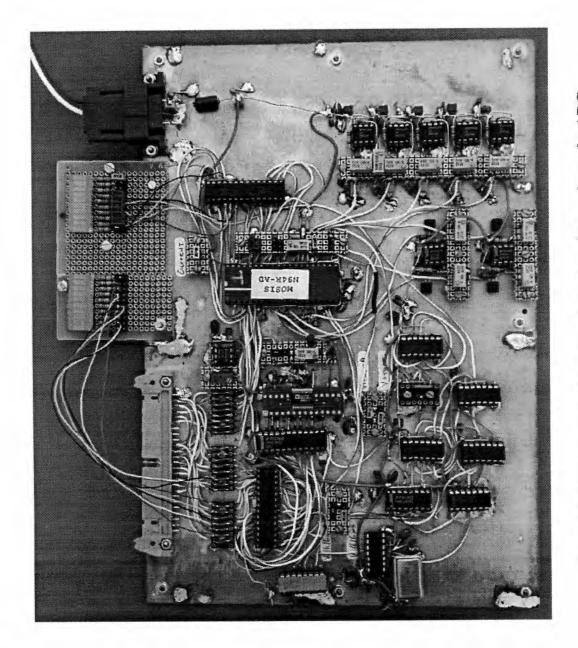

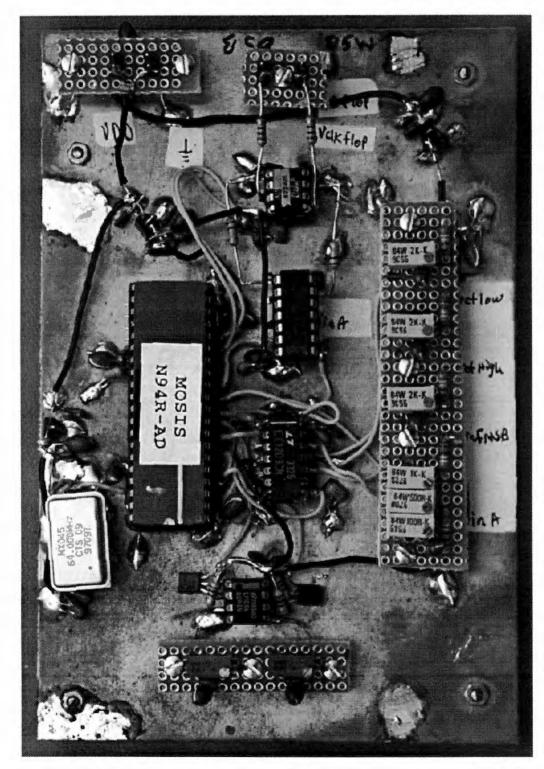

I would like to acknowledge my employer, Concorde Microsystems, Inc., for supporting my graduate school education and providing the opportunity to do this work. Many individuals at Concorde Microsystems were supportive of this research. First, I would like to express my appreciation to Dr. David Binkley. Dave was one of the people responsible for getting me interested in integrated circuit design and has been without question, one of the most influential people in my engineering career Also, I would like to thank Dr. Jim Rochelle who also has played a large role in my educational and career development at Concorde Microsystems. I would like to thank and recognize Lloyd Clonts who designed the ADC control logic and encoder based upon my specifications and provided CAD tool support. Charles Landen was tremendously supportive during this research. Charles assisted in extensive literature reviews, constructed a comparator test board (Figure 5-11), assisted in making many difficult laboratory measurements, and helped with data collection and presentation. Also, I would like to thank Mark Long of CTI PET Systems, Inc. who constructed the complex ADC test circuit (Figure 5-3) Many discussions of ideas with Scott Puckett were also beneficial in this research. Stefan Siegel

provided encouragement and many insightful discussions on the fundamentals of PET.

Additionally, Robert Nutt and Rhonda Goble offered continuing support throughout my work. Finally, I would like to thank Allen Blalock for his encouragement to unconditionally finish my Master's degree.

#### Abstract

The development of a 6-bit 15.625 MHz CMOS two-step analog-to-digital converter (ADC) is presented. The ADC was developed for use in a low dead time, high-performance, sub-nanosecond time-to-digital converter (TDC). The TDC is part of a new custom CMOS application specific integrated circuit (ASIC) that will be incorporated in the next generation of front-end electronics for high-performance positron emission tomography imaging.

The ADC is based upon a two-step flash architecture that reduces the comparator count by a factor-of-two when compared to a traditional flash ADC architecture and thus a significant reduction in area, power dissipation, and input capacitance of the converter is achieved. The converter contains time-interleaved auto-zeroed CMOS comparators. These comparators utilize offset correction in both the preamplifier and the subsequent regenerative latch stage to guarantee good integral and differential non-linearity performance of the converter over extreme process conditions. Also, digital error correction was employed to overcome most of the major metastability problems inherent in flash converters and to guarantee a completely monotonic transfer function.

Corrected comparator offset measurements reveal that the CMOS comparator design maintains a worse case input-referred offset of less than 1 mV at conversion rates up to 8 MHz and less than a 2 mV offset at conversion rates as high as 16 MHz while dissipating less than 2.6 mW. Extensive laboratory measurements indicate that the ADC achieves differential and integral non-linearity performance of less than ±½ LSB with a 20 mV/LSB resolution. The ADC dissipates 90 mW from a single 5 V supply and occupies a die area of 1.97 mm x 1.13 mm in 0.8 μm CMOS technology.

## **Table of Contents**

| 1. Introduction                                                    | 1   |

|--------------------------------------------------------------------|-----|

| 1.1 Time Measurement Application for Positron Emission Tomography  | 1   |

| 1.2 Time Measurement System Description and Requirements           |     |

| 1.2.1 Time Measurement Overview                                    | 3   |

| 1.2.2 TDC Specifications and Design Requirements                   |     |

| 1.2.3 ADC Specifications and Design Requirements                   |     |

| 1.3 Thesis Organization                                            |     |

| 2. ADC Architecture Selection and Description                      |     |

| 2.1 ADC Overview and Architecture Requirements                     |     |

| 2.2 Traditional Flash ADC Architecture                             |     |

| 2.3 Two-Step Flash ADC Architecture                                | 23  |

| 3. ADC Design and Analysis                                         |     |

| 3.1 Comparator Design and Analysis                                 |     |

| 3.1.1 Comparator Overview and Fundamentals                         |     |

| 3.1.2 Motivation for an Auto-zeroed Comparator                     | 33  |

| 3.1.3 Limitations of Offset Cancellation Due to Charge Injection   |     |

| 3.1.3.1 Channel Charge Injection Effects                           |     |

| 3.1.3.2 Clock Feedthrough Effects                                  |     |

| 3.1.3.3 Techniques to Minimize Charge Injection in CMOS Circuits   |     |

| 3.1.4 Comparator Offset Cancellation Techniques                    |     |

| 3.1.4.1 Input Offset Storage                                       |     |

| 3.1.4.2 Output Offset Storage                                      | 58  |

| 3.1.4.3 Multi-Stage Offset Storage                                 |     |

| 3.1.5 Comparator Architecture Selection and Channel Implementation | 65  |

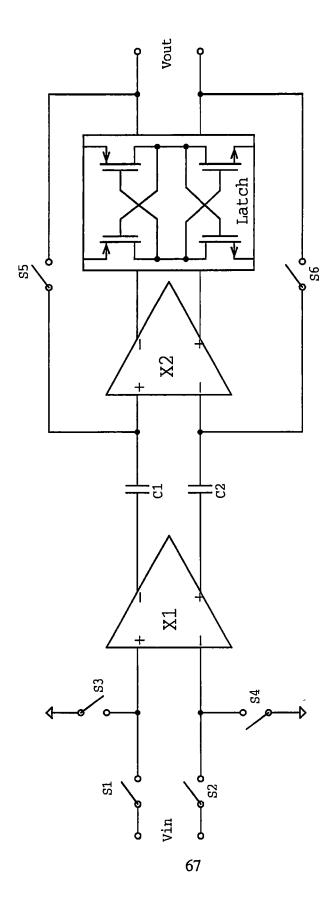

| 3.1.5.1 Comparator Offset Correction Topology                      | 65  |

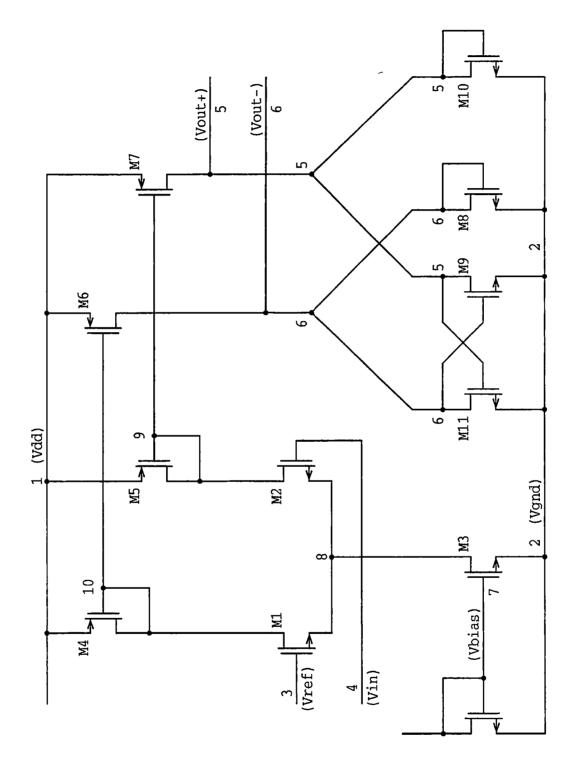

| 3.1.5.2 Preamplifier Design and Analysis                           | 68  |

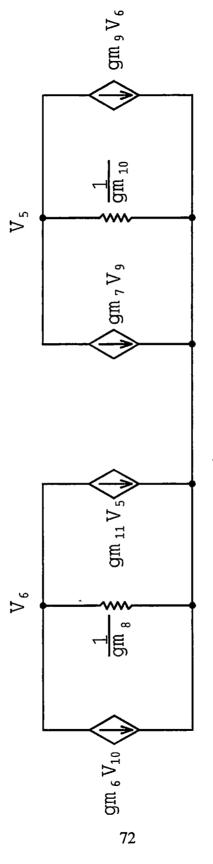

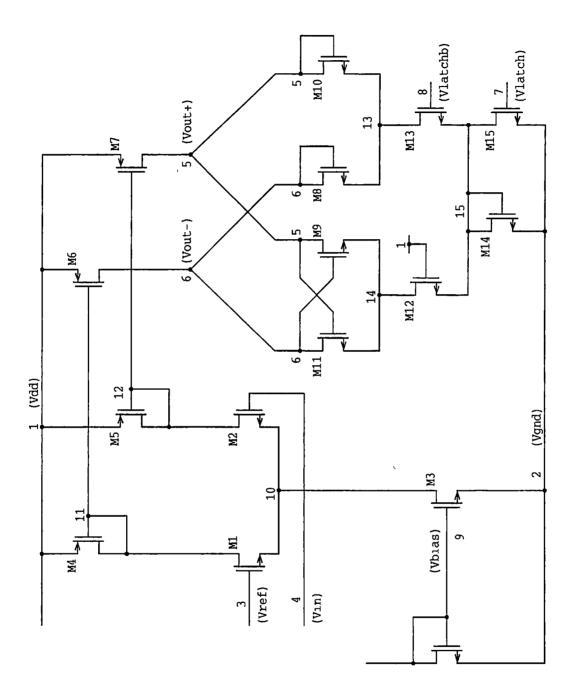

| 3.1.5.3 Regenerative Latch Design and Analysis                     | 78  |

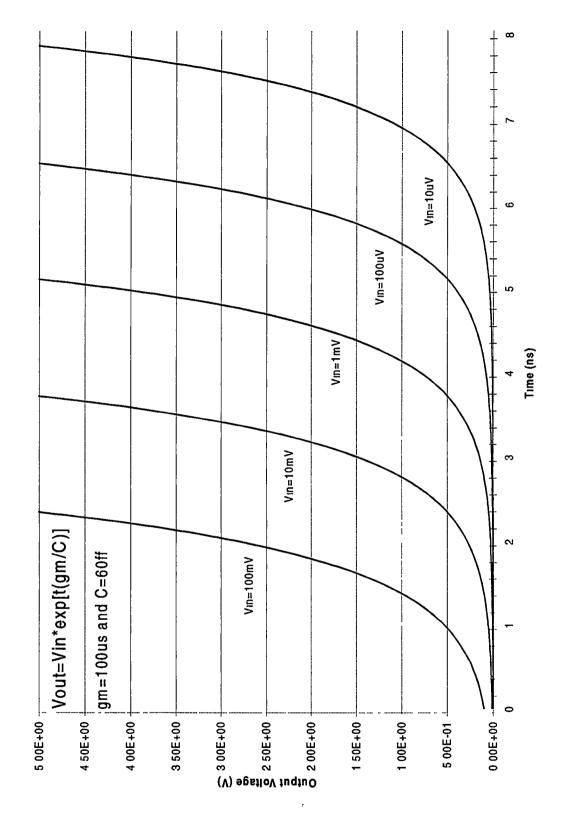

| 3.1.5.4 MSB and OSB Comparator Channel Integration                 | 87  |

| 3.2 Reference Generation Circuitry and Analysis                    | 92  |

| 3.3 ADC Non-linearity Analysis                                     | 97  |

| 3.4 Digital Error Correction and Encoder Description               | 99  |

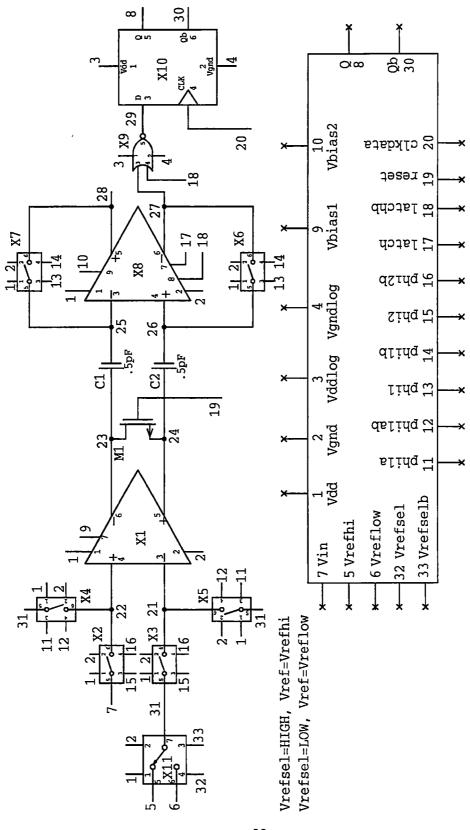

| 3.5 ADC Timing Information and Digital Controller Requirements     | 104 |

| 4. ADC Transistor Level Design, Layout, and Simulation             |     |

| 4.1 Preamplifier Design, Layout, and Simulation                    |     |

| 4.2 Regenerative Latch Design, Layout, and Simulation              |     |

| 4.3 Comparator Channel Design, Layout, and Simulation              |     |

| 4.4 Reference Generation Design, Layout, and Simulation            |     |

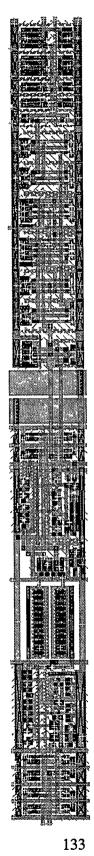

| 4.5 ADC Prototype Chip Design, Layout, and Simulation              | 134 |

| 5. Experimental Results                  |     |

|------------------------------------------|-----|

| 5.1 ADC Evaluation and Characterization  | 141 |

| 5.1.1 ADC Test Methodology and Circuitry | 141 |

| 5.1.2 DC Sweep Input Measurements        |     |

| 5.1.3 Dynamic Code Density Measurements  |     |

| 5.2 Comparator Offset Measurements       | 158 |

| 6. Conclusions                           |     |

| 6.1 Summary                              | 164 |

| 6.2 Suggested Design Improvements        |     |

| List of References                       | 168 |

| Vita                                     | 173 |

# **List of Tables**

| Table 2-1. Truth table for classical 3-bit flash ADC.                    | 22  |

|--------------------------------------------------------------------------|-----|

| Table 2-2. Truth table for 3-bit two-step flash ADC.                     | 27  |

| Table 5-1. Corrected comparator offset measurements at 8 MHz and 16 MHz. | 162 |

# **List of Figures**

| Figure 1-1. | Basic principles of PET event coincidence detection2                                            |

|-------------|-------------------------------------------------------------------------------------------------|

| Figure 1-2. | Block diagram of the high-performance LSO PET front-end ASIC 4                                  |

| Figure 1-3. | TDC system level timing signals                                                                 |

| Figure 1-4  | Block diagram of TDC architecture                                                               |

| Figure 1-5. | TDC conversion timing diagram                                                                   |

| Figure 1-6. | TDC conversion timing diagram with sample-and-hold implementation 14                            |

| Figure 2-1. | Block diagram of a classical 3-bit flash ADC architecture                                       |

| Figure 2-2  | Block diagram of a 3-bit two-step flash ADC architecture                                        |

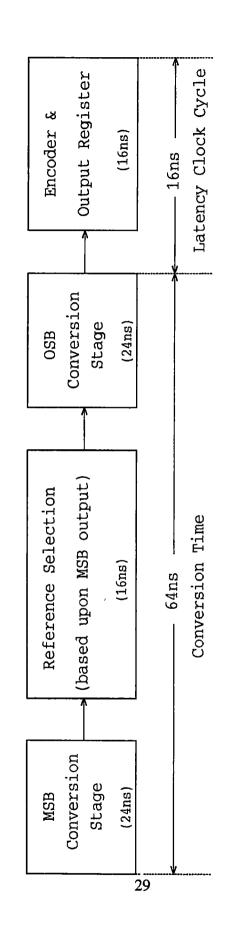

| Figure 2-3. | Preliminary timing diagram of proposed 6-bit two-step flash ADC 29                              |

| Figure 2-4. | Block diagram of the 6-bit two-step flash ADC architecture                                      |

| Figure 3-1. | Circuit symbol and transfer function of an ideal voltage comparator 32                          |

| Figure 3-2. | Ideal comparator transfer function including offset voltage effects 35                          |

| Figure 3-3. | Two adjacent comparators in a flash or flash-type ADC architecture 37                           |

| Figure 3-4. | ADC transfer function with a missing code due to excessively large comparator offsets 40        |

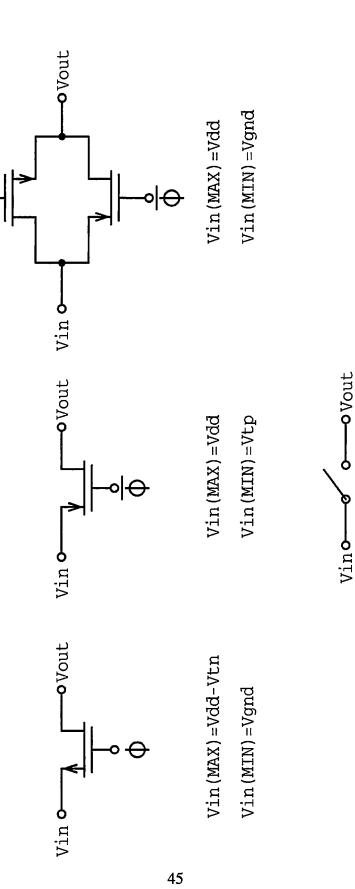

| Figure 3-5. | Typical analog switch configurations available in CMOS technology 45                            |

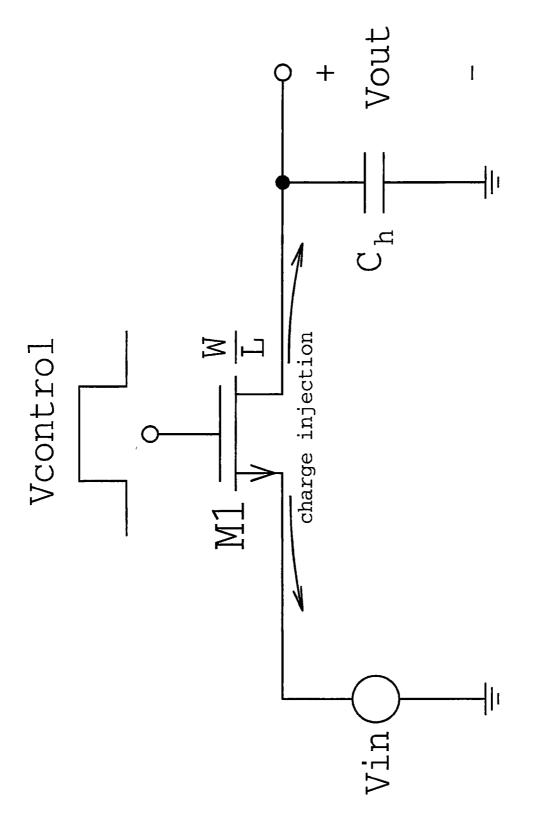

| Figure 3-6. | Simple circuit configuration using a NMOS switch to illustrate channel charge injection effects |

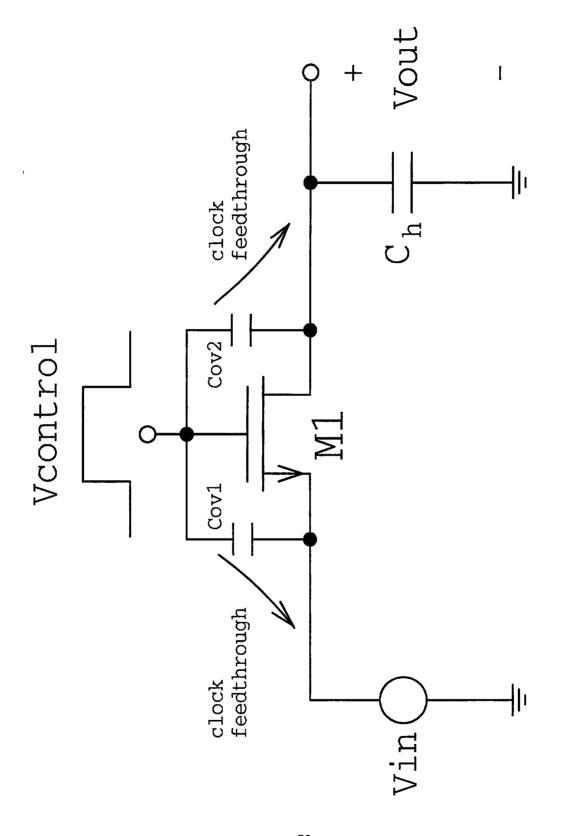

| Figure 3-7. | Simple circuit configuration using a NMOS switch to illustrate capacitive feedthrough effects   |

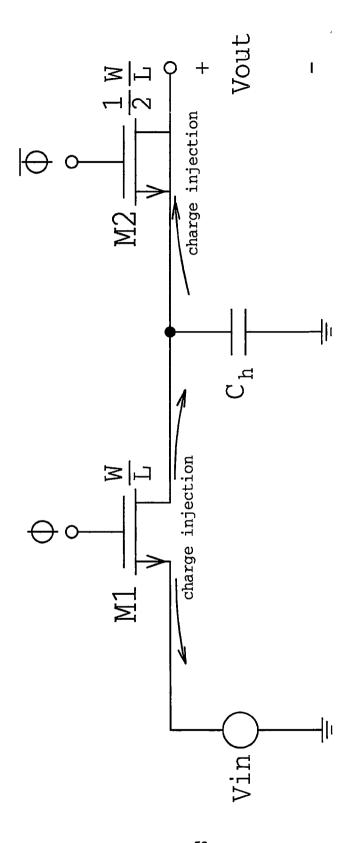

| Figure 3-8. | Simple circuit illustrating the use of a compensation transistor to minimize charge injection   |

| Figure 3-9. | Input offset storage calibration technique applied to a fully differential comparator           |

| Figure 3-10. Output offset storage calibration technique applied to a fully differential comparator      |

|----------------------------------------------------------------------------------------------------------|

| Figure 3-11. Multi-stage offset storage calibration technique applied to a fully differential comparator |

| Figure 3-12. Timing diagram for a three-stage MSOS comparator architecture 64                            |

| Figure 3-13. Fully differential comparator offset correction topology implemented in the 6-bit ADC       |

| Figure 3-14. Schematic diagram of the preamplifier used in the offset corrected comparator architecture  |

| Figure 3-15. Small signal equivalent circuit of the output gain stage in the preamplifier                |

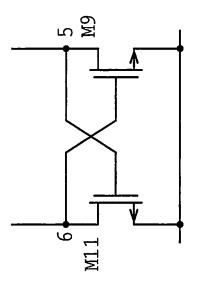

| Figure 3-16. Schematic diagram of the regenerative latch used in the offset corrected comparator channel |

| Figure 3-17. Small signal equivalent circuit of the regenerative output stage in the latch circuit       |

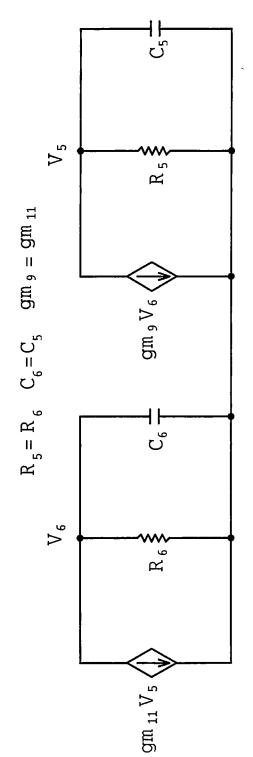

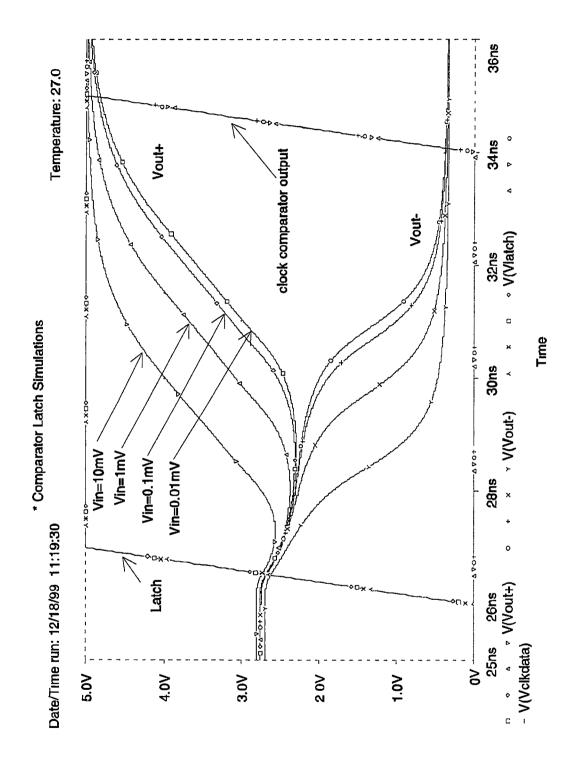

| Figure 3-18. Regenerative latch response for different levels of input voltage overdrive                 |

| Figure 3-19. Most significant bit (MSB) offset corrected comparator channel                              |

| Figure 3-20. Other significant bits (OSB) offset corrected comparator channel 89                         |

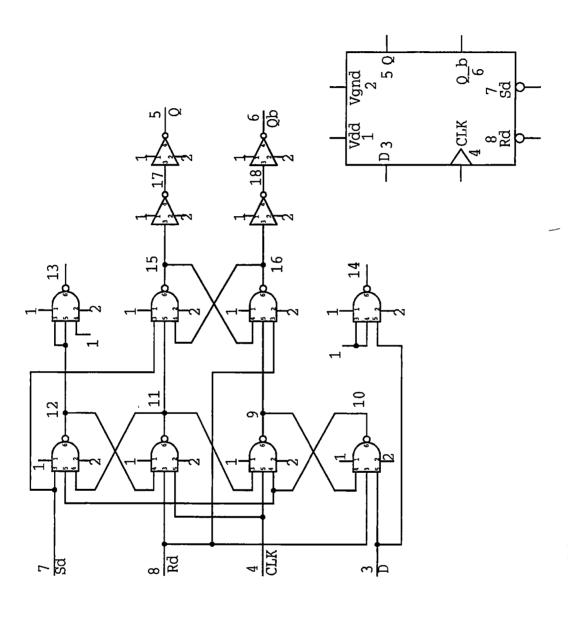

| Figure 3-21. Schematic diagram of the high-performance D flip-flop used in the comparator channel        |

| Figure 3-22. An example of a thermometer code in a classical 3-bit flash ADC 100                         |

| Figure 3-23. Limited digital error correction provided from 3-input NAND gates 101                       |

| Figure 3-24. An example of comparator metastability in a 3-bit flash ADC 103                             |

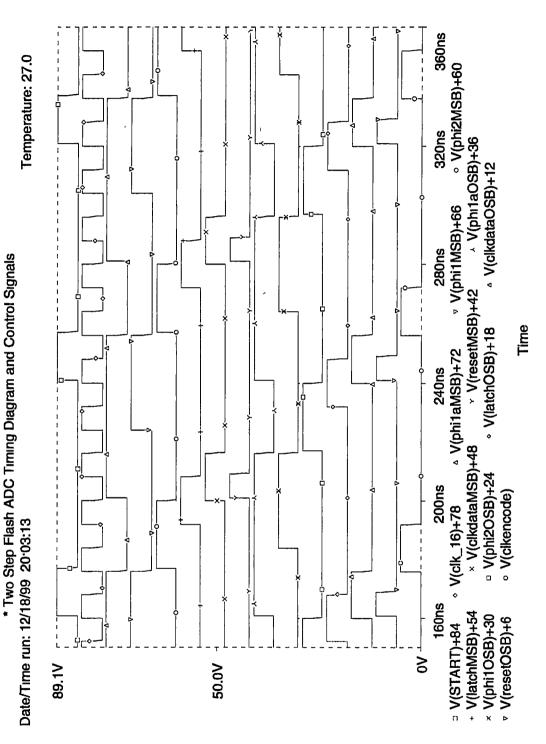

| Figure 3-25. Two-step flash ADC timing diagram and control signals                                       |

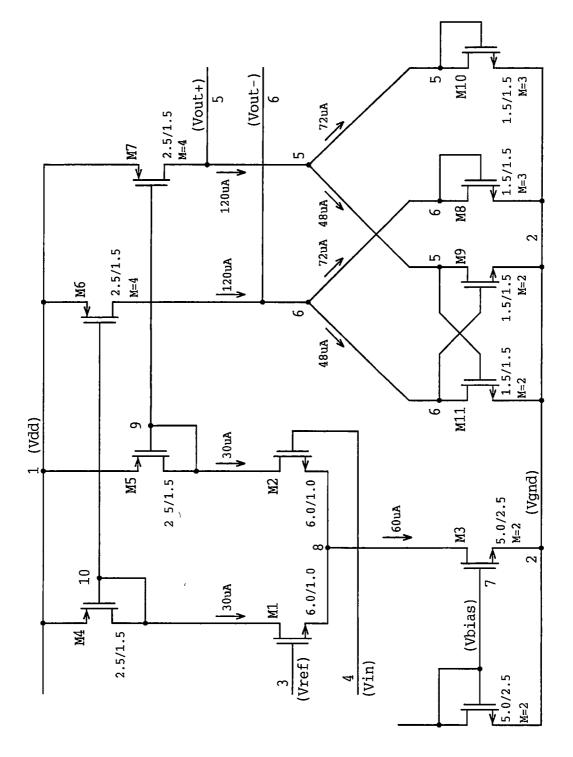

| Figure 4-1. Schematic diagram of preamplifier including transistor sizes (in µm) and bias currents       |

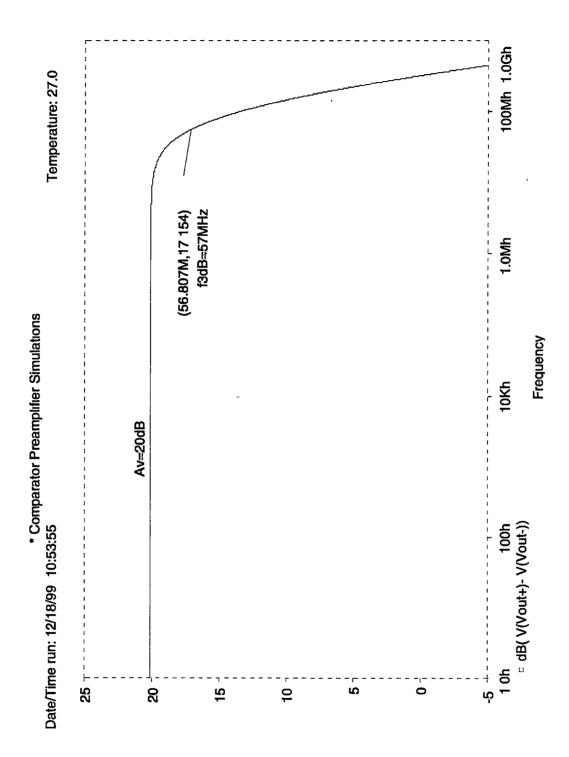

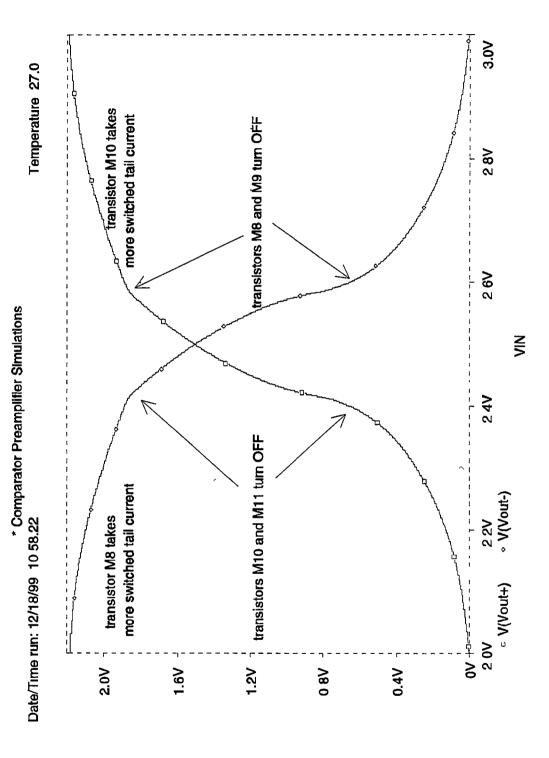

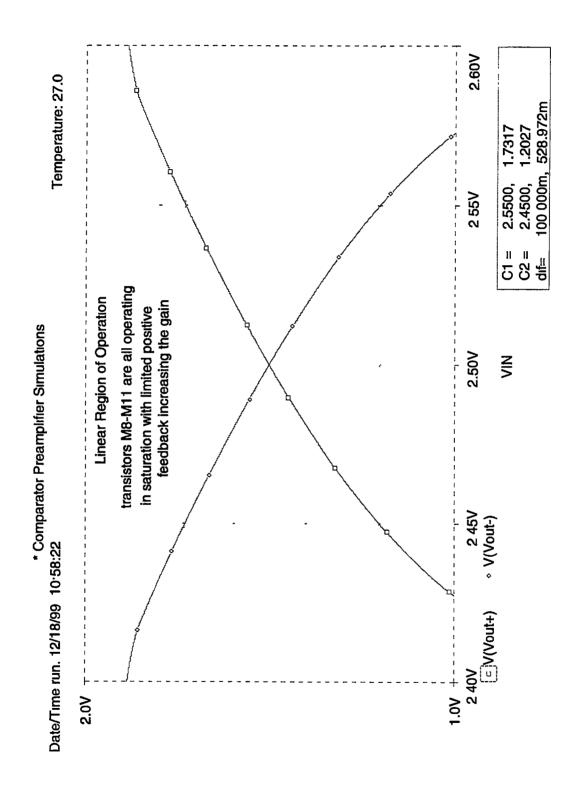

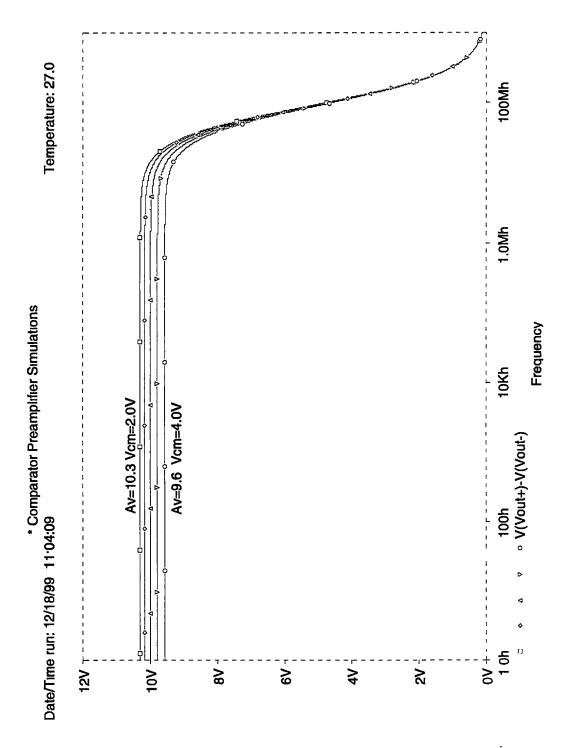

| Figure 4-2. Frequency response of the preamplifier with a 75 fF load capacitance 109                     |

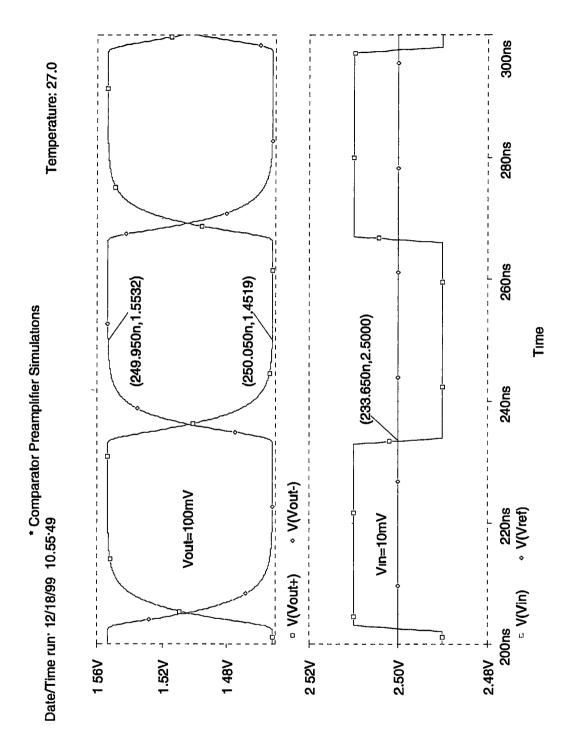

| Figure 4-3. Transient response of the preamplifier with a 10 mV input overdrive. signal.                        | l 1      |

|-----------------------------------------------------------------------------------------------------------------|----------|

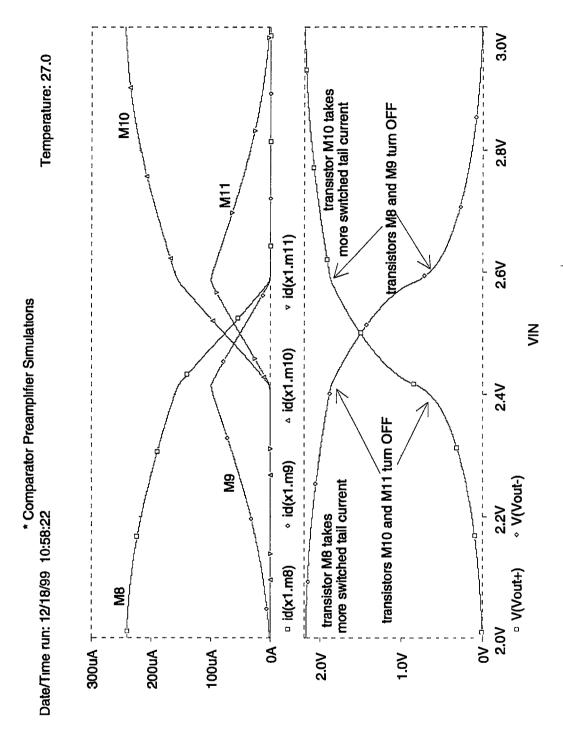

| Figure 4-4. DC sweep response giving the Vout vs. Vin transfer function of the preamplifier                     | l2       |

| Figure 4-5. DC sweep response showing the preamplifier's linear region of operation.                            | ا3       |

| Figure 4-6. DC sweep response of the preamplifier showing device currents and bias conditions                   | <b>4</b> |

| Figure 4-7. Preamplifier gain variation as a function of a 2-volt common-mode input range                       | 16       |

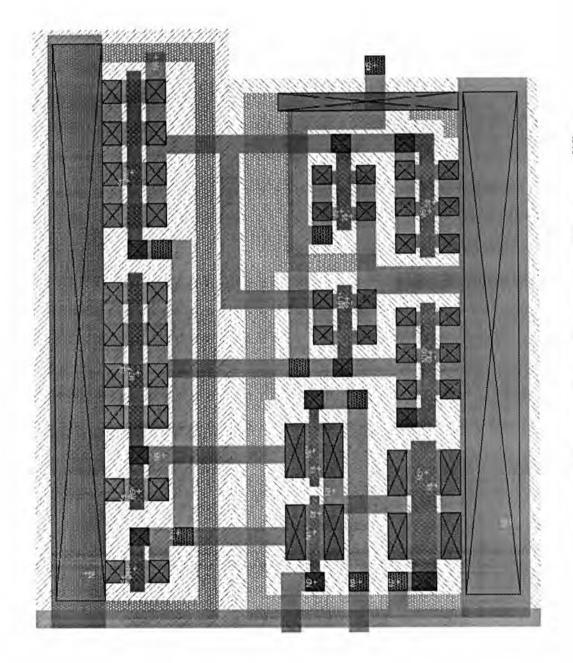

| Figure 4-8. Integrated circuit layout plot of the preamplifier                                                  | .8       |

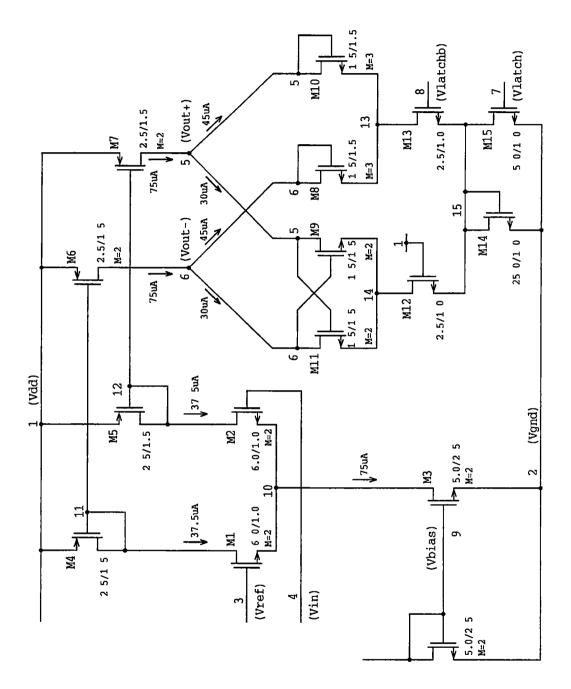

| Figure 4-9. Schematic diagram of regenerative latch including transistor sizes (in µm) and bias currents        | 9        |

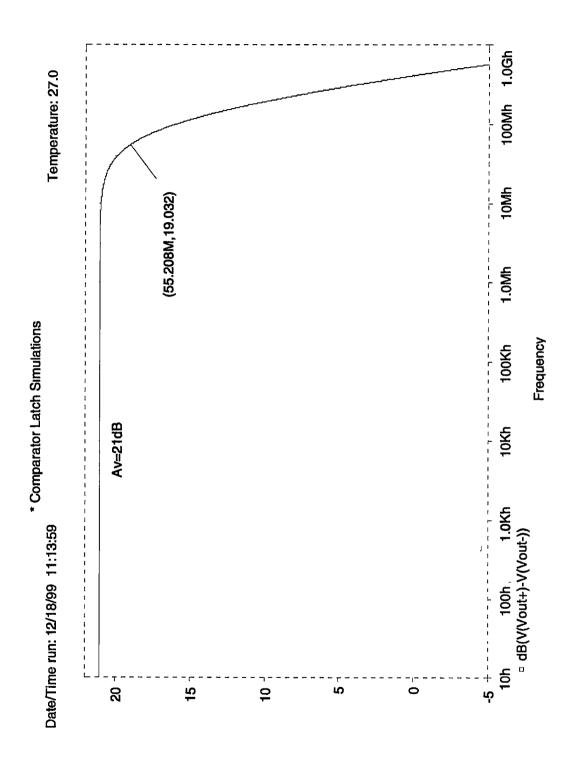

| Figure 4-10. Frequency response of the regenerative latch in compare mode with a 25 fF load capacitance         |          |

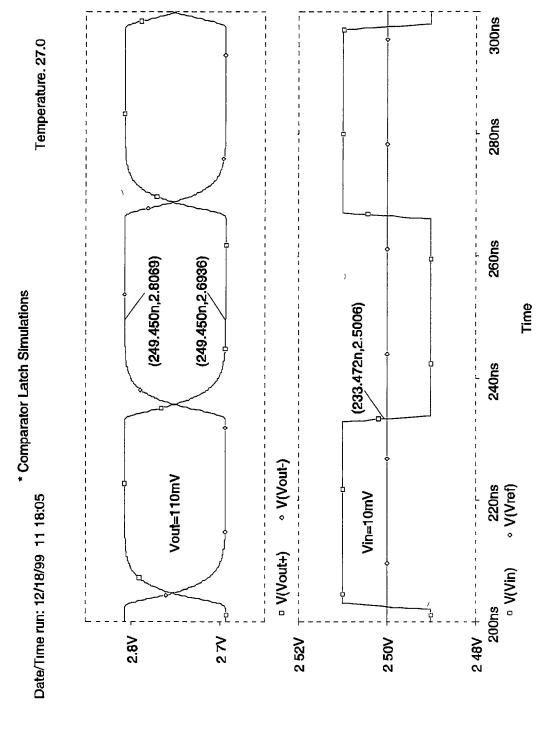

| Figure 4-11. Transient response of the regenerative latch in compare mode with a 10 mV input overdrive          |          |

| Figure 4-12. Transient response of the regenerative latch in latch mode for different levels of input overdrive | :3       |

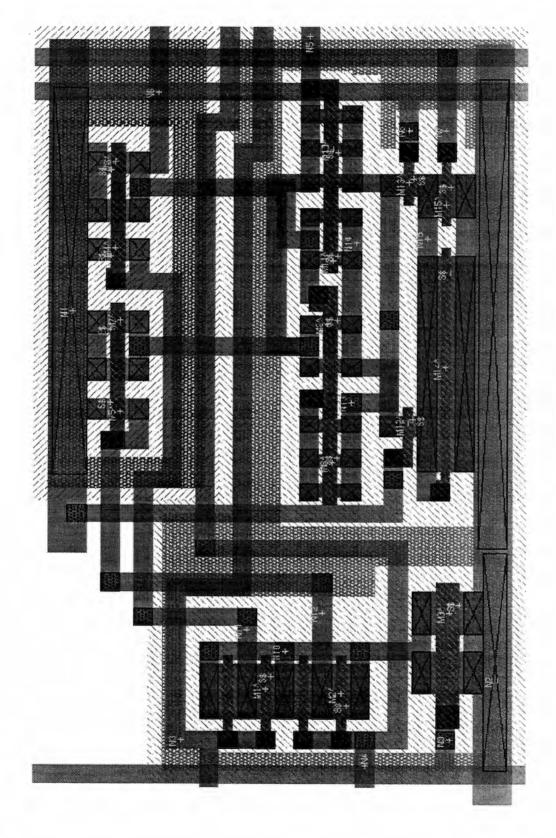

| Figure 4-13. Integrated circuit layout plot of the regenerative latch 12                                        | .4       |

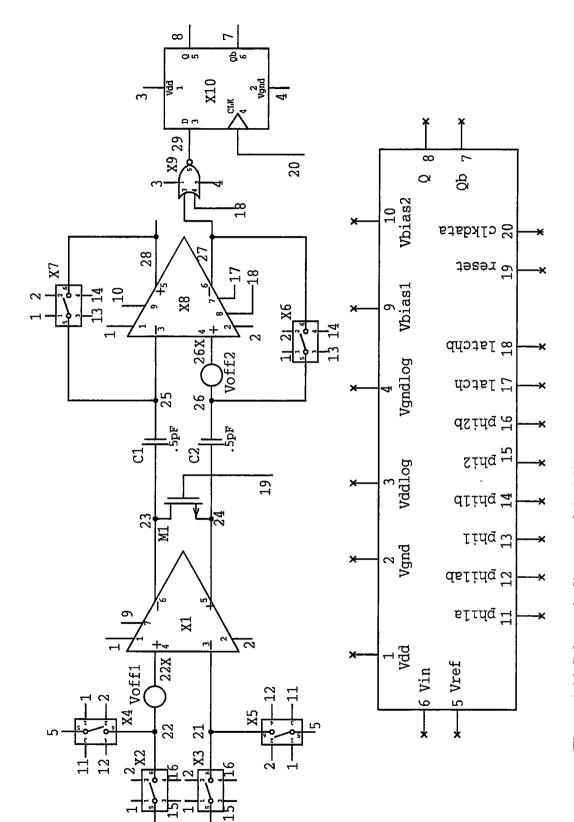

| Figure 4-14. Schematic diagram of the MSB comparator channel with offset voltage generators                     | :6       |

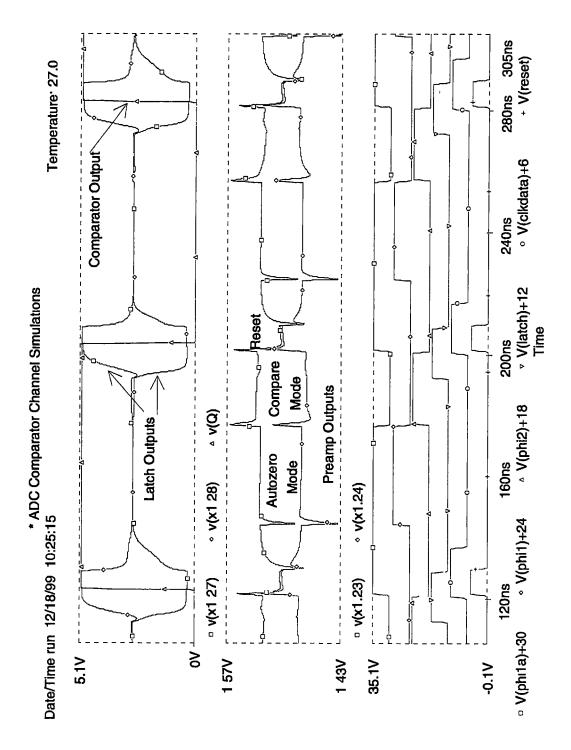

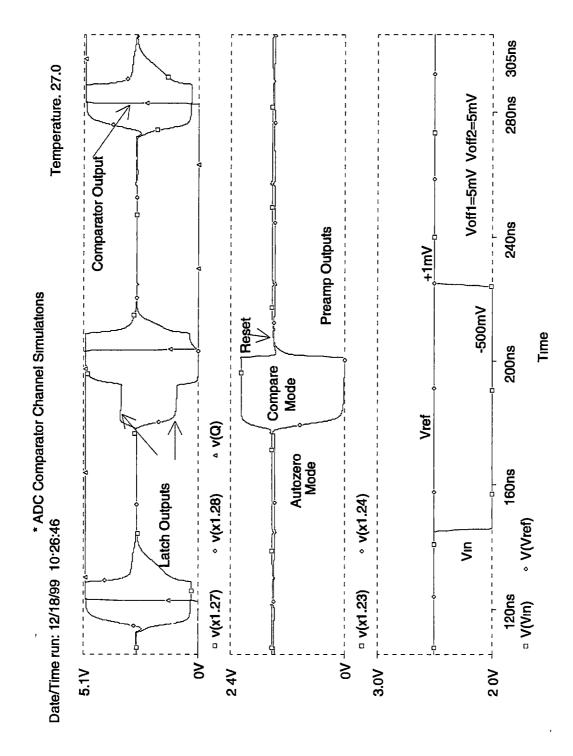

| Figure 4-15. Transient response of comparator channel with 1 mV input overdrive and 5 mV offsets                | Ω        |

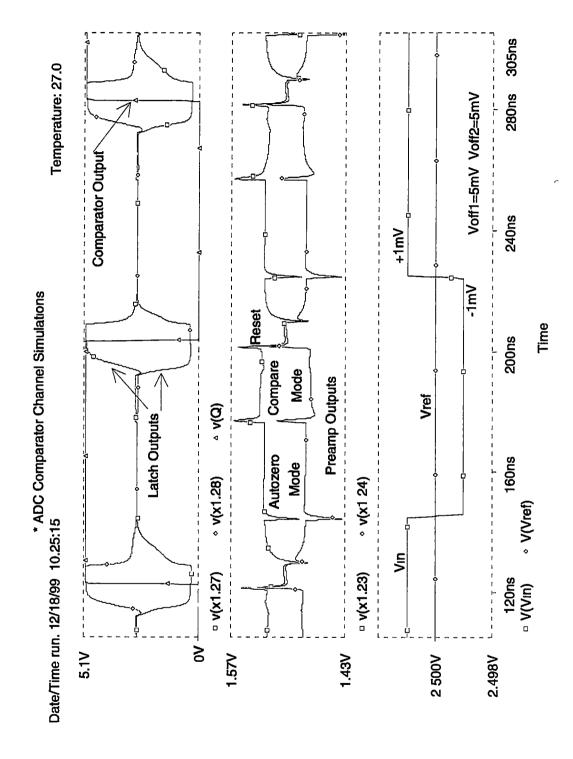

| Figure 4-16. Transient response of comparator channel showing comparator control waveforms                      |          |

| Figure 4-17. Transient response of comparator channel showing overdrive recovery performance                    | 0        |

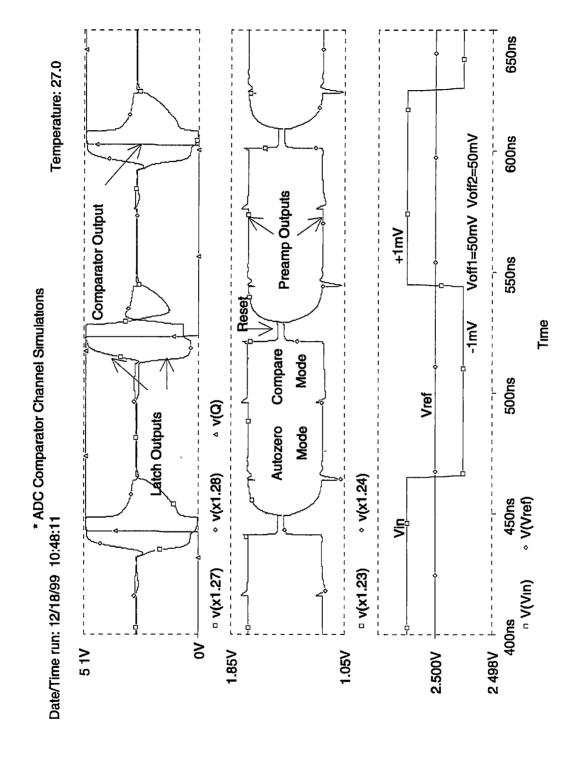

| Figure 4-18. Transient response of comparator channel with 1 mV input overdrive and 50 mV offsets               | 2        |

| Figure 4-19. Integrated circuit layout plot of MSB comparator channel                                           | 3        |

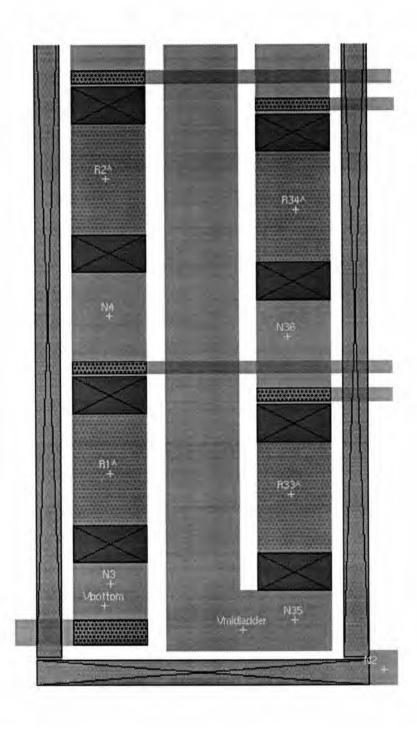

| Figure 4-20. Partial integrated circuit layout of the resistive divider network 135                  |

|------------------------------------------------------------------------------------------------------|

| Figure 4-21. Abbreviated listing of the ADC simulation output file                                   |

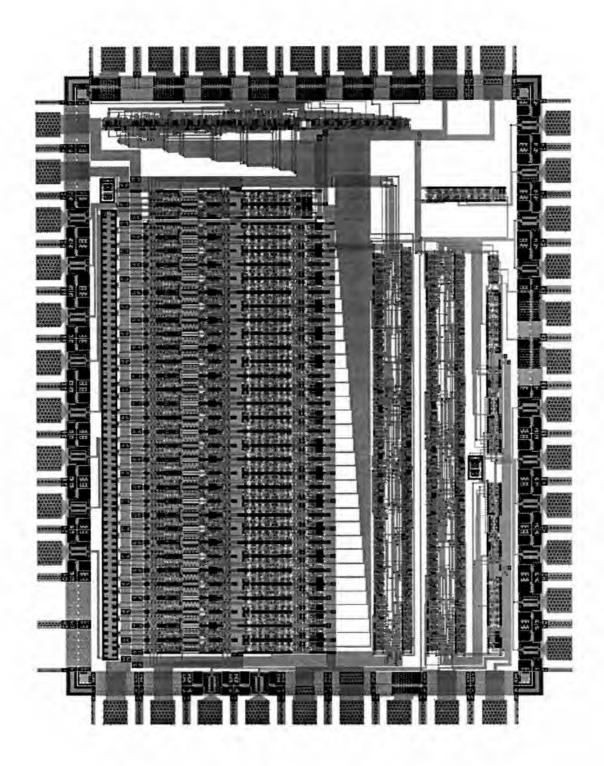

| Figure 4-22. Integrated circuit layout plot of the ADC prototype chip                                |

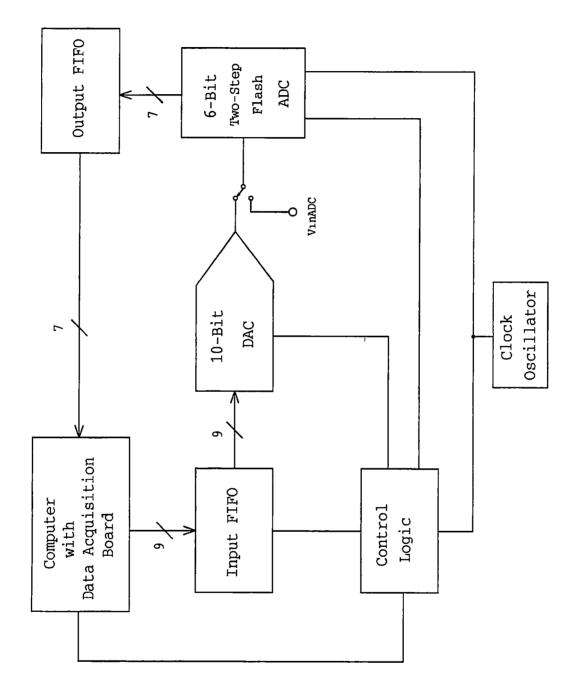

| Figure 5-1. Block diagram of experimental setup for testing the ADC 143                              |

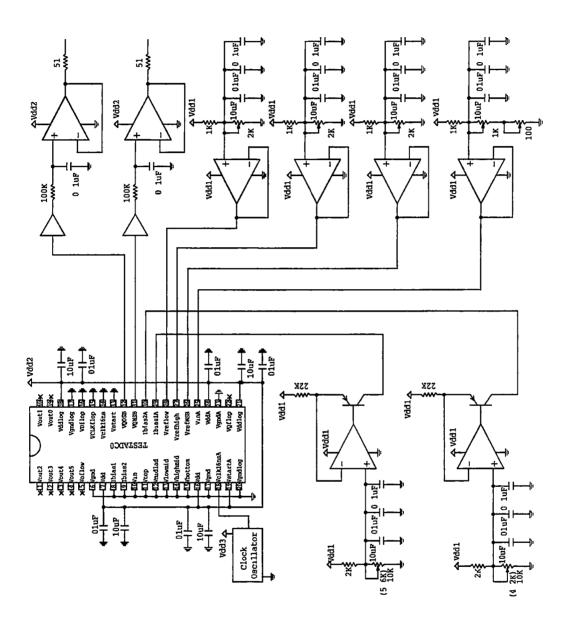

| Figure 5-2. Schematic diagram of test circuitry to fully characterize the ADC 145                    |

| Figure 5-3. Photograph of test board developed to evaluate the ADC 147                               |

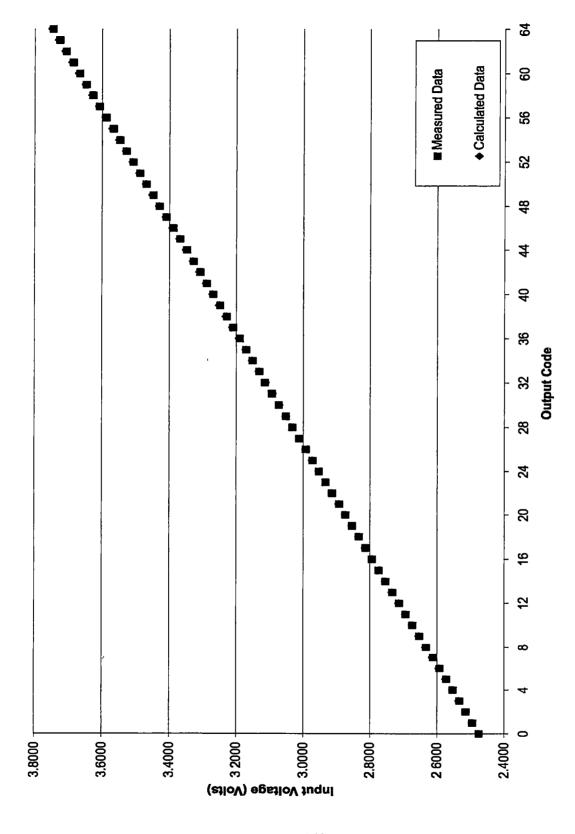

| Figure 5-4. Typical measured versus ideal transfer function characteristics of the ADC               |

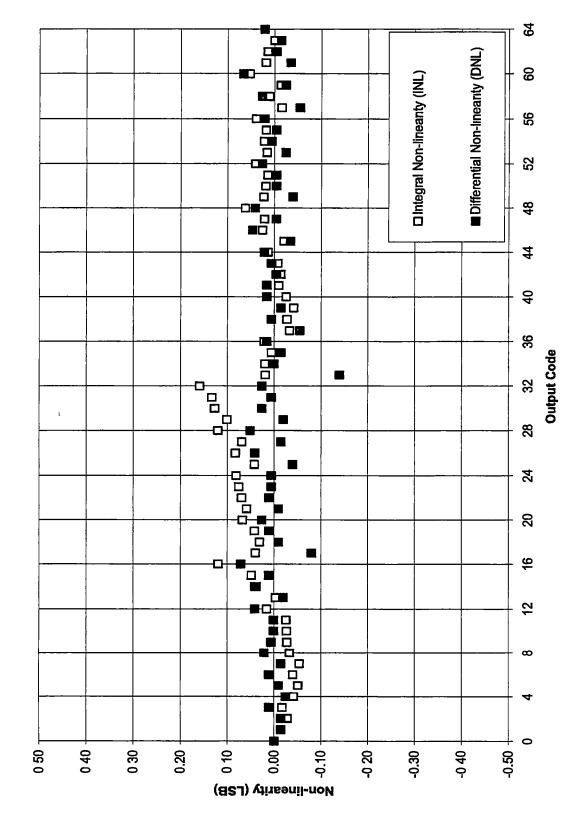

| Figure 5-5. Typical ADC non-linearity performance from DC sweep input measurements                   |

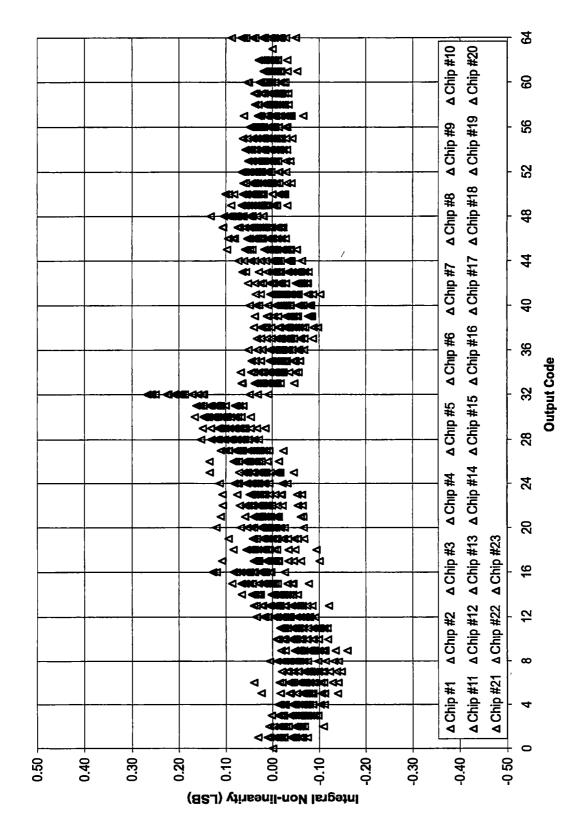

| Figure 5-6. Integral non-linearity performance of all ADC chips from DC sweep input measurements     |

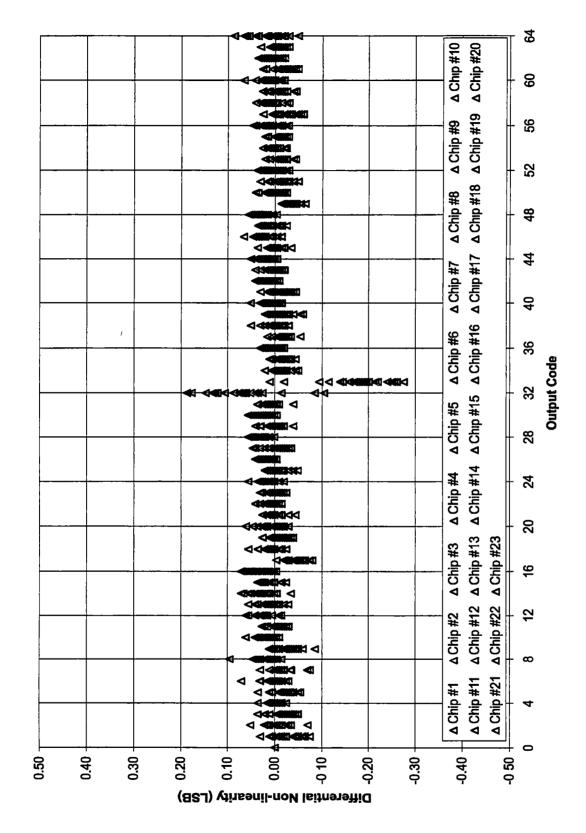

| Figure 5-7. Differential non-linearity performance of all ADC chips from DC sweep input measurements |

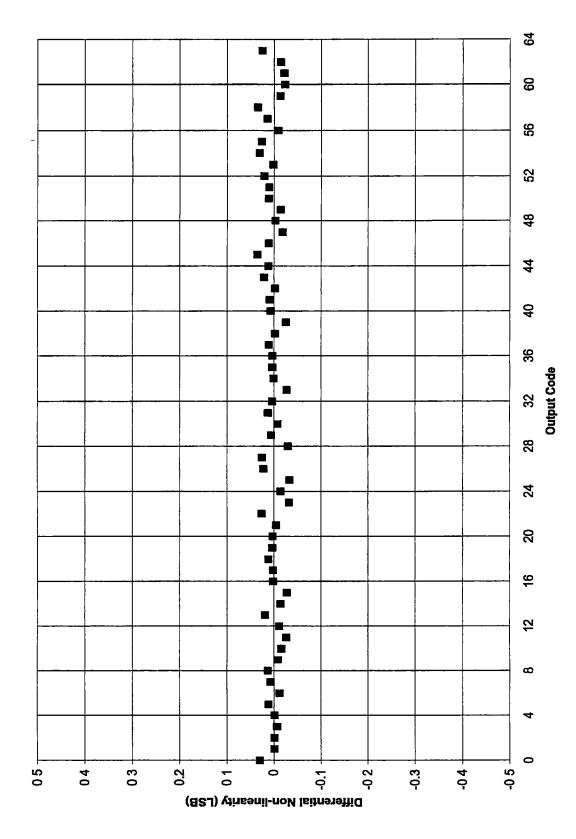

| Figure 5-8. Differential non-linearity of random data generated for code density test measurements   |

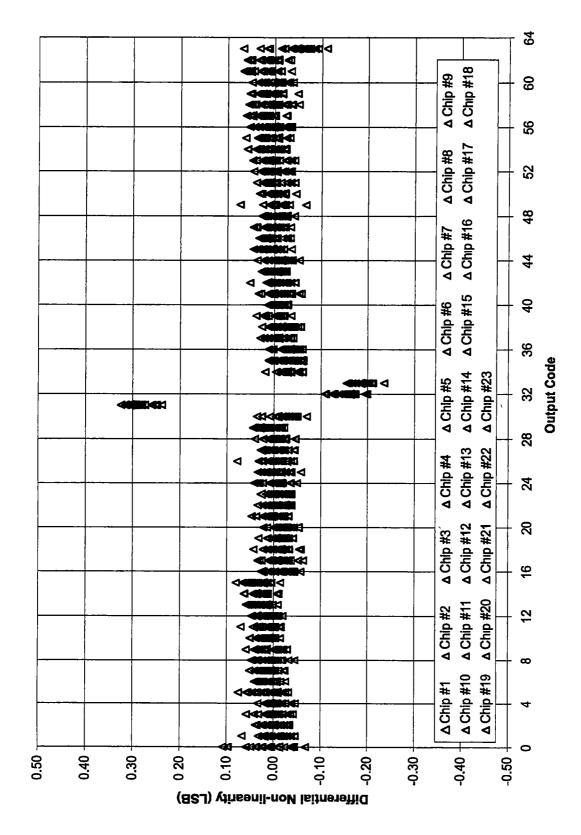

| Figure 5-9. Differential non-linearity performance of all ADC chips from code density measurements   |

| Figure 5-10. Schematic diagram of test circuitry designed to evaluate comparator offset performance  |

| Figure 5-11. Photograph of test board developed to perform comparator offset measurements            |

## Chapter 1

#### Introduction

#### 1.1 Time Measurement Application for Positron Emission Tomography

The precise electronic measurement of time between two physical events is very important and fundamental in many experimental and applied systems. A time-to-digital converter (TDC) is one type of an electronic instrumentation system that is capable of measuring the time difference between two random events. Time-to-digital converters have a variety of industrial and research applications. They are used in laser range finding where distance measurements are required, instrumentation and electronic test equipment such as digital storage oscilloscopes, positron emission tomographs and various high-energy physics experiments. The TDC described in this work is for use in commercial positron emission tomography (PET) medical imaging systems.

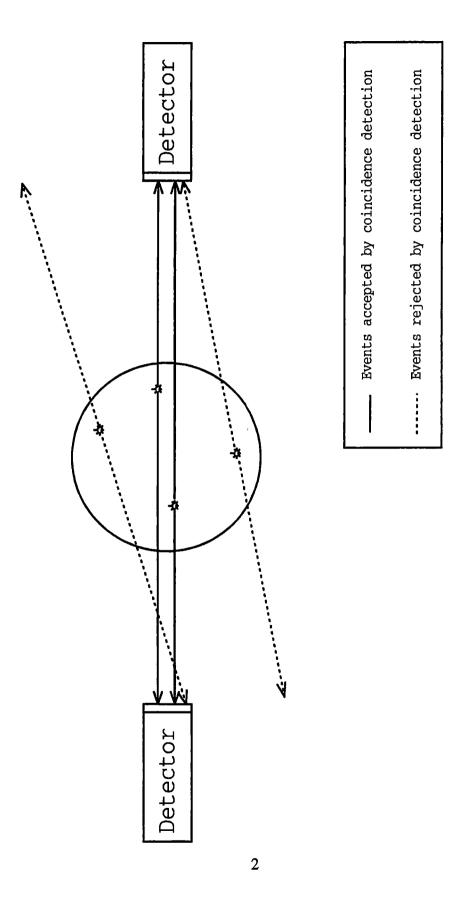

In a PET system, a positron emitting radionuclide is injected into the patient. When a positron comes into contact with an electron within the body, the two particles annihilate and produce two time coincident 511 keV gamma rays that are emitted 180 degrees apart. If two gamma ray detectors are placed on opposite sides of the body, the detection and coincidence measurement of two annihilation photons can be performed (Figure 1-1). Many gamma ray detectors are arranged in paralleled rings that encircle the patient to be imaged to generate a full tomographic data set [1]. A time measurement is required to detect the coincidence of two opposing gamma rays that hit two detector pairs. Coincidence refers to the arrival and detection of two events in a particular timing

Figure 1-1. Basic principles of PET event coincidence detection.

window. Only the events that are in coincidence are accepted and all others are rejected. The line between the two detector pairs is known as the line of response. From the timing measurements, a histogram array of coincident events is then generated that contains all possible lines of response. The histogram array of all possible lines of response is called a sinogram. This sinogram is converted into a medical image through various reconstruction techniques.

Since in a PET system a large number of measuring channels is required, a key goal is to realize the TDC in standard low cost technologies, such as CMOS, while meeting the design challenges of high-performance sub-nanosecond time resolution. The TDC discussed here will be part of a new custom, front-end CMOS integrated circuit for high-performance Lutetium Oxyorthosilicate (LSO) PET imaging applications. The motivation for the development of a custom, front-end CMOS integrated circuit is the reduction in cost, size, and power while simultaneously increasing performance, reliability, and testability of the system

#### 1.2 Time Measurement System Description and Requirements

#### 1.2.1 Time Measurement Overview

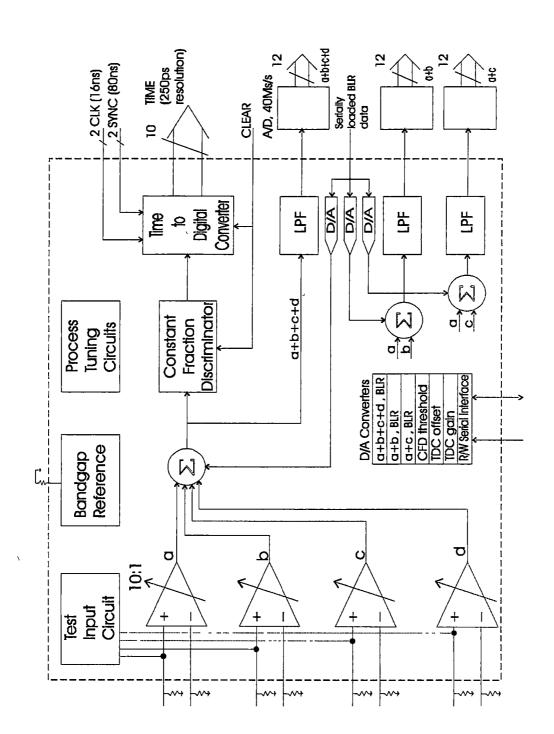

An architectural description of this proposed front-end CMOS application specific integrated circuit (ASIC) is shown in Figure 1-2. The timing output of the constant-fraction discriminator (CFD) is connected to the TDC where the event time is digitized with respect to the rising edge of the system clock. The CFD provides logic timing signal that is independent of the input signal amplitude. Figure 1-3 shows the system level

Figure 1-2. Block diagram of the high-performance LSO PET front-end ASIC.

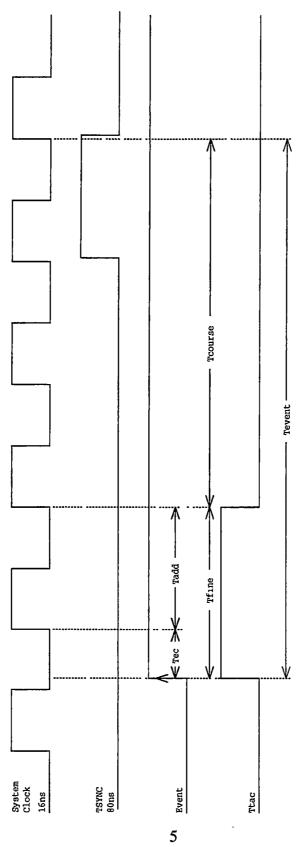

Figure 1-3. TDC system level timing signals.

timing waveforms that are relevant to the TDC. The event signal from the CFD is completely random with respect to the 16 ns system clock and serves as an asynchronous start command to the TDC. The 80 ns SYNC signal provides a synchronous stop command to the TDC. Thus, the objective is to digitize the time interval labeled  $T_{event}$  in Figure 1-3. This time period can be divided into two major parts: a  $T_{fine}$  time period and a  $T_{coarse}$  time period. The  $T_{coarse}$  time interval requires a coarse timing resolution of 16 ns and can be provided by just counting the system clock once the event signal has been detected. The duration of the  $T_{coarse}$  time interval can ideally vary from 0 ns to 80 ns depending upon the occurrence of the event signal relative to the rising edge of the system clock. A fine timing resolution system is needed to resolve and determine the time interval  $T_{fine}$ . The  $T_{fine}$  time interval is composed of the two time periods, which are  $T_{ec}$ and  $T_{add}$ . The interval  $T_{ec}$  is the total time from the event to the next rising edge of the clock.  $T_{add}$  is a fixed time period and is simply the duration of one clock cycle. The time period  $T_{add}$  is added to the interval  $T_{ec}$  to help improve the linearity of the time interval measurement and perhaps relax the propagation delay requirements of the signal processing circuits. Note that the duration of  $T_{fine}$  time interval can ideally vary from 16 ns to 32 ns depending upon the arrival of the event signal relative to the rising edge of the system clock.

#### 1.2.2 TDC Specifications and Design Requirements

For this sub-nanosecond time measurement application, the critical specifications and requirements of the TDC are:

- 250 ps time resolution

- Dead time < 80 ns

- Integral and Differential Non-linearity < ±½ LSB

- CFD circuitry will provide asynchronous START command

- 16 ns (62.5 MHz) system clock and 80 ns SYNC signal used for synchronous STOP command

- Multi-hit and multi-channel TDC implementations are not required for this application since there is only one timing channel per ASIC

- Single 5 V supply compatibility in CMOS technology

- Final design for either stand-alone or integrated function in larger chip

- Cost equal to or less than \$2.00 for discrete electronic circuit which has a 2 ns time resolution

The principle methods of time interval measurements were reviewed by Porat [2]. Many solutions to achieve nanosecond and sub-nanosecond TDCs in standard CMOS technologies have been recently reported [3-11]. So there are various TDC architectures one might consider using to satisfy these performance requirements. TDCs have traditionally been divided into two types: the current integration TDC being a high-resolution analog converter and the digital counter TDC being a low resolution converter.

Recently, other alternative TDC architectures have emerged mainly of the delay-locked loop (DLL) approach or some variation which have achieved resolutions somewhere in between these two extremes.

The digital counter based TDC is relatively easy to design, but only very limited resolution can be obtained with reasonable clock frequencies. For the counter based approach, sub-nanosecond timing requires a clock frequency of over 1 GHz which would consume a great deal of power and be very difficult to implement in standard CMOS processes. With a fundamental system clock frequency of 62.5 MHz, the digital counter based architecture gives a resolution of 16 ns with a  $\pm 16$  ns uncertainty and is therefore clearly unacceptable for this application. However, this counter based method can be used to determine the  $T_{coarse}$  timing information labeled in Figure 1-3.

DLL architectures rely on tuned delay elements to determine the resolution of the TDC. Basic CMOS gates are inverting and therefore two gates (inverters) are normally used as the fundamental delay element. As a result, most straight forward DLL architectures are limited to a time resolution that is basically the combined delay of two inverters in a given CMOS process. For our application, the delay of two inverters must be tuned to an overall delay of 250 ps. There is substantial technical risk and uncertainty whether tuned digital delays of 250 ps can be controlled over extreme process and temperature variations in 0.8 µm CMOS technology. Another major concern is the total number of tuned delay elements required for sub-nanosecond timing resolution. For our reference clock frequency of 62.5 MHz, 64 delay elements are required to achieve the desired 250 ps resolution. The 64 element delay line can be relatively long and therefore

these elements have a non-negligible amount of non-linearity due to process gradients. The linearity of the delay lines is limited by the matching of minimum sized logic delay elements. Therefore, to achieve good linearity performance, good matching between relatively small unit delay elements must be achieved and also systematic layout errors must be minimized. For these reasons, the fundamental DLL based TDC architecture was not selected for this application

Many variations of the DLL based TDC architecture have been developed to improve the time resolution beyond the basic delay of two inverters in a given CMOS technology [4, 5, 8]. These architectures contain some form of a timing generator that achieves sub-gate delays and can be implemented in standard digital CMOS processes. However, these architectures become more complex to design and are still susceptible to the fundamental non-linearity problems associated with the delay lines.

Because of the issues associated with the digital counter based and the DLL based TDC architectures, the analog current integration approach was chosen to achieve a high-performance sub-nanosecond TDC. There are many ways to implement an analog current integration based TDC. The classical analog current integration TDC that utilizes a time-to-amplitude converter (TAC) followed by an analog-to-digital converter (ADC) was selected for this application. This architecture is appropriate for this application since high-resolution, good linearity, and fast conversion times are preferred while multi-hit capability and multi-channel integration is not necessary. In fact, a discrete TDC design that was based upon this approach, but with different specifications, was previously developed and successfully incorporated in an earlier time-of-flight PET tomograph over

ten years ago [12].

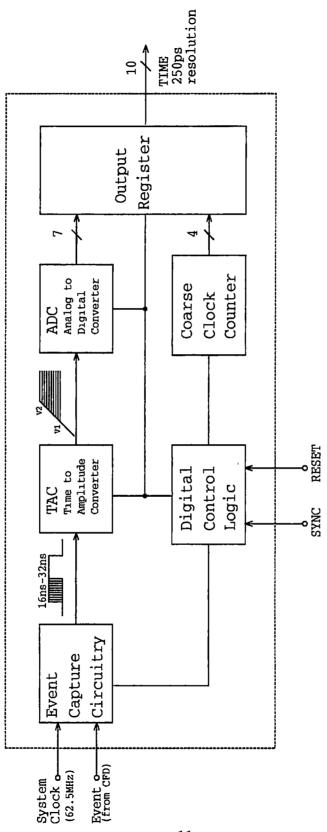

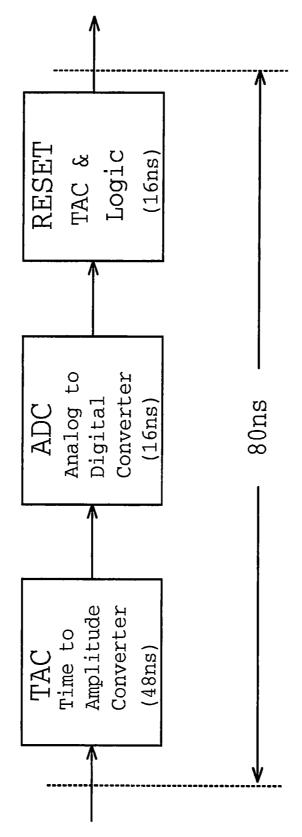

A block diagram of the chosen TDC architecture is shown in Figure 1-4. The major components of this TDC architecture consist of event capture circuitry, a TAC, an ADC, a coarse clock counter, digital control logic, and output register. The event capture circuitry generates a pulse whose width is proportional to the time difference between the event and the rising edge of the 16 ns system clock. This pulse width is labeled  $T_{\it fine}$  in Figure 1-3 and will ideally vary in duration from 16 ns to 32 ns, depending upon the arrival of the event signal relative to the system clock. The TAC receives this pulse as its input signal and generates a corresponding output voltage that is directly proportional to the pulse width. The TAC output voltage ideally varies from 2.475 V to 3.75 V, depending upon the input pulse width. The ADC then digitizes this voltage. Meanwhile, the coarse clock counter starts counting the number of clock cycles that occurs before the rising edge of clock and the 80 ns SYNC signal. The ADC output code is then combined with the output of the coarse clock counter to generate a final timing code for that particular event. This timing information is then stored in the digital output register that can be accessed by the system at a later time. The control logic generates all the necessary timing information and signals required to operate and interface to the TDC.

#### 1.2.3 ADC Specifications and Design Requirements

A key component in the TDC architecture described above is the ADC. To achieve the desired 250 ps time resolution, the system clock period of 16 ns needs to be resolved into 64 intervals or time bins. Therefore, a 6-bit ADC with 64 channels is

Figure 1-4. Block diagram of TDC architecture.

required to achieve the desired time resolution. Also, to satisfy the TDC's integral and differential non-linearity specification of ±½ LSB, the ADC will need equal or better performance. The TDC dead time specification of 80 ns will determine the required conversion speed of the ADC. The dead time specification for a TDC is typically defined as the time from when an event is detected until the TDC is ready to accept another event. This time period must include the conversion times of the TAC and ADC plus any additional time allocation for reset or re-initialization of circuitry. A timing diagram with time allocation on each functional block to achieve the 80 ns dead time requirement is shown in Figure 1-5. This particular timing configuration places very stringent demands on the speed performance of the ADC. The ADC will need to run at a 62.5 MHz conversion rate to satisfy the dead time specification. In general, ADCs in this speed category can be very complex and demanding to implement in CMOS technologies and also consume a good amount of power. Therefore, a sample-and-hold circuit was implemented at the system level to relax the performance requirements of the ADC.

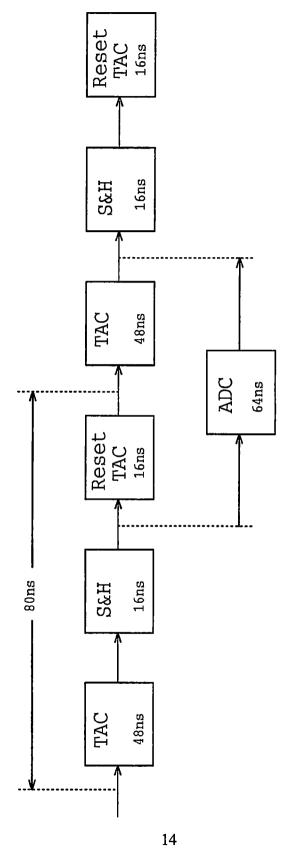

The new proposed TDC timing diagram that includes the use of sample-and-hold circuit is shown in Figure 1-6. Through the utilization of a sample-and-hold circuit, a paralleled architecture is achieved which reduces the speed requirements of the ADC by a factor-of-five. The ADC must now digitize an input voltage within the allotted time of 80 ns instead of 16 ns. One subtle issue is that the input voltage presented by the sample-and-hold circuitry to the ADC is only available for 64 ns. However, an extra 16 ns is available to the ADC before the next conversion is required. Therefore, an ADC with a conversion speed of 15.625 MHz with a one clock cycle latency of 16 ns is acceptable.

Figure 1-5. TDC conversion timing diagram.

Figure 1-6. TDC conversion timing diagram with sample-and-hold implementation.

The focus of this work is the development of an ADC for use in a low dead time high-performance sub-nanosecond time-to-digital converter. The performance of the ADC should meet the following specifications:

- 6-bits of resolution

- Differential non-linearity < ±½ LSB

- Integral non-linearity < ±½ LSB

- Conversion rate of 15.625 MHz (64 ns) with a latency of one clock cycle (16 ns)

- 62.5 MHz (16 ns) system clock used for timing and control logic

- Typical reference voltage of 1.275 V resulting in a 20 mV/LSB resolution

- Accommodation of a 2 V input range to the ADC with a typical input range from the TAC of 2.475 V to 3.75 V

- Significant offset error is tolerable since variations in the TAC output voltage will be corrected by system calibration of the ADC reference voltage

- Low metastability error rate performance is not required since the total error rate of the time measurement system will be dominated by system level issues

- Single 5 V supply compatibility in 0.8 μm CMOS technology

#### 1.3 Thesis Organization

The selection of an appropriate ADC architecture for the time measurement system application is found in Chapter 2. Also, a detailed description of the proposed two step flash ADC architecture is presented.

The design and analysis of the major functional blocks of the ADC are given in Chapter 3 with special emphasis placed on the development of an auto-zeroed CMOS comparator. After a brief introduction to comparators, the motivation and requirement for an offset corrected comparator is presented. The concept of charge injection is presented and the fundamental limitations of offset correction techniques due to charge injection is discussed. Next, the most common comparator offset cancellation techniques are explained. Extensive analysis of the selected comparator architecture is then presented. A complete non-linearity analysis of the ADC is presented which relates reference generation errors and comparator offsets to integral and differential linearity performance of the converter. Digital error correction and encoder design requirements are then shown. Finally, a brief description of the ADC control logic design is given.

Chapter 4 contains all key simulations and critical layout issues of the ADC design. Preamplifier and regenerative latch simulations are shown. Also, simulated performance of an ADC comparator channel is presented. Next, the simulation technique used to evaluate the complete ADC design is discussed. Integrated circuit layout plots of critical sections of the ADC are illustrated throughout Chapter 4.

Experimental results achieved by two different ADC test methodologies are presented in Chapter 5. The complex test circuitry required to fully characterize the ADC

is discussed. A summary of the experimental measurements obtained on the ADC is given. Also, corrected CMOS comparator offset measurements are reported.

Chapter 6 contains a summary of the work and potential design improvements are suggested.

## Chapter 2

## **ADC Architecture Selection and Description**

#### 2.1 ADC Overview and Architecture Requirements

An ADC is a device that takes an analog input signal and generates a digital output code. Most ADCs are required to interface analog signals to digital signal processing systems. A wide variety of ADC architectures and applications have been reported [13-23]. A literature review of current ADCs reveals that most recent research and implementations can be classified into four types of architecture: pipeline, flash or flash-type, successive approximation, and oversampled ADCs [24]. All of these ADC architectures have been customized and optimized for their particular application and span the spectrum of speed and resolution.

For mixed-signal system applications, the latency and speed of the ADC are important design parameters. The latency of an ADC is defined as the delay between the sampling of the analog signal and the moment that the corresponding digital output code is available. However, the latency specification of an ADC is generally referenced to the end of a conversion and usually specified in an integer multiple of clock cycles. It is important to differentiate this specification from the conversion speed of the ADC. The time required for the analog signal to be presented to the ADC for a successful conversion is typically defined as the conversion speed or throughput of the converter. For our application, an ADC conversion speed of 15.625 MHz is required. Therefore, the analog input signal is only available to the converter for a total time period of 64 ns

However, from the start of the conversion process, a total time period of 80 ns is available until the digital output code is required. Therefore, the ADC requirements are a conversion speed of 15.625 MHz with one 16 ns clock cycle latency while achieving 6-bits of resolution.

Architectural choices directly influence the speed and latency of a converter. For the ADC application described in Chapter 1, there is a requirement for a high-speed (15.625 MHz) and low latency (16 ns) converter architecture because the 6-bit ADC output code must be combined with output of the course clock counter at the end of the 80 ns SYNC period (Figures 1-3 and 1-4). There are a number of ADC architectures suitable for sampling rates of 15.625 MHz. However, the system requirement for a low latency converter eliminates most of the possible architectures from consideration. The ever popular pipeline ADC and other architectures have an inherently larger latency than a flash ADC architecture. Therefore, for high-speed and low latency ADC applications, the implementation of a flash or flash-type ADC architecture is almost mandatory. As a result, the investigation and implementation of an appropriate flash or flash-type ADC architecture for this application was performed.

#### 2.2 Traditional Flash ADC Architecture

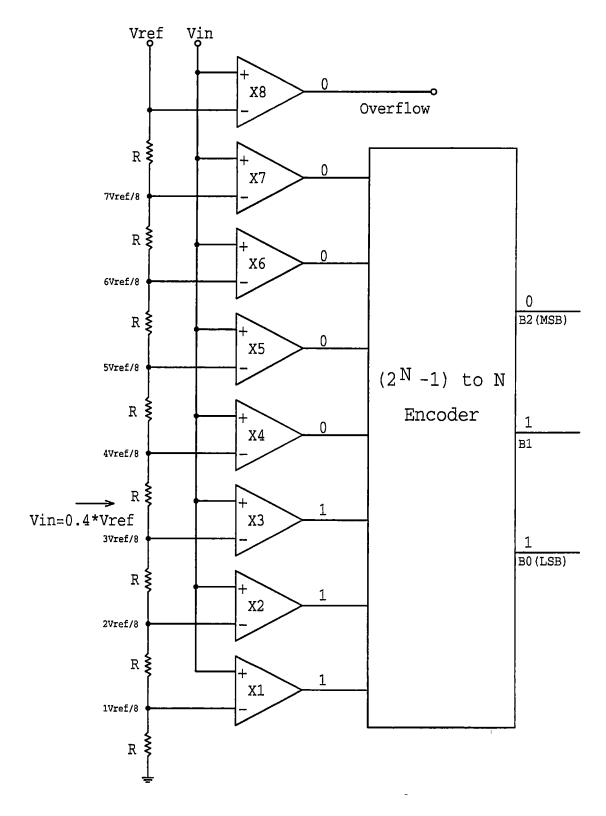

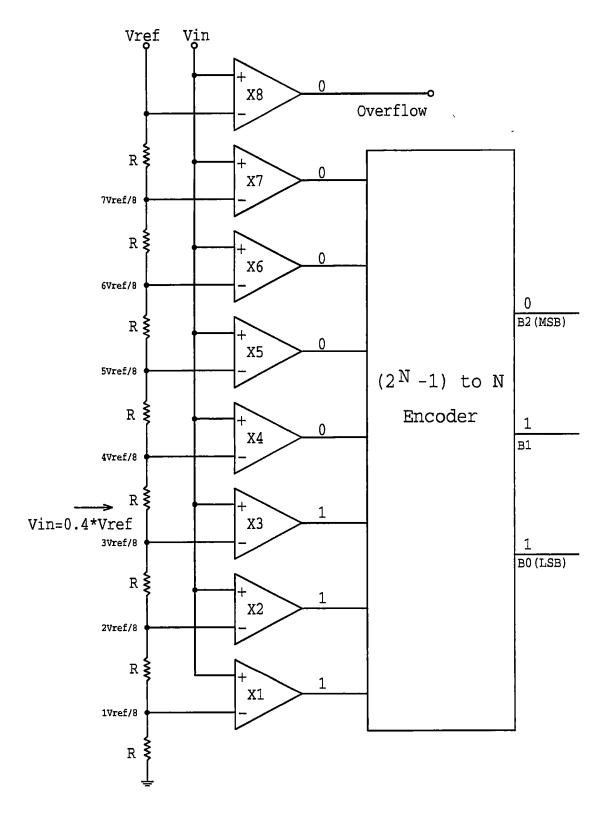

The fastest ADC architecture reported to date is the flash ADC [20]. Therefore, it has become one of the standard approaches for realizing high-speed converters. Figure 2-1 shows a block diagram of a classical three-bit flash ADC. This architecture utilizes (2<sup>N</sup>-1) comparators to achieve one comparator per quantization level and requires 2<sup>N</sup> resistors,

Figure 2-1. Block diagram of a classical 3-bit flash ADC architecture.

where N is the number of desired bits. The input signal,  $V_{in}$ , is connected to the positive input of all the comparators that are in parallel. The reference voltage,  $V_{ref}$ , is divided into  $2^{N}$ , or eight, reference values as indicated in the figure. Each of these references is applied to the negative input of a comparator. The input voltage is compared with each individual reference value or quantization level. The outputs of the comparators are passed into a digital encoder which generates a digital output code based upon the comparator outputs.

As an example, if  $V_{in}$  is equal to  $0.4*V_{ref}$ , then the outputs of the comparators, X4-X7, are a logical 0, and the bottom comparators outputs, X1-X3, are all a logical 1. The digital encoder logic would calculate 011 as the binary output code. Thus, any comparator connected to a resistor string node whose voltage is larger than  $V_{in}$  will have a logical 0 output while those who have voltages smaller than  $V_{in}$  will have a logical 1 output. This output code arrangement is typically called a thermometer code since it looks similar to the mercury bar in a thermometer. Table 2-1 shows the entire range of analog input voltages with the corresponding comparator outputs and the correct digitally encoded output code.

Although the classical flash converters are the fastest, they require (2<sup>N</sup>-1) comparators, where N is the number of desired bits. Therefore, the layout area, power dissipation, and input capacitance of the ADC are all directly proportional to the number of comparators (2<sup>N</sup>-1) for a given resolution. The required silicon area of an ADC is very important since it directly affects the cost and yield of the design. Also, power efficient CMOS integrated circuit design is always a goal and the power dissipation of ADCs is

Table 2-1. Truth table for classical 3-bit flash ADC.

| Analog Input Voltage    | Comparator Outputs |    |            |    |    |    |            | Digital Code |    |    |

|-------------------------|--------------------|----|------------|----|----|----|------------|--------------|----|----|

| Vin                     | Х7                 | Х6 | <b>X</b> 5 | X4 | Х3 | Х2 | <b>X</b> 1 | B2           | B1 | В0 |

| Vın < Vref/8            | 0                  | 0  | 0          | 0  | 0  | 0  | 0          | 0            | 0  | 0  |

| Vref/8 < Vin < 2Vref/8  | 0                  | 0  | 0          | 0  | 0  | 0  | 1          | 0            | 0  | 1  |

| 2Vref/8 < Vın < 3Vref/8 | 0                  | 0  | 0          | 0  | 0  | 1  | 1          | o            | 1  | 0  |

| 3Vref/8 < Vin < 4Vref/8 | 0                  | 0  | 0          | 0  | 1  | 1  | 1          | 0            | 1  | 1  |

| 4Vref/8 < Vin < 5Vref/8 | 0                  | 0  | 0          | 1  | 1  | 1  | 1          | 1            | 0  | 0  |

| 5Vref/8 < Vin < 6Vref/8 | 0                  | 0  | 1          | 1  | 1  | 1  | 1          | 1,           | 0  | 1  |

| 6Vref/8 < Vın < 7Vref/8 | 0                  | 1  | 1          | 1  | 1  | 1  | 1          | 1            | 1  | 0  |

| 7Vref/8 < Vın < Vref    | 1                  | 1  | 1          | 1  | 1  | 1  | 1          | 1            | 1  | 1  |

consistently a key specification. In some applications, the input capacitance of the ADC can ultimately limit the speed of the converter and may require an input buffer to drive the capacitive load presented by the ADC. Therefore, the main disadvantages of this architecture are that the layout area, power dissipation, and input capacitance nearly double for each additional bit of resolution needed. Consequently, most traditional flash converters implemented in CMOS technologies are typically limited to 6 to 8 bits of resolution [17-19, 25].

## 2.3 Two-Step Flash ADC Architecture

The traditional flash ADC architecture can be modified, at the expense of increased latency, to reduce the comparator count, and thus require less silicon area, dissipate less power, and achieve a smaller input capacitance. These groups of converters are commonly called a two-step flash ADC and are currently the most popular for achieving high-speed and medium resolution conversion. These converter architectures use a two-step conversion process and trade a factor-of-two in speed reduction for a large area and power savings.

There have been many types of two-step flash ADC architectures reported in the literature. Most two-step flash architectures require a DAC, amplifier, subtractor, digital error correction, and other additional circuitry [24, 26]. As a result, the design complexity of these converters drastically increases when compared to the traditional flash ADC implementation. The main drawbacks of most two-step ADC converters have been the requirement for a high-speed, high-gain operational amplifier and a digital-to-analog

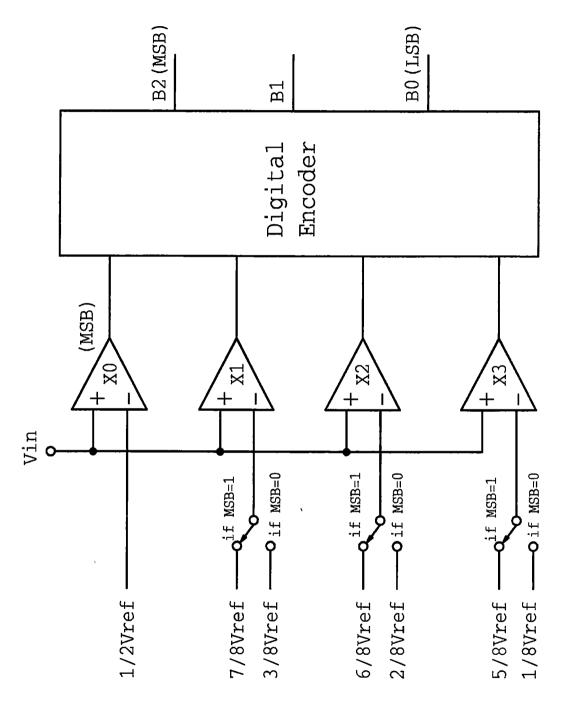

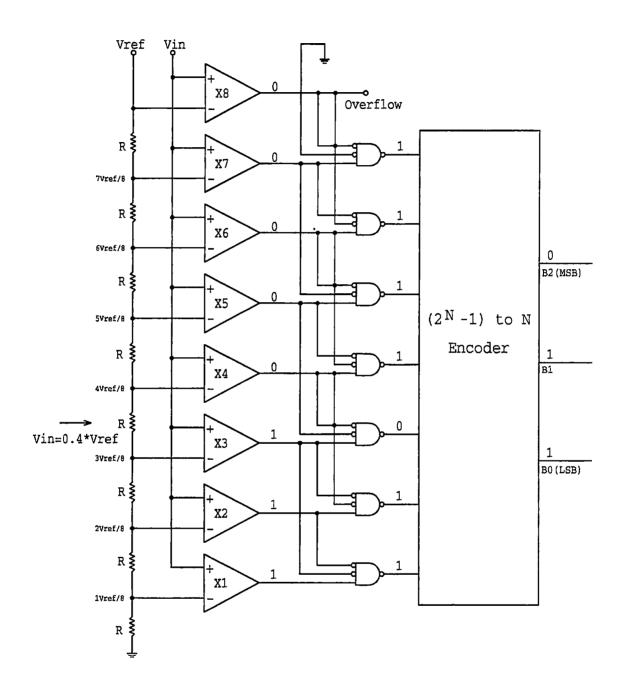

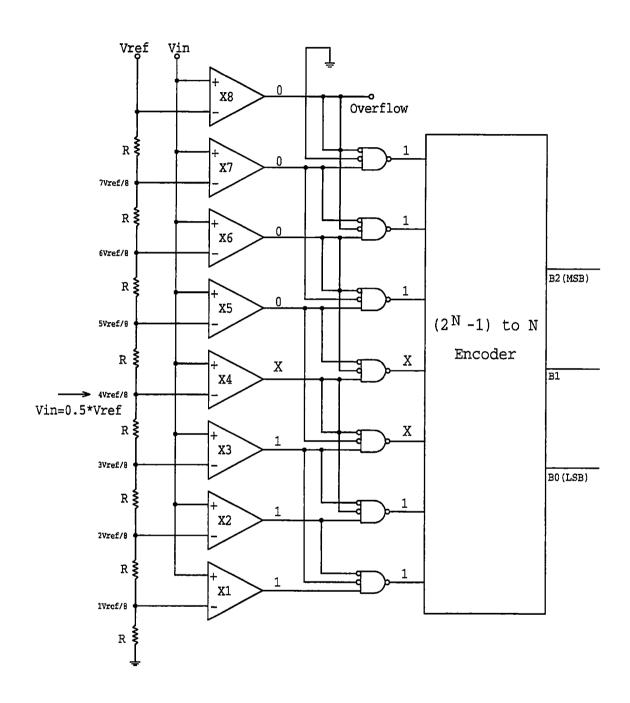

converter (DAC). However, one particular two-step flash ADC architecture reported by Ahmed [27] does not require any of these additional complex circuits. The design methodology of this two-step architecture can be explained by careful examination of the traditional flash ADC operation (Figure 2-1 and Table 2-1). In the classical flash ADC, the comparator, which compares the analog input voltage with  $\frac{1}{2}V_{ref}$ , generates the most significant bit (MSB) of the final output code. This aforementioned comparator is labeled X4 in Figure 2-1. Throughout this work, this comparator is referred to as the MSB comparator since it is the comparator that generates the MSB decision of the ADC output code. After analyzing Figure 2-1 and Table 2-1, it can be concluded that it is only necessary to observe either the comparator outputs of X1, X2, and X3, or X5, X6, and X7depending upon the decision of the MSB comparator. If the output of the MSB comparator is a logical 0, then it is only necessary to look at the outputs of X1, X2, and X3 to determine the final output code. Similarly, if the output of the MSB comparator is a logical 1, then only the outputs of X5, X6, and X7 are required to calculate the output code. Therefore, after the output of the MSB comparator is known, it is only necessary to look at the results of half the comparators in a traditional flash architecture to determine the output code. This information can be used to simplify the ADC design because the output of the MSB comparator can be used as a control signal to reduce the required number of comparators

A simplified block diagram of the proposed two-step flash ADC architecture for a 3-bit converter is shown in Figure 2-2 Just as in the traditional flash ADC, a resistive ladder can be used to generate all the necessary reference voltages, but this ladder

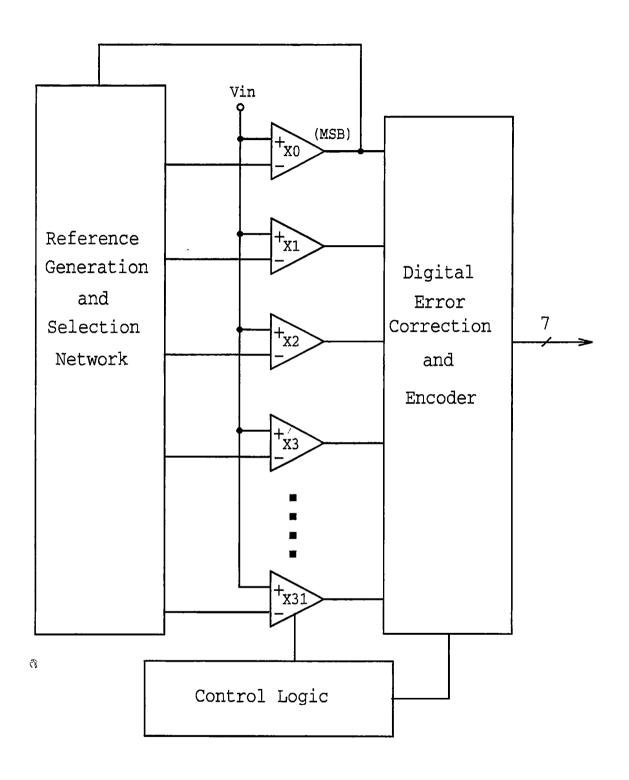

Figure 2-2. Block diagram of a 3-bit two-step flash ADC architecture.

network is omitted from the figure for clarity. The operation of this proposed converter architecture can be described as a two-phase conversion process. The output of the MSB comparator is generated in the first step of the conversion. Next, the MSB decision is used to select the appropriate references for the rest of the comparators (X1, X2, and X3) and the second conversion is made. The comparators X1, X2, and X3 will be referred to as other significant bits (OSB) comparators throughout the rest of this work. To encode the outputs of the comparators into a final binary output code, the basic truth table of Table 2-2 can be used. Note from the figure that the encoder design is also simplified because of the reduced number of inputs.

This simple two-step flash ADC architecture only requires 2<sup>(N-1)</sup> comparators for an N bit conversion. Therefore, the comparator count is reduced by factor-of-two when compared to the traditional flash ADC architecture. Another advantage of this architecture is that it does not require additional complex circuitry like most other two-step flash ADC architectures. For example, this architecture eliminates the need for a DAC and high-speed amplifier which are typically required in other two-step ADC architectures. Also, the required silicon area for the encoder design is reduced because of the lower number of inputs to the encoder relaxes the design requirements. The main disadvantage of this and all two-step flash ADC architectures is that the latency of the converter is now increased since two sequential conversions are required.

In this work, the two-step flash ADC architecture presented was chosen and customized to meet the requirements of the ADC for the high-performance subnanosecond TDC application. This topology can be expanded to 6-bits to meet the

Table 2-2. Truth table for 3-bit two-step flash ADC.

| Analog Input Voltage    | Comparator Outputs |            |     |    | Digital Code |    |    |  |

|-------------------------|--------------------|------------|-----|----|--------------|----|----|--|

| Vin                     | хо                 | <b>X</b> 1 | X2  | Х3 | B2           | B1 | В0 |  |

| Vin < Vref/8            | 0                  | 0          | · 0 | 0  | 0            | 0  | 0  |  |

| Vref/8 < Vin < 2Vref/8  | 0                  | 0          | 0   | 1  | 0            | 0  | 1  |  |

| 2Vref/8 < Vin < 3Vref/8 | 0                  | 0          | 1   | 1  | 0            | 1  | 0  |  |

| 3Vref/8 < Vin < 4Vref/8 | 0                  | 1          | 1   | 1  | 0            | 1  | 1  |  |

| 4Vref/8 < Vin < 5Vref/8 | 1                  | 0          | 0   | 0  | 1            | 0  | 0  |  |

| 5Vref/8 < Vin < 6Vref/8 | 1                  | 0          | 0   | 1  | 1            | 0  | 1  |  |

| 6Vref/8 < Vin < 7Vref/8 | 1                  | 0          | 1   | 1  | 1            | 1  | 0  |  |

| 7Vref/8 < Vin < Vref    | 1                  | 1          | 1   | 1  | 1            | 1  | 1  |  |

required resolution of the ADC. Since this two-step flash ADC architecture requires  $2^{(N-1)}$  comparators, a 6-bit converter implementation will require thirty-two comparators which will consist of one MSB comparator and thirty-one OSB comparators. Figure 2-3 shows a preliminary timing diagram to meet the 15.625 MHz conversion rate with a latency of one 16 ns clock cycle. The MSB comparator has 24 ns to compare the analog input voltage with  $\frac{1}{2}V_{ref}$ . A total time period of 16 ns is allowed for the interpretation of the MSB output and the selection of reference voltages for the OSB comparators. The OSB comparators are allowed 24 ns of conversion time. These time periods consume the entire allotted time of 64 ns that the analog input voltage will be available to the ADC. As a result, the encoding of the comparator outputs is performed during the allowed latency period of one clock cycle.

A block diagram of the 6-bit 15.625 MHz CMOS two-step flash ADC architecture is shown in Figure 2-4. The architectural requirements of the ADC can be divided into four major sections of development: MSB and OSB comparator design, reference generation and selection network, encoder design with digital error correction, and control logic. The development and performance requirements of these sections will be presented with special emphasis placed on the design and analysis of an auto-zeroed CMOS comparator.

Figure 2-3. Preliminary timing diagram of proposed 6-bit two-step flash ADC.

Figure 2-4. Block diagram of the 6-bit two-step flash ADC architecture.

# Chapter 3

## **ADC Design and Analysis**

## 3.1 Comparator Design and Analysis

#### 3.1.1 Comparator Overview and Fundamentals

A comparator is a circuit that compares two analog signals and outputs a binary signal based upon the comparison. Thus, a comparator can be thought of as a decision making circuit. Most comparators are considered nonlinear circuits since the inputs are not linearly related to the outputs. A comparator is not purely analog or digital and is considered a mixed-signal circuit since it interfaces analog signals to digital circuitry.

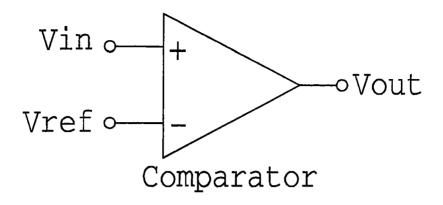

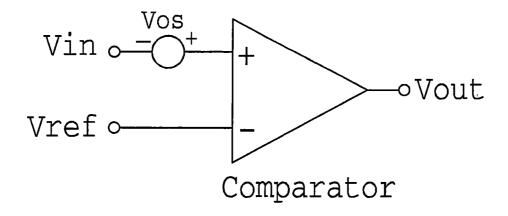

The schematic symbol and basic operation of a voltage comparator is shown in Figure 3-1. If the positive input signal,  $V_{in}$ , of the comparator is at a greater potential than the negative input,  $V_{ref}$ , then the output of the comparator is a logical 1 Conversely, if the positive input of the comparator is at a potential less than the negative input, then the output of the comparator is a logical 0 Thus, a comparator is used to determine whether a given signal is larger or smaller than another signal. Fundamentally, a comparator can be thought of as a one bit ADC since it takes an analog signal and generates a digital output.

The basic function of the comparator is that of providing sufficient amplification to generate digital output levels in response to small analog input differences. Depending upon the application, the amplification process of the comparator does not need to be linear and not necessarily continuous in time. Also, in applications where latency can be tolerated, the amplification process can be achieved by several cascaded amplifier stages.

If Vin>Vref then Vout=Vdd

If Vin<Vref then Vout=Vgnd</pre>

Figure 3-1. Circuit symbol and transfer function of an ideal voltage comparator.

In most data conversion systems, the comparator decision time is not arbitrary and must be made within a specified time interval. Therefore, most data converter comparators employ regeneration through positive feedback to make a decision in a timely manner. In fact, Lim and Wooley have reported that in order to achieve a minimum power-delay product, the amplification process in a comparator is best obtained by means of regeneration [28]. The comparator development presented here will focus on the application in a high-performance parallel ADC architecture and realizations that can be readily implemented in CMOS technology.

The performance of ADCs is generally limited by the speed and precision with which the function of comparison can be made. Therefore, the design and performance of a comparator is a critical and often limiting component in the design of high-speed data conversion systems. Converter architectures that incorporate a large number of comparators in parallel, such as a flash ADC architecture, to obtain high throughput impose very stringent conditions and constraints on the comparator performance. Key specifications and design parameters of a comparator commonly include: propagation delay, resolution, input offset voltage, power dissipation, area, input common-mode range, and input impedance. As typical in the design process, several tradeoffs between these parameters must be made when designing a comparator for a particular application.

#### 3.1.2 Motivation for an Auto-zeroed Comparator

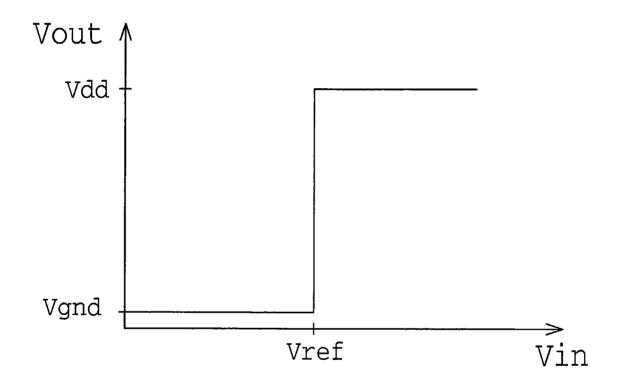

A particular difficulty encountered in the design and performance of a CMOS comparator is that of the input offset voltage. The comparator transfer function including

the input offset voltage effects is shown in Figure 3-2. The output does not change until the input difference of the comparator has reached a value of  $V_{OS}$ . The input offset voltage of a comparator is caused by two components: random offset and systematic offset effects. Random offsets are caused by device mismatch, such as transistor threshold voltage mismatch due to process gradients. Systematic offsets are present even when all devices are assumed ideal and no process variations exist. These offsets can be a result of charge injection, clock coupling, substrate noise, or could be inherent in the design of the comparator. Both of these offset effects can be minimized through careful circuit design, but typically can not be completely eliminated. For precision applications, such as a high-resolution ADCs, the comparator's offset voltage can severely limit the performance and operation of the converter. If the input offset voltage of a comparator could be predicted and well controlled, it could be managed much more easily through simple calibration techniques. However, most of the time the offset of the comparator varies randomly from circuit to circuit for a given design. Due to the fact that the chosen ADC architecture requires many comparators in parallel, the random distribution of the comparators offset voltages can completely distort the linearity of the output data.

One of the most fundamental issues in the selection of a CMOS comparator topology is the decision whether to employ offset cancellation techniques to the comparator. This decision should be based upon the desired resolution of the converter relative to the anticipated offset voltage of the comparator and the required linearity performance of the converter. A well-informed, intelligent decision cannot be made based solely upon the number of bits of a given converter. For example, due to the

If Vin>(Vref+Vos) then Vout=Vdd

If Vin<(Vref+Vos) then Vout=Vgnd</pre>

Figure 3-2. Ideal comparator transfer function including offset voltage effects.

difference in required resolution, an 8-bit converter may not require offset corrected comparators in one particular application, while a 4-bit converter may require offset correction techniques in another application.

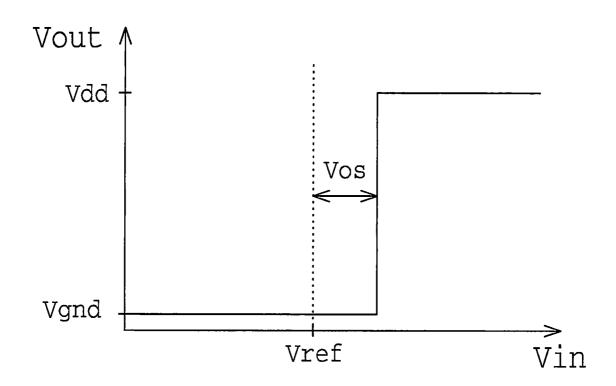

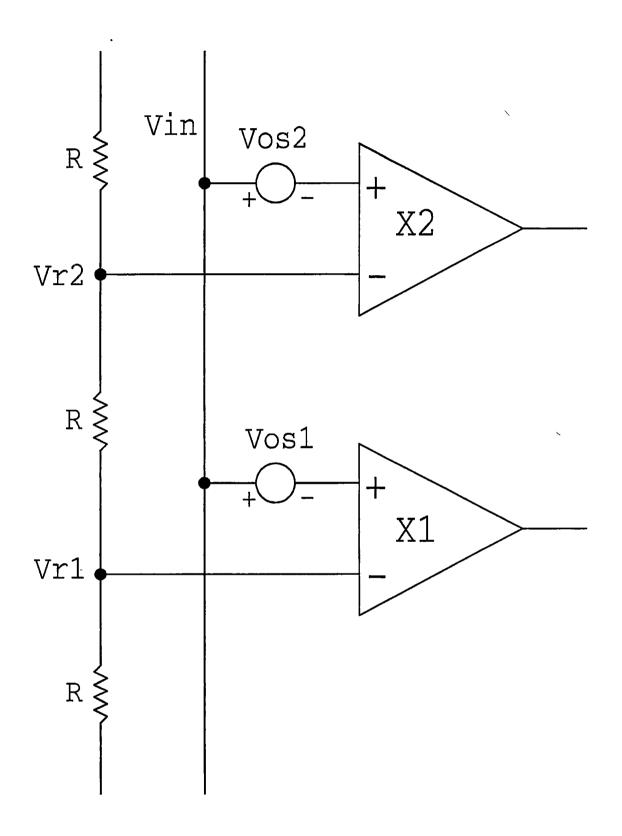

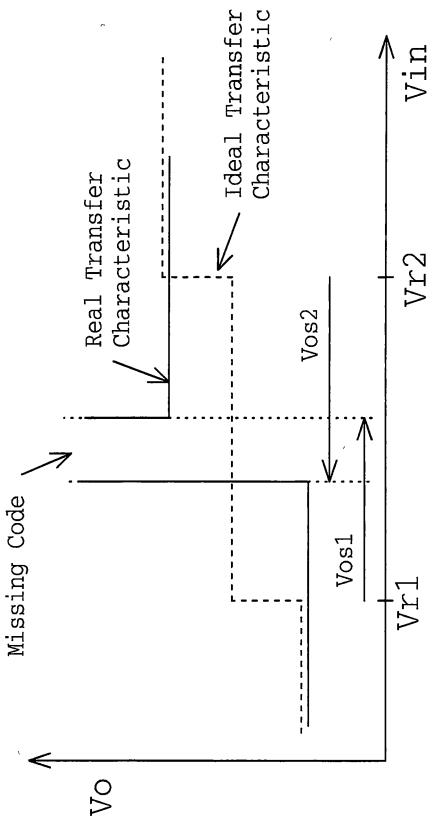

The relationship between the non-linearity errors of a flash or flash-type converter, the required resolution, and the comparator offset voltages can be developed. Consider two consecutive comparators in a flash or flash-type architecture shown in Figure 3-3. The output of comparator XI changes from 0 to 1 when  $V_{in} > V_{r1} - V_{OS1}$ . For comparator X2, the output change occurs when  $V_{in} > V_{r2} - V_{OS2}$ . The transition of one comparator ideally takes place when the input voltage,  $V_{in}$ , reaches its reference voltage. However, the actual transition occurs when  $V_{in}$  reaches  $V_r - V_{OS}$ . This deviation between the ideal transition and the actual transition is called integral non-linearity (INL). The INL error associated with one comparator is, its input offset voltage,  $V_{OS}$ , plus any error in the reference voltage,  $V_r$ , and is usually expressed as a fraction of a least significant bit (LSB).

The LSB of an ADC is defined as

$$LSB = \frac{V_{ref}}{2^N} , \qquad (3-1)$$

where  $V_{ref}$  is the reference voltage, equal to the ADC input voltage range, and N is the number of bits of the converter [25]. Considering comparator offset voltages and reference generation errors, the INL of a flash or flash-type ADC expressed as a fraction of a LSB can be written as

Figure 3-3. Two adjacent comparators in a flash or flash-type ADC architecture.

$$INL = \frac{\left|V_{os}\right| + \left|Vr_{actual} - Vr_{tdeal}\right|}{1 LSB} = \frac{\left|V_{os}\right| + \left|\Delta Vr\right|}{\frac{V_{ref}}{2^{N}}} . \tag{3-2}$$

Assuming the reference voltage,  $V_r$ , is ideal, the INL expressed as a fraction of a LSB simplifies to the expression

$$INL = \frac{\left|V_{os}\right|}{1 LSB} = \frac{\left|V_{os}\right|}{\frac{V_{ref}}{2^{N}}} . \tag{3-3}$$

The differential non-linearity (DNL) can be defined by considering the input values for which two consecutive comparators, XI and X2, change their output state. These values are  $V_{r1} - V_{OS1}$  and  $V_{r2} - V_{OS2}$  and the deviation of their difference with respect to their ideal value,  $\frac{V_{ref}}{2^N}$ , is the DNL. The DNL expressed as fraction of a LSB can be written as

$$DNL = \frac{1}{1 LSB} \left[ (V_{r2} - V_{OS2}) - (V_{r1} - V_{OS1}) - \frac{V_{ref}}{2^N} \right]. \tag{3-4}$$

If the references,  $V_{r1}$  and  $V_{r2}$ , are assumed to be ideal, then

$$(V_{r2} - V_{r1}) = \frac{V_{ref}}{2^N} , (3-5)$$

and the DNL expression can be simplified to

$$DNL = \frac{|V_{oS1} - V_{oS2}|}{1 LSB} = \frac{|V_{oS1} - V_{oS2}|}{\frac{V_{ref}}{2^N}}.$$

(3-6)

The derivation of Equations 3-3 and 3-6 illustrates the relationship between the comparator offset voltages, the resolution of the ADC, and the non-linearity

specifications of the ADC. Note that in general the DNL specification imposes a more stringent requirement on the offset voltage of the comparator,  $V_{OS}$ , than an INL specification of equal value.

Another important specification of an ADC is that of no missing codes. The condition of no missing codes refers to the fact that every ADC output code is present and represented. Figure 3-4 illustrates an ADC transfer function with a missing code. From the figure, it is evident that to satisfy the condition of no missing codes, the condition

$$|V_{OS1} \pm V_{OS2}| < V_{r2} - V_{r1} \tag{3-7}$$

must be satisfied. Again if the references,  $V_{r1}$  and  $V_{r2}$ , are assumed ideal, then the equation for the condition of no missing codes can be simplified to

$$|V_{os_1} \pm V_{os_2}| < \frac{V_{ref}}{2^N}$$

(3-8)

Most of the time a missing code is caused by excessively large differential non-linearity errors. If the DNL of an ADC is less than  $\pm 1$  LSB, then the condition of no missing codes is guaranteed. This application requires a DNL specification of  $\pm \frac{1}{2}$  LSB. Therefore, the condition of no missing codes is already represented by the DNL specification.

Based upon the linearity analysis presented, the calculation of the maximum allowable comparator offset voltage to meet the desired INL and DNL specifications of the converter can be performed by utilizing Equations 3-3 and 3-6. These foregoing equations can be used to derive conclusions concerning the implementation and architectural selection of a comparator in the design of ADCs employing parallel

Figure 3-4. ADC transfer function with a missing code due to excessively large comparator offsets.

conversion stages

For this particular application, the nominal reference voltage,  $V_{ref}$ , is 1.275 V and the number of desired bits, N, is 6. Therefore, the LSB of the ADC can be calculated as

$$1 LSB = \frac{1.275 V}{2^6} \approx 20 \ mV \ , \tag{3-9}$$

which results in a 20 mV/LSB resolution. To achieve the desired INL specification of  $\pm \frac{1}{2}$  LSB ( $\pm 10$  mV), the maximum allowable comparator offset can be calculated as

$$|V_{os}| < 10 \ mV$$

. (3-10)

Similarly, the maximum allowable offset voltage of two consecutive comparators to achieve the required DNL specification of  $\pm \frac{1}{2}$  LSB ( $\pm 10$  mV) can be calculated as

$$|V_{os1} - V_{os2}| < 10 \ mV \ . \tag{3-11}$$

If we assume that  $V_{OS1}$  and  $V_{OS2}$  are statistically independent random variables with zero average and equal standard deviation  $\sigma(V_{OS1}) = \sigma(V_{OS2}) = \sigma(V_{OS})$ , then

$$\sigma(V_{os1} - V_{os2}) = \sqrt{2}\sigma(V_{os})$$

, (3-12)

and Equation 3-11 can be expressed as

$$\sigma(V_{os1} - V_{os2}) = \sqrt{2}\sigma(V_{os}) < \frac{1}{2} LSB$$

(3-13)

Solving Equation 3-13 for the necessary standard deviation of the offset voltage to ensure a DNL specification of  $\pm \frac{1}{2}$  LSB ( $\pm 10$  mV) yields

$$\sigma(V_{os}) < 7 \ mV \ . \tag{3-14}$$

For good yield performance over extreme process conditions, we should impose a three sigma value of

$$3\sigma(V_{os}) < 7 \ mV \tag{3-15}$$

to satisfy the given INL and DNL specifications. Therefore, the required standard deviation of the offset voltage now becomes

$$\sigma(V_{os}) < 2.33 \, mV \, . \tag{3-16}$$

As Equations 3-10 and 3-16 illustrate, the standard deviation for each comparator's offset voltage is a very critical and crucial parameter to know in order to achieve good accuracy and linearity performance of a flash or flash-type ADC architecture.

A rough estimate of the offset voltage presented by a comparator can be performed if some basic assumptions about the offset phenomenon are made. The first simplification is that the random offset component of the comparator's offset voltage is the dominant source of error and therefore the systematic offset component is completely negligible. Also, if the input-referred offset voltage of a comparator is assumed to be dominated by the differential input transistor pair, then MOSFET transistor threshold voltage mismatch is the dominant source of offset voltage error. (As will be explained later in this chapter, these are not necessarily always good assumptions and will result in a very optimistic calculation. However, using these assumptions will provide an approximate offset voltage anticipated for a given comparator.) If these assumptions are granted, then the standard deviation of the random component of a comparator's offset voltage can be calculated using matching theory [29, 30]. The equation that predicts threshold voltage mismatch of adjacent devices with equal layout area is

$$\sigma(\Delta V_T) = \frac{A_{VTO}}{\sqrt{Weff \cdot Leff}} , \qquad (3-17)$$

where  $A_{VTO}$  is a constant and Weff and Leff are the effective channel width and length of the device, respectively. For submicron processes, reported values of  $A_{VTO}$  have been around the value of 25 mV  $\mu$  [22]. Using this expression, one can calculate the required transistor area to achieve the necessary threshold voltage matching for a low offset comparator. Assuming that  $\sigma(\Delta V_T) \approx \sigma(V_{OS})$  and the application requirement of  $\sigma(V_{OS}) < 2.33 \ mV$ , the required input transistor dimensions can be expressed as

$$Weff \cdot Leff = \left[ \frac{A_{VTO}}{\sigma(V_{OS})} \right], \tag{3-18}$$

and substitution of parameters yields

$$Weff \cdot Leff = \left[ \frac{25 \ mV \cdot \mu}{2.33 \ mV} \right]^2 \approx 115 \ \mu^2 \ . \tag{3-19}$$

This optimistic calculation illustrates the requirement for very large input devices of the comparator needed to achieve sufficient matching accuracy to guarantee an offset voltage,  $\sigma(V_{OS})$ , of less than 2.33 mV. Consequently, these devices will occupy a fair amount of silicon area and present a large input capacitance. Also, depending upon the actual selection of transistors sizes for the input pair, these transistors could also consume a large current for strong inversion operation. It is important to note that this calculation also assumes ideal reference voltage generation for the comparators. In reality, the voltage references provided for the comparators will be non-ideal and therefore the maximum allowable comparator offset voltage will be reduced. Also, unless sufficient statistical data is available for the  $A_{VTO}$  parameter of a given process, it is questionable whether low offset voltages can be achieved over extreme process conditions. Although

others have reported successful ADC implementations at the 6 to 8 bit level without the use of auto-zeroed or offset corrected comparators, it was decided to employ offset correction techniques instead of intensive transistor dimension optimization to achieve acceptable comparator offset performance for this application [18, 22].

#### 3.1.3 Limitations of Offset Cancellation Due to Charge Injection

CMOS technology provides the advantages of simple zero-offset, low leakage analog switches, high-impedance charge storage nodes, and complementary devices. This analog sampling capability inherent in CMOS technology provides a means whereby offsets can be periodically sensed, stored, and then subtracted from the input signal. These CMOS characteristics allow for the extensive use of circuit techniques for comparator offset cancellation. Comparator offset correction techniques are intended to achieve improved resolution and speed, while maintaining low power dissipation, small area and input capacitance, and low complexity.

Perhaps the major limitation on the offset cancellation process of a comparator is due to charge injection. This error is a result of unwanted charges that are injected into a circuit when transistor switches turn off. In CMOS technology, switches are usually implemented by either using a single NMOS or PMOS transistor or by a CMOS transmission gate that is composed of both a NMOS and PMOS device connected in parallel. Examples of these possible switch configurations are shown in Figure 3-5. All of these switches have their particular application which usually depends upon the desired pass signal voltage levels.

Figure 3-5. Typical analog switch configurations available in CMOS technology.

Unfortunately, the non-ideal effects typically associated with these CMOS switches can be significant and may ultimately limit the performance of some high precision circuits. The charge injection errors associated with CMOS switches are caused by two mechanisms known as channel charge injection and clock feedthrough

#### 3.1.3.1 Channel Charge Injection Effects

The channel charge injection effect usually dominates the overall charge injection error and can be understood with the help of Figure 3-6. When the control signal  $V_{CONTROL}$  is high or a logical 1, the NMOS device is in the ohmic region resulting in a very small  $V_{DS}$  of the device. Under this condition, the switch or transistor is considered to be on and charge is accumulated under the gate oxide of the device. The channel charge of a transistor that has zero  $V_{DS}$  is given by

$$Qch = W L C_{OX} \cdot (V_{GS} - V_T) , \qquad (3-20)$$

where W and L are the device dimensions,  $C_{OX}$  is the gate oxide capacitance, and  $(V_{GS} - V_T)$  is the gate overdrive of the device [24]. When the control signal is taken low or a logical 0, the NMOS transistor turns off and this channel charge must flow out of the channel region through the source and drain junctions of the transistor. As a result, a portion of this charge is injected onto the hold capacitor,  $C_h$ , and the input signal,  $V_{in}$ . If the control signal waveform is fast, this channel charge distributes equally between the two connecting nodes [31, 32]. Therefore, half of the channel charge is injected on  $C_h$  and the other half to the input signal generator. Since  $V_{in}$  is typically a low impedance node, the injected charge has little or no effect on this node. However, the  $Q_{Ch}/2$  charge

Figure 3-6. Simple circuit configuration using a NMOS switch to illustrate channel charge injection effects.

injected onto the hold capacitor results in a corresponding voltage change that introduces an error. Since in this example, a NMOS transistor is used as the switch, this injected charge is negative and will cause a decrease in voltage across the hold capacitor. The voltage change due to channel charge injection is given by the expression

$$\Delta V_{CCI} = \frac{\frac{Qch}{2}}{C_h} = \frac{-W \ L \cdot C_{OX} \ (V_{GS} - V_T)}{2 \ C_h} \ , \tag{3-21}$$

and can be calculated for a given transistor switch size, hold capacitor, and input signal voltage [24]. If CMOS logic levels are used for the transistor control signal, then Equation 3-21 can be simplified to

$$\Delta V_{CCI} = \frac{-W \quad L \cdot C_{OX} \quad [Vdd - V_{In} - V_T]}{2 \cdot C_h} \quad . \tag{3-22}$$

The current form of Equation 3-22 can sometimes mask a subtle problem associated with charge injection. At first glance it might appear as if the charge injection is linearly related to the input signal. However, the threshold voltage of the NMOS device is dependent upon the input signal voltage level due to the body effect of the device. Modifying Equation 3-22 to include the transistor threshold voltage dependence upon the input signal results in

$$\Delta V_{CCI} = \frac{-W \ L \cdot C_{OX} \ \left[ Vdd - V_{in} - \left( V_{TO} + \gamma \left( \sqrt{2\phi_F + V_{in}} + \sqrt{2\phi_F} \right) \right) \right]}{2 \cdot C_h}$$

(3-23)

Thus, the voltage change across  $C_h$  caused by channel charge injection is dependent upon the input signal in a nonlinear relationship. Since channel charge injection is input signal dependent, complete cancellation of channel charge injection is very difficult to achieve for varying ranges of input signal conditions.

#### 3.1.3.2 Clock Feedthrough Effects

The other component of charge injection is clock or capacitive feedthrough. This effect can be explained through the use of Figure 3-7. Illustrated in the figure are the gate-to-diffusion overlap capacitances associated with a MOS transistor. Clock feedthrough occurs on each transition of the clock or control signal edge. When the gate control signal switches, the clock signal feeds through the  $C_{ov1}$  and  $C_{ov2}$  overlap capacitances onto the source and drain nodes. However, this effect is usually only of concern when the control signal transition is in a direction to turn the switch off. This is because when the transistor is turned on, the capacitor  $C_h$  will charge to the correct final value regardless of the injected charge from the clock signal. Thus, the result is that capacitive feedthrough has no effect on the circuit when the switch is turned on. However, when the transistor turns off, the capacitive divider that exists between the  $C_{ov2}$  capacitance and the hold capacitance will couple the clock signal from the gate to the storage node and introduces an error which in some cases can be significant.

One can use capacitive voltage division to calculate the change in voltage across the  $C_h$  capacitor due to the clock feedthrough phenomenon [24]. Applying this to the circuit of Figure 3-7 results in

$$\Delta V_{CFT} = \frac{\Delta V_{in} \cdot C_{ov2}}{C_{ov2} + C_{b}} = \frac{\left(Vgnd - Vdd\right) C_{ov2}}{C_{ov2} + C_{b}} , \qquad (3-24)$$

which is just capacitive voltage division between the gate-to-diffusion overlap capacitance and the hold capacitor. This voltage excursion is typically less than the channel charge injection component of charge injection because  $C_{ov2}$  can be kept relatively small when compared to the capacitor  $C_h$ . However, for high-precision signal

Figure 3-7. Simple circuit configuration using a NMOS switch to illustrate capacitive feedthrough effects.

processing circuits both components of charge injection must be considered and minimized.

#### 3.1.3.3 Techniques to Minimize Charge Injection in CMOS Circuits

To illustrate the significance of charge injection errors in CMOS circuits, an example calculation will be performed. Assume in Figure 3-6 or Figure 3-7 the following conditions:  $C_h$ =0.5 pF,  $C_{OX}$ =2.11 fF/ $\mu$ m<sup>2</sup>,  $W_1$ =2.5  $\mu$ m,  $L_1$ =0.8  $\mu$ m,  $C_{ov1}$ = $C_{ov2}$ =0.525 fF,  $V_T$ =0.8 V,  $V_d$ d=5 V, and  $V_{in}$ =2.5 V. These are typical parameters in a 0.8  $\mu$ m CMOS process. Based upon these conditions, the channel charge injection component can be calculated using Equation 3-22 and is given by

$$\Delta V_{CCI} = \frac{-(2.5 \text{ um}) \cdot (.8 \text{ um}) (2.1 \text{ fF/um}^2) \cdot [5 \text{ V} - 2.5 \text{ V} - 0.8 \text{ V}]}{2 500 \text{ fF}} = -7.1 \text{ mV} . (3-25)$$

The clock feedthrough error component of charge injection can be calculated using Equation 3-24 and is given by

$$\Delta V_{CFT} = \frac{(-5V)(0.525 \ fF)}{500 \ fF + 0.525 \ fF} = -5.2 \ mV \ . \tag{3-26}$$

Thus the total charge injection error due to the non-ideal effects of the NMOS switch can be found by adding the results of Equations 3-25 and 3-26, which sums to

$$\Delta V_{ERROR} = \Delta V_{CCI} + \Delta V_{CFT} = (-7.1 \, mV) + (-5.2 \, mV) = -12.3 \, mV$$

(3-27)

The result of Equation 3-27 shows a charge injection error that is about factor-of-five larger than the allowed corrected comparator offset voltage. Obviously, additional measures must be taken in order to minimize the effects of charge injection errors in offset correction circuits.

Based upon Equations 3-22 and 3-24, both components of charge injection can be reduced by the use of largest possible capacitors values, the use of minimum geometry switches, and keeping control signal levels as small as possible. However, these obvious solutions to minimize charge injection are sometimes very difficult to satisfy and still meet high-performance design requirements. Therefore, certain design compromises must always be made. For example, linear capacitors on an integrated circuit require a large amount of silicon area and these capacitors typically have large (10-15%) parasitic capacitances associated with them. These parasitic capacitances can be significant and can reduce the bandwidth performance of circuits. As a result, capacitors cannot just be made arbitrarily large to reduce charge injection effects. In addition, the reduction in control signal voltages to minimize charge injection drastically reduces the dynamic range of single device switches and thus the signal processing circuits. Also, minimum size switches cannot always be used either. These small switches usually have a high switch on resistance that can create non-negligible time constants on critical nodes in a circuit. Therefore, other solutions to minimize charge injection errors must be utilized. Since charge injection limits the performance of offset cancellation techniques in comparators and other circuits, many methods have been reported to reduce its effects

One of the most common charge injection cancellation techniques is the use of a compensation transistor or dummy switch. This circuit configuration is illustrated in Figure 3-8. Note that two complementary control signals are now required for operation of the switch. Although transistor M2 has its drain and source connected to the capacitor node, a channel charge is still formed under the gate oxide when a voltage is applied to

Figure 3-8. Simple circuit illustrating the use of a compensation transistor to minimize charge injection.

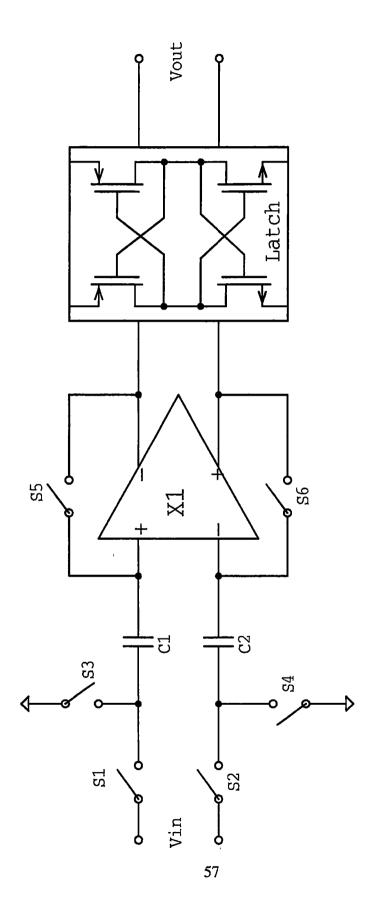

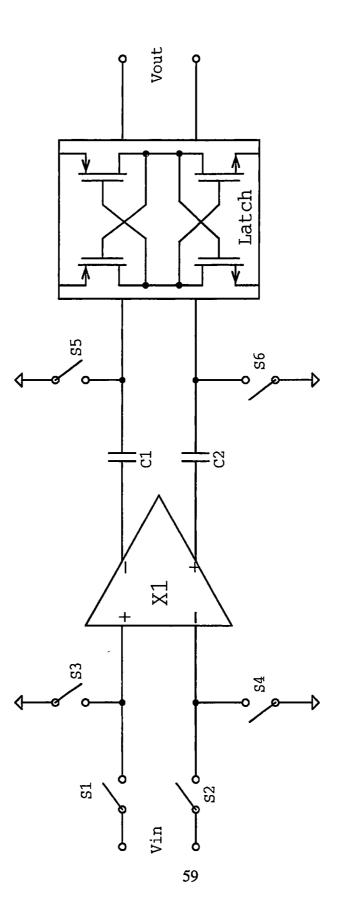

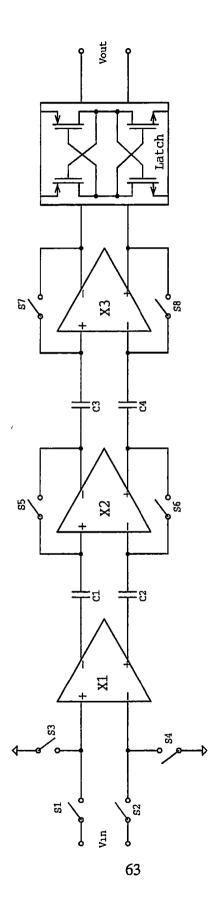

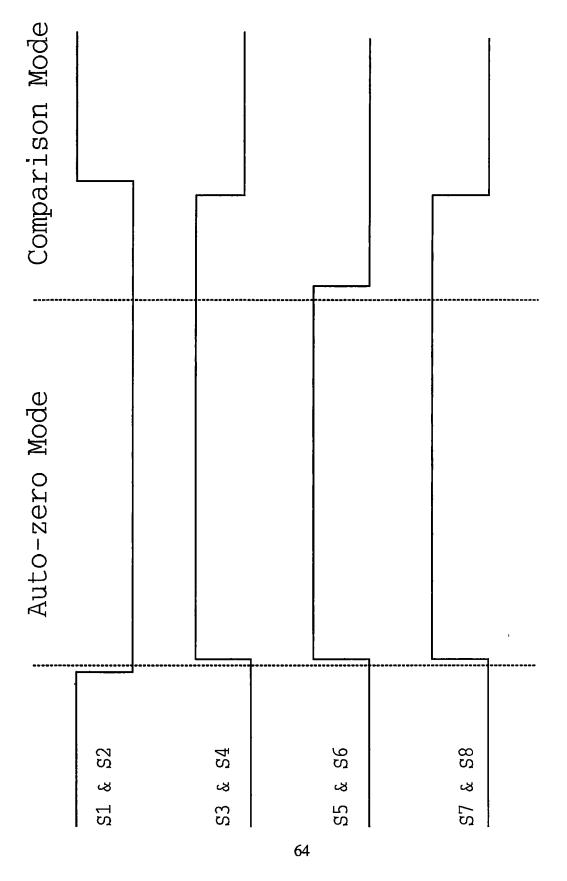

the gate of the device. The size of transistor M2 is designed to provide charge cancellation and is usually selected as half the size of transistor M1. As discussed earlier, when transistor M1 turns off, half of the channel charge is injected onto the hold capacitor. However, with transistor M2 in the circuit, the charge injected by transistor M1 is absorbed or matched by the charge induced by the transistor M2 and the overall channel charge injection is cancelled. Also, this configuration provides partial clock feedthrough cancellation because transistors M1 and M2 have complementary clock control signals.