# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

Masters Theses

**Graduate School**

8-2000

# A low-noise microluminometer for a bioluminescent bioreporter integrated circuit

**Gregory Wayne Patterson**

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

#### **Recommended Citation**

Patterson, Gregory Wayne, "A low-noise microluminometer for a bioluminescent bioreporter integrated circuit. " Master's Thesis, University of Tennessee, 2000. https://trace.tennessee.edu/utk\_gradthes/9470

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Gregory Wayne Patterson entitled "A low-noise microluminometer for a bioluminescent bioreporter integrated circuit." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

James M. Rochelle, Major Professor

We have read this thesis and recommend its acceptance:

Michael L. Simpson, T. Vaughn Blalock

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council

I am submitting herewith a thesis written by Gregory Wayne Patterson entitled "A Low-Noise Microluminometer for a Bioluminescent Bioreporter Integrated Circuit " I have examined the final copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with major in Electrical Engineering

m Rochella

James M Rochelle, Major Professor

We have read this thesis and recommend its acceptance

Michael J. pringsers J. Vaugher Blalock

Accepted for the Council

Lewminkel

Associate Vice Chancellor and Dean of The Graduate School

# A Low-Noise Microluminometer for a Bioluminescent Bioreporter

**Integrated Circuit**

A Thesis

Presented for the

Master of Science

Degree

The University of Tennessee, Knoxville

Gregory Wayne Patterson

August 2000

•

## **Dedication**

This thesis is dedicated to my parents,

Mr Robert L Patterson

And

Mrs Shirley A Patterson

who have given me love and encouragement throughout my academic career

#### Acknowledgements

I would like to thank several people without whom this thesis could never have been completed I would first like to thank the members of my thesis committee I thank my major professor, Dr James M Rochelle, for the many hours he spent with me in the laboratory during testing and the helpful advice he gave me concerning design issues and the direction of my thesis He has been an excellent mentor I thank Dr Michael L Simpson for giving me the opportunity to be a part of this research and giving me valuable instruction throughout my work I thank Dr T V Blalock for his help during the writing of this thesis, particularly in the area of noise analysis I also thank him for the outstanding undergraduate education I received in analog electromics

I am grateful to the University of Tennessee and the Oak Ridge National Laboratory for making my graduate work possible through the UT/ORNL Joint Program in Mixed-Signal VLSI and Monolithic Sensors I would also like to thank the Perkin-Elmer Corporation, the U S Department of Energy, and the Oak Ridge National Laboratory for sponsoring this research Several other individuals are also responsible for the completion of this work I would like to thank Eric Bolton, who will be continuing this research in pursuit of his Master's Degree I also thank Dr David Binkley of Concorde Microsystems for providing me with valuable information on low-noise design and device noise modeling Finally, I want to thank my family for their love and support I thank God for them and all of the blessings He has given me in my life

1

#### Abstract

This thesis presents the analysis and design of a low-noise microluminometer for a hybrid electronic/biological chemical sensor known as a Bioluminescent Bioreporter Integrated Circuit (BBIC) The microluminometer consists of photodetection and signal processing Both functions are integrated in a standard bulk CMOS process (HP 0 5 µm CMOS)

The photodetection is first described in terms of physical operation The implementation of photodetectors in a CMOS integrated circuit process is then presented The signal processing system is analyzed, and the errors introduced by individual system components are described A detailed system-level noise analysis is also presented The design of a low-noise amplifier is the focus of this thesis The amplifier design is described in detail Finally, the results from testing of the fabricated prototype are presented

# **Table of Contents**

| Chapter 1: Introduction                                      | 1   |

|--------------------------------------------------------------|-----|

| 1 1 Distributed Chemical Sensing                             | 1   |

| 1 2 Biosensors                                               | 1   |

| 1 2 1 Whole-cell Biosensors                                  | . 2 |

| 1 2 2 Bioluminescent Bioreporters                            | 2   |

| 1 3 The Bioluminescent Bioreporter Integrated Circuit (BBIC) | 3   |

| 1 3 1 Low-Noise Microlumnometer                              | 5   |

| 1 3 1 1 Integrated Photodetection .                          | 5   |

| 1 3 1 2 Low-Noise Signal Processing                          | 6   |

| 1 3 2 BBIC Design Challenges .                               | 6   |

| 1 4 Scope of Thesis                                          | 7   |

| Chapter 2: Microluminometer System Analysis and Design       | 9   |

| 2 1 Microluminometer System Overview .                       | 9   |

| 2 2 Photodetection                                           | 11  |

| 2 2 1 Photodiode Operation                                   | 11  |

| 2 2 2 Photodiode Modeling                                    | 16  |

| 2 2 2 1 Photodiode Currents                                  | 16  |

| 2 2 2 2 Photodiode Resistance                                | 19  |

|    | 2 2 2 3 Photodiode Capacitance            | 19 |

|----|-------------------------------------------|----|

|    | 2224 Photodiode Noise                     | 20 |

|    | 2 2 3 Detector Biasing                    | 23 |

|    | 2 2 4 Integrated Photodetection in CMOS   | 23 |

|    | 2241 CMOS Photodetector Evaluation        | 25 |

| 23 | Signal Processing                         | 29 |

|    | 2 3 1 Signal Processing Requirements      | 29 |

|    | 2 3 2 Basic System Topology and Operation | 30 |

|    | 2 3 3 Signal Processing Components        | 35 |

|    | 2 3 3 1 Integrator                        | 35 |

|    | 2 3 3 1 1 Integration Capacitor           | 37 |

|    | 2 3 3 1 2 Gain Error                      | 40 |

|    | 2 3 3 1 3 Reset Error                     | 41 |

|    | 2 3 3 1 4 Amplifier Offset Voltage        | 44 |

|    | 2 3 3 1 5 Amplifier Noise                 | 45 |

|    | 2 3 3 2 Reset Switch                      | 46 |

|    | 2 3 3 2 1 Charge Injection                | 46 |

|    | 2 3 3 2 2 Switch Leakage                  | 49 |

|    | 2 3 3 3 Low-pass Filter                   | 52 |

|    | 2 3 3 4 Comparator                        | 54 |

|    | 2 3 3 5 One-shot                          | 54 |

|    | 2 3 3 6 Toggle Flop                       | 55 |

| 2 3 3 7 Counter and Other Digital Circuitry                                                                                                                                                                                                                                    | . 55                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 4 System Noise Analysis                                                                                                                                                                                                                                                      | 57                                           |

| 2 4 1 White Noise Analysis                                                                                                                                                                                                                                                     | 58                                           |

| 2 4 1 1 Detector Noise                                                                                                                                                                                                                                                         | 58                                           |

| 2 4 1 2 Amplifier Voltage Noise                                                                                                                                                                                                                                                | . 64                                         |

| 2 4 1 3 Combined White Noise Analysis                                                                                                                                                                                                                                          | 68                                           |

| 2 4 2 1/f Noise Analysis                                                                                                                                                                                                                                                       | 69                                           |

| 2 4 2 1 Detector Noise                                                                                                                                                                                                                                                         | 70                                           |

| 2 4.2 2 Amplifier Voltage Noise                                                                                                                                                                                                                                                | 73                                           |

| 2.5 System Simulation                                                                                                                                                                                                                                                          | 75                                           |

| 2 6 CMOS Implementation                                                                                                                                                                                                                                                        | 80                                           |

|                                                                                                                                                                                                                                                                                |                                              |

| Chapter 3: Low-Noise Amplifier Design                                                                                                                                                                                                                                          | . 86                                         |

| Chapter 3: Low-Noise Amplifier Design 3 1 Amplifier Requirements                                                                                                                                                                                                               | . 86<br>86                                   |

|                                                                                                                                                                                                                                                                                |                                              |

| 3 1 Amplifier Requirements                                                                                                                                                                                                                                                     | 86                                           |

| 3 1 Amplifier Requirements       3.2 Amplifier Topology                                                                                                                                                                                                                        | 86<br>. 87                                   |

| 3 1 Amplifier Requirements         3.2 Amplifier Topology         3 3 Amplifier Noise Analysis                                                                                                                                                                                 | 86<br>. 87<br>93                             |

| <ul> <li>3 1 Amplifier Requirements</li> <li>3.2 Amplifier Topology</li> <li>3 3 Amplifier Noise Analysis</li> <li>3 3 1 Noise Modeling</li> </ul>                                                                                                                             | 86<br>. 87<br>93<br>93                       |

| <ul> <li>3 1 Amplifier Requirements</li> <li>3.2 Amplifier Topology</li> <li>3 3 Amplifier Noise Analysis</li> <li>3 3 1 Noise Modeling</li> <li>3 3 2 Mathematical Analysis</li> </ul>                                                                                        | 86<br>. 87<br>93<br>93<br>95                 |

| <ul> <li>3 1 Amplifier Requirements</li> <li>3.2 Amplifier Topology</li> <li>3 3 Amplifier Noise Analysis</li> <li>3 3 1 Noise Modeling</li> <li>3 3 2 Mathematical Analysis</li> <li>3 4 Frequency Response/Stability Analysis</li> </ul>                                     | 86<br>. 87<br>93<br>93<br>93<br>95<br>. 100  |

| <ul> <li>3 1 Amplifier Requirements</li> <li>3.2 Amplifier Topology</li> <li>3 3 Amplifier Noise Analysis</li> <li>3 3 1 Noise Modeling</li> <li>3 3 2 Mathematical Analysis</li> <li>3 4 Frequency Response/Stability Analysis</li> <li>3 5 Final Amplifier Design</li> </ul> | 86<br>. 87<br>93<br>93<br>95<br>. 100<br>104 |

| 3 6 3 Gain Error Analysis                                | 109 |

|----------------------------------------------------------|-----|

| Chapter 4: Measurement Results                           | 113 |

| 4 1 Test Setup                                           | 113 |

| 4 2 Initial Evaluation                                   | 115 |

| 4 3 Test Results                                         | 122 |

| 4 3 1 Room Temperature Testing                           | 122 |

| 4 3 1 1 Leakage Current                                  | 122 |

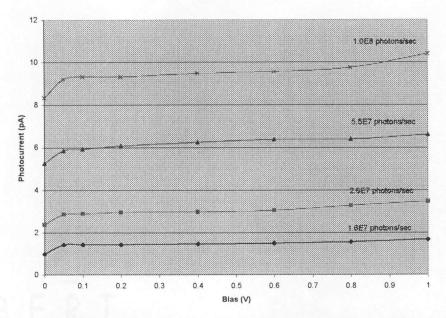

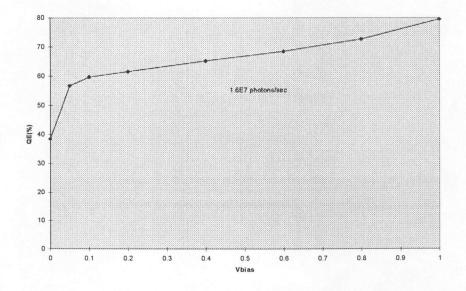

| 4 3 1 2 Photocurrent Measurement                         | 126 |

| 4 3 2 Temperature Effects                                | 130 |

| Chapter 5: Conclusions and Future Work                   | 132 |

| 5 1 Conclusions                                          | 132 |

| 5 2 Future Work                                          | 133 |

| References                                               | 135 |

| Appendices                                               | 141 |

| Appendix 1 – BSIM1 MOS Device Models                     | 142 |

| Appendix 2 – Extracted System Netlist                    | 144 |

| Appendıx 3 – Low-Noise Amplifier Netlist                 | 154 |

| Appendix 4 – Low-Noise Amplifier DC Operating Point Data | 156 |

| Vita                                                     | 158 |

# List of Figures

| Figure                                                             | Page |

|--------------------------------------------------------------------|------|

| Figure 1 The Bioluminescent Bioreporter Integrated Circuit Concept | 4    |

| Figure 2 Basic Microluminometer Operation                          | 10   |

| Figure 3 Photodiode Operation                                      | 12   |

| Figure 4 Absorption Coefficient of Crystalline Silicon             | 15   |

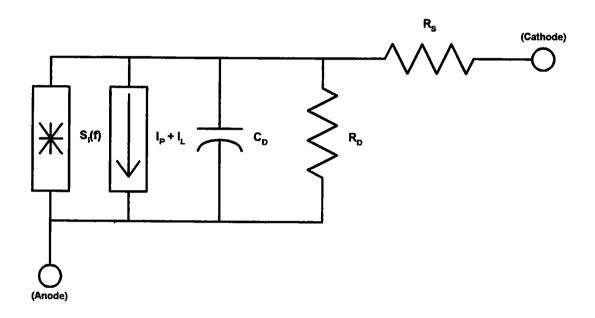

| Figure 5 Simple Photodiode Model                                   | 17   |

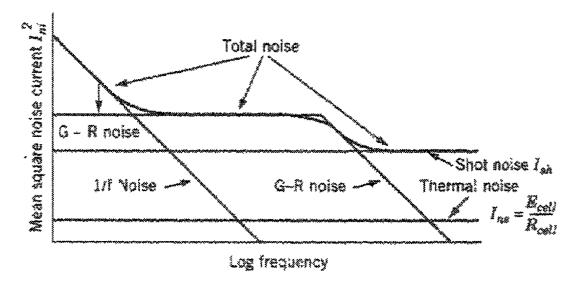

| Figure 6 Composite Photodiode Noise Current Spectrum               | 22   |

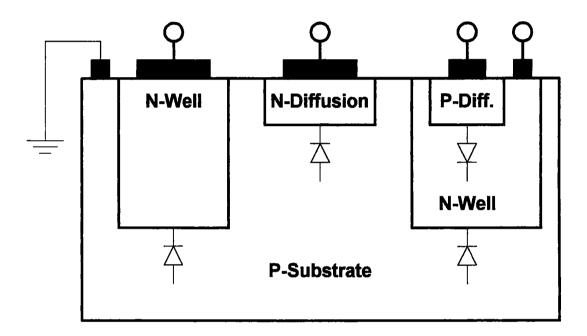

| Figure 7 CMOS-compatible Photodetectors                            | 24   |

| Figure 8 CMOS Photodetector Evaluation Test Chip                   | 26   |

| Figure 9 N-well Photodetector                                      | 27   |

| Figure 10 Light-to-Frequency Converter                             | 31   |

| Figure 11 System Timing                                            | 32   |

| Figure 12 Integrator with Error Sources                            | 36   |

| Figure 13 Simple MOS IC Capacitor                                  | 38   |

| Figure 14 Linearized IC Capacitor                                  | 39   |

| Figure 15 Charge Injection Error                                   | 47   |

| Figure 16 Switch Leakage Error                                     | 50   |

| Figure 17 Low-pass Filter                                          | 53   |

| Figure 18 Frequency Divider                             | 56  |

|---------------------------------------------------------|-----|

| Figure 19 Switched Integrator with Detector Noise       | 59  |

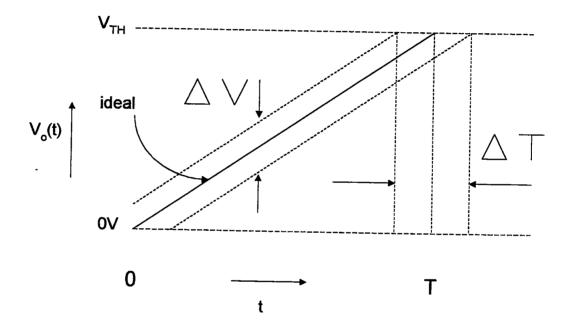

| Figure 20 Translation of Voltage Noise to Timing Jitter | 60  |

| Figure 21 Noise Sampling During Reset                   | 65  |

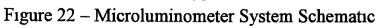

| Figure 22 Microluminometer System Schematic             | 76  |

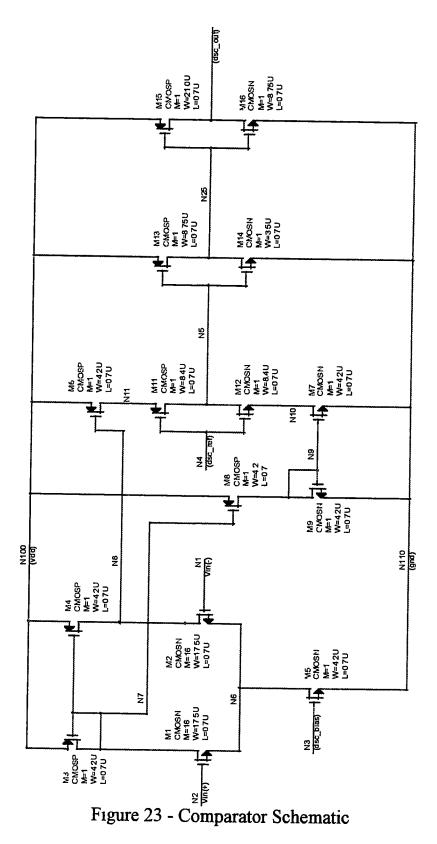

| Figure 23 Comparator Schematic                          | 77  |

| Figure 24 One-Shot Schematic                            | 78  |

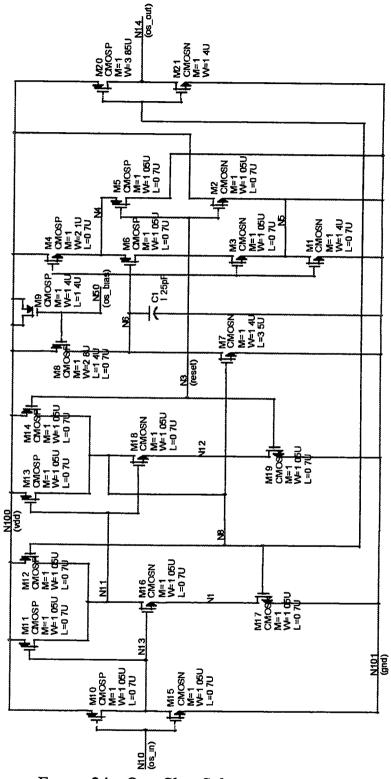

| Figure 25 Bias Cell                                     | 79  |

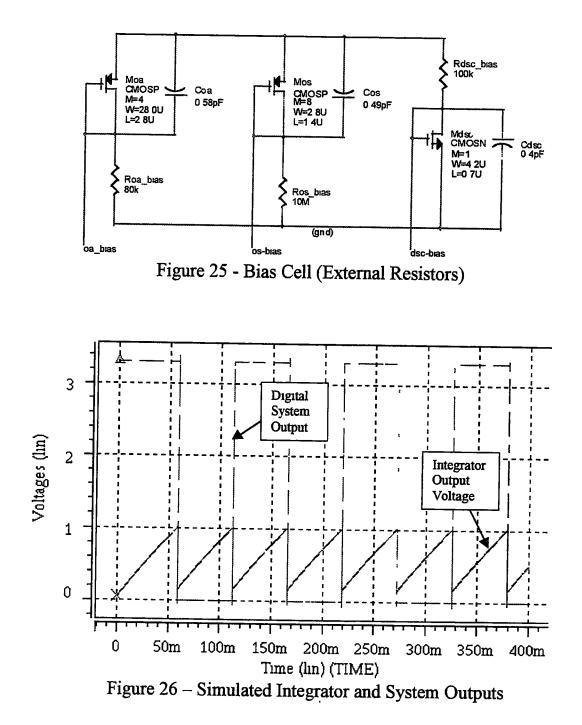

| Figure 26 Simulated Integrator and System Outputs       | 79  |

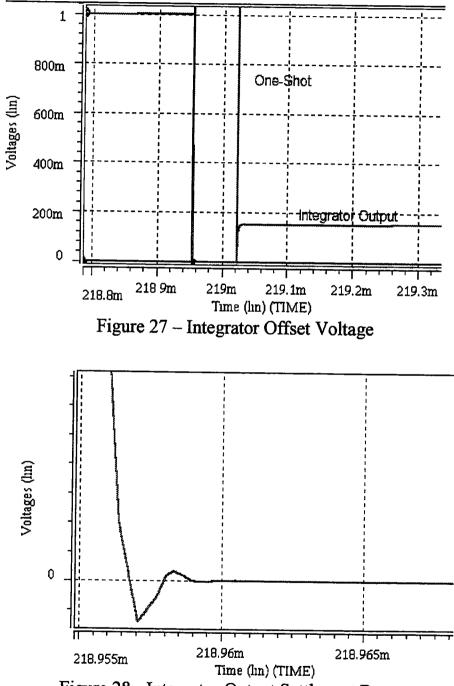

| Figure 27 Integrator Offset Voltage                     | 81  |

| Figure 28 Integrator Output Settling at Reset           | 81  |

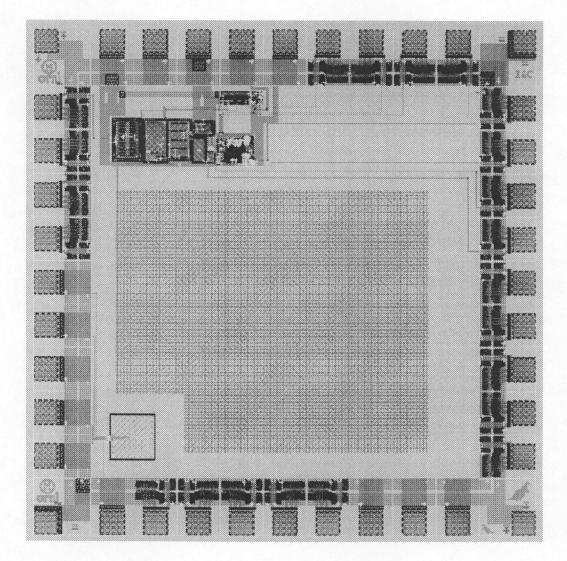

| Figure 29 Microluminometer Prototype IC Layout          | 82  |

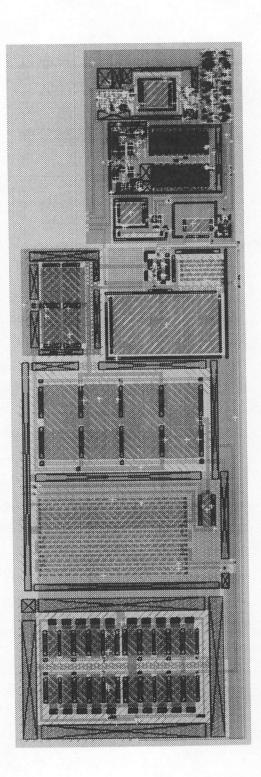

| Figure 30 Signal Processing Layout                      | 83  |

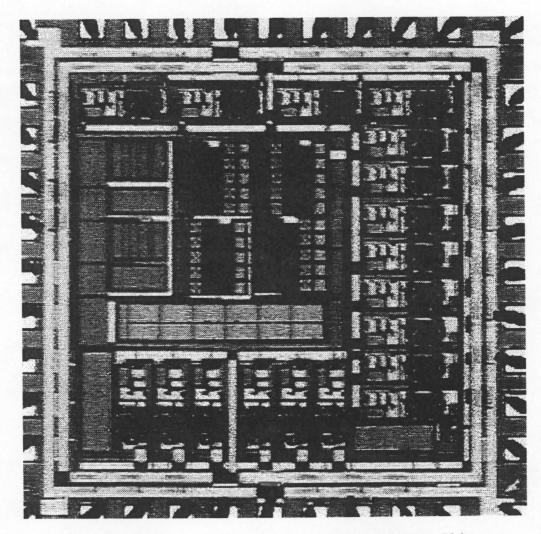

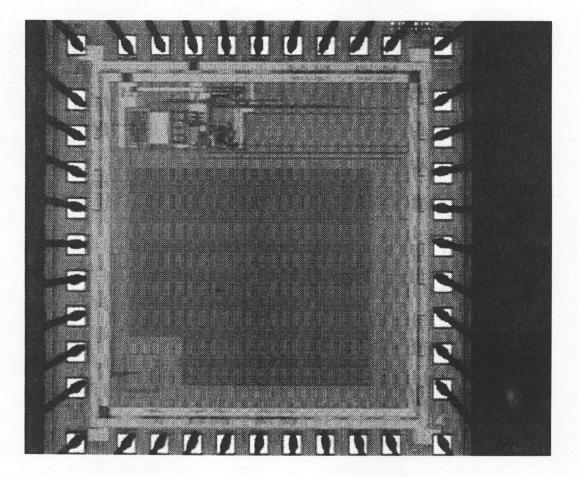

| Figure 31 Microluminometer Prototype Chip Photograph    | 85  |

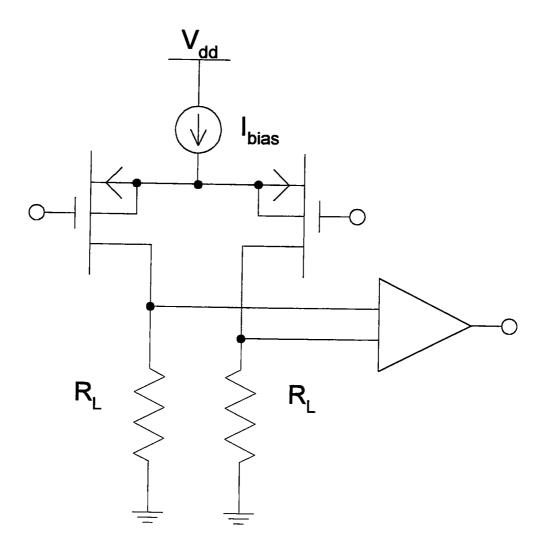

| Figure 32 Resistively Loaded Amplifier Topology         | 89  |

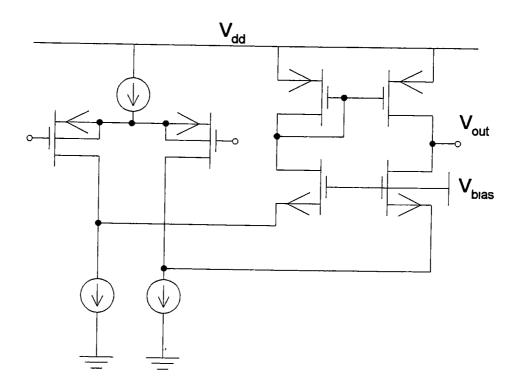

| Figure 33 Folded Cascode Amplifier                      | 90  |

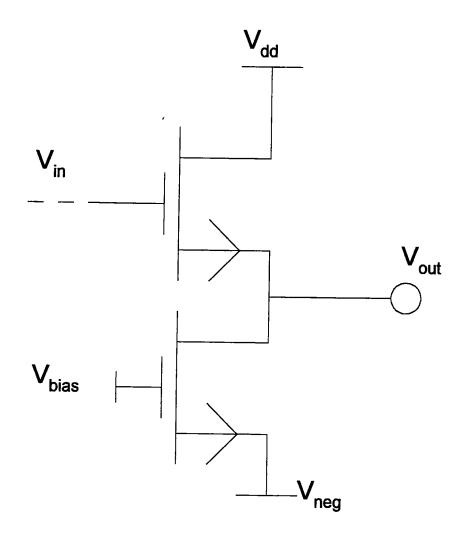

| Figure 34 Output Buffer                                 | 92  |

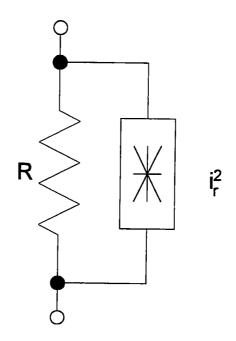

| Figure 35 Resistor Noise Model                          | 94  |

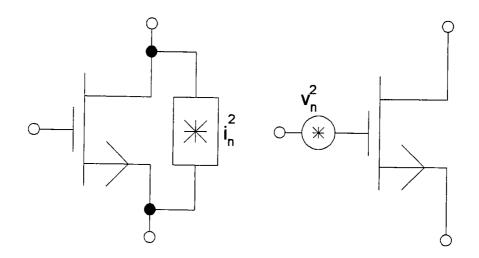

| Figure 36 MOS Noise Model                               | 94  |

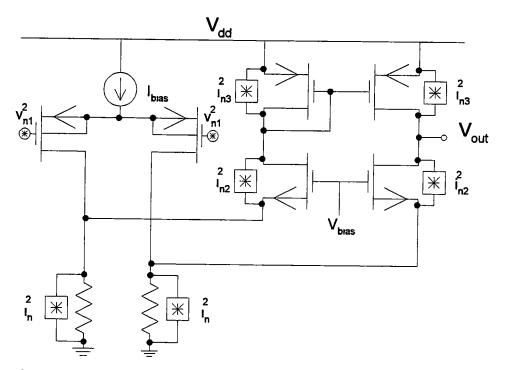

| Figure 37 Folded Cascode Amplifier with Noise Sources   | 96  |

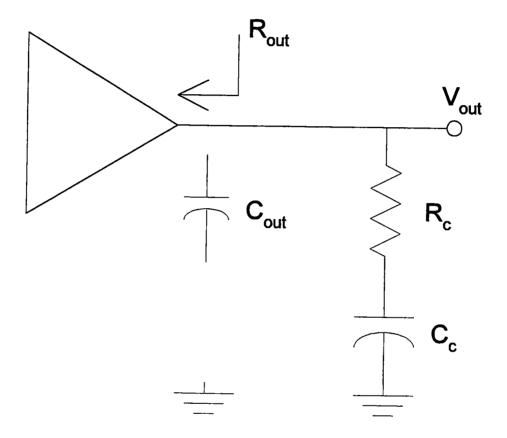

| Figure 38 Lead Compensation                             | 102 |

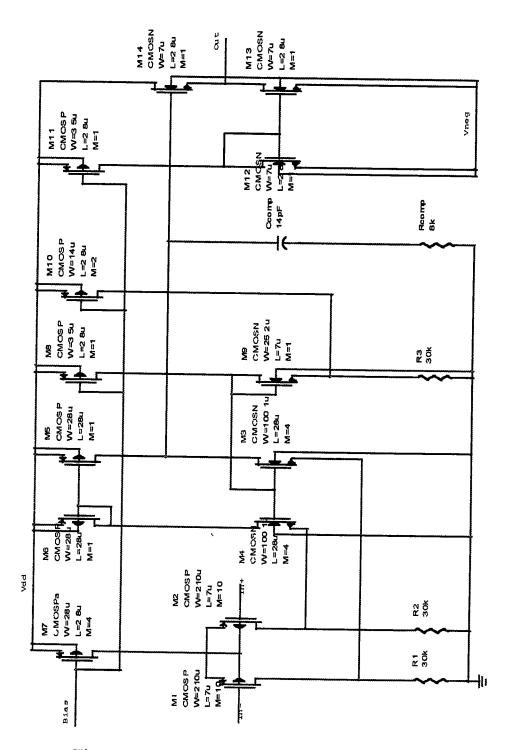

| Figure 39 Low-Noise Amplifier Schematic                 | 105 |

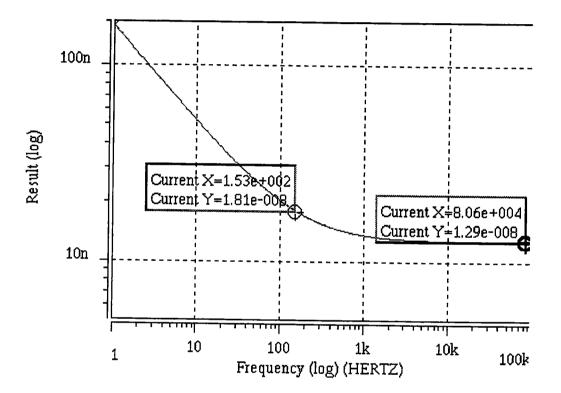

| Figure 40 Input Equivalent Noise Voltage                           | 107 |

|--------------------------------------------------------------------|-----|

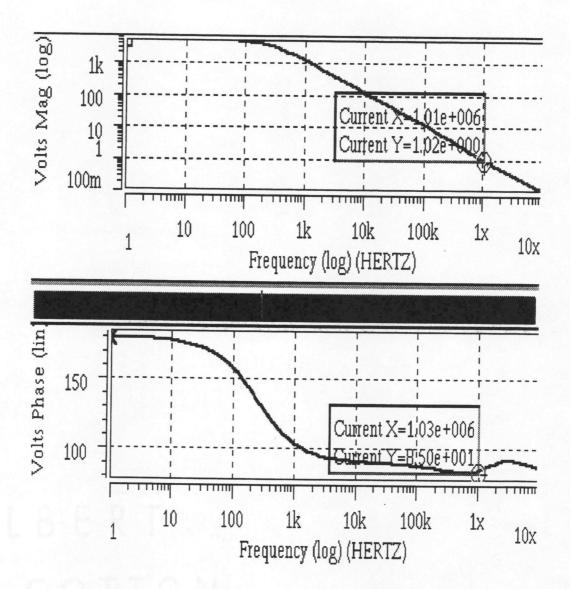

| Figure 41 LNA Frequency Response                                   | 110 |

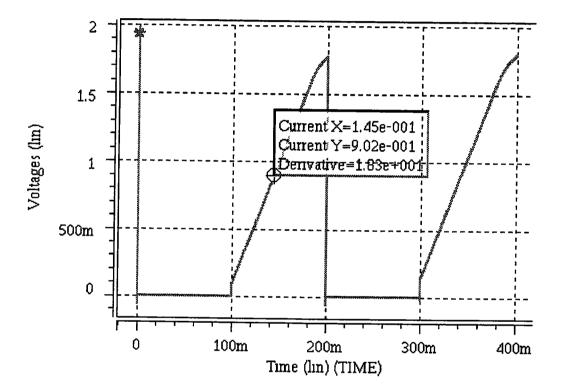

| Figure 42 Gain Error Measurement                                   | 112 |

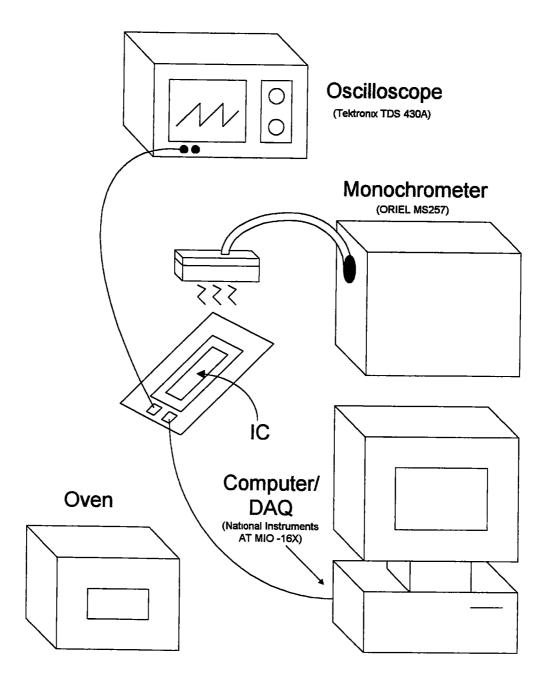

| Figure 43 Microluminometer Prototype Test Setup                    | 114 |

| Figure 44 System Error due to Inaccurate Reset                     | 116 |

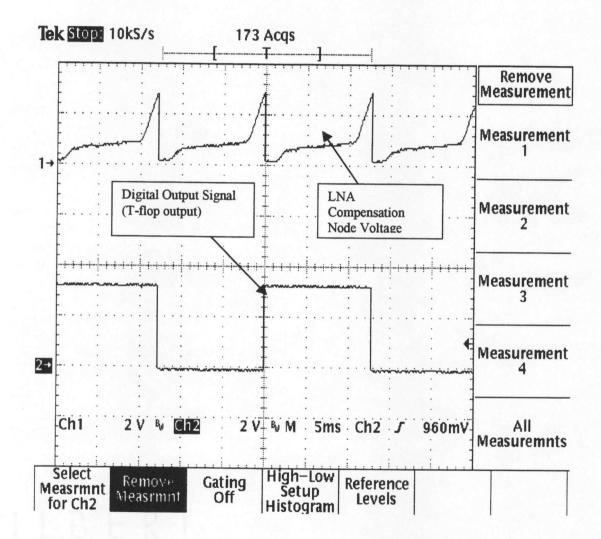

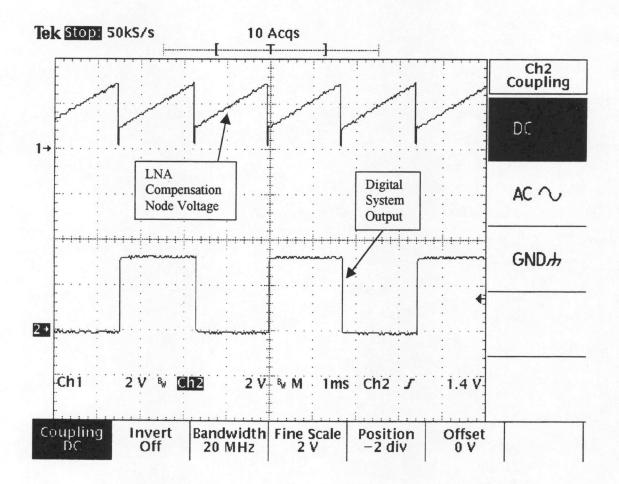

| Figure 45 System Operation with Adjusted Reset Time                | 118 |

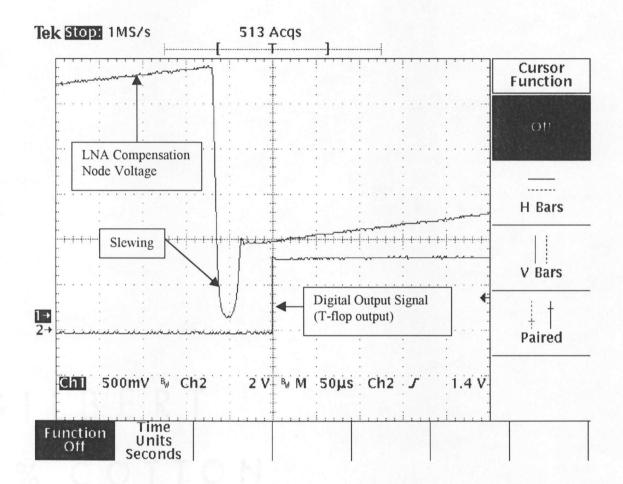

| Figure 46 Integrator Slewing during System Reset                   | 119 |

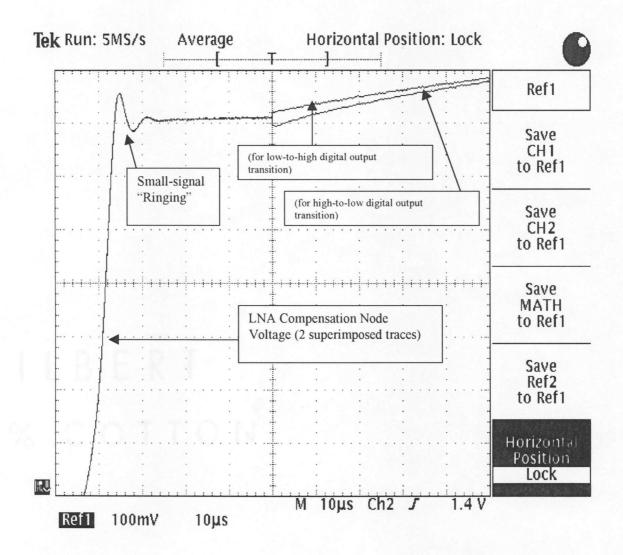

| Figure 47 Integrator Offset at System Reset                        | 120 |

| Figure 48 Integration of Spurious Leakage in the Substrate         | 121 |

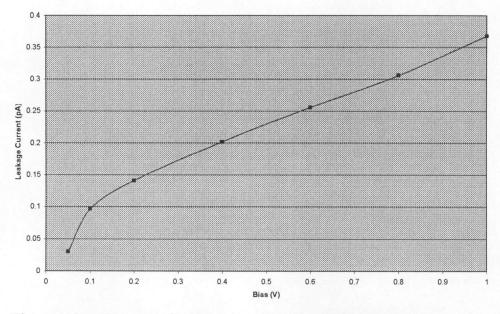

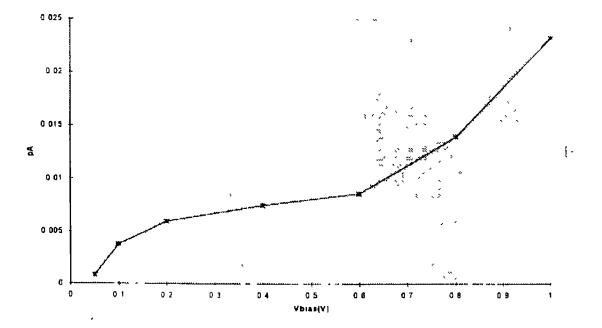

| Figure 49 Detector Leakage vs Reverse Bias                         | 123 |

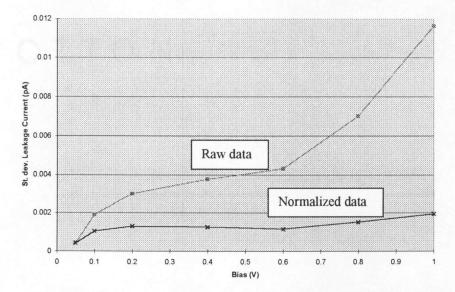

| Figure 50 $\sigma$ and Normalized $\sigma$ Leakage vs Reverse Bias | 123 |

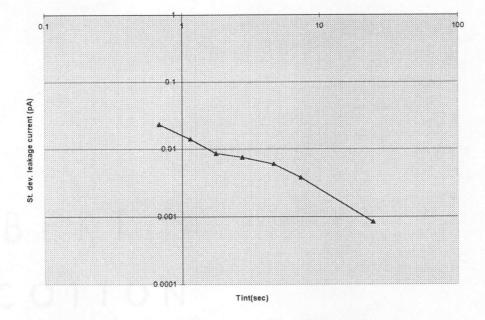

| Figure 51 $\sigma$ Leakage vs Integration Period                   | 125 |

| Figure 52 Minimum Detectable Signal                                | 127 |

| Figure 53 Average Photocurrent vs Detector Bias                    | 128 |

| Figure 54 Quantum Efficiency vs Detector Bias                      | 128 |

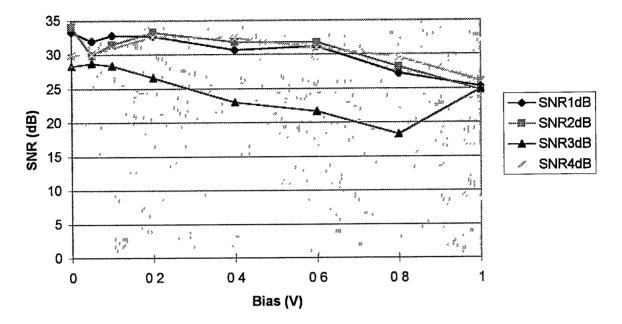

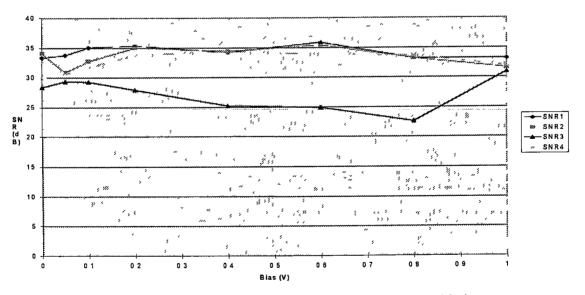

| Figure 55 Signal-to-Noise Ratio                                    | 129 |

| Figure 56 Normalized Signal-to-Noise Ratio                         | 129 |

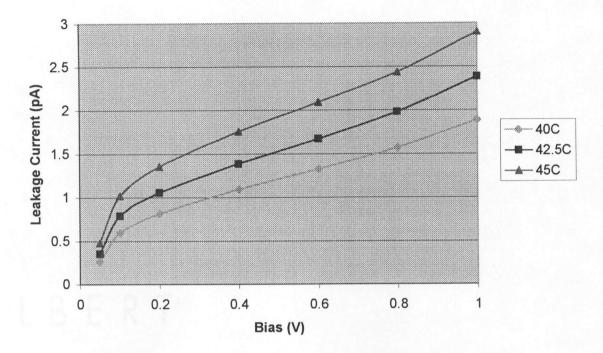

| Figure 57 Detector Leakage vs Temperature and Bias                 | 131 |

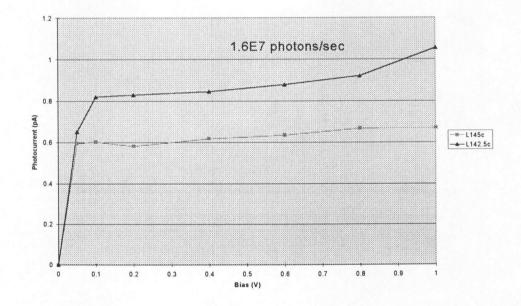

| Figure 58 Photocurrent vs Temperature and Bias                     | 131 |

e

# List of Tables

| Table                                                         | Page |

|---------------------------------------------------------------|------|

| Table 3 1 LNA Noise Simulation Results                        | 108  |

| Table 3 2 LNA Frequency Response/Stability Simulation Results | 111  |

## **Chapter 1**

## Introduction

# **1.1 Distributed Chemical Sensing**

Distribured sensing is a scheme in which a collection of remote sensors is deployed throughout a region to be monitored It allows for parallel testing and quicker access to comprehensive test data than a more centralized measurement [1] Various measurement applications benefit from distributed chemical sensing Among these are environmental monitoring and therapeutic drug discovery Many measurement systems do not lend themselves easily to these types of applications The large detection devices, cabling, and cost involved in some systems often make them impractical for applications in which remote sensing, small volumes, or multiple parallel sensing are involved These applications require an instrumentation solution that is small, inexpensive, and accurate [2]

#### **1.2 Biosensors**

Biosensors are one class of sensors that may be used in distributed systems A biosensor is the combination of a biological sensing component, or bioreporter, with a transducer device The biological element reacts with a targeted substance, and the

transducer then detects this reaction The most common bioreporters make use of enzymes and antibodies, surface plasmon resonance (SPR) sensors being a popular example SPR sensor technology has been shown to be feasible for distributed chemical sensing [1]

#### **1.2.1 Whole-cell Biosensors**

Whole-cell biosensors use intact living cells as the biological component One of the advantages of using a whole-cell biosensor is that not only is analytical information such as the concentration of a substance obtained, but functional information is gained also Functional information describes how a stimulus affects a living system This information is particularly useful for environmental monitoring, drug screening and other applications requiring the measurement of biological outcomes One type of important functional information is bioavailability, or the availability of a substance to living organisms In environmental monitoring, for example, the total bioavailability of a pollutant is a concern Whole-cell biosensors are well suited to environmental sensing, because they can be made small enough for use in the field, are able to survive in the field, and are capable of continuous monitoring [3]

#### **1.2.2 Bioluminescent Bioreporters**

Bioluminescence is the production of light by a living organism Measuring bioluminescence is a convenient means of continuously monitoring cell activity in a whole-cell biosensor Calorimetric means (e g measuring the heat of metabolism) have commonly been used as a signaling mechanism between cells and transducers

2

However, this method suffers from many biological and non-biological sources of heat noise Fortunately, bioluminescent bioreporters can be made to selectively interact with a targeted substance This is done by fusing bioluminescent genes with the genes of the bioreporter cell The end result is a luminescent response that is tightly coupled to a very specific metabolic response Genetically engineered bioluminescent bioreporters have been developed, using both prokaryotic and eukaryotic cells, for use in environmental monitoring applications [2]

# **1.3 The Bioluminescent Bioreporter Integrated Circuit**

A solution to some of the problems of distributed sensing lies in system integration Current integrated circuit (IC) technology allows signal processing, communication, and other functions to be implemented in a single chip, minimizing both size and cost The use of CMOS technology is particularly desirable The benefits of CMOS include low cost and the ability to easily integrate both digital and analog circuits CMOS is also particularly useful in low-power applications The combination of a CMOS IC with a bioluminescent bioreporter provides a powerful integrated sensor technology

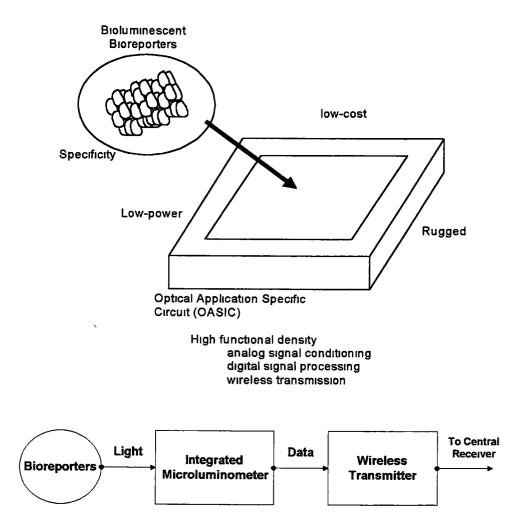

The Bioluminescent Bioreporter Integrated Circuit (BBIC) concept is shown in Figure 1 Here, the bioreporters are placed on a CMOS IC that detects bioluminescence, performs low-noise signal processing, and transmits the sensor data The IC can be divided into two main sections the microluminometer (which includes

Figure 1 - The Bioluminescent Bioreporter Integrated Circuit Concept

integrated photodetection and signal processing), and the transmitter (which performs wireless data transmission) The BBIC is novel in that it integrates the biological element with the rest of the sensor In this situation, the bioreporter can be seen as a component of the integrated circuit, analogous to a resistor or transistor [2]

An advantage of the BBIC concept is the close proximity of the sensing element to the transducer Having the bioreporters affixed to an IC with an integrated microluminometer eliminates the need for external optical devices Many optical biosensors, such as the SPR sensors previously mentioned, require devices to couple the signal from the detector to the rest of the measurement system Fiber-optic cables, lenses, gratings, and waveguides, which are commonly used, are not needed in the BBIC. An integrated wireless transmitter also replaces the cabling often needed for communication with the sensor This method produces a stand-alone sensor that is selective, sensitive, low-power, rugged, and inexpensive

#### **1.3.1 Low-noise Microluminometer**

#### **1.3.1.1 Integrated Photdetection**

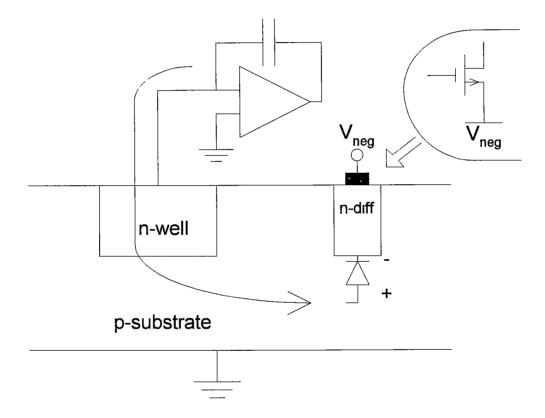

The light produced by the bioreporters must first be converted to an electrical signal Photodetection must be done with maximum quantum efficiency and minimum addition of noise, allowing for the detection of the smallest possible optical signal Measurement of the bioluminescent signal can be integrated easily in bulk CMOS N-well/p-substrate, n-diffusion/p-substrate, and p-diffusion/n-well junctions are available in a standard n-well process for use as photodiodes The performance of such devices

has been demonstrated in a fully integrated CMOS photo-spectrometer [4]

#### 1.3.1.2 Low-noise Signal Processing

The level of photocurrent is proportional to the light output of the bioreporters, which is proportional to the concentration of the targeted substance The signalprocessing section of the microluminometer must digitize the information contained in the level of photocurrent, making it available for data transmission This system should introduce as little measurement error as possible, again allowing for the smallest possible detectable signal, since the bioreporters produce low-level light in response to low concentrations of the targeted substance The system must be optimized for lownoise performance, having as a key component some form of low-noise amplification

#### **1.3.2 BBIC Design Challenges**

The BBIC is an innovative solution to distributed sensing, but it does present certain design challenges not yet mentioned Whole-cell biosensors present the problems of dealing with living organisms The bioreporters must first be kept alive for as long as possible. Proposed methods to increase cell lifetime are the inclusion of a food source on the IC and a freeze-drying technique in which the cells are stored until needed The bioreporters also must be protected from the environment, while allowing contact with the substances to be measured The protective structure must also have the proper optical properties Currently, a sol-gel process is being used, in which the cells are entrapped in a glass matrix Finally, the growth of the cells must be accounted for Cell growth is accompanied by an increase in bioluminescent intensity, which is detected as an increase in the concentration of the targeted substance Similarly, a decrease in cell population is detected as a decrease in concentration Any cell growth that is not the directly correlated to an increase in chemical concentration can be seen as a form of biological noise Genetic engineering methods to regulate bioreporter cell growth are being considered

The IC itself presents certain challenges A coating is needed to protect the IC from the cells and the environment Any protective coating must provide optical shielding and must not be detrimental to the cells Thin-film, amorphous silicon nitride is currently being investigated for this purpose. The fact that the BBIC is a wireless sensor also presents a problem. The BBIC cannot be connected to a power source via any type of cabling, the initial solution being battery power. Therefore, the electronics must be both accurate and power efficient.

#### **1.4 Scope of Thesis**

This thesis will describe the development of a low-noise microluminometer for the BBIC sensor A prototype of the microluminometer has been fabricated in the HP 0 5  $\mu$ m CMOS process available through the MOSIS fabrication service [5] This prototype includes a large-area, integrated photodetector coupled to a low-noise signal processing system

Chapter 2 presents a system-level design analysis of the microluminometer The requirements of the microluminometer are outlined A discussion of the integrated

photodetection is first presented, describing both the physical operation and IC implementation of the photodetector A description of the signal processing system is then given. The basic system topology is presented, and its operation is explained The various system components and their error contributions to the system are each examined A system-level noise analysis is also performed The optimization of the system for low-noise performance is explained in detail Finally, the implementation of the system in CMOS and results of computer simulation are given

Chapter 3 details the development of a low-noise amplifier (LNA) incorporated in the signal processing The design of this amplifier is the focus of the design work in this thesis The optimization of the LNA for low noise contribution is described in great detail Simulation results are presented, as is the implementation of the amplifier in CMOS

Chapter 4 presents the results from testing of the aforementioned microluminometer prototype Results using a laboratory light source are given Chapter 5 gives some conclusions and proposes future improvements that could be implemented

8

## **Chapter 2**

## Microluminometer System Analysis and Design

#### 2.1 Microluminometer System Overview

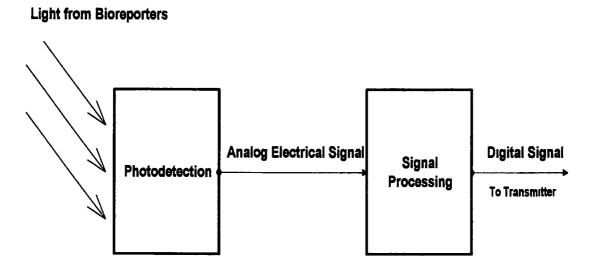

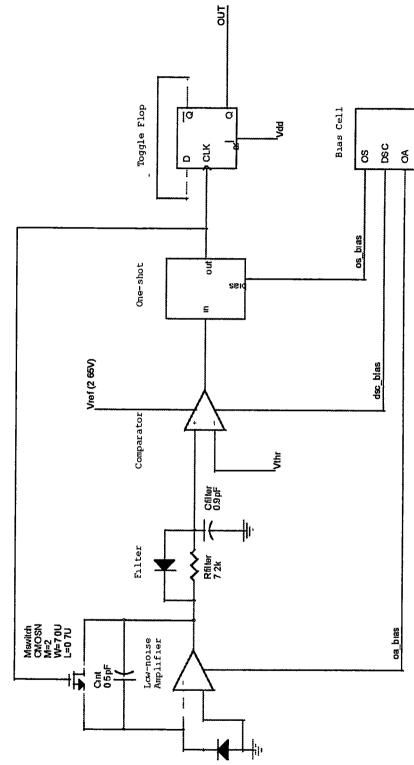

The microluminometer is composed of two main sections photodetection and low-noise signal processing, as shown in Figure 2 The sensor data (chemical concentration) is contained in the intensity of light from the bioreporters The light is converted to an analog electrical signal by a photodetector This signal must then be converted to a form that can be reported by the BBIC The BBIC sensor data is reported through the use of a digital transmitter, therefore the signal processing section of the microluminometer must perform some form of analog-to-digital conversion

The main design goal of the microluminometer is that it be sensitive to the lowest possible level of light, thereby making the BBIC sensitive to the lowest possible concentration of the targeted chemical substance The minimum detectable signal (MDS) is determined by such factors as the quantum efficiency of the photodetector, detector leakage current, and the intrinsic noise of the detector and signal processing electronics It is also necessary that all of the microluminometer functions, including photodetection, be realized in a standard CMOS process Finally, power consumption must be considered, because the BBIC is a wireless sensor

Figure 2 – Basic Microluminometer Operation

#### **2.2 Photodetection**

#### **2.2.1 Photodiode Operation**

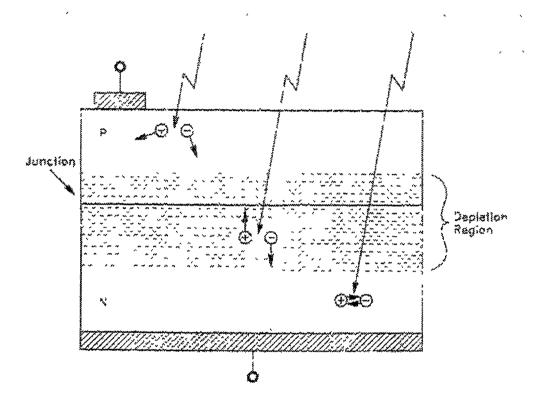

A simple p-n junction diode can be used to convert light into an electrical signal Figure 3 [6] illustrates the mechanism by which this conversion takes place The energy of incident photons is absorbed by the atoms of the semiconductor This energy transfer moves electrons in the valence band to the conduction band, producing electron-hole pairs The carriers then may or may not contribute to a detectable photocurrent Carriers that are optically generated in the depletion region (or diffuse there from the neutral regions) are accelerated toward the diode contacts by the "built-in" electric field produced by the bound ions present there. These carriers almost certainly contribute to the photocurrent. The carriers that recombine before they reach the contacts do not contribute to a current. These are generated mostly in the neutral regions, sufficiently far from the edges of the depletion region. This method of photodetection does not allow for single photon counting, as do photomultiplier tubes.

Quantum efficiency  $(\eta)$  describes the effectiveness of a detector in producing a detectable signal and is given by [7]

$$\eta = \frac{I_p h \cdot v}{P_{op} \cdot A_{det} \cdot q} \cdot 100\% \quad , \tag{21}$$

where  $I_p$  is the photocurrent(A), *h* is Planck's constant(6 626 x 10<sup>-34</sup> Jsec), *v* is the optical frequency(Hz),  $P_{op}$  is the optical power(W/cm<sup>2</sup>),  $A_{det}$  is the detector area(cm<sup>2</sup>),

Figure 3 - Photodiode Operation

and q is the charge of an electron(1 602 x 10<sup>-19</sup> C) Quantum efficiency can be expressed more simply as the transfer function for a photodetector Photons strike a detector at a certain rate and result in the emission of carriers at another rate (photocurrent), giving

$$\eta = \frac{I_p}{q \cdot R_{ph}} \frac{electrons}{photon} \quad , \tag{2.2}$$

where  $R_{ph}$  is the rate at which photons strike the detector (photons/sec) Quantum efficiency is the most important figure of merit for a photodetector, and is expressed as a percentage An ideal detector would have a quantum efficiency of 100 percent, signifying that each photon produces a detectable signal

Real photodiodes have quantum efficiencies that are less than ideal due to the loss of carriers through recombination The likelihood that a free electron or hole will recombine is dependent on several factors, one being the location of its generation in relation to the depletion region As previously discussed, carriers that reach the depletion region (or are generated there) most likely become part of the signal current Carriers generated in the neutral regions are driven primarily by diffusion, because there is only a weak electric field there due to concentration gradients Therefore, carriers released at a distance greater than a diffusion length from the depletion region have a low probability of becoming part of the photocurrent [6] The location of photon absorption in a photodiode is a function of the properties of the semiconductor and the wavelength of the incident light This function can be expressed as [4]

$$F_{abs}(d) = F_0 \cdot [1 - e^{-(\alpha \ d)}]$$

(2.3)

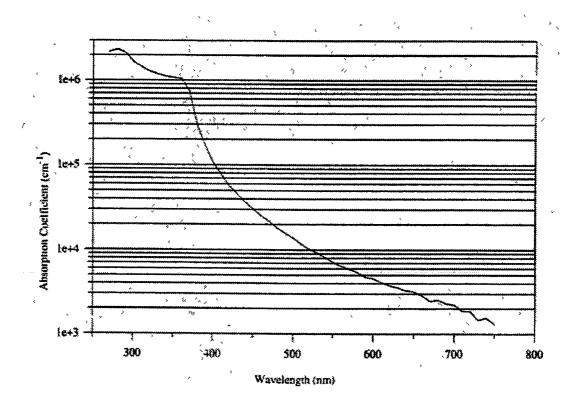

where  $F_{abs}(d)$  is the number of photons absorbed at a distance d from the surface of the semiconductor,  $F_0$  is the number of incident photons, and  $\alpha$  is the absorption coefficient for a particular semiconductor The absorption coefficient is a function of the wavelength of incident light, and is plotted for silicon in Figure 4 [4] The absorption coefficient is inversely proportional to the wavelength of incoming light, indicating that detectors with shallower junction depths are more effective at detecting short wavelengths of light The bioreporters that have been developed for the BBIC produce light at a wavelength near 490 nm [2], suggesting the use of such a detector

The location of the depletion region is dependent on the location of the junction (see Figure 3) This can be controlled, in a limited sense, through the choice of detector type in a given IC process (as explained in section 2 2 4) The width of the depletion region and its arrangement about the junction are determined by bias and doping profile Taking the simple case of an abrupt p-n junction, the depletion region width is given by [8]

$$W_{dep} = \sqrt{\frac{2 \cdot \varepsilon_s}{q} \cdot \left(\frac{N_A + N_D}{N_A \cdot N_D}\right) \cdot \left(V_{b_l} + V_R\right)} \quad , \tag{2.4}$$

where  $\varepsilon_s$  is the permittivity of the semiconductor,  $V_{bi}$  is the "built-in" potential of the junction,  $V_R$  is the applied reverse bias voltage, and  $N_A$  and  $N_D$  are the acceptor and donor concentrations respectively The geometry for this simple case is described by

Figure 4 - Absorption Coefficient for Crystalline Silicon

$$N_A \cdot \mathbf{x}_p = N_D \cdot \mathbf{x}_n \quad , \tag{2.5}$$

where  $x_p$  and  $x_n$  are the distances that the depletion region extends into the p and n sides of the junction respectively Two important characteristics of the depletion region are seen in these equations First, its width increases with an increase in applied reverse bias, improving the charge collection of the detector Second, it extends further into the side of the junction that is more lightly doped Knowledge of the size and location of the depletion region and the absorption characteristics of the semiconductor are important in photodiode design

## 2.2.2 Photodiode Modeling

A model for the photodiode is necessary for system design A simple model for a reverse-biased photodiode is shown in Figure 5

### 2.2.2.1 Photodiode Currents

The current generator,  $I_p + I_L$ , represents the sum of the photocurrent and leakage current These currents flow in the same direction The value of the photocurrent,  $I_p$ , is determined by the intensity of the optical signal and the quantum efficiency of the detector The leakage current, or dark current, of the detector is represented by  $I_L$  To first order, this leakage can be determined from the ideal diode equation [9]

Figure 5 - Simple Photodiode Model

,

$$I_d = I_s \cdot \left( e^{\frac{V_b}{V_i}} - 1 \right) \quad , \tag{2.6}$$

where  $I_d$  is the forward diode current,  $I_S$  is the reverse saturation current of the diode,  $V_D$  is the applied forward bias voltage, and  $V_t$  is the thermal voltage (approximately equal to 26mV at room temperature) For sufficient reverse bias, the leakage current is therefore approximately equal to the saturation current This current is directly proportional to junction area and approximately doubles for every 5 °C increase in temperature [9]

The ideal diode equation adequately predicts the current for low-bandgap semiconductors (GaAs) at low current densities, but only gives qualitative agreement otherwise, due to generation or recombination in the depletion region [8] The current due to generation in the depletion region for reverse bias is given by [8]

$$I_{gen} = \frac{q \cdot A_{det} \cdot n_i \ W_{dep}}{\tau_g}$$

(2.7)

where  $n_i$  is the intrinsic carrier concentration (approximately 1 45 x 10<sup>10</sup> cm<sup>-3</sup> for silicon at room temperature) and  $\tau_g$  is the generation lifetime Generation current may dominate the leakage for reverse bias at room temperature in silicon, due to the relatively low value of  $n_i$  in silicon At higher temperatures, the dark drift current ( $I_S$ ) eventually dominates [8]

Another non-ideal effect occurs at the surface of the semiconductor Here, the

lattice structure of the semiconductor is disrupted, producing "dangling" bonds This creates generation-recombination centers at the surface, leading to increased recombination of carriers and the reduction of signal current The recombination rate is directly proportional to the recombination center density per unit area at the surface, which can be reduced through processing [8]

#### **2.2.2.2 Photodiode Resistance**

The shunt resistance of the photodiode is modeled by  $R_D$  This is the resistance of the zero-biased diode, which is very large  $R_D$  is so large that it can generally be neglected  $R_S$  represents the series resistance of the semiconductor material This resistance is low and again can usually be ignored [6]

#### 2.2.2.3 Photodiode Capacitance

The capacitance of the detector is represented by  $C_D$ . For reverse bias, this capacitance is essentially the junction capacitance and is given for an abrupt junction diode as [10]

$$C_{D} = \sqrt{\frac{q \, \varepsilon_{s}}{2 \, \left(V_{b_{l}} + V_{R}\right)} \cdot \frac{N_{A} \cdot N_{D}}{N_{A} + N_{D}}} \cdot A_{det}$$

(2.8)

This capacitance is directly proportional to area and decreases with increased reverse bias A lowered detector capacitance has several benefits, including decreased noise in charge-sensitive applications (to be discussed in section 2.4)

#### 2.2.2.4 Photodiode Noise

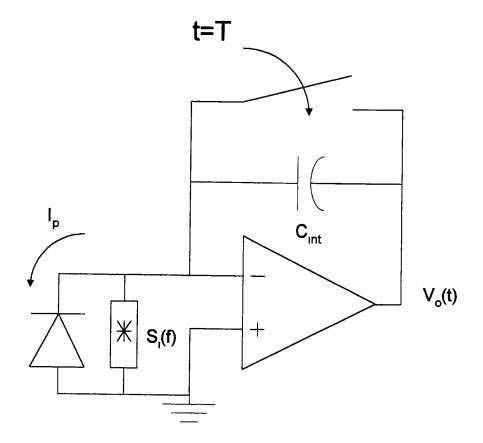

The intrinsic noise spectral density of the photodiode is modeled by the current source  $S_i(f)$  (A<sup>2</sup>/Hz) A major component of diode noise is shot noise, which is the result of carriers crossing a junction Shot noise is broadband noise with a "white" power spectral density (PSD) The diode current is due to both dark current and photocurrent Neglecting the effects of generation in the depletion region, the dark current is equal to  $I_S$  for sufficient reverse bias The one-sided PSD of the shot noise for a reverse-biased photodiode is therefore equal to

$$I_{shot}^{2} = 2 \cdot q \cdot \left(I_{s} + I_{p}\right) \frac{A^{2}}{Hz}$$

(2.9)

For the special case of the zero-biased detector, the forward diffusion current exactly cancels out the reverse drift current This results in zero net diode current, but the noise powers of the two opposing currents add directly [11], giving

$$I_{shot}^{2} = 2 \cdot q \cdot \left(2 \cdot I_{s} + I_{p}\right) \frac{A^{2}}{Hz}$$

(2.10)

The zero-biased diode, therefore, may have higher noise than that of a reverse-biased diode

Another component of photodiode noise, not predicted by the ideal diode equation, is due to the generation/recombination of carriers in the depletion region Generation/recombination noise (g-r noise) often dominates the noise of photodetectors [11]. For reverse-bias and low frequencies, the one-sided power spectrum of g-r noise is given by [12]

$$I_{g-r}^{2} = 2 \cdot q \cdot I_{D} \cdot \frac{e_{p}^{2} + e_{n}^{2}}{\left(e_{p} + e_{n}\right)^{2}} \frac{A^{2}}{Hz} \quad , \qquad (2.11)$$

where  $e_p$  is the emission rate of holes from a center, and  $e_n$  is the emission rate of electrons from a center. This noise has a white power spectrum for frequencies well below a frequency determined by the lifetime of the carriers in the photodetector [13].

Flicker noise in a diode is due to fluctuations in the surface recombination processes [12], and can be simply modeled (one-sided PSD) as

$$I_{fluc\,ker}^{2} = \frac{K \ I_{D}^{a}}{f} \frac{A^{2}}{Hz} \quad , \tag{2.12}$$

where K is a flicker noise coefficient that depends on process and geometry, a is the flicker noise exponent (usually near unity), and f is frequency (Hz). Flicker noise is commonly referred to as "1/f noise", because its power spectrum is inversely proportional to frequency

The total diode noise is the composite of all the noise mechanisms described above. The power spectra of each of these noise sources add directly. A representative frequency spectrum of the total noise in a photodiode is given in Figure 6 [11] At low frequencies, flicker noise dominates At intermediate frequencies, the shot noise and g-r noise combine to give the diode noise a flat (or white) spectrum.

Figure 6 - Composite Photodiode Noise Current Spectrum

The g-r noise eventually decays at higher frequencies, leaving the shot noise as the dominant noise source. Also shown in Figure 6 is the thermal noise due to the series resistance of the diode (shown as  $E_{cell}/R_{cell}$ ). As previously stated, this resistance is usually very small, so its noise can also be neglected in most cases

#### 2.2.3 Detector Biasing

A photodiode should obviously be reverse-biased or zero-biased for low-level light detection. A large value of reverse bias creates a large depletion region in the diode (Equation 2.4). This increases the collection area of the detector, and thereby improves quantum efficiency The increased width of the depletion region also decreases detector capacitance. A major disadvantage of a large reverse bias is increased leakage current, partly due to the fact that a larger depletion region leads to higher g-r current (Equation 2.7) The leakage is minimized at zero bias, but the shot noise is increased (Equation 2.10). Also, detector capacitance is increased, and the quantum efficiency suffers The reduction of leakage current is essential for low-level detection. Lower levels of signal current become increasingly difficult to distinguish from a large leakage current, and the variation of the leakage current with temperature is measured as a change in signal. Therefore, zero bias is the optimum configuration (even at the expense of lower quantum efficiency and higher noise).

#### **2.2.4 Integrated Photodetection in CMOS**

Figure 7 shows three types of photodiodes available in a standard n-well CMOS IC process. These detectors are formed by the junctions between: p-diffusion/n-well, n-well/p-substrate, and n-diffusion/p-substrate The diffusions are

Figure 7 - CMOS-compatible Photodetectors

highly doped and are used to form the sources/drains of transistors The p-diffusion/nwell type (which is actually a combination of two diodes) has a shallow junction, making it a reasonable candidate for detection of the blue-green light (approximately 490 nm) produced by the bioreporters The junction extends mostly into the n-well, because it is much more lightly doped than the diffusion The n-well/p-substrate type of detector has a deeper junction, but can be biased at 0V for low leakage The ndiffusion/p-substrate detector has a shallow junction and can also be biased at 0V Its depletion region extends mostly into the substrate Initially, it would seem that the ndiffusion/p-substrate is best suited for use in the BBIC

### 2.2.4.1 CMOS Photodetector Evaluation

An IC was fabricated in the HP 0.5  $\mu$ m CMOS (n-well) process to evaluate the relative performance of the different types of photodetectors Figure 8 is a photograph of the actual test chip The large center section is an array of photodetectors containing variations of the three basic detector types The array is surrounded by 18 channels of an early signal-processing prototype Each detector is connected to a channel of signal processing, and the output is brought off-chip for evaluation

Testing showed both the p-diffusion/n-well and n-diffusion/p-substrate detector types to have very poor collection efficiency The n-well/p-substrate detector type, however, had a measured quantum efficiency of 66% at 490 nm It also had a low measured leakage current of approximately 70 fA for a 1-V reverse bias and a bottom junction area of 8,600  $\mu$ m<sup>2</sup> The n-well detector type was therefore chosen for use in the BBIC Figure 9 is a photograph of the actual n-well photodetector used in

Figure 8 - CMOS Photodetector Evaluation Test Chip

Figure 9 – N-well Photodetector

the microluminometer prototype The detector is formed by an array of small, parallel, n- well electrodes in the p-substrate This method is intended to reduce detector capacitance and leakage by decreasing the junction area of the total detector, while retaining a large active collection area For this design, the individual electrodes have an area of 5 6  $\mu$ m × 5 6  $\mu$ m and are spaced 12 6  $\mu$ m apart The total detector area is approximately 1 2 mm<sup>2</sup>

Initially, the diffusion-type detectors were expected to have higher quantum efficiencies at 490 nm, due to their shallower junctions A possible reason for their poor performance comes from analysis of the IC processing steps The diffusion areas (and wells) are created through a high-energy ion-implantation process that allows for greater precision and repeatability in processing This process damages the silicon lattice, and thereby creates generation-recombination centers that lead to signal loss (carrier recombination)

After 10n-implantation, an annealing process occurs, in which the silicon wafer is held at a moderate temperature for a period of time (about 1000°C for 15 to 30 minutes), and then allowed to slowly cool This repairs some of the lattice damage done in ion implantation by thermally vibrating the atoms and allowing bonds to reform [10] The amount of lattice repair is dependent on the time and temperature of the annealing process Higher temperature and/or longer annealing time results in greater repair to the lattice This also leads to deeper diffusion of the 10ns into the lattice, both vertically and laterally (lateral diffusion) A great deal of lateral diffusion in the drain/source regions of transistors cannot be tolerated in a process with sub-micron feature lengths The annealing process, and therefore the lattice repair, is limited in the p/n-diffusion regions In the creation of an n-well, however, a broad diffusion profile is intended, so greater restoration of the lattice occurs through a longer annealing This would explain the adequate performance of the n-well detectors and the inferior performance of the diffusion-type detectors

### **2.3 Signal Processing**

### **2.3.1 Signal Processing Requirements**

The signal processing system converts the photocurrent signal to digital form The signal processing must be compatible with the photodiode, allowing for a current input and proper biasing of the detector Low power consumption is also a priority As previously stated the main goal for this system is to be sensitive to the smallest possible signal The minimum detectable signal (MDS) in photons for a photodiode approaches a limit given by [2]

$$MDS = \frac{1}{q \ \eta} \sqrt{\frac{4 \cdot q \cdot A_{det} \cdot I_s}{T_{meas}}} \quad , \tag{2.13}$$

where  $T_{meas}$  is the total integration time of the measurement This equation assumes zero bias and zero dark current It also does not account for the noise of the signal processing electronics Equation 2 13 indicates that a measurement system capable of a long measurement time could be sensitive to very low levels of light

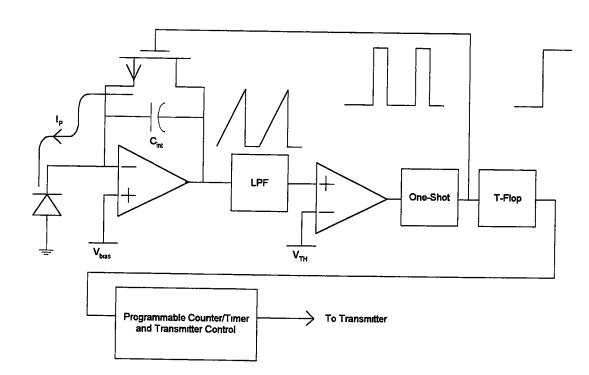

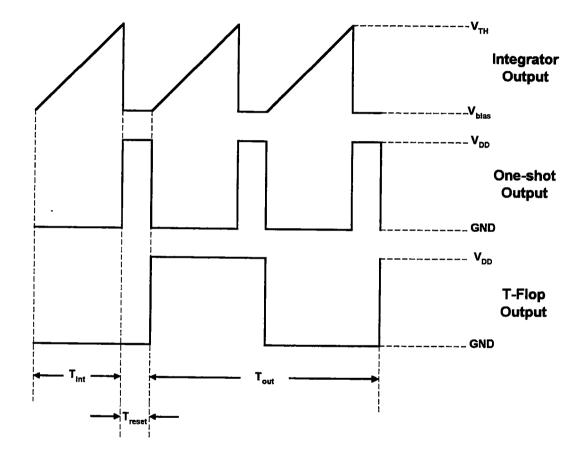

# 2.3.2 Basic System Topology and Operation

A signal processing system that meets these requirements is a current-tofrequency converter (CFC) The use of a CFC with a photodiode results in a light-tofrequency converter (LFC), as shown in Figure 10 Light produces a photocurrent in the detector that is collected (integrated) on the feedback capacitor of the integrator The integrator presents a low impedance to the detector and sets the detector bias As the charge collects on the feedback capacitor, the output voltage of the integrator increases at a rate (S) directly proportional to the photocurrent ( $I_p$ ) and inversely proportional to the value of the integration capacitor ( $C_{int}$ )

$$S = \frac{I_p}{C_{\rm int}} \frac{V}{\sec}$$

(2.14)

The output voltage continues to increase at this rate until it reaches a value equal to the threshold voltage ( $V_{TH}$ ) of the comparator When this happens, the output of the comparator goes from "low" to "high" The transition produces a pulse at the output of a monostable multivibrator ("one-shot") that resets the output of the integrator to the baseline level ( $V_{bias}$ ) This series of operations continues indefinitely, producing digital pulses at a frequency dependent on the level of photocurrent

Figure 11 shows the waveforms at several points in the system The time required for the integrator output to ramp from the baseline  $(V_{bias})$  to the threshold  $(V_{TH})$  is equal to

Figure 10 - L1ght-to-Frequency Converter

-

,

Figure 11 - System Timing

$$T_{\rm int} = \frac{C_{\rm int} \cdot (V_{TH} - V_{bias})}{I_p} = \frac{V_{TH} - V_{bias}}{S}$$

(2.15)

The pulse width of the one-shot output 1s equal to the reset time  $(T_{reset})$  The period of the one-shot output  $(T_{os})$  is equal to the sum of these two times

$$T_{os} = T_{\rm int} + T_{reset} \tag{2.16}$$

The output of the one-shot drives a D flip-flop connected as a toggle flop (Tflop) The output of the T-flop changes states only when a high-to-low transition occurs at its input The T-flop performs a frequency divide-by-two function and corrects the duty cycle to 50% for a constant photocurrent The period of the output waveform ( $T_{out}$ ) is therefore twice that given by Equations 2 15 and 2 16, and its frequency is

$$f_{out} = \frac{1}{T_{out}} = \frac{1}{2 \cdot (T_{int} + T_{reset})} = \frac{1}{2 \cdot \left[\frac{V_{TH} - V_{bias}}{S} + T_{reset}\right]}$$

(2.17)

For the normal case in which the integration time is much longer than the reset time, Equation 2 17 reduces to

$$f_{out} = \frac{I_p}{2 \cdot C_{\rm int} \cdot \Delta V} \quad , \tag{2.18}$$

where

$$\Delta V = V_{TH} - V_{bras} \tag{2 19}$$

The output pulses are at digital logic levels and contain the sensor information via their frequency The pulses are counted by a digital counter for a set (programmable) measurement time If N pulses are counted in a measurement time  $(T_{meas})$  then an average photocurrent level can be calculated as

$$\bar{I}_{p} = \frac{2 \cdot N \cdot C_{\text{int}} \cdot \Delta V}{T_{\text{meas}}}$$

(2.20)

The average photocurrent can then be related to an average concentration of the targeted chemical substance The pulse count at the end of the measurement interval is available in digital form at the output of the counter Digital circuitry serializes this data and sends it to the on-chip transmitter The counter is then reset for the next measurement

This signal-processing scheme performs a long-time, integrated measurement that is practically limited by such factors as the size (number of bits) of the digital counter and the lifetime of the bioreporters An averaged measurement such as this has the benefit of improved accuracy through the "averaging out" of noise An added benefit is lowered power consumption in the IC, due to the fact that it is not necessary for the transmitter to run continuously Data is only available for transmission at the end of each measurement interval During the measurement, the transmitter can be in a low-power, or "sleep", mode Control of the transmitter mode can be achieved with additional digital circuitry This power reduction is extremely important, since the transmitter consumes an enormous amount of power, relative to the rest of the IC, when it is active

# 2.3.3 Signal Processing Components

The performance of the signal processing system is dependent on the performance of the individual components Measurement errors can be directly traced to non-ideal effects in these components Effects such as leakage, offset, and noise limit the sensitivity of the system to low-level signals The operation of the major system components is discussed in this section, as are their contributions to the measurement error of the system

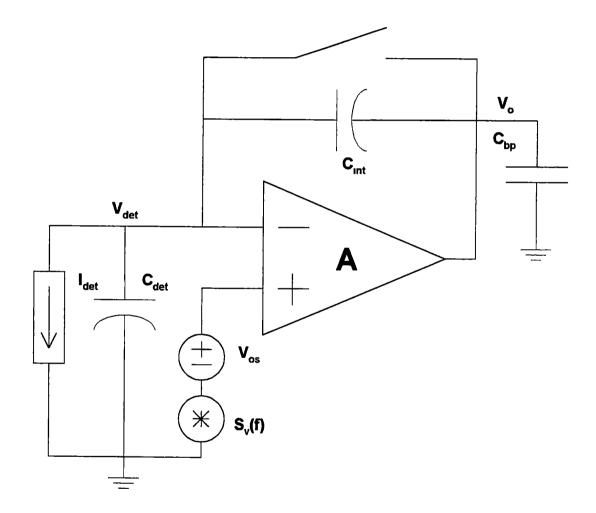

#### 2.3.3.1 Integrator

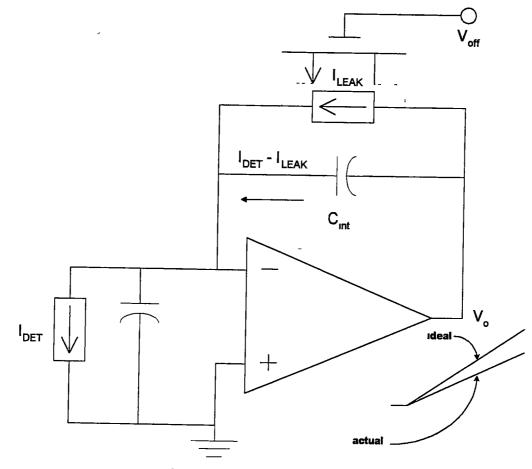

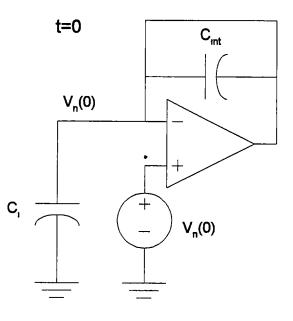

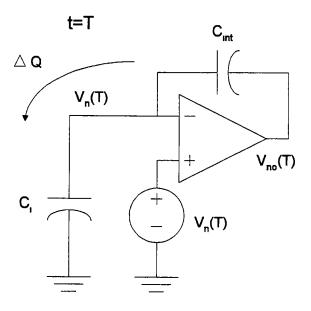

The integrator provides the interface between the photodiode and signal processing system The feedback of the integrator sets the bias on the photodetector and presents a low input impedance A voltage ramp waveform (Figure 11) is produced in response to input photocurrent according to the relationship in Equation 2 14 The integrator is the first stage of the processing electronics and can easily become a dominant source of error in the system Care must therefore be taken to recognize the sources of integrator error and minimize them Figure 12 shows the integrator modeled with some of its error sources and the detector bias set for 0V The reset switch is treated as a separate component and is discussed in section 2 3 3 2

Figure 12 - Integrator with Error Sources

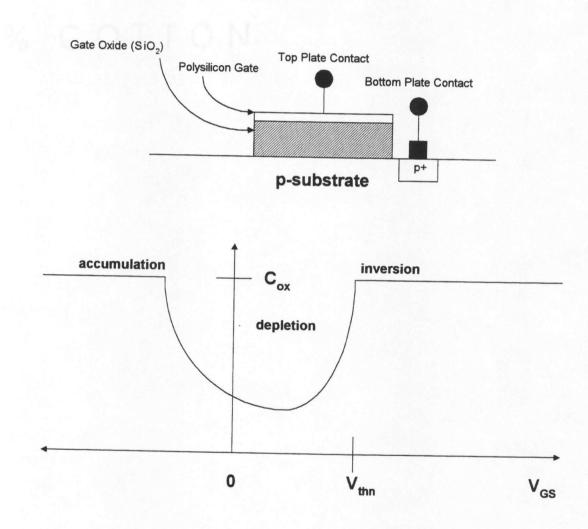

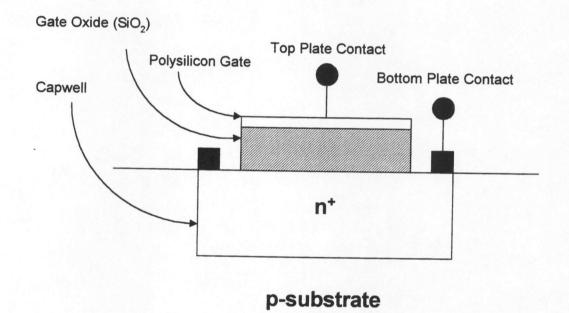

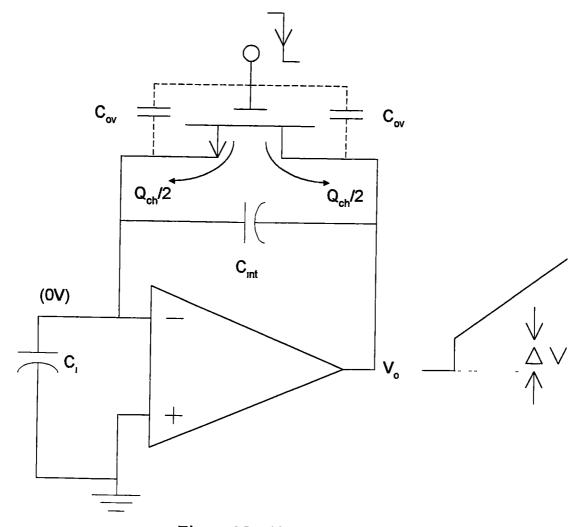

### 2.3.3.1.1 Integration Capacitor

The integrator error is mostly due to non-ideal effects in the amplifier, but the integration capacitor ( $C_{unt}$ ) must also be considered A common problem with integrated capacitors is linearity The simple MOS capacitor, for example, has a value that is highly voltage-dependent, as shown in Figure 13 for low frequencies The variation of capacitance with voltage is due to the fact that the bottom "plate" of the MOS capacitor(in the substrate) can be in one of three modes of operation depending on the applied gate voltage accumulation, depletion, or inversion In depletion mode, the depletion region that forms adds to the separation between the capacitor plates, decreasing the capacitance [14]

The IC capacitor structure shown in Figure 14 has improved linearity over that of the simple MOS capacitor The bottom plate of the capacitor is a highly doped area or "capwell" This technique helps to prevent the voltage coefficient problem in the simple MOS structure [15] This linearized capacitor structure is available in the HP 0 5  $\mu$ m CMOS process [5] and is used to form the integration capacitor The improved structure has better linearity, but there is still the problem of a parasitic, back-plate capacitance that exists between the well and substrate (C<sub>bp</sub>) Back-plate capacitance can have a value of up to 20 percent of the nominal capacitor value [10] Therefore, the feedback capacitor of the integrator is oriented with the back plate connected to the amplifier output, as shown in Figure 12 If this capacitance appeared at the input, it would contribute to the same problems that the detector capacitance causes (increased noise, etc.)

Figure 13 - Simple MOS IC Capacitor

## 2.3.3.1.2 Gain Error

One error that may result from a large input capacitance, other than increased noise, can be described as a gain error The input capacitance  $(C_i)$  is approximately equal to the sum of the detector capacitance and input capacitance of the amplifier Ideally, the integrator holds the voltage across the input capacitance equal to the voltage at its noninverting input (0V in this case) An amplifier with a finite gain (A) actually requires the detector voltage to increase as the integrator output voltage increases

$$V_{\rm det} = \frac{V_o}{A} \tag{2.21}$$

The change in voltage across the input causes the flow of a charging current onto the input capacitance This means that some of the detector photocurrent actually flows onto the input capacitance instead of the integration capacitor The output no longer increases at a rate given by Equation 2 14, but at a lower rate equal to

$$S_{eff} = \frac{I_p}{C_{eff}} \quad , \tag{2.22}$$

where

$$C_{\text{eff}} = \frac{C_i + C_{\text{int}} \cdot (A+1)}{A}$$

(2.23)

The resulting error in the integrator output pulse period is given by

% error =

$$\left[1 - \frac{C_{\text{int}} A}{C_{\text{int}} \cdot (A+1) + C_i}\right] \times 100\%$$

(2.24)

This error becomes negligible as the product of the amplifier gain and integration capacitance becomes much larger than the input capacitance A large gain is required if the input capacitance is much larger than the integration capacitor, which is likely the case

The gain should also remain constant A change in gain, especially for low values of gain, will result in a change in the measured signal As the gain decreases, the slope of the integrator output decreases as given by Equations 2 22 and 2 23 The gain can change significantly due to the nonlinearity of the amplifier A drastic decrease in gain occurs if the integrator output exceeds the amplifier's dynamic range, presenting the challenge of designing a single-supply amplifier with an output dynamic range that includes 0V (described in Chapter 3) The gain can also change as a result of temperature change The temperature dependence of the amplifier gain is an important consideration for the BBIC, because it will be used as an environmental sensor This effect can, again, be made negligible if the amplifier is designed for high gain

### 2.3.3.1.3 Reset Error

Integrator errors can occur due to improper reset Ideally, the amplifier output is reset to the baseline (0V) before the reset switch opens The ramp waveform at the output then begins its rise from the baseline to the threshold During the time that the reset switch is closed, the amplifier is connected in a unity-gain configuration This leads to the obvious requirement that the amplifier be unity-gain stable If the amplifier is unstable during reset, it will oscillate (or possibly saturate) If the amplifier is stable but has a poor phase margin, its transient response will exhibit excessive "ringing" when the switch closes, and integrator output may not settle before the switch opens The amplifier must, therefore, be adequately compensated to allow for a full reset

In order to analyze the stability of this system the open-loop transfer function must be known The loop transmission of the integrator during reset is approximately given by

$$T(s) = \frac{H_a(s) \cdot (1 + s \cdot R_{on} \cdot C_f)}{1 + s \cdot R_{on} \cdot (C_i + C_f)} \quad , \qquad (2.25)$$

where  $H_a(s)$  is the open-loop transfer function of the amplifier and  $R_{on}$  is the onresistance of the reset switch The amplifier transfer function is affected by loading and will be explained in more detail in chapter 3 The feedback network introduces both a pole and a zero to the loop transmission

$$f_{p} = \frac{1}{2 \cdot \pi \ R_{on} \cdot (C_{i} + C_{f})} Hz$$

(2.26)

and

$$f_z = \frac{1}{2 \cdot \pi \cdot R_{on} \cdot C_f} Hz \tag{2.27}$$

The pole and zero nearly cancel each other out for relatively low values of input capacitance  $(C_i)$  However, for a large input capacitance, the pole occurs at a frequency much lower than the zero frequency, producing significant phase shift. This situation presents a stability against oscillations problem, since the system will oscillate if the phase shift around the loop reaches 180 degrees at a frequency where the magnitude of the transfer function is greater than one [9] Luckily, the value of  $R_{on}$  should be relatively small, and both the pole and zero should occur at relatively high frequencies. If the bandwidth of the amplifier can be held much lower than these frequencies, their effect will be negligible. The stability analysis will be carried out further in Chapter 3

A large-signal, transient effect can also occur during reset Just before the reset switch closes, the output of the integrator is at the threshold voltage  $(V_{TH})$  Just after the switch closes, the output voltage is applied to the input capacitance through the on-resistance of the switch This fast voltage change on a large capacitance can result in the flow of a large charging current from the amplifier output If the charging current required is more than that available at the amplifier's output, the amplifier is pulled out of linear operation toward the lower supply rail Feedback then slowly pulls the system back to linear operation, and the output settles to its final value This 'slewing'' effect can take a great deal more time than any ringing in the small-signal,

43

linear response If the reset switch opens during this time, integration will begin while the amplifier is in a low-gain state (gain error) The output voltage will then ramp upward until linear operation is restored Both this effect and small-signal ringing increase the required reset time, limiting the maximum frequency of the system operation and the upper limit of the sensor's dynamic range

# 2.3.3.1.4 Amplifier Offset Voltage

The offset voltage of the amplifier is modeled as the voltage  $V_{os}$  in Figure 12 The offset voltage is the differential voltage that must be applied to the amplifier's input to bring the output to zero [16] The polarity of the offset, though shown in Figure 12, is not known for from one amplifier to the next Offset voltage has two components random offset and systematic offset Random offset is due to random mismatches in devices, which can be reduced through proper layout Systematic offset is an offset inherent in the amplifier design This type of error is removed through careful design [10]

1

The offset voltage presents an error, because there is an unintentional bias on the detector It is intended to put a zero bias on the detector in the BBIC for low leakage, so this error must be considered The offset voltage also results in a shift in the baseline of the integrator output, which leads to a measurement error in the average photocurrent (Equations 2 19, 2 20) If this error remains constant, it can be calibrated out of the measurement However, the offset voltage changes, or "drifts", with temperature, resulting in an error similar to that produced by low-frequency

44

noise. Offset cancellation techniques, such as autozeroing, have been used effectively [17], but are limited by errors from the switching involved

### 2.3.3.1.5 Amplifier Noise

The intrinsic noise of the amplifier is modeled as  $S_{\nu}(f)$  in Figure 12 This voltage source is an equivalent, input-referred noise voltage spectrum An input current noise current due to gate leakage can also be modeled, but it is usually negligible in CMOS [10] at low frequencies The noise spectral density of the amplifier has two main components white thermal noise with a flat spectrum and flicker noise with a spectrum that varies inversely with frequency The composite spectrum can be represented as

$$S_{\nu}(f) = E_{th}^2 \cdot (1 + \frac{f_c}{f}) \frac{V^2}{Hz} \quad , \qquad (2\ 28)$$

where  $E_{th}^{2}$  is the thermal noise power, and  $f_{c}$  is the flicker noise corner frequency The corner frequency is the frequency at which the white noise power spectral density is equal to that of the flicker noise power

The intrinsic noise of the amplifier and detector cause random voltage variations at the output of the integrator, resulting in random variations in the output pulse period A large input capacitance, as previously mentioned, amplifies this problem The averaging involved in this system, however, reduces the error The time-variant nature of this system leads to a complicated noise analysis This analysis is reserved for Section 2.4

#### 2.3.3.2 Reset Switch

The switch 1s implemented with a single NMOS transistor, as shown in Figure 15 The gate voltage controls the operation of the switch When the gate voltage is high, the gate-source voltage is above the threshold voltage of the device, and the transistor is in the deep ohmic region The on-resistance of the switch 1s given by [10]

$$R_{on} = \frac{1}{\mu_n \cdot C_{ox} \cdot \left(\frac{W}{L}\right) \cdot \left(V_{GS} - V_T\right)} \quad , \tag{2.29}$$

where W and L are the effective gate width and length respectively,  $C_{ox}$  is the gate oxide capacitance per unit area,  $V_{GS}$  is the gate-source voltage, and  $V_T$  is the threshold voltage of the device The switch provides a discharge path for the integration capacitor, resetting the integrator output When the gate voltage is low, the transistor is in the deep subthreshold region, and the switch is effectively turned off Two important errors that occur in the simple MOS switch are charge injection and leakage

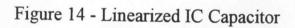

# 2.3.3.2.1 Charge Injection

Charge injection error is an offset that occurs when a MOS switch is opened Charge injection actually occurs in two phases During the first phase, the gate voltage is above the threshold voltage, and a channel charge exists When the switch is on, there is no voltage between the drain and source, and the channel charge is equal to [10]

Figure 15 - Charge Injection Error

$$\left|Q_{CH}\right| = W \cdot L \cdot C_{ox} \cdot \left(V_{GS} - V_{T}\right)$$

(2.30)

This charge is negative for an NMOS switch As the switch is being turned off, the gate voltage falls, and the channel charge exits the device If the transistor is switched quickly, this charge splits evenly between both drain/source terminals [18] as shown in Figure 15. The charge that flows to the output of the amplifier has little effect, but the charge that flows to the input is collected on the integration capacitor, producing an offset voltage at the output equal to

$$\Delta V_{o_1} = \frac{\left| Q_{CH} \right|}{2 \cdot C_{\text{int}}} \tag{2.31}$$

The expelling of channel charge is usually the dominant charge injection effect

When the gate voltage falls below the threshold voltage, the channel charge has been expelled, but an error still occurs through the gate-diffusion overlap capacitance  $(C_{ov})$  of the transistor shown in Figure 15 The falling gate voltage is coupled to the integrator through this capacitance, producing an additional offset If feedback holds the integrator input at baseline voltage, this offset is equal to

$$\Delta V_{o_2} = \frac{C_{ov} \cdot \Delta V_{sw}}{C_{int}} , \qquad (2.32)$$

where  $\Delta V_{sw}$  is the voltage difference between the maximum and minimum values of the switching voltage at the gate The two offsets add to produce the offset voltage error shown in Figure 15

Several techniques can be used to reduce charge injection error Equations 2 30 and 2 31 show that the offset can be reduced by using a small-area switch transistor, switching the transistor with a low-amplitude control signal, and using a large integration capacitor An additional technique involves the switching speed. If the gate of the transistor is switched at a slower rate, the channel charge will not exit equally through the two ends of the switch [18]. This property can be used to reduce the charge that flows onto the integration capacitor. Other common techniques are the use of a "dummy transistor", as described in [19], or a complementary CMOS switch that provides partial charge cancellation More drastic measures, such as active charge-injection compensation [20], are even possible Fortunately, the offset due to charge injection should remain signal-independent in this case, because the source voltage of the switch transistor is held constant through feedback. This offset can be calibrated out of the measurement if it remains constant

## 2.3.3.2.2 Switch Leakage

Switch leakage is the current that flows in the switch when turned off As shown in Figure 16, the switch leakage current subtracts from the detector current This presents a serious problem when trying to detect low levels of photocurrent The switch leakage is a combination of subthreshold current, surface leakage current, and even package leakage current [19] Subthreshold current will be the primary focus A MOS switch in the off condition can be modeled as being in the deep subthreshold region of operation The drain current of a MOS transistor in weak inversion

Figure 16 - Switch Leakage Error

(subthreshold) is given by [21]

$$I_{D} = I_{D0} \cdot \frac{W}{L} \cdot e^{\frac{V_{GS} - V_{T}}{nV_{t}}} \cdot \left(1 - e^{\frac{-V_{DS}}{V_{t}}}\right) , \qquad (2.33)$$

where  $I_{D0}$  is a process-dependent (and temperature-dependent) coefficient, and n is given by [21]

$$n = \frac{C_{ox} + C_{depl}}{C_{ox}} \approx 15 \quad , \tag{2.34}$$

where  $C_{depl}$  is the depletion capacitance For a drain-source voltage above a few thermal voltages (about 75mV at room temperature), Equation 2 32 reduces to

$$I_D \approx I_{D0} \cdot \frac{W}{L} \cdot e^{\frac{V_{GS} - V_T}{nV_t}}$$

(2.35)

The subthreshold drain current of (2 35) seems to have no dependence on drain-source voltage For short-channel devices, this is far from true In short-channel devices, the drain bias interacts with the gate bias by lowering the barrier potential between the source and body regions [21] This effect, known as Drain Induced Barrier Lowering (DIBL), lowers the threshold voltage of the device as the drainsource voltage increases The decrease in threshold voltage results in an increase in drain current (switch leakage) It can be shown [21] that the DIBL contribution to the output impedance is exponentially related to the drain voltage The DIBL effect becomes more pronounced as the effective gate length decreases [22]

Switch leakage is affected by several factors Increasing temperature increases the leakage current The leakage, as reported in [19], doubles for every 8°C increase in temperature This increase is partly due to the diffusion-to-body leakage, which approximately doubles for every 5°C increase Switch leakage also increases with the drain-source voltage of the transistor, due the DIBL effect From (2 33) the subthreshold current becomes zero for zero drain-source voltage In this application, however, the drain voltage of the NMOS switch increases as the detector current is integrated Increasing the gate length of the switch device can reduce the effects of subthreshold current This solution, however, is in opposition to the considerations for low charge injection

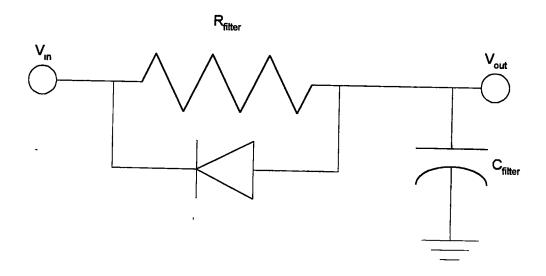

## 2.3.3.3 Low-pass Filter

The output of the integrator passes through a low-pass filter before it reaches the comparator The purpose of the filter is to remove some of the noise due to the integrator and detector at higher frequencies The simple R-C low-pass filter is shown in Figure 17 The diode is present to provide a fast discharge path for the capacitor during reset This filter produces a single-pole response given by

$$H_{filter}(s) = \frac{1}{1 + s \cdot R_{filter} \cdot C_{filter}}$$

(2.36)

The bandwidth of the filter should be low to filter out as much noise as possible (but not low enough to distort the integrator output)

Figure 17 - Low-pass Filter

-

### 2.3.3.4 Comparator

The comparator can be simply described as a high-gain amplifier that intentionally saturates, thereby detecting whether one of its input voltages is higher or lower than the other The comparator in this system produces a high output voltage when the integrator output reaches the threshold voltage As previously discussed, this transition causes the system to reset Two main sources of error in the comparator are intrinsic noise and offset These errors can be modeled as they were for the amplifier in the integrator (Figure 12) The offset voltage for a comparator is simply the input differential voltage, ideally zero, at which an output transition occurs Both the offset voltage and noise of the comparator affect the system tuning The comparator ideally causes the reset to occur exactly when the integrator output reaches the threshold Noise causes random fluctuations in the reset transition time The offset voltage causes a timing offset that can drift with temperature as the offset voltage drifts The timing errors are imposed on the integration time  $T_{int}$  in Figure 11, resulting in error in the measurement

### 2.3.3.5 One-shot

The one-shot produces the pulse that resets the system The width of the pulse is controllable by some design parameter In the case of the one-shot used in this system, the pulse width is adjustable by the bias current, more current producing a longer pulse width The reset time should be negligible when compared with the integration time, so the performance requirements of the one-shot should not be as stringent as those for the other system components

## 2.3.3.6 Toggle Flop

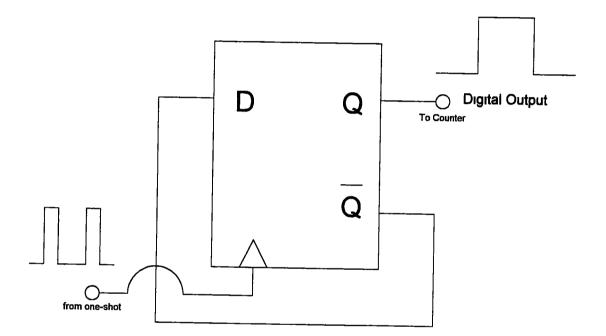

The toggle flop performs a frequency division of the one-shot output signal, as previously discussed The toggle is a simple D flip-flop connected as shown in Figure 18 The logic level present at the D input is clocked to the Q output when a high-tolow transition (from the one-shot) occurs at the CLK input The level at the "Q-bar" output, which is fed back to the D input, becomes the opposite logic of the D input The result is that the Q output only changes states on the falling edge of the one-shot output This produces a signal at one half of the frequency and with a 50% duty cycle The toggle-flop output produces the pulses that are counted by the digital counter

# 2.3.3.7 Counter and Other Digital Circuitry