### Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Jan 2023

## Application of TVS Models for SEED Simulation of a Variety of **TVS Devices**

Li Shen

Yang Xu

Steffen Holland

Sergej Bub

et. al. For a complete list of authors, see https://scholarsmine.mst.edu/ele\_comeng\_facwork/5139

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

L. Shen et al., "Application of TVS Models for SEED Simulation of a Variety of TVS Devices," 2023 Joint Asia-Pacific International Symposium on Electromagnetic Compatibility and International Conference on ElectroMagnetic Interference and Compatibility, APEMC/INCEMIC 2023, Institute of Electrical and Electronics Engineers, Jan 2023.

The definitive version is available at https://doi.org/10.1109/APEMC57782.2023.10217579

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Application of TVS Models for SEED Simulation of a Variety of TVS Devices

Li Shen Missouri S&T EMC Laboratory Missouri University of Science and Technology Missouri University of Science and Technology Rolla, USA lsy69@mst.edu

sergej.bub@nexperia.com

Sergej Bub Nexperia GmbH Germany

Yang Xu Missouri S&T EMC Laboratory Rolla, USA xyang1@mst.edu

> David Pommerenke SAL-Graz EMC lab Graz University of Technology Graz, Austria david.pommerenke@tugraz.at

Steffen Holland Nexperia GmbH Germany steffen.holland@nexperia.com

Daryl Beetner Missouri S&T EMC Laboratory Missouri University of Science and Technology Rolla, USA daryl@mst.edu

Abstract— Accurate models of transient voltage suppression (TVS) devices are important for determining the suitability of electrostatic discharge (ESD) protection strategies early in the design process. An improved TVS model is used in the following paper to represent a variety of TVS devices, including a snapback device, non-snapback device, and a varistor. The models include recent improvements to represent conductivity modulation and the overall shape of the TVS device's transient response. The models are tuned based on characterizations of these protection devices using a transmission line pulse (TLP), and are then used in a system efficient ESD design (SEED) simulation to predict the transient voltages and currents in a system consisting of an offchip TVS, an IC with on-chip ESD protection, and a PCB trace in between. Simulated transient voltage and current waveforms closely match measurements both when testing the TVS devices by themselves and in SEED simulations. Peak and quasistatic currents through the TVS and on-chip diode were typically captured within about 10% or less across the devices tested while varying both the rise time and level of the injected TLP.

Keywords—electrostatic discharge, simulation, system-level modeling, transient voltage suppression

#### I. INTRODUCTION

Transient voltage suppression (TVS) devices are often placed on board to protect Integrated Circuits (ICs) from electrostatic discharge (ESD). The off-chip protection must be designed to ensure the off-chip protection device turns on and shunts the ESD current away from ESD protection on-chip, so the on-chip protection does not take the full event and fail. System-Efficient ESD Design (SEED) provides a methodology to predict the interaction between the off-chip protection, passive components, and the internal protection within the IC, so that ESD issues can be identified early and protection strategies can be optimized. SEED simulations require highly accurate transient device models [1].

Several simulation models for TVS devices have previously been proposed. The models in [2] and [3] are easy to implement, but only account for the steady-state IV curve of the device, and not its transient characteristics. The authors in [4] and [5] proposed an improved model, but its ability to accurately

determine voltage overshoot is limited. Conductivity modulation of the protection was accounted for in [6]. A SPICE behavioral model for TVS devices was developed in [7] and later improved in [8]-[10] to fully describe the transient characteristics of the device, like conductivity modulation.

The following paper demonstrates that the improved model in [8]-[10] can be used to accurately represent a variety of common ESD protection devices: a non-snapback TVS, a snapback TVS, and a varistor. The model is validated in a SEED simulation of a test board including an off-chip TVS and on-chip protection to demonstrate the performance of the model in the much more challenging simulation conditions seen in-system.

Section II describes the ESD protection device model. Section III presents the experimental characterization and modeling of the ESD protection devices. SEED simulations are shown in Section IV. Section V discusses possible simulation convergence problems and their solution. Conclusions are presented in Section VI.

#### II. TVS DEVICE MODEL

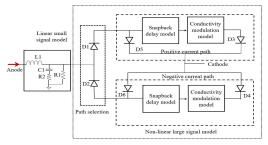

Fig. 1 shows a block diagram of the SPICE behavioral TVS model developed in [7]-[10]. D1 and D2 are ideal diodes which determine if a positive or negative current path is activated. The nonlinear large-signal model contains a pre-snapback model (D5 and D6), TVS turn-on behavioral model (including snapback delay, and conductivity modulation), and a quasi-static I-V model to represent the characteristics after snapback (D3 and D4). The pre-snapback diodes allow for current flow before the voltage reaches  $V_{t1}$ , the snapback trigger voltage.

Fig. 1. Block diagram of the SPICE behavioral TVS model.

This work was supported in part by the National Science Foundation (NSF) under Grant IIP-1916535.

The conductivity modulation sub-model is used to describe the change in conductivity during the first moments of the event. Fig. 2 shows the original structure of the conductivity modulation sub-model prior to modification. Roff is tuned to mimic conductivity modulation after the snapback switch has been thrown. The on resistance, Ron, is small to allow diodes D3 and D4 (Fig. 1) to dominate device behavior. The current-controlled current-source (CCCS - Fig. 2) charges the capacitor C2. The voltage across C2 determines when the conductivity modulation switch will switch from Roff to Ron. When the switch is thrown is determined by the amount of charge passing through the TVS device as set by the gain of the CCCS, the size of the capacitor, and the switch trigger voltage Von [8].

Fig. 2. Sub-model for conductivity modulation.

Equation (1) shows the relationship dictating the turn on and off behavior of the switch before improvement:

$$\begin{split} R_{Switch} &= exp \left\{ ln \left( \sqrt{R_{on}R_{off}} \right) + 3 \, ln \left( \frac{R_{on}}{R_{off}} \right) \cdot \frac{v_{control} - \frac{v_{on} + v_{off}}{2}}{2(v_{on} - v_{off})} - \right. \\ &\left. 2 \, ln \left( \frac{R_{on}}{R_{off}} \right) \cdot \left( \frac{v_{control} - \frac{v_{on} + v_{off}}{2}}{V_{on} - v_{off}} \right)^{3} \right\} \quad (1) \end{split}$$

This switch follows a numerical function which is not based on physics, and thus may not fully represent device behavior. The improved model for conductivity modulation directly changes the conductivity according to the delivered charge as [6],[10]:

$$R_{modulated(t)} = \frac{R_{off}}{1 + \frac{Q_{charge(t)}}{Q_0}}$$

(2)

where  $R_{off}$  is the resistance when current first starts to flow,  $Q_{charge(t)}$  represent the total injected charge, and  $Q_0$  the threshold charge needed to establish conduction.

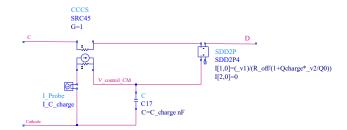

The modified model for conductivity modulation is shown in Fig. 3. The time-dependent resistance  $R_{modulated}(t)$  is controlled by the voltage across capacitor C17. C17 is charged by a current-controlled current-source so that the voltage is directly proportional to the charge injected into the system.

Fig. 3. Improved conductivity modulation model.

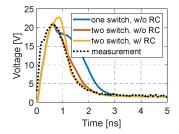

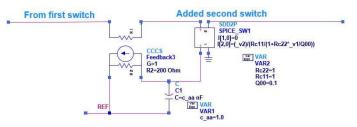

A single switch to represent snapback is only roughly able to predict the transient behavior of the device as shown in Fig. 4. A second switch was added in [9] to better capture this behavior as illustrated in Fig. 5.

Fig. 4. Snap-back delay sub-model requires a second switch [9].

Fig. 5. Improved sub-model for snapback.

#### III. DEVICE CHARACTERIZATION AND MODELING

The ability of the improved model to accurately represent a variety of ESD protection devices is investigated in the following sections by comparing measurement and simulation of a snapback TVS device, a non-snapback diode, and a varistor. The turn-on behavior of the components was measured through very fast transmission line pulse (VF-TLP) testing. An ESD-EMC TLP-ES620-50 compact pulsed IV-curve system with a 2 GHz 10 GSa/s Rohde & Schwarz oscilloscope was used to record 10 ns-long VF-TLP waveforms. The current risetime was set to 200 ps. Both the quasi-static I-V curves and their transient responses were captured. Transient models were developed through tuning to match measurements. The small-signal model on the front-end of each TVS device was found by measuring S11 into the device when it was in an "off" state [9].

#### A. Snapback TVS Diode: PESD3V3Y1BSF

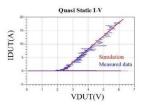

A bidirectional TVS with a low trigger-voltage and low clamping voltage was investigated first. Fig. 6 shows the measured and simulated I-V curves for this device.

Fig. 6. I-V curve of a snapback TVS device.

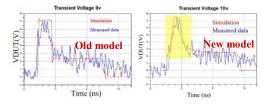

Fig. 7 shows the simulated transient response of the snapback diode before and after modification of the device model. The old model does a reasonable job of capturing the IV curve of the device and the transient voltage waveform, but the improved model captures both the shape of the waveform and the magnitude of the peak better.

Fig. 7. Measured and simulated transient response of the TVS snapback device simulated with the old device model (left) and the new model (right).

#### B. Non-Snapback TVS Diode

Simulated and measured IV curves for the non-snapback TVS diode were captured well by both models, so are not shown here. An example of the simulated and measured transient response of using the models are shown in Fig. 8. The improved model better captures the transient voltage overshoot.

Fig. 8. Measured and simulated transient response of the non-snapback TVS device using the old TVS model (left) and using the improved model (right).

#### C. Varistor

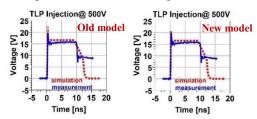

The "quasi-static" I-V curve of a metal-oxide varistor is similar to a non-snapback TVS diode, but the current rises more slowly with voltage due to its slow response time. Both the old and improved device models predict the IV curve well, so it is not shown here.

Fig. 9. Transient response of the varistor as predicted with the original TVS model (left) and using the improved model (right).

Fig. 9 shows the simulated and measured transient response of the varistor. During conduction, the varistor voltage remains relatively constant even when the current changes by several orders of magnitude. The impact of conductivity modulation is significant. The improved model was able to better capture the transient voltage response as demonstrated in Fig. 9. Setting the parameters for the conductivity modulation sub-model was particularly important for this device.

#### IV. SEED MODELING

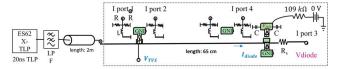

The ability to predict the interaction between two ESD protection devices was tested for each modeled TVS in a SEED simulation where an off-chip ESD protection device protected an IC with an on-chip diode (Fig. 10). Measurements were performed on a custom PCB test board [9]. The IC ESD protection was represented with a simple diode, which was also modeled using the improved modeling approach. Between the TVS device and the IC there was a 50-ohm PCB trace. An ESDEMC Inc. TLP was connected via an SMA connector to the input of the board. The voltages and currents on the board were captured using a 12 GHz Agilent DSO81204B oscilloscope with 40 GSa/s and a 2 GHz 10 GSa/s Rohde & Schwarz oscilloscope.

Fig. 10. SEED test configuration.

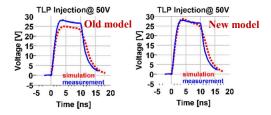

Measurements were performed using 20 ns wide TLP pulses with levels varied according to the characteristics of each device and with rise times varying from 0.65 ns to 2 ns. Information regarding the quasi-static and peak current through each device was extracted to demonstrate the performance of the device models. The TLP voltage was also measured when injecting into a 50-ohm load and was used in the SEED simulations.

#### A. Snapback TVS Diode with On-Chip Diode

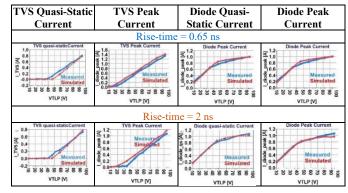

Fig. 11 shows the measured and simulated results when the snapback TVS was used to protect the on-chip diode. In most cases, the quasi-static and peak currents were predicted within a few percent. The peak TVS and diode current was more challenging to capture for a slow rise time, but overall was acceptable (generally within 5%).

Fig. 11. Simulated and measured voltages and currents when the snapback TVS diode was used with the on-chip diode.

#### B. Non-Snapback TVS Diode with On-Chip Diode

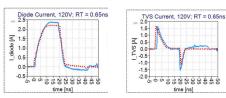

The non-snapback TVS device and on-chip diode were tested with levels ranging from 120 V to 400 V. An example transient response is given in Fig. 12. The ability to predict the peak and quasistatic currents are shown in Fig. 13. Quasi-static and peak current were captured within about 2%.

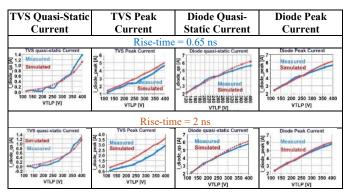

#### C. Varistor with On-Chip Diode

Fig. 14 shows the results when a varistor was protecting an on-chip diode. While results are acceptable, the model performance with the varistor was modestly worse than with the other devices, in particular when predicting the peak current through the varistor itself. This error results when the rise time of the current associated with the varistor turn-on varies between the measurement and the simulation, since the current often does not reach its peak level over the duration of the 20 ns TLP event.

Fig. 12. Transient response for the off-chip non-snapback TVS and IC protection diode.

| TVS Quasi-Static                                                                                                               | TVS Peak                                                                            | Diode Quasi-                                                                      | Diode Peak                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Current                                                                                                                        | Current                                                                             | Static Current                                                                    | Current                                                                                     |

| Rise-time = $0.65 \text{ ns}$                                                                                                  |                                                                                     |                                                                                   |                                                                                             |

| TVS quasi-static Current    Measured                                                                                           | TVS Peak Current  7 85 85 85 87 87 88 88 88 88 88 88 88 88 88 88 88                 | Diode quasi-static current  3.5  \$3.0  9.2.5  Measured  Simulated  2.6  VILP [V] | Diode Peak Current  1 8 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                 |

| Rise-time = 2 ns                                                                                                               |                                                                                     |                                                                                   |                                                                                             |

| TVS quasi-static Current  4 3 Simulated  5 2 Measured  90 1  1 1 1 1 1 2 2 2 2 2 3 3 4 5 5 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | TVS Peak Current  6 5 5 Measured 68 4 Simulated 80 90 90 91 10 18 80 80 80 VILP [V] | 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8                                           | Diode Peak Current  3.6 3.6 3.7 3.7 3.8 3.2 3.8 3.2 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8 3.8 |

Fig. 13. Simulated and measured voltages and currents when the non-snapback TVS diode was used with the on-chip diode.

Fig. 14. Simulated and measured voltages and currents when the varistor was used with the on-chip diode protection.

#### V. CONVERGENCE PROBLEMS

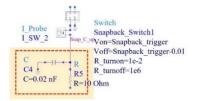

The fast non-linear responses of the ESD protection device and the diode working in parallel can cause SPICE convergence issues. Ensuring the value of  $V_{off}$  is at a reasonable value is important. Tuning the RC low pass filter (Fig. 15) can slow down the snapback and improve convergence. If this does not improve convergence, one may also try to vary the SPICE integration coefficient, mu, increase the time-point iteration limit, or adjust the current and voltage tolerances.

Fig. 15. First snapback switch in sub-model structure.

#### VI. CONCLUSIONS

The improved TVS behavioral model can closely predict measured results for different protection devices. The model performs well even in the challenging case. Performance was worst for slow rise times, but still within 10% of measurements for nearly all of the cases studied. Convergence can be an issue, but can be addressed by either slowing down the switching of parts or by modifying SPICE simulation parameters.

#### ACKNOWLEDGMENT

This work was supported in part by the National Science Foundation (NSF) under Grant IIP-1916535.

#### REFERENCES

- P. Wei, G. Maghlakelidze, A. Patnaik, H. Gossner and D. Pommerenke, "TVS Transient Behavior Characterization and SPICE Based Behavior Model," 2018 40th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), 2018.

- [2] N. Monnereau et al "Behavioral-modeling methodology to predict Electrostatic-Discharge susceptibility failures at system level: An IBIS improvement," 10th International Symposium on Electromagnetic Compatibility, York, 2011

- [3] L. Wei, et al., "A convergence robust method to model snapback for ESD simulation," CAS 2011 Proceedings (2011 International Semiconductor Conference), Sinaia, 2011

- [4] Dobrescu, D., et al., "A SPICE modeling of the negative resistance breakdown region for the bipolar junction transistor." Microelectronics, 2000

- [5] Z. Pan, et al., "Understanding and Modeling of Diode Voltage Overshoots During Fast Transient ESD Events," in IEEE Transactions on Electron Devices, vol. 61, no.8, pp. 2682-2689, Aug. 2014.

- [6] J. Willemen et al., "Characterization and modeling of transient device behavior under CDM ESD stress," 2003 Electrical Overstress/Electrostatic Discharge Symposium, 2003, pp. 1-10.

- [7] L. Shen, S. Marathe, J. Meiguni, G. Luo, J. Zhou and D. Pommerenke, "TVS Devices Transient Behavior Modeling Framework and Application to SEED," 2019 41st Annual EOS/ESD Symposium (EOS/ESD), 2019, pp. 1-10, doi: 10.23919/EOS/ESD.2019.8869992.

- [8] A. Pak, S. M. Mousavi, D. Pommerenke, G. Maghlakelidze and Y. Xu, "Improvement of SPICE based ESD Protection Models for I/O Protection Modeling," 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, 2021.

- [9] J. Zhou, Y. Xu, S. Bub, S. Holland, J. Meiguni, D. Pommerenke, D. Beetner, "Transient Response of ESD Protection Devices for a High-Speed I/O Interface," IEEE Trans. EMC, vol. 64, no. 4, pp. 907-14, 2022.

- [10] Y. Xu, J. Zhou, S. Bub, S. Holland, J. Meiguni, D. Pommerenke, D. Beetner, "Improved SEED Modeling of an ESD Discharge to a USB Cable," IEEE Trans. EMC, to appear available IEEE Access.