## Multiport DC-DC Converters for Hybrid Energy Systems

Immanuel Ninma Jiya

# Multiport DC-DC Converters for Hybrid Energy Systems

## **Immanuel Ninma Jiya**

# Multiport DC-DC Converters for Hybrid Energy Systems

Doctoral Dissertation for the Degree *Philosophiae Doctor (PhD)* at the Faculty of Engineering and Science, Specialisation in Renewable Energy

University of Agder

Faculty of Engineering and Science

2023

Doctoral dissertations at the University of Agder 423

ISSN: 1504-9272

ISBN: 978-82-8427-139-2

© Immanuel Ninma Jiya, 2023

Printed by Make!Graphics Kristiansand, Norway

#### Acknowledgements

I am humbled and grateful to have reached this milestone in my academic journey, and I would like to take a moment to acknowledge the many individuals who have in one way or the other contributed to the completion of this work.

Firstly, I would like to express my sincere appreciation to my supervisor, Prof. Huynh van Khang for his unwavering guidance, support, and mentorship. His expertise, intellectual curiosity, and insightful feedback have been indispensable throughout the course of my research. Your commitment to my academic development and well-being has been a source of great inspiration and motivation. In the league of super-sport agents and football managers like Jorge Mendes and José Mourinho, I consider you a super supervisor. I would also like to extend my gratitude to Prof. Rade Ciric, my co-supervisor, and Prof. Nand Kishor, an external volunteer collaborator on the PhD project, for their valuable feedback, constructive criticism, and challenging questions. Their insightful comments and suggestions have contributed significantly to the quality of this work, and I am deeply grateful for their time and effort. To Steve Schading, your help and technical support with fabrication and modification of equipment and tools is deeply appreciated.

I would also like to thank the many institutions and organizations that have supported my research, especially the Research Council of Norway. Their financial support has enabled me to pursue this research with vigor and enthusiasm. And to Prof. Yunwei Li of the University of Alberta, Edmonton, Canada, I am deeply grateful for their investment in my academic development, through the opportunity to conduct a six-month research visit in this Lab. Also, to Emma Elisabeth Horneman of the PhD Program Committee for Engineering (PPCE) for her efforts and help administratively and other things during my fellowship and studentship at the University of Agder (UiA). Your proactive attitude to your work and responsiveness to requests made my study life a lot easier.

My gratitude also goes to my family, especially my Mum and Dad, Prof. Elisha and Florence Jiya, my siblings, Jemimah and Nasara, I am forever grateful for your love, support, and encouragement. To my uncles and aunties, Mr. & Mrs. Obadiah & Sarah Jiya, Mr. & Mrs. John & Comfort Jiya, Mr. & Mrs. Andrew Jiya, Mr. & Barr. (Mrs.) Emmanuel and Martha Sule, Mr. & Mrs. Enock & Mary Jiya, Mr. & Mrs. Peter & Susan Jiya, your unwavering belief in me and your constant reassurance has been a source of strength and inspiration throughout my journey. And to my cousins, Dr. J. Y. Jiya (Ya Joe), Ya Yebo, Babayisa, Ya Victor, Uncle

Dauda, Samuel Samson, Samuel Jiyah, Joshua Jiya, and Mike Sule to list just a few, thank you for always being there for me, even when I couldn't be there for you.

I am also deeply grateful to my colleagues, Ghali Yakoub, Haidar Hosamo, Thomas Ferriday, Milad Golzar, Basant Paudyal, Arild Husebø, Jayachandra Malavatu, Pasan Gunawardena, Juan Pardo, Juan Diego, Raju Shrestha, Sarang Kumar, Rohan Money, Drs. Saba Mirza, Salem Ahmed, Nils Johannesen, Antoine Shyikira, Gulshan Noorsumar, Dipendra Subedi, Paula Molina, Carla Terron and Assoc. Prof. Jagath Senanayaka, for their camaraderie. The countless hours spent discussing ideas, sharing resources, and offering feedback have created a stimulating intellectual environment that has enriched my academic experience. I would also like to express my appreciation to my friends, Ayomide, Oscar Segbefia, Solomon Adamako, David Offo, Dr. Ofuafo Ajari, Marvelous Kasali, Joshua James, Christiana Stevens, Janet Carboo, Pius Oladoyin, Precious Maigeri, Dika Ututu, Jeremy Aweda, Yommy Madamori, Abigail Doshima, and Hannah Richi, for their unwavering support and encouragement during some of the challenging moments of my PhD journey.

I am particularly grateful to Profs. Abraham Usman, Jacob Tsado, Olushola Alabi, Rupert Gouws, Job Nmadu, Dr., and Dr. (Mrs.) Ogunrombi, Mr. Akin Ibimidun, Engr. Daniel Shaba, Dr. Bala Shehu, Dr. and Mrs. Abaya, Pastor Tunde Raji, and Evangs. Kayode and Fumi Olutimehin, whose unwavering encouragement, support, and belief in me has been a constant source of strength throughout my academic journey. Their support has provided a safe haven during the many moments of doubt and uncertainty.

Finally, I would like to dedicate this thesis to my Lord and King, God almighty, for the gift of salvation through his son Jesus Christ and for the Holy spirit whose inspiration and insight has been the cornerstone of my success. His love for me has provided a foundation of strength and resilience, and I could not have reached this point without Him.

In conclusion, I would like to extend my deepest appreciation to everyone who has supported me throughout my journey towards completing this thesis. Your unwavering support, encouragement, and belief in me have been instrumental in helping me to achieve this milestone, and for that, I am forever grateful.

#### **Summary**

Renewable energy sources (RESs) like solar and wind have gained attention for their potential to reduce reliance on fossil fuels and mitigate climate change. However, integrating multiple RESs into a power grid is challenging due to their unpredictable nature. Power electronic converters can manage hybrid energy systems by controlling power flow between RESs, storages, and the grid. Conventional single input dc-dc converters have limitations such as low efficiency, bulky designs, and complex control systems. Multiport dc-dc converters (MPCs) have emerged as a solution for hybridizing multiple sources, storages, and load systems by providing a common interface. Existing MPCs have limitations such as high component count, limited operational range, complex control strategies and restrictions on the number of inputs to list a few. Thus, there is a need to develop new MPCs that combine the advantages of existing designs while overcoming their limitations. Isolated MPCs with unipolar or bipolar outputs are needed that can accommodate any number of inputs, offer high voltage gain, use fixed magnetic components for galvanic isolation (regardless of the number of ports), and have a simplified control strategy. Additionally, new non-isolated MPCs with unipolar or bipolar outputs are required, featuring reduced component count, simultaneous power transfer and power flow between input ports, high voltage gain, low control complexity, and modular design allowing for arbitrary increase in the number of input ports. There is also an opportunity to apply MPCs in the integration of RESs and storages to ac grids through multilevel inverters for low component count, high efficiency, low harmonics, and higher power density. Further, advances in bipolar MPCs provide the chance to balance the dc bus without requiring a complex control system.

In this dissertation, five novel MPC topologies ( $T_A$  to  $T_E$ ) of non-isolated ( $T_A$ ,  $T_B$  and  $T_D$ ) and isolated ( $T_C$  and  $T_E$ ) configuration with unipolar ( $T_A$ , to  $T_C$ ) and bipolar outputs ( $T_D$  and  $T_E$ ) were developed and verified for various hybrid energy system applications. All these contributions were made in eight publications (Papers I – VIII), including three journals and five conference papers. These papers are listed in Chapter 1, highlighting the details of their specific contributions, respectively. Further, the ac grid integration through integrating some of the MPCs ( $T_A$  and  $T_D$ ) with MLIs were explored and validated. The integration of the bipolar MPCs to bipolar dc transmission/distribution infrastructure with the possibility of supplying a critical unipolar dc load was also verified. The initial idea of  $T_A$ , a new non-

isolated MPC with unipolar outputs was presented in paper I with more detailed analysis and the experimental validations presented in paper II. Paper III presents  $T_C$ , an isolated MPC topology with unipolar outputs, along with key results. Paper IV, presents  $T_D$ , a novel family of non-isolated MPCs with bipolar outputs, and key results including the ac grid integration using an MLI is verified in this paper. In paper V, a modified unidirectional version of  $T_A$  was used to achieve the unipolar dc to ac grid integration, verifying the use of an auxiliary circuit and control-based approach for balancing the dc link voltage. Paper VII presents  $T_B$ , an improvement to  $T_A$ , which allows for power flow between the RES ports and the energy storage ports. The initial idea of  $T_E$ , a new isolated MPC with bipolar outputs was presented in paper VI with more detailed analysis, and the experimental validations were implemented in paper VIII. The verification of integrating  $T_E$  to a bipolar dc distribution infrastructure supplying a critical unipolar dc load was also presented in paper VIII. The steady state operation of these new MPC topologies was analysed mathematically and verified using detailed simulation and validated on an in-house hardware-in-the-loop (HIL) platform and on an experimental test rig, respectively. The novelty of the proposed MPC topologies is highlighted through detailed comparative studies, underscoring some important metrics such as component count, modularity, and voltage gain to list just a few. The development of these converters can significantly contribute to the integration of RESs and storages into the power grid and promote sustainable energy practices. This dissertation has five main chapters: the first presents the introduction and background to MPC, the second reviews the state of the art while the third and fourth presents the new MPCs proposed herein and the main results, respectively, and a concluding Chapter 5 at the end, highlighting the key findings and the limitations of this PhD study.

#### Sammendrag

Fornybare energikilder (RESs) som sol- og vindenergi har fått oppmerksomhet for sitt potensial til å redusere avhengigheten av fossile brensler og begrense klimaendringer. Imidlertid er det utfordrende å integrere flere RES-er i strømnettet på grunn av deres uforutsigbare natur. Kraftomformere med kraftelektronikk kan håndtere hybride energisystemer ved å kontrollere kraftflyten mellom RES-er, lagringsenheter og nettet. Konvensjonelle enkeltinngang DC-DC-omformere har begrensninger som lav effektivitet, klumpete design og komplekse kontrollsystemer. Multippel inngang DC-DC-omformere (MPC-er) har blitt en løsning for å kombinere flere kilder, lagringsenheter og lastsystemer ved å gi en grensesnitt. Eksisterende MPC-er har begrensninger komponenttall, begrenset operasjonsområde, komplekse kontrollstrategier og begrensninger på antall innganger, for å nevne noen. Det er derfor behov for å utvikle nye MPC-er som kombinerer fordelene med eksisterende design samtidig som de overvinner deres begrensninger. Det trengs isolerte MPC-er med unipolare eller bipolare utganger som kan romme et hvilket som helst antall innganger, tilby høy spenningsgevinst, bruke faste magnetiske komponenter for galvanisk isolasjon (uavhengig av antall porter) og ha en forenklet kontrollstrategi. I tillegg kreves det nye ikke-isolerte MPC-er med unipolare eller bipolare utganger, med redusert antall komponenter, samtidig kraftoverføring og kraftflyt mellom inngangsportene, høy spenningsgevinst, lav kontrollkompleksitet og modulært design som tillater vilkårlig økning i antall inngangsporter. Det er også muligheter for å bruke MPC-er i integreringen av RES-er og lagringssystemer i AC-nett gjennom flernivåinvertere for lavt komponenttall, høy effektivitet, lav harmonisk forvrengning og høyere effekttetthet. Videre gir fremskritt innen bipolare MPC-er muligheten til å balansere likestrømsbussen uten å kreve et komplekst kontrollsystem.

I denne avhandlingen ble det utviklet og verifisert fem nye MPC-topologier ( $T_A$  til  $T_E$ ) av ikke-isolert ( $T_A$ ,  $T_B$  og  $T_D$ ) og isolert ( $T_C$  og  $T_E$ ) konfigurasjon med unipolare ( $T_A$  til  $T_C$ ) og bipolare utganger ( $T_D$  og  $T_E$ ) for ulike anvendelser innen hybride energisystemer. Alle disse bidragene ble presentert i åtte publikasjoner (Artikkel I - VIII), inkludert tre tidsskrifter og fem konferanseartikler. Disse artiklene er oppført i kapittel 1, og detaljene om deres spesifikke bidrag blir fremhevet. Videre ble AC-nettintegrasjon gjennom integrering av noen av MPC-ene ( $T_A$  og  $T_D$ ) med MLIs utforsket og validert. Integrering av bipolare MPC-er til bipolare DC-

transmisjons- / distribusjonsinfrastruktur med mulighet for å forsyne en kritisk unipolar DC-last ble også bekreftet. Den første ideen til  $T_A$ , en ny ikke-isolert MPC med unipolare utganger, ble presentert i artikkel I med mer detaljert analyse og eksperimentell validering i artikkel II. Artikkel III presenterer  $T_C$ , en isolert MPCtopologi med unipolare utganger, sammen med nøkkelresultater. Artikkel IV presenterer  $T_D$ , en ny familie av ikke-isolerte MPC-er med bipolare utganger, og nøkkelresultater, inkludert AC-nettintegrasjon ved bruk av en MLI, blir verifisert i denne artikkelen. I artikkel V ble en modifisert ensrettet versjon av  $T_A$  brukt for å oppnå integrasjon av unipolar likestrøm til vekselstrømnett, og bruken av en hjelpestrømskrets og en kontrollbasert tilnærming for å balansere likestrømslenken ble bekreftet. Artikkel VII presenterer  $T_B$ , en forbedring av  $T_A$ , som tillater kraftflyt mellom RES-porter og energilagringsporter. Den første ideen til  $T_E$ , en ny isolert MPC med bipolare utganger, ble presentert i artikkel VI med mer detaljert analyse, og de eksperimentelle valideringene ble implementert i artikkel VIII. Verifiseringen av integrering av  $T_E$  til en bipolær DC-distribusjonsinfrastruktur som forsyner en kritisk unipolar DC-last ble også presentert i artikkel VIII. Den stabile driftstilstanden til disse nye MPC-topologiene ble analysert matematisk og verifisert ved hjelp av detaljerte simuleringer og valideringer på en internt utviklet hardware-in-the-loop (HIL) plattform og på en eksperimentell testrigg, henholdsvis. Nyskapningen til de foreslåtte MPC-topologiene blir fremhevet gjennom detaljerte sammenlignende studier, og viktige mål som komponenttall, modularitet og spenningsgevinst blir understreket. Utviklingen av disse omformerne kan bidra betydelig til integreringen av RES-er og lagringssystemer i strømnettet og fremme bærekraftige energipraksiser. Denne avhandlingen har fem hovedkapitler: det første presenterer introduksjonen og bakgrunnen for MPC, det andre gir en gjennomgang av kunnskapsstatus, mens det tredje og fjerde presenterer de nye MPC-ene som er foreslått her, og hovedresultatene, henholdsvis. Avslutningsvis presenteres kapittel 5, som fremhever de viktigste funnene og begrensningene i denne doktorgradsstudien.

#### **List of Publications**

The following listed papers from latest to earliest are based on research activities conducted by the author within the framework of the PhD study and have been published or submitted for publications in peer-reviewed journals and conference proceedings.

- I. N. Jiya, H. V. Khang, N. Kishor and R. Ciric, "Four Quadrant Switch Based Multiple-Input DC-DC Converter," in 2021 IEEE 12th Energy Conversion Congress & Exposition Asia (ECCE-Asia), Singapore, Singapore, 2021, pp. 2199-2204, doi: 10.1109/ECCE-Asia49820.2021.9479432.

- II. N. Jiya, A. M. S. Ali, H. V. Khang, N. Kishor and R. Ciric, "Novel Multisource DC-DC Converter for All-electric Hybrid Energy Systems," IEEE Transactions on Industrial Electronics, vol. 69, no. 12, pp. 12934–12945, Dec. 2022, doi: 10.1109/TIE.2021.3131871.

- III. I. N. Jiya, A. Salem, and H. V. Khang, "Novel Isolated Multiple-Input Buck-Boost DC-DC Converter for Renewable Energy Sources," *IECON* 2021 47th Annual Conference of the IEEE Industrial Electronics Society, Toronto, Canada, 2021, pp. 1-6, doi: 10.1109/IECON48115.2021.9589538.

- IV. I. N. Jiya, H. V. Khang, N. Kishor, and R. M. Ciric, "Novel Family of High-Gain Nonisolated Multiport Converters With Bipolar Symmetric Outputs for DC Microgrids," *IEEE Transactions on Power Electronics*, vol. 37, no. 10, pp. 12151–12166, Oct. 2022, doi: 10.1109/TPEL.2022.3176688.

- V. **I. N. Jiya,** H. V. Khang, A. Salem, N. Kishor and R. Ciric, "Integrated Multiport DC-DC and Multilevel Converters for Energy Sources," *2022 IEEE Industry Applications Annual Meeting*, Detroit, Michigan, 2022, pp. 1-7, doi: 10.1109/IAS54023.2022.9939764.

- VI. I. N. Jiya, H. V. Khang, N. Kishor and R. Ciric, "Novel High Gain Multiport Isolated DC-DC Converter with Bipolar Symmetric Outputs," IECON 2022 – 48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 2022, pp. 1-6, doi: 10.1109/IECON49645.2022.9968834.

- VII. I. N. Jiya, P. Gunawardena, H. V. Khang, N. Kishor and Y. Li, "Multiport DC-DC Converter for Integrating Energy Systems in All-Electric Vehicles," 2023 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International

- *Transportation Electrification Conference (ESARS-ITEC)*, Venice, Italy, 2023, pp. 1-6, doi: 10.1109/ESARS-ITEC57127.2023.10114856.

- VIII. **I. N. Jiya,** H. V. Khang, P. Gunawardena, N. Kishor and Y. Li, "Novel Isolated Multiport DC Converter with Natural Bipolar Symmetry for Renewable Energy Source Integration to DC Grids," in *IEEE Access*, (Submitted).

**Other Works:** The following papers were published during the time of the PhD project but are not included in the dissertation.

- I. A. Salem, H. V. Khang, **I. N. Jiya** and K. G. Robbersmyr, "Hybrid Three-Phase Transformer-Based Multilevel Inverter With Reduced Component Count," in *IEEE Access*, vol. 10, pp. 47754-47763, 2022, doi: 10.1109/ACCESS.2022.3171849.

- II. N. Jiya, Ahmed Salem, Huynh Van Khang, and Raimondas Pomarnacki, "Integrated Multiport DC-DC and Multilevel Converters for Multiple Renewable Energy Source Integration," in *IEEE Access*, (Submitted).

## **Contents**

| Ackno   | owledgements                              | v     |

|---------|-------------------------------------------|-------|

| Summ    | nary                                      | vii   |

| Samm    | nendrag                                   | ix    |

| List of | f Publications                            | xi    |

| Conte   | nts                                       | xiii  |

| List of | f Figures                                 | XV    |

| List of | f Tables                                  | xxi   |

| List of | f Abbreviations and Symbols               | xxiii |

| 1 Intro | oduction                                  | 1     |

| 1.1     | Background                                | 1     |

| 1.2     | Motivation and research problem           | 5     |

| 1.3     | Contributions of the dissertation         | 5     |

| 1.4     | Dissertation structure                    | 13    |

| 2 State | e of the art                              | 15    |

| 2.1     | Non-isolated MPCs with unipolar outputs   | 16    |

| 2.2     | Isolated MPCs with unipolar outputs       | 19    |

| 2.3     | Non-isolated MPC with bipolar outputs     | 22    |

| 2.4     | Isolated MPC with bipolar outputs         | 23    |

| 2.5     | Grid integration applications             | 25    |

| 3 Nove  | el multiport converters                   | 27    |

| 3.1     | Proposed MPC topology A (T <sub>A</sub> ) | 27    |

| 3.      | 1.1 Circuit description                   | 27    |

| 3.      | 1.2 Steady state analysis                 | 29    |

| 3.2     | Proposed MPC topology B (T <sub>B</sub> ) | 34    |

| 3.      | 2.1 Circuit description                   | 34    |

| 3.      | 2.2 Steady state analysis                 | 35    |

| 3.3     | Proposed MPC topology C (T <sub>C</sub> ) | 41    |

| 3.      | 3.1 Circuit description                   | 41    |

| 3.      | 3.2 Steady state analysis                 | 41    |

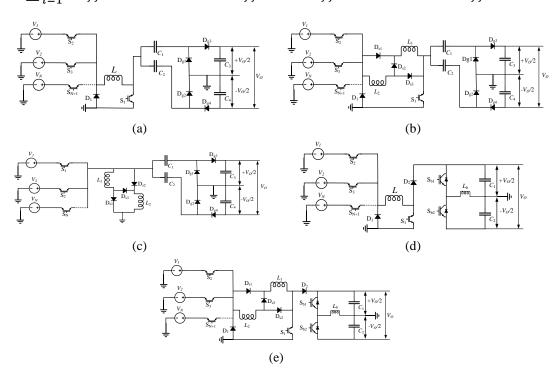

| 3.4     | Proposed MPC topology D (T <sub>D</sub> ) | 45    |

| 3.      | 4.1 Circuit description                   | 45    |

| 3.      | 4.2 Steady state analysis                 | 46    |

| 3.5     | Proposed MPC topology E (T <sub>E</sub> ) | 54    |

| 3.      | 5.1 Circuit description                   | 54    |

| 3.     | .5.2 Steady state analysis                       | 56  |

|--------|--------------------------------------------------|-----|

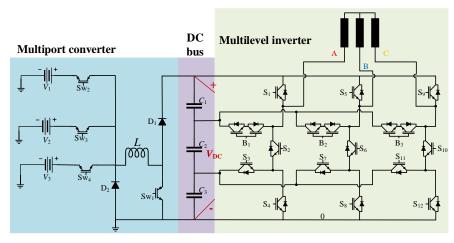

| 3.6    | Grid integration                                 | 60  |

| 3.     | .6.1 Bipolar DC to Critical Unipolar DC          | 60  |

| 3.     | .6.2 Unipolar MPC to AC                          | 61  |

| 3.     | .6.3 Bipolar MPC to AC                           | 65  |

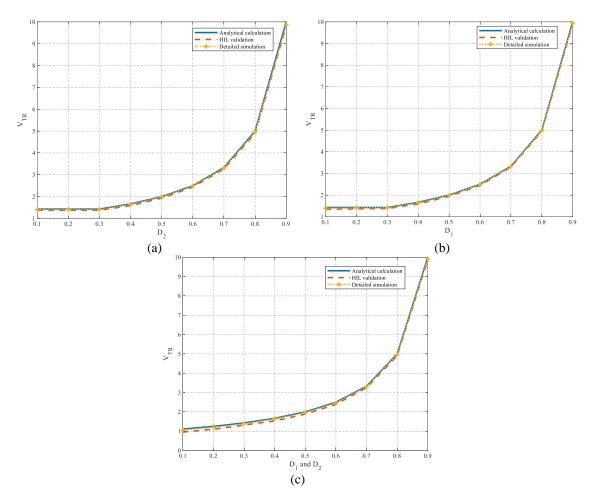

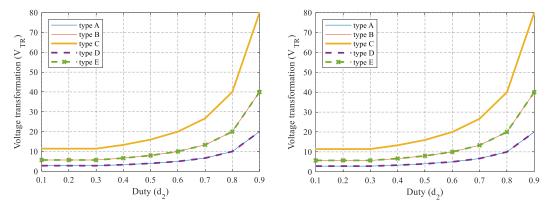

| 3.7    | Voltage transformation factor (V <sub>TR</sub> ) | 65  |

| 3.     | $7.1 V_{TR}$ for $T_A$                           | 66  |

| 3.     | $7.2 V_{TR}$ for $T_B$                           | 66  |

| 3.     | $.7.3 \ V_{TR}  \text{for T}_{\text{C}}$         | 66  |

| 3.     | $7.4 V_{TR}$ for $T_D$                           | 66  |

| 3.     | $7.5 V_{TR}$ for $T_E$                           | 67  |

| 4 Resu | ults and discussions                             | 69  |

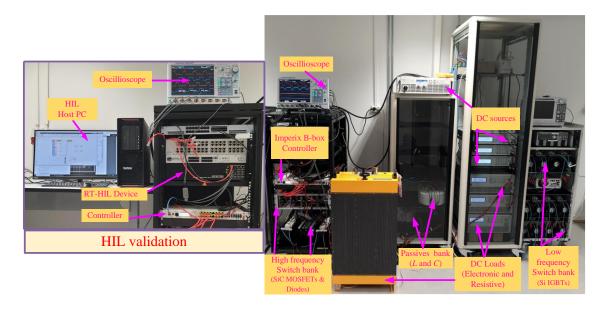

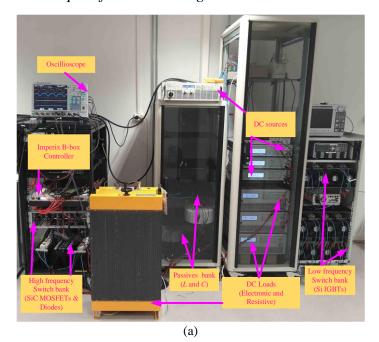

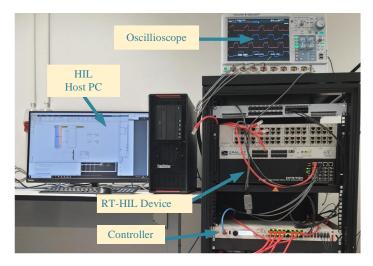

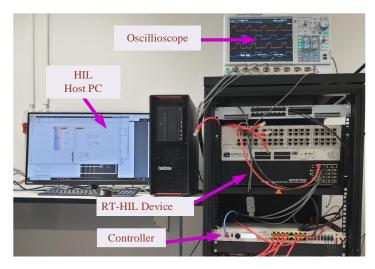

| 4.1    | In-house test setup                              | 69  |

| 4.2    | Key results for T <sub>A</sub>                   | 70  |

| 4.3    | Key results for T <sub>B</sub>                   | 77  |

| 4.4    | Key results for T <sub>C</sub>                   | 79  |

| 4.5    | Key results for T <sub>D</sub>                   | 83  |

| 4.6    | Key results for T <sub>E</sub>                   | 91  |

| 4.7    | Key results for grid integration                 | 96  |

| 4.8    | Comparison studies                               | 101 |

| 5 Con  | cluding remarks                                  | 107 |

| 5.1    | Conclusions                                      | 107 |

| 5.2    | Limitations and future work                      | 110 |

| Refer  | ences                                            | 113 |

| Apper  | ndices                                           | 121 |

| Pape   | er I:                                            | 123 |

| Pape   | er II:                                           | 137 |

| Pape   | er III:                                          | 163 |

| _      | er IV:                                           |     |

| _      | er V:                                            |     |

| Pape   | er VI:                                           | 229 |

| Pape   | er VII:                                          | 247 |

| Pane   | er VIII:                                         | 265 |

## **List of Figures**

| Figure 1. 1: Schematic overview of a hybrid energy system with multiple      |   |

|------------------------------------------------------------------------------|---|

| sources, storages and loads enabled by power electronic                      |   |

| converters.                                                                  | 3 |

| Figure 1. 2: Contributions of this dissertation based on the scope of MPCs   |   |

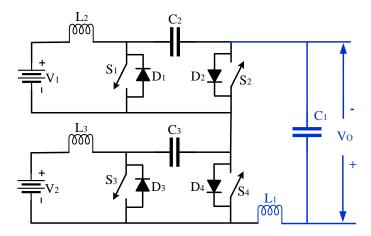

| Figure 2. 1: Developed non-isolated MPCs with unipolar outputs proposed      |   |

| in [32] 1                                                                    | 6 |

| Figure 2. 2: Developed non-isolated MPCs with unipolar outputs proposed      |   |

| in [36] 1                                                                    | 6 |

| Figure 2. 3: Developed non-isolated MPCs with unipolar outputs proposed      |   |

| in [39] 1                                                                    | 7 |

| Figure 2. 4: Developed non-isolated MPCs with unipolar outputs proposed      |   |

| in [38]                                                                      | 8 |

| Figure 2. 5: Developed non-isolated MPCs with unipolar outputs proposed      |   |

| in [37] 1                                                                    | 8 |

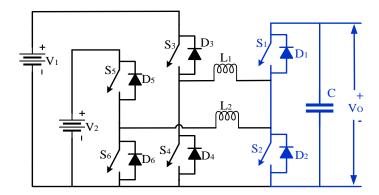

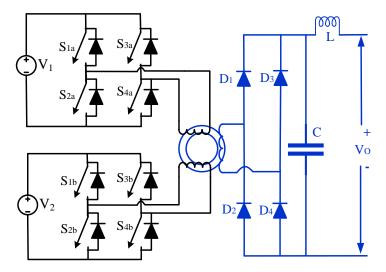

| Figure 2. 6: Developed isolated MPCs with unipolar outputs as proposed in    |   |

| [70]                                                                         | 0 |

| Figure 2. 7: Developed isolated MPCs with unipolar outputs as proposed in    |   |

| [23]                                                                         | 0 |

| Figure 2. 8: Developed isolated MPCs with unipolar outputs as proposed in    |   |

| [24]                                                                         | 1 |

| Figure 2. 9: Developed isolated MPCs with unipolar outputs as proposed in    |   |

| [29]                                                                         | 1 |

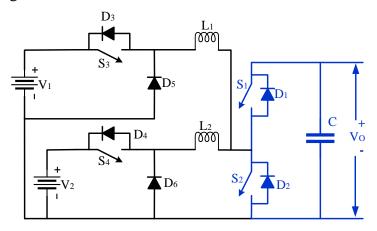

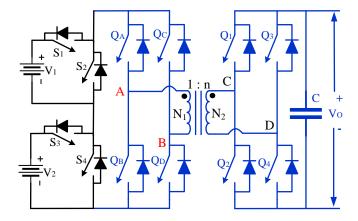

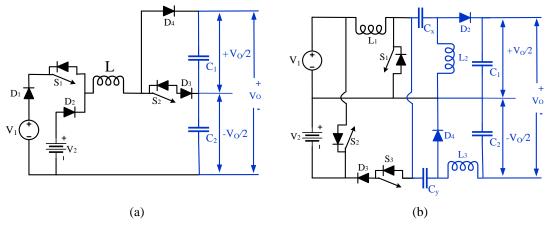

| Figure 2. 10: Recently proposed non-isolated MPCs with bipolar outputs in    |   |

| (a) [48], and (b) [47]2                                                      | 3 |

| Figure 2. 11: Recently proposed isolated MPCs with bipolar outputs in (a)    |   |

| [49], and (b) [50]                                                           | 4 |

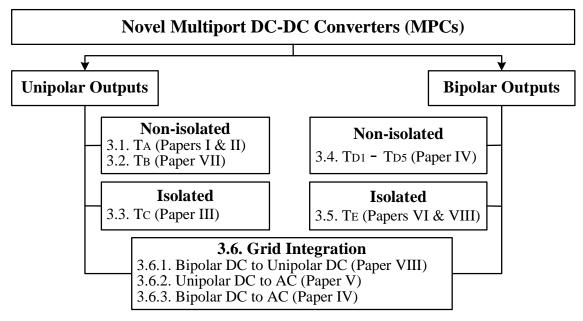

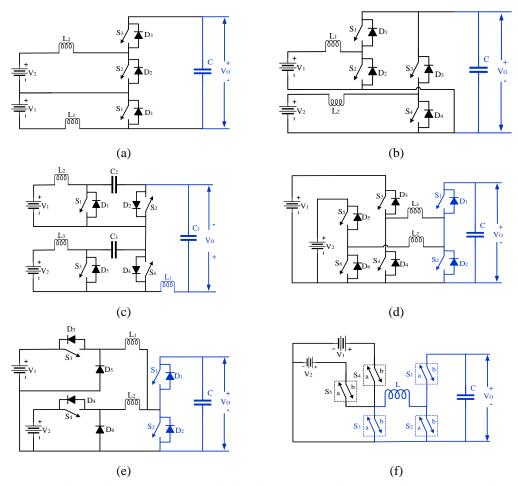

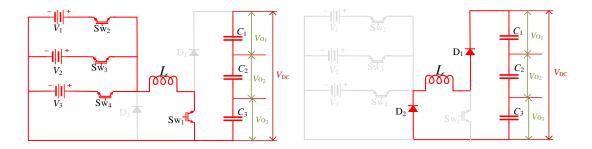

| Figure 3. 1: Layout of the new MPC topologies proposed in this dissertation. |   |

| 2                                                                            | 7 |

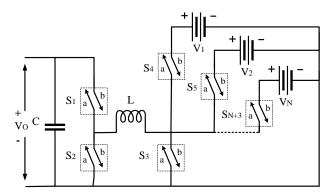

| Figure 3. 2: The proposed MPC topology A                                     | 8 |

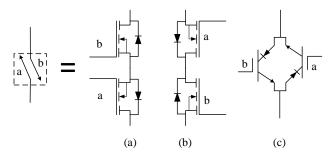

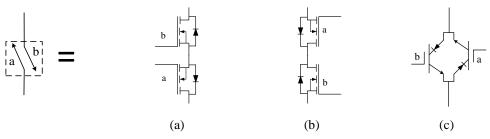

| Figure 3. 3: Four-quadrant switch using (a) common source (b) common         |   |

| drain and (c) reverse blocking IGBTs in antiparallel                         |   |

| configuration                                                                | 8 |

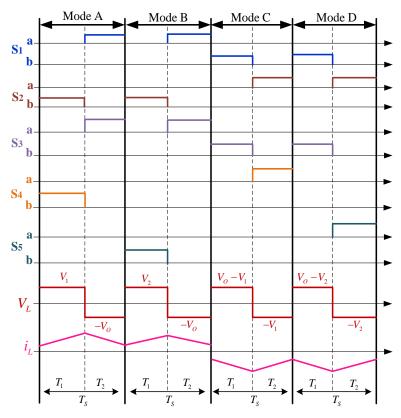

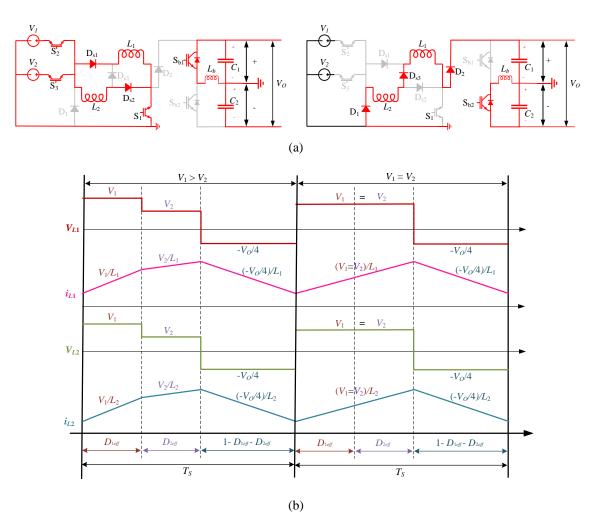

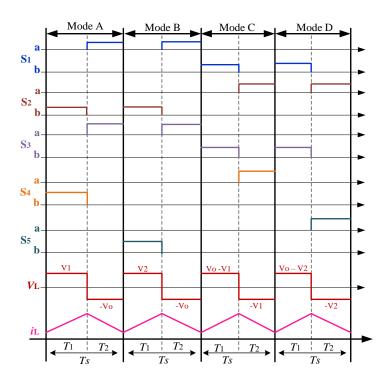

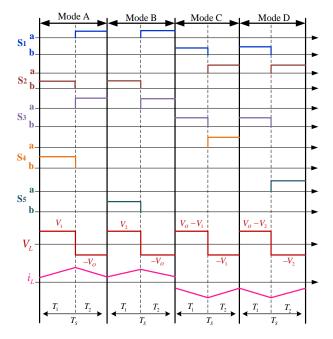

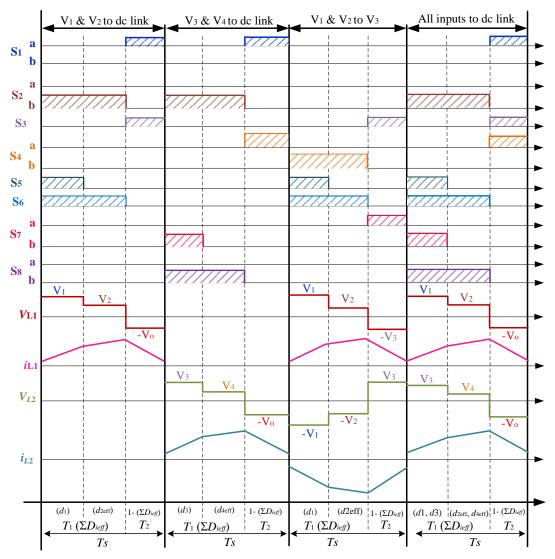

| Figure 3. 4: Steady-state waveforms of operation in CCM for modes A to D.    |   |

|                                                                              | 0 |

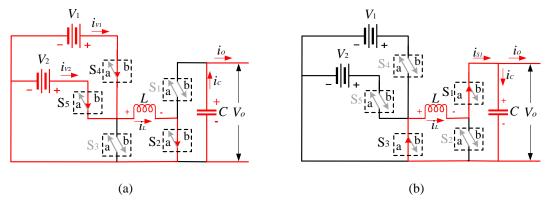

| Figure 3. 5: Path of current flow during mode E for inductor (a) charging and                           |      |

|---------------------------------------------------------------------------------------------------------|------|

| (b) discharging during steady state operation.                                                          | . 31 |

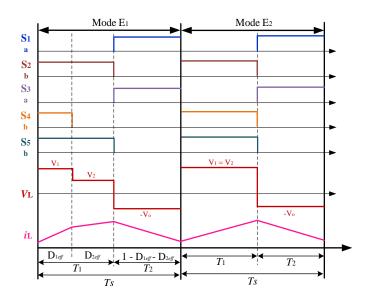

| Figure 3. 6: Steady-state CCM waveform in mode E.                                                       | . 31 |

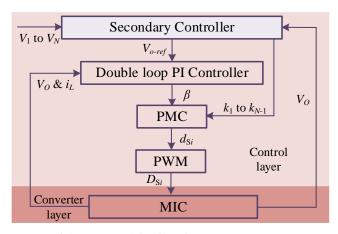

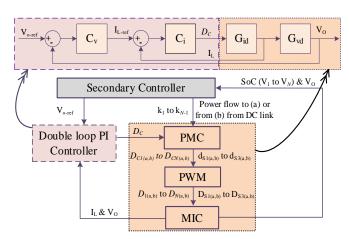

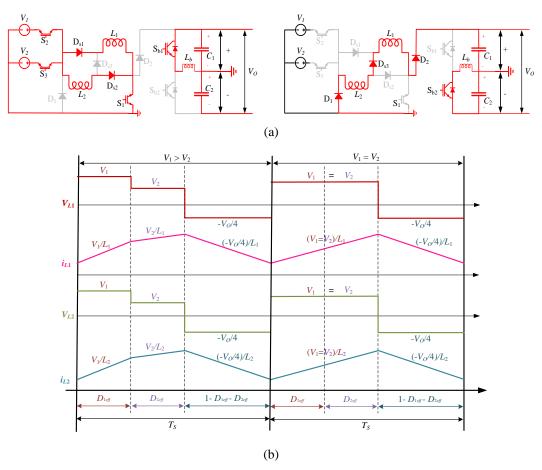

| Figure 3. 7: Converter operational control structure.                                                   | . 33 |

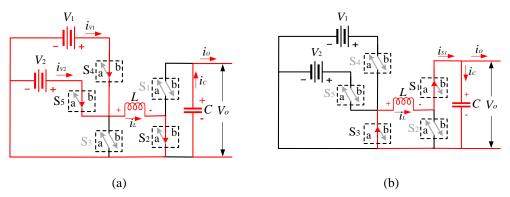

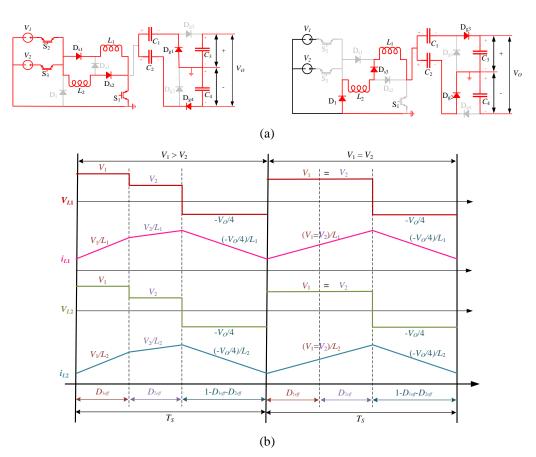

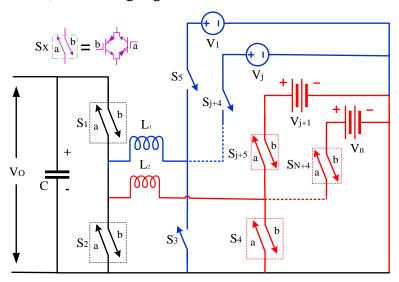

| Figure 3. 8: Circuit schematic of $T_B$ for integrating multiple energy sources                         |      |

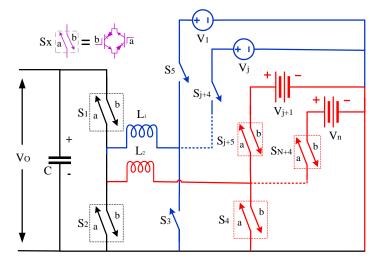

| and storages.                                                                                           | . 35 |

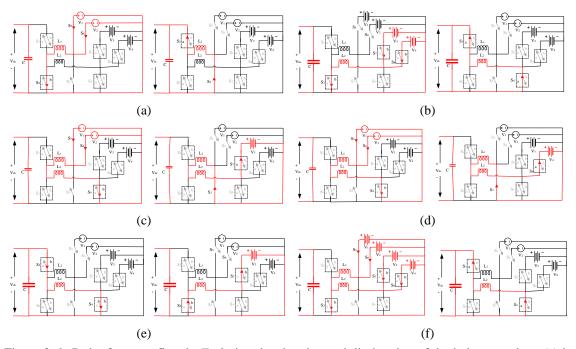

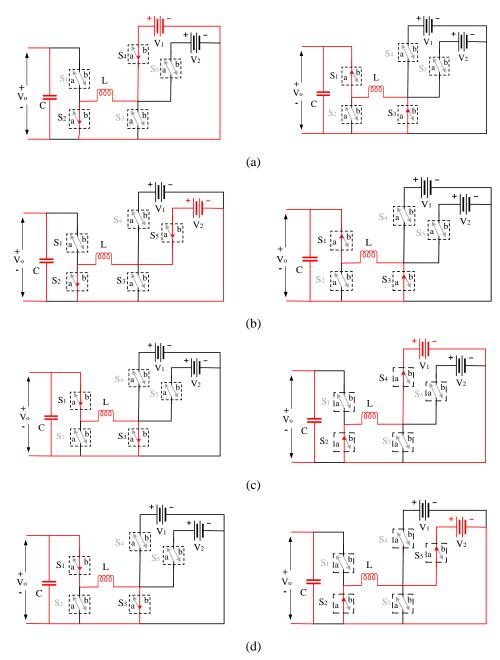

| Figure 3. 9: Path of current flow in $T_B$ during the charging and discharging                          |      |

| of the inductors where (a) is simultaneous power flow from                                              |      |

| energy source cluster to the dc link, (b) is simultaneous power                                         |      |

| flow from energy storage cluster to the dc link, (c & d) is                                             |      |

| simultaneous power flow from energy source cluster to the                                               |      |

| energy storage cluster respectively, (e) is power flow from the                                         |      |

| dc link to the first storage device and (f) is simultaneous power                                       |      |

| flow from both clusters to the dc link.                                                                 | . 37 |

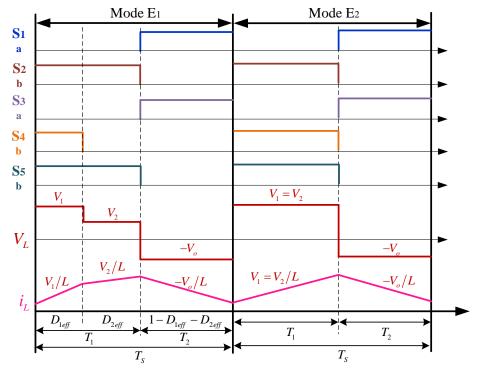

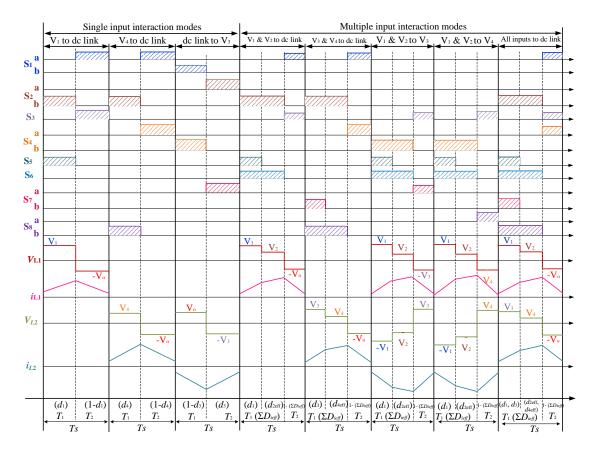

| Figure 3. 10: Steady state waveforms of the MPC operation in CCM for key                                |      |

| modes of operation.                                                                                     |      |

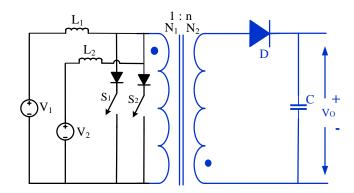

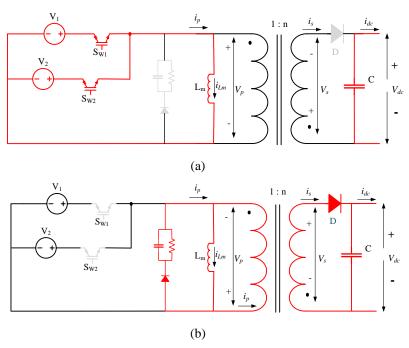

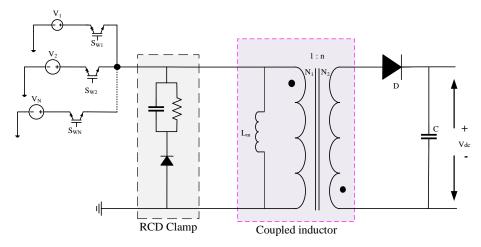

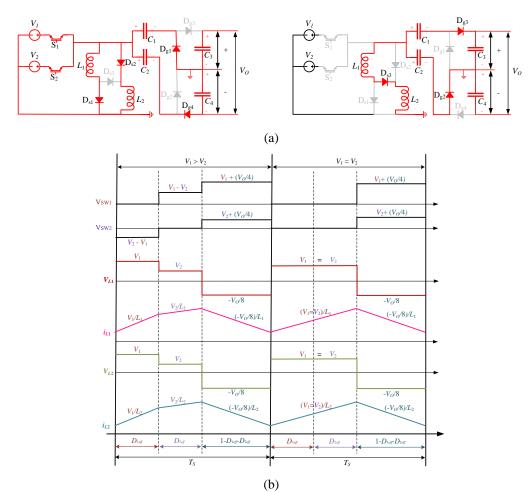

| Figure 3. 11: Flyback-based isolated MPC.                                                               | . 41 |

| Figure 3. 12: Path of current during $Lm$ (a) charging and (b) discharging for                          |      |

| simultaneous operation of a two-input configuration of $T_C$                                            | . 42 |

| Figure 3. 13: Steady state CCM waveform for the MIC with two inputs                                     | . 43 |

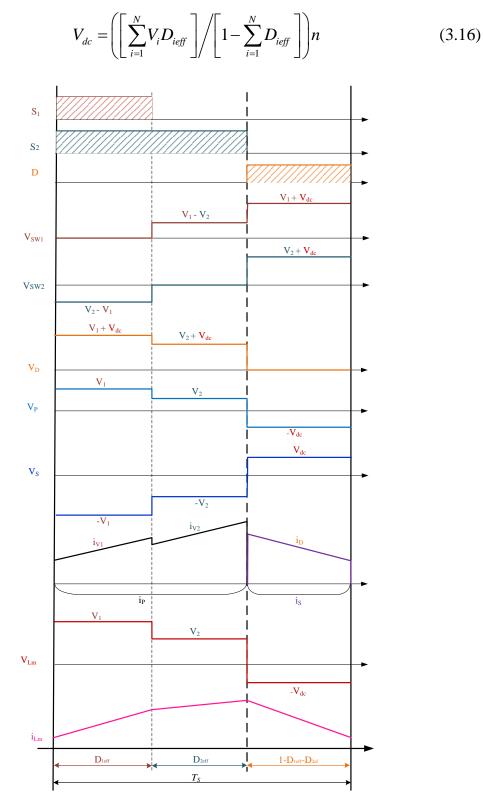

| Figure 3. 14: Steady state DCM waveform for the two inputs configuration                                |      |

| of $T_C$                                                                                                | . 44 |

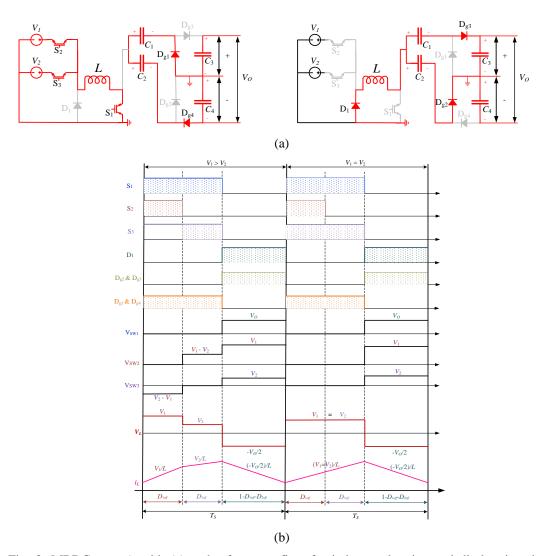

| Figure 3. 15: Schematic of $T_D$ with (a) $T_{D1}$ , (b) $T_{D2}$ , (c) $T_{D3}$ , (d) $T_{D4}$ and (e) |      |

| $T_{D5}$                                                                                                | . 46 |

| Figure 3. 16: $T_{D1}$ with (a) path of current flow for inductor charging and                          |      |

| discharging time, respectively, and (b) steady state CCM                                                |      |

| waveforms.                                                                                              | . 48 |

| Figure 3. 17: $T_{D2}$ with (a) path of current flow for inductor charging and                          |      |

| discharging time, respectively, and (b) steady state CCM                                                |      |

| waveforms.                                                                                              | . 49 |

| Figure 3. 18: $T_{D3}$ with (a) path of current flow for inductor charging and                          |      |

| discharging time respectively and (b) steady state CCM                                                  |      |

| waveforms.                                                                                              | . 50 |

| Figure 3. 19: $T_{D4}$ with (a) path of current flow for inductor charging and                          |      |

| discharging time respectively and (b) steady state CCM                                                  |      |

| waveforms.                                                                                              | . 51 |

| Figure 3. 20: $T_{D5}$ with (a) path of current flow for inductor charging and            |

|-------------------------------------------------------------------------------------------|

| discharging time, respectively and (b) steady state CCM                                   |

| waveforms                                                                                 |

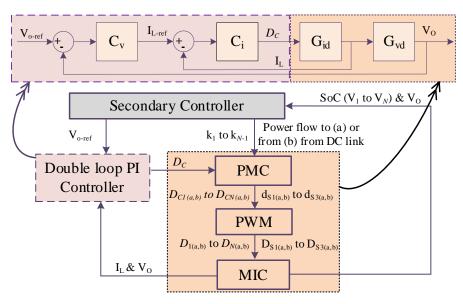

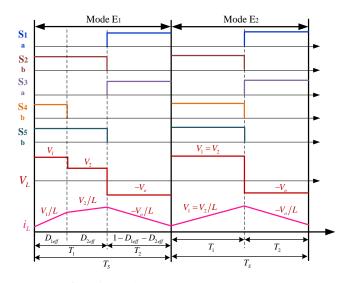

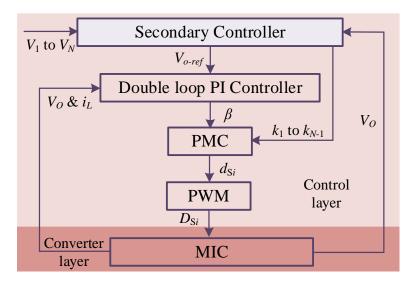

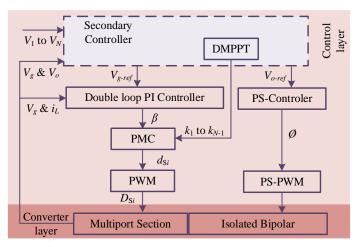

| Figure 3. 21: Control structure of the proposed family of MBDCs 53                        |

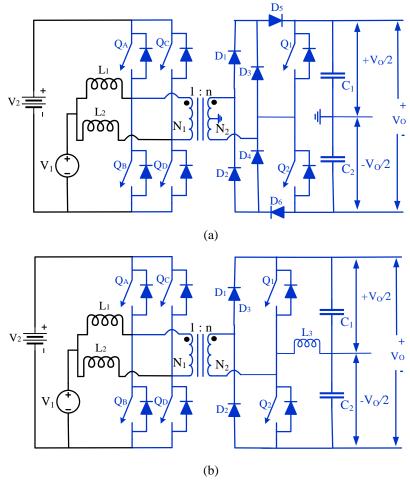

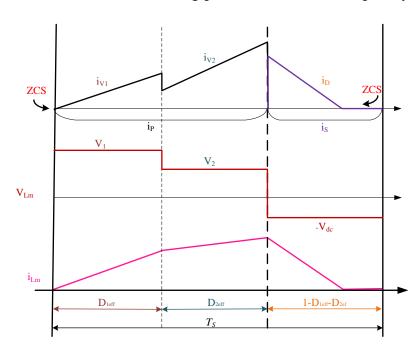

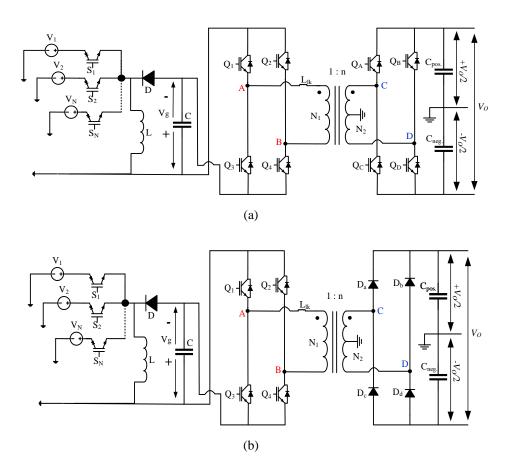

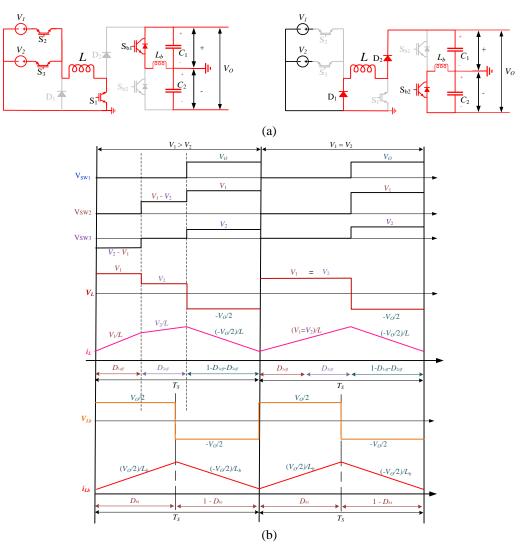

| Figure 3. 22: $T_E$ based on (a) dual-active-bridge and (b) full-bridge                   |

| converters 55                                                                             |

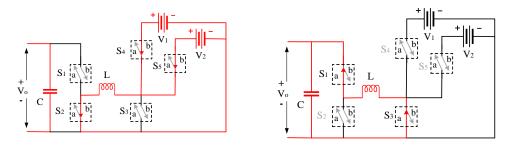

| Figure 3. 23: Path of current flow in in the multiport section during (a)                 |

| charging and (b) discharging of L, for simultaneous power flow                            |

| with two inputs57                                                                         |

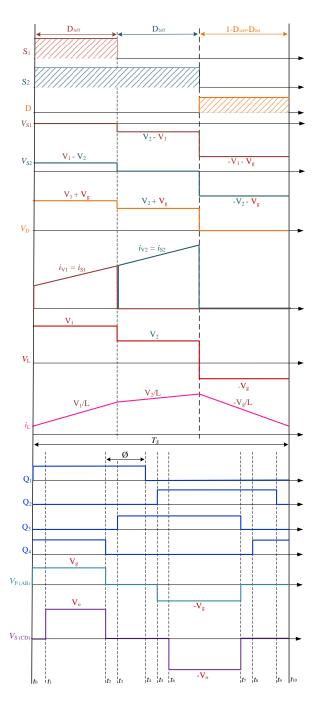

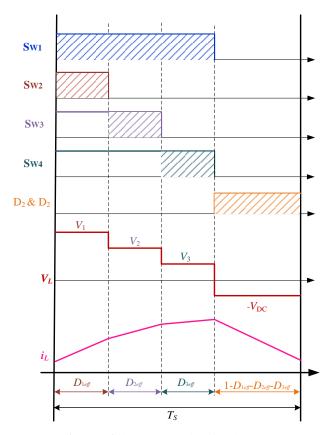

| Figure 3. 24: Steady state key waveforms of the phase-shifted full-bridge                 |

| based <i>T<sub>E</sub></i>                                                                |

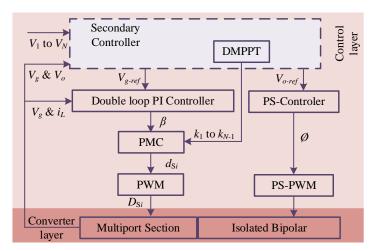

| Figure 3. 25: Control structure of $T_E$ .                                                |

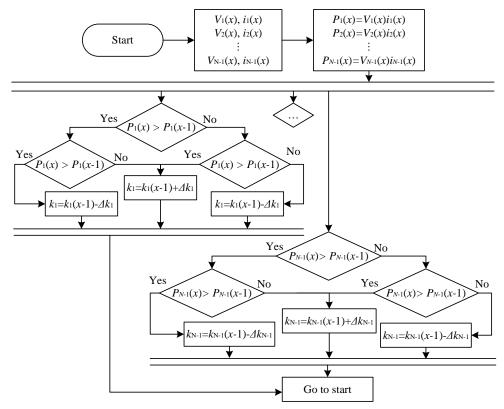

| Figure 3. 26: Flowchart of DMPPT controller of $T_E$                                      |

| Figure 3. 27: Schematic of bipolar to unipolar dc-dc converter for critical               |

| loads61                                                                                   |

| Figure 3. 28: Schematic of the integrated multiport converters system                     |

| Figure 3. 29: Path of current flow of the modified $T_A$ in steady state CCM              |

| under simultaneous power transfer for inductor charging and                               |

| discharging 63                                                                            |

| Figure 3. 30: Steady state CCM waveforms of the modified $T_A$ under                      |

| simultaneous power transfer from the three sources to the dc                              |

| link63                                                                                    |

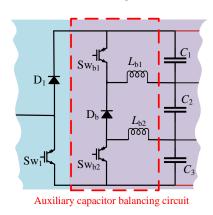

| Figure 3. 31: Schematic of the auxiliary circuit for capacitor balancing 64               |

| Figure 3. 32: Integrating $T_{D4}$ with the multilevel inverter proposed in [96] 65       |

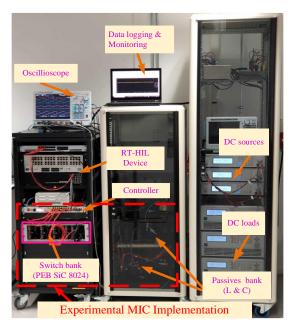

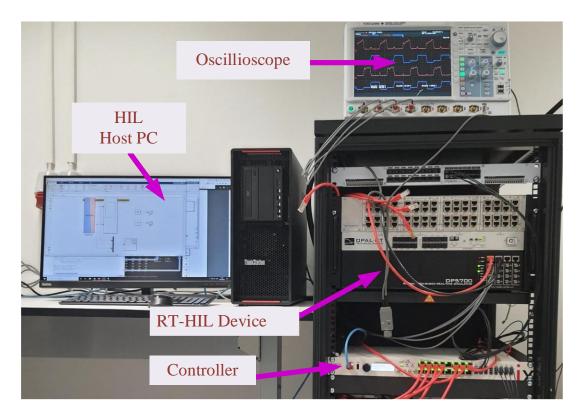

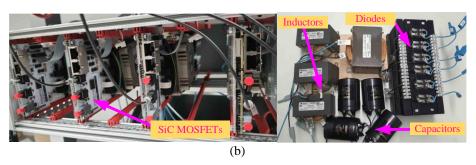

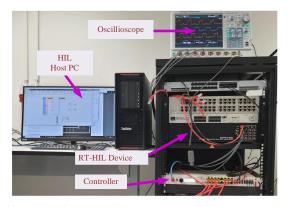

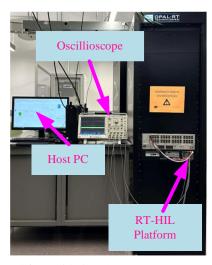

| Figure 4. 1: The in-house experimental and validation setups                              |

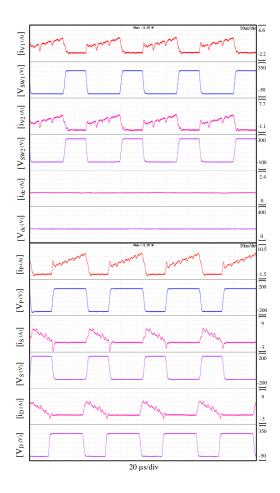

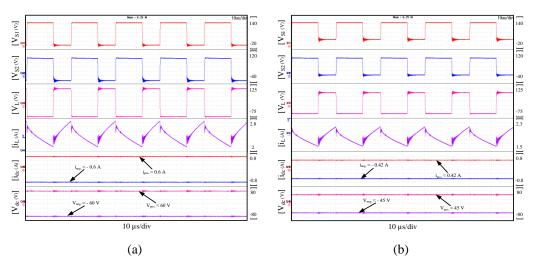

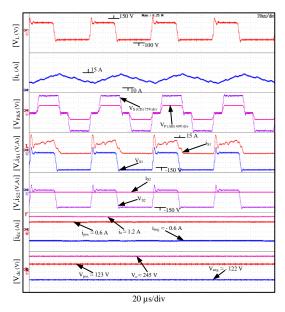

| Figure 4. 2: Experimental results with V1=300 V, V2=200 V, under 500W                     |

| load where VL & iL: inductor voltage & current, iO & VO:                                  |

| output current & voltage, and iS4, iS5, VS4 & VS5: S4 & S5                                |

| current & voltage, for (a) Mode A, $D_1$ =50% and $D_2$ =0 and (b)                        |

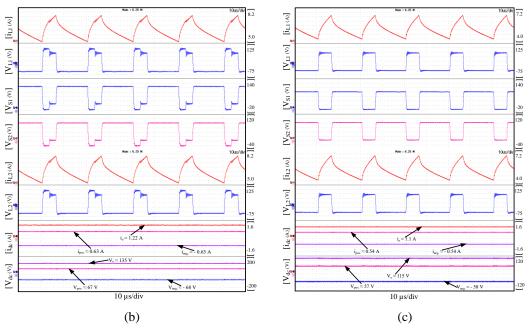

| Mode B, $D_1$ =0 and $D_2$ =50%71                                                         |

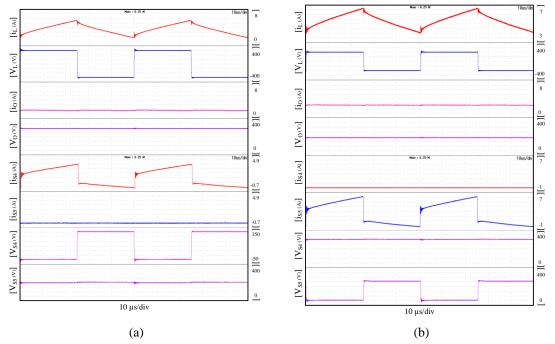

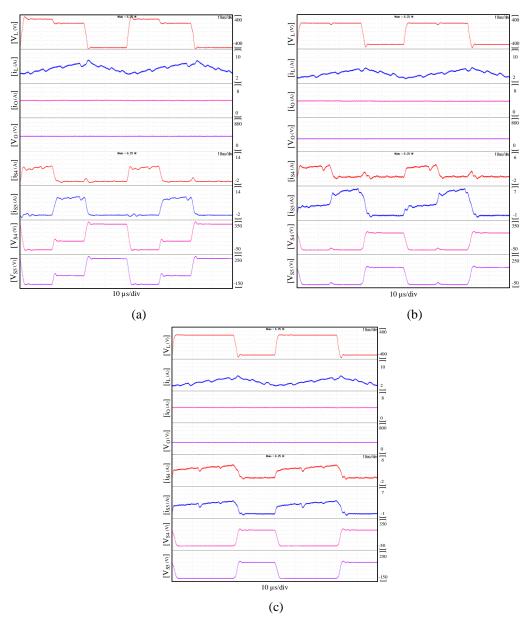

| Figure 4. 3: Mode E experimental results where VL & iL: inductor voltage &                |

| current, iO & VO: output current & voltage, and VS4 & VS5:                                |

| voltage of S <sub>4</sub> & S <sub>5</sub> , for (a) $V1=300$ V, $V2=200$ V, $D_1=30\%$ , |

| $D_2$ =60% and load=1.5 kW, (b) $V1$ = $V2$ =200 V, $D_1$ =30%,                           |

| $D_2=60\%$ and load=1 kW (c) V1=V2=200 V $D_1=D_2=60\%$                                   |

| and load=1 kW. $FSW = 20$ kHz in (a)–(c) while in (d)–(f)                                               |

|---------------------------------------------------------------------------------------------------------|

| $V1=300 \text{ V}, V2=200 \text{ V}, D_1=30\%, D_2=60\%$ and load=1 kW, but                             |

| <i>FSW</i> = 50kHz, 100kHz & 150kHz72                                                                   |

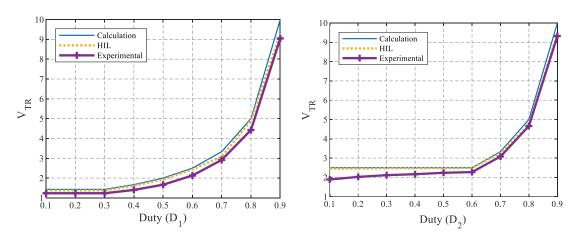

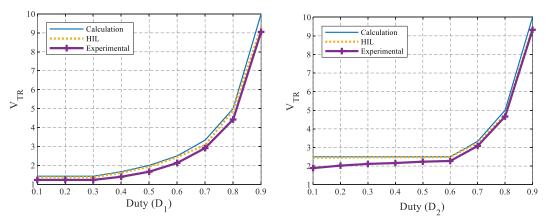

| Figure 4. 4: $VTR$ comparison in mode E, with $FSW$ =20kHz, $V_1$ =50 V, $V_2$ =25                      |

| $V, D_1=0.3 \text{ and } D_2=0.6.$ 73                                                                   |

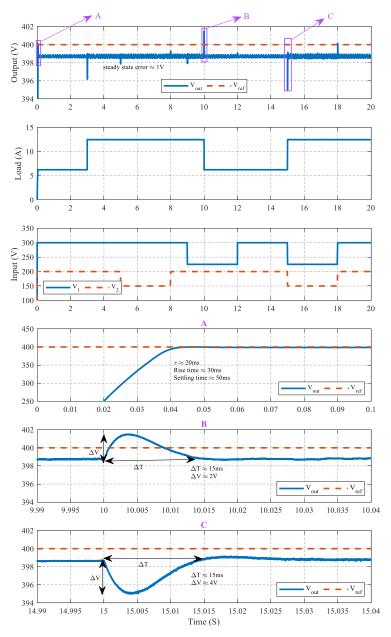

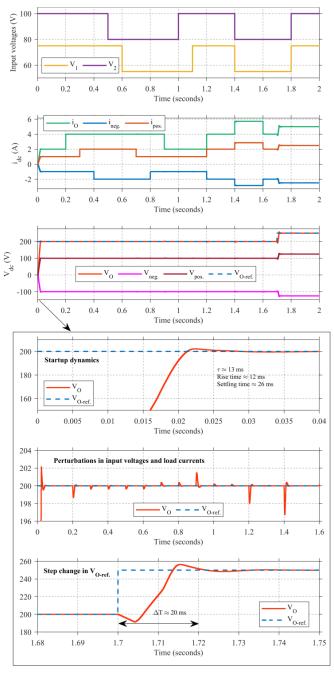

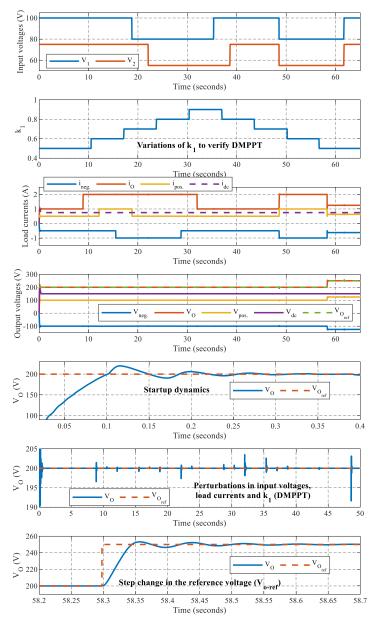

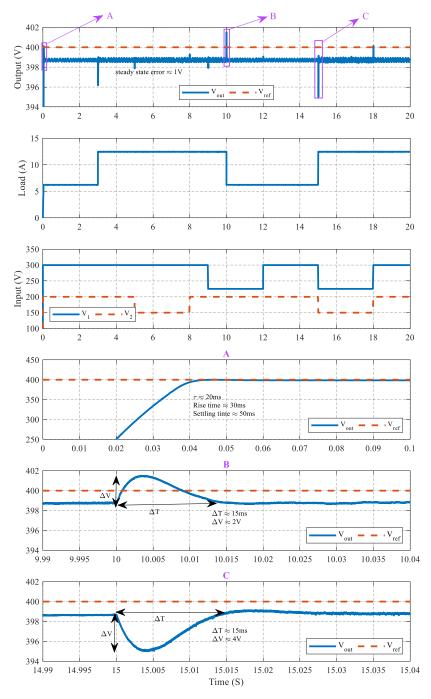

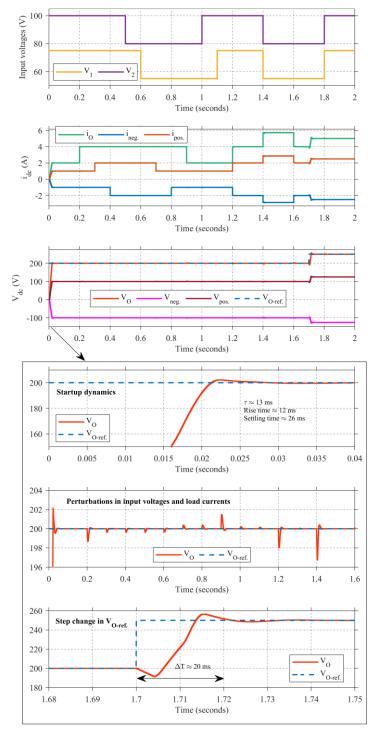

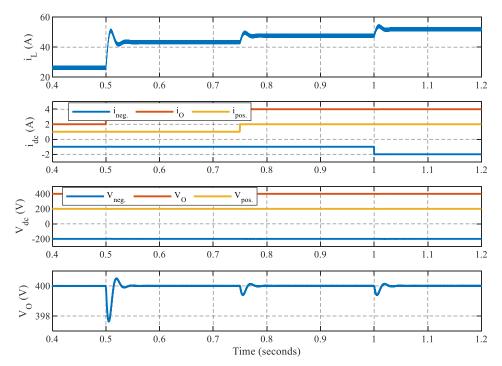

| Figure 4. 5: Closed loop performance under voltage and current                                          |

| perturbations74                                                                                         |

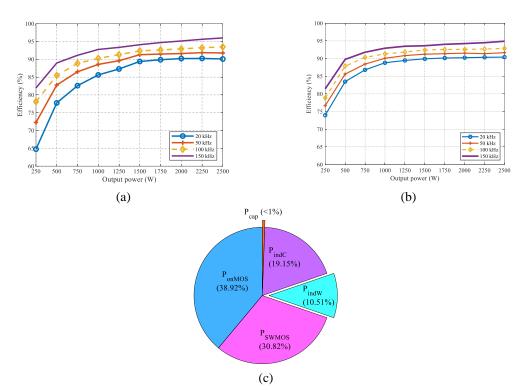

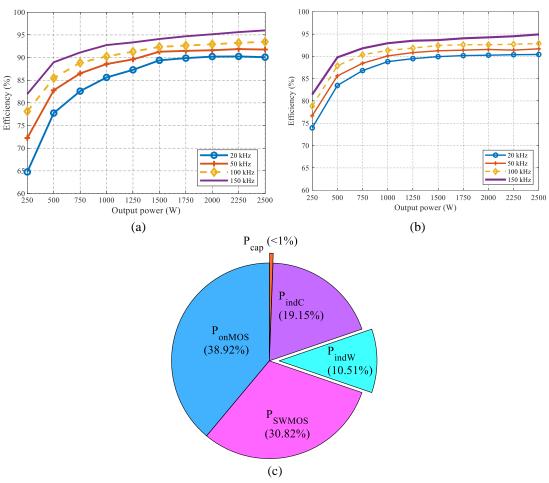

| Figure 4. 6: Experimental efficiency analysis of the MIC under varying FSW                              |

| for (a) $D_1 = 0.3$ , $D_2 = 0.6$ , $V_1 = 300 \text{ V } \& V_2 = 200 \text{ V}$ , (b) $D_1 =$         |

| $D_2 = 0.6 \& V_1 = V_2 = 200 \text{ V}$ and (c) theoretically obtained loss                            |

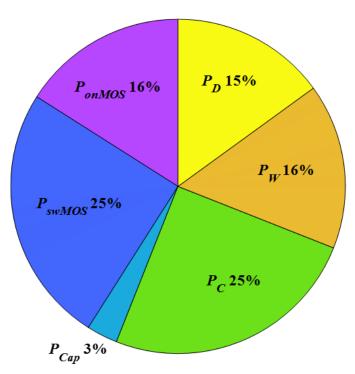

| distribution at 2.5 kW load and FSW=150 kHz75                                                           |

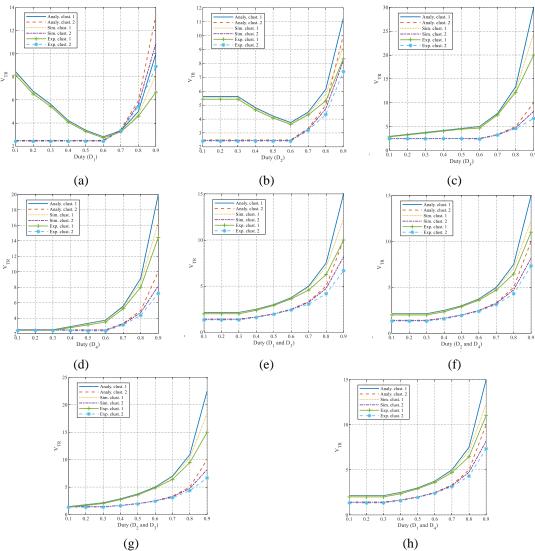

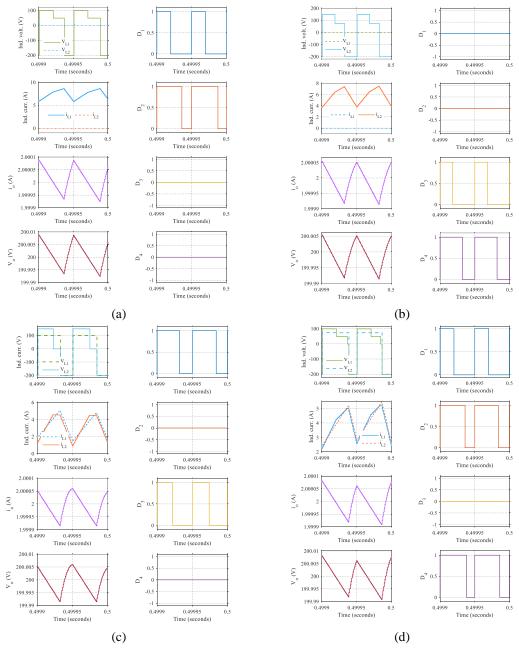

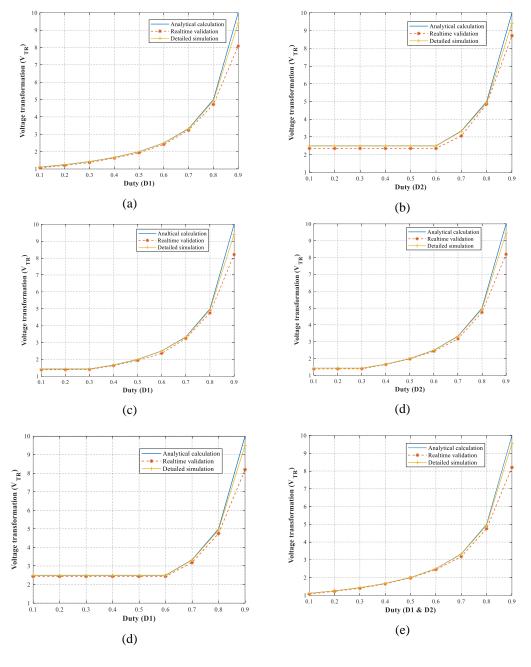

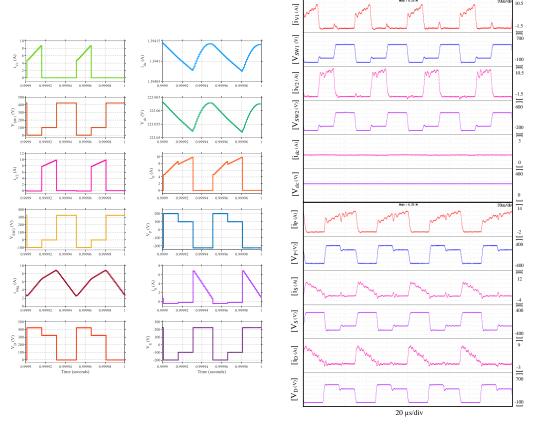

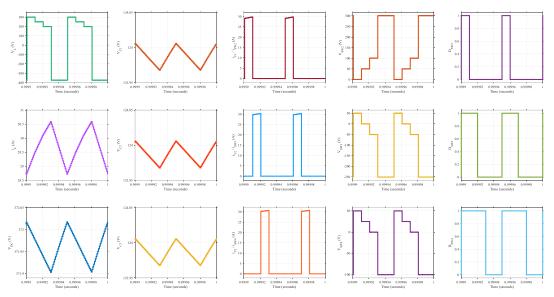

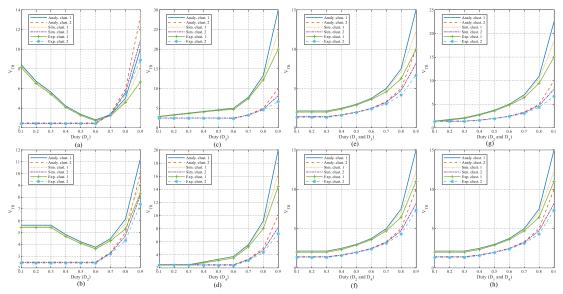

| Figure 4. 7: Verification of the MPC with the obtained <i>VTR</i> per cluster from                      |

| analytical calculation, detailed simulation, and HIL                                                    |

| experimental results for (a) $D_2=D_3=0.3$ , and $D_4=0.6$ , (b)                                        |

| $D_1=D_3=0.3$ , and $D_4=0.6$ , (c) $D_1=0.3$ , and $D_2=D_4=0.6$ , (d)                                 |

| $D_1=D_3=0.3$ and $D_2=0.6$ , (e) $D_1=D_3=0.3$ , (f) $D_2=D_4=0.3$ , (g)                               |

| $D_2=D_3=0.3$ and (h) $D_1=D_4=0.3$                                                                     |

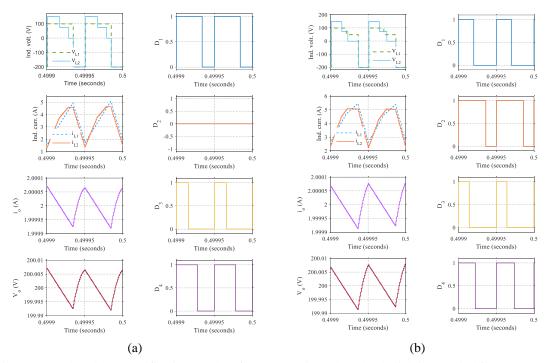

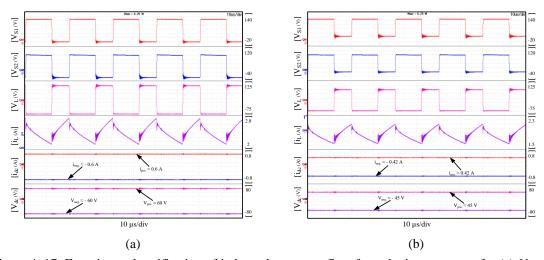

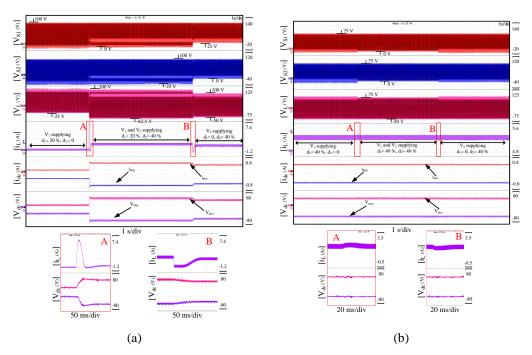

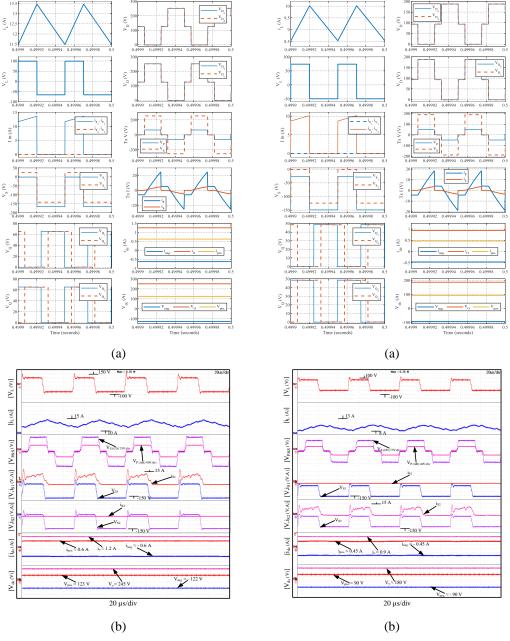

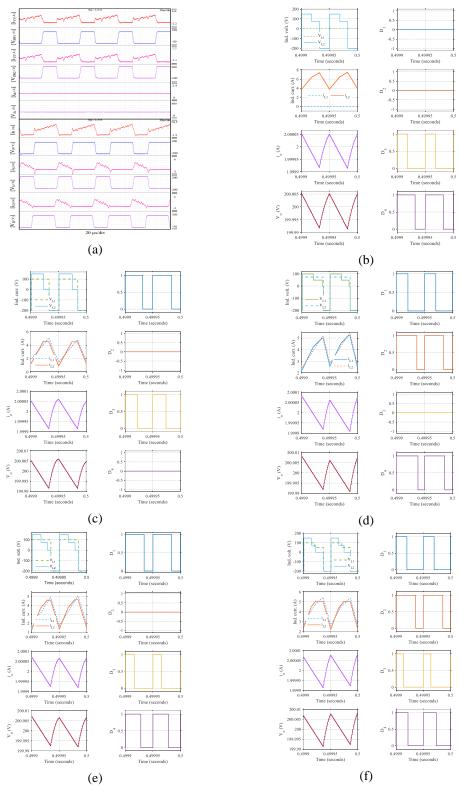

| Figure 4. 8: Closed loop verification results of the MPC operation when the                             |

| dc link is supplied form (a) $V_1$ and $V_2$ (b) $V_3$ and $V_4$ (c) $V_1$ and                          |

| $V_3$ and (d) $V_1$ , $V_2$ and $V_4$                                                                   |

| Figure 4. 9: Closed loop verification results of $T_B$ 's operation when the dc                         |

| link is supplied from (a) V <sub>1</sub> , V <sub>3</sub> and V <sub>4</sub> and (b) All four inputs.   |

| 79                                                                                                      |

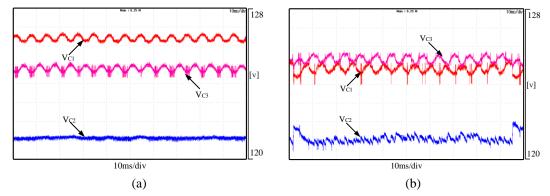

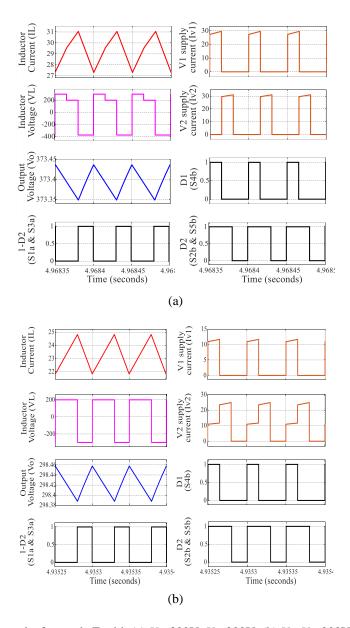

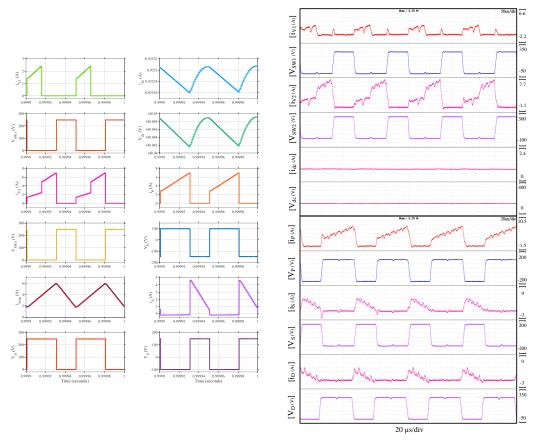

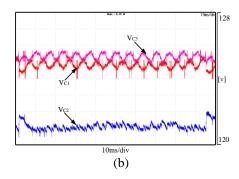

| Figure 4. 10: HIL results for $V_1$ =200 V, $V_2$ =100 V, $D_1$ =0.3 and $D_2$ =0.6 80                  |

| Figure 4. 11: HIL results for $V_1$ = $V_2$ =100 V, $D_1$ =0.3 and $D_2$ =0.6                           |

| Figure 4. 12: HIL results for $V_1$ = $V_2$ =100 V and $D_1$ = $D_2$ =0.6. 82                           |

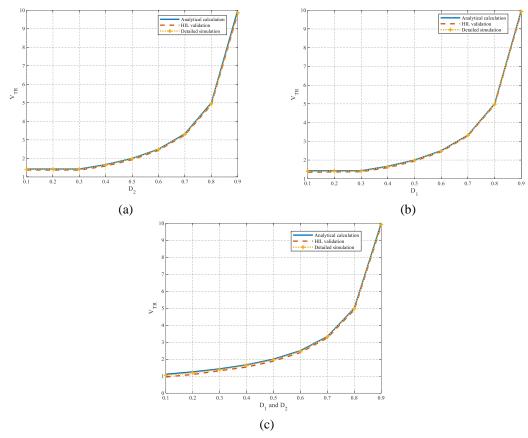

| Figure 4. 13: Obtained $V_{TR}$ where (a) $V_1 = 200 \text{ V}$ , $V_2 = 100 \text{ V}$ and $D_1 = 0.3$ |

| (b) $V_1 = V_2 = 100 \text{ V}$ and $D_2 = 0.3$ and (c) $V_1 = V_2 = 100 \text{ V}$                     |

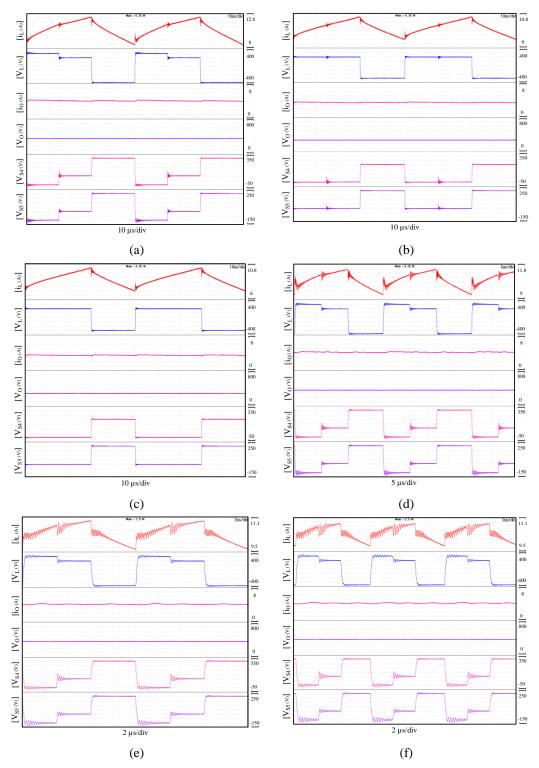

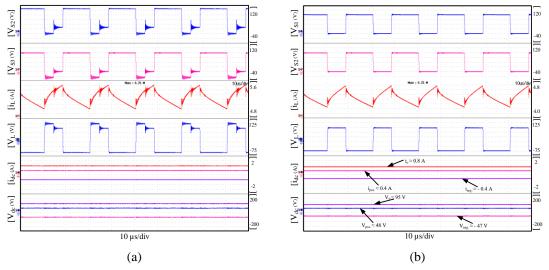

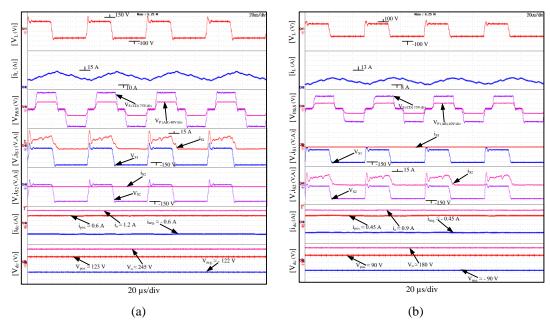

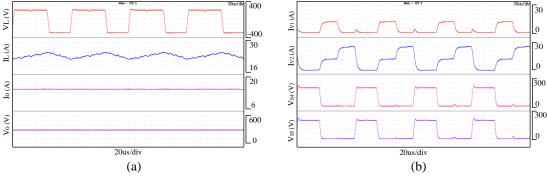

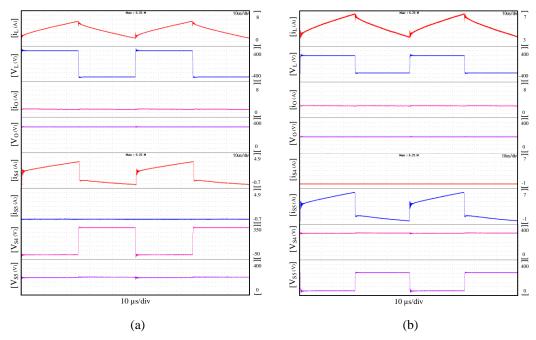

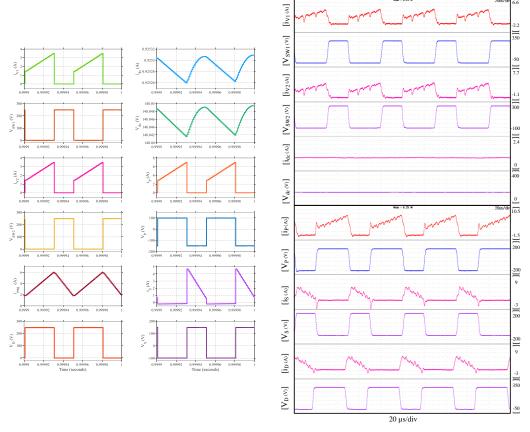

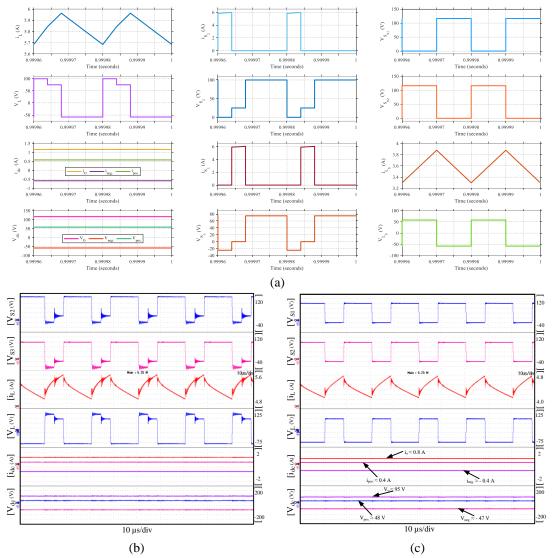

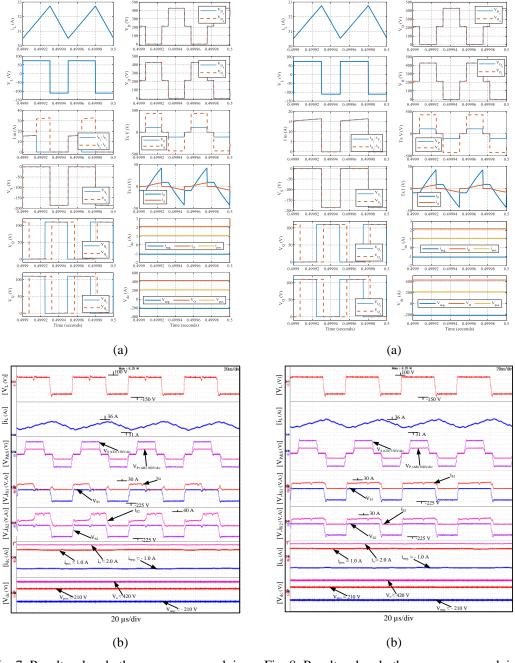

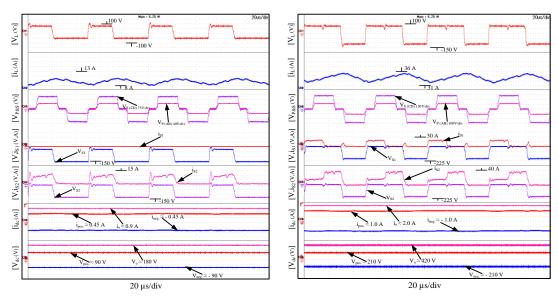

| Figure 4. 14: Verification results for operating $T_{D4}$ when (a) $V_1$ =100V,                         |

| $V_2$ =75V, $d_1$ =20% and $d_2$ =40% and (b) $V_1$ = $V_2$ =75V and $d_1$ =                            |

| $d_2 = 40\%$                                                                                            |

| Figure 4. 15: Experimental verification of $T_{D4}$ at high duty of $d_1$ =30% and                      |

| $d_2$ =60% for (a) $V_1$ =100V, $V_2$ =75V, and (b) $V_1$ = $V_2$ =75V85                                |

| Figure 4. 16:   | Verification results for operating $T_{D5}$ when (a) $V_1=100\text{V}$ ,                 |    |

|-----------------|------------------------------------------------------------------------------------------|----|

| 7               | $V_2 = 75V$ , $d_1 = 20\%$ and $d_2 = 40\%$ and (b) $V_1 = V_2 = 75V$ and $d_1 = 10\%$   |    |

| <i>a</i>        | <i>d</i> <sub>2</sub> =40%                                                               | 86 |

| Figure 4. 17: H | Experimental verification of independent power flow from the                             |    |

| i               | input sources for (a) $V_1$ only supplying when $V_1=100\text{V}$ ,                      |    |

| 1               | $V_2$ =75V, $d_1$ =40% and $d_2$ =0, and (b) $V_2$ only supplying when                   |    |

| 1               | $V_1$ =100V, $V_2$ =75V, $d_1$ =0 and $d_2$ =40%                                         | 87 |

| Figure 4. 18: I | Experimental verification of operating mode transition for (a)                           |    |

| 1               | $V_1=100 \text{ V}, V_2=75 \text{ V}, \text{ and (b) } V_1=V_2=75 \text{ V}.$            | 88 |

| Figure 4. 19: ' | Verification results for operating $T_{D4}$ under unbalanced loads                       |    |

| 7               | when $V_1=100\text{V}$ , $V_2=75\text{V}$ , $d_1=20\%$ and $d_2=40\%$ for (a)            |    |

| S               | simulation result, (b) experimental for $R_{pos.}=R_{neg.}=100\Omega$ , (c)              |    |

| $\epsilon$      | experimental for $R_{pos.}$ =50 $\Omega$ , $R_{neg.}$ =100 $\Omega$ and (d) experimental |    |

| f               | for $R_{pos}$ = 100 $\Omega$ , $R_{neg}$ =50 $\Omega$ .                                  | 88 |

| Figure 4. 20: C | Closed loop performance of $T_{D1}$ under perturbations in the input                     |    |

| 7               | voltages, load currents and output reference voltage                                     | 89 |

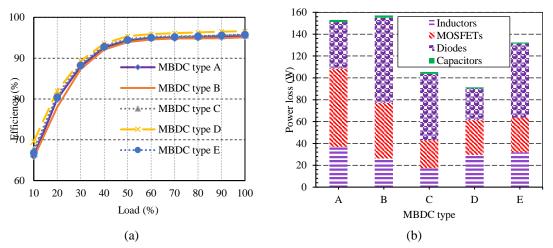

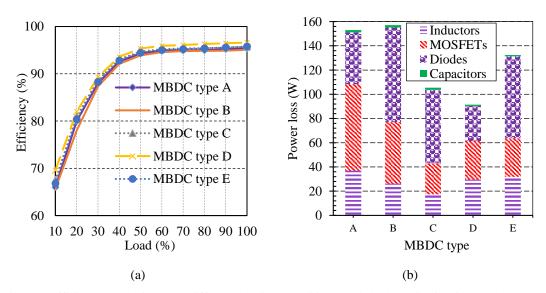

| Figure 4. 21: 1 | Efficiency analysis (a) at different loading conditions and (b)                          |    |

| 1               | loss distribution at 2 kW load with $V_O = 200$ V and $V_1 = V_2 =$                      |    |

| 1               | 100 V                                                                                    | 90 |

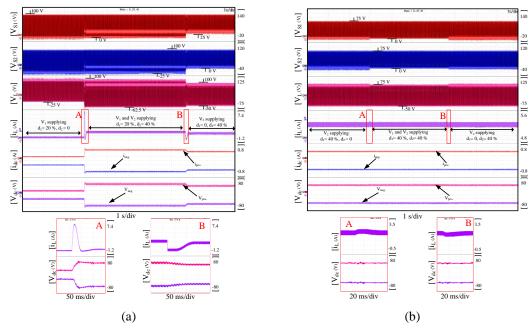

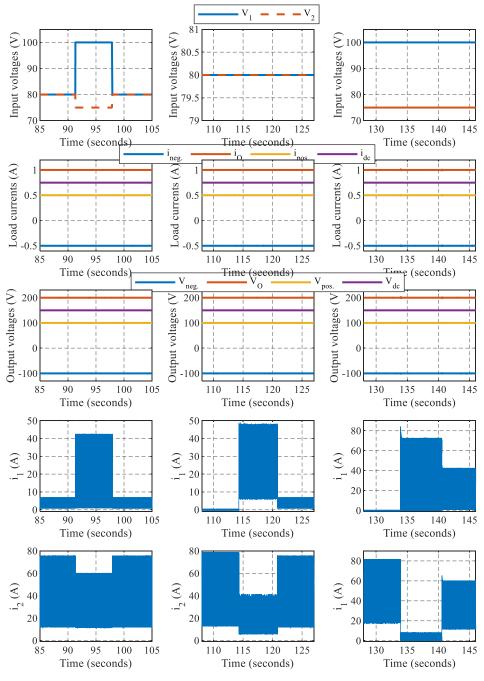

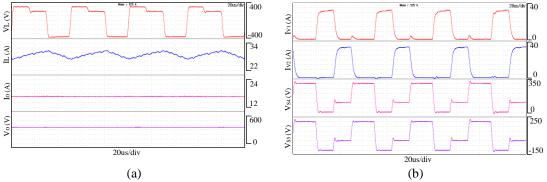

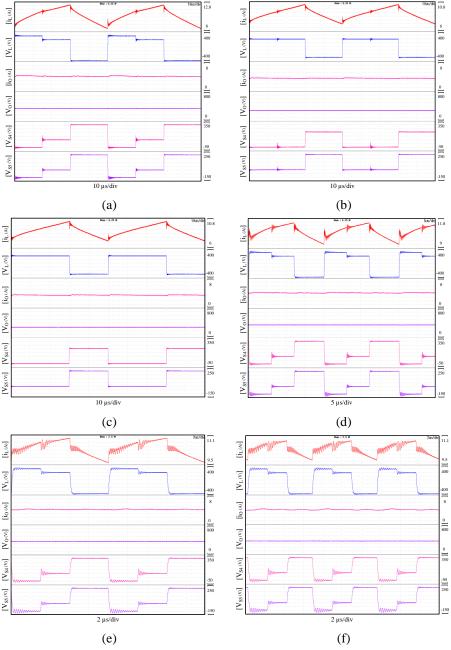

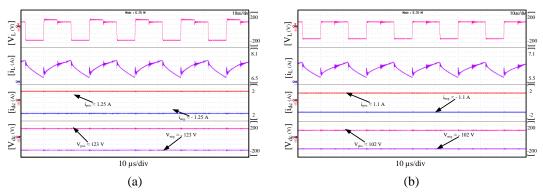

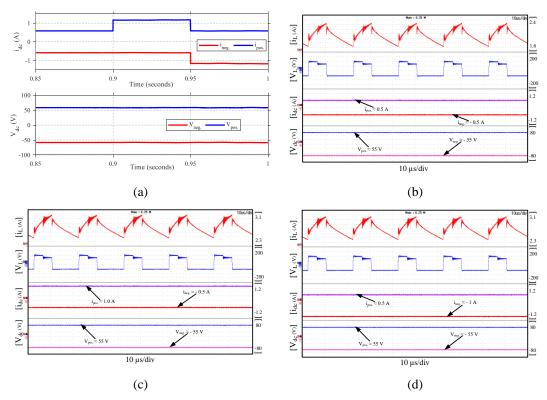

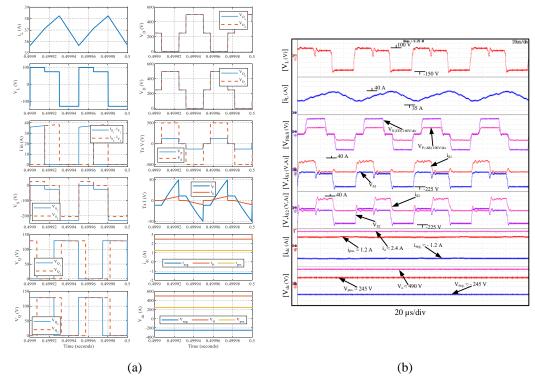

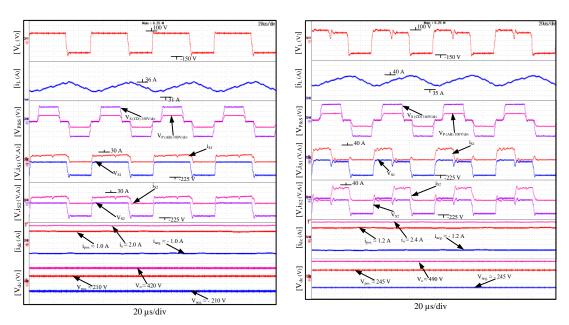

| Figure 4. 22: F | Results of supply to the dc bus where $V_1=100\text{V}$ , $V_2=75\text{V}$ , from        |    |

| (               | (a) only $V_1$ , thus $D_1$ =0.4 and $D_2$ =0 and (b) only $V_2$ thus $D_1$ =0           |    |

| 8               | and $D_2 \!\!=\!\! 0.4.$                                                                 | 92 |

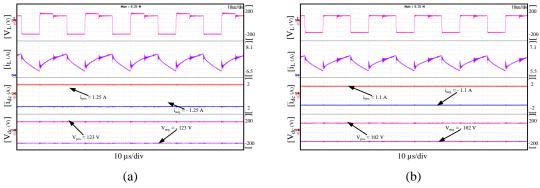

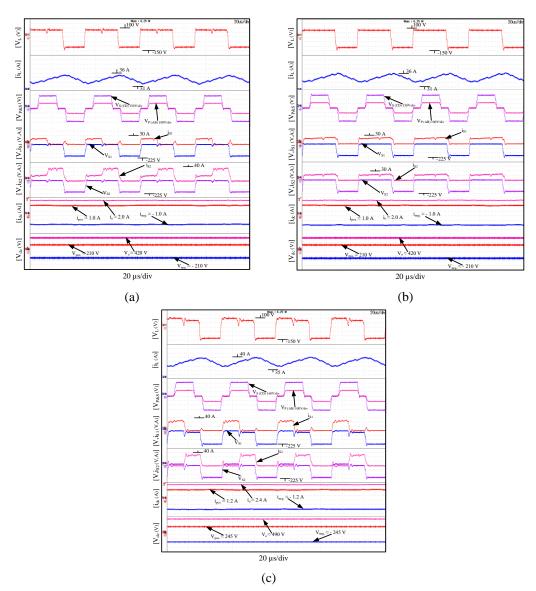

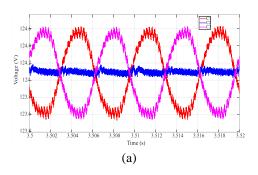

| Figure 4. 23: I | Results when both sources are supplying the dc bus where (a)                             |    |

| 1               | $V_1=V_2=75V$ , $D_1=0.3$ and $D_2=0.6$ , (b) $V_1=V_2=75V$ and                          |    |

| 1               | $D_1=D_2=0.6$ , and (c) $V_1=100$ V, $V_2=75$ V, $D_1=0.3$ and $D_2=0.6$                 | 93 |

| Figure 4. 24: C | Closed loop performance of the MIBDC under perturbations in                              |    |

| t               | the input voltages, load currents and output reference voltage                           | 94 |

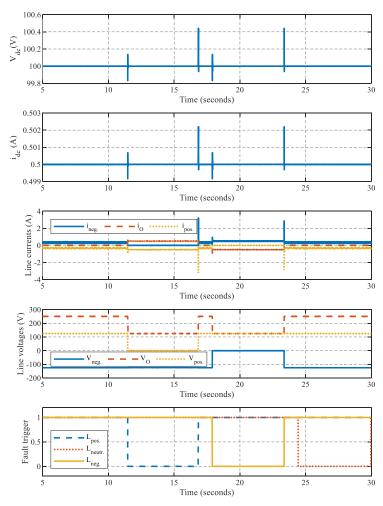

| Figure 4. 25: V | Verification of operating mode transitions.                                              | 95 |

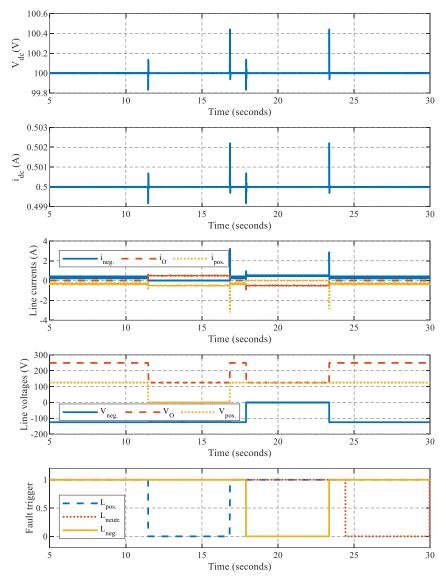

| Figure 4. 26: 0 | Closed loop performance under line failures                                              | 96 |

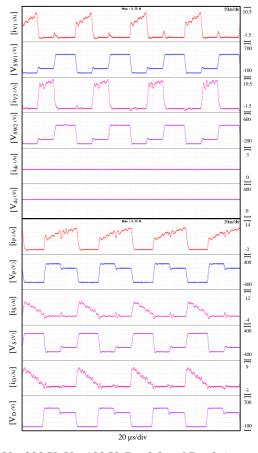

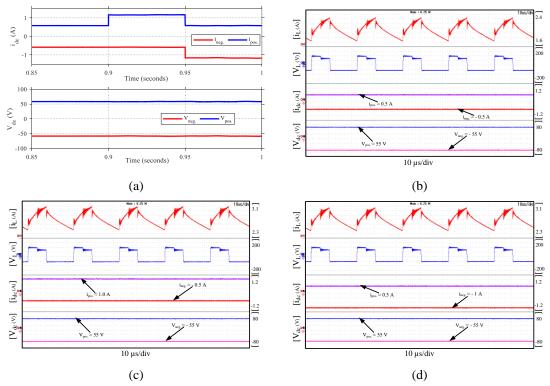

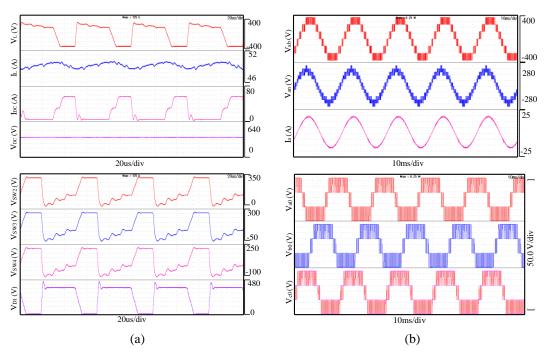

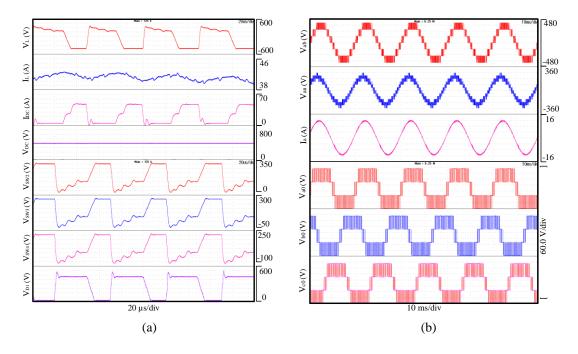

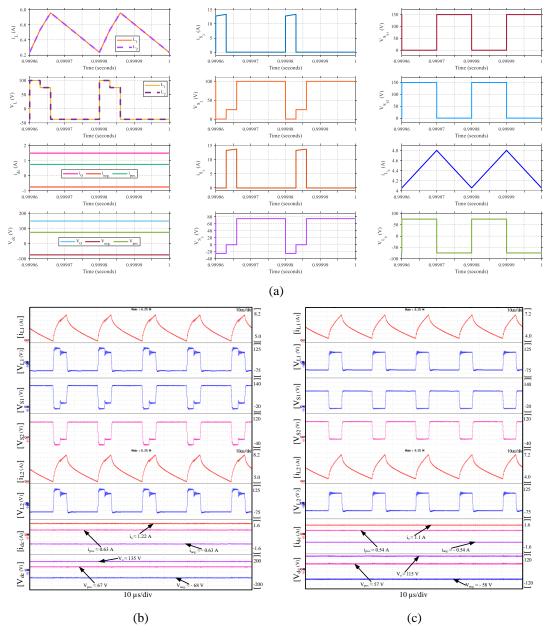

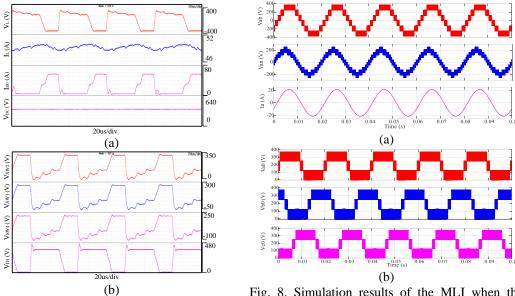

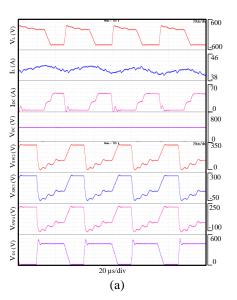

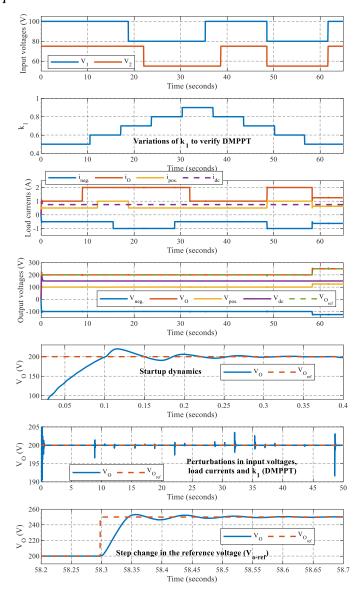

| Figure 4. 27: C | Open loop HIL implementation results showing key waveforms                               |    |

| (               | of the integrated MPC-MLI operation when $D_1 = 20\%$ , $D_2 =$                          |    |

| 4               | 40% and $D_3 = 60\%$ for (a) MPC operation and (b) MLI                                   |    |

| (               | operation                                                                                | 97 |

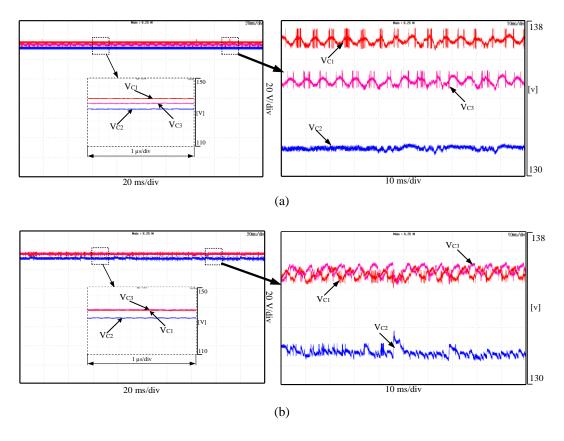

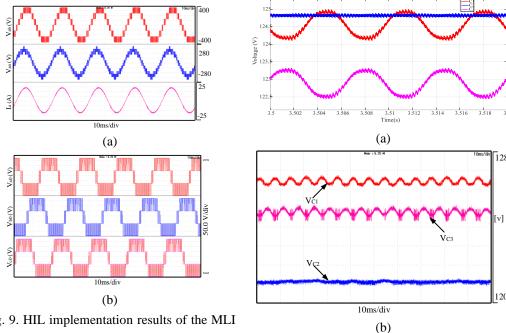

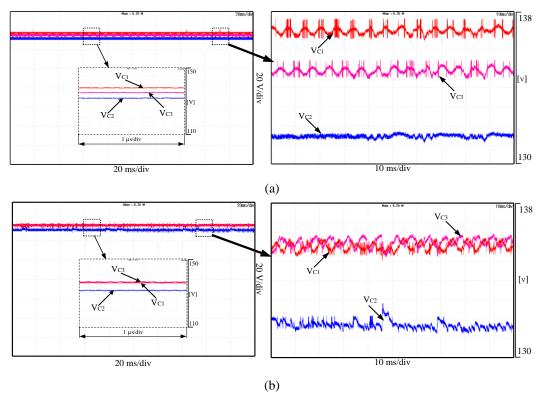

| Figure 4. 28: I | Results of dc link capacitor voltage balancing for (a) control-                          |    |

| 1               | pased and (b) auxiliary circuit-based techniques.                                        | 99 |

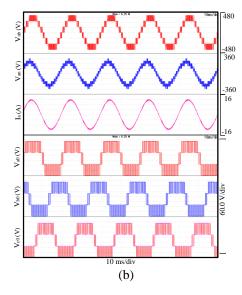

| Figure 4. 29: Closed loop implementation results showing (a) key waveforms     |    |

|--------------------------------------------------------------------------------|----|

| of the MPC operation and (b) output current and voltage                        |    |

| waveforms and the pole voltages9                                               | 19 |

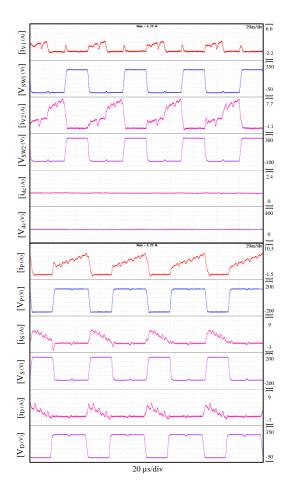

| Figure 4. 30: Results under closed operation of the MPC for (a) control-based  |    |

| and (b) auxiliary circuit-based dc link capacitor voltage                      |    |

| balancing 10                                                                   | 0  |

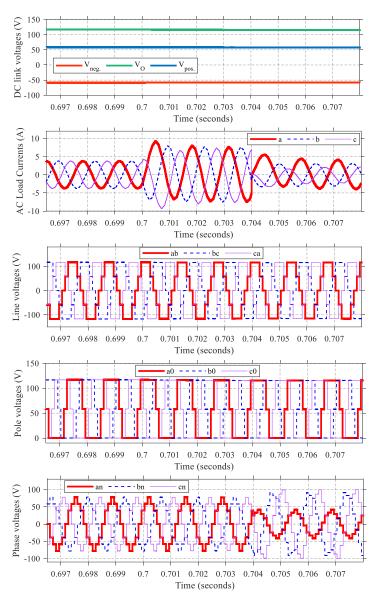

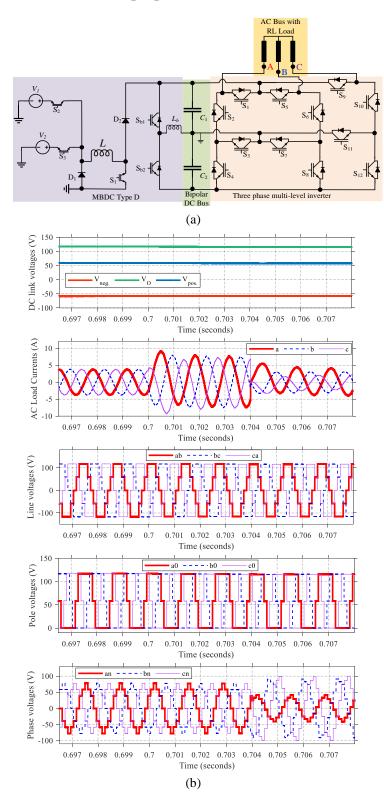

| Figure 4. 31: Results of integrating $T_{D4}$ with the MLI in [96] showing the |    |

| bipolar DC link voltages and the ac stage voltages and current                 |    |

| under different load conditions                                                | )1 |

## **List of Tables**

| Table 3. 1: Parameter scaling by the PMC and PWM                              | . 33 |

|-------------------------------------------------------------------------------|------|

| Table 3. 2: Switching pattern for the different modes of operation            | . 36 |

| Table 3. 3: Conduction of devices in the bipolar to unipolar dc-dc converter  |      |

| for critical power transmission and distribution                              | . 61 |

| Table 4. 1: Parameters used in the validation of $T_A$                        | . 70 |

| Table 4. 2: Parameters used in the validation of $T_B$                        | . 76 |

| Table 4. 3: Parameters used in the validation of $T_C$                        | . 80 |

| Table 4. 4: Parameters used in the validation of $T_D$                        | . 83 |

| Table 4. 5: Parameters used in the validation of $T_E$                        | . 91 |

| Table 4. 6: Parameters used in system verification.                           | . 97 |

| Table 4. 7: Comparison of $T_A$ and $T_B$ with existing non-isolated unipolar |      |

| MPCs                                                                          | 102  |

| Table 4. 8: Comparison of $T_C$ with existing isolated unipolar MPCs          | 103  |

| Table 4. 9: Comparison of the $T_D$ with existing non-isolated bipolar MPCs   | 104  |

| Table 4. 10: Comparison of $T_E$ with existing isolated bipolar MPCs          | 105  |

#### List of Abbreviations and Symbols

AC alternating current

BDC bipolar dc-dc converter

BDCG bipolar dc grid

CCM continuous conduction mode

CMV common-mode voltage

D duty cycle

DAB dual active bridge

DC direct current

DCM discontinuous conduction mode

$D_{ieff}$  effective duty of i

DMPPT distributed maximum power point tracking

EMI electromagnetic interference ESR equivalent series resistance

ESS energy storage system

EV electric vehicle

FB full bridge

FBS fully-controllable bidirectional switch

F<sub>SW</sub> switching frequency

GaN gallium nitride

GVD greinacher voltage doubler

HB H-bridge

HIL hardware-in-the-loop

HVDC high voltage dc

IEA international energy agency

IEEE institute of electrical and electronics engineers

IGBT insulated-gate bipolar transistor

$i_L$  inductor current  $i_L$  inductor current  $i_o$  output current

IPF independent power flow  $L_m$  magnetizing inductance

MBDC multiport non-isolated dc-dc converter with bipolar outputs

MIBDC multiport isolated dc-dc converter with bipolar outputs

MIMO multiple input multiple output

MISO multiple input single output

MLI multilevel inverter

MOSFET metal-oxide-semiconductor field-effect transistor

MPC multiport dc-dc converter

MPPT maximum power point tracking

nturns ratio $N_1$ primary turns $N_2$ secondary turns $\emptyset$ phase shift

P&O perturb and observe

PC personal computer

Pcap capacitor losses

PCS pulsating current source PI proportional integral

P<sub>indC</sub> core losses

P<sub>indw</sub> winding losses

P<sub>L</sub> power losses

PMC power management control

PonMOS MOSFET conduction losses

PS phase shift PV photovoltaic

PVS pulsating voltage source PWM pulse width modulation

RB reverse blocking  $R_{DSon}$  on-state resistance

RES renewable energy source

SBC synchronous buck converter

SiC silicon carbide

SISO single input single output

SoC state of charge

SPF simultaneous power flow

$T_A$  topology A  $T_B$  topology B  $T_C$  topology C  $T_D$  topology D  $T_E$  topology E

THD total harmonic distortion

$\begin{array}{ll} t_{off} & & \text{off time} \\ t_{on} & & \text{on time} \end{array}$

Ts switching period UDCG unipolar dc grid

VCS variable carrier scheme

$V_{dc}$  dc link current  $V_{dc}$  dc link voltage  $V_o$  output voltage

$V_{o\text{-ref}}$  output voltage reference  $V_{TR}$  voltage transformation ZCS zero current switch ZVS zero voltage switch

## Chapter 1

### 1 Introduction

#### 1.1 Background

Despite the decreasing world population growth rate over the years, the human population on planet earth has continued to grow, reaching over eight (8) billion people so far [1]. This growing population coupled with a drastic increase in industrialisation on a massive scale, has brought about huge demands for energy. The international energy agency (IEA) projects a 25% increase in the global primary energy demand between the years 2017 and 2040. It is also predicted that if no further improvement occurs in energy efficiency, it could lead to a 50% increase in energy demands [2]. This rather radical increase in energy demand alongside the damaging effects of climate change and degradation of planet earth has resulted in an aggressive exploitation of non-renewable and pollutant sources of energy over the years. To combat the detrimental effects of man's long-standing pollution of the environment and attempt to attain a state of balance and environmental purity on planet earth, there has been a rise in the utilisation of renewable energy sources. Although the supply of energy from renewable energy sources (RESs) to the energy supply mix continues to grow to reach this state of balance and purity in the energy cycle, there needs to be a consistent increase in the efficiency of energy generation, supply, and utilisation. These needs define the drive of the power, energy, and electronics industry [3].

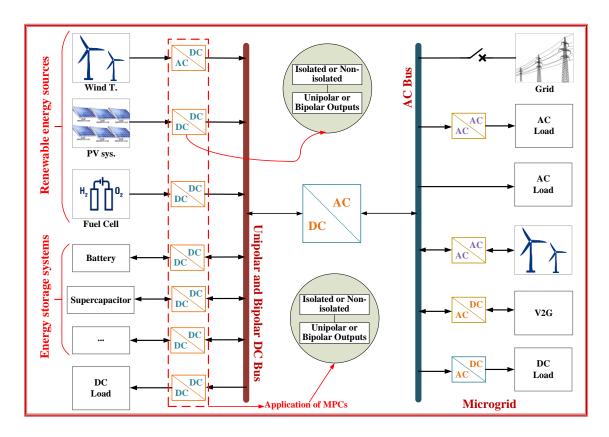

Due to the intermittent nature of many RESs, energy storage presents a huge opportunity in the advancement towards renewable or green energy solutions. To this end, hybridisation of energy sources and storages through power electronic converters, as illustrated in Figure 1.1, has been the theme of a lot of research [4]. Therefore, it is an effective and economic solution towards improving the performance of RESs. The application of hybridised energy systems cannot be overemphasized as they find relevance in a wide area of applications, ranging from dc micro grids, energy storage backup for communication systems to electric vehicles (EVs) of any kind. Especially, since all-electric hybrid energy systems have played a key role in microgrids [5] and zero-emission transportations, e.g in

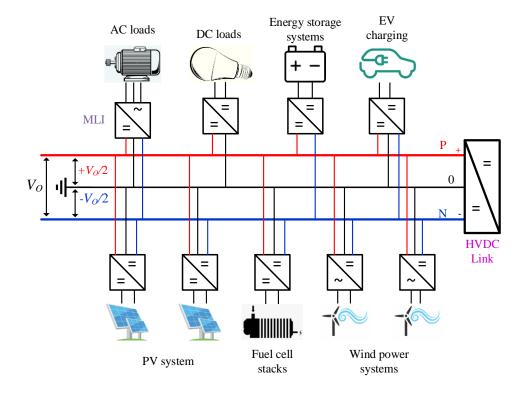

ferry boats [6], EVs [7]. Hybridization in electric energy systems requires a simultaneous power flow of several electric energy sources, and bidirectional operations are strictly required in such systems equipped with energy storage. Further, distributed RE generation systems are the backbone of future power systems, which are mainly based on dc microgrids, since they have no issue with reactive power and synchronisation beside advantages like lower losses and less conductor material, as compared to the ac microgrids [8-10]. Three-wire dc bus grid systems, called bipolar dc grids (BDCG) are also fast gaining popularity since they have been recently implemented in telecommunication systems, EVs and marine vessel charging, data centres and high voltage dc (HVDC) transmission and distribution systems [11–13]. This fast adoption is due to the higher efficiency because to transmit the same power, the current is smaller in BDCGs than in unipolar dc grids (UDCGs). The reliability of BDCGs is also higher than that of UDCGs because when one of the poles fails, the other pole can continue to transmit power with reduced capacity. Further, BDCGs offer an easier and better-quality conversion from dc to ac voltage using multilevel inverters (MLIs), due to the three voltage levels  $(\pm \frac{V_0}{2})$  and  $(\pm \frac{V_0}{2})$  while UDCGs offer only one voltage level. With the increasing penetration of multiple RESs, which are intermittent in nature, power electronic converters have gained popularity for effective energy utilization [14]. Power electronic converters can be categorized based on their application in four main groups namely, dc-ac, ac-dc, ac-ac and dc-ac converters and can be either isolated or non-isolated based on the feature of magnetic isolation or lack thereof [15]. However, among the others, dc-dc converters (e.g. buck, boost, buck-boost and full-bridge converters etc.) have been widely used to convert the different voltage levels of several dc sources to a standard operating voltage in dc microgrids [16]. Further, with the attractive features of BDCGs and UDCGs, RESs and dc loads can be more easily integrated by dc-dc converters [17] as shown in Figure 1.1. However, many sources and loads have different voltage levels, requiring many single-input single-output (SISO) dc-dc converters to step-up or step-down the voltage to or from the dc bus. Consequently, bulky and complex configurations, as well as high component count and cost, amidst global semiconductor chip shortages are the major reluctances of using SISO dc-dc converters in energy source and storage hybridization systems [18, 19].

Figure 1. 1: Schematic overview of a hybrid energy system with multiple sources, storages and loads enabled by power electronic converters.

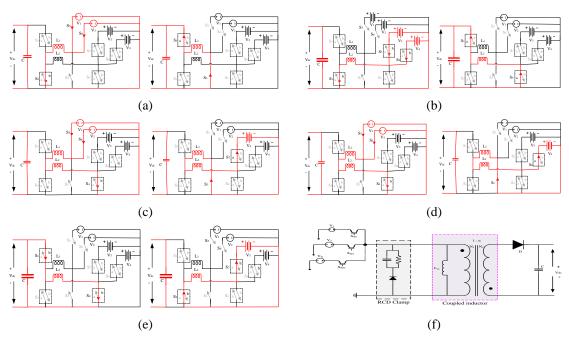

Multiport dc-dc converters (MPCs), which are generally derived from conventional SISO converters with a goal of sharing as much components as possible between the input ports of the MPCs [20, 21], have lately been offered as a solution to the mentioned problems in SISO dc-dc converters [22–25]. To this end, a lot of research has gone into proposing several MPCs isolated (with galvanic) and non-isolated (without galvanic) isolation. The isolated MPCs are based on magnetically connected circuits (through transformers or coupled inductors) while the non-isolated MPCs are based on electrically connected circuits [15]. Due to the magnetic separation of input and output given by the magnetic components, isolated MPCs have significant features of soft switching ability, high gain, and safety over non-isolated MPCs [22, 23]. Several isolated MPCs have been proposed, but their common limitation is the use of multiple windings for the inputs of the transformers or coupled inductors based on flux additivity [22, 23, 26–28]. This leads to reduced power density, increased size, and control complexity since the phase-shifted pulse width modulation (PS-PWM) control is required to achieve simultaneous power transfer from the input sources in certain cases. Further, since multiple windings are required at the primary side

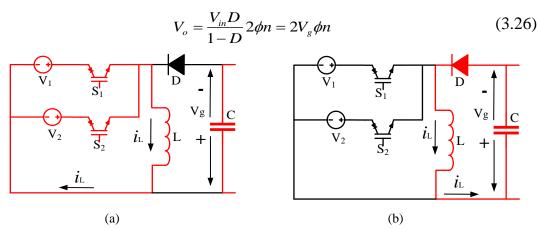

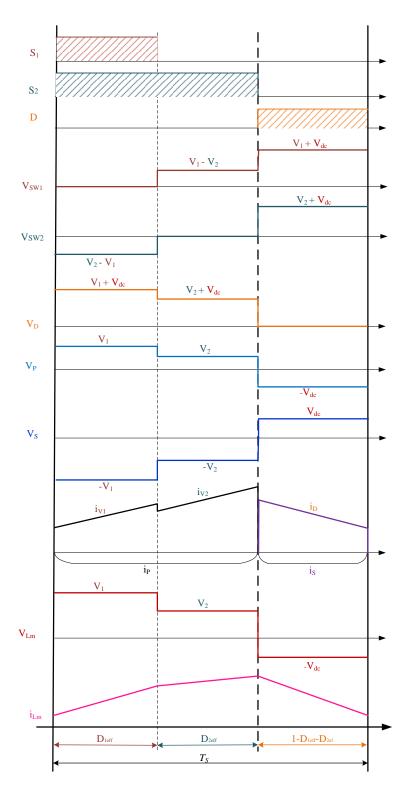

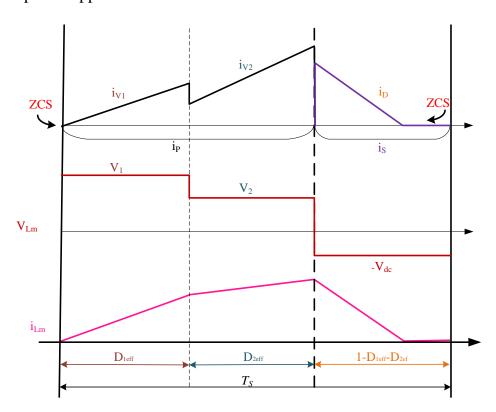

of the magnetics for the input sources, and multiple clamping circuits will also be required, thus further increasing component count and potentially control complexity if any active clamping is to be applied. To mitigate these issues, isolated MPCs with only two windings, one primary and secondary each, have been proposed in [24, 25, 29, 30]. However, these MPCs also suffer from high component count with some requiring multiple inductors and capacitors at each input [29]. Bulky structure and complex control restrict the isolated MPCs from hybrid energy systems, which do not require an isolation feature. The non-isolated MPCs have features of reduced size, cost, and ease of miniaturization [31]. These features allow non-isolated MPCs to gain popularity over isolated counterparts in hybrid energy systems with extensive developments in recent years [32–42]. MPCs can also be either multi output or single output topologies. In [23, 24, 34, 35, 40, 42], MPCs with multiple-inputs and single-outputs (MISO) have been proposed for RES integration with features such as reduced component count and simplified control strategy, but they are all unsuitable for BDCG systems because they have only one output port. To overcome this, isolated and non-isolated MPCs with multiple inputs and outputs (MIMO) have been proposed in [43–46]. However, these MIMO MPCs must deal with cross-regulation of the voltage at the output ports, requiring complex controllers to suppress this problem. This problem birthed the need for bipolar dc-dc converters (BDCs), which typically have only two symmetrical outputs, one for each pole (positive and negative), respectively. To resolve this, multiport BDCs have been proposed recently in [47–50]. However, these multiport BDCs have some disadvantages such as: they cannot allow for an arbitrary independent power flow from either of the input sources to the bipolar dc bus, aside the requirement for complex control to achieve balanced symmetric output voltages, significant component count, limitation on number of inputs and low voltage gain. These disadvantages underline the demand for novel multiport BDCs to fill the need. Furthermore, compared to their unipolar counterparts, fewer MPCs with bipolar symmetric outputs have been proposed in literature.

Summarily, despite of the plethora of research in this field, there is still a gap to be filled in energy system hybridization and the implementation of MPCs with both unipolar and bipolar outputs for hybrid energy system applications. The opportunities to develop new MPCs using the latest technological developments in power electronics for application in grid integration are abundant.

#### 1.2 Motivation and research problem

Opportunities for further developments in MPCs, which are largely classified based on the galvanic isolation (that is, the isolated and non-isolated topologies) with either unipolar or bipolar outputs, can be summarized around three key areas. Firstly, in component count, there is a need to further increase the number of components shared by the input ports of the MPCs. An increase in this metric reduces the overall component count and potentially increases the power density of the MPC and the efficiency of conversion as well as that of the converter. Secondly, the control of power sharing among the inputs to the respective MPC, especially during simultaneous power transfer from the inputs to the dc link has received less attention over the years. Lastly, there is more room to propose new MPCs, which have desirable performance and operational characteristics and still possess the attractive feature of high voltage gain. Particularly, in the isolated MPC topologies, the need to propose new MPCs, whose inputs can be arbitrarily increased, without modifications to the core of the magnetic component utilized in achieving galvanic isolation, is noteworthy. In the non-isolated counterparts, which are usually characterized by low voltage gain, there is need to explore the possibilities of increasing the voltage gain through novel MPC topologies, while also retaining the characteristic of low component count. Further, the MPCs with bipolar symmetric outputs have a longstanding challenge of maintaining the symmetry of the bipolar outputs under disturbances in the output voltage or/and loads. Thus, the need for implementation of less complex control strategies to maintain balanced bipolar output voltage or natural output voltage symmetry with low component count, cannot be overemphasized. These issues give rise to the need for this research.

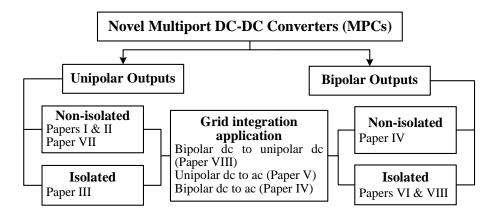

#### 1.3 Contributions of the dissertation

The scientific contributions of this dissertation are highlighted in this section and are based on three IEEE journal papers (two published and one under review) and five conference papers (four published and one accepted). Figure 1.2 presents an overview of how these contributions fit into the scope of MPCs. These contributions cover the isolated and non-isolated MPCs with and without bipolar outputs and their applications for grid integration.

Figure 1. 2: Contributions of this dissertation based on the scope of MPCs.

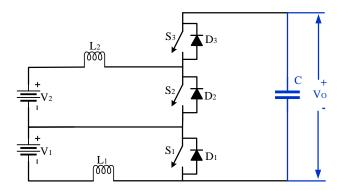

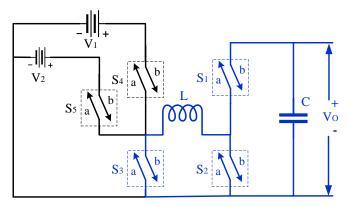

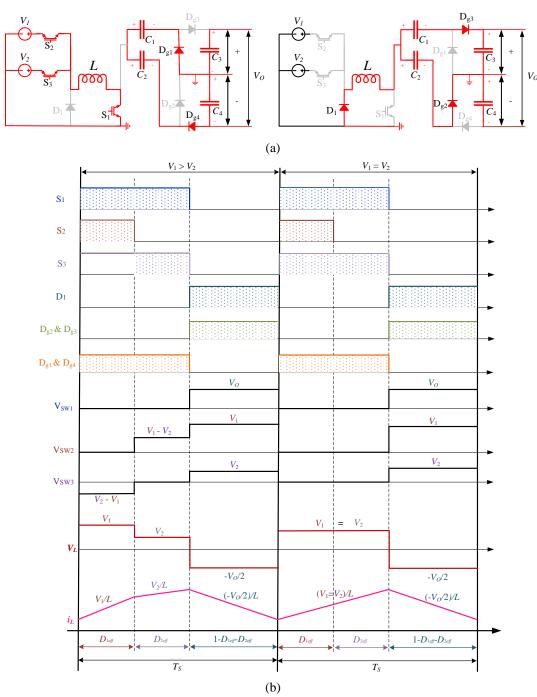

#### Paper I: Four Quadrant Switch Based Multiple-Input DC-DC Converter

**Summary:** In this paper, a novel non-isolated multiport dc-dc converter (MPC) is proposed and analysed for two inputs. The MPC uses four-quadrant switches, only one inductor and capacitor. It is capable of bidirectional operation in non-inverting buck-boost configuration and can accommodate the simultaneous transfer of energy from more than one source of different voltage levels to the DC bus. As compared to existing MPCs of similar characteristics in literature, the proposed converter utilizes less number of inductors and requires only one switch to integrate any extra energy storage. Different operation modes of the proposed MPC are numerically verified and validated on a high-fidelity hardware-in-the-loop (HIL) device.

**Contribution:** A non-isolated MPC with unipolar outputs based on bidirectional switches with unique attributes and low part count is proposed. It is recommended for energy storage hybridisation applications where bidirectional power flow is required. Numerical simulations and HIL implementation were performed to verify the operation of the proposed MPC.

#### This paper has been published as:

**I. N. Jiya**, H. Van Khang, N. Kishor and R. Ciric, "Four Quadrant Switch Based Multiple-Input DC-DC Converter," in *2021 IEEE 12th Energy Conversion Congress & Exposition - Asia (ECCE-Asia)*, Singapore, Singapore, 2021, pp. 2199-2204, doi: 10.1109/ECCE-Asia49820.2021.9479432.

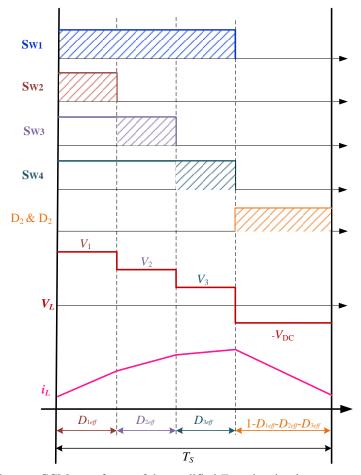

# Paper II: Novel Multisource DC-DC Converter for All-Electric Hybrid Energy Systems

Summary: In paper II, the novel non-isolated MPC proposed in paper I is further verified with an application focus for all-electric hybrid energy storage systems. The proposed MPC is capable of bidirectional operation in non-inverting buck-boost configuration and can accommodate the simultaneous energy transfer from multiple sources of different voltage levels to the dc bus. As compared to counterparts, the proposed MPC utilizes a smaller number of inductors and requires only one bidirectional switch to integrate any extra energy storage. Within the framework, a novel voltage transformation, operation modes and control method are presented in detail. This is in addition to a detailed comparison of the proposed MPC with other existing MPCs with similar characteristics to highlight its unique superiority. The performance and key features of operation with varying voltage levels and duty cycles of the proposed MPC are numerically verified through a high-fidelity HIL platform and experimentally validated on an inhouse test rig.

Contribution: Although the initial idea alongside preliminary results based on simulations of the MPC proposed in paper II was presented in paper I, the detailed analysis and features are further experimentally validated using an in-house SiC-switch based experimental test rig. Within this framework, a novel voltage transformation factor is proposed, and a single input single output (SISO) controller for parallel configuration with multiple voltages involved is introduced and verified on the high-fidelity HIL platform.

#### This paper has been published as:

**I. N. Jiya,** A. M. S. Ali, H. Van Khang, N. Kishor and R. Ciric, "Novel Multisource DC-DC Converter for All-electric Hybrid Energy Systems," *IEEE Transactions on Industrial Electronics*, vol. 69, no. 12, pp. 12934–12945, Dec. 2022, doi: 10.1109/TIE.2021.3131871.

# Paper III: Novel Isolated Multiple-Input Buck-Boost DC-DC Converter for Renewable Energy Sources

**Summary:** An isolated MPC with unidirectional buck-boost characteristics and simultaneous power transfer is proposed for multi-sources in renewable

energy systems in paper III. As compared to existing isolated MPCs with unipolar outputs, the proposed MPC significantly reduces the component count and control complexity since it requires a fixed coupled inductor with only one primary and secondary winding each for any number of inputs and does not require any phase-shifted pulse-width modulation. The operation of the proposed converter for simultaneous power transfer from multiple sources with varying voltages is numerically verified in simulation and validated on OPAL-RT's OP5700 HIL validation platform.

**Contribution:** An isolated MPC with unipolar outputs is proposed, based on reverse blocking switches with unique attributes of low part count and fixed primary and secondary windings. It is recommended for renewable energy source applications, where only unidirectional power flow is required. Numerical simulations and HIL implementation were performed to verify the operation of the MPC in paper III.

#### This paper has been published as:

**I. N. Jiya,** A. Salem, and H. Van Khang, "Novel Isolated Multiple-Input Buck-Boost DC-DC Converter for Renewable Energy Sources," *IECON 2021 – 47th Annual Conference of the IEEE Industrial Electronics Society*, Toronto, Canada, 2021, pp. 1-6, doi: 10.1109/IECON48115.2021.9589538.

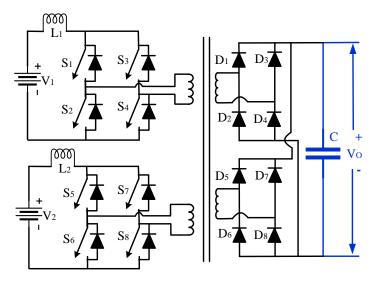

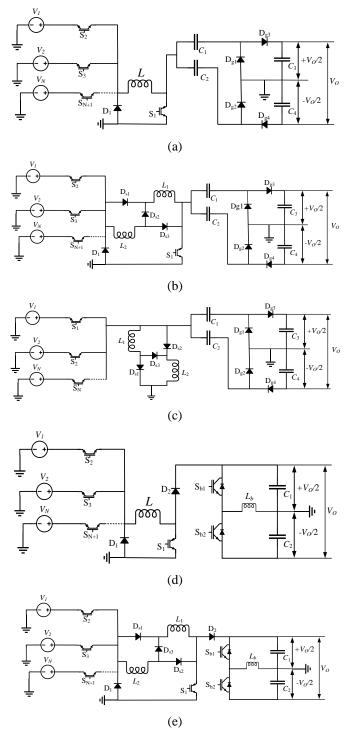

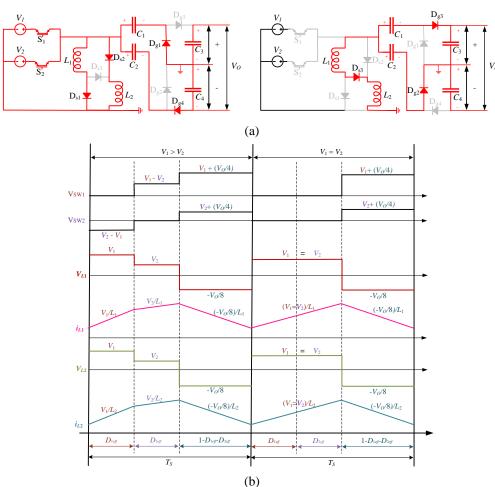

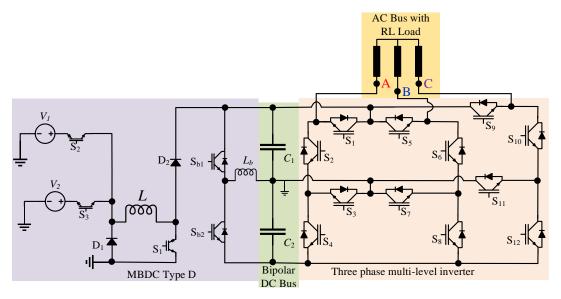

#### Paper IV: Novel Family of High-Gain Nonisolated Multiport Converters With Bipolar Symmetric Outputs for DC Microgrids

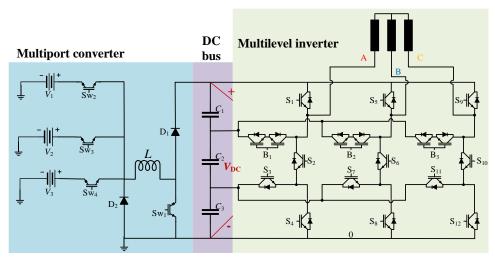

**Summary:** Bipolar dc grid systems are fast gaining attraction for renewable energy source (RES) integration, because of their merits of higher reliability, efficiency and robustness as compared to the unipolar dc grids. However, the progress in multiport converters, resulting into lower cost and more compact design for bipolar microgrid systems, is slow. Therefore, paper IV proposes a novel family of five non-isolated multiport dc-dc converter topologies with bipolar symmetric outputs. The performance and key operational features of the proposed converters under varying input voltages, duty cycles and loads are numerically verified and experimentally on an in-house test setup to prove the concept of the proposed converters. In the experimental validation, the operation of the converter under

simultaneous and arbitrary individual power transfer from two input ports is tested. Further, the easy integration of the proposed converters with a multilevel inverter to achieve high-quality ac voltages is demonstrated. As compared to the few existing counterparts, the proposed converters have a competitive edge in terms of higher number of input ports and voltage gains. Alongside the possibility of arbitrary independent power flow from the input ports, inherently symmetrical outputs require a simple balance control for asymmetrical members of the family.

Contribution: In this paper, a novel family of five non-isolated MPCs with bipolar outputs (MBDCs) is proposed. These MBDCs possess novel features of high gain, simplified control, ability to arbitrarily increase the number of inputs and inherently symmetrical bipolar outputs or simple output voltage balancing control in the case of the asymmetrical topologies. Within this framework, the proposed novel family of MBDCs is analysed for two input sources of equal and unequal input voltage levels under simultaneous power transfer from both sources. The analysis is then numerically verified and experimentally validated using an in-house SiC-switch based experimental test rig. Finally, the integration of the proposed MBDCs with future dc-ac conversion systems was also demonstrated.

#### This paper has been published as:

**I. N. Jiya,** H. Van Khang, N. Kishor, and R. M. Ciric, "Novel Family of High-Gain Nonisolated Multiport Converters With Bipolar Symmetric Outputs for DC Microgrids," *IEEE Transactions on Power Electronics*, vol. 37, no. 10, pp. 12151–12166, Oct. 2022, doi: 10.1109/TPEL.2022.3176688.

# Paper V: Integrated Multiport DC-DC and Multilevel Converters for Energy Sources

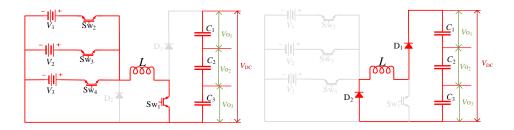

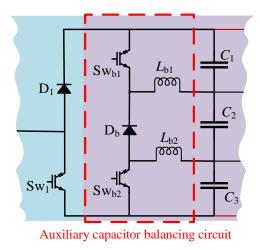

**Summary:** Paper V presents a novel converter system for integrating multiple renewable energy sources for both dc and ac grids. The proposed converter system is formed by integrating a modified unidirectional version of the novel MPC topology presented in papers I and II with a multilevel inverter topology. This was done to achieve multiple source integration with low component count and higher efficiency on the multiport converter section and efficient dc to ac conversion on the multilevel inverter section.

As compared to counterparts in literature, where each energy source requires its own dc converter and the dc to ac conversion is achieved using a two-level converter, the converter system proposed in this paper has more attractive features of buck-boost operation, better power quality characteristics and low part counts. Within the framework, an auxiliary circuit-based dc link voltage balancing technique is proposed to balance the voltage on the dc link as compared to the more complex control-based balancing scheme. Open and closed loop operations of the converter system are numerically verified using simulations and validated by a high-fidelity hardware-in-the-loop implementation platform.

Contribution: A converter system for integrating multiple energy sources and converting to ac with unique attributes of low part count, high gain and high-quality ac power is proposed. A comparison of two methods of balancing the dc link capacitor voltage is evaluated, and both were found to achieve desirable performance characteristics. This converter system is recommended for renewable energy source integrations applications, where conversion to ac is also required. The converter system was validated using numerical simulations and on the HIL validation platform.

#### This paper has been published as:

**I. N. Jiya,** H. Van Khang, A. Salem, N. Kishor and R. Ciric, "Integrated Multiport DC-DC and Multilevel Converters for Energy Sources," *2022 IEEE Industry Applications Annual Meeting*, Detroit, Michigan, 2022, pp. 1-7, doi: 10.1109/IAS54023.2022.9939764.

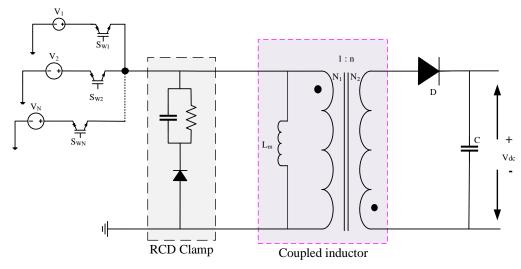

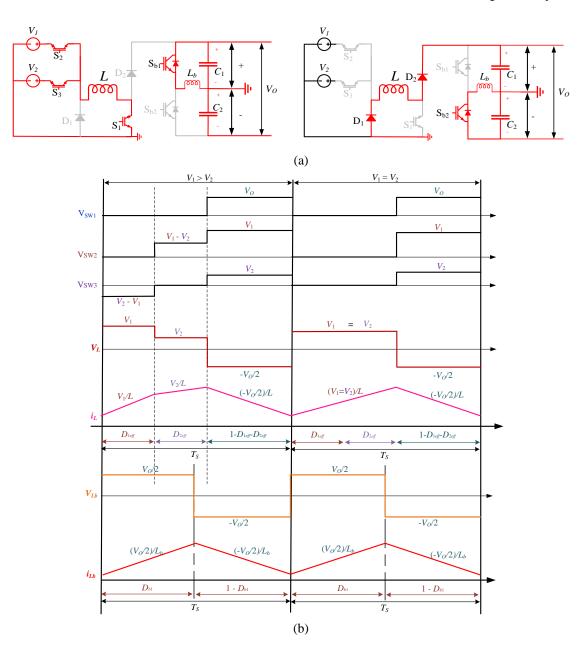

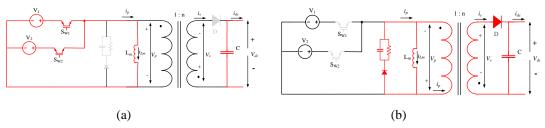

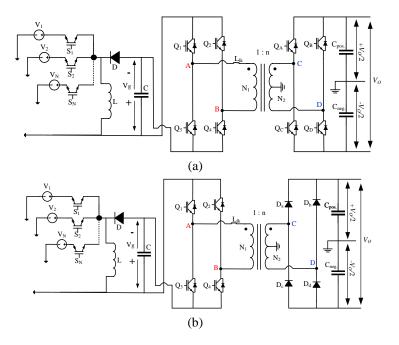

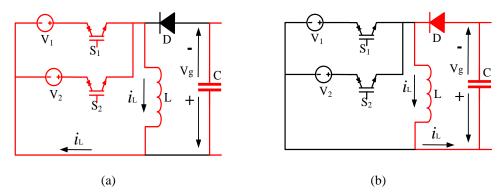

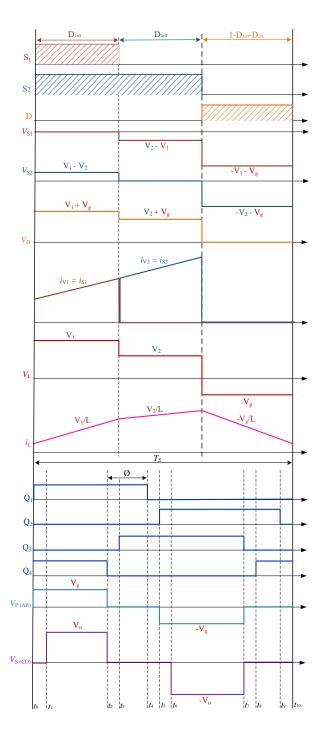

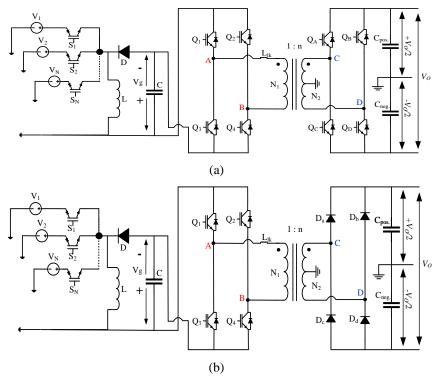

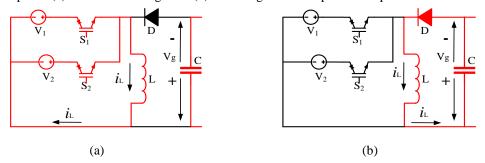

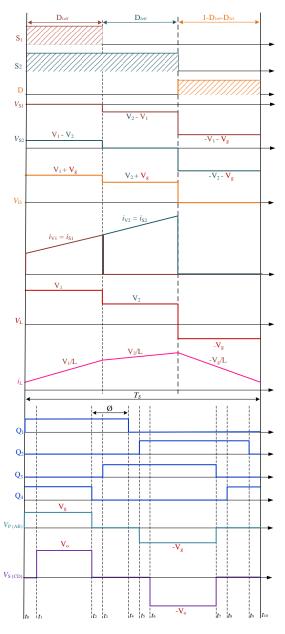

# Paper VI: Novel High Gain Multiport Isolated DC-DC Converter with Bipolar Symmetric Outputs

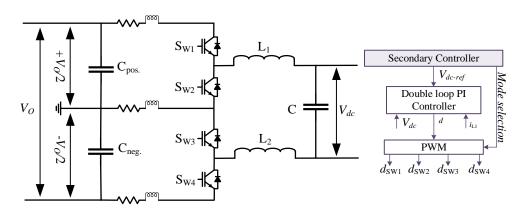

**Summary:** In paper VI, an isolated multiport dc-dc converter with inherently symmetric bipolar outputs (MIBDC) is proposed. The suggested converter has a competitive advantage over its few counterparts in terms of the number of input ports, voltage gain, and natural symmetry of the outputs. Furthermore, because the proposed MIBDC uses a fixed transformer with only one primary and secondary winding for any number of inputs, it considerably decreases component count and control complexity. The proposed converter's operation is quantitatively tested in

simulation and on OPAL-RT's HIL validation platform for independent and simultaneous power transfer from multiple sources with varying voltages.

Contribution: An isolated MPC with bipolar outputs is proposed, based on the centre tapped transformer of a dual active and phase-shifted full-bridge converter. It has a unique attribute of inherently symmetrical bipolar outputs. As compared to counterparts, its number of inputs can be arbitrarily increased without any modifications to the core of the isolation transformer. It is recommended for energy source hybridisation applications where bidirectional power flow is not required. Numerical simulations and implementation on the HIL validation platform was performed to verify the operation of the proposed MPC.

#### This paper has been published as:

**I. N. Jiya,** H. Van Khang, N. Kishor and R. Ciric, "Novel High Gain Multiport Isolated DC-DC Converter with Bipolar Symmetric Outputs," *IECON* 2022 – 48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 2022, pp. 1-6, doi: 10.1109/IECON49645.2022.9968834.

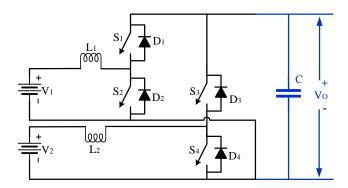

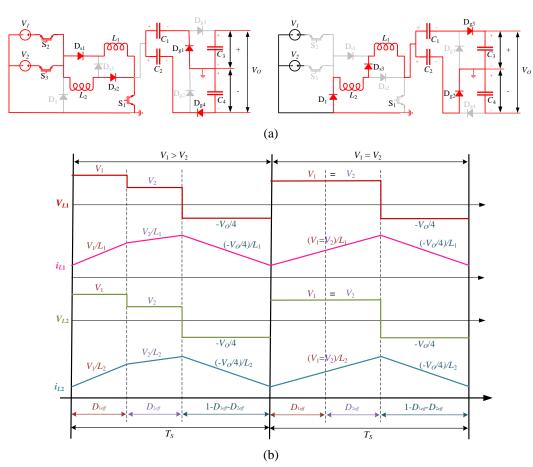

# Paper VII: Multiport DC-DC Converter for Integrating Energy Systems in All-Electric Vehicles

Summary: In this paper, a non-isolated multiport dc-dc converter (MPC) of non-inverting buck-boost configuration is proposed for integrating multiple energy resources in automotive applications. A typical example of such automotive application is an electric vehicle (EV), powered by one or more renewable energy sources (RESs) and consisting of one or more energy storage systems (ESSs), e.g. batteries and supercapacitors. The inputs to the MPC are clustered based on source or storage and integrated using uni- or bi-directional switches, respectively. It is capable of bi-directional operation between the storage cluster and the dc link, allowing for a simultaneous transfer of energy from more than one source of varying voltage levels (irrespective of its' cluster) to the dc link. The proposed MPC is analysed for four inputs, comprising of two per cluster in this paper. As compared to existing MPCs in literature, the proposed converter utilizes a fixed number (two) of inductors and is robust such that it requires only one

additional switch to integrate any extra energy storage or source in a respective cluster. Different operating modes of the proposed MPC are numerically verified and validated on OPAL-RT's OP5700 hardware-in-the-loop (HIL) platform.

**Contribution:** The non-isolated MPC with unipolar outputs proposed in paper VII is suggested as an improvement to the MPC in papers I and II. This is because the MPC in papers I and II can only accommodate energy storages while the MPC in paper VII can accommodate both storages and sources. Numerical simulations and HIL implementation were performed to verify the open and closed loop operation of this MPC.

### This paper has been submitted as:

**I. N. Jiya,** P. Gunawardena, H. Van Khang, N. Kishor and Y. Li, "Multiport DC-DC Converter for Integrating Energy Systems in All-Electric Vehicles," 2023 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC), Venice, Italy, 2023, pp. 1-6, doi: 10.1109/ESARS-ITEC57127.2023.10114856.

# Paper VIII: Novel Isolated Multiport DC Converter with Natural Bipolar Symmetry for Renewable Energy Source Integration to DC Grids

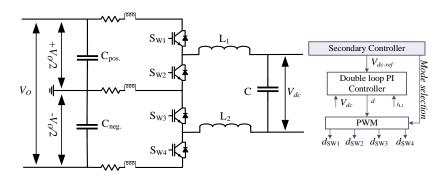

**Summary:** In paper VIII, the novel isolated MPC with bipolar inherently symmetric outputs (MIBDC) proposed in paper VI is analysed. The suggested converter has a competitive advantage over its few counterparts in terms of the number of input ports, voltage gain, and natural symmetry of the outputs. Further, the proposed MIBDC uses a fixed transformer with only one primary and secondary winding for any number of inputs, it considerably decreases component count and control complexity. The converter requires a comparatively simple control structure, using only a single input single output (SISO) controller, such as the standard double loop PI controller. The proposed converter's operation is quantitatively tested in simulation and experimentally verified on OPAL-RT's OP5700 hardware-in-the-loop (HIL) platform for open and closed loop performance under varying conditions.

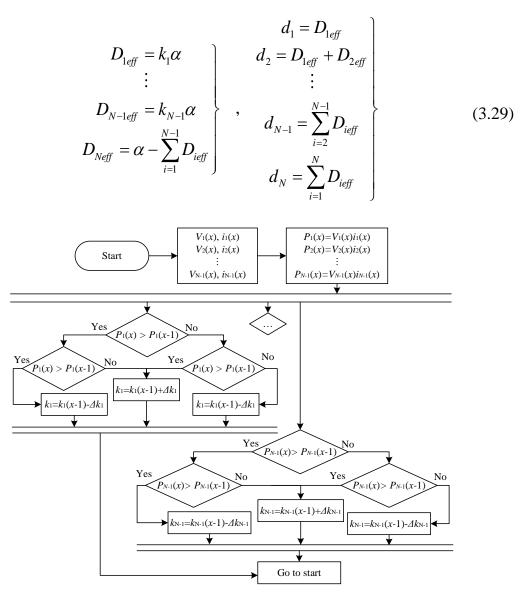

Contribution: By adopting a DAB-based and a FB-based topology with a fixed two winding (one primary and secondary winding each) transformer and many ports constructed using pulsating voltage sources, the MIBDC presented in paper VIII addresses the constraints of previous topologies. The component count is kept minimal, while the single inductor is time multiplexed to allow for any arbitrary independent and simultaneous power transfer from multiple sources. Further, a distributed MPPT (DMPPT) technique is proposed to reduce the complexity and thus requiring only one MPP controller for any number of inputs. The initial idea of the MIBDC proposed in this work has been presented in paper VI while the detailed analysis and features are numerically verified and results from experimental validation using the HIL test rig are presented in this paper.

#### This paper has been submitted as:

**I. N. Jiya,** H. Van Khang, P. Gunawardena, N. Kishor and Y. Li, "Novel Isolated Multiport DC Converter with Natural Bipolar Symmetry for Renewable Energy Source Integration to DC Grids," in *IEEE Transactions on Industrial Electronics*, (Submitted).

#### 1.4 Dissertation structure

This dissertation consists of five chapters, numbered one to five, and is presented as follows:

#### **Chapter 1: Introduction**

In chapter one, a brief background and introduction to MPCs is provided alongside the motivation of the research. The main contributions of the dissertation are highlighted, and the structure of the dissertation is addressed.

#### **Chapter 2: State-of-the-art**

This chapter presents a literature review of the recently developed MPC topologies in terms of their structure, unique features, and drawbacks. The MPCs considered cover four broad MPC categories, that is, the isolated and non-isolated MPCs with unipolar outputs and, the isolated and non-isolated MPCs with bipolar outputs. This is done with the aim of highlighting the gaps in the existing MPC topologies,

which usher in the novel MPCs proposed in this dissertation to fill these gaps as presented in chapter 3.

### Chapter 3: Novel multiport converter topologies

Chapter 3 presents the circuit configurations of the novel MPCs in this dissertation. Their steady state operating characteristics and control strategies are analyzed, and some grid integration applications were also presented.

### **Chapter 4: Results and discussions**

A summary of the results and findings is presented in chapter five, based on papers I-VIII, in which the operation and performance characteristics of the novel MPCs are numerically verified and experimentally validated through in-house laboratory test rigs. Furthermore, their novel features are emphasized by comparative analysis with existing MPCs of similar structure and characteristics.

#### **Chapter 5: Concluding remarks**

The conclusions drawn based on the work carried out in the research are presented in chapter five. Further, the limitations and future room improvements are also highlighted.

# Chapter 2

# 2 State of the art

In this chapter, some interesting MPC topologies developed recently are reviewed to highlight their characteristics, salient features, and limitations. The reviewed MPC topologies cover the topologies that address hybridization of multiple energy sources and/or storages. Specifically, the isolated and non-isolated MPCs with unipolar and bipolar outputs are addressed in this chapter.