# Power Electronics for Plasma Processing

Citation for published version (APA):

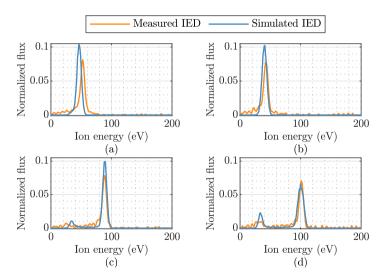

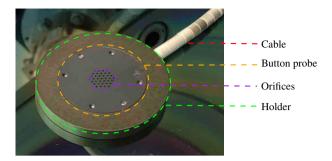

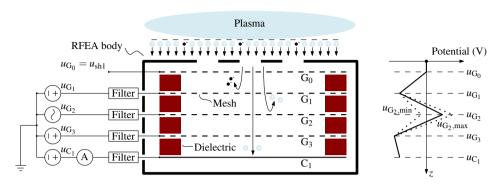

Yu, Q. (2023). Power Electronics for Plasma Processing: Enabling Energy-Efficient and Accurate Ion Energy Control for Semiconductor Manufacturing. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Eindhoven University of Technology.

#### Document status and date:

Published: 13/09/2023

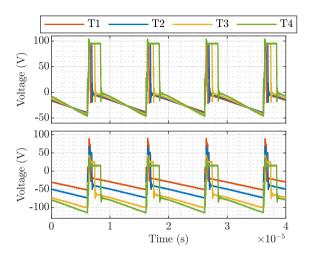

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 17. Nov. 2023

# Power Electronics for Plasma Processing

\_\_\_\_\_

Qihao Yu

This work is part of the project Research on a Radio Frequency Bias Voltage Generator for Remote Plasma Application of the research programme High Tech Systems and Materials (HTSM), which was supported by Prodrive Technologies B. V. under Project 10025565.

Thesis layout: Maurice Roes.

First edition. Published in the Netherlands, 2023.

Copyright © Qihao Yu, 2023. All rights reserved. No part of this thesis may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

A catalogue record is available from the Eindhoven University of Technology Library.

ISBN: 978-90-386-5618-6.

# Power Electronics for Plasma Processing

Enabling Energy-Efficient and Accurate Ion Energy Control for Semiconductor Manufacturing

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr. S.K. Lenaerts, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op woensdag 13 september 2023 om 16:00 uur.

door

Qihao Yu

geboren te Zhejiang, People's Republic of China

Dit proefschrift is goedgekeurd door de promotor. De samenstelling van de promotiecommissie is als volgt:

voorzitter: prof. dr. ir. A. B. Smolders 1<sup>e</sup> promotor: prof. ir. C. G. E. Wijnands copromotoren: dr. ir. B. J. D. Vermulst

dr. ir. E. Lemmen

leden: prof. dr. J. Kyyrä (Aalto-yliopisto)

prof. dr. ir. W. M. M. Kessels

prof. dr. T. Batista Soeiro (Universiteit Twente)

prof. dr. G. Papafotiou

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# **Summary**

### Power Electronics for Plasma Processing

LASMA is an ionized gas consisting of positive ions, electrons, and neutral particles. It is used in essential process steps in semiconductor manufacturing, for both deposition and etching. Deposition is a process of growing thin film layers on the substrate, and etching is a process of selectively removing the material layers of a specific pattern. Plasma is crucial in these processes as it provides additional reaction energy, lowers the process temperature, increases throughput, enhances anisotropy, and so forth.

The ever-growing demand for more powerful computing capability continuously pushes the transistors in the integrated circuits (ICs) to shrink, enabling more circuitry to be laid down in the same space. With the advent of an artificial intelligence (AI) revolution led by ChatGPT, this demand will reach new heights, posing critical challenges to plasma processing in semiconductor manufacturing. One of these challenges is accurately controlling the plasma ion energy to allow more precise process control and improved quality.

Plasma processing occurs within a plasma reactor. In the reactor chamber, plasma is ignited and sustained by applying a power source to a feedstock gas. This power source can be either capacitively or inductively coupled with the feedstock gas. With the substrate wafer placed on the reactor table, the fast-moving electrons in the plasma can get lost in the wafer, forming a region on the substrate surface where the ion density exceeds the electron density, known as the plasma sheath. An electric potential difference is built over the sheath, causing the substrate surface potential to be consistently lower than the plasma potential. Consequently, ions are accelerated in the plasma sheath, bombard the substrate, and enhance material processing reactions on the substrate surface. Different processing recipes require different plasma ion energy. The bombarding ions should carry sufficient energy to be effective in the reactions, but excessive ion energy could degrade the process quality

and damage the substrate. In short, this means that the ion energy distribution (IED) should fall into a narrow window.

The ion energy can be controlled by a bias converter, which is electrically connected to the reactor table and the bottom side of the substrate. The bias converter generates voltage waveforms, typically negative on average, to further increase the voltage difference over the plasma sheath, thus accelerating the ions to the desired energy. Among the various bias waveforms that can be used, the tailored waveform is found particularly promising, since it can achieve a narrow IED for a broad range of applications.

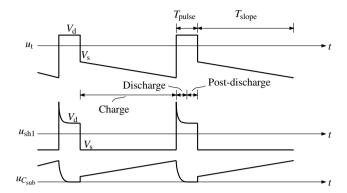

The tailored waveform comprises a negative voltage slope followed by a positive voltage pulse. The negative voltage slope compensates for the charge accumulation effect caused by the bombarding ions in the capacitance of the dielectric substrate. The voltage pulse is applied to discharge and reset all the capacitors in case of overvoltage and restart the process with the desired substrate surface potential.

Traditionally, such tailored waveforms are generated by linear amplifiers, which are of low efficiency. Besides, a matching network is required for the linear amplifier, adding additional energy dissipation. While switched-mode power converters (SMPCs) are well-known energy-efficient alternatives to linear amplifiers, they are not yet widespread in this cutting-edge technology. However, they have recently demonstrated immense potential. Nevertheless, designing an effective SMPC requires a well-established load that reflects the electrical responses of the plasma. Currently, such models are unavailable, which is a significant obstacle to transitioning towards efficient power electronics.

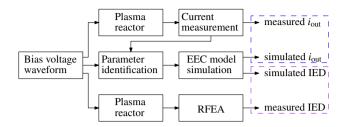

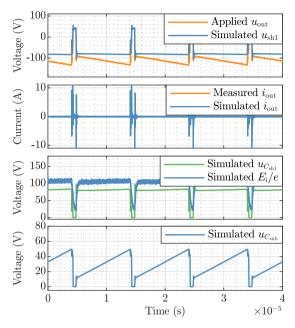

Therefore, this thesis derives an equivalent electric circuit (EEC) of the plasma processing that depicts the electrical behavior for all phases in tailored waveform biasing. It can be simulated in combination with the bias converter on a circuit level. Moreover, the IED can also be reproduced from the circuit simulation, which substantially reduces the computational effort compared to traditional plasma simulations like particle-in-cell (PIC). Furthermore, a parameter identification method is proposed to extract all the parameters of the EEC model. This method only requires the voltage and current measurements on the bias converter side, which is non-intrusive to the process.

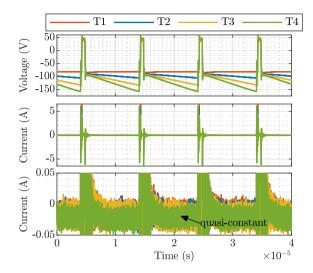

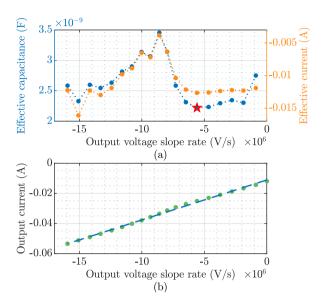

The proposed model reveals that the below-zero portion of the falling edge of the voltage pulse determines the ion energy value, while the voltage slope determines the width of IED. The optimal slope should result in the narrowest IED, and it is dependent on the ion current and the substrate capacitance, thus varying under different operating conditions. Conventionally, this optimal slope is manually tuned by measuring the IED in real-time using a retarding field energy analyser (RFEA). Such manual tuning needs to be repeatedly conducted once the operating conditions

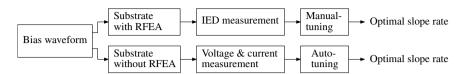

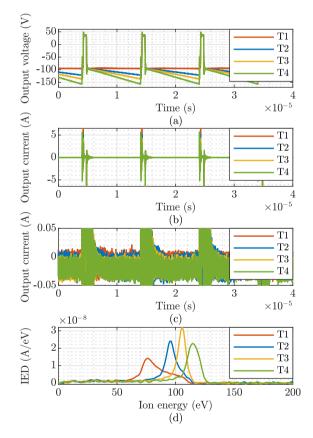

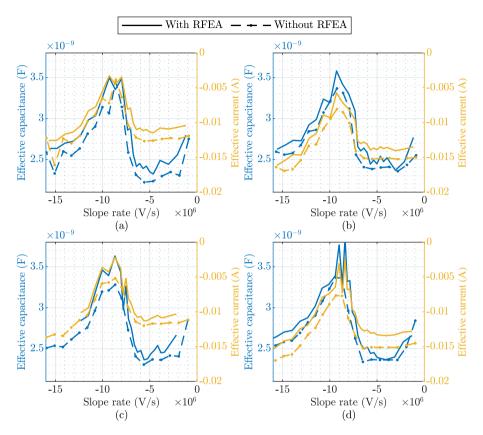

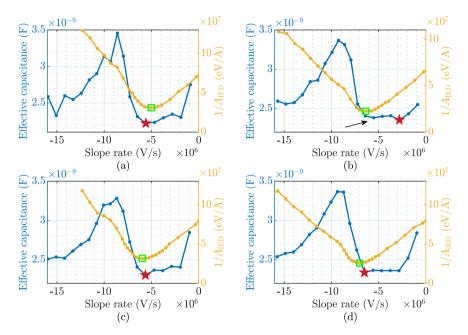

change. Meanwhile, the RFEA can introduce errors. This thesis develops an autotuning method, which finds the optimal slope based on mathematical relations between voltage and current, thus eliminating the need for an RFEA.

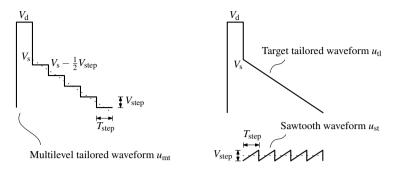

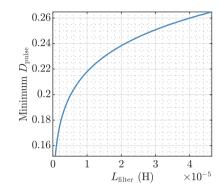

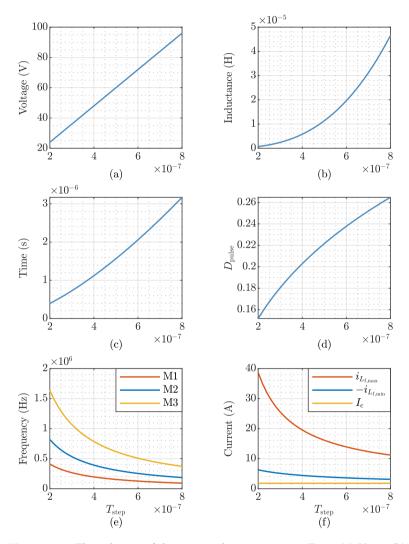

Based on the proposed model, this thesis proposes a multilevel tailored waveform bias converter concept, which is based on efficient switched-mode operation. The original tailored waveform, specifically the voltage slope, is replaced by a sequence of monotonically decreasing voltage levels. Approximating the voltage slope with the multilevel waveform can introduce undesired voltage ripples on the substrate surface, which could broaden the IED. To overcome this, a filter inductor can be added to further reduce the voltage ripple, at the cost of a slower voltage pulse. This compromise is analyzed in this thesis, and the constraints for the multilevel waveform configurations given by the required IED are derived. Based on the analysis, it is found that multilevel voltage converters can be used in this application, offering the benefits of scalability and modularity compared to other existing concepts. Specially, an asymmetrical multilevel converter, formed by a T-type converter and two cascaded H-bridge converters, is proposed in this research.

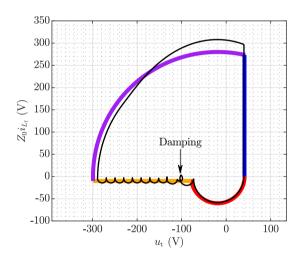

The plasma reactor is a capacitive load, thus forming an LC circuit with all the inductance in the converter loop. This LC circuit can cause severe resonance triggered by the voltage pulse. To minimize the resonance in a non-dissipative manner, a trajectory control method is developed. This method utilizes multiple intermediate voltage levels and determines a specific switching sequence during the rising and falling edge of the voltage pulse.

A converter prototype is designed to verify the various concepts. The magnitude and frequency of the multilevel waveform are optimized by pushing the switching components to their limits based on a comprehensive switching loss model. Based on the EEC model, a plasma-reactor mockup is designed and built to emulate the electrical responses of the plasma reactor, which is used as the qualification load for the converter prototype. This research provides a systematic solution for accurate ion energy control, from plasma processing modeling to converter design, control, and optimization, paving the way towards more energy-efficient and accurate semiconductor manufacturing.

# **Contents**

| Su            | Summary |                      |                                                          | iii |

|---------------|---------|----------------------|----------------------------------------------------------|-----|

| 1             | Intro   | oductio              | on                                                       | 1   |

|               | 1.1     | Plasm                | a physics                                                | 2   |

|               |         | Plasma fundamentals  | 2                                                        |     |

|               |         | 1.1.2                | Plasma sheath                                            | 5   |

|               |         | 1.1.3                | High-voltage sheath                                      | 10  |

|               | 1.2     | Plasm                | a processing                                             | 12  |

|               |         | 1.2.1                | Semiconductor manufacturing                              | 12  |

|               |         | 1.2.2                | Plasma deposition                                        | 14  |

|               |         | 1.2.3                | Plasma etching                                           | 15  |

|               |         | 1.2.4                | Ion energy control                                       | 17  |

|               | 1.3     | Resear               | rch objectives                                           | 20  |

|               | 1.4     | Organ                | ization of this thesis                                   | 21  |

| 2             | Mod     | lel of p             | lasma processing                                         | 23  |

|               | 2.1     | _                    | alent electric circuit model                             | 24  |

|               |         | 2.1.1                | Traditional equivalent electric circuit model            | 24  |

|               |         | 2.1.2                | Improved equivalent electric circuit model               | 28  |

|               |         | imental verification | 34                                                       |     |

|               |         | 2.2.1                | Experimental setup                                       | 34  |

|               |         | 2.2.2                | Simulation setup                                         | 36  |

|               |         | 2.2.3                | Electric waveform and ion energy distribution simulation | 39  |

|               |         | 2.2.4                | Case study of variant pulse duty cycles                  | 42  |

|               | 2.3     | Concl                | usion                                                    | 44  |

| 3 Auto-tuning |         |                      | g                                                        | 47  |

| -             | 3.1     |                      | tuning concept                                           | 48  |

|   | 3.2  | System influence of retarding field energy analyser | 50  |

|---|------|-----------------------------------------------------|-----|

|   | 3.3  | Experimental verification                           | 52  |

|   | 3.4  | Conclusion                                          | 57  |

| 4 | Para | meter identification                                | 59  |

|   | 4.1  | Parameter identification procedure                  | 59  |

|   | 4.2  | Experimental verification                           | 62  |

|   |      | 4.2.1 Example implementation                        | 62  |

|   |      | 4.2.2 Discussion                                    | 64  |

|   | 4.3  | Conclusion                                          | 65  |

| 5 | Bias | converter                                           | 67  |

|   | 5.1  | Existing bias converter concept                     | 68  |

|   |      | 5.1.1 Voltage source converter                      |     |

|   |      | 5.1.2 Hybrid source converter                       |     |

|   | 5.2  | Multilevel bias converter concept                   |     |

|   |      | 5.2.1 Multilevel tailored waveform                  |     |

|   |      | 5.2.2 Extra filter inductor                         | 73  |

|   | 5.3  | Multilevel bias converter topology                  |     |

|   |      | 5.3.1 Topology evaluation                           | 76  |

|   |      | 5.3.2 Bias converter topology                       | 78  |

|   |      | 5.3.3 Operating principle                           | 81  |

|   | 5.4  | Conclusion                                          | 82  |

| 6 | Traj | ectory control                                      | 85  |

|   | 6.1  | •                                                   | 86  |

|   | 6.2  | Trajectory control of the bias converter            |     |

|   |      | 6.2.1 Preparation                                   |     |

|   |      | 6.2.2 General principles                            |     |

|   |      | 6.2.3 Discharge phase                               | 90  |

|   |      | 6.2.4 Post-discharge phase                          | 92  |

|   |      | 6.2.5 Restart charge phase                          | 92  |

|   |      | 6.2.6 Charge phase                                  | 93  |

|   | 6.3  | Simulation                                          | 94  |

|   | 6.4  | Conclusion                                          | 97  |

| 7 | Top- | -down design                                        | 99  |

|   | 7.1  | Specification                                       | 100 |

|   | 7.2  | Converter dimensioning                              |     |

|   | 7.3  | Switching transient                                 |     |

|   |      | 7.3.1 Simplified analysis                           |     |

|   |      | 7.3.2 Switching transient model                     |     |

|    |       | 1 1                                                | .08 |

|----|-------|----------------------------------------------------|-----|

|    | 7.4   | 0                                                  | .13 |

|    |       | 7.4.1 Worst case estimation                        | .13 |

|    |       | 0                                                  | .15 |

|    | 7.5   | Conclusion                                         | .17 |

| 8  | Expe  |                                                    | 19  |

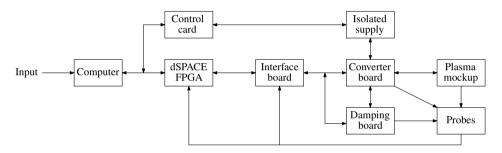

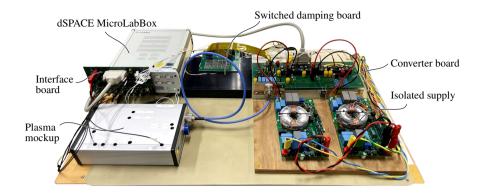

|    | 8.1   | T                                                  | .19 |

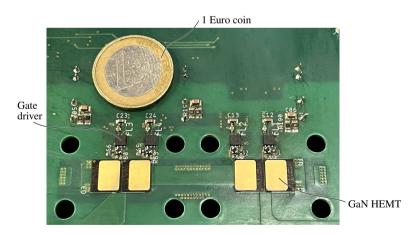

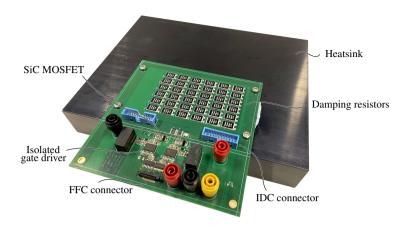

|    |       | 8.1.1 Converter board                              |     |

|    |       | 8.1.2 Switched damping board                       | .22 |

|    |       | 8.1.3 Interface board                              | .23 |

|    |       | 8.1.4 Isolated supply board                        | .23 |

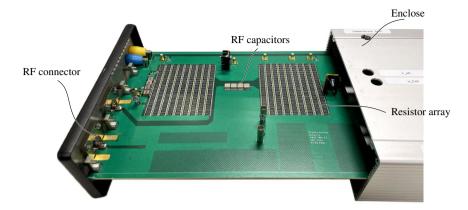

|    |       | 8.1.5 Plasma mockup                                | 25  |

|    |       | 8.1.6 Overview of the experimental setup           | .27 |

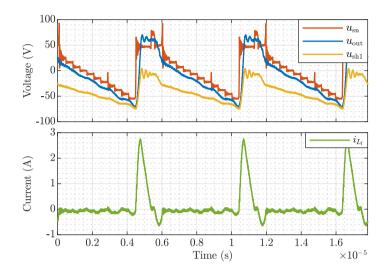

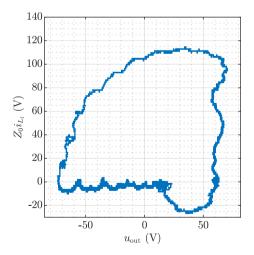

|    | 8.2   | Experimental results                               | 28  |

|    |       | 8.2.1 Functional test                              | 28  |

|    |       | 8.2.2 Stress test                                  | 34  |

|    | 8.3   | Conclusion                                         | .39 |

| 9  | Clos  | ing 1                                              | 41  |

|    | 9.1   | Conclusions                                        | 41  |

|    | 9.2   | Recommendations                                    | 43  |

|    | 9.3   | Scientific contributions                           | 45  |

|    | 9.4   | Publications                                       | 47  |

|    |       | 9.4.1 Journal publications                         | 47  |

|    |       | 9.4.2 Conference publications                      | 47  |

|    |       | *                                                  | 48  |

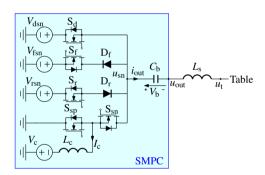

| A  | Cust  | om switched-mode power converter 1                 | 49  |

| В  | Line  | ar time-invariant system during the charge phase 1 | 53  |

| C  | Ion ( | energy distribution 1                              | 157 |

|    |       |                                                    |     |

| D  | -     |                                                    | 61  |

|    | D.1   |                                                    | .61 |

|    | D.2   |                                                    | 62  |

|    | D.3   |                                                    | .67 |

|    | D.4   | y .                                                | .67 |

|    | D.5   | Acronyms                                           | .67 |

| Re | feren | ces 1                                              | 71  |

## x | CONTENTS

| Curriculum vitae | 187 |

|------------------|-----|

| Acknowledgements | 189 |

# CHAPTER

## Introduction

LASMA is widely recognized as the fourth state of matter, along with solid, liquid, and gas [14]. It not only exists in nature, such as within the Sun and during lightning strikes, but can also be artificially generated, as is the case with the plasma in a neon light and nuclear fusion [88].

Essentially, a plasma refers to an ionized gas, whereby at least one electron is stripped off a neutral atom, leaving a free-moving negatively charged electron and a positively charged ion [23]. Similar to how heating a liquid can produce a gas, adequately heating a gas can also create a plasma since gaseous particles, when colliding with one another with sufficient energy, can knock off electrons [63].

Plasma plays a crucial role in semiconductor manufacturing, particularly in plasmaenhanced deposition and etching processes for nanodevice fabrication [72, 149]. Nowadays, the ever-growing demand for the semiconductor industry attaches more and more importance to plasma processing. As the size of ICs continues to shrink, new challenges are brought to plasma processing, which are the central focus of this thesis.

While plasma physics is fascinating, it can be quite complex. This chapter provides a first glimpse into plasma and plasma processing. Necessary plasma physics and the basics of plasma processing are introduced in this chapter. Subsequently, the research scope and the thesis outline are provided.

This chapter is based on [183].

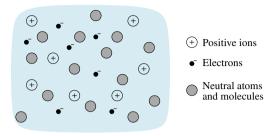

**Figure 1.1** The composition of a plasma.

## 1.1 Plasma physics

#### 1.1.1 Plasma fundamentals

Not all gas atoms need to be ionized to create a plasma. A plasma can be composed of positive ions, electrons, and neutral atoms and molecules, as depicted in Figure 1.1. The quantities of ions, electrons, and neutral particles per unit volume are represented by  $n_i$ ,  $n_e$ , and  $n_n$ , respectively. From a macroscopic viewpoint, a plasma is expected to have an approximately neutral net charge, known as quasineutrality [2]. It should be stressed that only the singly charged ions are considered in this thesis. Therefore, quasi-neutrality implies that  $n_i = n_e \equiv n$ , where n denotes the charged particle density in the plasma.

The behavior of plasma can vary significantly based on its degree of ionization, which is defined as

$$D_{\rm i} = \frac{n_{\rm i}}{n_{\rm i} + n_{\rm n}}.\tag{1.1}$$

A plasma with  $D_i \approx 1$  is considered fully ionized while  $D_i \ll 1$  corresponds to a weakly or partially ionized plasma [2]. As a matter of course, the Sun's core and the nuclear fusion plasmas are fully ionized [84,118].

In the semiconductor manufacturing industry, weakly ionized plasmas are typically used, making them the main focus of this thesis. The most common method of exciting plasma is by applying an electric field to a neutral gas at low pressure and relatively low temperature. The electric field accelerates free electrons, which then collide with the gas atoms. If the kinetic energy of the electrons is greater than the ionization energy, these collisions can create new charged particles [31]. This ionization process can be represented by

$$e + A \longrightarrow 2e + A^+$$

where e is the electron, and A represents an atom. The ionization releases additional free electrons, which in turn further the ionization process as an avalanche. In this

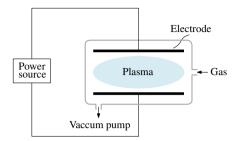

**Figure 1.2** The schematic of a gas discharge.

way, a weakly ionized plasma is ignited by the electric field, also known as "gas discharge" [154].

Figure 1.2 provides an example of a gas discharge in which two electrodes are connected to a power source, generating an electric field between them. With the feedstock gas infused, a plasma is excited and sustained. The power source can be of various types, such as direct current (dc) [42], pulsed dc [12], radio-frequency (RF) [95,162], etc [31].

Different types of particles undergo collisions within a plasma. In a weakly ionized plasma, these collisions can be inelastic, meaning that the total kinetic energy changes after the collisions [167]. Inelastic collisions in a plasma include ionization, excitation, dissociation, and electron attachment [30]. For instance, during the excitation process, a colliding electron can provide energy to an atom, causing it to enter its excited state. The electron within the atom jumps from the ground state to a higher energy level. This excitation requires less energy compared to ionization, and it is unstable. Within a short period, the excited atom can return to the ground state, and a photon can be emitted [126]. The photon emission explains the glow we see from a plasma and can be described by

$$e + A \longrightarrow e + A^* \longrightarrow e + A + photon,$$

where A\* is the atom in excited state. Dissociation is another vital reaction in plasma processing, which can be expressed as

$$e + AB \longrightarrow e + A + B$$

where AB is a molecule, and A and B could be radicals with high chemical reactivity.

Electrons can lose their kinetic energy in these inelastic collisions [181]. Usually, a vacuum pump is adopted to lower the pressure in the chamber, as depicted in Figure 1.2. A lower pressure results in smaller particle densities and larger interparticle distances generally [107], thus sharply reducing the collisions and enabling and sustaining plasma excitation at a low temperature.

When discussing "low temperature" in this context, it is important to clarify what is meant by this term. Temperature is a macroscopic property of a system, so it is not typically discussed in reference to a single particle. Additionally, temperature is normally only defined in systems that are in thermal equilibrium [84]. A gaseous system in thermal equilibrium is one in which particles collide randomly and exchange their energy sufficiently with each other. In this scenario, particles have different velocities that can be described by the Maxwell-Boltzmann distribution. Specifically, in one-dimensional coordinate x, the distribution is

$$f(v_x) = \left(\frac{m}{2\pi k_{\rm B}T}\right)^{\frac{1}{2}} e^{-\frac{mv_X^2}{2k_{\rm B}T}},\tag{1.2}$$

where  $v_x$  is the particle velocity in one dimension,  $f(v_x)$  is the probability density function,  $k_B$  is Boltzmann's constant, T is the system temperature, and m is the mass of the particles [84]. In three-dimensional coordinates, the velocity distribution is given as

$$f(v) = \left(\frac{m}{2\pi k_{\rm B}T}\right)^{\frac{3}{2}} 4\pi v^2 e^{-\frac{mv^2}{2k_{\rm B}T}},\tag{1.3}$$

where v is the particle velocity. It is worth noting that v is a scalar value. The velocity distribution of particles of the same species is solely determined by the temperature. Since particles are of different velocities, a single representative value, such as the average velocity  $v_{\rm avg}$  given by

$$v_{\text{avg}} = \int_0^\infty v f(v) dv = \sqrt{\frac{8k_{\text{B}}T}{\pi m}}$$

(1.4)

and the root-mean-square (RMS) velocity  $v_{\rm rms}$  given by

$$v_{\rm rms} = \sqrt{\int_0^\infty v^2 f(v) dv} = \sqrt{\frac{3k_{\rm B}T}{m}},\tag{1.5}$$

can be chosen to describe the temperature [80]. Moreover, the corresponding particle kinetic energy *E* can be calculated by

$$E = \frac{1}{2}mv_{\rm rms}^2 = \frac{3}{2}k_{\rm B}T,\tag{1.6}$$

which relates the average energy of gaseous particles with the temperature. Such representative velocity  $v_{\rm rms}$  is also named the thermal velocity.

In a weakly ionized plasma, the inter-particle distance is deliberately increased, and the particle collisions are brought down. Therefore, the energies of electrons, ions, and neutral particles are not equalized. Hence, a weakly ionized plasma is not in thermal equilibrium. Technically, in this case, the Maxwell-Boltzmann distribution is not applied, and the definition of temperature is more complex [19].

Nevertheless, electrons, as a single species, are in near-thermal equilibrium [2], so they are assumed to follow the Maxwell-Boltzmann distribution at electron temperature  $T_e$  in this thesis. For simplicity, ions and neutral particles can also be considered in thermal equilibrium at their respective temperature ( $T_i$  and  $T_n$ ) [84], assuming that particles of the same species collide sufficiently with themselves but interact much less with other species [24].

The temperatures  $T_e$  and  $T_i$  can be significantly different. Simply considering a charged particle with an elementary charge e, it experiences an acceleration a in an electric field *E*, governed by

$$a = \frac{F}{m} = \frac{eE}{m},\tag{1.7}$$

where *F* is the force exerted on the particle. The work *W* done by the electric field on the particle is determined by

$$W = Fx = F \cdot \frac{1}{2}at^2 = \frac{(eEt)^2}{2m},$$

(1.8)

where x is the displacement, and t is the time. As a result of their significantly smaller mass, electrons in the plasma gain substantially more energy from the electric field compared to the ions. In contrast, ions can only obtain a very limited amount of energy from elastic collisions with electrons, which can be easily solved using the laws of conservation of energy and momentum [180]. Consequently,  $T_e$  is significantly higher than  $T_i$ . In a typical weakly ionized plasma,  $T_e$  can be on the order of 10<sup>4</sup> K, while T<sub>i</sub> ranges from 300 to 1000 K [126]. Neutral particles, which have dominant quantities, stay at a lower temperature from 300 to 500 K. Therefore, the plasma as a whole is considered low-temperature.

#### 1.1.2 Plasma sheath

Quasi-neutrality, as previously introduced, holds for a bulk plasma. However, it may be locally violated in the region near a solid material surface, such as a wafer, probe [22], or electrode, as shown in Figure 1.2. This special region is called the plasma sheath, where the ion density is greater than the electron density.

To provide an intuitive perception, first consider a plasma surrounded by two solid material surfaces with floating electric potential, as depicted in Figure 1.3(a). Since a weakly ionized plasma is typically contained in a vessel [56], such a parallel plate system can be seen as the elementary construction of the plasma system in one dimension. According to Maxwell's equations [66], the electric field is determined by

$$\nabla \cdot \mathbf{D} = \nabla \cdot \epsilon \mathbf{E} = \rho_f, \tag{1.9}$$

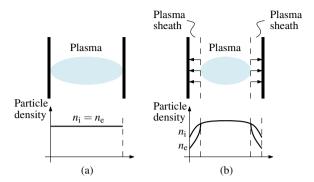

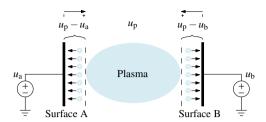

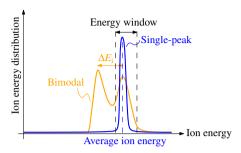

**Figure 1.3** The formation of plasma sheaths. (a) Initially, the plasma is surrounded by two solid material surfaces. (b) Shortly, the plasma sheaths are formed on the material surfaces. The arrows indicate the direction of the electric fields.

where  $\nabla \cdot$  is the divergence operator, D is the electric displacement field,  $\epsilon$  is the dielectric constant, and  $\rho_f$  is the volume charge density. Quasi-neutrality, as represented by  $n_i = n_e$ , leads to

$$\rho_f = e (n_i - n_e) = 0. (1.10)$$

Therefore, initially, both the electric field E and the electric potential u are zero everywhere in the plasma. In other words, the electrons and ions are not confined and can move freely [2]. As derived in (1.6), the velocity of electrons is much larger than that of ions due to their much higher temperature and lower mass. The electrons immediately flux into the materials, thus negatively charging the material with respect to the plasma. The negatively charged materials form electric fields towards their surfaces, as shown in Figure 1.3 (b). Meanwhile, the electric potential of the bulk plasma increases and becomes higher with respect to the materials. The electric potential continues to rise as long as there is a net flux of negative electrons until the steady state is reached when the ion and electron fluxes get balanced [56]. Consequently, the ion density is larger than the electron density near the material surface, and such a region is called the plasma sheath.

Because the plasma sheath is an essential and unique characteristic of plasma, it is important to derive its basic properties in order to provide a quantitative understanding. The voltage drop over the sheath is of particular interest, as it determines the energy of ions bombarding the surface. For a parallel plate system, as shown in Figure 1.3, one side can be focused on since both material surfaces are symmetrical, as shown in Figure 1.4. Some basic hypotheses should be accepted for simplicity, including:

• The electrons follow a Maxwell-Boltzmann distribution at  $T_e$ , including in the

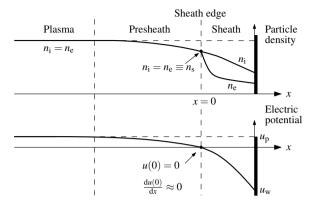

**Figure 1.4** The formation of the plasma sheath and presheath [2].

sheath, as elaborated in the previous section.

- Quasi-neutrality holds at the sheath edge, such that  $n_i = n_e \equiv n_s$  at x = 0, where  $n_s$  represents the density of charged particles at the sheath edge.

- The plasma oscillation is neglected so that the plasma is time-independent [62].

- The sheath is collisionless, so there is no ionization happening within it, and the ion flux is equal along with x (known as the fluid model) [58,62,137].

By assuming these conditions, a better understanding of the fundamental properties of the plasma sheath can be achieved. First and foremost, the conservation of energy must always be upheld. For ions in the sheath, it follows

$$\frac{1}{2}m_{\rm i}v_{\rm i}^2(x) + eu(x) = \frac{1}{2}m_{\rm i}v_{\rm is}^2, \tag{1.11}$$

where  $v_i(x)$  is the ion velocity function with respect to the one-dimensional coordinate x,  $m_i$  is the mass of the ion,  $v_{is}$  is the ion velocity at the sheath edge, and u(x) is the electric potential defined as zero at x = 0, as shown in Figure 1.4. The continuity of the ion flux  $\Gamma_i$  must be guaranteed, leading to

$$\Gamma_{\rm i} = n_{\rm s} v_{\rm is} = n_{\rm i}(x) v_{\rm i}(x).$$

(1.12)

The ion density distribution in the sheath can be obtained by solving (1.11) and (1.12), yielding

$$n_{\rm i}(x) = n_{\rm s} \left( 1 - \frac{2eu(x)}{m_{\rm i}v_{\rm is}^2} \right)^{-\frac{1}{2}}.$$

(1.13)

In an electric field, the electron density is governed by the Boltzmann relation in

thermal equilibrium [2], as described by

$$n_{\rm e}(x) = n_{\rm e}(0) {\rm e}^{\frac{e(u(x) - u(0))}{k_{\rm B}T_{\rm e}}} = n_{\rm s} {\rm e}^{\frac{eu(x)}{k_{\rm B}T_{\rm e}}}.$$

(1.14)

Poisson's equation in vacuum gives

$$\nabla^2 u = -\frac{\rho_f}{\epsilon_0},\tag{1.15}$$

where  $\nabla$  is the gradient operator, and  $\epsilon_0$  is the vacuum permittivity. Based on the assumption that  $n_i = n_e \equiv n_s$  at the sheath edge, the electric potential along the coordinate can be derived according to Equation 1.15, as given by

$$\frac{\mathrm{d}^2 u(x)}{\mathrm{d}x^2} = -\frac{e}{\epsilon_0} \left( n_{\mathrm{i}}(x) - n_{\mathrm{e}}(x) \right) = \frac{e n_{\mathrm{s}}}{\epsilon_0} \left[ e^{\frac{e u(x)}{k_{\mathrm{B}} T_{\mathrm{e}}}} - \left( 1 - \frac{2e u(x)}{m_{\mathrm{i}} v_{\mathrm{is}}^2} \right)^{-\frac{1}{2}} \right]. \tag{1.16}$$

By examining (1.13) and (1.16), it can be deduced that a reasonable value for  $v_{is}$  is required in order for  $n_i$  to decrease along the coordinate x, which is given by

$$v_{\rm is} \ge v_{\rm B} = \sqrt{\frac{k_{\rm B}T_{\rm e}}{m_{\rm i}}},\tag{1.17}$$

where  $v_B$  is called Bohm velocity. Such a requirement is known as the Bohm sheath criterion, which must be satisfied to form a collisionless sheath [144]. The criterion involves extensive mathematics to deal with (1.16), and it is omitted here. Based on (1.5), the RMS ion velocity is  $(3k_BT_i/m_i)^{-1/2}$ , which is negligible compared to  $v_B$  for  $T_i \ll T_e$ . Therefore, Bohm velocity can only be obtained by the acceleration in the electric field in the presheath, *i.e.*, the plasma has a positive potential  $u_p$  with respect to the sheath edge, which is determined by

$$eu_{\rm p} = \frac{1}{2}m_{\rm i}v_{\rm B}^2 = \frac{1}{2}k_{\rm B}T_{\rm e}.$$

(1.18)

Substituting (1.18) into (1.14) leads to the electron density at the sheath edge as

$$n_{\rm S} = ne^{-\frac{1}{2}} \approx 0.61n. \tag{1.19}$$

The ion flux  $\Gamma_i$  can be calculated by

$$\Gamma_{\rm i} = n_{\rm s} v_{\rm is} = n_{\rm s} \sqrt{\frac{k_{\rm B} T_{\rm e}}{m_{\rm i}}}.$$

$$(1.20)$$

To obtain the electron flux on the material surface, the average electron velocity  $v_{\rm e,avg}$  should be calculated, which can be obtained from (1.4) as

$$v_{\rm e,avg} = \sqrt{\frac{8k_{\rm B}T_{\rm e}}{\pi m_{\rm e}}},\tag{1.21}$$

where  $m_e$  is the mass of electron. Therefore, the electron flux  $\Gamma_e$  onto the material surface can be obtained by [24]

$$\Gamma_{\rm e} = n \cdot \frac{1}{4} v_{\rm e,avg} = n_{\rm s} \sqrt{\frac{k_{\rm B} T_{\rm e}}{2\pi m_{\rm e}}} e^{\frac{e u_{\rm w}}{k_{\rm B} T_{\rm e}}}, \qquad (1.22)$$

where  $u_{\rm w}$  is the electric potential of the material surface. To balance the net charge flux during the steady state, the electron flux should be equal to the ion flux on the material surface. Consequently, equalizing (1.20) and (1.22) yields

$$u_{\rm W} = \frac{k_{\rm B}T_{\rm e}}{2e} \ln \left(\frac{2\pi m_{\rm e}}{m_{\rm i}}\right). \tag{1.23}$$

To conclude, in this plasma system, the plasma maintains a positive floating potential respective to the floating material surface, given by

$$V_{\rm p} = u_{\rm p} - u_{\rm w} = \frac{k_{\rm B}T_{\rm e}}{2e} - \frac{k_{\rm B}T_{\rm e}}{2e} \ln\left(\frac{2\pi m_{\rm e}}{m_{\rm i}}\right).$$

(1.24)

This potential difference  $V_p$  is determined by the electron temperature  $T_e$ , electron mass  $m_e$ , and ion mass  $m_i$ . For a typical argon (Ar) plasma with  $m_i = 40$  atomic mass unit (amu) and  $T_e = 56\,000\,\mathrm{K}$ ,  $V_p$  is about 25 V. It implies that the Ar ions are bombarding the material surfaces with an energy  $E_i = 25 \,\mathrm{eV}$ .

The sheath model is derived based on two symmetrical floating surfaces, but it also applies to the case where the two symmetrical surfaces are connected to the same voltage potential (equivalently short-circuited). The voltage potential drop over the sheath should apparently remain the same.

Furthermore, the sheath thickness can be calculated numerically. It is typically thin, in the sub-millimeter to millimeter range [131], and can be approximated by a few Debye lengths  $\lambda_D$  (e.g.,  $5\lambda_D$  in [21]), which is defined by [165]

$$\lambda_{\rm D} = \sqrt{\frac{\epsilon_0 k_{\rm B} T_{\rm e}}{ne^2}}.$$

(1.25)

Therefore, this sheath is also named the Debye sheath.

Readers familiar with semiconductors might experience déjà vu and find an analogy between the plasma sheath and a pn-junction. In a pn-junction, the free-moving electrons in the n-type semiconductor diffuse into the p-type and combine with the holes in the p-type semiconductor. Consequently, in the vicinity of the junction, the p-type has excess electrons and is negatively charged (similar to the material surface). The n-type has excess holes and is positively charged (similar to the bulk plasma). Regions with non-zero net charge form a depletion layer (similar to the

**Figure 1.5** The parallel plate system, in which the material surfaces are asymmetrically biased. Here  $u_a$  and  $u_b$  are the potentials of surface A and B, respectively. The arrow pointing from the minus sign to the plus sign indicates the voltage direction over the sheath.

plasma sheath). An electric field is established towards the p-type, resulting in a built-in potential in the depletion layer (similar to the sheath voltage) [122].

Moreover, both a pn-junction and a plasma sheath have nonlinear capacitances that are voltage-dependent. In fact, a plasma sheath is often modeled by a nonideal diode with a parasitic capacitance in the equivalent circuit model, which will be further elaborated on in the following chapters.

## 1.1.3 High-voltage sheath

Just like a diode that can be negatively biased, a plasma sheath can also be negatively biased to increase the voltage drop over the sheath. This biasing technique is commonly used in semiconductor manufacturing so that ions can be accelerated by a larger voltage in the sheath and bombard the material surface with higher energy. In a biased parallel plate system, as shown in Figure 1.5, it is equivalent to the case where the material surfaces are asymmetrically biased such that  $u_a \neq u_b$ .

The voltage drops in each sheath are  $u_p - u_a$  and  $u_p - u_b$ , respectively, resulting in two different sheaths. Under this circumstance, the plasma potential  $u_p$  is always determined by the more positive one [24]. For example, if  $u_a > u_b$ , the Debye sheath, as previously introduced, is formed between the plasma and surface A, and the plasma potential is equal to  $u_p = u_a + V_p$  (where  $V_p$  is determined by (1.24)).

In practice, surface A can represent the wall of a plasma reactor, which is typically grounded to earth for electrical safety ( $u_a = 0$ ) [146]. Consequently, the voltage drop over the sheath near surface B is determined by  $u_p - u_b = V_p - u_b$ . Such a high voltage drop cannot be fully taken by the Debye sheath, and an extra sheath smoothly joins the Debye sheath, called the Child law sheath [2], as depicted in Figure 1.6. It must be stressed that these "two sheaths" are imposed artificially for better illustration and easier modeling [24], but in reality, there is only one sheath.

**Figure 1.6** The formation of the high-voltage sheath. The presheath still exists, but it is neglected here for simplicity.

Assuming  $|u_b| \gg V_p$  when the surface B is negatively biased by a high voltage,  $V_p$  can be considered zero for simplicity. Similar to deriving the Debye sheath, the conservation of energy for the ions and the continuity of ion flux give

$$\frac{1}{2}m_{\rm i}v_{\rm i}^2(x) + eu(x) = eu_{\rm p} \approx 0 \tag{1.26}$$

and

$$e\Gamma_{i} = en_{i}(x) v_{i}(x) = en_{s}v_{B} = I_{i}, \tag{1.27}$$

respectively, where  $J_i$  is the constant ion current density. Solving (1.26) and (1.27) for  $n_i(x)$  yield

$$n_{\rm i}(x) = \frac{J_{\rm i}}{e} \left( -\frac{2eu(x)}{m_{\rm i}} \right)^{-\frac{1}{2}}.$$

(1.28)

According to (1.14), the electron density  $n_e$  falls exponentially with u(x). Hence,  $n_e$  can be neglected in the Child law sheath, *i.e.*, there exist only ions. Poisson's equation is then written as

$$\frac{\mathrm{d}^2 u(x)}{\mathrm{d}x^2} = -\frac{e}{\epsilon_0} \left( n_{\mathrm{i}}(x) - n_{\mathrm{e}}(x) \right) = \frac{J_{\mathrm{i}}}{\epsilon_0} \left( -\frac{2eu(x)}{m_{\mathrm{i}}} \right)^{-\frac{1}{2}}.$$

(1.29)

Considering the boundary conditions u(0) = 0,  $\frac{du(0)}{dx} = 0$ , and at the surface B  $u(d_{sh}) = u_b$ , where  $d_{sh}$  is the sheath thickness as shown in Figure 1.6, (1.29) can be solved for  $J_i$  as [11]

$$J_{\rm i} = \frac{4}{9} \epsilon_0 \sqrt{\frac{2e}{m_{\rm i}}} \frac{u_{\rm b}^{\frac{3}{2}}}{d_{\rm sh}^2}.$$

(1.30)

(1.30) is known as the Child-Langmuir law [26,99], after which the sheath is named. Furthermore,  $d_{sh}$  can be determined by

$$d_{\rm sh} = \frac{\sqrt{2}}{3} \lambda_{\rm D} \left(\frac{2eu_{\rm b}}{k_{\rm B}T_{\rm e}}\right)^{\frac{3}{4}},\tag{1.31}$$

which can be the order of 100 Debye lengths dependent on the voltage over the sheath [2].

There is a distinct difference between the Debye sheath and the Child law sheath. In the Debye sheath, the ion and electron flux are balanced during the steady state. Thus, there is no net current through the surface. However, in the Child law sheath, the continuous ion flux introduces a net current into the surface because the electron density is almost zero. As a consequence, the bias voltage source  $u_b$  is continuously drawing a constant current from the sheath.

Obviously, the ions bombard the surface B with an energy  $E_i = e(V_p - u_b)$ . By controlling the value of  $u_b$ , the energy of the bombarding ions can be controlled correspondingly for material processing on surface B.

This section provides the necessary fundamentals of plasma for the research. It is also worth noting that the physics model derived in this chapter is based on simplified hypotheses, so it may deviate to some extent from practical scenarios. For further reading, the author suggests referring to the sources cited in the references [2, 23, 24, 161].

## 1.2 Plasma processing

### 1.2.1 Semiconductor manufacturing

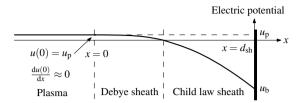

Semiconductors undoubtedly form the bedrock of nearly all modern industries and technologies. The process of creating a commercial semiconductor device from a polished wafer involves hundreds of sequential steps, of which a repeated cycle of essential steps is depicted in Figure 1.7 [1].

In semiconductor manufacturing, deposition (or thin film technology) is a process of growing thin film layers of atom-scale to micrometer range on a substrate [112]. These thin films can be composed of oxides, metals, or other component materials. Figure 1.7(b) shows a typical deposition process for a silicon dioxide ( $SiO_2$ ) layer on the most common silicon (Si) wafer. This layer can act as an insulator in various components, such as the gate dielectric in a metal–oxide–semiconductor field-effect transistor (MOSFET) [134].

After necessary post-deposition cleaning, a photoresist is coated onto the wafer surface [38]. The wafer is then exposed to deep or extreme ultraviolet light in a lithography machine, as illustrated in Figure 1.7(c). The ultraviolet light projects the reticle pattern of the mask to the photoresist through the lens. The exposed portion of the photoresist undergoes a structural change. Either the exposed portion (for positive photoresist) or the masked portion (for negative photoresist) of the

Figure 1.7 The essential processes in semiconductor manufacturing. (a) A silicon wafer. (b) A magnified wafer section after deposition. (c) Lithography process. (d) A magnified wafer section after development. (e) A magnified wafer section after etching. It is worth noting that a photoresist is coated on the wafer surface between (b) and (c), but this process is not drawn here for brevity.

photoresist can be dissolved by a developer, while the other portion remains on the wafer [103]. As a consequence, the reticle pattern is transferred to the photoresist, leaving the exposed portion of the  $SiO_2$  layer ready for removal, and the remaining photoresist acting as an etching mask, as shown in Figure 1.7(d).

Etching is a process to selectively remove the material layers from the substrate surface. In this particular example, we seek to remove the exposed  $SiO_2$  layer as efficiently as possible while retaining the photoresist, the covered  $SiO_2$ , and the underlying Si. This requirement is known as etching selectivity. After etching, the reticle pattern is transferred to the  $SiO_2$  layer, as shown in Figure 1.7(e). Afterwards, the photoresist is tripped.

To produce a complex component like a central processing unit (CPU), these processes must be repeated multiple times with various materials, structures, and operating conditions. Deposition, lithography, and etching are the most crucial processes in semiconductor manufacturing [149]. Plasma is deeply involved in both deposition and etching, which are the primary applications of the technology described in this thesis. While there are other plasma processes in semiconductor manufacturing, such as ion implantation, they are not the focus of this thesis.

#### 1.2.2 Plasma deposition

Although the primary focus is on plasma deposition, it is important to clarify that deposition can occur without plasma involvement. Thermal oxidation, for instance, is the simplest method to grow  $SiO_2$  on Si because Si can be directly oxidized by oxygen  $(O_2)$  at high temperature (ranging from 800 to  $1200\,^{\circ}$ C) [124], as shown in the reaction

$$Si(s) + O_2(g) \xrightarrow{high temperature} SiO_2(s).$$

While thermal oxidation is highly efficient, its application scope is relatively limited. For example, it cannot be applied to the substrates that contain certain metals because the reaction temperature has exceeded the melting points of these metals [75].

Chemical vapor deposition (CVD) is a more versatile method. In CVD, gases or vapor (known as precursors) are decomposed, and solid materials are deposited onto the substrate surface. An example of CVD depositing  $SiO_2$  utilizing silane ( $SiH_4$ ) and  $O_2$  is given as [124]

$$SiH_4(g) + O_2(g) \xrightarrow{430\,^{\circ}\text{C},40\,\text{Pa}} SiO_2(s) + 2\,H_2(g).$$

In this reaction, hydrogen  $(H_2)$  is produced as a by-product. Moreover, CVD could also produce higher-quality materials compared to thermal oxidation [101].

Plasma-enhanced chemical vapor deposition (PECVD) can lower the required temperature of CVD [124] and further extend to more precursors, materials, and structures [68]. Numerous different reactions happen in parallel in PECVD, making it exceedingly complex to describe [98,116]. The reaction's essence is that the plasma provides high-energy electrons, which collide with precursor atoms and molecules, creating chemically reactive radicles by dissociation (an inelastic collision as introduced in the previous section), and enabling the reactions at a lower temperature [68]. The plasma ions can also increase the reaction rates. For example, the positive oxygen ions in the  $\rm O_2$  plasma can directly participate in the oxidation reactions and also help removing the undesired H atoms from SiH<sub>4</sub> [35].

The plasma ion energy is a critical factor in the PECVD process, as it affects the throughput and film quality [113]. It is intuitive to think that adequately increasing the ion energy can enhance the chemical reaction, thus obtaining a higher deposition rate [136,143]. However, too high energy can conversely lower the deposition rate [4]. Furthermore, the energetic ions can lead to defects and damages to the films [104]. It has been observed that low (10 to 30 eV) or intermediate (about 100 eV) ion energies generally have a positive effect on the film quality [114,168].

With the shrinkage of IC devices, a more precise deposition method, named atomic layer deposition (ALD), comes into being, which allows growing thin films layer by layer of sub-nm scale [51]. It is advantageous in conformality and suitable

for growing high aspect ratio (HAR) structures [127]. It introduces two or more precursors sequentially to the substrate surface, where each precursor participates in the chemical reaction at a time and saturates itself. In the case of ALD of SiO<sub>2</sub> on Si, silicon tetrachloride (SiCl<sub>4</sub>) and water (H<sub>2</sub>O) can be used as precursors [155]. First, the Si surface is hydroxylated by water, where hydroxyl groups are formed on the surface [87]. Then the precursor SiCl<sub>4</sub> introduces the half-reaction A as

$$s$$

-Si $-OH(s) + SiCl_4(g) \longrightarrow s$ -Si $-O-Si-Cl_3(s) + HCl(g)$ ,

where s-Y indicates the surface with surface groups Y [92]. After the necessary purge, the second precursor H<sub>2</sub>O (also named by co-reactant) introduces the half-reaction B as

$$s-Si-Cl(s) + H_2O(g) \longrightarrow s-Si-OH(s) + HCl(g).$$

Consequently, a monolayer of SiO<sub>2</sub> is grown. With cyclic reactions, SiO<sub>2</sub> can be grown layer by layer. Such reaction requires a temperature of 327 to 407 °C if without a catalyst [155].

It should not be surprising that plasma-enhanced atomic layer deposition (PEALD) can lower the required temperature [140] and expand to more precursors [171]. Apart from enhancing chemical reactions, recent researches have shown that the plasma ion energy can serve as an additional control degree of freedom to tailor the material properties in PEALD [6,52,138]. Observations suggest that increasing ion energy below certain thresholds can improve properties, while exceeding them can cause degradation [53]. The optimal ion energy varies significantly depending on the materials and processes.

In this thesis, plasma deposition mainly refers to PECVD and PEALD. While there are other deposition methods, such as sputtering, that also utilize plasma, they are not discussed here due to significant differences in their reactors [59].

#### Plasma etching 1.2.3

Speaking of etching, electrical engineers might be familiar with etching a printed circuit board (PCB), in which a solution like ferric chloride (FeCl<sub>3</sub>) is used to remove the unwanted copper. This type of etching with liquid chemicals or etchants is referred to as wet etching. In contrast, plasma etching is considered dry etching, where material is removed by exposing the substrate to plasmas, which generally has better anisotropy than wet etching [126].

The most straightforward plasma etching method is sputtering etching, which uses high-energy ions to bombard the substrate and knock off the surface atoms. This etching method only involves physical reactions. Depending on the applications, the energy of the bombarding ions can range from 50 to 2000 eV [38].

Reactive ion etching (RIE) utilizes both energetic ions and gas phase reactants, resulting in a significantly higher reaction efficiency than sputtering etching or pure chemical reactions [28]. It is now the most widely used etching method in semiconductor manufacturing [38]. The reaction mechanism is complex [81], but similar to PECVD, plasma ions and electrons generate chemically reactive radicles, thus accelerating the chemical reactions. Besides, the normal direction of the ion bombardment enhances anisotropy [39].

Similar to plasma deposition, RIE also critically demands a precise plasma ion energy. Ions with inefficient energy can yield a low etch rate and poorer anisotropy [29,166]. However, ions with excessively high energy can impair the etching mask [38], degrade etching selectivity [175], and damage the structure [90].

Atomic layer etching (ALE) can be regarded as the reversed process of ALD, which can bring material removal to atomic resolution as well [127]. Although ALE can occur with only spontaneous chemical reactions, it is much more common to have energetic species as assistance [105]. For instance, plasma-enhanced atomic layer etching (PEALE) uses energetic ions for material removal in the second half-reaction.

In PEALE, the substrate surface is first exposed to the precursors to weaken the binding energy between the surface and bulk atoms of the substrate [51]. This step aims to modify the surface so that the surface atoms can be removed without affecting the underlying material [85]. Afterward, energetic plasma ions bombard the modified substrate surface, break the bonds of the surface layer of atoms, and release the volatile by-products [163].

As previously mentioned, the binding energy between the surface and bulk atoms of the substrate is lowered in the first half-reaction. The energy of bombarding ions should at least be higher than the lowered binding energy to effectively and completely remove the modified surface. To achieve high selectivity, the bombarding ions should avoid sputtering the underlying bulk. Therefore, the ion energy should not exceed the binding energy between the bulk atoms. Consequently, the required ion energy is located in a range known as the ALE window [127]. This energy window is dependent on the material and process. Under certain circumstances, this energy window can be as narrow as 10 eV such as the plasma ALE of germanium (Ge) using chlorine (Cl<sub>2</sub>) plasma for surface modification [86].

In summary, this section introduces three different plasma etching methods: sputtering etching, RIE, and PEALE. Although other plasma etching methods exist, they are omitted for the sake of brevity.

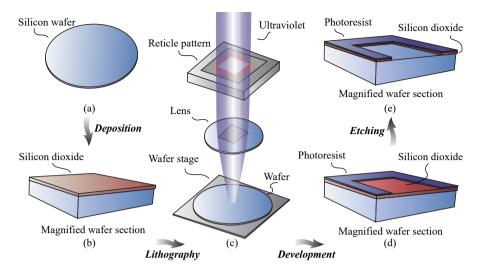

**Figure 1.8** Single-peak and bimodal ion energy distribution. Here  $\Delta E_i$  represents the difference of the ion energy peaks.

#### 1.2.4 Ion energy control

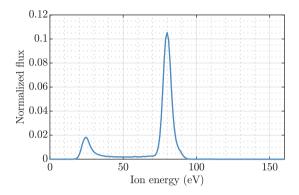

As demonstrated in this section, ion energy plays a predominant role in plasma deposition and etching. It not only affects the reaction rate but also has a crucial impact on the process quality. In most processes, the energetic ions are desired to fall into a specific energy window within a lower and upper bound. This window varies tremendously with different materials, applications, and process recipes and can be very narrow. Additionally, the required ion energy can span a wide range of magnitudes, from typically tens of eV in plasma deposition to thousands of eV in sputtering etching. Such requirements can be translated into a single-peak IED located in an energy window with controllable average ion energy, as shown in Figure 1.8. For comparison, Figure 1.8 also depicts a bimodal IED, which is the most common case in plasma processing.

In a traditional capacitively coupled plasma (CCP), as shown in Figure 1.2, a single power source is used to control the ion density, ion flux, ion energy, and other plasma properties, which can easily lead to plasma nonuniformity [135,148] and makes it difficult to accurately control the ion energy independently of ion flux [2]. To address this issue, dual-frequency CCPs were invented [64,65]. They use a high-frequency RF source to mainly control ion flux and an RF source of a lower frequency to control ion energy separately. Dual-frequency CCP offer better plasma uniformity over large surface areas compared to single-frequency CCPs [13]. However, the coupling effect of the two RF sources can cause issues such as substrate damage or reduced etching rate [102].

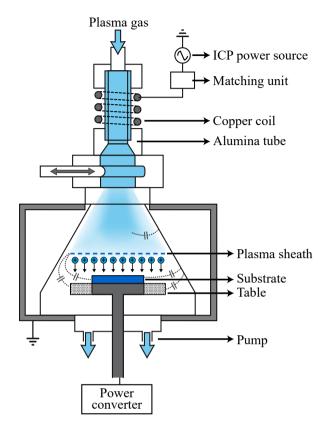

Compared to CCPs, inductively coupled plasmas (ICPs) further decouple the ion energy and flux. ICPs also enjoy the benefit of higher plasma density. A schematic representation of a typical ICP is depicted in Figure 1.9. In this ICP, the RF power is inductively coupled to the plasma across a dielectric window, which is used to excite and sustain the plasma and mainly determines the plasma density and ion flux. The

**Figure 1.9** A typical setup of an inductively coupled plasma reactor. The solid part of the table is covered by the substrate, while the gridded part is directly exposed to the plasma.

substrate is placed on the conductive table for plasma processing. A power converter is connected to the table, biasing the substrate surface potential with specific voltage waveforms and controlling the ion energy. This power converter is also called bias converter, and the output waveform of the bias converter is referred to as the bias waveform in this thesis.

For a conductive substrate, such as a metal, the bias converter can deliver a negative dc voltage directly. The substrate surface potential is equal to the output voltage of the bias converter, thus building a high-voltage sheath (as modeled in the previous section) and accelerating ions toward the substrate surface. By adjusting the output dc value, the ion energy on the substrate can be controlled as desired. However, for a dielectric substrate, such as the most commonly used Si substrate, the substrate surface potential does not exactly equate to the output voltage of the bias converter due

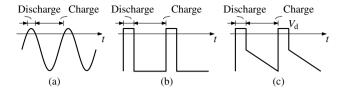

**Figure 1.10** (a) RF biasing voltage waveform. (b) Pulse-shaped biasing voltage waveform. (c) Tailored waveform biasing voltage waveform. Here  $V_{\rm d}$  represents a positive discharge voltage.

to the equivalent capacitance of the dielectric substrate [10]. If a negative dc voltage is suddenly applied to the table, the substrate surface potential initially becomes negative. The bombarding ions then continuously charge the equivalent capacitance and increase the substrate surface potential until it reaches zero. Therefore, a simple negative dc bias voltage cannot control the ion energy for dielectric substrates.

Various biasing techniques for dielectric substrates in ICPs have been studied [44, 139,141], the most typical ones including RF biasing [3,138], pulse-shaped biasing [9, 153,166], and tailored waveform biasing [54,55,70,96,108,111,174,176], the voltage waveforms of which are shown in Figure 1.10(a), (b) and (c), respectively. In all three techniques, the negative parts of the bias waveforms are utilized to create a negative voltage potential on the substrate surface to enhance ion energy. The bombarding ions are charging the substrate capacitance during this time. Therefore, to prevent overvoltage on the substrate, a short positive voltage is periodically applied to attract the electrons and reset the voltage potential, *i.e.*, discharging the substrate.

RF biasing generates a sinusoidal voltage potential on the substrate surface, resulting in a broad and bimodal IED as depicted in Figure 1.8 [119,159], which is not desirable in plasma processing. While increasing the RF biasing frequency can narrow the IED, it is limited by the ion mass and less effective for lighter ions, such as hydrogen. Additionally, a sufficiently large biasing frequency makes the RF wavelength comparable to the substrate dimension, which can cause severe nonuniformities [3].

Pulse-shaped biasing can deliver a narrow single-peak IED, as depicted Figure 1.8 under specific conditions, especially for a dielectric substrate with large capacitance. However, if the substrate capacitance is small, the IED can become heavily distorted since a small substrate capacitance leads to a considerable voltage potential rise due to the charging effect, thus resulting in a broad IED [96]. Although increasing pulse-shaped biasing frequency can reduce this charging effect as well, similar drawbacks occur as with increasing the RF biasing frequency.

In contrast to pulse-shaped biasing, tailored waveform biasing uses a negative voltage slope to compensate for the charging effect. The voltage slope rate should

be well-tuned, and its value is determined by the properties of the substrate and the ion flux. Under this circumstance, the voltage potential of the substrate bottom linearly decreases, keeping the substrate surface potential quasi-constant. Tailored waveform biasing requires a significantly reduced repetition frequency compared to RF and pulse-shaped biasing. The capability of accurate ion energy control makes tailored waveform biasing well-suited for highly-selective plasma processing. It has been proven promising in both PECVD [111,176] and PEALE [54]. This thesis focuses on its derivation and generation.

## 1.3 Research objectives

The primary objective of this research is to develop a power electronics system for plasma processing with tailored waveform biasing. This objective leads to the following major research questions.

- What is the equivalent electric circuit model of plasma processing? To build a power electronics system, the load should be primarily defined, and its EEC model is required for circuit simulation and design. In this application, the load is the complex plasma processing, which is divided into multiple phases in a fundamental period, and its electrical response is peculiar during each phase. The EEC model should reproduce its electrical responses and essential plasma properties, such as IED. Moreover, the parameters of the model should be identified.

- How does the tailored waveform profile influence the ion energy? The tailored waveform profile contains a negative slope and a positive pulse. Both the slope rate and the pulse magnitude affect the ion energy. It is known that the slope rate determines the width of the IED. For each operating condition, there is an optimal slope rate leading to the narrowest IED. However, finding this optimal slope rate requires repetitive manual tuning. An automatic method to find the optimal slope rate is desired. The pulse magnitude determines ion energy. However, whether the entire pulse or just part of the pulse takes effect is unknown. Furthermore, how the pulse duty cycle influences the process remains unsettled. These issues should be related to the EEC model of plasma processing.

- What topology and control strategy should be used for the bias converter? On the one hand, the bias converter should be able to generate various voltage pulses with fast rising and falling edges. On the other hand, it can deliver a linear voltage slope of different slope rates. The uniqueness of the waveform profile calls for a special topology for the bias converter. Moreover, since the load is capacitive, it forms an LC network together with the inductance in the loop. Such an LC network could cause severe resonance, especially during the voltage rising and falling edge of the

**Figure 1.11** The organization of this thesis. The digits in the figure represent the chapter numbers.

voltage pulse. Therefore, it also demands a smart control strategy to damp out or prevent the resonance.

## 1.4 Organization of this thesis

The organization of this thesis is illustrated in Figure 1.11, which depicts the connections between the various research questions and corresponding chapters.

Chapter 1 provides background information on plasma physics and plasma processing applications. Based on the plasma physics, Chapter 2 examines the limitations of the traditional EEC model of plasma processing and presents an improved model that enables the explicit solution of the tailored waveform profile. The factors that determine the optimal slope rate and the effect of the voltage pulse are analyzed in details in this chapter.

In Chapter 3, an auto-tuning method is developed, which can automatically find the optimal slope rate using only the voltage and current measurements on the bias converter side. Besides, the system influence of the RFEA is also elaborated on.

Based on the proposed EEC model, the magnitude of the voltage pulse and the slope rate of the tailored waveform profile can be derived. In return, by applying different waveform profiles, the parameters of the EEC model can be identified with the help of voltage and current measurements. This parameter identification method is introduced in Chapter 4.

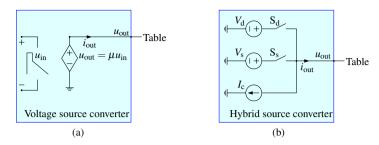

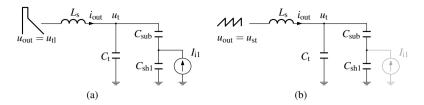

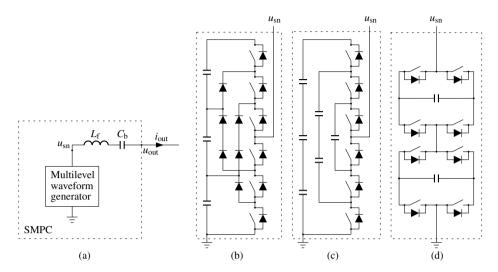

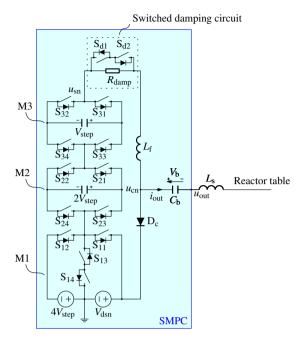

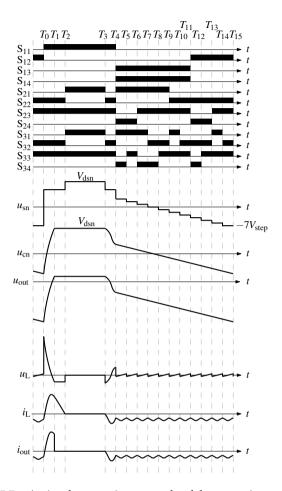

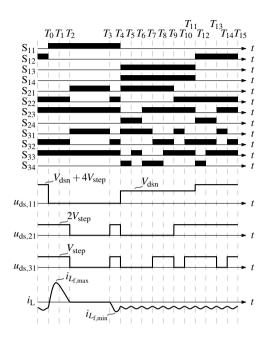

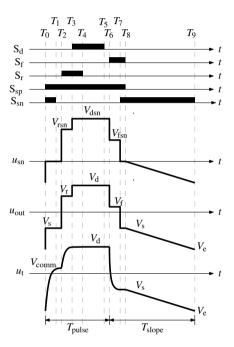

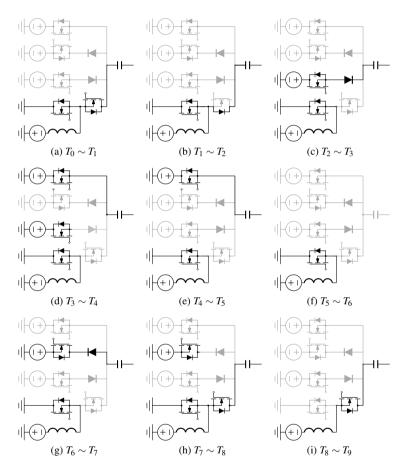

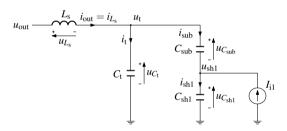

With the EEC model and the waveform profile, the topology of the bias converter can be derived. Chapter 5 analyzes and compares two basic bias converter concepts, the voltage source converter and the hybrid source converter, and introduces a multilevel tailored waveform concept. With a filter inductor, the multilevel tailored waveform can be smoothed into the required tailored waveform. The value of the filter inductance is solved analytically to ensure a qualified ion energy distribution. Based on this concept, a multilevel converter topology is developed to generate the waveform, which consists of a T-type converter and a series of cascaded H-bridge submodules.

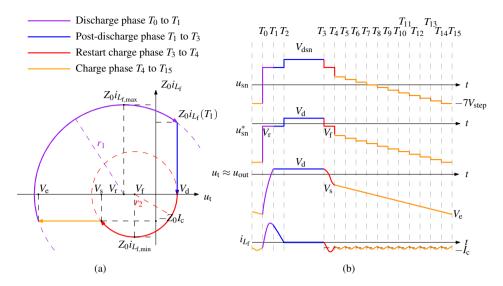

Chapter 6 presents a trajectory control method to damp out the resonance that may be triggered during the rising and falling edges of the pulse due to the LC network formed by the capacitive load and the filter inductance. It uses multiple intermediate voltages to damp out the resonance, which is non-dissipative theoretically. The time duration of each voltage level can be solved analytically based on the trajectory control method, and the required waveform profile can be generated.

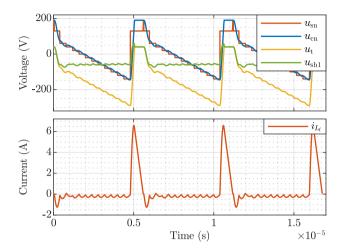

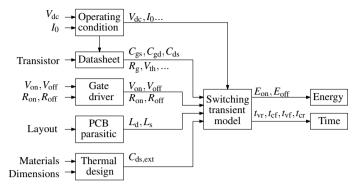

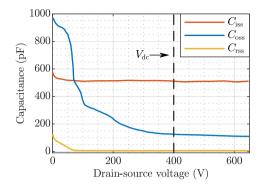

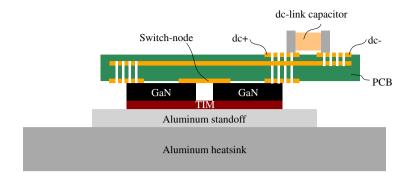

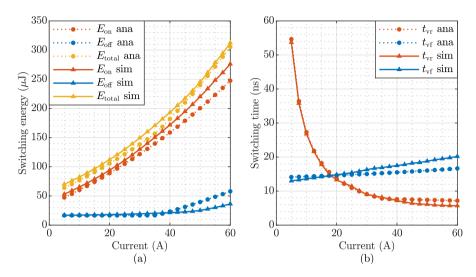

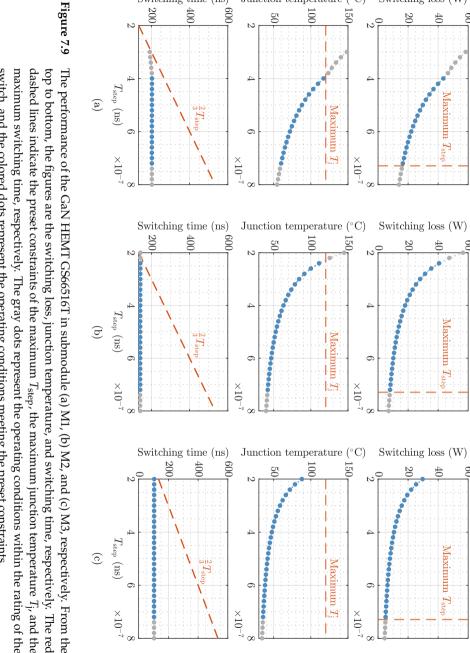

With the trajectory control method, the operating conditions of the switching devices in each submodule of the bias converter, including the switching frequency, voltage, and current, can be obtained. These operating conditions are determined by the selection of the time step of the multilevel tailored waveform. Chapter 7 introduces a switching transient model that can solve the switching loss and time analytically under different operating conditions based purely on datasheet parameters. By knowing the exact limits of the devices together with an accurate estimation of the device stress, the system can be used up to their full capacities.

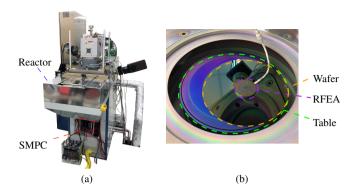

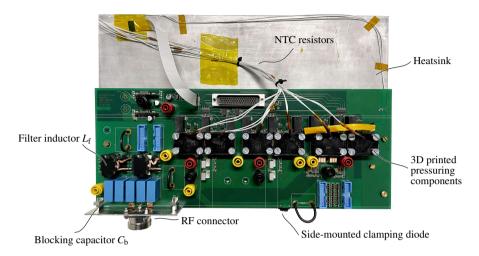

Chapter 8 presents the design of a prototype to validate the analysis provided in the previous chapters. Specially, a passive load is built to emulate the electrical responses of plasma processing, as modeled in the previous chapters. The experimental results confirm the analysis on the model, profile, and converter.

Finally, in Chapter 9, conclusions are drawn, recommendations are given for the future research, and the scientific contributions are summarized.

# CHAPTER

# Model of plasma processing

HE tailored waveforms introduced in the previous chapter are delivered by a bias converter. Traditionally, class-A linear amplifiers have been adopted for this purpose [179], but they are typically energy inefficient. In addition, a tuned matching network is necessary to match the impedance of the linear amplifier and the plasma reactor [138].

Recently, variants of switched-mode power converters have been applied to generate the tailored waveform, which are significantly more energy-efficient than linear amplifiers [5,17,18,40,41,48,49,91,123,187]. These converters also advantageously eliminate the need for a matching network, and they can actively and flexibly generate the required bias waveforms with controllable pulse magnitude and voltage slope rate.

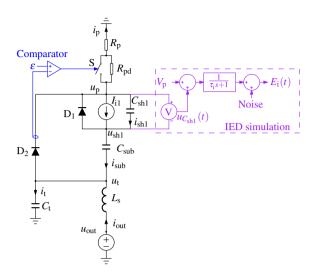

The SMPCs offer significant convenience and flexibility in tailored waveform biasing. However, for electrical engineers, an EEC model of plasma processing is required to conduct circuit simulations and optimize electrical design. For plasma physicists, such a model is also desired to combine the simulation of the bias converter and plasma processing to simulate the IED and optimize the bias waveform. A complete EEC model of plasma processing could enable this combined simulation at the circuit level, which would significantly reduce computation time compared to traditional plasma simulation methods like PIC.

This chapter is based on [183, 186].

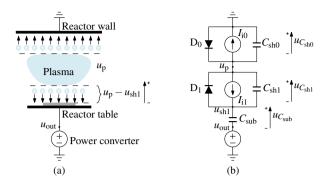

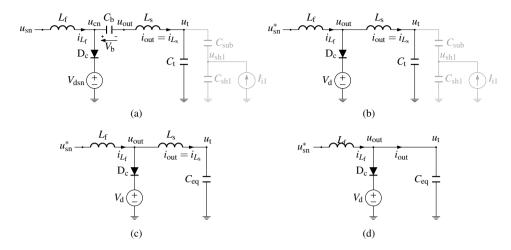

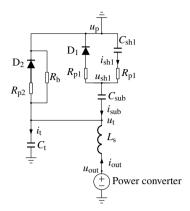

Figure 2.1 (a) An asymmetric parallel plate system representation of the ICP plasma reactor. (b) The traditional EEC model of the ICP plasma reactor. The plasma sheath between the reactor wall and the plasma is modeled by a diode  $D_0$ , a current source  $I_{i0}$ , and a sheath capacitance  $C_{\rm sh0}$  in parallel. The plasma sheath between the substrate and the plasma is modeled by a diode  $D_1$ , a current source  $I_{i1}$ , and a sheath capacitance  $C_{\rm sh1}$  in parallel.

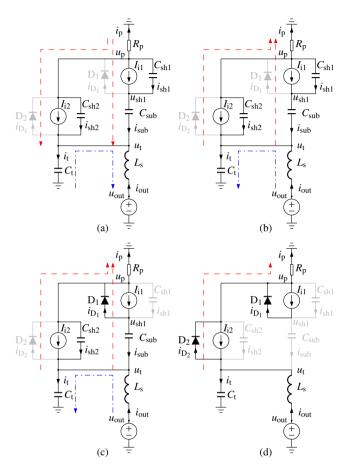

Although some models have been derived in previous researches, most of them are used for RF biasing [2, 34, 60, 108, 138, 147] or a steady-state simplification of tailored waveform biasing [18, 184, 187]. These models cannot be directly used for transient analysis in tailored waveform biasing, as they do not accurately include the discharge process. In [186], a modified model is proposed that emulates the discharge process using a virtual sheath reset circuit. While this modified model can roughly represent the charge and discharge processes and can be used for electric simulation, it significantly increases the complexity of the circuit.

This chapter aims to analyze the limitations of the existing models and propose an improved EEC model that satisfies the requirements of electric waveform and IED simulation at the circuit level.

#### 2.1 Equivalent electric circuit model

#### 2.1.1 Traditional equivalent electric circuit model

As introduced in Section 1.1.2, a parallel plate system is the elementary construction of a plasma system. In a typical ICP reactor, the bulk plasma is confronted with two major surfaces: the grounded reactor wall and the reactor table. The reactor table is electrically connected to the bias converter. The area of the reactor wall is larger than that of the table, so the plasma reactor can be simplified as an asymmetrical parallel

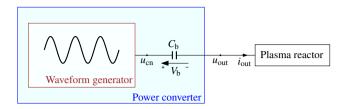

**Figure 2.2** A power converter which is coupled with the plasma reactor with a blocking capacitor. *i*<sub>out</sub> represents the output current of the power converter.

plate system, as depicted in Figure 2.1(a). In most cases, the substrate is dielectric, as indicated by the gray area in the figure.

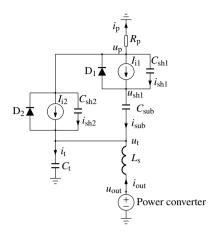

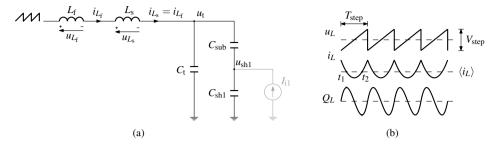

The traditional EEC model focuses on RF biasing as described in [2,60,93,94,138,147], which can be generalized by the EEC model shown in Figure 2.1(b). In this model, two sheaths are formed between the plasma and reactor wall, and the plasma and substrate, respectively. It must be stressed that this model is used to describe the waveform biasing, while the plasma generation in ICP is not modeled and regarded as fully decoupled with the waveform biasing. As demonstrated in Section 1.1.2, the plasma sheath is analogous to a nonideal diode with parasitic capacitance. Therefore, each sheath is modeled by a diode, a sheath capacitor, and a constant current source in parallel. The current source accounts for the equivalent current generated by bombarding ions in a high-voltage sheath. The dielectric substrate is modeled by a capacitor  $C_{\rm sub}$ , and  $u_{\rm sh1}$  represents the substrate surface potential.

In RF biasing, a blocking capacitor is usually used to couple the power converter to the table, as shown in Figure 2.2. Thereby the power converter can be assumed to consist of a waveform generator and a blocking capacitor  $C_{\rm b}$ . The waveform generator delivers the voltage waveforms of desired shapes. In RF biasing, this waveform generator delivers a voltage sinusoidal  $u_{\rm cn}$  given by

$$u_{\rm cn} = V_{\rm rf} \sin\left(2\pi f_{\rm rf}t\right),\tag{2.1}$$

where  $V_{\rm rf}$  is the amplitude of the RF voltage, and  $f_{\rm rf}$  is the RF frequency.

A self-biased blocking voltage  $V_b$  is formed over  $C_b$ , and the output voltage  $u_{\text{out}}$  is shifted to a more negative value with respect to  $u_{\text{cn}}$ . The self-biased voltage  $V_b$  arises from the initial unbalance between the inflow and outflow currents. Once the steady state is reached, the net current flowing through the blocking capacitor is zero in each fundamental period, and  $V_b$  can be considered constant if  $C_b$  is sufficiently large [160]. The bias waveform  $u_{\text{out}}$  is the voltage waveform after the blocking capacitor, and it can be described by

$$u_{\text{out}} = V_{\text{rf}} \sin\left(2\pi f_{\text{rf}}t\right) - V_{\text{b}}.\tag{2.2}$$

In the traditional model, the bombarding ions enter the sheath with an initial energy equal to  $eu_p = -eu_{C_{\rm sh0}}$ . For simplicity, it can be assumed for now that the sheath thickness is negligible so that the ion transit time in the sheath is much shorter than the RF period. As a result, the extra energy that ions obtained in the sheath due to the acceleration in the electric field is equal to  $eu_{C_{\rm sh1}}$ , which is determined by the instantaneous value of  $u_{C_{\rm sh1}}$  at the moment when ions enter the sheath.

During the steady state in RF biasing,  $C_{\text{sh0}}$ ,  $C_{\text{sh1}}$ , and  $C_{\text{sub}}$  constitute a capacitive voltage divider. As a result, the voltages over these capacitors are determined by

$$\begin{pmatrix} u_{C_{\text{sh0}}} \\ u_{C_{\text{sh1}}} \\ u_{C_{\text{sub}}} \end{pmatrix} = - \begin{pmatrix} \frac{1}{C_{\text{sh0}}} \\ \frac{1}{C_{\text{sh}}} \\ \frac{1}{C_{\text{sub}}} \end{pmatrix} \cdot \frac{V_{\text{rf}} \sin(2\pi f_{\text{rf}}t)}{\frac{1}{C_{\text{sh1}}} + \frac{1}{C_{\text{sub}}} + \frac{1}{C_{\text{sub}}}} + \begin{pmatrix} V_0 \\ V_1 \\ V_{\text{sub}} \end{pmatrix},$$

(2.3)

where  $V_0$ ,  $V_1$ , and  $V_{\text{sub}}$  are the dc offset voltages over  $C_{\text{sh0}}$ ,  $C_{\text{sh1}}$ , and  $C_{\text{sub}}$ , respectively. The values of  $V_0$ ,  $V_1$ , and  $V_{\text{sub}}$  are determined by the bias waveform and the capacitance values. According to Kirchhoff's voltage law, they are governed by

$$V_0 + V_1 + V_{\text{sub}} = V_{\text{b}}. (2.4)$$

Since  $C_{\rm sh0}$  cannot be positive and  $C_{\rm sh1}$  cannot be negative due to the diodes,  $V_0$  and  $V_1$  should satisfy the constraints:

$$\begin{cases} V_{0} \leq -\frac{\frac{1}{C_{\text{sh0}}}}{\frac{1}{C_{\text{sh0}}} + \frac{1}{C_{\text{sh1}}} + \frac{1}{C_{\text{sub}}}} V_{\text{rf}} \\ V_{1} \geq \frac{\frac{1}{C_{\text{sh1}}} + \frac{1}{C_{\text{sh1}}} + \frac{1}{C_{\text{sub}}}}{\frac{1}{C_{\text{sh1}}} + \frac{1}{C_{\text{sub}}}} V_{\text{rf}} \end{cases}$$

(2.5)

The ions bombard the substrate surface with an energy equal to

$$E_{\rm i}(t) = e \left( u_{\rm p}(t) + u_{\rm C_{\rm sh1}}(t) \right),$$

(2.6)

which can be described by

$$E_{i}(t) = \frac{\frac{1}{C_{sh0}} - \frac{1}{C_{sh1}}}{\frac{1}{C_{sh0}} + \frac{1}{C_{sh1}} + \frac{1}{C_{sub}}} V_{rf} \sin(2\pi f_{rf}t) + V_{1} - V_{0}.$$

(2.7)

Since the asymmetrical sheath yields  $C_{\text{sh}0} \neq C_{\text{sh}1}$  [147], the bombarding ions have an average energy equal to  $e(V_1 - V_0)$  and an energy variance  $\Delta E_i$  equal to

$$\Delta E_{\rm i} = eV_{\rm rf} \left| \frac{\frac{1}{C_{\rm sh0}} - \frac{1}{C_{\rm sh1}}}{\frac{1}{C_{\rm sh}} + \frac{1}{C_{\rm sh}} + \frac{1}{C_{\rm sub}}} \right|. \tag{2.8}$$

This results in a bimodal IED as shown in Figure 1.8.

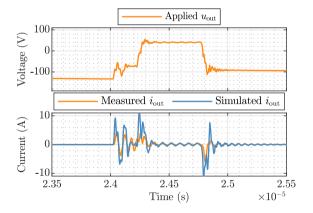

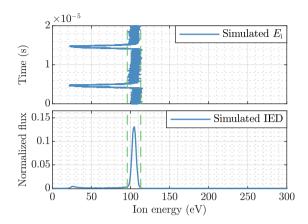

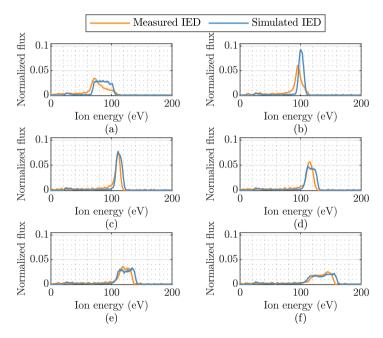

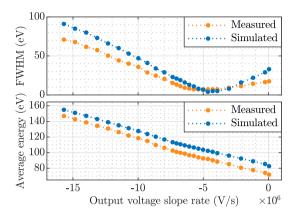

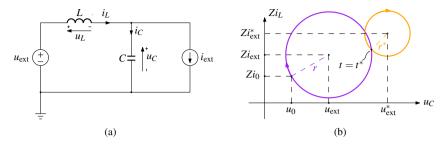

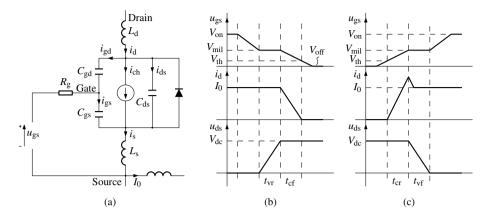

In practice, the ion transition in the sheath takes time, since the thickness of the high-voltage sheath is much larger than a Debye length and ions have a finite velocity, as introduced in the previous chapter. Therefore, the extra energy that ions obtain in the sheath is the average of  $eu_{C_{\rm sh1}}(t)$  over the ion transit time. This effect acts as an energy damper and can reduce the width of the IED, leading to a smaller  $\Delta E_{\rm i}$ . Furthermore, it also explains why higher  $f_{\rm rf}$  induces narrower IED, as introduced in Section 1.2.4, as ions can perceive an average voltage over multiple fundamental periods instead of a small portion of the RF waveform. Therefore,  $f_{\rm rf}$  is typically in the megahertz magnitude range [158].