# A Construction Kit for Efficient Low Power Neural Network Accelerator Designs

PETAR JOKIC, CSEM, Switzerland and ETH Zurich, Switzerland ERFAN AZARKHISH, ANDREA BONETTI, MARC PONS, and STEPHANE EMERY, CSEM, Switzerland

LUCA BENINI, ETH Zurich, Switzerland and University of Bologna, Italy

Implementing embedded neural network processing at the edge requires efficient hardware acceleration that combines high computational throughput with low power consumption. Driven by the rapid evolution of network architectures and their algorithmic features, accelerator designs are constantly being adapted to support the improved functionalities. Hardware designers can refer to a myriad of accelerator implementations in the literature to evaluate and compare hardware design choices. However, the sheer number of publications and their diverse optimization directions hinder an effective assessment. Existing surveys provide an overview of these works but are often limited to system-level and benchmark-specific performance metrics, making it difficult to quantitatively compare the individual effects of each utilized optimization technique. This complicates the evaluation of optimizations for new accelerator designs, slowing-down the research progress.

In contrast to previous surveys, this work provides a *quantitative* overview of neural network accelerator optimization approaches that have been used in recent works and reports their *individual* effects on edge processing performance. The list of optimizations and their quantitative effects are presented as a construction kit, allowing to assess the design choices for each building block individually. Reported optimizations range from up to  $10,000 \times$  memory savings to  $33 \times$  energy reductions, providing chip designers with an overview of design choices for implementing efficient low power neural network accelerators.

$CCS\ Concepts: \bullet\ Computing\ methodologies \rightarrow Neural\ networks; \bullet\ Hardware \rightarrow\ Application\ specific\ integrated\ circuits;$

Additional Key Words and Phrases: Edge processing, hardware accelerator, design optimization

# **ACM Reference format:**

Petar Jokic, Erfan Azarkhish, Andrea Bonetti, Marc Pons, Stephane Emery, and Luca Benini. 2022. A Construction Kit for Efficient Low Power Neural Network Accelerator Designs. *ACM Trans. Embedd. Comput. Syst.* 21, 5, Article 56 (October 2022), 36 pages.

https://doi.org/10.1145/3520127

This work was supported in part by the Electronic Components and Systems for European Leadership Joint Undertaking ANDANTE under Grant 876925 and in part by the Swiss National Science Foundation (SNSF) BRIDGE under Grant 40B2-0\_181010.

Authors' addresses: P. Jokic, CSEM: Technoparkstrasse 1, Zurich, ZH (state), 8005, Switzerland; email: petar.jokic@csem.ch; E. Azarkhish, A. Bonetti, M. Pons, and S. Emery, CSEM, Technoparkstrasse 1, Zurich, ZH, 8005, Switzerland; emails: {erfan.azarkhish, andrea.bonetti, marc.pons, stephane.emery}@csem.ch; L. Benini, ETH Zurich: Gloriastrasse 35, Zurich, ZH, 8092, Switzerland, Switzerland and University of Bologna: Viale del Risorgimento 2, Bologna, BO, 40136, Italy; email: lbenini@iis.ee.ethz.ch.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2022 Copyright held by the owner/author(s). Publication rights licensed to ACM.

1539-9087/2022/10-ART56 \$15.00

https://doi.org/10.1145/3520127

56:2 P. Jokic et al.

## 1 INTRODUCTION

Machine learning (ML) algorithms, especially neural networks (NN), have been widely used to provide smart systems with complex data analysis capabilities like visual object detection [1] and audio key-word spotting [2]. While NNs enable algorithm developers to implement difficult-to-model tasks, given that sufficient training data is available, their computational complexity is challenging the design of processing hardware. Miniaturized and battery-powered ML applications thus require high computational throughput while being limited to low power consumption, rendering computing efficiency a key design objective for low power ML accelerators. The rapid progress of ML algorithm research further challenges designers to quickly adopt newly introduced network features, requiring fast development times. While fully-connected (FC) and convolutional neural networks (CNN) like AlexNet [3] have dominated the field during the past decade, residual networks (ResNet) [4], recurrent NNs (RNN) and derivations like dense CNNs [5] have gained importance, claiming ever-improving algorithm performance. What remains constant are the working horses of NNs, namely parallelized multiply-and-accumulate (MAC) operations.

Improving computing efficiency has been a key driver for the invention of laptops (~2000), smartphones (~2010) and high-performance server operation [6]. The current decade (~2020) strives for ubiquitous smart devices like wearables and **internet-of-things (IoT)** nodes [7], capable of processing sensory data. Performing data analysis on the sensor nodes at the edge of a connected network, so-called edge processing [8] or edge intelligence [9], can significantly reduce latency and power consumption but requires efficient ML accelerators.

Thus, edge processing is increasingly used in applications where long battery lifetimes are mandatory, e.g. in smart glasses with object detection [10], face detection [11], or hand-gesture and speech recognition [12], as well as smart cameras with automatic acquisition using scene classification [13], smart doorbells with face recognition [14], or tools that help blind people read texts and recognize people [15]. Many more could benefit from edge ML in the future [16, 17]. An overview of ML applications that are feasible on current hardware platforms is summarized in [18], illustrating the challenge of the limited edge processing power budget (<1W).

Existing ML accelerator chips cover the application domain from **ultra-low power (ULP)** and low-complexity processing, implementing 18uW key-word spotting with 105kB on-chip memory [19], to high-throughput server-grade acceleration, provided by chips like Google TPUv3 [20] or Graphcore IPU [21], consuming more than 100W. Allowing edge processing devices to run more complex ML applications, which can currently only be computed in cloud servers, requires more efficient edge ML accelerators. To identify relevant accelerator designs among the vast number and diversity of publications proposing efficient implementations, quantitative surveys are necessary. However, existing surveys often only provide qualitative comparisons or benchmark implementations on a system-level, obscuring the individual effects of each employed optimization technique. Comparing these optimizations is essential for motivating design choices during the development of new accelerators, currently requiring time-consuming literature research.

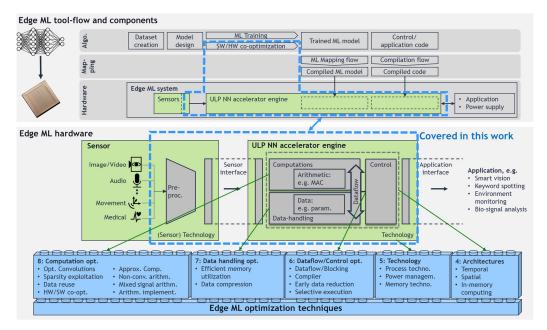

This work summarizes and, for the first time, quantitatively compares design optimizations of existing NN accelerators for tiny (<10mW) and edge (<1W) processing applications. It is presented as a construction kit, listing optimization options for each building block along with their reported quantitative effects, enabling **application-specific integrated circuits (ASIC)** designers to evaluate and assess optimizations for new implementations. Figure 1 illustrates the covered building blocks on a generic end-to-end edge processing system and localizes optimizations within the edge ML design flow.

The paper is organized as follows: Section 2 presents related surveys that complement this work. Section 3 introduces basic notations used throughout the paper, followed by an overview

Fig. 1. Overview of the edge ML tool flow with a summary of the discussed hardware optimizations for NN accelerators (with chapter numbers of the paper).

of architectures in Section 4, technological optimizations in Section 5, dataflow optimizations in Section 6, data handling optimizations in Section 7, computation optimizations in Section 8, and finally, the quantitative comparison of all relevant optimizations in Section 9.

#### 2 RELATED WORK

Various surveys have been conducted to summarize existing NN accelerator designs and implementations, explaining their techniques, and comparing their system-level performance.

To keep track of the vast number of academic and industrial ML hardware accelerators proposed every year, a periodically updated online list [22] is provided, listing the main performance metrics for each chip to compare them in terms of power, throughput, and computational efficiency. A similar survey in paper form was presented in 2019 [23] and updated in 2020 [24]. It lists the computational performance and precision of academic research works and commercially available devices. A survey from 2017 claims to cover the past 35 years of works in neuromorphic computing, listing more than 2,600 references that accelerated the research field since the 1980s [25]. It covers models, learning approaches and hardware ranging from analog to digital implementations, covering programmable FPGAs and custom ASICs.

Sze et al. [26] provide a thorough survey on efficient processing of **deep NNs (DNN)**, covering historic aspects, common layer types, training frameworks and popular datasets, extending their previous work [27]. The sections on hardware platforms and energy efficient dataflows are motivated in their preceding work [28], proposing edge processing for extracting meaningful information to reduce the extreme amount of data produced by the ever-increasing number of sensors in connected devices. A similar summary is presented in [29] and a more FPGA-focused one in [30].

Another well-structured and exhaustive survey on DNN acceleration is presented in [31], covering existing hardware acceleration approaches including software optimizations, and a chapter on security of DNN approaches and their benchmarking. Survey [32] presents a broad overview of

56:4 P. Jokic et al.

| Work (Year)       | Optimizations                                         | Throughput [GOPS]            | Efficiency   |

|-------------------|-------------------------------------------------------|------------------------------|--------------|

|                   |                                                       |                              | [TOPS/W]     |

| ShiDianNao (2015) | Local data reuse                                      | 194 (16b)                    | 0.606        |

| EIE (2016)        | Sparsity, weight sharing, compression, zero skipping  | 102 (16b)(~3'000 *)          | 0.17 (5.0 *) |

| Envision (2017)   | Multi-precision, DVFAS, body biasing                  | 76 (4b)                      | 10           |

| Eyeriss (2017)    | Local data reuse, zero compression, zero skipping     | 84 (16b)                     | 0.166        |

| YodaNN (2018)     | Binary weights, standard-cell memory, voltage scaling | 1'500 (1b w., 12b a.)        | 1,1          |

| UNPU (2018)       | Multi-precision, LUT-based bit-serial MAC (1-16b)     | 346/7372 (16b/1b w., 16b a.) | 3.1/50.6     |

| Eyeriss v2 (2019) | Local data reuse, sparsity, compressed computing      | 202 (8b)                     | 0.963        |

Table 1. Selected ML Accelerator Chips from Previous Years

the ML field, focusing on big data, training techniques, and applications. A similarly broad view, additionally covering the transition from modelling biological NNs to implementing artificial NNs in hardware is presented in [33], focusing on novel memories and their use-cases in the field.

In the survey of [34], various ML accelerators and processing blocks are presented and compared to their research group's own works. They list neuromorphic processors, including spiking NN engines, ranging from fully digital to fully analog computations, and discuss possible future directions. Survey [35] also discusses the architectures of selected DNN accelerators and explains their working principles and supported networks.

Surveys [9] and [36] present an extended view on edge intelligence, covering pure edge processing and combinations with cloud processing. They discuss related optimization strategies, namely compression and early model exit.

While the listed related works give an excellent overview of existing ML accelerators and optimization techniques, none of them attempted to quantitatively compare used optimization approaches, as covered in this work, allowing designers to evaluate and assess optimizations for new implementations.

This work focuses on (deep) NN inference, noting that the field of ML is much broader, containing other approaches like support vector machines, decision trees and many others.

## 3 CONSTRUCTION KIT FOREWORD

ML accelerators often combine multiple optimization techniques, as shown in Table 1, summarizing a selection of relevant accelerator chips from the past six years. This complicates the assessment of individual optimizations as their effects are obscured by system-level benchmarking. Thus, we only add individual optimizations to the comparison and only if sufficient quantitative information is reported. We focus on five performance indicators, namely (1) energy/power, (2) area (cost), (3) memory size, (4) computational throughput, and (5) impact on algorithmic accuracy.

In the following sections, we briefly discuss the importance of a system-level view for meaningful optimization evaluations and introduce some basic performance indicators and notations that are used throughout the paper.

#### 3.1 System-Level View

Edge ML devices process sensory data onboard, communicating with sensors (and memories) for subsequent analysis in an ML engine. Regardless of this fact, publications on low-power ML accelerator designs often neglect the impact of such off-chip communication on system-level power consumption and performance. Analyzing system-level power-breakdown helps to identify

<sup>\*</sup>including skipped operations.

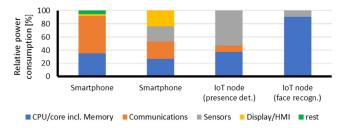

Fig. 2. Power break-down of mobile/edge systems (smartphones [44], presence detection IoT node [45], and face recognition IoT node [46]).

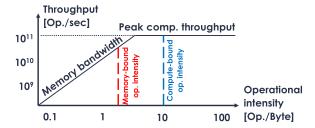

Fig. 3. Roofline plot showing two operating points, constrained by the available memory bandwidth and the computational throughput.

power-dominating sub-systems, allowing to optimize them based on the Pareto principle. Figure 2 shows the power breakdown of four mobile system implementations: two smartphone analyses were taken from a smartphone battery usage review [44], showing dominating communication power, while two IoT nodes were evaluated in a visual presence detection system [45] and an always-on face recognition system [46], reporting dominating sensor and processing power. While core optimizations would only enable marginal system improvements in the first three systems, the fourth example shows a typical edge ML IoT node with processing-dominated power distribution, enabling significant system improvements through core optimizations.

#### 3.2 Meaningful Performance Indicators and Metrics

To identify useful optimization strategies, relevant performance indicators and benchmarks must be chosen. Parameter quantization, for example, can easily reduce memory size but also heavily impacts accuracy [47, 48]. Similarly, the throughput is subject to large variations across different workloads as pointed out in [23], reporting  $20 \times$  lower throughput than stated in the datasheet. Thus, application-relevant benchmarks are indispensable. For a fair cross-device comparison, standard ML benchmarks have been created for smartphones [49] and for general purpose devices (MLPerf) [50] and are now adopted to edge devices (TinyMLPerf) [51]. This is similar to microcontroller benchmarks (e.g. CoreMark [52]).

Roofline models [53] are used to visualize the architectural boundaries of a system's operating points, namely the memory bandwidth and the peak computational throughput, as illustrated in Figure 3. Depending on the operating point, the system operates in a memory- or a computation-bound region.

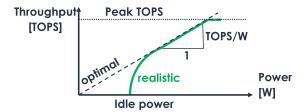

NN accelerator performance metrics are often limited to the peak throughput, in **tera operations per second (TOPS)**, and the computational power efficiency (TOPS/W). Figure 4 illustrates that these metrics can be misleading in edge applications, operating in the low power region where extrapolating the efficiency becomes inaccurate (idle power).

56:6 P. Jokic et al.

Fig. 4. NN processing throughput versus power consumption.

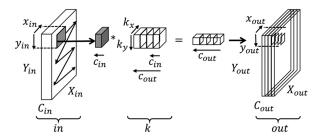

Fig. 5. Generic CNN layer with dimension notations.

#### 3.3 Neural Network Notations

Figure 5 illustrates a generic NN layer along with the notations of layer dimensions that we use throughout the paper. The input activations in have  $C_{in}$  input channels and extend  $X_{in} \cdot Y_{in}$  in spatial dimensions. All  $C_{out}$  kernels contain  $C_{in} \cdot k_x \cdot k_y$  parameters and generate output activations out of dimension  $X_{out} \cdot Y_{out}$  with  $C_{out}$  output channels. While a generic convolution layer is shown here, it also covers dense (FC) layers, which have restricted dimensions  $k_x = k_y = X_{in} = Y_{in}$  and  $X_{out} = Y_{out} = 1$ . Other layer types can be described using the same notation, e.g. ResNets have additional bypass inputs  $in_{by}$  of the same dimension as in and are added point-wise. Depth-wise separable CNNs split kernels in the  $C_{in}$  dimension, yielding  $C_{out} = C_{in}$ , avoiding cross-channel links.

#### 4 HARDWARE ARCHITECTURES

Two main architectural concepts are dominating today's NN accelerators [27]: temporal and spatial architectures. This section discusses them and adds emerging in-memory computing as a third concept, offering a distinct data flow. While temporal architectures sequentially access the memory, process the data, and finally return the results, spatial architectures aim at reducing these data movements by sharing activations and parameters across neighboring processing elements. In-memory computing offers an orthogonal concept that tries to entirely remove data movements by computing data directly inside the memory.

## 4.1 Temporal Architecture

Temporal architectures comprise, among others, the wide-spread **central processing units** (CPU) and **graphic processing units** (GPU), featuring a central control unit that schedules tasks and distributes computations across **arithmetic logic units** (ALU). Data is moved from the memory to the ALU and back, offering a high parallelization potential using **single instruction**, **multi-data** (SIMD) instructions for vector processing. This is based on the traditional Von Neuman architecture [54], characterized through a generic **single instruction**, **single data** (SISD) processing scheme that stores both instructions and data in the memory. It typically features a

control unit that reads instructions and data from the memory, an ALU to perform the operations, and a data bus to communicate across blocks and through a peripheral interface.

Multi-issue processors [55], e.g. super-scalar processors, extend this concept by enabling multiple parallel operations through a single instruction, reducing the control overhead, to increase the operational intensity (see Figure 3).

## 4.2 Spatial Architecture

In contrast to temporal architectures, spatial architectures allow their arithmetic units, often called **processing elements (PE)**, to move data between neighboring PEs, allowing to reduce memory accesses by employing local buffers.

Systolic arrays are pipelined 2D spatial architectures that enable data reuse across neighboring PEs. This can be exploited for implementing efficient **general matrix multiplication (GEMM)** through contraction ("systole" in old Greek) of computations, reusing results from adjacent nodes, and thus minimizing memory accesses. This is exploited in many prominent accelerators like Google TPU [56] and Eyeriss [57]. Replacing single-PE systolic arrays with tensor-PEs, each one computing an entire matrix multiplication per cycle, further allows reducing area and power in a 16nm process by 2.1× and 1.4x, respectively [58]. Increased intra-PE data reuse and fewer pipeline buffer registers enable this improvement but require efficient load distribution to avoid low PE utilization. SCALE-Sim [59] provides a simulation tool to evaluate such design parameters, comparing different dataflows and arrays.

## 4.3 In-memory Computing

The motivation behind in-memory computing, or **compute-in-memory (CIM)**, is the data-intensive nature of neural network inference, requiring high memory bandwidths which result in memory-dominated performance [60], the so-called memory wall [61]. To mitigate this, computations can be directly performed in the memory, where high data access rates are available at a much lower power cost. While the computational efficiency can be largely increased with this approach, it increases the overhead in the memory and limits the flexibility. Combined with analog memory types, the efficiency can be further improved by computing directly in the analog domain. Analog CIM computes matrix multiplications by breaking them down into vector dot products [62], multiplying analog input voltages (activations) with NVM cell conductances (weights) and accumulating the resulting column current (MAC result). Special design considerations to achieve high accuracy inference along with high computational efficiency are discussed in [60].

SRAM-based CIM is presented in [63], using a 55nm 8T 3.8kb SRAM macro with support for 1–4b input activation and 1–5b weights. The 130nm circuit in [64] demonstrates simple down-sampled MNIST computations, reporting 13× system energy reduction for 1b weight and 5b activation precision compared to a traditional (out-of-memory) computation. CIM integrated in the analog SRAM periphery is evaluated in [65] on a simulated 65nm process, reporting 4.9× system energy efficiency and 2.4× throughput improvement compared to digital processing. A 384kb SRAM-based 8b precision CIM in 28nm [66] is demonstrated to have 28% area overhead compared to a pure SRAM array while achieving up to 22.75TOPS/W throughput.

Non-volatile memory (NVM)-based CIM implementations are summarized in [62]. Their previous survey [67] provides a comprehensive list of the utilized emerging NVMs, illustrating that NVM can increase bit density and reduce leakage compared to SRAM and possibly store multiple bits per cell. In [68] an MRAM-based 54×108 CIM crossbar is presented in a 180nm process (MRAM on top of CMOS circuit). Over-lifetime variations of up to 4.2% and device-to-device variations of 4.5% have been reported, requiring special considerations (e.g. [69]).

56:8 P. Jokic et al.

Among many other RRAM works, a 1Mb multibit CIM on a 55nm process [70] and a 128×64b CIM array [71] on a 90nm process are presented. NVM-based CIM is an active field of research with various directions, for example 3D CIM architectures [72], reporting up to 28.6× higher energy efficiency compared to 2D chips. A CIM benchmarking tool [73] further reports advantages of NVM- over SRAM-based CIM implementations in a 32nm process, while 7nm SRAM CIM still outperforms any NVM-based work in throughput and both area and energy efficiency.

Note that also DRAM has been used for CIM [74], however, targeting high performance server applications which goes beyond the scope of this work.

#### 5 TECHNOLOGY

**Integrated circuits (IC)** for NN accelerators are strongly influenced by the underlying semiconductor technology. This chapter introduces common process technologies and related power optimization techniques that are employed in various optimizations throughout the paper, followed by an overview of memories, which are often linked to process technologies and tend to dominate the performance of ML hardware accelerators (see Section 3.1).

## 5.1 Semiconductor Process Technology

Annual improvements in semiconductor manufacturing technology have been a major driving force in the chip industry as indicated by the (now saturating) Moore's law [75, 76], empirically predicting the doubling of component density on chips every 1–2 years. However, the smaller process nodes increased the static power consumption, resulting in the end of Dennard scaling [77]. This related heuristic scaling trend factor describes the annual shrinking of the minimum feature size in silicon chips and related power savings, culminating in the so-called power wall [78], limiting process improvements because the increased power density has approached physical limits of silicon-based circuits over the past few years.

This process scaling enables significant power reductions [79], as it yields lower supply voltages and smaller switching capacitances. However, improved process technologies are often linked to a significant cost increase and might not support all features of older technologies (e.g. special memory types, photo diodes, etc.). Multi-die solutions can mitigate this problem, exploiting the properties of multiple processes across the dies, each one optimized for a specific target like reduced cost, specialized memory support, or high logic density [17, 80]. Combining multi-process solutions with 3D die stacking additionally provides short communication paths and increased densities, as shown in the 8-die-stacked NN accelerator with 96MB of memory [81].

The following sub-sections give a brief introduction of the main semiconductor process technologies used today as they will be referred to throughout the paper. We limit the scope to **complementary metal-oxide-semiconductor (CMOS)** technology, which dominates digital designs and refer the interested reader to the annual IEEE white paper on future directions of semiconductor technologies (e.g. the 2020 update [82]) for a look into possible future directions.

5.1.1 Bulk. Bulk technology is based on standard silicon wafers and mainly evolves through spatial scaling. However, these annual scaling improvements are slowing down due to increasing difficulties with electrostatic and short-channel effects [83].

**Deeply depleted channel (DDC)** technology improves bulk technology by introducing multiple vertical doping regions in the channel, forming a threshold setting region and a biascontrollable screening region [84]. This enables reduced supply voltages, low leakage, low process variation as well as improved body biasing characteristics, allowing to dynamically adjust the threshold voltage of the transistor.

- 5.1.2 FinFET. The introduction of 3D gates in so-called FinFETs, improved on the performance of bulk CMOS by enabling lower supply voltages, and thus reduced power consumption, as shown for 22nm tri-gate FinFET [83] and later 14nm FinFET [85]. However, the improved performance comes at a higher production cost due to the complex 3-dimensional structures, requiring more fabrication masks than the bulk technology [86–88].

- 5.1.3 FD-SOI. Fully depleted silicon-on-insulator (FD-SOI) technology employs very thin insulating layers in the substrate of the transistors, reducing leakage. In [87] a 22nm FD-SOI technology is presented, achieving on par power and performance efficiency compared to 16/14nm FinFET technology while being lower cost due to the use of a planar processes, requiring fewer masks. Thus, FD-SOI is more suitable for low-end mobile and IoT applications where cost is an important factor. A detailed comparison between FD-SOI and FinFET is provided in [86], reporting superior performance of FinFETs in terms of power, delay, and density, for which FD-SOI can compensate through **body-biasing (BB)**. BB allows to dynamically adjust the threshold voltage, boosting speed with a forward body bias or reducing leakage using reverse body biasing (higher threshold).

- 5.1.4 Specialized Processes. Recent advances in materials and manufacturing technologies have enabled the integration of novel memory technologies (both volatile and non-volatile) close to processing logic. They offer advantageous characteristics that go beyond transistor density scaling. However, most of them require special process technologies, making them more difficult to integrate within the widely available processes. More details on novel memories can be found in Section 5.3.

## 5.2 Power Management

The power consumption of ICs [78] can be decomposed into dynamic and static power. Dynamic power is described in Equation (1), taking the circuit switching operations into account. Variable U is the supply voltage, C the switching capacitance,  $\alpha$  the switching activity and f the frequency of the circuit. Static power, often also called leakage power, is described in Equation (2), reflecting the current consumption  $I_{leak}$  when no switching takes place.

$$P_{dynamic} \sim \frac{1}{2} \cdot U^2 \cdot C \cdot \alpha \cdot f \tag{1}$$

$$P_{static} \sim U \cdot I_{leak}$$

(2)

Based on these equations, various optimizations have been proposed to reduce the overall power consumption, using the supply voltage and the frequency as control knobs. The most prominent techniques are listed in the following section, namely sub- and near-threshold operation, **adaptive body biasing (ABB)**, and **dynamic voltage and frequency scaling (DVFS)**. If the application permits, duty cycling (pausing the operations to reduce the switching activity  $\alpha$ ) and power gating (to reduce static current  $I_{leak}$ ) can be used to further reduce the power consumption.

5.2.1 Sub- and Near-Threshold Operation. Sub- and near-threshold operation exploits the supply voltage knob, operating transistors below or close to their threshold voltage, respectively, to reduce power consumption [89]. This enables to reduce dynamic power quadratically and static power linearly, as shown in Equations (1) and (2).

However, these savings come at the cost of slower transistor operation, limiting the application frequency. In embedded IoT applications, energy is usually more important than power consumption, as it directly determines the lifetime of the battery. Thus, the **minimum energy point (MEP)** is identified for each application by adjusting the supply voltage such that the total energy for a

56:10 P. Jokic et al.

specific workload is minimal. Sub- and near-threshold operation extends the supported supply voltage range, reaching the MEP for a large set of workload scenarios.

Lowering the voltage implies higher sensitivity to process variations, which must be carefully evaluated during the design phase to ensure robustness under all operating conditions. Special layout considerations and compensation techniques (see ABB and DVFS) can reduce the effects.

The 180nm sub-threshold standard cell library developed in [89] demonstrates an extended 0.4–1.0V supply voltage, reducing power by 5× compared to a standard low power library at 1.0V. Their follow-up work presents 1kb sub-threshold SRAM [90] and a 32b microcontroller [91] design, achieving 0.84–3.2nW (3.8×) power scalability for 0.27–0.6V voltage scaling and 7× power scalability for 0.37–1.8V voltage scaling, respectively.

5.2.2 ABB. Adaptive body biasing (ABB) [92] adjusts the bias voltage of the transistor body to control its threshold voltage, influencing its speed and power consumption as discussed in Section 5.2.1. FD-SOI and DDC can fully exploit BB, while the effect in bulk technology largely depends on the design parameters. Adapting the BB to the operating point enables to reduce the adverse effect of sub-threshold operation on timing across process and temperature variations (e.g. worst case corner distance from  $21\times$  to  $0.2\times$  [93]). This allows to implement a wide range of timing-clean operating points from fast to slow and low power. Note that increasing the speed through a strong forward body bias also increases the leakage.

Publications on ABB report  $30 \times$  frequency and  $20 \times$  leakage scaling on a RISC microcontroller core and SRAM [92].

5.2.3 DVFS. Dynamic voltage, frequency, (and accuracy) scaling (DVF(A)S) allows to trade-off speed against power consumption through supply voltage scaling. The basic principle was already evaluated in the 1990s, allowing CPUs to lower the frequency and voltage for low intensity tasks, reporting power reductions of  $1.05-4 \times [94]$ , and  $9.2 \times [95]$ .

DVAS [96] extends the principle to dynamic accuracy scaling through adjustable arithmetic bitwidths, allowing for lower supply voltages due to shortened critical paths. Demonstrated on a simulated 40nm 16bit array multiplier, DVAS achieves 11.7× energy reduction for scaling down to 8b precision, noting that the critical path length is reduced by 40%. Pipelined architectures require bypassable pipeline registers to evenly distribute the path length reductions, adding area and energy overhead. On a 16b multiplier, 11.1× energy reduction is reported for 8b operation at 8% energy overhead. Envision [39] also combines accuracy scaling with DVFS on a 28nm process, running at constant throughput while scaling precision from 1·16b operations to 4·4b operations at a quarter of the 16b frequency. Combined with body biasing to reduce leakage at low frequencies, power is reduced by 25×.

## 5.3 Memory

Data handling is dominating today's accelerator power consumption and area, requiring careful selection of the memory type and the access strategies. Memory access energy is subject to large variations across memory types and sizes, as summarized for a standard 45nm SRAM [79, 97] in Table 2. DRAM is reported to have 200× higher access energy than a small 8kB SRAM (for 64b word width) [79].

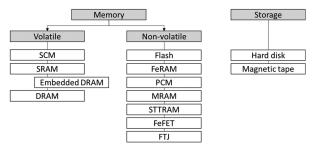

Figure 6 shows an overview of the existing memory types, distinguishing storage (e.g. non-volatile hard disk) and memory (e.g. RAM) due to their significant difference in access times, density and power consumption [98]. Systems with long idle/sleep phases might not be dominated by access power but (idle) leakage power. In that case, rare accesses to (power-intensive) non-volatile memories could be cheaper than retaining data over a long period of time, constantly consuming leakage power.

| Size(kB) | Access energy per 16b word [pJ] |       |       |       |  |  |  |  |

|----------|---------------------------------|-------|-------|-------|--|--|--|--|

| SIZC(KD) | 64b                             | 128b  | 256b  | 512b  |  |  |  |  |

| 1        | 1.2                             | 0.93  | 0.69  | 0.57  |  |  |  |  |

| 2        | 1.54                            | 1.37  | 0.91  | 0.68  |  |  |  |  |

| 4        | 2.11                            | 1.68  | 1.34  | 0.9   |  |  |  |  |

| 8        | 3.19                            | 2.71  | 2.21  | 1.33  |  |  |  |  |

| 16       | 4.36                            | 3.57  | 2.66  | 2.19  |  |  |  |  |

| 32       | 5.82                            | 4.8   | 3.52  | 2.64  |  |  |  |  |

| 64       | 8.1                             | 7.51  | 5.79  | 4.67  |  |  |  |  |

| 128      | 11.66                           | 11.5  | 8.46  | 6.15  |  |  |  |  |

| 256      | 15.6                            | 15.51 | 13.09 | 8.99  |  |  |  |  |

| 512      | 23.37                           | 23.24 | 17.93 | 15.76 |  |  |  |  |

| 1024     | 36.32                           | 32.81 | 28.88 | 25.22 |  |  |  |  |

Table 2. Energy Per Memory Access in 45nm SRAM

Fig. 6. Overview of memory technologies.

The range of available memory technologies is rapidly increasing, being an active area of research. A recent overview of novel memories used in neuromorphic computing [99] notes that the memory technologies mostly differ in their writing speed, while the reading process is dominated by the sensing circuit interfacing the memory cells. Survey [98] provides an overview of recent non-volatile memories, focusing on PCM, STTRAM, RRAM, and FeFET.

In the following sections we summarize novel memory types, as they are important components of CIM implementations, as well as the dominantly used SRAM and standard cell memories. Quantitative optimization results from the literature are mainly available for the more mature FeFET, SRAM, SCM and DRAM types.

- 5.3.1 PCM. Phase change memory (PCM) [98] is based on the heat-induced reversible phase transition of chalcogenides. It can switch between the low-resistance crystalline phase and the high-resistance amorphous phase, implementing a bipolar switch. The relatively large switching current requires powerful access circuits, dominating the size. Speed is limited by the transition from amorphous to crystalline phase while the reverse process dominates the power consumption. Endurance and speed are estimated around 1G cycles and <100ns, respectively [98]. TSMC presents a 1Mb PCM memory array in 40nm [100], reporting 300uA write current at 100ns write speed, achieving >200k cycles endurance.

- 5.3.2 STTRAM. Spin-transfer-torque RAM (STTRAM) [98] is based on a magnetic tunnel junction (MTJ) with two ferromagnetic layers separated by an ultra-thin tunnel oxide layer. It

56:12 P. Jokic et al.

uses the spin transfer torque of spin-polarized electrons to change the resistance of the memory element, enabling non-volatile states. The access circuit dominates its size due to the relatively high writing currents but is still smaller than SRAM.

STTRAM is demonstrated on 7–8Mb arrays (industrialized 1Gb cluster [101]) in 22–28nm [102, 103], reporting densities up to 10.6Mb/mm<sup>2</sup> and write endurance of >1M–10G cycles.

5.3.3 RRAM. Resistive RAM (RRAM) [98] stores information by modulating the resistance of a metal oxide and is therefore often called memristor. A similar approach is **conductive-bridge** RAM (CBRAM), that forms a conductive metallic bridge in the on-state and interrupts it for the off-state. Endurance of 1M–1G cycles have been reported. However, there are tradeoffs between speed, power, and endurance.

Various RRAM implementations in 14–40nm have been shown [70, 104–107], reporting 0.9–244.8Mb/mm<sup>2</sup> density at supply voltages down to 0.7V for 1Mb–32Gb sizes.

5.3.4 FeFET. Ferroelectric FET (FeFET) [98] employs a ferroelectric gate dielectricum that allows to change the resistance of the FET in a non-volatile fashion. This principle is similar to the Flash technology, that uses a floating gate instead. While the power consumption is low due to the low leakage through the gate oxide, the switching speed is high (~20ns). However, its endurance is relatively low, at 10k–100k cycles. Its similarity with standard CMOS transistors makes FeFET compatible with many standard processes.

In [108], a 10Mb FeFET memory array is implemented in a 22nm process, reporting 200k cycles endurance at 2.5-4.5V supply voltage. Their previous work [109] presents a  $64\times64b$  array in the same 22nm process and compare it to a 6T SRAM array of the same size, reporting  $74\times$  lower static power and  $>5.3\times$  lower area for FeFET cells (without peripherals). Writing is  $10\times$  more energy-intensive and  $10\times$  slower while reading costs  $1.6\times$  more energy but is  $1.5\times$  faster.

A similar, but less mature, type of ferroelectric memory is **ferroelectric tunnel junction (FTJ)**. The tunneling resistance of its ferroelectric layer between two metal electrodes can be adjusted through ferroelectric polarization reversal [98].

5.3.5 SRAM. Static random-access memory (SRAM) is the most often used on-chip memory as it can be easily implemented along with digital circuits. It features higher memory density than standard-cell memory as foundries use "layout pushed rules" to optimize SRAM bit-cell area beyond standard layout rules.

Standard SRAM bit-cells use **6 transistors (6T)**, but many larger cell structures have been proposed for power reductions. For low leakage operation a 7-transistor SRAM is presented in [17], reducing area by 18% and 50% compared to standard low leakage 8-and 10-transistor designs, respectively, while achieving similar performance and leakage power.

Power optimizations using non-uniform memory hierarchy in SRAM is presented in a 40nm NN accelerator [110], allowing up to 60% power savings when accessing the smallest instead of the largest level (32× smaller memory). The 67.5kB memory is split into four levels (1.5, 6, 12, and 48kB). SRAM access energy is shown to increase nearly linearly with the memory size above  $\sim$ 100kB [97] as shown in Table 2.

Low leakage SRAM sleep-mode retention is presented on a 55nm process [111], reporting 26× lower retention power for a 16kB memory. Leakage is reduced by optimizing the design rules (increasing area by 2.7×) and the process corner. An additional sleep controller with a charge-pump for the retention voltage allows to power-gate the rest of the chip. Leakage is also reduced in [80], using 180nm low leakage 10T SRAM along with a 65nm 8T SRAM for dense scratchpad memory. The low-leakage memory consumes 4242× less standby power while being 11.3× larger in area.

To optimize the data access for 2D structures like CNNs, a transpose SRAM has been proposed [112], allowing to selectively read a row vector or a column vector of data in parallel, reducing power consumption by 47%.

5.3.6 SCM. Standard-cell memory (SCM) is implemented directly in digital logic using flipflops or latches. This allows exploiting voltage scaling capabilities and avoids dependencies on vendor-specific memory generators.

A dedicated placement strategy for SCM (instead of standard logic **place-and-route (P&R)**) is presented in [113], reporting area and power savings on a 28nm process. Their experiments on 256b–32kb SCM macros show area reductions of >35% compared to standard P&R with access energy reduction of up to 65% for reading and 50% for writing. SCM macro sizes of up to 1kb are shown to be smaller than SRAM, but are already 2–3× larger for 4kb macros (larger area of D-latch cell compared to 6T SRAM bit-cell starts dominating).

A BNN accelerator [114] with a hybrid memory consisting of 456kB SRAM and 8kB SCM demonstrates power savings of SCM compared to SRAM. It reduces the supply voltage to 0.4V when SCM is used, while SRAM requires 0.6V, leading 3× energy savings in 22nm post-layout measurements.

5.3.7 DRAM. Dynamic RAM (DRAM) is a volatile high-density memory that stores information as a capacitor charge, which is periodically refreshed. DRAM is usually not compatible with standard logic processes, requiring separate DRAM dies. However, the **hybrid memory cube** (HMC) architecture [115] proposes high density DRAM access to standard logic processes through 3D stacking of DRAM dies on top of a logic die using through-silicon vias. HMC is implemented in TETRIS [116], providing DRAM access to a 45nm processing die. 3D DRAM is shown to consume 3.5–4.2× more energy compared to on-chip 256kB SRAM, but 1.5× less than a planar baseline DRAM at 4.1× higher throughput.

**Embedded DRAM (eDRAM)** [117] is a CMOS-compatible derivative of DRAM, targeting high density volatile memory. A 4-transistor 8kb eDRAM array is presented in 28nm [117], reporting 17% lower area and 23% lower static power consumption compared to 6T SRAM at equal voltage. The same author also evaluates a 2T design [118], showing slightly lower retention power than low power SRAM cells but 2.5–3.8× lower size for a simulated 28nm 4kb array.

5.3.8 Flash. Flash memory [119] dominates NVM technology on the market, being embedded in most commercial chips where data retention during off-state is required. It can be implemented using standard logic process flows by adding a few additional masking layers, e.g. three extra masks on a 65nm process [120].

## 6 DATAFLOW AND CONTROL OPTIMIZATIONS

NNs have a relatively simple structure, their efficient implementation on hardware accelerators often complicates the dataflow. Efficient parallelization requires smart workload distribution among processing elements while ensuring coherent algorithmic functionality. Thus, this chapter discusses algorithm blocking optimizations, efficient scheduling, selective execution, and early data reduction.

# 6.1 Dataflow and Blocking

NN accelerators have optimized memory allocation and access patterns for efficient computation, splitting a task into smaller blocks that fit on the available resources. The utilized blocking (scheduling) strategy impacts the data access order and thus possible data reuse within the computation blocks. Higher reuse can reduce the number of memory accesses, decreasing the total power consumption [97].

56:14 P. Jokic et al.

6.1.1 Layer-wise Processing. Traditionally, NNs are processed layer-by-layer, also called layer-wise or layer-first approach. This enables the reuse of layer parameters (e.g. convolution weights), as they are repeatedly used across the layer. However, this also implies that at least one complete layer is always buffered in memory, as explained in more detail in Section 7.1.

6.1.2 Depth-first Processing. The increasing size of feature maps (e.g. higher resolution images) requires large activation buffers to be allocated for layer-wise processing. However, networks can be processed in a "depth-first" streaming fashion instead [121], allowing each layer to buffer only a minimum set of input activations that are needed for computing the next set of output activations. Up to  $200\times$  memory bandwidth reduction or alternatively up to  $10,000\times$  memory space reduction is reported for this approach. In a follow-up work [122] depth-first processing is implemented on a FPGA and benchmarked on five models reporting throughput increase of  $0.91-1.27\times$  and memory bandwidth reduction of  $3.9-81\times$ .

A similar work on "fused layers" [123] observes that each output of a convolution layer only depends on a small region of input values. Tracking these dependencies back through multiple layers, results in a pyramid-shaped region. The paper proposes to compute the entire pyramid until the final output while only storing the computed intermediate features instead of buffering each complete. The additional cost for buffering intermediate results locally is traded-off against external memory accesses, achieving up to 95% reduction in off-chip memory traffic for running VGGNet-E.

6.1.3 Loop Ordering and Optimization. Neural network can generally be described using nested loops, with the outer most one looping through the layers of the network. The ordering of these loops influences the possible parallelisms and the required memory size. To process larger networks on limited on-chip memory resources, loop tiling is used: the workload of each layer can be split into overlapping tiles, which are processed sequentially. Parallelization and data reuse can be increased by unrolling parts of the sequential loops and thus parallelizing their computations. Unrolling the entire kernel computation is shown in [124], achieving unprecedented power efficiency at the cost of larger area and limited layer size support.

Various tools have been proposed to optimize loop ordering [97, 125–127], improving energy efficiency and memory size. Commonly implemented microcontrollers provide specialized libraries to make NN processing more efficient. For example, ARM provides the CMSIS-NN library for its Cortex-M microcontrollers [128], supporting CNN, FC, and pooling layers, as well as 8b or 16b fixed point precision. Evaluated on a network running the CIFAR-10 task, a 4.6× improvement in throughput and 4.9× in energy efficiency is reported, compared to a DSP-functions-limited baseline code. A biomedical signal analysis application [129] reports energy savings of 41.6% for enabling 8 core processing instead of single core, noting that the overhead of multi-core execution is fully compensated by efficiency improvements above a certain throughput. Block and memory power gating shows 16.8% energy savings but must be traded off against restart time and related energy and storage implication.

## 6.2 Early Data Reduction

The high cost of data access during NN inference motivated to reduce the data flow from the sensor, condensing information early and thus minimizing costly data transfers.

One approach is to process the first layer(s) of an NN in the sensor itself. In [130] diffraction gratings above the pixels are used to optically detect Gabor filter-like patterns, as they are often found in the first layer of NNs. Evaluated on the MNIST and CIFAR-10 tasks, sensor communication bandwidth reductions of  $10\times$  are reported, with moderate accuracy impacts of -0.1% and

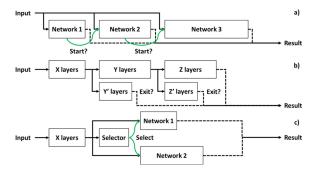

Fig. 7. Selective execution and early exiting approaches: (a) scalable-effort execution, (b) early exiting, and (c) selective execution.

-4.6%, respectively. However, the first layer of the employed LeNet-5 only accounts for 3.8% of all operations, rendering the computation reduction negligible.

Another study implements the first CNN layer in the optical domain using a controllable (grayscale) mask [131]. All filters (output channels) are displayed in the same plane, allowing the image sensor behind to capture all convolution results in parallel, forwarding them to the last layers implemented in the digital domain. Evaluated on MNIST and EMNIST tasks, operation reductions of  $250\times$  and  $460\times$  are reported while accuracy drops by 0.4% and 1.7%, respectively.

The analog nature of most sensor signals requires **analog-to-digital conversion (ADC)** which can be exploited by implementing matrix multiplication directly in the ADC [132]. An algorithmic reformulation is shown to implement a simple classification task using boosted linear classifiers, embedded in a single matrix transformation. The matrix multiplication is implemented in the feedback path of the SAR ADC, reporting 13× and 29× energy savings compared to SVM-based implementation with similar accuracy for ECG arrhythmia detection and 160×120 pixel gender classification tasks.

RedEye [133] implements an image sensor with analog on-die CNN processing capabilities on a simulated 180nm process. It uses SAR ADCs and tunable capacitors to implement weighted summation to mimic MAC operations, reporting 73% system energy reductions for running the first 1–5 layers of an 8bit GoogleNet on the ImageNet task.

Early data reduction is also implemented in distributed computing [134, 135], splitting the DNN computation across the edge and the cloud to reduce costly data communications, latency and preserve privacy by keeping raw data at the edge.

Furthermore, application-specific early data reduction mechanisms exist: visual attention [10] is shown to reduce the object recognition workload in smart glasses by limiting the analyzed region to the detected eye-gaze direction.

#### 6.3 Selective Execution and Early Abortion

This section presents techniques to dynamically adapt the network complexity to the input, enabling "simple" inputs to be analyzed with a fraction of the network capacity without decreasing the accuracy for complex ones. Average latency and power consumption can thus be reduced if simple inputs dominate the execution. Figure 7 illustrates the techniques, covering (a) hierarchically scalable effort [39, 136], (b) early exiting [137, 138], and (c) selective execution [139].

6.3.1 Hierarchically Scalable Effort. Identifying early exits during training enables 2–6× latency reduction on MNIST and CIFAR-10 tasks [136]. A scalable-effort approach [140] proposes to use a chain of networks with increasing complexity, allowing simple inputs to complete processing

56:16 P. Jokic et al.

with smaller networks than more complex ones. Evaluated on various classification tasks, they achieve 1.2–9.8× average reduction of operations per benchmark. The Envision NN accelerator [39] demonstrates this on a face recognition task, hierarchically increasing the network complexity, starting with a 12MOP network for presence detection (6.4mW, active 98% of time), followed by a network recognizing the owner, a set of 10 identities, 100 identities, and finally 5,760 different identities (77mW, 0.01% of time).

6.3.2 Early Exiting. Adding special output classifiers after every few layers allows for terminating an NN execution early if classifiers report a high confidence [137]. The trained network is analyzed after each layer to estimate a gain metric, quantifying the ratio between reduced number of operations and increased overhead due to the added classifier. Benchmarked on two 6-and 8-layer networks with one and two early exits, respectively, 1.73× and 1.91× reduction in number of operations are reported at iso accuracy. The same technique is used in the 12-class keyword spotting accelerator [138], reporting 69% of the inputs exiting early, reducing the average power consumption by 22% compared to always executing the complete network.

6.3.3 Selective Execution. Selective execution [139] enables different execution paths that can be selected depending on the input provided: an embedded selector network decides which branch to execute, providing less complex network branches for simpler inputs to reduce the average number of computations.

#### 7 DATA HANDLING OPTIMIZATIONS

The data-intensive nature of NNs challenges the memories and related access energy efficiencies. In many systems more than 50% of the total power consumption is related to memories and data handling [79]. This chapter discusses optimizations for efficient memory utilization and compression, reducing the amount of data to be accessed. Related sections cover the efficient reuse of data across computation elements (Section 8.3) and the reduction of data through computational optimizations (Section 8).

## 7.1 Efficient Memory Mapping

Efficient memory utilization reduces the required memory space, saving power, chip area and thus IC cost.

The traditionally used buffering scheme for layer-wise NN processing is often called ping-pong buffering [126], following a double buffing approach to allow simultaneous reading of input activations and writing to output activations. It maps the activations of subsequent layers to two disjunctive memory regions, which must therefore allocate at least the maximum sum of any two subsequent layers. By allowing the activation memory regions to overlap during layer-wise processing, memory savings of up to 50% compared to standard ping-pong double buffering can be achieved [141]. The extent of savings depends on the layer dimensions and increases for large layers with small kernel sizes.

## 7.2 Data Compression

Compression reduces the memory footprint of data content and can be adopted in NN accelerator designs.

Run-length compression (RLC) of zero values is used in Eyeriss [40] to reduce the memory footprint and bandwidth. It encodes the number of zero entries in 5b, followed by the next non-zero value, reporting 1.2–1.9× reduced memory accesses for AlexNet. Eyeriss v2 [43] uses a "compressed sparse column format" for both weights and activations, allowing to skip sparse

operations directly in the compressed form, reducing memory bandwidth and energy. Compared to RLC, it simplifies the addressing of sliding window striding.

Loss-less Huffman coding [142], is shown to reduce weight memory by 20–30%. It employs variable-length codewords, providing smaller bit-widths for more common values, reducing the overall memory. An edge ML Huffman-coding DMA is shown to reduce data bandwidth by up to 5.8× [39].

Weight sharing is used in [142], replacing weights with table indices, referencing a limited number of physically stored values. The upper bound of memory savings is defined by the weight bit-width  $N_{width,w}$  and the number of table entries  $N_{values}$  as shown in Equation (3). The 45nm accelerator EIE [38] reports 8× energy savings through weight sharing (4b indices referring to 16 16b weight values).

$$N_{wshare,max} = N_{width,w}/\log_2(N_{values})$$

(3)

#### 8 COMPUTATION OPTIMIZATIONS

NNs contain millions of MAC operations, requiring fast and efficient accelerator designs. This chapter discusses computation optimizations ranging from operation reductions (optimized convolution operations, sparsity, or data reuse) to arithmetic simplifications (quantization, approximate computing, energy-quality scaling, or non-conventional arithmetic) and circuit optimizations (mixed-signal arithmetic, non-conventional arithmetic).

## 8.1 Optimized Convolution Implementations

The dominance of convolution operations in many network architectures [143, 144] motivated optimized convolution implementations, aiming for similar algorithmic behavior while reducing computational complexity and resources.

8.1.1 Separable Convolutions. Separable convolutions are based on a separable filter approximation, splitting higher dimensional kernels (e.g. a  $k_x \cdot k_y$  2D convolution) into multiple lower-dimensional ones (e.g. 2 1D convolutions of  $k_x \cdot 1$  and  $1 \cdot k_y$ ), significantly reducing the number of operations.

A 2D approach is used in [112], replacing a  $5\times5$  convolution layer with a horizontal and a vertical  $5\times1$  and  $1\times5$  layer, reducing the number of operations by  $4\times$ . Evaluated on an LFW face recognition NN, the total number of operations is reduced by 1.7x, while accuracy was decreased by 1%. To optimize parallel data access for the vertical direction, a transpose SRAM (T-SRAM) is proposed, enabling both row and column vector readout, reducing power by 47%.

**Depth-wise separable convolutions (DSC)** separate the kernel only in the depth dimension, convolving inputs in the spatial directions, followed by a pointwise (across depth) convolution that combines the filtered inputs to an output. In contrast to standard convolutions that combine the filtering and output generation, DSCs enable memory savings and reduces MAC operations. MobileNets [145] use such DSCs, reporting computation and parameter size reductions according to Equation (4). Evaluated for the ImageNet task, parameters can be reduced by 7× while the number of MAC operations is reduced by 8.5× at an accuracy drop of just 1%.

$$reduction = \frac{1}{c_{out}} + \frac{1}{k_x \cdot k_y} \tag{4}$$

8.1.2 Frequency Domain Computation of CNN (FDC). Transforming a convolution operation into the Fourier domain results in a point-wise multiplication as shown in Equation (5) [146]. This property can be exploited to reduce the number of operations for computing CNNs. While the forward and backward transformations, using **fast Fourier transformation (FFT)**, increase the

56:18 P. Jokic et al.

computational effort and memory needs, the operation count can be significantly reduced for large input and kernel sizes, achieving  $1.75-5.3\times$  faster computation at iso-accuracy for  $3\times3$  and  $11\times11$  kernels in experiments on various layer sizes [146]. The reported speedup s, in terms of operation counts, is shown in Equation (6) for batch size B. However, this method requires large memories for the FFT and the subsequent matrix multiplication. A recent study [147] builds up on the FFT-based approach, additionally exploiting tiling, result-reuse, and symmetry of real-valued FFTs, roughly cutting the number of operations and Fourier outputs in half. It demonstrates  $0.96-1.74\times$  increase in throughput compared to the pure FFT-base approach on  $9\times9-3\times3$  kernel sizes.

$$f * g = \mathcal{F}^{-1} \{ \mathcal{F} \{ f \} \cdot \mathcal{F} \{ g \} \}$$

(5)

$$s = \frac{\left(B \cdot c_{in} \cdot c_{out} \cdot x_{out}^2\right)}{\left(2 \cdot x_{out}^2 \cdot \log\left(x_{out}\right) \cdot \left(c_{out} \cdot B + c_{in} \cdot B + c_{in} \cdot c_{out}\right) + 4B \cdot c_{in} \cdot c_{out} \cdot x_{out}^2\right)}$$

(6)

8.1.3 Winograd Algorithm. For highly parallelized convolution computations, the sliding window operation can be flattened to convert it into a large point-wise matrix multiplication. The overlapping windows create significant redundancy with neighboring data, allowing to combine certain kernel-weights offline, which reduces the number of multiplications at the cost of more additions [144]. This so-called Winograd convolution achieves 1.4–2.26 speedup for computing 3×3 convolutions.

8.1.4 Strassen Algorithm. Large matrix multiplications, as used in NNs with large kernels, can be efficiently computed using the recursive Strassen algorithm, reducing the number of operations [148]. Evaluated on AlexNet, operations are reduced by 47%: while the dominating 3×3 and 5×5 convolutions are reduced in terms of operations, the 11×11 convolution in the first layer suffers from an increase of 18% compared to standard multiplication.

# 8.2 Sparsity Exploitation and Pruning

Le Cun et al. [149] observed more than three decades ago that a significant number (75%) of NN parameters can be removed without affecting its algorithmic accuracy. A recent exhaustive survey [150] provides explanations to this phenomenon and estimates 10-100× model size reduction for various networks. It focuses on sparsification methods that set parts of a network to zero (pruning), while keeping its complexity constant. They reduce a network's size to its minimum required complexity by creating a (too) high dimensional representation to improve the training, knowing that the network can be reduced again through pruning. Previous works, report weight sparsity ratios of up to 99.996% for a LeNet-5 network with 99.3% accuracy on the MNIST task [151]. We refer the interested reader to the literature for more details on the main reduction techniques: model down-sizing through neural architecture search [152], operator factorization [153], quantization (Section 8.4.3), compression (Section 7.2), parameter sharing [154], and sparsification [150]. A survey on hardware acceleration of compressed models can be found in [155].

To create more sparse models, a three-step approach is proposed [156], first learning the importance of each connection, then dropping low-weight ones and finally fine-tuning the training. Evaluated on AlexNet and VGG16 running the ImageNet task, they report 9× and 13× parameter reduction at iso-accuracy. Energy-aware pruning [157] optimizes the pruning strategy to achieve a minimum energy cost. Observing that layers which are pruned in an early stage, tend to have larger sparsity, they start pruning energy-intensive layers first, estimating their cost based on the number of computations and memory accesses. Evaluated on AlexNet running the ImageNet task, reports  $3.7\times$  energy reduction and  $11\times$  weight reduction at <1% accuracy drop.

Envision [39] exploits sparsity by skipping sparse memory accesses and MAC operations using a sparsity map (1b entries per value). It reports  $1.6\times$  system energy saving for 30-60% activation sparsity. Similarly, NullHop [158] exploits sparsity by skipping sparse computations using a sparsity map combined with non-zero value list compression, achieving up to  $3.68\times$  throughput increase in  $28\,\mathrm{nm}$  synthesis results.

Zero-value skipping logic using a zero-free neuron array format is evaluated on a 65nm accelerator [159], reporting 1.37× average throughput increase for various networks at the cost of 25% memory increase (for zero sparsity).

A special form of temporal sparsity is proposed in CBinfer [160] and discussed in Section 8.3.

## 8.3 Data Reuse

Memory data that is used multiple times within a short period of time can be buffered in a local cache memory to allow cheaper and faster access. Special focus is set on data that has been fetched from energy expensive external memory. Three main structures of such data reuse have been studied extensively [27] and are summarized below, namely **row-stationary (RS)**, **weight stationary (WS)** and **output stationary (OS)** approaches. While a WS setup minimizes movements of weights, as it is used in CIM architectures, OS keeps the partial sums for computing each output feature local, and RS approaches combine weight and activation data reuse.

Eyeriss [40, 57] implements an RS approach to maximize on-chip data-reuse and reduce costly external memory accesses. The 65nm chip can buffer one activations row (up to 224 16b values) and one weight row (up to 12 16b values), increasing energy efficiency by 1.4–2.5×.

A weight stationary approach is presented in [161], reducing the weight memory accesses by moving activations along cached weights during convolution computations.

OS processing is used in ShiDianNao [37], computing one output per processing element in its 8×8 array (64 outputs of the same output channel). This avoids moving partial sums to the memory and allows sharing inputs with neighboring PEs, reducing the memory bandwidth by up to 10×. Compared to their prior work DianNao [162], featuring no local data reuse, it allows to reduce power consumption by more than 1.66x, while increasing throughput by 1.87×. CORAL [163] employs coarse-grained reconfigurable MAC arrays that allow programming different OS data reuse options. Another output stationary approach is used in Hyperdrive [164], keeping the feature maps stored entirely on-chip and streaming in weights. This is motivated by the use of binary weights, consuming 16× less memory bandwidth than the 16b float activations.

Eyeriss v2 [43] implements a flexible **network-on-chip** (**NoC**) that can be reconfigured into four main reuse modes, enabling high activation and weight reuse in convolution layers while the dense layer mode can maximize activations broadcast because weights cannot be reused. Evaluated on MobileNet, they report a throughput increase of 5.6×.

Temporal data reuse is proposed in CBinfer [160], demonstrating that CNN-based CV applications with a static field of view can reuse large portions of each CNN layer and only compute those features that changed over time. They first detect changes in the input, generating a temporal sparsity map to update the connected output features for which the inputs exceed a calibrated threshold and buffer the new feature map. Evaluated on a 5-layer CNN for 10-class scene segmentation, this achieves an average speed-up of  $8.6\times$ .

## 8.4 Hardware/Software Co-optimization

A recent publication proposes less artificial intelligence [165], suggesting that today's networks are too high dimensional and thus prone to overfitting limited datasets, providing some intuition why high sparsity and quantization are viable optimization strategies. Today's NN algorithms exploit

56:20 P. Jokic et al.

this observation, being developed with the challenges of resource-constrained edge ML hardware in mind. Thus, optimized algorithms like MobileNets [145] or SqueezeNets [166], reducing complexity through separable convolutions and kernel size minimization, have been introduced. These co-optimization strategies are covered in this section.

- 8.4.1 Complexity Scaling. The growing number of network architectures created a large design space, shifting the design strategies from hand-crafted architectures to (semi) automatic **network** architecture search (NAS), identifying optimal trade-offs between design constraints like accuracy and computational complexity. Frameworks like adaDeep [167] provide multi-dimensional model selection strategies to find the optimal model scaling strategies for a specific model and usecase. Dynamic complexity scaling is proposed by once-for-all networks [168], which are trained once but can then be deployed in various down-scaled complexities (in depth, width, kernel size, and resolution) without re-training. This allows deploying them on platforms ranging from high-performance cloud servers to low-power edge devices, with low accuracy degradations for the reduced-size versions.

- 8.4.2 Energy-quality-scaling. Energy-quality (EQ) scalable systems [169] introduce a quality metric that describes a network's complexity. This allows to identify the knobs for power-scaling through (acceptable) quality degradations. The presented framework for EQ-scalable systems and EQ architectures [169] helps identifying applications where sensing and/or processing quality degradation is acceptable, for example in noise-resilient applications like computer vision. The list of quality knobs for dynamically adjusting EQ scaling encompasses arithmetic precision, bit error rates, sampling rates, algorithmic complexity and more. Follow-up works exploit this concept for implementing ULP voice activity detection [170] or always-on computer vision system [171]. Voice activity detection is shown to support EQ scaling [170], achieving 3.5× lower energy for 2% accuracy degradation using decision trees on a 28nm chip. Joint voltage and EQ scaling applied to a traditional computer vision task [171] is shown to achieve 3× lower energy through EQ scaling and 3.4× lower energy through VDD scaling on a 40nm process.

- 8.4.3 Quantization and Reduced Precision. NNs can tolerate significant parameter and activation quantization with negligible effects on accuracy [47]. To reduce the effect of reduced precision, quantization-aware training techniques are used (e.g. straight-through estimators [172]) to keep the model derivable for back-propagation. Quantization works especially well in networks which are limited in training data, while the accuracy degradation increases for smaller (complexity-limited) networks, which cannot compensate for the loss of information [173]. Lowering precision reduces memory size, simplifies computational arithmetic, and lowers the power consumption, which also motivated Google to add 8bit support in their TPUs [56]. The viability of fully binary NNs (BNNs) [174], limiting activation and weight precision to 1bit, finally demonstrates the full range of quantization possibilities. BNNs have considerable accuracy degradations but allow to process multiplications using simple XNOR logic, reducing area and power needs.

Survey [48] provides an in-depth analysis of quantization schemes with a special section on sub-8bit quantization and a short overview of quantization-optimized hardware. Weight sharing is another form of quantization, limiting the number of supported values, as discussed in Section 7.2.

Energy and area savings of reduced precision arithmetic have motivated quantization optimizations. The energy for additions and multiplications are evaluated on a 45nm process [79], reporting 14× and 20× MAC energy reduction for 8b int compared to 32b int and 32b float, respectively, as summarized in Table 3. A 45nm overview [175] reports power and area increase with bit-width for adders (linear increase) and multipliers (quadratic increase), as shown in Table 4. Comparing a MAC-combination, total area and power are reduced by 13× and 10.8x, respectively, for 32b to

Precision Int32 Float16 Float32 Int8 Addition energy [pJ] 0.03 0.1 0.4 0.9 Multiplication energy [pJ] 3.7 0.23.1 1.1 Total energy/MAC [pJ] 0.23 3.2 1.5 4.6

Table 3. 45nm Energy per Operation for Different Precisions

Table 4. 45nm Adders/Multipliers for Different Precisions

| Precision  |            | Int8 | Int16 | Int32 |

|------------|------------|------|-------|-------|

| Adder      | Area [um²] | 212  | 322   | 1117  |

|            | Power [uW] |      | 2235  | 4819  |

| Multiplier | Area [um²] | 1038 | 4209  | 15126 |

|            | Power [uW] | 2830 | 10816 | 34034 |

Table 5. 65nm Multipliers for Different Precisions

| Precision  |            | Int16 | Float32 |

|------------|------------|-------|---------|

| Multiplier | Area [um²] | 1309  | 7998    |

| Multiplier | Power [uW] | 577   | 4230    |

8b, and by  $3.6 \times$  and  $3.6 \times$ , respectively, for 16b to 8b. Similarly, this was shown on multipliers for a 65nm process [162] as illustrated in Table 5.

The 65nm accelerator in [162], achieves  $6.1\times$  reduction in area and  $7.33\times$  in power consumption for implementing 16b fixed point multipliers instead of baseline 32b floating point arithmetic while maintaining comparable accuracy. Envision [39] exploits 1–16b dynamic precision scaling combined with DVFS, reporting reductions in energy per MAC operation (relative to 16b) of  $>5\times$  for 8b and  $>50\times$  for 4b precision using sub-word parallel computations in a 28nm process.

UNPU [176] employs a non-linear quantization support that replaces a 16b multiplier by a  $2\times4$ -bit lookup table, indexing 16 16b activations and 16 16b weights, with the result of each combination stored in the table. They report 79% power reduction and 93% lower latency while the area is reduced by  $1.3\times$  compared to instantiating a 16b multiplier.

A review on scalable precision MAC architectures [177] compares recent 2-8b scalable implementations, discussing spatial and temporal MAC architectures and benchmarking them on a 28nm process using a data-gated 8b-input MAC as baseline. Throughput is roughly increased quadratically for cutting precision by a factor of 2, reaching up to 14.5× for 2b precision. Area is increased 1.1-4.4× for parallel precision-scalable designs while bit-serial implementations can reduce area by up to 40%. The overhead for scalability-support increases the energy per operation in full precision modes by up to 52% for single level, up to 94% for dual level scalability, and up to 14× for multi-cycle bit-serial MACs. The energy per operation only reduces linearly with precision in the baseline but decreases supra-linearly for the scalable MACs, achieving up to 4× lower energy at 2b precision (overhead compensated at 6-4b precision for parallel and at 2b for bit-serial MACs).

An XNOR-based 22nm BNN accelerator [114] exploits the reduced precision by utilizing SCM instead of SRAM, enabling lower power consumption. Similarly, the 65nm binary-weight (12b activation) CNN accelerator YodaNN [41], reports improved performance using voltage-scalable SCM. Combining binary weights (instead of 12b) with SCM (replacing SRAM) allows them to reduce the power by  $11.6\times$ .

56:22 P. Jokic et al.

Cross-layer bit-width optimization [178], shows more than 20% parameter size reduction compared to homogeneous bit-width fixed-point quantization at iso-accuracy on the CIFAR-10 task. Furthermore, knowledge distillation can be used for low-precision quantization [179], improving the accuracy of a highly quantized model using "distilled" knowledge from a larger (higher precision) teacher network during training.

# 8.5 Approximate Computing

Approximate computing trades power consumption, speed, and area off against arithmetic accuracy [180]. Approximation approaches are either based on **voltage over-scaling (VOS)** below the technology's threshold voltage or on functional modifications ranging from algorithm- to circuit-level [181]. It differs from energy-quality-scaling (Section 8.4.2, due to its circuit-based scaling approach.

A 2020 survey [182] on approximate computing for DNNs reports power, delay and area numbers from synthesized approximate adders, multipliers and dividers using a 28nm process at 1V. It reports up to 69% energy savings (power-delay product) for an image sharpening task while for JPEC compression only 20% savings are achieved.

An earlier survey [181] reports an approximate integer data format and related arithmetic operation implementations in 45nm [175], limiting values and computation precisions to a dynamically selected range of most significant non-zero bits. This achieves 55-65% power reduction compared to accurate computations at <0.5% accuracy drop in KNN and SVM tasks. Approximate computing using 2- and 3-bit adder designs [183] reports further power and accuracy improvements.

VOS introduces bit errors due to missed timing constraints and other unwanted effects but reduces power consumption as shown on a 28nm CNN accelerator [184]. Reducing the SRAM voltage from nominal 1.0V to 0.51V enables 3.12× memory and 2.13× system power reduction for running a 9-layer fully binary CNN at <1% accuracy drop. They report stronger effects on accuracy from weight errors than activation errors, enabling further activation memory voltage scaling.

#### 8.6 Non-Conventional Arithmetic

To further optimize NN computations, non-conventional computer arithmetic has been surveyed [185], comparing currently used CMOS technology and alternative emerging technologies for implementing computer arithmetic. Also alternative number systems are evaluated, for example a logarithmic system on a 65nm process [186], showing  $3\times$  higher energy per addition compared to floating point, but  $1.5\times$  lower for multiplications,  $17\times$  lower for divisions and  $38\times$  lower for square root computations.

8.6.1 Spiking Arithmetic. Biological neurons in the human brain function with spike-based signaling and computing, inspiring researchers to rethink the traditional level-based arithmetic in ICs [187]. Neuromorphic spiking arithmetic is employed in IBM's 28nm TrueNorth [188], implementing a total of one million digital spiking neurons, and Intel Loihi [189], implementing 131k neurons in a 14nm process. Due to the significantly different computing paradigm, which cannot be directly compared with other optimization approaches, we refer the reader to the specific literature for more details [187, 190, 191].

8.6.2 Hyperdimensional Computing. Hyperdimensional computing is another brain-inspired computing approach that encodes information in very high-dimensional binary vectors with thousands of entries, called hypervectors. The similarity of information contained in hypervectors is encoded in a distance metric, making them robust against bit errors and thus suitable for VOS. Tasks like image recognition are performed by comparing the distance of an input vector (e.g. features of an image) with a known reference vector. We refer to the specific literature [185, 192] for more details as this goes beyond the++ scope of this work.

#### 8.7 Mixed Precision Arithmetic