# ON THE HEAT DISSIPATION IN MICRO-ELECTRONICS AND ADVANCED THERMAL CONTROL DEVICES

Timm Philipp Erik Swoboda

# ON THE HEAT DISSIPATION IN MICRO-ELECTRONICS AND ADVANCED THERMAL CONTROL DEVICES

### DISSERTATION

### to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. ir. A. Veldkamp,

on account of the decision of the Doctorate Board

to be publicly defended

on Monday 25 September 2023 at 14.45 hours

by

Timm Philipp Erik Swoboda

born on the 18th of July, 1994 in Frankfurt am Main, Germany

This dissertation has been approved by:

Supervisors

prof. dr. ir. G. Brem prof. dr. M. Muñoz Rojo

The presented research was funded by and carried out in the Thermal and Fluid Engineering group, Faculty of Engineering Technology, University of Twente, The Netherlands.

Cover design: Timm Swoboda, partially linked to the following article:

T. Swoboda, K. Klinar, A. S. Yalamarthy, A.Kitanovski and M. Muñoz Rojo, Adv. Electron. Mater., 2020, 7, 2000625.

Link: https://onlinelibrary.wiley.com/doi/abs/10.1002/aelm.202170008

Printed by: Ipskamp printing

ISBN (print): 978-90-365-5773-3

ISBN (digital): 978-90-365-5774-0

URL: https://doi.org/10.3990/1.9789036557740

© 2023 Timm Philipp Erik Swoboda, The Netherlands. All rights reserved. No parts of this thesis may be reproduced, stored in a retrieval system or transmitted in any form or by any means without permission of the author. Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd, in enige vorm of op enige wijze, zonder voorafgaande schriftelijke toestemming van de auteur.

### **Graduation Committee:**

Chair / secretary: prof.dr.ir. H.F.J.M. Koopman

Supervisors: prof.dr.ir. G. Brem

Universiteit Twente, ET, Thermal

Engineering

prof. dr. M. Muñoz Rojo

Spanish National Research Council (CSIC), Instituto de Ciencia de

Materiales de Madrid (ICMM)

Committee Members: prof. dr. A. Kitanovski

University of Ljubljana, Faculty of

Mechanical Engineering

prof. dr. ir. H. Hilgenkamp University of Twente, TNW

prof. dr. J.B. Roldán

University of Granada, Electronics and

Computer Technology Department

prof.dr.ir. W. Rohlfs

Universiteit Twente, ET, Department of

Thermal and Fluid Engineering

dr. K.M. Dowling

TU Delft, Faculteit Elektrotechniek,

Wiskunde & Infomatica

dr. ir. W.W. Wits

Multiscale Modeling & Simulation group at

EEMCS, UTwente

Mechanical & Electrical Engineering

department at Thales Nederland B.V.

### **Summary**

Future and current technologies aim for the improvement of our energy conservation, conversion and harvesting capabilities. Heat, as a form of energy, is essential to generate electricity in thermodynamic processes but it is also behind the limited efficiency or performance of some technology. For example, heat is a limiting factor for the performance of our electronic devices or low grade waste heat is the major source of losses in multiple thermodynamic processes.

This thesis addresses aspects around the concept of heat in two different domains. On the one hand, fundamental understanding of heat dissipation and its impact on the operation of nanostructured electronic devices is studied. For the characterization of the heat dissipation, I calibrate and use a scanning thermal microscope (SThM). On the other hand, a novel thermal diode design is developed by means of finite element modelling to obtain modulated heat rectification factors beyond the start of the art. Based on this design, I propose to integrate this diode in heat storage tanks to improve our energy management and storage capabilities.

As the power density of electronics increases with device size reduction, heat dissipation has become a growing concern in modern electronic design. Electronic devices in operation generate Joule heating, which can negatively impact device performance, cause thermal stresses, and eventual failure due to overheating. Therefore, efficient heat dissipation is key to improve the energy efficiency in modern electronics.

The characterization of heat dissipation of electronic devices is very challenging due to the nano- or micro-scale size of the devices and eventual non-uniformity and local nature of the heating features. Optical-based techniques, such as Raman thermometry or infrared scopes, are diffraction limited, meaning that their spatial resolution is not enough to characterize nanoscale heating features. Scanning thermal microscopy presents nanoscale spatial resolution and it has emerged as a promising tool for studying local heating features of devices. However, the calibration of the SThM for quantitative temperature analysis is one of the most challenging aspects of this approach due to complex thermal exchange processes between the tip and the surface. Calibrated SThM systems have been employed to study the heat dissipation in multiple electronic devices,

including filamentary based memory devices like resistive random access memories (RRAM).

RRAM devices are based on the formation and rupture of nanoscale confined conductive filaments (CF) with high power densities. The capabilities of these devices make them specially interesting for neuromorphic computing. Several theoretical and experimental studies have been carried out to determine the electrical switching capabilities of RRAMs, but little information is known about their heating features. SThM is a powerful tool to be employed for studying the hot spots that are generated at the surface of RRAMs when CFs are formed. The characterization of these heating features provides a better fundamental understanding of the electro-thermal mechanism that affects RRAM's operation.

The experimental focus of this thesis is on the thermal characterization of metal-oxide RRAMs. Particularly, titanium-oxide (TiO<sub>2</sub>) RRAMs are studied with a calibrated scanning thermal microscope (SThM) to quantify the effect of heat generation of CF in operation. These measurements aim to provide deep insights on the electro-thermal switching mechanism of RRAM devices and how it affects their performance variability. Such fundamental information is crucial for the effective thermal design and management of such devices.

First, a calibration method to investigate the impact of the probe-sample thermal exchange processes based on the characterization of metal lines of different widths is performed. The calibration allows converting the electrical response of thermo-resistive probes into temperature and takes into account variable probe-sample thermal exchange processes.

Second, the SThM measurements on the investigated RRAM devices reveal a correlation of the heat dissipation with its electrical characteristics. In this context, the results indicate that a shift of the filament position within the device area correlates with a significant source of performance variability. The shift of the hot spot position appears in devices with larger area sizes. The results offer the possibility to develop electro-thermal models of filaments that do not only rely only on electrical data but also in thermal data. This will advance our fundamental knowledge of RRAMs and it could favor the design of more reliable devices.

Regarding advanced thermal management, solid-state thermal control devices have emerged as potential candidates for heat management in electronics and beyond e.g., energy conversion or storage systems. They distinguish themselves from traditional passive thermal management

devices in that they possess a sharp non-linear relation in their heat transfer characteristics which can be modulated by the heat flow direction or the operating temperature. As a promising example, thermal diodes present an asymmetrical heat flow depending on the temperature gradient direction. This feature makes them interesting for application in a vast field of heat related subjects ranging from thermoelectric and nanoelectronics to heat storage systems. Nonetheless the application of thermal diodes is still limited by the moderate rectification ratios of current device designs.

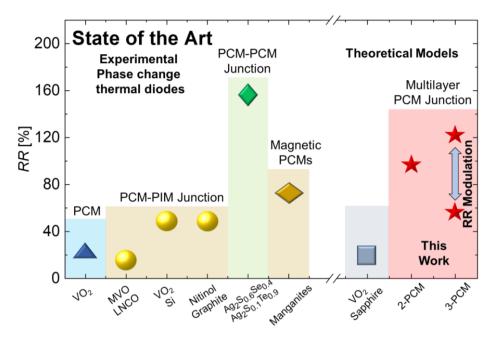

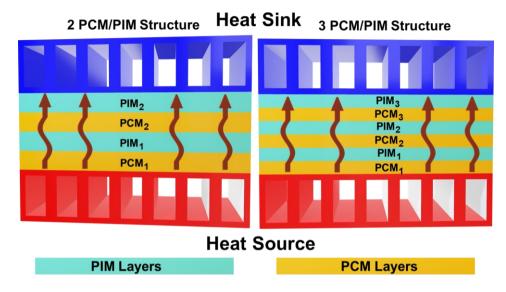

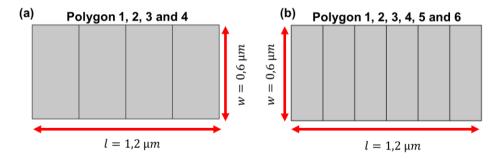

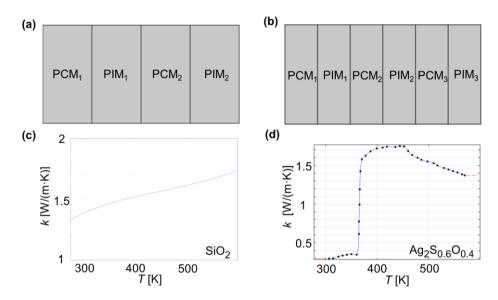

This thesis also focuses on the design and application of solid-state thermal diodes as advanced heat control devices. For that purpose, a finite element method (FEM) model of a novel solid-state thermal diode design that presents state-of-the-art rectification ratios is developed. In the context of this study the rectification ratio of two novel thermal diode designs based on the combination of multiple phase change material (PCM) layers are analyzed. The two structures display rectification ratios ranging from 96 to 133 % for temperature differences of up to 250 K in between the heat terminals at around room temperature conditions. These values are 50-80 % higher than other studied PCM thermal diodes. Moreover, the existence of multiple layers of PCMs and phase invariant materials (PIMs) allows better control of the temperature gradients across materials. This facilitates modulation of the rectification factor depending on the gradient of temperature. Finally, an analytical study shows that these thermal diodes can be implemented in thermal storage elements to increase their heat retention up to 17 %. Overall, these thermal diodes represent new opportunities for efficient energy management.

### Samenvatting

Toekomstige en huidige technologieën zijn gericht op de verbetering van onze mogelijkheden om energie te behouden, om te zetten en te verkrijgen. Warmte, als een vorm van energie, is essentieel om elektriciteit op te wekken in thermodynamische processen, maar het is ook de oorzaak van de beperkte efficiëntie of prestaties van sommige technologieën. Warmte is bijvoorbeeld een beperkende factor voor de prestaties van onze elektronische apparaten of laagwaardige afvalwarmte is de belangrijkste bron van verliezen in meerdere thermodynamische processen.

Deze dissertatie behandelt aspecten rondom het concept warmte in twee verschillende domeinen. Aan de ene kant wordt fundamenteel begrip van warmteafvoer en de invloed ervan op de werking van nano elektronische apparaten bestudeerd. Voor de karakterisering van de warmtedissipatie kalibreer en gebruik ik een zogeheten scanning thermal microscope (SThM). Aan de andere kant wordt een nieuw ontwerp van een thermisch diode ontwikkeld door middel van een eindige-elementenmethode (FEM) om gemoduleerde warmte-rectificatie factoren te verkrijgen die verder gaan dan de nieuwste technieken. Op basis van dit ontwerp stel ik voor om deze diode te integreren in warmteopslagtanks om ons energiebeheer en onze opslagmogelijkheden te verbeteren.

Omdat de vermogensdichtheid van elektronica toeneemt naarmate de apparaten kleiner worden, is warmteafvoer een steeds groter probleem geworden in het moderne elektronische ontwerp. Elektronische apparaten genereren Joule-warmte, wat de prestaties van het apparaat negatief kan beïnvloeden, thermische spanningen kan veroorzaken en uiteindelijk defecten kan veroorzaken door oververhitting. Daarom is efficiënte warmteafvoer essentieel om de energie-efficiëntie van moderne elektronica te verbeteren.

Het karakteriseren van de warmteafvoer van elektronische apparaten is een grote uitdaging vanwege de nano- of micro grootte van de apparaten en de eventuele niet-uniformiteit lokale aard en van de verwarmingseigenschappen. Optische technieken, zoals een Raman thermometrie of een infraroodcamera, zijn buigingsbegrensd, wat betekent dat hun ruimtelijke resolutie niet voldoende is om verwarmingseigenschappen op nanoschaal te karakteriseren. SThM biedt een ruimtelijke resolutie op nanoschaal en is een veelbelovend hulpmiddel geworden voor het bestuderen van lokale verwarmingseigenschappen van apparaten. De kalibratie van de SThM voor kwantitatieve temperatuuranalyse is echter een van de meest uitdagende aspecten van deze techniek vanwege de complexe thermische uitwisselingsprocessen tussen de tip en het oppervlak. Gekalibreerde SThM-systemen zijn gebruikt om de warmtedissipatie in verschillende elektronische apparaten te bestuderen, waaronder op filamenten-gebaseerde geheugenapparaten zoals het zogeheten resistive random access memory (RRAM).

RRAM-apparaten zijn gebaseerd op de vorming en breuk van op nanoschaal bearensde conductieve filamenten (CF) ruimteliik vermogensdichtheden. De mogelijkheden die deze apparaten bieden maken ze speciaal interessant voor neuromorfische computersystemen. Er zijn verschillende theoretische en experimentele studies uitgevoerd om de elektrische schakelmogelijkheden van RRAMs te bepalen, maar er is weinig informatie bekend over hun verwarmingseigenschappen. SThM is een krachtig hulpmiddel om de hotspots te bestuderen die ontstaan aan het oppervlak van RRAMs wanneer CFs worden gevormd. De karakterisering van deze verwarmingseigenschappen zorgt voor een beter fundamenteel begrip van het elektrothermische mechanisme dat de werking van RRAMs beïnvloedt.

De experimentele focus van deze dissertatie ligt op de thermische karakterisering van metaaloxide RRAMs. Specifiek, titanium-oxide (TiO<sub>2</sub>) RRAMs worden bestudeerd met een gekalibreerde SThM om het effect van warmtedissipatie van CF tijdens operatie te kwantificeren. Het doel van deze metingen is om beter inzicht te verkrijgen in het elektrothermische schakelmechanisme van RRAM-apparaten en hoe dit de variabiliteit van hun prestaties beïnvloedt. Dergelijke fundamentele informatie is cruciaal voor een effectief thermisch ontwerp en beheer van dergelijke apparaten.

In eerste instantie wordt een kalibratiemethode uitgevoerd om de invloed van de thermische uitwisselingsprocessen tussen sonde en monster te onderzoeken, gebaseerd op de karakterisering van metaallijnen van verschillende breedtes. De kalibratie maakt het mogelijk om de elektrische respons van sondes met thermoweerstand om te zetten in temperatuur waarbij rekening gehouden wordt met variabele thermische uitwisselingsprocessen tussen de sonde en het monster.

Ten tweede onthullen de SThM-metingen aan de onderzochte RRAMapparaten een correlatie tussen de warmtedissipatie en de elektrische karakteristieken. In deze context geven de resultaten aan dat een verschuiving van de positie van de CF binnen het RRAM-gebied correleert met een significante bron van prestatievariabiliteit. De verschuiving van de hotspotpositie treedt op in apparaten met een groter oppervlak. De resultaten bieden de mogelijkheid om elektrothermische modellen van CFs te ontwikkelen die niet alleen gebaseerd zijn op elektrische gegevens, maar ook op thermische gegevens. Dit zal onze fundamentele kennis van RRAMs vergroten en kan het ontwerp van betrouwbaardere apparaten bevorderen.

Met betrekking tot geavanceerd thermisch management, zijn solid-state thermisch controleapparaten gekomen als potentiële kandidaten voor warmtemanagement in elektronica daarbuiten. en biivoorbeeld energieomzettings- of opslagsystemen. Ze onderscheiden zich van traditionele passieve apparaten voor thermisch management doordat ze een niet-lineaire relatie hebben scherpe in hun warmteoverdrachtskarakteristieken die gemoduleerd kunnen worden door de richting van de warmtestroom of de bedrijfstemperatuur. veelbelovend voorbeeld zijn thermische dioden met een asymmetrische warmtestroom afhankelijk van de richting van de temperatuurgradiënt. Deze eigenschap maakt ze interessant voor toepassing in een breed gebied van warmtegerelateerde toepassingen, variërend van thermo-elektrische en nano-elektronica tot warmteopslagsystemen. Toch is de toepassing van thermische dioden nog steeds beperkt door de geringe rectificatie ratios (RR) van de huidige apparaten.

Deze dissertatie richt zich ook op het ontwerp en de toepassing van solidstate thermische dioden als geavanceerde apparaten voor warmteregeling. Voor dat doel is een eindige-elementenmethode ontwikkeld van een nieuw ontwerp van een solid-state thermische diode met de hoog RR. In het kader van deze studie wordt de RR van twee nieuwe thermische dioden ontwerpen geanalyseerd die gebaseerd zijn op de combinatie van meerdere lagen van fase-veranderbare materialen (PCMs). De twee structuren vertonen een RR van 96 tot 133 % voor temperatuurverschillen tot 250 K tussen de warmtebron en warmteput bij kamertemperatuur. Deze waarden zijn 50-80% hoger dan andere bestudeerde PCM thermische dioden. Bovendien maakt het bestaan van meerdere lagen PCMs en fase-onveranderbare materialen (PIMs) een betere controle van de temperatuurgradiënten over de materialen maakt modulatie mogelijk. Dit van de RR afhankeliik temperatuurgradiënt mogelijk. Tot slot toonde een analytische studie aan dat deze thermische dioden geïmplementeerd kunnen worden in elementen voor thermische opslag om hun warmtebehoud tot 17 % te verhogen. In het algemeen bieden deze thermische dioden nieuwe mogelijkheden voor efficient energiebeheer.

# **Table of contents**

| Summary    |                                                              | i   |

|------------|--------------------------------------------------------------|-----|

| Samenvat   | ting                                                         | iv  |

| Table of c | ontents                                                      | vii |

| Chapter 1  | Introduction                                                 | 1   |

| 1.1 Energ  | gy dissipation in electronics                                | 4   |

| 1.1.1      | RRAM device fabrication                                      | 6   |

| 1.1.2      | RRAM operation principle                                     | 7   |

| 1.1.3      | Electrical performance in RRAM                               | 8   |

| 1.1.4      | Limitations and potential sources of device failure          | 10  |

| 1.2 Therr  | nal characterization of RRAM devices                         | 11  |

| 1.2.1 C    | peration principle of SThM                                   | 12  |

|            | ThM calibration approaches for sensing nanoscale heatings    |     |

| 1.2.3 R    | RAM filamentary hot spot characterization with SThM          | 14  |

| 1.3 Therr  | nal control devices for advanced thermal management          | 16  |

| 1.3.1 C    | peration of thermal diodes                                   | 17  |

| 1.3.2 lr   | ntroduction to two-segment thermal diodes                    | 18  |

| 1.3.3 J    | unction of materials with different thermal properties (JMT) | )18 |

| 1.3.4 P    | hase change material (PCM) thermal diodes                    | 21  |

| 1.4 Scope  | e of this thesis                                             | 25  |

| 1.5 Rese   | arch questions and lines                                     | 26  |

| 1.6 Thesi  | s organization                                               | 27  |

| 1.7 Rese   | arch contributions                                           | 28  |

| 1.8 Introd | luction references                                           | 30  |

| •          | Nanoscale temperature sensing of electronic dev              |     |

| with calib | rated scanning thermal microscopy                            | 37  |

| 2.1 Introd | luction                                                      | 38  |

| 2.2 Experimental setup                                                                                                         | .40 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2.1 Fabrication of the calibration sample                                                                                    | .40 |

| 2.2.2 Atomic force microscopy (AFM) analysis of the topography of the lines                                                    |     |

| 2.2.3 Electrical characterization of the lines                                                                                 | .42 |

| 2.2.4 Operation of the SThM calibration                                                                                        | .44 |

| 2.2.5 COMSOL simulation for characterization of the temperature increase                                                       | .46 |

| 2.2.6 Estimation of the probe power during the measurement                                                                     | .48 |

| 2.2.7 Estimation of the temperature of the probe utilizing null-point method (NPM) measurements                                | .49 |

| 2.3 Results                                                                                                                    | .52 |

| 2.3.1 Estimation of the <i>CaF</i>                                                                                             | .52 |

| 2.3.2 Comparison of the results with a second probe                                                                            | .53 |

| 2.3.3 Calibration factor at high power                                                                                         | .55 |

| 2.4 Discussion and SThM application to measure electronic devices                                                              | .55 |

| 2.4.1 Validation of calibration                                                                                                | .56 |

| 2.5 Conclusions                                                                                                                | .57 |

| 2.6 References                                                                                                                 | .58 |

| 2.7 Appendix                                                                                                                   | .60 |

| 2.7.1 SThM measurements                                                                                                        | .60 |

| 2.7.2 Conversion of SThM signal into temperature signal                                                                        | .61 |

| Chapter 3 Spatially resolved thermometry of filamentary nanoscale hot spots in TiO <sub>2</sub> resistive random access memory |     |

| devices                                                                                                                        | 63  |

| 3.1 Introduction                                                                                                               | .64 |

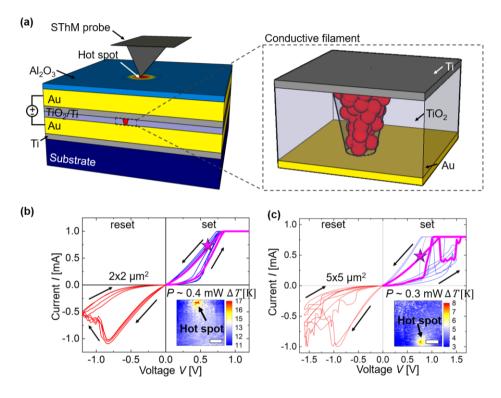

| 3.2 Experimental setup                                                                                                         | .65 |

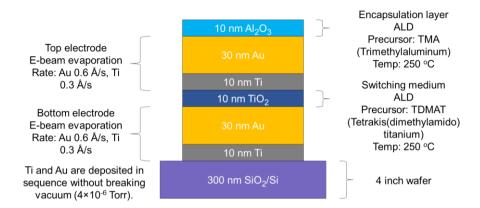

| 3.2.1 Synthesis of the RRAM device structure                                                                                   | .65 |

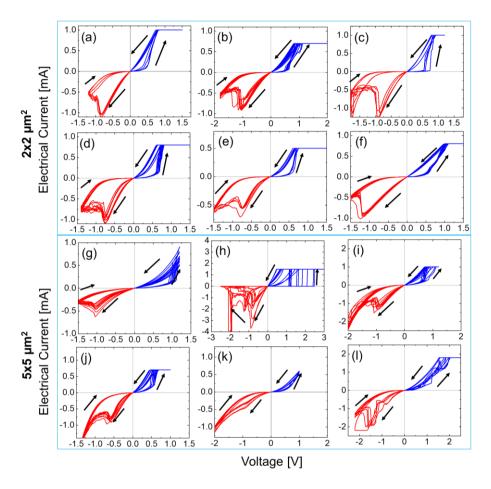

| 3.2.2 Characterization of the current-voltage characteristics                                                                  | .67 |

| 3.2.3 Device-to-device and cycle-to-cycle variability                                                                          | .68 |

| 3.2.4 Thermal characterization with SThM                                                                                       | .69 |

| 3.2.5 Conversion of SThM electrical signa          | al into temperature70 |

|----------------------------------------------------|-----------------------|

| 3.3 Results                                        | 72                    |

| 3.3.1 Steady state measurements                    | 72                    |

| 3.3.2 COMSOL model for the characterizatemperature |                       |

| 3.3.3 Estimation of the hot spot character         | istics78              |

| 3.3.4 In-operando SThM measurements a              | at the hot spot80     |

| 3.3.5 Steady state characterization after of       | cycling81             |

| 3.4 Discussion                                     | 82                    |

| 3.4.1 Influence of the area size                   | 83                    |

| 3.4.2 Characterization of the line resistant       | ce83                  |

| 3.4.3 STEM characterization of the layer s         |                       |

| 3.5 Conclusions                                    |                       |

| 3.6 References                                     |                       |

| 3.7 Appendix                                       |                       |

| 3.7.1 Electrical characterization in RRAM          |                       |

| 3.7.2 Hot spot location with cycling               |                       |

| 3.7.3 Simulation characteristics                   |                       |

| Chapter 4 Thermal rectification in multi           |                       |

| naterial structures for energy storage a           | • •                   |

| 4.1 Introduction                                   | • •                   |

| 4.2 Modelling approach                             | 99                    |

| 4.2.1 Geometry                                     |                       |

| 4.2.2 Material selection                           |                       |

| 4.2.3 Heat transfer model                          |                       |

| 4.2.4 Mesh                                         |                       |

| 4.2.5 Study                                        | 105                   |

| 4.3 Results                                        |                       |

| 4.3.1 Rectification ratio of 2- & 3- PCM/PI        |                       |

| thermal bias                                       | 106                   |

| 4.3.2 RR of 2- & 3-PCM/PIM multilayers vs heat source tem                                             | -   |

|-------------------------------------------------------------------------------------------------------|-----|

| 4.3.3 Calculation of thermal conductivity vs heat source tem                                          | -   |

| 4.3.4 Validation                                                                                      | 111 |

| 4.3.5 Influence of geometry, interfaces and number of layers rectification of PCM/PIM diodes          |     |

| 4.4 Discussion on thermal diode applications                                                          | 115 |

| 4.4.1 Application design                                                                              | 115 |

| 4.4.2 Analytical model                                                                                | 116 |

| 4.4.3 Calculation heat losses                                                                         | 120 |

| 4.4.4 Cycling of thermal storage system                                                               | 121 |

| 4.4.5 Integration of thermal contacts                                                                 | 122 |

| 4.5 Conclusion and prospects                                                                          | 123 |

| 4.6 References                                                                                        | 124 |

| 4.7 Appendix                                                                                          | 126 |

| 4.7.1 Verification heat losses                                                                        | 126 |

| Chapter 5 Conclusion and future perspectives                                                          | 127 |

| 5.1 Characterization of electro-thermal switching in metal-oxid with SThM                             |     |

| 5.2 Development of a novel solid-state thermal diode and eval its potential for advanced heat control |     |

| 5.3 Recommendations & outlook                                                                         | 130 |

| List of publications                                                                                  | 132 |

| Acknowledgments                                                                                       | 135 |

# **Chapter 1 Introduction**

T. Swoboda, K. Klinar, A. S. Yalamarthy, A. Kitanovski and M. Muñoz Rojo, Adv.

Chapter 1.3 is derived from the publication:

Electron. Mater., 2020, 7, 2000625.

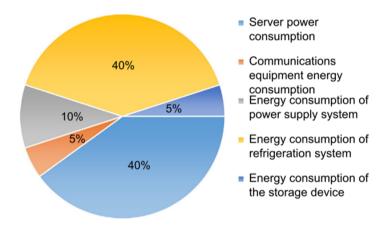

Energy consumption, dissipation and waste are behind some key challenges of our modern society. Heat, as a form of energy, plays an essential role in many applications, such as thermodynamic processes or heat storage. On the other hand, heat could also limit the efficiency and performance of some technologies, such as electronics. As an example, data centers consume enormous amount of energy that is used for example in servers or networks. However, a major part of the energy input in data centers is dedicated to cool down their electronic racks. As shown in Fig. 1.1 roughly 40 % of the whole energy consumption in data centers is related to cooling purposes (e.g., air conditioning).<sup>1,2</sup> From an energy consumption point of view this is especially relevant as the combined electricity consumption of data centers in the world (220-320 TWh) was approximately twice as high as the total electricity consumption of the Netherlands (116 TWh) in 2020.<sup>3</sup>

**Figure 1.1** Energy consumption distribution of data centers Adapted with permission from Rong *et al.*<sup>2</sup>

In the coming years the demand for data network services is expected to increase even further due to data intensive activities like video streaming, augmented reality or more currently crypto mining.<sup>4</sup> In that context the data volume of the global internet traffic increased by 440 % from 2015 to 2021<sup>4</sup> and the cooling demands are becoming more drastic.<sup>5,6</sup> This has made companies like Google or apple to move their data centers to cold places like northern Europe, where they can take advantage of the environment to cool down electronics more efficiently.<sup>6</sup>

The heat generated in data centers comes primarily from electronic devices that heat up due to Joule heating effects.<sup>6</sup> On the one hand, efficient management of this heat is necessary to avoid malfunctioning or damage of the electronics racks.<sup>7</sup> On the other hand, gaining more insights about how heat dissipates in individual electronic devices, like nanoscale transistors or memories, can favor the development of more efficient electronic architectures. These new electronics will avoid unpleasant effects, like reduction of device performance, thermal stresses, thermal crosstalk or eventual failure due to overheating.<sup>8–10</sup> Therefore, heat dissipation at different scales is behind the core of the energy efficiency of data centers.

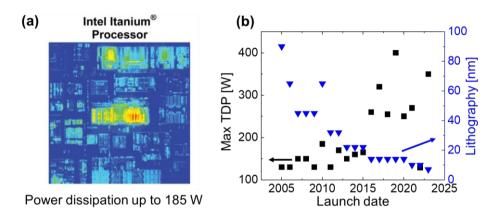

**Figure 1.2 (a)** Temperature map of an Intel Itanium Processor. **(b)** Highest thermal design power (TDP) of new released Intel processors (left axis) as a function of their launch data. The right axis displays the used lithography size of the same processors. **(a)** Adapted with permission from Mahajan *et al.*<sup>9</sup> **(b)** Data obtained from the Intel product database. <sup>12</sup>

Thermal management of electronic components is therefore essential to keep electronics at a safe temperature and reliable performance. We often refer to Moore's law as an indicator for the exponential growth of the transistor count in electronics and the power density of our computing capabilities. However, from a microscopic point of view the urge for improved thermal designs in electronics has therefore increased at the same time. As an example, confined electronics' self-heating hot spots with power densities from 300 W/cm² and above are a significant threat for the long-term use of microprocessors. To illustrate the impact of heat in electronics, Fig. 1.2 (a) shows a temperature map of an Intel Itanium processor with an asymmetric heat spreading along the processor. An important metric related

with thermal management in these processors is the thermal design power (TDP). TDP describes the average power dissipation of the processor when operating at base frequency. Fig. 1.2 (b) shows the maximum TDP and the lithography size of new released processors from Intel as a function of their launch date. We can observe that the max TDP tends to increase while the miniaturization of the device level continues. Therefore, improving our thermal management capabilities at lower scales is an essential need for the reduction of the TDP in microprocessors. Thermal control devices at the micro and nanoscale that can manage heat in a more advanced way will not only have an impact in electronics but also in other energy related applications, such as storage or scavenging technologies.

The following sub-sections elaborate in detail the domains of energy dissipation in electronics and novel thermal management strategies which are relevant to this thesis.

### 1.1 Energy dissipation in electronics

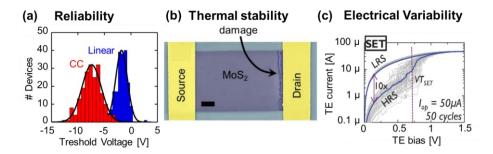

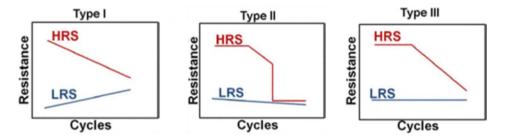

The flow of charge carriers along a material under the presence of an electric field results in scattering with the atoms of the lattice. This leads to the generation of Joule (self) heating.<sup>1</sup> The magnitude of this heat dissipation scales with the current density and the electrical field of the flow. Following the trends of power density in electronics, the magnitude of Joule heating becomes an equally growing issue in nanoscale devices like transistors and interconnects.<sup>13</sup> In that context Fig. 1.3 shows various performance limitations in different nanoscale electronics which are originated from heating.<sup>14–16</sup> As an example, in modern transistor device heat dissipation is a severe limitation for their reliability and can lead to thermal breakdown as illustrated in Fig. 1.3 (a) and (b).<sup>13–15</sup> As another example, in modern memory devices, heat is a major source for the variability of operation leading to a strong shift of the current vs voltage behavior in between cycles, as illustrated in Fig. 1.3 (c).

This thesis focuses on the thermal characterization of memory resistive switching (RS) devices, which are very promising compared to other state-of-the-art memories.<sup>17</sup> The unique features of RS devices include non-volatility, high storage density and fast parallel computing ability which make them ideal for neuromorphic computing.<sup>17</sup> In comparison to commercially available memory technologies, as static random-access memory (SRAM) or dynamic random access memory (DRAM) devices, RS devices are

**Figure 1.3 (a)** Distribution of the threshold voltage of hundreds of  $MoS_2$  field effect transistors (blue: linear method, red: constant current method). **(b)** colored SEM image of a  $MoS_2$  2D transistor channel after thermal breakdown (scale bar 1  $\mu$ m). **(c)** electrical current at the top electrode (TE) as a function of the applied bias during the set process of a resistive switching (RS) device during 50 cycles. **(a)** Adapted with permission from Lanza *et al.* <sup>14</sup> **(b)** Adapted with permission from Yalon *et al.* <sup>15</sup> **(c)** Adapted with permission from Lanza *et al.* <sup>16</sup>

typically non-volatile and therefore do not require a power intensive refresh. <sup>18</sup> Currently used non-volatile memories as flash devices require a comparably high programming voltage (< 10 V) with a typical endurance of > 10<sup>4</sup>-10<sup>5</sup> cycles. RS devices can be operated at relative low programming voltages (< 3V) with a higher endurance (> 10<sup>6</sup> cycles). <sup>18</sup>

Promising candidates for RS memory include conductive bridge random access memory (CBRAM), phase change memory (PCMe) and resistive random access memory (RRAM) devices. <sup>19</sup> In PCMe structures a phase change material, like vanadium dioxide (VO<sub>2</sub>) or chalcogenides that can change between an insulating and conductive state, is placed in between two electrodes. <sup>19–21</sup> The phase change is induced by applying a current through the material that heats it up. The two different resistive states of the two phases represent the logic states. <sup>19</sup> On the other hand, RRAM devices consist of a metal-insulator-metal (MIM) structure. <sup>22</sup> By applying a bias across the two electrodes one can form and disrupt an electrically conductive path based on oxygen vacancies in an oxide based insulating material. <sup>19</sup> Finally, in CBRAM the metal oxide is replaced by a solid electrolyte and an easily oxidizable metal is used as the top electrode. By applying a bias, mobile metal atoms from the top electrode form an electrical path to the

bottom electrode.<sup>19</sup> Challenges of RS devices are connected with the variability, reliability and thermal stability of the switching process.<sup>17</sup>

In that regard, heat dissipation plays an essential role in the operation and performance of RS devices in many ways. 17 As an example, the operation of PCMe devices is based on the thermally activated phase transition of the active material.<sup>21,23</sup> However, heat dissipation can be a potential source of device failure for PCMe as well. In filamentary-type RRAM the switching process is based on the formation and rupture of spatially confined conductive paths mostly referred to conductive filaments (CF).<sup>24</sup> Due to the extremely confined area of the filament, potentially down to 10 - 7 nm in diameter, extremely high power densities > 10<sup>13</sup> W/cm<sup>3</sup> are estimated to be achieved during operation.<sup>25</sup> Hence, Joule heating in these devices can facilitate thermal activated processes as ionic diffusion.<sup>26</sup> However, the development of this technology is limited by its high operation variability that originates partially from the spatial extent and temperature of the filaments. 17,27 The following section focuses on challenges related to heat dissipation in RRAM devices, which are characterized in the course of the experimental work in this thesis.

### 1.1.1 RRAM device fabrication

As mentioned above, RRAM devices consist of a metal-insulator-metal structure, where the insulator is typically a metal oxide. In the recent years, a wide variety of metal oxides have been studied for RRAM devices, like  $HfO_2$ .  $^{25,28,29}$ .  $Ta_2O_5$   $^{30,31}$  or  $TiO_2$   $^{32-34}$ .

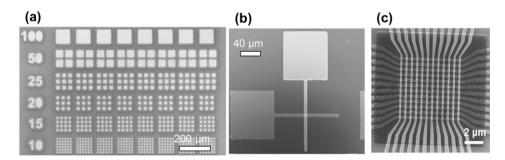

**Figure 1.4** Common device structures in resistive random access memory (RRAM) devices. **(a)** Common bottom electrode structure (scale bar 200  $\mu$ m), **(b)** cross-point structure (40  $\mu$ m), **(c)** crossbar structure (2  $\mu$ m). Adapted with permission from Lanza *et al.* <sup>16</sup>

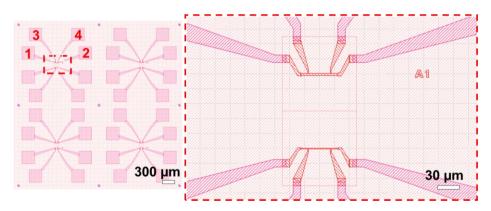

Concerning the RRAM device structure, one usually distinguishes between three different types, as presented in Fig. 1.4. <sup>16</sup> Fig. 1.4 (a) shows the typical bottom electrode method. In this case an insulating layer is grown all over a conducting substrate. The metallic top electrodes are patterned on top of the insulating layer. However, this method is limited to a minimum electrode size of ~ 100 µm² for allowing the probe access for electrical characterization. <sup>16</sup> Fig. 1.4 (b) shows an example of a cross-point device area. The fabrication process of the cross-point structure is more complex than the common bottom electrode approach, as it requires at least two lithography steps. <sup>16</sup> However these structures allow a characterization of single devices with areas below microscale. For the analysis of the switching characteristics on a circuit level, crossbar structures as depicted in Fig. 1.4 (c) are widely used. In this case the individual device areas are interconnected with thin wires to common large electrode pads. <sup>16</sup>

### 1.1.2 RRAM operation principle

In RRAM devices based on metal oxides we can switch from a high resistive (HRS) to a low resistive (LRS) state. We transition between these states through processes of set, i.e., HRS to LRS, and reset, i.e., LRS to HRS. <sup>16,35</sup> Fig. 1.5 shows a schematic illustration of the initial forming, set and reset process of the filament in a metal-insulator-metal based RRAM device. We can consider Ti/Au-TiO<sub>2</sub>-Ti/Au for illustration purposes. <sup>36</sup> At the beginning,

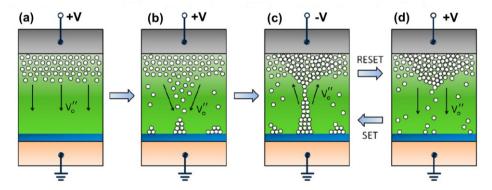

**Figure 1.5** Schematic of the forming, set and reset mechanisms in an oxygen vacancy driven RRAM device with a metal-insulator-metal (MIM) structure. The figures present the oxygen vacancy  $V_0^{\prime\prime}$  distribution (white circles) of the RRAM device in **(a)** pristine, **(b)** during set, **(c)** in the ON and **(d)** OFF state. The operation is achieved by applying a voltage bias of different polarity +V and -V across the electrodes. Adapted with permission from Hu *et al.*<sup>36</sup>

i.e., pristine state (Fig. 1.5 (a)), the RRAM devices are in their HRS. An oxygen vacancy rich layer on top of the TiO<sub>2</sub> layer is originated during the metallization of the top electrode. When applying a sufficiently high electric field, a CF is formed in the oxide between the top and bottom electrodes (Fig. 1.5 (b-c)).24 The device is then in the LRS, i.e., set process. Due to the application of a positive voltage bias, drifting vacancies are partially reduced and redistributed towards the bottom electrode (as shown in Fig. 1.5 (b)).36 As a result, a localized path of oxygen vacancies is formed in the active area (Fig. 1.5 (c)), 36 which create a small conductive path. The breakdown of the filament happens when applying a sufficiently high bias of reversed polarity (bipolar) or at the same polarity (unipolar).<sup>24</sup> For this particular example, by applying a reverse bias the CF is dissolved and oxygen vacancies are pulled back to the top electrode (as shown in Fig. 1.5 (d)). When the CF breakdown occurs, the device returns to its HRS, i.e., reset process (Fig. 1.5 (d)), For the initial forming of the CF usually a higher voltage is required than for the subsequent set processes due to the low intrinsic defect density in the pristine state.<sup>24</sup> RRAM devices can be set and reset during multiple cycles with endurances of up to 10<sup>12</sup> cycles and beyond.<sup>37</sup>

It is worth noting that this explanation is not a universal answer to describe the physical mechanisms of switching in all RRAM devices, since the process of forming can be more complex. However, It is a good representation of the operation principles of the metal-oxide RRAMs presented in this thesis.

### 1.1.3 Electrical performance in RRAM

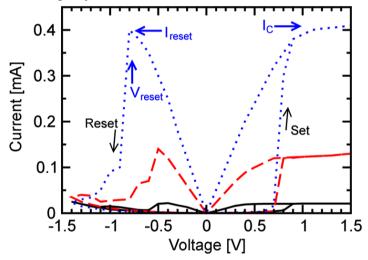

RRAM devices are electrically characterized through current vs voltage (IV) measurements during cycling. <sup>16</sup> Fig. 1.6 shows typical IV curves obtained in a bipolar RRAM device for three different current compliances. <sup>38</sup> Starting in HRS, the electrical current displays a small magnitude at low bias during the set process. Once the applied voltage exceeds the set voltage, the current increases abruptly due to the formation of the conductive filament. The device remains in LRS after turning off the voltage, showing non-volatile behavior. When applying a sufficiently high voltage at the reversed polarity,  $V_{\rm reset}$ , the current drops again showing the transition from LRS to HRS.

Usually, a higher electrical power is required for the reset process than for the set process. The type and the size of the filament during the forming can be customized by adjusting the current compliance  $I_c$  during the set process. The filament size and thus the resistance in the set state correlates with the intensity of the current applied. However, the higher the  $I_c$  is, the higher  $V_{\text{reset}}$

is required for the filament breakdown. If filaments with too large diameter are formed, they cannot be reset anymore.<sup>17</sup> Therefore, during RRAM operation one must consider a tradeoff between high ON/OFF ratios and cycling reliability.

The electrical performance of RRAM devices has been characterized in a broad number of studies. 16,18,24,39 Therefore, the reliability of the cycling in RRAM devices is most commonly evaluated by the endurance, state retention, switching time and energy consumption, variability and scalability of the *IV* behavior. A common tool for the electrical characterization of RRAM devices is a semiconductor parameter analyzer (SPA). This tool can perform simple *IV* sweeps in a reliable way to obtain the characteristic *IV* curves of the device, as displayed in Fig. 1.6. However, this technique is time intensive (30-60 seconds per cycle). Pulsed voltage stresses (PVS) methods can be employed for a more convenient characterization of the endurance of the device for a high cycle number > 1000.16

**Figure 1.6** Electrical current vs voltage of a RRAM device during the set (at positive voltage) and reset (at negative voltage). The cycles are obtained for different current compliances ( $I_{\rm C}$ ), which correspond to black, red and blue lines. The reset is achieved by applying a reverse bias ( $V_{\rm reset}$ ) corresponding to the initial bias polarity. The magnitude of the reset current ( $I_{\rm reset}$ ) depends on the  $I_{\rm C}$  applied during the set. Reproduced with permission from lelmini *et al.*<sup>38</sup>

### 1.1.4 Limitations and potential sources of device failure

RRAM devices combine excellent stability, high switching speed, a long endurance, low power consumption and a simple structure, making it especially interesting in a vast field of applications. 18,40 On the flipside, performance variability of the operation resistive switching memories is still a major limitation for an extended application of these devices. 16 For example, high variability limits the reliable programming of multiple resistive states. Thermal stresses can reduce the lifetime and reliability of devices significantly. 41

The lack of reliability in device operation and storage mechanisms in RRAM devices results in high variability of their electrical performance. <sup>42,43</sup> In that context one distinguishes between the cycle-to-cycle (C2C) variability and the device-to-device (D2D) variability of the electrical switching. On the one hand, the C2C variability shows how *IV* curves vary for different cycles within the same device. On the other hand, the D2D variability describes how the *IV* curves change between different devices of the same kind. While variability might be even beneficial for some applications e.g., for random number generators, it is a major limitation for information storage. <sup>16</sup> This variability is in a great level intrinsically related with the nature and formation process of the filament.

Therefore, understanding the underlying fundamental operation, like filament sizes<sup>44</sup> and positions,<sup>45</sup> current densities<sup>46</sup> and heating,<sup>47</sup> is essential for the

**Figure 1.7** Illustration of the resistance vs cycle behavior for three main failure mechanisms of RRAM devices. Type 1 refers to the formation of an interfacial electron barrier. Type 2 refers to the enlarging of the conductive filament by means of redundant oxygen vacancies. Type 3 illustrates the gradual change of the HRS due to a decreasing recombination rate of oxygen vacancies. Adapted with permission from Chen *et al.*<sup>27</sup>

evaluation, design and optimization of RRAM devices. Different studies estimated that the diameter of conductive filaments could reach values down to 10 nm and below. 48,49 High power densities during device operation can result in extremely high temperature increments of >1000 K in memories.<sup>25</sup> These elevated temperatures are a major source for a potential failure of RRAM devices, affecting their endurance. Fig. 1.7 shows the three types of failure mechanisms in RRAMs.<sup>27</sup> One type of failure, label as type 1 in Fig. 1.7, originates from the development of an interfacial electron barrier sourced from high temperature and high current. 17 As a consequence the switching in the active area gets less relevant. Another type of failure, i.e., type 2 in Fig. 1.7, corresponds to the electric field and elevated temperature that led to an excess production of oxygen vacancies. This phenomenon results in an increment of the filament size. If the filament size becomes too big, the device cannot be reset anymore. Finally, failure type 3 in Fig. 1.7 appears at frequent cycling, when the recombination of oxygen ions and vacancies is reduced during the reset process. This leads to a gradual decay of the HRS.<sup>17</sup>

Beyond this threat for the individuals components, extensive heat dissipation from single devices can also affect the performance characteristics of devices in proximity, referred to as thermal crosstalk. Within this context, thermal management is becoming essential in memory based circuits, like neuromorphic computing, where controlling temperature variations is needed for efficient and stable data processing. Therefore, further observations and analysis of filamentary induced hot spots in RRAMs remain relevant as they reveal the need for thermal management to achieve optimum, reliable and efficient performance of their resistive states.

Even though there has been an extensive amount of research on the characterization of the electrical current vs voltage behavior in these devices, only few studies on the exact characterization of the energy dissipation have been conducted. Therefore, further studies concerning the thermal characterization of the energy dissipation in these devices are essential. We must obtain better understanding of how heat affects the resistive switching in memories, and thus, to facilitate the development of new thermal designs that reduce variability.

### 1.2 Thermal characterization of RRAM devices

Several experimental<sup>25,52,53</sup> and theoretical<sup>25,54–57</sup> approaches have been applied to study the temperature of CFs in RRAM devices. As an example,

thermal analysis with finite element modelling have been conducted to estimate the filament temperature and thermo-dynamics in memories.<sup>25,54–57</sup> However, the experimental investigation of the temperature reached by filaments during operation remains challenging.

On the one hand a high spatial resolution is required to map accurately the hot spots generated by conductive filaments with sizes down to 100 nm. On the other hand, the CF is buried under the top electrode surface, which needs to be taken into account during the analysis. Optical based techniques, like Raman thermometry or infrared scopes, do not present enough spatial resolution to resolve the hot spots generated by CFs in RRAMs. Recently, scanning thermal microscopy (SThM), <sup>23,58–63</sup> i.e., a scanning probe microscopy based technique, has been able to resolve successfully localized heating features at the surface of RRAM devices. <sup>25,52,53</sup>

SThM operates in contact mode obtaining both topographic and thermal maps of the sample surface. It combines a high temporal resolution with a thermal time constant of few hundreds of microseconds and nanoscale spatial resolution.<sup>64</sup> Given these features, SThM has become a popular choice in different studies for the characterization of thermal properties at the nanoscale, like in thermoelectric materials, phase change materials or filamentary based memory.<sup>63,65,66</sup>

### 1.2.1 Operation principle of SThM

The SThM uses a special thermal probe that can work both as nanoscale heater and/or thermometer. Over the years, there has been a wide variety of probes that have been developed to allow this functionality, such as thermoresistive or thermovoltage probes among others.<sup>64,67</sup> In this thesis, only thermoresistive probes are used.

A thermoresistive SThM probe is made of an element whose electrical resistance correlates with changes in temperature. This probe senses differences in the temperature of a scanned surface due to changes in its electrical resistance. The electrical resistance of the probe  $(R_{probe})$  can be written as a function of the probe temperature T as follows,

$$R_{\text{probe}}(T) = R_0 \cdot \left(1 + TCR \cdot (T - T_0)\right) \tag{1.1}$$

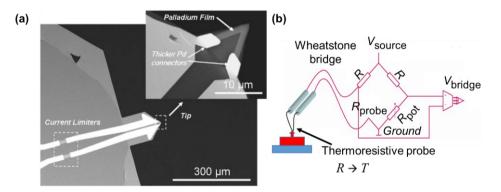

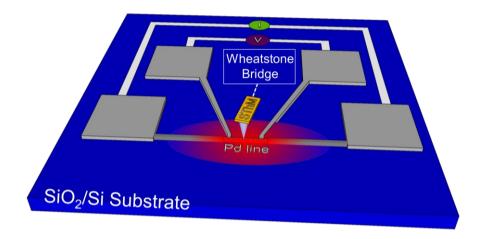

where  $(R_0)$  is the probe resistance at a reference temperature  $(T_0)$  and TCR is the temperature coefficient of resistance. The TCR indicates how much the resistance of a thermoresistive material changes when it increases one degree in temperature. Fig. 1.8 (a) shows a scanning electron microscopy (SEM) image of the thermoresistive probe model that is used in this thesis. It consists of a thin palladium (Pd) line on top of a silicon nitride (SiN) substrate. The Pd-film is the thermoresistive element, which is a popular material for this type of probes as it possesses a high TCR and thus a high temperature sensistivity.  $^{64}$

**Figure 1.8** Scanning electron microscopy (SEM) image of a Pd film based thermoresistive SThM probe, **(b)** Schematic illustration of an electrical Wheatstone bridge connected to a SThM probe resistance ( $R_{\text{probe}}$ ). The remaining bridge consists of two fixed resistances (R) and an adjustable potentiometer ( $R_{\text{pot}}$ ). During SThM measurements, variations in the temperature of the probe can be sensed by electrical variations across the bridge ( $V_{\text{bridge}}$ ). Adapted with permission from Puyoo *et al.*<sup>69</sup>

For accurately reading the electrical response of the probe due to thermal variations, the SThM probe is usually connected to an external circuit called Wheatstone bridge. Fig. 1.8 (b) shows a schematic illustration of the SThM probe within a Wheatstone bridge. <sup>69</sup> The Wheatstone bridge consists of four resistances, two fixed resistances (R), one adjustable potentiometer ( $R_{pot}$ ) and the resistance of the probe itself ( $R_{probe}$ ). When using the SThM as temperature sensor a small bias is applied along the bridge ( $V_{source}$ ) to read the electrical resistance of the probe while minimizing its self-heating. When scanning the SThM probe under this configuration over a heated sample, one can sense an increase in the potential signal across the bridge ( $V_{bridge}$ ).

The electrical resistance of the probe, i.e., and hence  $V_{\text{bridge}}$ , varies during the scan as the temperature along the sample surface modifies.

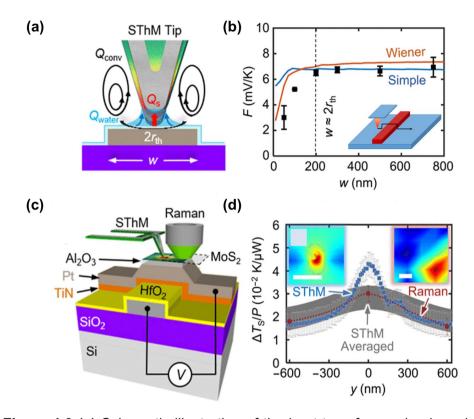

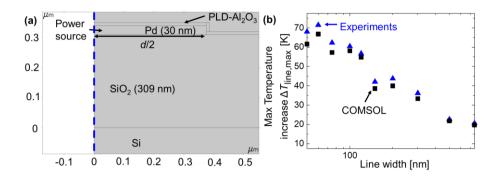

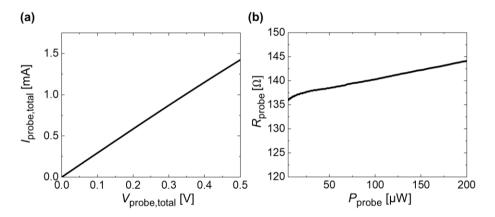

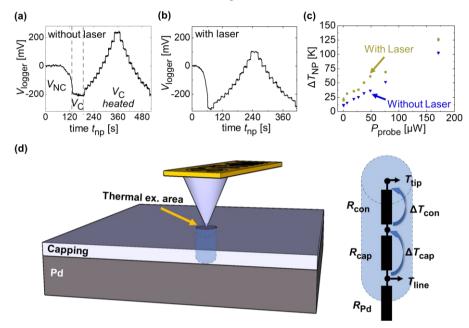

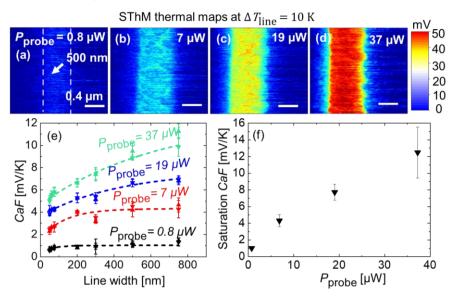

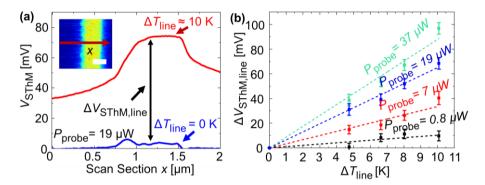

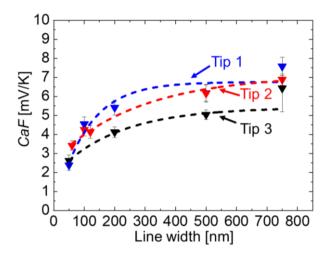

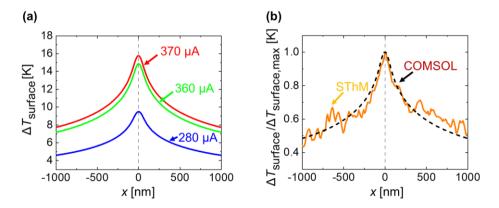

# 1.2.2 SThM calibration approaches for sensing nanoscale heating features

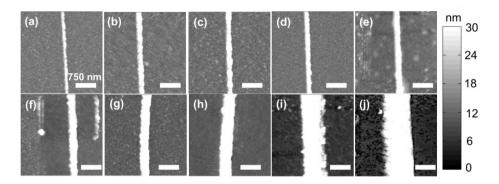

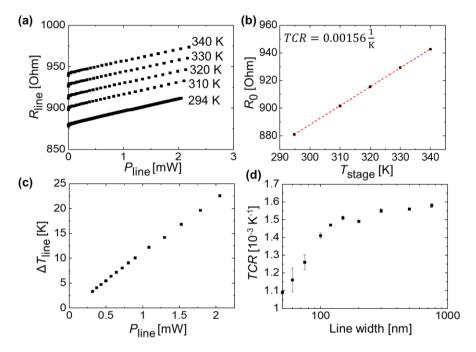

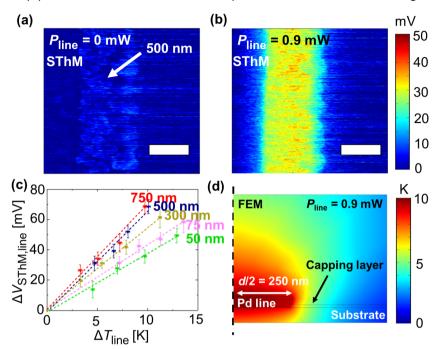

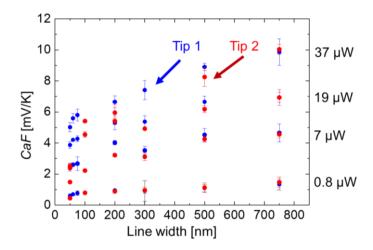

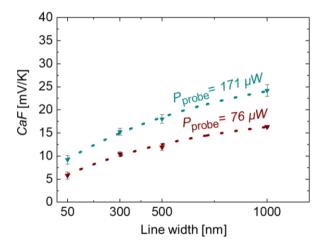

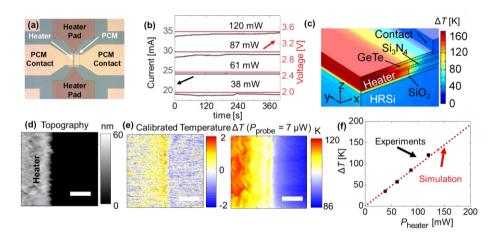

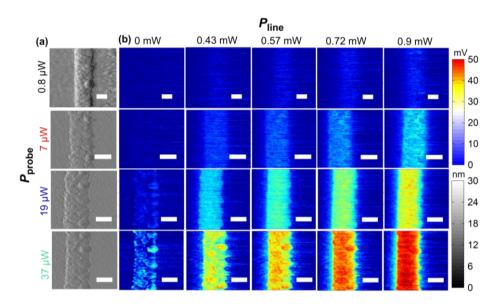

One of the major challenges of the SThM is to convert the electrical signal measured in the Wheatstone bridge (mV) into temperature readings (K). For that purpose, one requires to employ a careful calibration approach. 25,52,70-72 As an example, Deshmukh et al. 25 suggested a calibration method based on scanning heated Pd metal lines of different widths, w. In this approach, the SThM signal is obtained when scanning the heated surface lines. The temperature of the metal lines at certain power are calculated once one determines their TCR and using equation 1.1. By connecting the SThM signal in mV with the temperature in K of the lines, a calibration factor (CaF) is obtained. Fig. 1.9 (a) schematically illustrates the main heat transfer mechanisms between the probe and the sample at atmospheric conditions during this calibration approach. The authors assumed that the major source of heat exchange at the vicinity of the probe are due to convection ( $Q_{conv}$ ), water meniscus ( $Q_{water}$ ) and conduction ( $Q_{S}$ ) between the sample and the tip. The water meniscus is formed when the probe tip is in contact with the sample in humid or atmospheric air conditions. Hereby a liquid water bridge is formed between the tip and the sample surface which pulls the cantilever in contact with the sample. 145 In this case additional heat is transported through the water meniscus. 64 The area of heat exchange between them can be approximated by a disc with a thermal exchange radius of  $r_{th}$ . Fig. 1.9 (b) shows the calibration factors obtained as a function of the line width. From this graph they observed a saturation on the calibration factor for line widths larger than 200 nm. The authors argued that this cut-off in the line width should define the natural thermal exchange radius of the probe. At line widths lower than that, the thermal exchange radius between probe and tip is truncated and thus the calibration factor varies.<sup>25</sup>

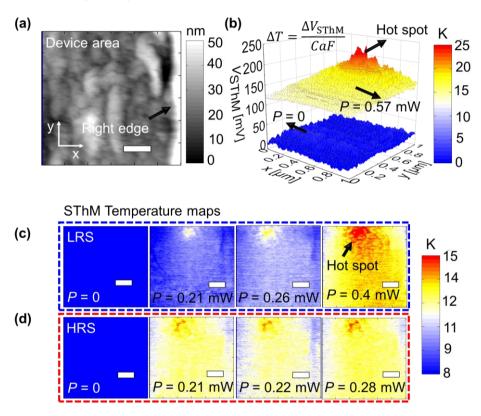

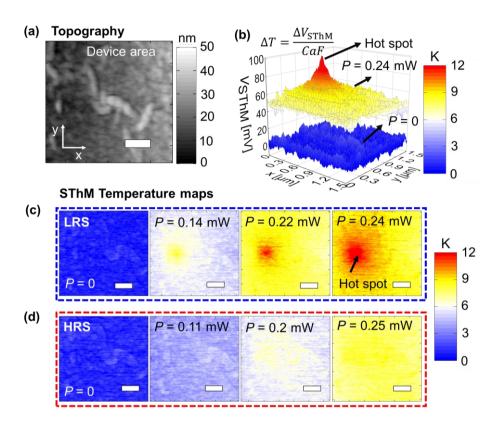

### 1.2.3 RRAM filamentary hot spot characterization with SThM

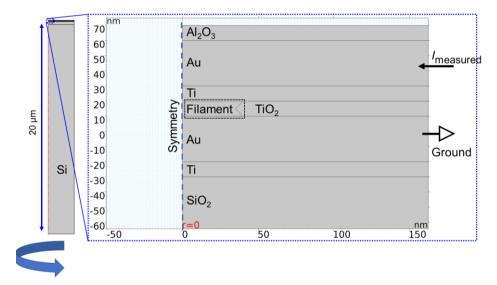

Recently, a calibrated SThM has been used to characterize the hot spots in filamentary based RRAM devices. Fig. 1.9 (c) shows the schematic set up and device structure of the study conducted by Deshmukh *et al.* based RRAM devices by means of a SThM that is calibrated as explained in section 1.2.2. Fig. 1.9 (d) shows the temperature profiles and thermal maps of hot spots measured with SThM (left inset image). The results are compared to the

**Figure 1.9 (a)** Schematic illustration of the heat transfer mechanisms in between a SThM probe and a Pd metal line with the width w. The heat between tip and sample is exchanged due to thermal conduction ( $Q_S$ ), water meniscus ( $Q_{water}$ ) and convection ( $Q_{conv}$ ) in a thermal exchange area with a thermal exchange radius of  $r_{th}$  (the contribution of radiation in this experiment is negligible); **(b)** SThM calibration factor estimated by characterizing Pd metal line as depicted in (a) as a function of the line width; **(c)** Setup for the thermal measurement of hot spots in HfO<sub>2</sub> based RRAM devices by means of SThM and Raman thermometry; **(d)** SThM and Raman temperature maps and top temperature profiles along the hot spot, normalized by the applied power of hot spots in the same RRAM device (scale bars 750 nm). Adapted with permission from Deshmukh *et al.*<sup>25</sup>

thermal analysis carried out with Raman thermometry, an optical based technique (right inset image). Raman thermometry is not capable to resolve spatially the hot spot generated from CFs, which highlights the advantage and need of using SThM to characterize nanoscale thermal features.

Similarly, Nandi *et al.*<sup>53</sup> investigated the temperature distribution in  $NbO_x$  based RRAM devices.

Apart from the above mentioned examples, experimental studies on heat dissipation in RRAM remain scarce. This thesis aims to expand our knowledge in various aspects of the energy dissipation in RRAM devices to offer innovative design routes that improve their performance. For this purpose, I plan to characterize the electrical properties and heat dissipation in TiO<sub>2</sub> based RRAM devices with different areas and compare these features with the device variability. For achieving this, I first extend the calibration approach described in section 1.2.2 to enlarge the versatility of SThM for thermal characterization of electronic devices. Based on the knowledge gained, I draw conclusions on how to take advantage of the electro-thermal analysis of the RRAMs to design future devices.

# 1.3 Thermal control devices for advanced thermal management

Thermal management of electronics can help to regulate the temperature of devices to favor optimum performance. Being at frontiers of thermal management that expand our capabilities to control heat will not only improve our heat dissipation in electrical based technology, but it will bring new opportunities to fields related with energy conversion or storage. As an example, better heat management has a high potential to improve the efficiency of thermoelectric devices or heat storage tanks. Being at frontiers of thermoelectric devices are help to regulate the temperature of thermoelectric devices can help to regulate the temperature of thermoelectric devices are help to regulate the temperature of thermoelectric devices are help to regulate the temperature of thermoelectric devices are help to regulate the temperature of the temperature of the regulate the regulate the regulate the temperature of the regulate the regu

In this context, the field of solid-state thermal control devices, i.e., thermal diodes, regulators, switches and transistors has received an increased attention during the last decade. These thermal control devices are made of materials that exhibit non-linear and switchable thermal behavior. They offer new opportunities to control the heat compared to the traditional toolkit of thermal resistors and capacitors. Solid-state thermal devices are silent, reliable, do not present moving parts and can be easily scaled down, which represents an advantage compared to fluidic or mechanical thermal devices. This makes them ideal for thermal management of batteries and electronics, and electronics, on the development of novel thermal technologies such as phonon logic. The development of novel thermal technologies such as phonon logic. The development of novel thermal technologies such as phonon logic. The higher performance shown by solid-state thermal devices is typically lower than the ones obtained by mechanical or fluidic devices. The higher performance characteristics of mechanical and fluidic devices is enabled due to the activation principle of moving parts and

comes on the cost of the advantage of the reliable operations in solid state as mentioned above.

Nevertheless, solid-state devices have plenty of room for improvement because of their high degree of material tunability (size, 89-94 shape, 95,96 physical-chemistry, 97 etc.). Currently, there is an increasing number of experimental and theoretical publications that focus on the study of new structures and materials for advanced thermal control. 90 This thesis will only focus on one type of non-linear thermal device, i.e. the thermal diode.

### 1.3.1 Operation of thermal diodes

Solid-state thermal diodes present an asymmetric heat flow that depends on the direction of the temperature gradient, i.e., forward (fwd) vs reverse (rev) direction. This is typically achieved by material engineering or by connecting materials (junction) with dissimilar thermal properties. The research of solid-state thermal diodes started when Starr showed thermal rectification in copper oxides in 1936. More recently, nanotechnology has brought new material engineering opportunities to design reliable and efficient thermal rectifiers. The development of these devices has shown promising features for better management of heat in electronics, 102–105 electrocaloric refrigeration of for thermal computing.

Nanotechnology offers multiple strategies to improve the performance of thermal diodes.<sup>99</sup> This section mainly focuses on nano- to micro-scale thermal diodes based on the combination of different materials, i.e., two-segment materials.<sup>106</sup> Different diode designs can be compared using the following parameters, which are key to determine the device performance:

i) Rectification ratio (RR): Corresponds to the ability of the device to rectify heat. It is typically expressed as,

$$RR = \frac{|\dot{Q}_{\text{fwd}}| - |\dot{Q}_{\text{rev}}|}{|\dot{Q}_{\text{rev}}|}$$

(1.2)

where  $\dot{Q}_{\rm fwd}$  and  $\dot{Q}_{\rm rev}$  are the heat fluxes in the forward and reverse direction when  $|\dot{Q}_{\rm fwd}| > |\dot{Q}_{\rm rev}|$ .

ii) *Thermal bias:* It is the difference of temperature across the device, where  $T_h$  and  $T_c$  correspond to the temperatures of the heat source (hot terminal) and the heat sink (cold terminal).

### 1.3.2 Introduction to two-segment thermal diodes

The simplest design of a thermal diode in solid-state is based on two-segment materials. Such a device consists of a combination of two different material blocks with dissimilar thermal properties. The basic idea to achieve thermal rectification is that the two materials have a different thermal conductivity dependence with temperature. Under this condition, an inversion of the thermal bias (temperature gradient) direction results in a different magnitude of the heat flow (forward vs reverse) due to a change in the effective or overall thermal conduction across the two-segment material structure.

In solid state, we differentiate between three approaches to develop a thermal diode based on two-segment materials. First, devices in which the two material blocks have opposite thermal conductivity trends with rising temperature. For the sake of convenience, we define them as junction of materials with different thermal properties (JMT) diodes. Second, thermal diodes based on phase change materials (PCM). In these PCM diodes a solid to solid phase change is the basis for thermal rectification. Third thermal diodes based on radiative heat transfer. Radiative thermal diodes are less relevant for this thesis. Hence, the following part only focuses on the first two types of thermal diodes in the following.

### 1.3.3 Junction of materials with different thermal properties (JMT)

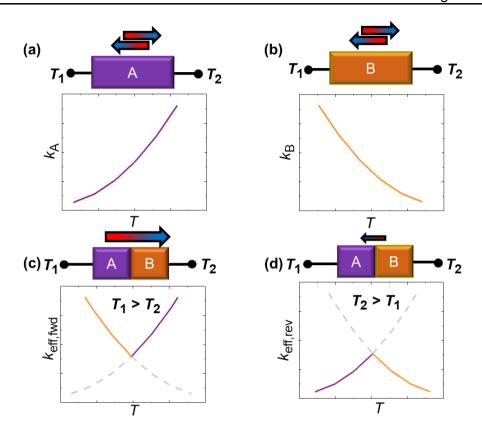

A JMT thermal diode is a two-segment material thermal diode made of two dissimilar material blocks, e.g., block A and block B.  $^{108,109}$  These two blocks present different temperature (T) dependent thermal conductivity (k) trends, as presented in Fig. 1.10. Fig. 1.10 (a) and (b) illustrate the thermal conductivity of the two material blocks ( $k_A$ ) and ( $k_B$ ) as a function of the temperature. Fig. 1.10 (a) shows that material block A has an increase in the thermal conductivity with increasing temperature. Fig. 1.10 (b) shows that the thermal conductivity of material block B is decreasing with increasing temperature. To understand how such a material system leads to thermal rectification, we must consider the effective thermal properties of the two-segment material structure depending on the thermal bias directionality. Hence, we need to consider two cases, i.e., when the thermal bias is applied in the forward ( $A \rightarrow B$ ) vs the reverse direction ( $B \rightarrow A$ ).

**Figure 1.10** Schematic drawing of the thermal conductivity (k) as a function of the temperature (T) in a JMT diode. Thermal conductivity of **(a)** block A and **(b)** of block B separately. Effective thermal conductivity  $(k_{\text{eff}})$  (continuous line) of the JMT diode in the **(c)** forward and **(d)** reverse direction.

Fig. 1.10 (c) and (d) illustrate the effective thermal conductivity of the material junction A-B structure in the forward and reverse direction. In the forward direction, a temperature gradient from the hot block A to the cold block B is established. Therefore, the effective thermal conductivity ( $k_{\rm eff,fwd}$ ) of the segment structure, i.e., continuous purple (block A) and orange lines (block B) of Fig. 1.10 (c), is high in the forward direction. In the reverse configuration, the temperature gradient is established from the hot block B to the cold block A. In this case the thermal conductivity trend of both blocks is now reversed compared to the forward case. As a result, the effective total thermal conductivity ( $k_{\rm eff,rev}$ ) of the two-segment structure is lower than in the

forward direction, i.e., continuous purple (block A) and gold (block B) lines of Fig. 1.10 (d). Hence, the total heat flux is expected to be higher in the forward direction in comparison to the reverse configuration under the condition that the temperatures of the terminals ( $T_h$  and  $T_c$ ) are held constant.

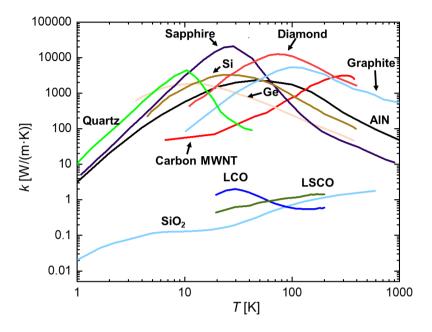

Fig. 1.11 shows the thermal conductivity trends of some materials as a function of temperature. These trends are in agreement with the theory of thermal transport expected for these materials. The From a simplistic point of view, the temperature-dependent thermal conductivity (k(T)) trends of typical materials can be described as: i) At low temperatures, k(T) is increasing with T due to the increase of the heat capacity until it reaches a peak. The peak position and magnitude of the thermal conductivity depends on the material. ii) At higher temperatures, the thermal conductivity decreases due to a reduction in the phonon mean free path (MFP). A combination of two materials with thermal conductivity peaks at different temperatures will result in the desired two-segment material junction structure.

In general, the thermal conductivity peak is reached below room temperature for most of the materials presented in Fig. 1.11. Additionally, there are some materials that present an increase of the thermal conductivity at room temperature (e.g., carbon nanotubes, 112 amorphous silicon oxide, 111 or caloric materials like gadolinium 121). To take advantage of the asymmetry in the effective thermal properties of the two blocks that form part of the JMT diode, the design is usually limited to low temperatures.

Jezowski and Rafalowicz<sup>106</sup> developed the first JMT diode experimentally in 1978. The authors investigated a junction of graphite and quartz considering absolute temperatures between 6 K and 95 K. The peak of the thermal conductivity of quartz can be found near 6 K.<sup>116,122</sup> In graphite this peak in the thermal conductivity is reached at around 100 K.<sup>115,123</sup> On the one hand, for temperatures below 100 K, graphite presents an increase in the thermal conductivity with rising temperature (block A). On the other hand, the thermal conductivity of quartz decreases for temperatures above 6 K (block B). This thermal diode reaches a maximum rectification of RR = 70% for a thermal bias of 40 K between heat source and heat sink.<sup>33</sup> Similarly, Kobayashi *et al.*<sup>107,124</sup> investigated LaCoO<sub>3</sub>/La<sub>0.7</sub>Sr<sub>0.3</sub>CoO<sub>3</sub> (LCO/LSCO) structures for thermal rectification. LSCO has an increasing k(T) with rising temperature, while LCO presents a decreasing k(T) behavior below 200 K. The authors

observed a thermal rectification of RR = 43% between 40 K (heat sink) and 98.9 K (heat source).<sup>107</sup>

**Figure 1.11** Thermal conductivity (k) of some materials as a function of the temperature (T). Data obtained from refs.<sup>78,111–116,124</sup>

### 1.3.4 Phase change material (PCM) thermal diodes

A phase change material (PCM) thermal diode is another type of two-segment material thermal diode. Here, the two-segment structure is made of a PCM block and a phase invariant material (PIM) block. On the one hand, a solid to solid structural change of the PCM occurs at a critical transition temperature ( $T_{\rm crit}$ ), leading to a variation of the PCMs thermal conductivity. On the other hand, the phase of the PIM remains invariant at the temperature of application. Bringing together a PCM and a PIM can lead to thermal rectification by taking advantage of the thermal conductivity change due to the phase transition of the PCM block. When the PCM block is in direct contact with the heat source and the temperature is higher than the transition temperature, a phase change in the PCM is induced. However, in the reverse case, when the temperatures in the PCM block are lower than the transition one, no phase change occurs.

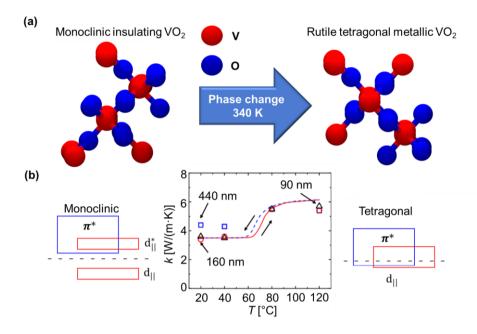

**Figure 1.12** Schematic drawing of the changes of  $VO_2$  at its phase transition. **(a)** Crystallographic structure phase change at 340 K from a monoclinic to a tetragonal phase, **(b)** Simple band diagrams and plot of the thermal conductivity (k) changes along the phase transition of  $VO_2$  films with thicknesses ranging from 90 to 440 nm as a function of the temperature (T). **(a)** Data obtained for the crystal structures from refs. <sup>140–144</sup> **(b)** Adapted with permission from Oh *et al.* <sup>129</sup> and Eyert. <sup>134</sup>

Therefore, two different effective thermal conductivities result from applying a gradient of temperature in the forward vs reverse direction. Recently, some research projects showed that a combination of two different PCMs is a promising approach to achieve high thermal rectification which may exceed values obtained by the regular PCM/PIM structures. 125–127

In many PCMs the change in the thermal properties occur in a small temperature range (few K) due to a change in the material crystalline structure when the temperature is higher than  $T_{\rm crit}$ . For that reason, in comparison to JMT diodes, high rectification ratios can already be achieved for small thermal biases (few K). However, the main challenge of PCM diodes is to choose a material that exhibits a phase change resulting in a large difference in thermal conductivity. As an example, vanadium dioxide

$(VO_2)$  is a PCM that has been used in thermal diodes.<sup>131,132</sup>  $VO_2$  presents a metal insulator phase transition (MIT) near room temperature.<sup>133</sup>

Fig. 1.12 depicts the MIT in VO<sub>2</sub> and its change in the thermal conductivity. Fig. 1.12 (a) shows that VO<sub>2</sub> has a monoclinic insulating state that typically changes to a rutile tetragonal metallic state when the temperature rises above ~ 340 K. The thermal conductivity increases across this phase transition. 129,130 As an example, Oh et al. 129 reported a  $\sim$  60% increase of k (from  $k \sim 3.5 \text{ W/(m·K)}$  to  $k \sim 5.5 \text{ W/(m·K)}$ ) in thin film  $VO_2$  as a consequence of the phase change. The reason for this thermal transition is based on the changes in the band structure and the influence of the electronic heat transport, illustrated in Fig. 1.12 (b). 129,134 While in the insulating state the valence band d<sub>1</sub> is separated from the conduction band due to a large band gap, the two bands overlap in the metallic state. 134 As a result, the electrical conduction is increased and hence the thermal conductivity, given the influence of the electrons as heat carriers. It is also worth noting that VO<sub>2</sub>, like other PCMs, might present hysteresis, meaning that the temperature at which the phase change happens when cooling vs heating might shift slightly. 135

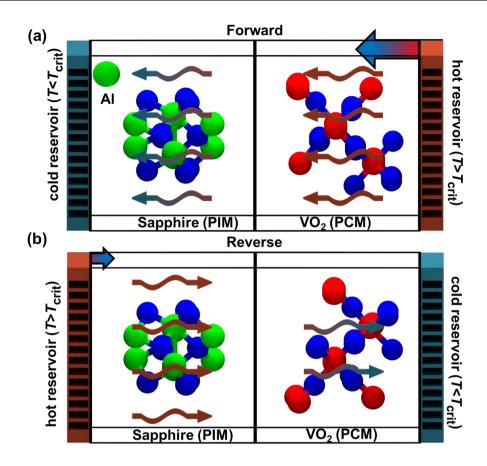

An example of a PCM diode using  $VO_2$  is illustrated in Fig. 1.13. This structure corresponds to the thermal diode based on a  $VO_2$ /Sapphire material combination which is reported by Ordonez-Miranda *et al.*<sup>136</sup> In the forward direction, the heat is flowing from the  $VO_2$  heat source to the sapphire heat sink. The temperature at the heat source is above  $T_{\rm crit}$  = 340 K, inducing the  $VO_2$  block to transition to its metallic state. However, in the reverse direction, the  $VO_2$  block is now at the insulating phase because the temperature is below its transition temperature. The phase of sapphire remains the same in both scenarios, i.e., PIM block. Under this scenario, the effective thermal conductivity of the PCM diode in the forward direction is higher than in the reverse one.

Kobayashi *et al.* <sup>128</sup> developed a millimeter sized PCM thermal rectifier based on La<sub>1.98</sub>Nd<sub>0.02</sub>CuO<sub>4</sub> (PIM) and MnV<sub>2</sub>O<sub>4</sub> (PCM). MnV<sub>2</sub>O<sub>4</sub> has a structural phase change at  $T_{crit}$  = 57 K that leads to an abrupt decrease in the thermal conductivity as the temperature increases. At this temperature the structure is converted from a tetragonal phase with a high thermal conductivity to a cubic phase with a lower one. <sup>128,137</sup> The authors observed a thermal rectification of *RR* = 14% for a temperature span between 55.4 K (heat sink)

**Figure 1.13** Schematic drawing of a sapphire/VO<sub>2</sub> diode. **(a)** Heat flux in forward direction (from the hot VO<sub>2</sub> to the cold sapphire), **(b)** Heat flux in reverse direction (from the hot sapphire to the cold VO<sub>2</sub>). The arrows show the direction of heat and indicate that the higher heat flux is in the forward direction. Data obtained for the crystal structures from refs.  $^{140-144}$

and 57.4 K (heat source), which can be considered as a high value considering the small thermal bias below 2 K. <sup>128</sup> Additionally, Garcia-Garcia and Alvarez-Quintana investigated the thermal rectification in a Nitinol/Graphite PCM thermal diode. In this case Nitinol is used as the PCM and graphite as the PIM. Nitinol has a structural phase change at around  $T_{\rm crit}$  = 330 K from a monoclinic martensite phase to a cubic austenite phase at temperatures higher than the transition one. <sup>138</sup> The authors observed a rise in the thermal conductivity of the Nitinol from  $k \sim 7.8$  W/(m·K) in the

martensite to  $k \sim 17.3$  W/(m·K) in the austenite phase. They obtained a maximum thermal rectification of RR = 47% at a temperature of 290 K with a thermal bias of 160 K.<sup>138</sup> The thermal conductivity rose gradually above the phase transition temperature and not as stepwise, which involved a significant enhancement of the thermal rectification at higher temperatures.

Solid-state thermal control devices like thermal diodes represent an emerging field that could make the leap into advanced heat control, expanding our thermal management capabilities. However, one of the limiting factors of these thermal devices is related to their characteristic performances. Solid state thermal diodes typically display rectification ratios below 100 %. Therefore this thesis aims to characterize a new design for the development of a thermal diode based on multilayer phase change materials. In that context I attempt to extend the prior described PCM/PIM structures. Due to that I expect to exceed rectification ratios obtained in simple state of the art PCM/PIM solid state thermal diodes. Moreover, I attempt to create additional degrees of freedom in the operation of such devices. Finally, I make on effort on presenting a potential application approach in which these thermal diodes can be implemented in thermal storage elements to increase their heat retention.

### 1.4 Scope of this thesis

This thesis revolves around the concept of heat at nano- and micro-scales and how to improve its management and control for applications related with electronics and heat storage.

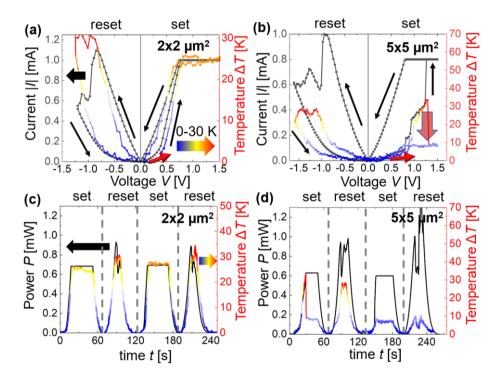

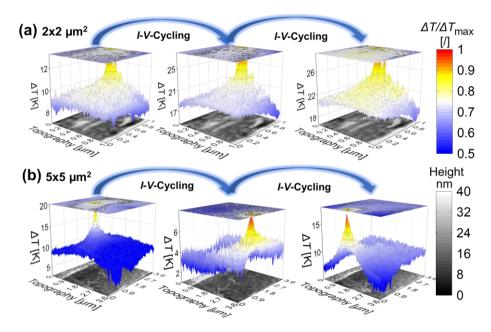

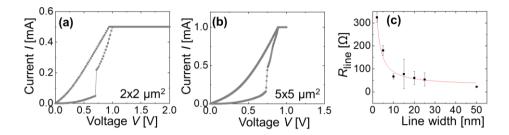

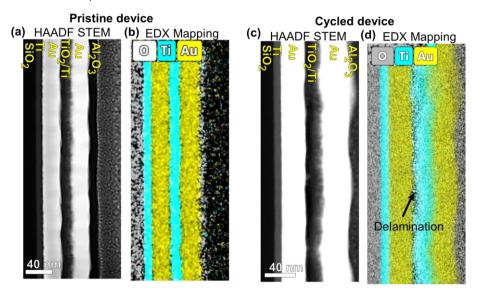

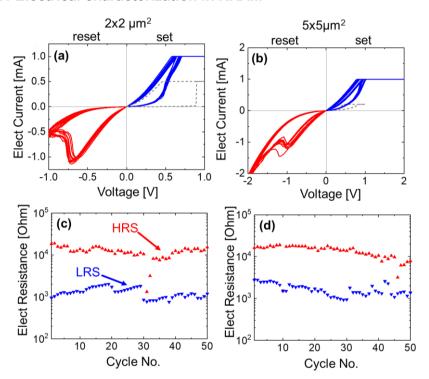

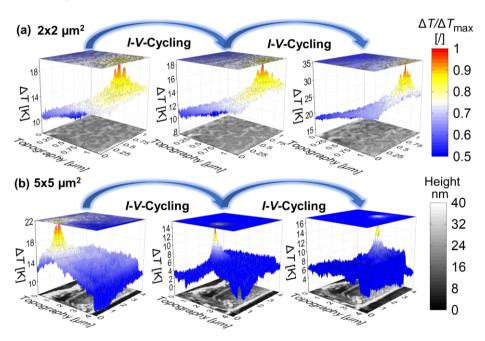

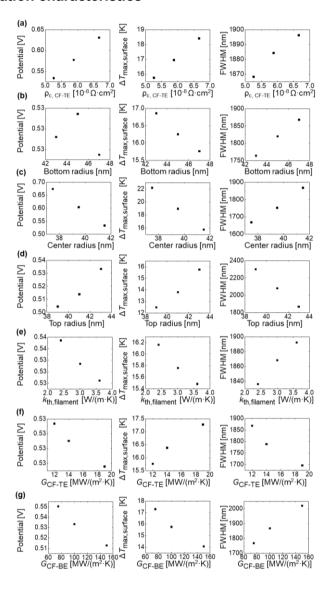

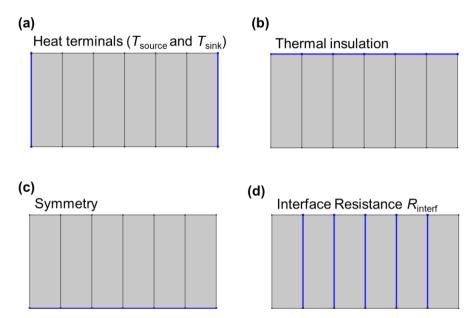

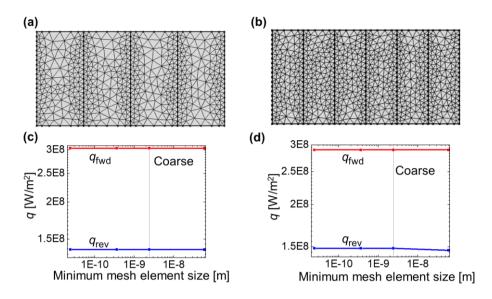

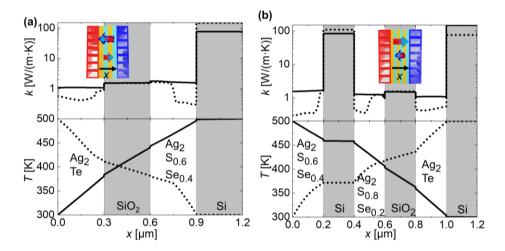

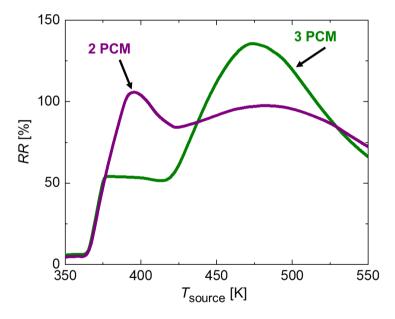

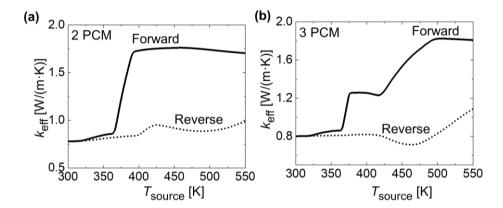

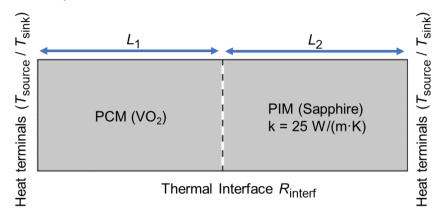

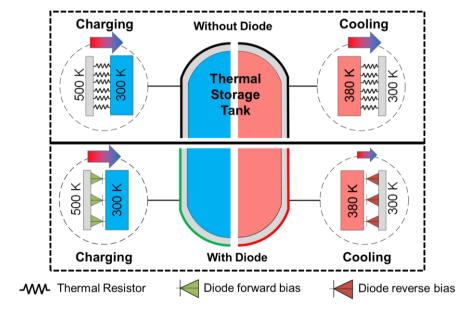

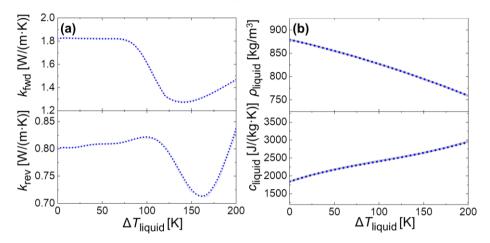

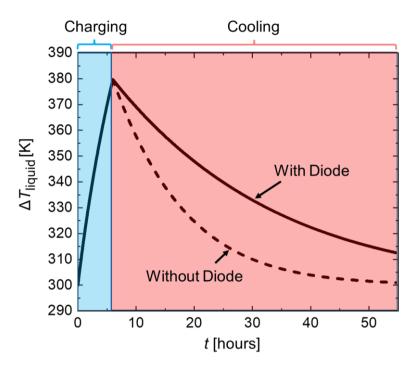

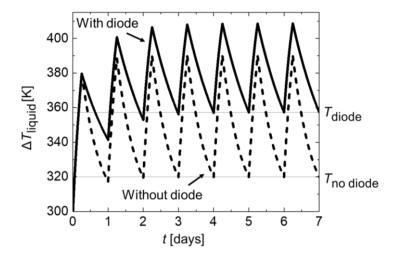

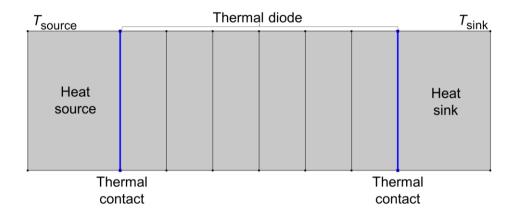

On the one hand, my first general goal is to gain deep insights on the electro-thermal switching mechanism of RRAM devices and how it affects their performance variability. For that purpose, I used scanning thermal microscopy (SThM) as a powerful and versatile tool for quantitative nanoscale thermal characterization of energy dissipation in electronics. A deeper understanding of the heat generated by modern memory devices will help our scientific and technological communities to develop design strategies that result in more efficient electronics. To achieve that, I had to overcome challenges related with the calibration of SThM and to carry out complex electro-thermal analysis of distinct types of TiO<sub>2</sub> RRAM devices.