# Marine Thruster I/O Board Redesign, Prototyping, and Certification

A thesis by

Frode Løvbrekke Aase

For the degree of

Master of Science in Physics

Institute of Physics and Technology

University of Bergen

August 2023

#### Abstract

For about 20 years, the company Marine Technologies have used a circuit board called the IOB, which controls input and output signals. The Input Output Board (IOB) uses a logic device to manage the different signals. For the last 20 years this has been an FPGA (Field Programmable Gate Arrays). The manufacture, design, and supply of IOB belonged to another company, but the time came for Marine Technologies to claim the ownership of the IOB and make a design of their own. This was a good opportunity to make design changes and the possibility of using microcontrollers instead of FPGAs became an interesting pursuit. Microcontrollers naturally are cheaper and easier to acquire and have become considerably advanced, making them a possible replacement candidate. This thesis explores the process of implementing a microcontroller with the new IOB design and having the product certified.

The new IOB must fulfill Marine Technologies' set of demands which require it to be functionally identical to the original; it also needs to fulfill the international sets of standards that amongst other things set the demands for environmental robustness and Electromagnetic Compatibility (EMC) performance. To meet this set of demands, I completed an analysis of the current I/O usage of Marine Technologies' systems and reduced the amount of I/O available to match this actual usage. This proved that a microcontroller have enough resources to handle the actual required I/O load of Marine Technologies' systems. In terms of EMC, the best one can do is to design a circuit board that follows design guidelines for EMC as closely as possible and test it when the prototype arrives. The number one rule for EMC minded design, is to allow return currents to flow directly under the outgoing signal trace, which is best achieved by having dedicated, proper, and unbroken power and ground planes, placed in the layers between the top and bottom layer of the PCB.

The design of the new IOB, called MT-IOB-Mk3-Transit, was done by closely examining the design of the previous two FPGA based iterations of the IOB, called the MT-IOB-Mk1 and MT-IOB-Mk2. The IOB-Mk3-Transit uses elements from both boards, by looking at 20 years of field testing and usage, what works best and what does not, while at the same time considering how the new microcontroller fits within these elements. In most aspects the IOB-Mk3-Transit is a mosaic containing elements from both the IOB-Mk1 and the Mk2, which are known to function reliably for 20 years.

During functional testing of the IOB-Mk3-Transit, the crucial functions were working well. The board was tested in a certification lab in Italy, and due to the board being designed with sub optimal EMC practice, we used two attempts in Italy before finally passing the EMC tests, requiring some research at home before travelling for the second attempt. The product was then certified, installed on a vessel and is now in use.

Taking the lessons learned from the IOB-Mk3-Transit, the new iteration purely called the MT-IOB-Mk3 has been designed, following the stated EMC guidelines closely to improve performance, and correcting a few minor issues of the IOB-Mk3-Transit. This board has yet to be tested. In the end, the question of using a microcontroller instead of an FPGA to perform the duties of the IOB, is only partially answered. Yes, the microcontroller can perform all the required functions that the FPGA did, and it will be implemented as a part of the Marine Technologies environment for now, but long-term reliability is a question that can only be answered by long-term use and testing.

## Acknowledgements

Words simply cannot express how thankful I am for my advisor Johan Alme from the University of Bergen. I could not have completed my thesis without your willingness for patience, guidance and understanding. I also must state my vast gratitude to the company Marine Technologies LLC for the opportunity to take on this task and providing me with the necessary resources to do so.

I would like to extend my thanks to my colleagues at Marine technologies of receiving my many questions and responding with many answers. In addition to many questions, the number of dry jokes you had to brave from my part is not lost on me, I commend your resilience.

As for my friends, my family, and my wife. Friends, you sent me words of encouragement and provided me with laughter when I needed it. Dearest family, you showed unwavering support and provided a place of peace and restitution. And lastly my wife, you stood by me when I needed help and never gave up faith in me.

# Contents

| Abstract |      |       |        |                                    | 1    |

|----------|------|-------|--------|------------------------------------|------|

| Α        | ckn  | owle  | edger  | nents                              | 2    |

| Fi       | gur  | res   |        |                                    | 6    |

| Τā       | able | es    |        |                                    | 8    |

| Te       | erm  | ninol | ogy a  | nd Abbreviations                   | 9    |

| 1        |      | Intro | oduct  | ion                                | . 10 |

|          | 1.:  | 1     | I/O I  | Board                              | . 12 |

|          | 1.2  | 2     | Obje   | ective                             | . 14 |

|          | 1.3  | 3     | Outl   | ine of Thesis                      | . 15 |

|          |      | Cha   | oter 2 | Requirements of the New IOB Design | . 15 |

|          |      | Cha   | oter 3 | Predesign Considerations           | . 16 |

|          |      | Cha   | oter 4 | Design                             | . 16 |

|          |      | Cha   | oter 5 | Test and Verification              | . 16 |

|          |      | Cha   | oter 6 | Integrated Design Phase            | . 16 |

|          |      | Cha   | oter 7 | Discussion and Conclusion          | . 16 |

| 2        |      | The   | Requ   | irements of the New IOB Design     | . 17 |

|          | 2.:  | 1     | Mar    | ine Technologies Requirements      | . 17 |

|          |      | 2.1.  | 1      | IOB-Mk1 and Mk2 Description        | . 17 |

|          |      | 2.1.2 | 2      | Functional Overview                | . 17 |

|          | 2.2  | 2     | Inte   | national Requirements              | . 19 |

| 3        |      | Pred  | lesigr | n Considerations                   | . 21 |

|          | 3.   | 1     | FPG    | A and Microcontroller in the IOB   | . 21 |

|          | 3.2  | 2     | Micr   | ocontroller Considerations         | . 22 |

|          |      | 3.2.  | 1      | Pin Function Planning              | . 23 |

|          | 3.3  | 3     | EMC    | Minded Design                      | . 24 |

|          |      | 3.3.  | 1      | The Path of Least Inductance       | . 24 |

|          |      | 3.3.2 | 2      | Layer Structure and Polygons       | . 26 |

| 4        |      | Desi  | gn     |                                    | . 27 |

|          | 4.   | 1     | The    | Digital Inputs and Outputs         | . 28 |

|          |      | 4.1.  | 1      | Digital Inputs (DI)                | . 28 |

|          |      | 4.1.2 |        | Digital Output (DO)                | . 29 |

|          |      | 41:   | 3      | Watchdog                           | 30   |

|   | 4.2   | Ana   | log Inputs (AI)                                     | . 32 |

|---|-------|-------|-----------------------------------------------------|------|

|   | 4.2   | .1    | Mk1 and Mk2 Analog Input Design                     | . 32 |

|   | 4.2   | .2    | Mk3-Transit Analog Input Design                     | . 34 |

|   | 4.3   | Ana   | log Outputs (AO)                                    | . 35 |

|   | 4.3   | .1    | Voltage Output                                      | . 35 |

|   | 4.3   | .2    | Current Output                                      | . 36 |

|   | 4.3   | .3    | Broken Loop Detection                               | .38  |

|   | 4.3.4 |       | Isolated Analog Output                              | . 39 |

|   | 4.4   | Data  | a Transmission                                      | . 40 |

|   | 4.4   | .1    | Ethernet                                            | . 40 |

|   | 4.4   | .2    | Serial Inputs                                       | .41  |

|   | 4.4   | .3    | I2C                                                 | .42  |

|   | 4.5   | Nuc   | leo Modification                                    | . 43 |

|   | 4.6   | Pow   | rer Distribution                                    | . 44 |

|   | 4.6   | .1    | Digital Power Distribution                          |      |

|   | 4.6   | .2    | Analog Power Distribution                           | . 45 |

|   | 4.6   | .3    | ±10V Reference                                      | .46  |

|   | 4.7   | PCB   | Layout                                              | .46  |

| 5 | Tes   | t and | Verification                                        | . 47 |

|   | 5.1   | PCB   | Build and Voltage Bias                              | . 49 |

|   | 5.1   | .1    | Voltage References                                  | . 49 |

|   | 5.2   | Fun   | ctional Verification                                | .50  |

|   | 5.2   |       | Ethernet Connectivity                               | . 50 |

|   | 5.2   |       | Analog Inputs                                       |      |

|   | 5.2   | .3    | Isolated Analog Outputs                             | .51  |

|   | 5.2   | .4    | Broken Loop Detection                               |      |

|   | 5.2   |       | Watchdog                                            |      |

|   | 5.3   | EMO   | and Certification                                   |      |

|   | 5.3   | .1    | Radiated Emissions Testing: Westcontrol             | . 55 |

|   | 5.3   |       | First Attempt EMC Certification                     |      |

|   | 5.3   | .3    | Test Using Spectrum Analyzer at Marine Technologies |      |

|   | 5.3   | .4    | Second Attempt EMC Verification                     | . 60 |

|   | 5.3   | .5    | Temperature Test                                    | . 63 |

|    | 5.4   | Overall Testing Results6                  | 4 |

|----|-------|-------------------------------------------|---|

| 6  | Int   | egrated Design Phase6                     | 5 |

|    | 6.1   | Corrected Issues6                         | 6 |

|    | 6.2   | EMC Improvements6                         | 7 |

| 7  | Dis   | cussion and Conclusion6                   | 9 |

| 8  | Re    | ferences7                                 | 0 |

| Αŗ | pend  | ix7                                       | 2 |

|    | A.    | EMC Certification Test Setup7             | 2 |

|    | В.    | Nucleo Pin Selection7                     | 3 |

|    | Nucle | eo Dev Board Pin Selection C11 Left Row7  | 3 |

|    | Nucle | eo Dev Board Pin Selection C11 Right Row7 | 4 |

|    | Nucle | eo Dev Board Pin Selection C12 Left Row7  | 5 |

|    | Nucle | eo Dev Board Pin Selection C12 Right Row7 | 6 |

|    | C.    | IOB 4X 80p Hirose usage7                  | 7 |

|    | J3.   | 7                                         | 7 |

|    | J4.   | 7                                         | 9 |

|    | J8.   | 8                                         | 1 |

|    | J9.   | 8                                         | 3 |

|    | D.    | PCB Layers for Mk3-Transit8               | 5 |

|    | E.    | PCB Layers for IOB-Mk39                   | 3 |

|    | F     | Certification tests and Documents 10      | 1 |

# Figures

| Figure 1-1: ASD Tug 5016 Vessel                                                                 | 10 |

|-------------------------------------------------------------------------------------------------|----|

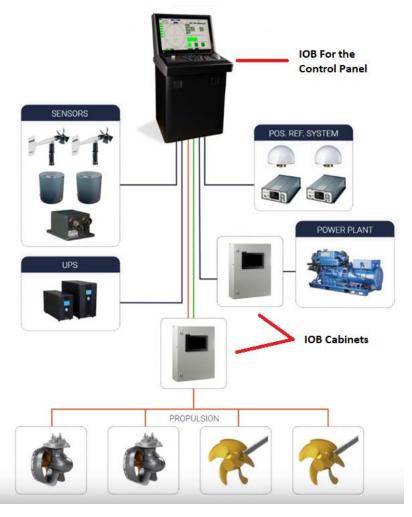

| Figure 1-2: MT DP1 System Overview                                                              | 11 |

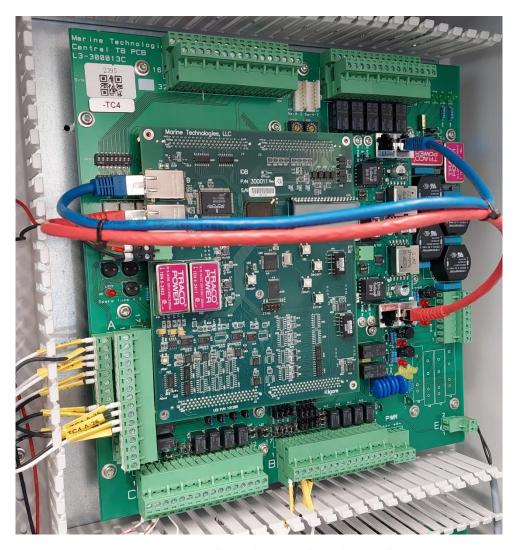

| Figure 1-3: Example of a IOB-Mk2 Board                                                          | 13 |

| Figure 1-4: Central-TB with an IOB-Mk1 card mounted                                             | 14 |

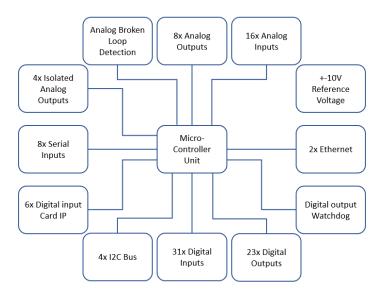

| Figure 2-1: Sketch given the functional requirements of the IOB in terms of functional entities | 18 |

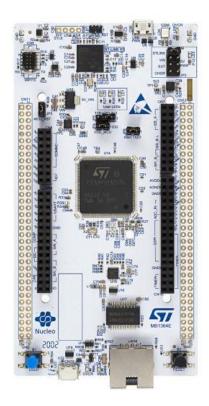

| Figure 3-1: Nucleo MB1364                                                                       | 22 |

| Figure 3-2: Nucleo Demo Board CN12 [5]                                                          | 23 |

| Figure 3-3: Current return path visualization of a high frequency signal [8]                    | 25 |

| Figure 3-4: Circular Loop Antenna                                                               | 25 |

| Figure 4-1: IOB-Mk3-Transit Board                                                               | 27 |

| Figure 4-2: Mk1 DI (Left) and Mk2 DI (Right)                                                    | 28 |

| Figure 4-3: Mk3 Transit DI pullups                                                              | 29 |

| Figure 4-4: IOB-Mk2 Digital Output Driver [10]                                                  | 29 |

| Figure 4-5: Central-TB Digital Output Relay                                                     | 30 |

| Figure 4-6: IOB-Mk2 Watchdog                                                                    | 31 |

| Figure 4-7: IOB-Mk3 Transit Watchdog circuit                                                    | 32 |

| Figure 4-8: Stage 1 Analog Input IOB-Mk1 and Mk2                                                | 33 |

| Figure 4-9: Mk3-Transit AI stage 2                                                              | 34 |

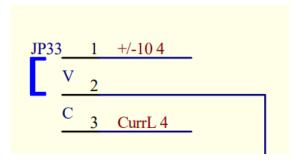

| Figure 4-10: Central TB Analog Output mode selection [16]                                       | 35 |

| Figure 4-11: IOB-Mk2 Analog Voltage Output Amp [10]                                             | 36 |

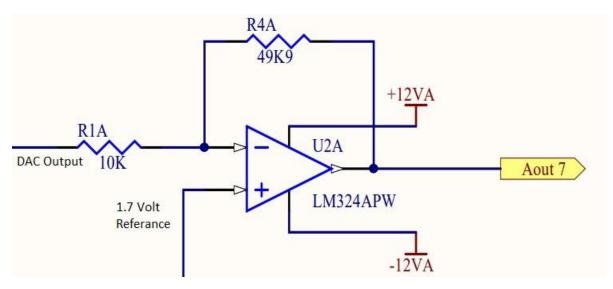

| Figure 4-12: IOB-Mk2 Analog Current Output [10]                                                 | 37 |

| Figure 4-13: IOB-Mk2 Broken Loop Shift Register [10]                                            | 39 |

| Figure 4-14: Isolated Analog I2C DAC input                                                      | 39 |

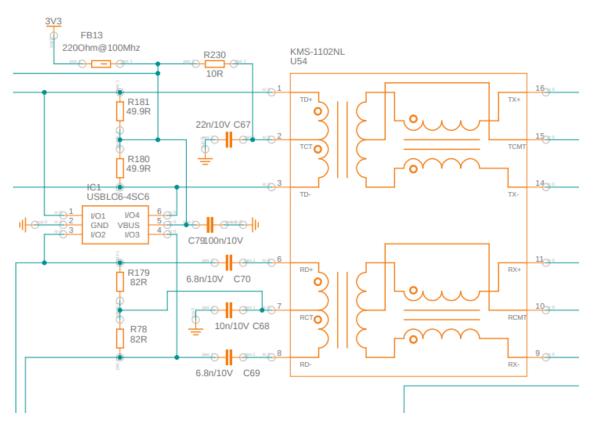

| Figure 4-15: SPI Ethernet Magnetics                                                             | 40 |

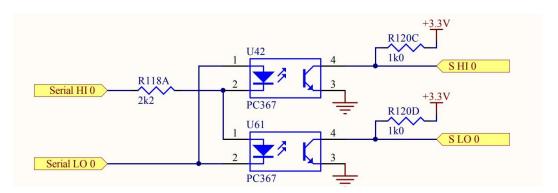

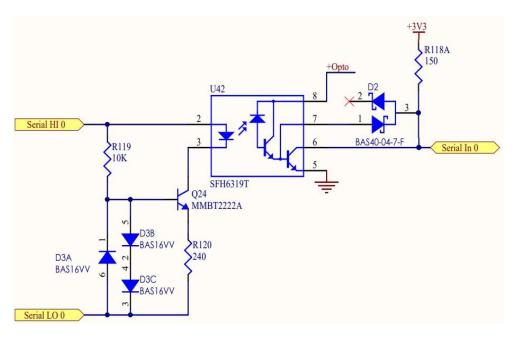

| Figure 4-16: IOB-Mk1 Serial Input [12]                                                          | 41 |

| Figure 4-17: IOB-Mk2 Serial Input [10]                                                          | 42 |

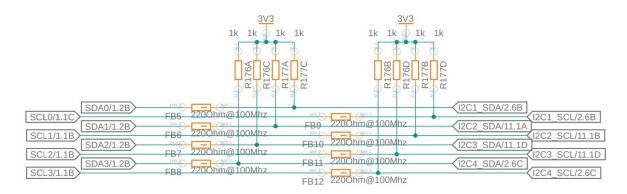

| Figure 4-18: Mk3 I2C Implementation                                                             | 43 |

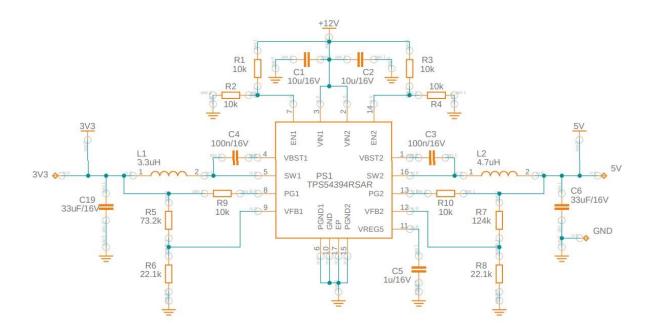

| Figure 4-19: Mk3-Transit 3.3V and 5V regulator                                                  | 44 |

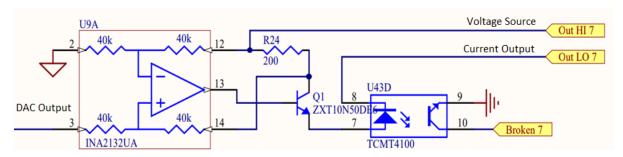

| Figure 4-20: Analog Power Filtering                                                             | 45 |

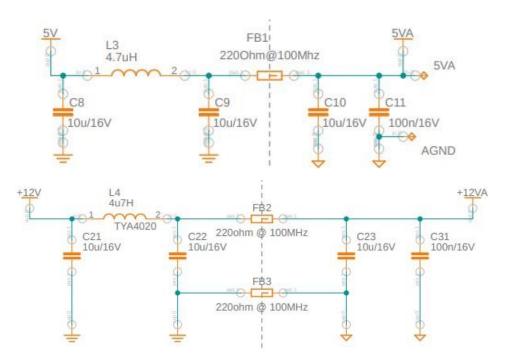

| Figure 4-21: Negative 12V Converter Layout [18]                                                 | 45 |

| Figure 5-1: MT IO Test tool                                                                     |    |

| Figure 5-2: Certification EMC Margin Requirement [19]                                           |    |

| Figure 5-3: Test Setup Conducted Emissions [19]                                                 |    |

| Figure 5-4: Test setup Radiated (30MHz-1000MHz) [19]                                            |    |

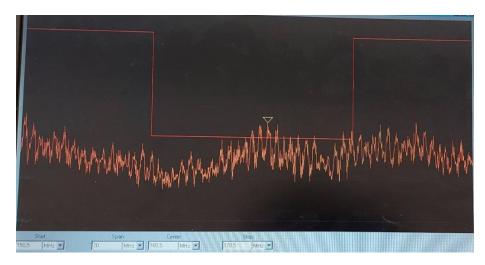

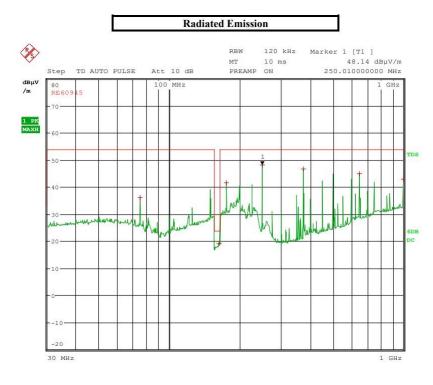

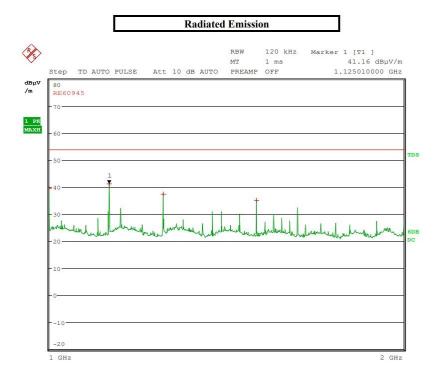

| Figure 5-5: Initial Radiated EMI test at West Control (156-165MHz)                              | 55 |

| Figure 5-6: Initial Radiated EMI test at West Control (30MHz-2GHz)                              | 55 |

| Figure 5-7: Initial Radiated EMI test at West Control (156-165MHz) with input ferrite           | 56 |

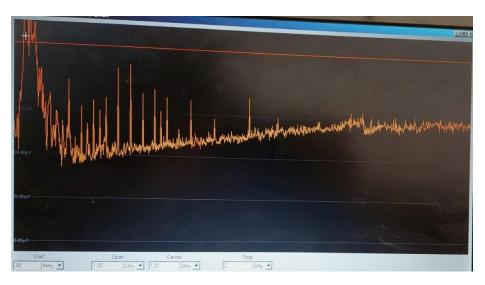

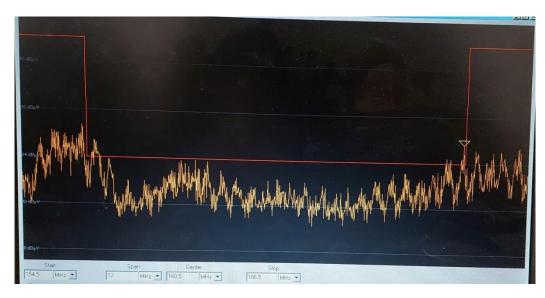

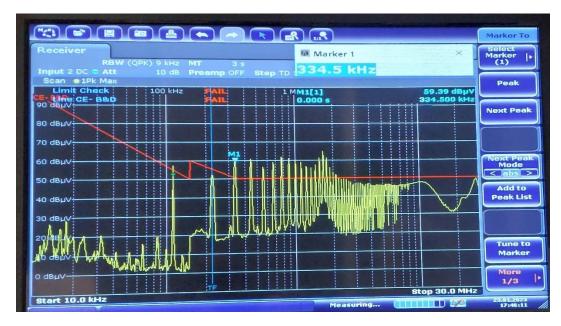

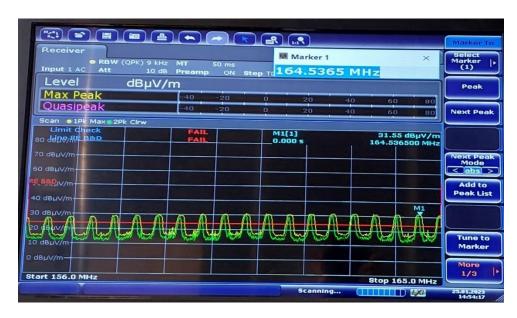

| Figure 5-8: Conducted Emissions Failure (10KHz-30MHz)                                           |    |

| Figure 5-9: Radiated Emissions Failure (156MHz-165MHz)                                          |    |

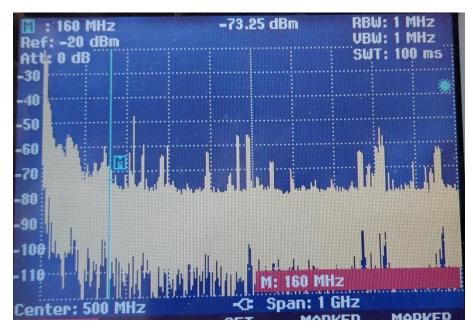

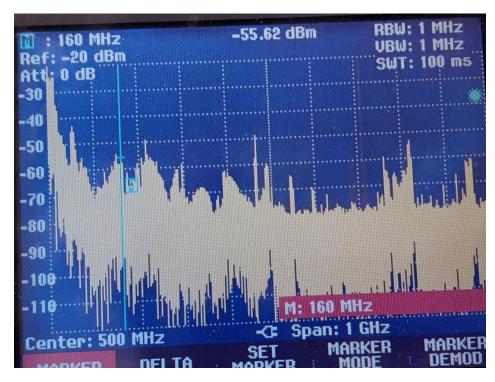

| Figure 5-10: Background Measurement                                                             | 58 |

| Figure 5-11: No Change Measurement                                                              | 59 |

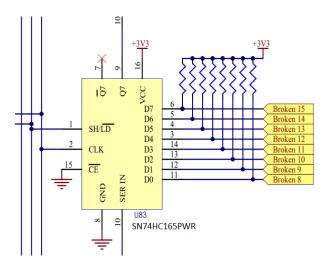

| Figure 5-12: 6.8mH Choke PI Filter with New DCDC Power                                          | 59 |

| Figure 5-13: Passed Conducted (10KHz-30MHz) [19]                                                | 60 |

| Figure 5-14:Passed Radiated (150KHz-30MHz) [19]               | 61  |

|---------------------------------------------------------------|-----|

| Figure 5-15: Passed Radiated (156-165MHz) [19]                | 61  |

| Figure 5-16: Passed Radiated (30MHz-1GHz) [19]                | 62  |

| Figure 5-17: Passed Radiated (1GHz-2GHz) [19]                 | 62  |

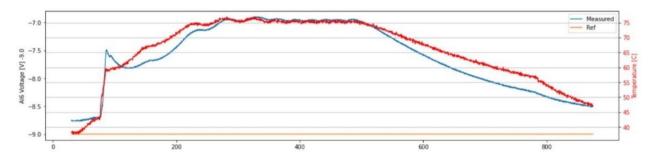

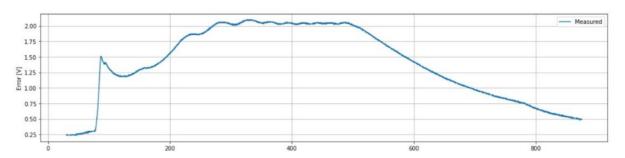

| Figure 5-18: Analog Input Temperature Test                    | 63  |

| Figure 5-19: Analog Input Test Voltage Error                  | 63  |

| Figure 5-20: ADC Input, Voltage Protection [20]               | 64  |

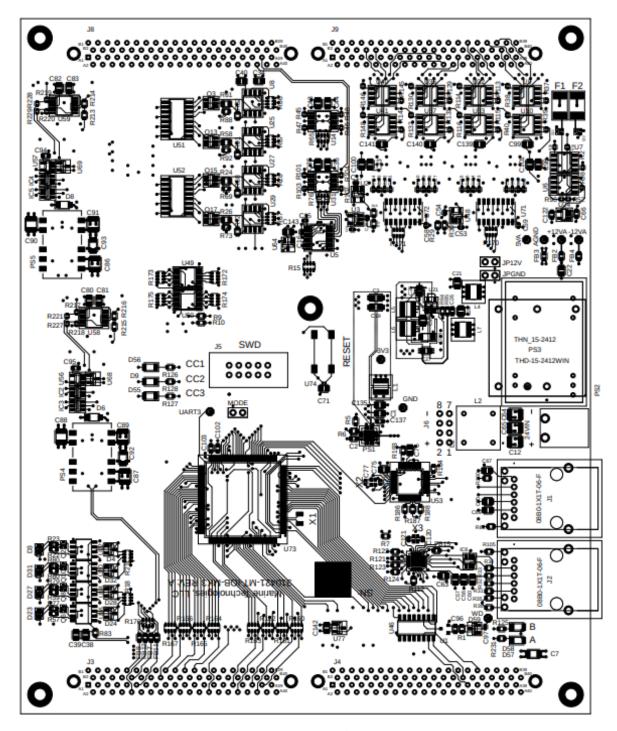

| Figure 6-1: IOB-Mk3                                           | 65  |

| Figure 6-2: IOB-Mk3 Watchdog Charge Pump [22]                 | 66  |

| Figure 6-3: IOB-Mk3 Layer 4 Power Polygons                    | 68  |

| Figure 0-1: Radiated Emissions Test Setup (150KHz-30MHz) [19] | 72  |

| Figure 0-2: Test Setup Radiated 1GHz and Above [19]           | 72  |

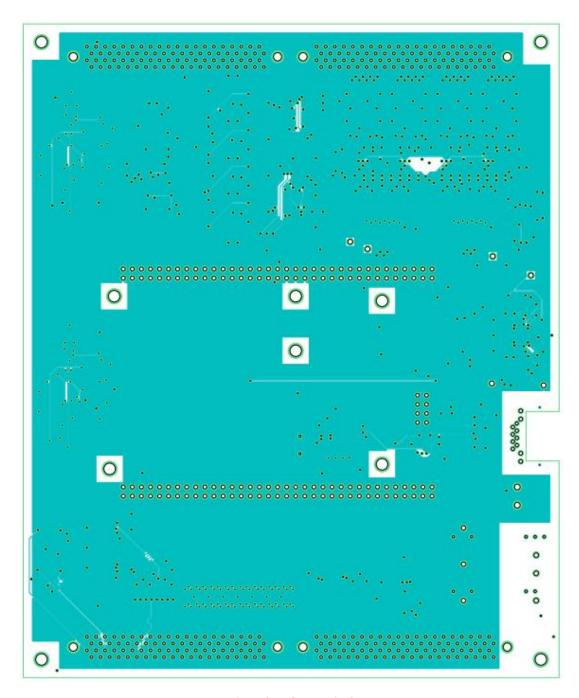

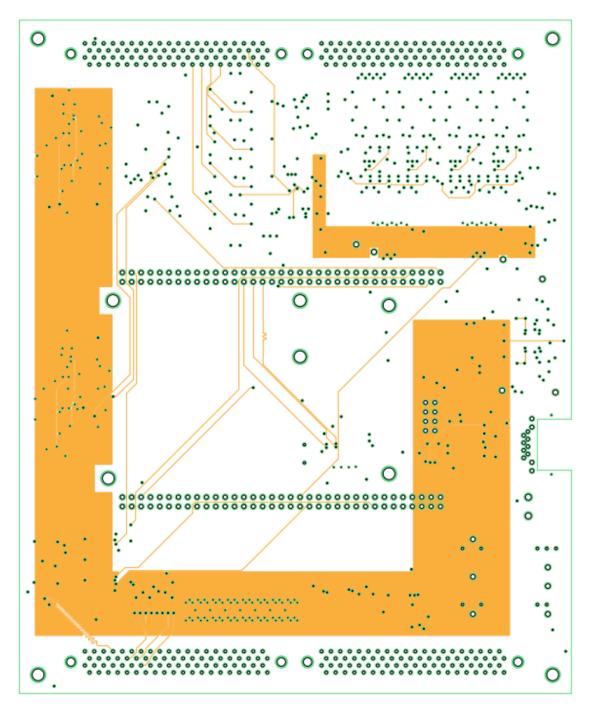

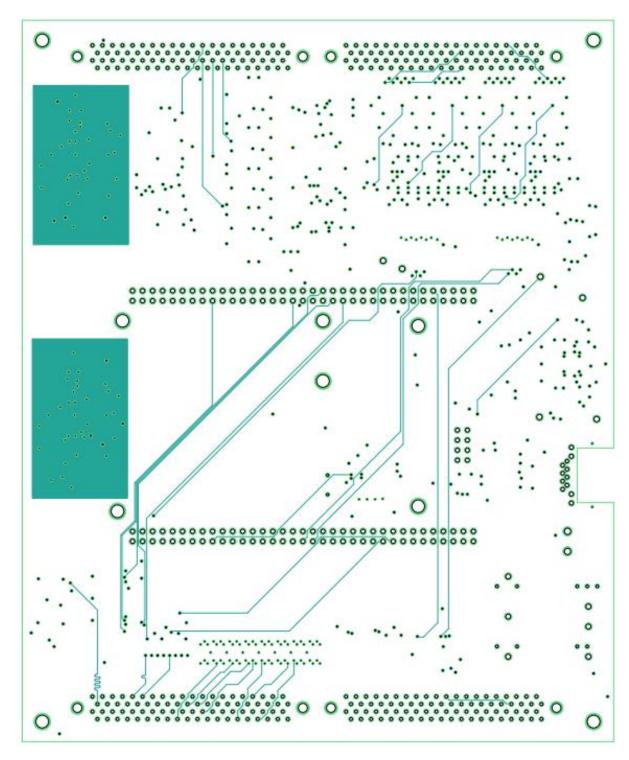

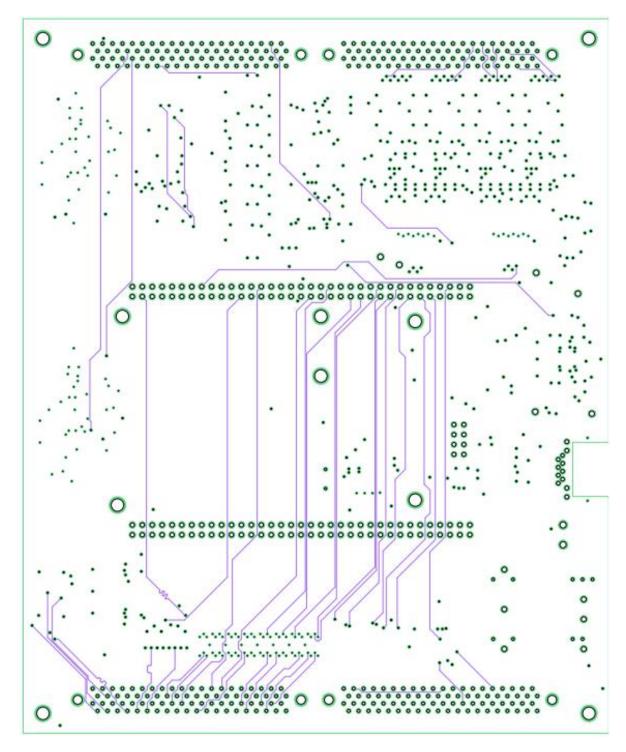

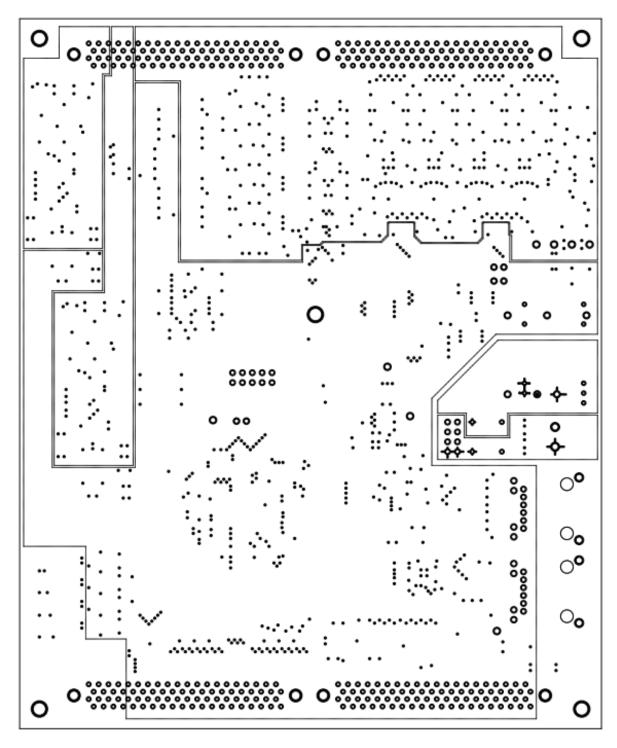

| Figure 0-3: IOB-Tranist L1                                    | 85  |

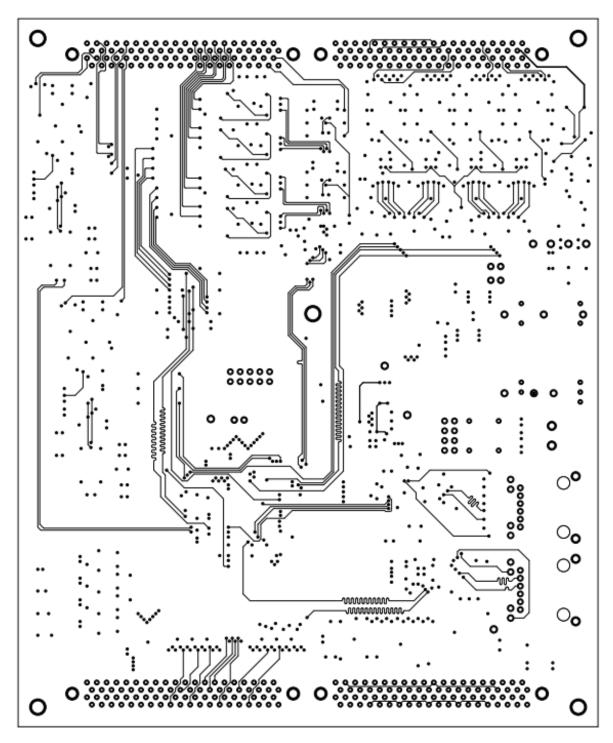

| Figure 0-4: IOB-Transit L2                                    | 86  |

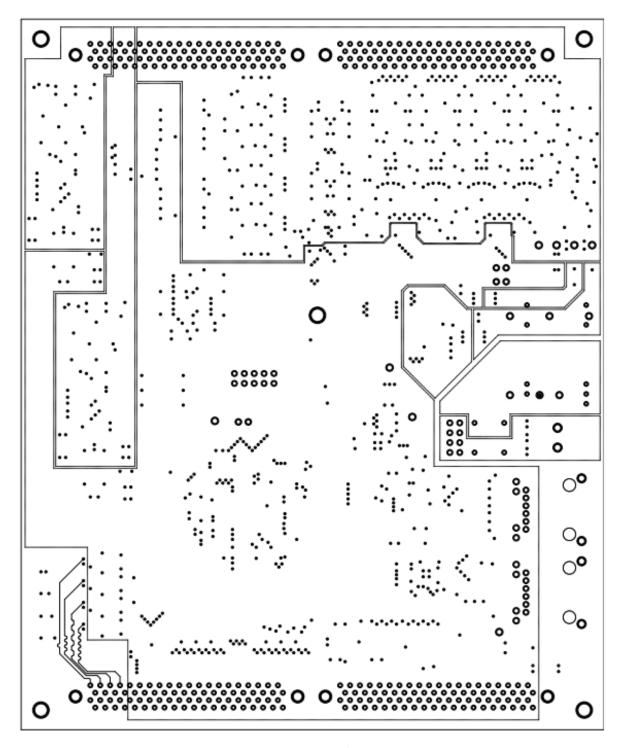

| Figure 0-5: IOB-Transit L3                                    | 87  |

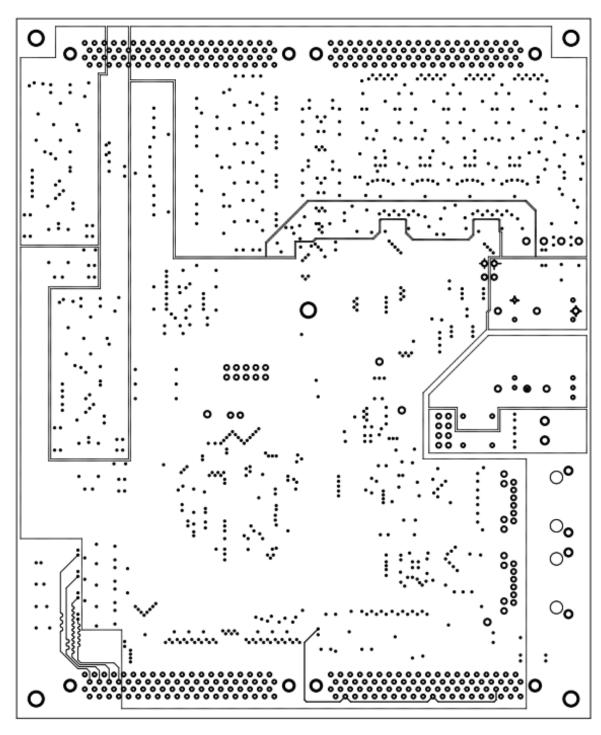

| Figure 0-6: IOB-Transit L4                                    | 88  |

| Figure 0-7: IOB-Transit L5                                    | 89  |

| Figure 0-8: IOB-Transit L6                                    | 90  |

| Figure 0-9: IOB-Transit L7                                    | 91  |

| Figure 0-10: IOB-Transit L8                                   | 92  |

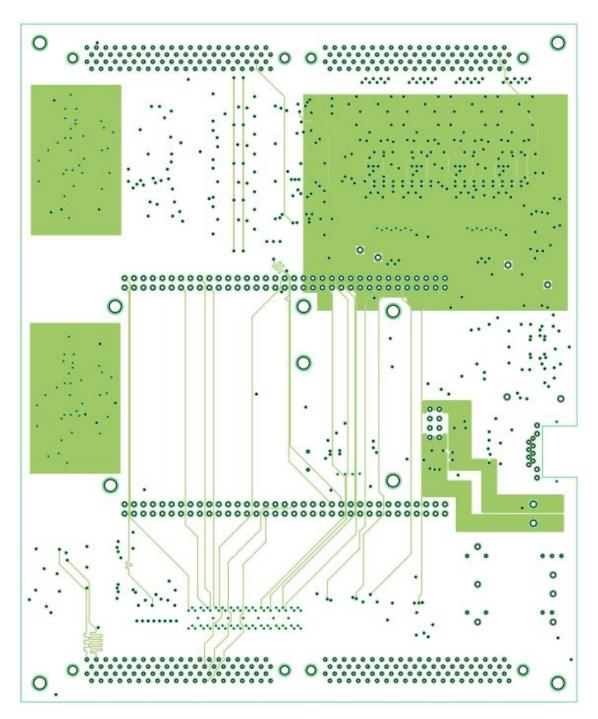

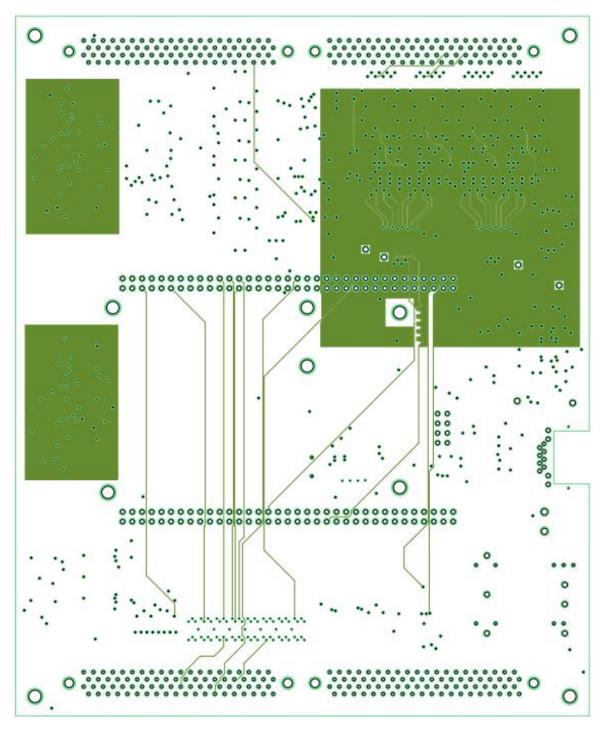

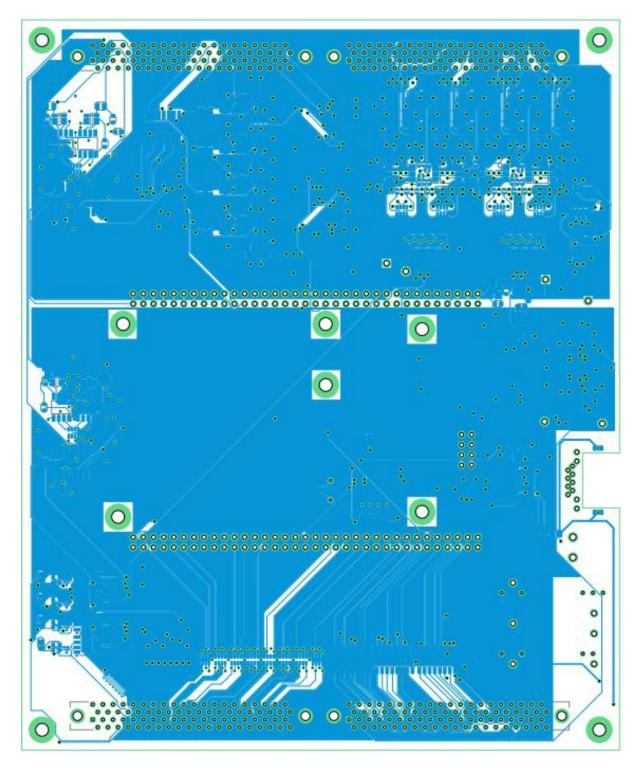

| Figure 0-11: IOB-Mk3 L1                                       | 93  |

| Figure 0-12: IOB-Mk3 L2                                       | 94  |

| Figure 0-13: IOB-Mk3 L3                                       | 95  |

| Figure 0-14: IOB-Mk3 L4                                       | 96  |

| Figure 0-15: IOB-Mk3 L5                                       | 97  |

| Figure 0-16: IOB-Mk3 L6                                       | 98  |

| Figure 0-17: IOB-Mk3 L7                                       | 99  |

| Figure 0-18: IOB-Mk3   8                                      | 100 |

# Tables

| Table 2-1: IOB-Mk2 Functionality Summary Table Table 2-1: IOB-Mk2 Functionality Summary Table | 19 |

|-----------------------------------------------------------------------------------------------|----|

| Table 2-2: Conducted Emissions IEC 60945                                                      | 20 |

| Table 2-3: Radiated Emissions IEC 60945                                                       | 20 |

| Table 2-4: Radiated Emissions DNV 0339                                                        | 20 |

| Table 3-1: PCB Layer Configuration Examples                                                   | 26 |

| Table 4-1: Nucleo Modification Table                                                          | 43 |

| Table 4-2: IOB-Mk3 Transit PCB Layer Stack Assignment                                         | 46 |

| Table 5-1: Testing and Verification Overview                                                  | 48 |

| Table 6-1: IOB-Mk3 Layer Structure                                                            | 67 |

# Terminology and Abbreviations

ADC (Analog to Digital Converter)

AI (Analog Input) AO (Analog Output)

CAN (Controller Area Network)

DAC (Digital to Analog Converter)

DI (Digital Input)

DNV (Det Norske Veritas)

DO (Digital Output)

DP (Dynamic Positioning)

ECDIS (Electronic Chart Display and Information System)

EMC (Electromagnetic Compatibility)EMI (Electromagnetic Interference)

EUT (Equipment Under Test) FAT (Factory Acceptance Test)

FPGA (Field Programmable Gate Arrays)

GPS (Global Positioning System)

IEC (International Electromechanical Commission)

IMO (International Maritime Organization)

IOB (I/O Board)

MCU (Micro Controller Unit)

MRU (Motion Reference Unit)

MT (Marine Technologies)

PCB (Printed Circuit Board)

PISO (Parallel In Serial Out)

RAM (Random Access Memory)

RBW (Resolution bandwidth)

RMII (Reduced Media-Independent Interface)

ROM (Read-Only Memory)

SMD (Surface Mounted Device)

SPI (Serial Peripheral Interface)

UART (Universal Asynchronous Receiver/Transmitter)

#### 1 Introduction

The offshore industry is a vast and advanced field, requiring a multitude of different technologies and areas of expertise to cover everything from transport to fishing, wind farming and oil and gas production. A crucial commonality between offshore industries are the ships in use. Advancements in ship construction, sailing and navigation have heavily influenced human progress throughout history. The motorization of shipping meant steady and consistent sailing that the unpredictable use of wind could not match. Timekeeping pieces like the H1 marine chronometer clock was a large step towards solving the longitude problem, meaning one step closer to an efficient method of mapping and positioning. And now highly advanced communications systems have given us GPS and ECDIS (Electronic Chart Display and Information system), allowing a vessel always to be aware of its position and the terrain below where it is sailing.

Figure 1-1: ASD Tug 5016 Vessel

The thesis is written in collaboration with Marine Technologies LLC (MT)<sup>1</sup>. Marine Technologies specializes in Dynamic Positioning (DP) systems for industrial class marine vessels. DP allows a vessel to use its multiple thrusters along with GPS data to anchor the ship and its orientation to a geographical point, counteracting the currents and winds at sea to keep the vessel still.

The basic working principle of a DP system could be split into two main parts, what the ship can see, and what the ship can do. First let us cover what can the ship see, which is what data is has. The vessel

-

<sup>&</sup>lt;sup>1</sup> https://www.marine-technologies.com/

has access to accurate GPS positioning, wind speed and direction data, sea current data and vessel orientation by using MRU's that have gyroscopes and accelerometers. The vessel now knows where is, it knows how it is oriented and the vessel knows what direction it is being pushed and how hard it is being pushed.

How does a vessel use this data? Vessels that use DP usually have multiple thrusters that can generate thrust in any direction. Using these thrusters, the vessel can directly oppose the forces of wind and current while maintaining its orientation and geographical position. However, to do this, computers must be used to calculate the vessels response based on the data it can see. With this data, the computers and the thrusters can maintain ship position with an accuracy within one meter.

Figure 1-2: MT DP1 System Overview

This process requires use of feedback systems and controllers, which means communication between the antennas, the DP computer, control computers, and the thruster control boards which are shown as IOB cabinets in Figure 1-2. Our focus in this thesis is one of MT's crucial components in this network,

the General purpose I/O Board (henceforth called IOB). The original IOB-Mk1 was designed and made operational in 2003, and IOB-Mk2 in 2014, and is one of the most important PCBs in the system. The IOB is mounted directly on the thruster board and is responsible for receiving and executing the thruster control commands. The Mk1 and Mk2 boards are designed with an FPGA solution creating Fly by Wire control over ethernet from lever to thruster.

At the time of writing, the world market has had to fight a shortage problem that started to take a foothold during and after the COVID-19 outbreak. This shortage has also affected IC's and other circuit board components and silicon-based chips. Together with the rising capability of standard microcontrollers means that it is of interest to implement them in an IOB redesign, moving away from the FPGA based solution that has been used for 20 years.

#### 1.1 I/O Board

The IOB is a general purpose I/O control and monitoring board. It is made to be general purpose so that it can be used for a wide array of devices internally for MT. The IOB is mainly used in thruster control cabinets to connect thruster command and monitoring to the ships network, but the IOB is also used for operating panels that comprise of buttons, joysticks, heading wheels and the like. The system overview in Figure 1-2 includes two examples of where the IOB is put to use.

Although the IOB is equipped with multiple communication functions, its main features are its inputs and outputs, its "I/Os". The IOB has two varieties of I/O, the first is analog I/O and secondly, digital I/O.

Imagine the analog inputs as your ear, as it can not only hear sounds, but also can hear how loud they are; this loudness is represented in the IOB as electrical voltage, which can go as loud as 10 volts. Now think of how your ear can deduce if a sound is in front of you or behind you; this is represented as positive voltage in front of you and as a negative voltage behind you. For us, the sound is often a signal from a ship's rudder, reporting its position, where zero volts is quietly in the middle position. Next, imagine your voice as an analog output that produces sound. This analog output can produce the same negative and positive 10 volts to for example control a rudders position.

For digital I/O, your eye and a light are a good example of a digital input, since you can perceive with your eye when the light is on or off. Just as your eye can tell if a light is on or off, a digital input can tell whether a signal is high or low. This signal is often used to tell us if a button is being pushed. As for digital outputs, this is simply like you turning a switch on or off, and that switch can be used to turn external systems such as pumps on or off.

Figure 1-3: Example of a IOB-Mk2 Board

Another circuit board that is essential to fully understand the IOB is the Central-TB (Thruster board). The IOB and Central-TB were designed in tandem with each other, and therefore they are best explained in company with each other.

For another board to make use of the IOB, it must have four sets of 80-pin board to board sockets. The IOB's matching pin headers can be seen on the boards four corners in Figure 1-3. The Central-TB board takes these pins from the board-to-board contacts and passes them on to wire termination blocks on the Central-TB so that technicians can wire I/O to the vessel.

Figure 1-4: Central-TB with an IOB-Mk1 card mounted

#### 1.2 Objective

Though Central-TB's design and manufacture is handled by Marine Technologies, the design of the IOB belongs to a separate company that Marine technologies purchases the IOB from. Marine Technologies needs the IOB to become fully proprietary and have therefore decided to design the next IOB iteration themselves. This thesis outlines the process of the IOB-Mk3 from concept to product, based on the requirements set by Marine Technologies LLC. This is a multi-step process that requires concept evaluation, in-house design review and approval, prototyping and external verification and certification.

The process starts with evaluation of the redesign concept and if it is at all manageable and worth taking the risk of putting in time and resources in development of the IOB-Mk3. The main aspect of this redesign was converting the previous FPGA-based design to a microcontroller-based design. Is essence this is a change from a hardware base processing unit to a device that runs on software code

to process I/O data. This is to our knowledge the first time a software-based unit will directly take on this task in this industry.

The starting objective is to evaluate if the switch from FPGA to a microcontroller could realistically be done. This means compiling all the previous IOB functionality and mapping them to the microcontrollers pin functions and checking for pin availability on the microcontroller, as well as evaluating speed, memory, and reliability.

Next objective is to review peripheral circuitry and its compatibility to the MCU, reworking them to be compatible and updating components that could approach the end of their lifecycle.

After the analyzation portion of the assignment, actual design of a prototype will take place by use of CAD software to create circuit diagrams, a board layout in GERBER format and a specified Bill of Materials (BOM). Circuit diagrams must be made orderly so it can be easily reviewed and understood by others in the future.

Crucially, at the time of writing, the world is still in a state of material and goods shortage. This is especially felt in the electrical component and IC market. Therefore, component sourcing, and choosing easily replaceable components is important in the design phase. Of course, all this is influenced by availability.

With the design finalized, prototype boards will be manufactured so we can perform in-house testing. It is necessary to test and verify all areas of the board to find any faults that exist in the IOB design due to either the circuit diagram or board layout. Discovered faults must be corrected and accounted for in the next iteration of boards until we can satisfy the function requirements.

Finally, after function has been verified, a series of tests performed by a 3<sup>rd</sup> party authorized laboratory will have to be conducted to receive a lab report, detailing that the board meets all requirements for a device to be used in offshore vessels. The main obstacle and our focus will be on the Electromagnetic Compatibility (EMC) portion of the tests. These tests are often the first to be issued because they are the tests that often fail due to the strict but necessary demands; thus, it is crucial that EMC is heavily considered in the design phase.

#### 1.3 Outline of Thesis

This thesis describes a design that is highly internal to the company and a large portion of the work material are internal documents, schematics and lists that are not publicly available. This implies that there is a distinct lack of external citations and references when addressing Marine Technologies systems related material. Since this is mostly the basis of my work, this results in fewer external references than one might expect in a thesis in total. Internal documents will however be cited and referenced despite not being publicly available.

#### Chapter 2 Requirements of the New IOB Design

This chapter gives the specific requirements for the redesigning of the IOB. The requirements are divided into two parts. First are the requirements as stated by Marine Technologies, which specifies

the required functionality of the IOB product. Thereafter, focusing on internationally set requirements for devices used in maritime applications. This set of requirements pertains to the sturdiness and compatibility of the device, of which I focus on the EMC tests.

#### **Chapter 3 Predesign Considerations**

In this chapter I discuss why the FPGA was the correct solution in the first version of the IOB board from 2002/2003 and why Marine Technologies decided to move forward with the redesign project replacing the FPGA with a microcontroller. Then looking at some of the predesign planning that took place to best prepare myself for the design. I also discuss guidelines for Electromagnetic Compatibility (EMC) minded design, as well as PCB layout and PCB stack principles.

#### Chapter 4 Design

The different aspects of the design are discussed here. The aspects being component selection, circuit design and schematics. The main principle of the design is a proof-of-concept approach to the IOB-Mk3 where a development kit board is used, combined with a peripheral board to complete the IOB-Mk3-Transit. I mainly compare the previous circuit solutions and consider how to implement them for the new board.

#### Chapter 5 Test and Verification

This chapter covers the process and findings of the in-house testing process of the IOB-Mk3-Transit board. Here, the tests performed are described, together with the results of these tests. The faults uncovered and their solutions are also presented.

After that, I cover the process of board Certification, mostly looking at EMC testing. I show the results of the successful certification by presenting some EMI graphs of the IOB.

#### Chapter 6 Integrated Design Phase

This chapter describes the phase where the microcontroller is integrated with the PCB to make a single unit, as well as making general improvements to the design. I look at the process of testing the first version of the IOB and use what was learned to make the integrated board version design.

#### Chapter 7 Discussion and Conclusion

This chapter concludes the thesis. It discusses the state of the current product at the time of writing, and then considers future work and potential improvements and looks at the lessons learned.

# 2 The Requirements of the New IOB Design

The redesigned IOB has two primary areas of requirements. The first set is required by IEC (International Electrotechnical Commission) and IMO (International Maritime Organization) and are verified and controlled by DNV (Det Norske Veritas)<sup>2</sup>. The other set of requirements is provided by MT itself.

For anything to be mounted and used onboard a marine vessel, said equipment must comply with a set of rules and requirements that are in place to insure uptime, performance, compatibility and most importantly, crew safety.

For the updated version of the IOB to be successful, these requirements must be met, along with the additional requirements from Marine Technologies itself. This IOB must be function identical to the previous versions of the IOB. To the point where retrofitting previous vessel installations with this new board must be seamless. Marine Technologies must be able to use the redesign as a drop-in replacement for the previous IOB in any given installation.

#### 2.1 Marine Technologies Requirements

As the MT set of requirements are centered on previous IOBs, this chapter will cover what those functions are. Since there are two iterations of the IOB, it is useful to look at the commonalities between them, as that will be an accurate method to examine the required specifications. This set of requirements is mainly based on the IOB-Mk2, but is partially dependent on the Mk1 as well, for example when Mk1's solutions performed more favorably in long term tests and use in the field.

In addition, multiple updates to this set of requirements are done during the project because of information acquired and lessons learned. This section presents the requirements in their final iteration.

#### 2.1.1 IOB-Mk1 and Mk2 Description

The IOB series of circuit boards are Input/Output boards that are made for general purpose use within the Marine Technologies system framework. The IOB must be mounted onto a circuit board made to interface with a specific piece of equipment. The receiving circuit board must be designed to be compatible with the four Board-to-board connectors of 80 pins each and their pinout. When the IOB is mounted, that piece of equipment becomes connected to a network that can command and monitor its I/Os.

#### 2.1.2 Functional Overview

Figure 2-1 displays a block diagram with the required functions to be present on the IOB-Mk3. All the functions are peripherals that are required to be connected to the MCU apart from the +-10V reference that is mainly used to bias joystick potentiometers. All these peripherals need to connect

<sup>&</sup>lt;sup>2</sup> DNV – Det Norske Veritas are the world's leading classification society and a recognized advisor for the maritime industry. <a href="https://www.dnv.com/">https://www.dnv.com/</a>

to the MCU because the MCU's main task is to pack all the data into an ethernet package structure and forward it to the network and the control computers.

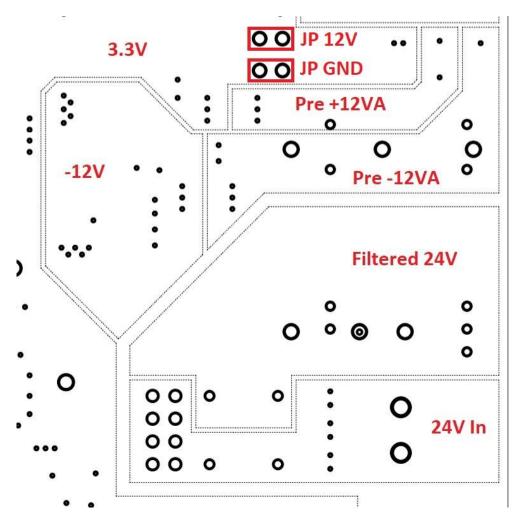

There is also a physical form factor requirement regarding mechanical mounting and electrical connection. The dimensions of the board and the placement of the M3 screw holes must be identical to Mk1 and Mk2. The electric connectivity points that have been present in earlier versions must also be present in the updated version. Of these, there are five pin headers that require identical placement to the previous versions. Four of them are the 80-pin board-to-board connectors that are responsible for breaking out the IOB's functionality, and the last is J6, the 24VDC input power connector. The rest of the electrical connection points should be placed as identical to the previous versions as possible.

Figure 2-1: Sketch given the functional requirements of the IOB in terms of functional entities.

Table 2-1 shows the peripheral functionality available on the Mk2 IOB and some notes on each function. Comparing the block diagram in Figure 2-1 with this table, notice the I/O reduction in some of the functions, like analog inputs for example. The requirement reduction stems from an overestimation in previous specification that has not been necessary to correct until recently. However, the reduction in the amount of I/O in each function greatly eases the requirement and makes it easier to accomplish.

The IOB's actual I/O requirement has been thoroughly observed by the example of use over 20 years, those observations can be used to cut down the requirement of the IOB-Mk3 to its actual requirement.

Table 2-1: IOB-Mk2 Functionality Summary Table

| Interface               | Amount | Notes                                    |

|-------------------------|--------|------------------------------------------|

| I2C Buses               | 4      | Standard I2C                             |

| Digital Inputs          | 32     | Triggered by grounding the input         |

| Digital Outputs         | 34     | Darlington Collector type pulldown       |

|                         |        | output                                   |

| Analog Inputs           | 32     | Can read either +-10V mode or 4mA to     |

|                         |        | 20mA mode. (External shunt resistor      |

|                         |        | required for current mode)               |

| Analog Outputs          | 16     | +-10V out and 4mA to 20mA                |

| Isolated Analog Outputs | 4      | +-10V out and 4mA to 20mA                |

| +10V Reference          | 1      | 100mA polyfuse (Resettable fuse)         |

| -10V Reference          | 1      | 100mA polyfuse (Resettable fuse)         |

| RS-422 RX Inputs        | 8      | Convert differential RX input to single  |

|                         |        | wire UART RX signal                      |

| IP Address Inputs       | 8      | Digital inputs reserved to determine the |

|                         |        | IOB's IP address                         |

| Ethernet Interface      | 2      | Network A and B both present for         |

|                         |        | redundancy                               |

I/O reduction was done by looking at every single circuit board that the IOB is paired with, and taking note over what pins from the IOB that the product board has available for use. To clarify "available for use", I mean no actual wires are connected to that specific I/O, hence that I/O is not electrically supported by that product board.

A table that lists the IOB connector pinout and what functions are electrically supported by the product boards, and hence what functions can be omitted, can be found in the appendix.

It is important to keep any function that is used, even if a function is only used with one product board, since the Mk3 is required to be a drop-in replacement for the Mk1 and Mk2, both in older and newer installations.

#### 2.2 International Requirements

The international requirements can be divided into two parts in this project, the most difficult requirement to fulfill tends to be the EMC portion, as it is easy to underestimate its strictness. The second part is environmental testing, which demands that the device function and integrity is maintained across many circumstances and stresses that the device can experience in the field. This section gives a summary of these requirements<sup>3</sup>.

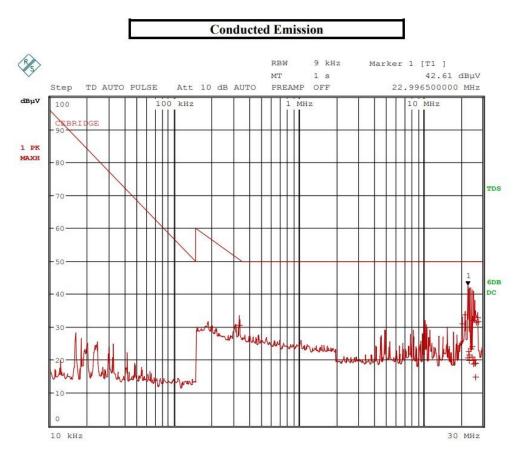

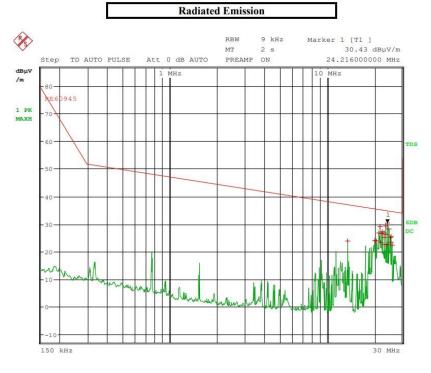

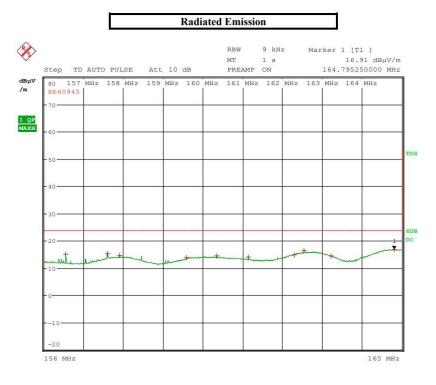

The usual major obstacle of the certification process, hence a major focus in this thesis, is to make the product conform with the EMC requirements stated in IEC-60945. See Table 2-2, Table 2-3 and Table 2-4 for the requirements. The EMC requirements are made up of two parts, conducted emissions and

19

<sup>&</sup>lt;sup>3</sup> The documents that the requirements are based on are not available free of charge.

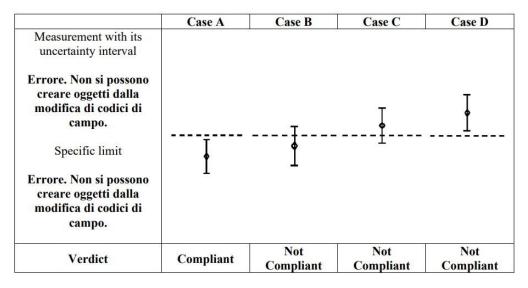

radiated emissions. These two parts focus on different frequency areas and have different emission limit requirements. Keep in mind that to meet the requirements, the equipment under test must beat the requirement listed, along with a margin equal to the third-party laboratory's measurement error margins worst case scenario. Also observe that in the radiated emissions requirement, there is an exception range at 156MHz to 165MHz. This is the emergency frequency band, in which the requirements are ever stricter to ensure proper communication in times of distress.

Table 2-2: Conducted Emissions IEC 60945

| Frequency Range | Emission Limit    |

|-----------------|-------------------|

| 10kHz – 150kHz  | 96 dBμV – 50 dBμV |

| 150kHz – 350kHz | 60 dBμV – 50 dBμV |

| 350kHz – 30MHz  | 50 dBμV           |

Table 2-3: Radiated Emissions IEC 60945

| Frequency Range                   | Emission limit                           |

|-----------------------------------|------------------------------------------|

| 30MHz – 2GHz                      | 54 dBμV/m                                |

| 156MHz – 165MHz (Exception range) | 24 dBμV/m peak (Or 30 dBμV/m Quasi peak) |

Table 2-4: Radiated Emissions DNV 0339

| Frequency Range                   | Emission Limit                           |

|-----------------------------------|------------------------------------------|

| 150kHz – 300kHz                   | 80 dBμV/m – 52 dBμV/m                    |

| 300kHz – 30MHz                    | 52 dBμV/m – 34 dBμV/m                    |

| 30MHz – 1GHz                      | 54 dBμV/m                                |

| 1GHz – 6GHz                       | 54 dBμV/m                                |

| 156MHz – 165MHz (Exception range) | 24 dBμV/m peak (or 30 dBμV/m Quasi Peak) |

The challenge with EMC requirements is that it is difficult to know how your prototype performs prior to executing the tests in a designated lab facility; EMC lab facilities of good quality are hard to come by as well. There is a high probability that EMC issues will be uncovered while attempting to get the device certified. However, the designers should try to follow typical EMC friendly design guidelines to minimize EMI as much as possible. Those guidelines will be explored in section 3.3.

As for the environmental requirements, these include being able to withstand situations such as high voltage ESD to buttons that one can expect personnel to touch, temperature variation, mechanical vibration, power supply spike and power supply voltage drops.

Arguably the issue of functional redundancy is also a requirement, but this is already considered by matching the functions given by the previous iterations of the IOB. The only real instance of function redundancy present on the board are the two ethernet interfaces (NET A and NET B), making the board network redundant. These interfaces have the same functionality, but in case the active network interface loses connection for some reason, the other interface will be used instead.

## 3 Predesign Considerations

With the stated requirements in mind, there are further considerations to make. Typically, the design process starts with understanding the requirements, considering them and their implications, planning possible solutions and then starting the design. However, anyone in this position quickly learns that with a complex system, this approach is an oversimplification.

One cannot completely understand the requirements and foresee potential adaptations of the requirements beforehand. Additionally, one cannot plan for every case and complication before shaping the design. This chapter will however present the initial planning that is crucial for being able to proceed to the design phase.

#### 3.1 FPGA and Microcontroller in the IOB

The first and major consideration, the one that the whole project leans on, is the microcontroller. The main feature and major difference from previous iterations is the fact that Marine Technologies has been using IOBs with FPGAs as their processor for 20 years. That is 20 years of field testing on actual in use vessels, and 20 years of finetuning the firmware and circuitry. It is truly a big risk to change something that has worked reliably for that large amount of time.

The main reason for the redesign of the IOB is that the IOB is not proprietary to Marine Technologies. Instead, they are bought from another company that designs and manufactures them. Since the IOB is a very important product, it is of great long-term value for Marine Technologies to own the design themselves. Thus, redesigning and making the IOB proprietary has been a goal for some time. However, the worldwide component shortage following the 2020 global pandemic pushed the issue forward. As the FPGAs as well as other components used for the previous iterations of the IOB were no longer available anywhere, the question arose if the functionality of the IOB could be implemented by a microcontroller instead.

Using FPGAs for the IOB in 2002/2003 made sense since the flexibility, stability and I/O capacity of an FPGA far outmatched that of any microcontrollers at the time. In the early 2000s, reprogrammable flash MCUs that matched the price of One Time Programmable MCUs had barely hit the market [1], and they had very limited memory capacity and pin availability. In short, microcontroller technology and capability were just not mature enough to handle the I/O load needed for the IOB, therefore the processor chosen for the first IOB was the "Xilinx Spartan XC2S600E" FPGA [2].

Now, choosing a microcontroller in the redesign is not unthinkable, since the MCU capability has in many ways been improved to the point that they can cover the processing requirement of the IOB at a significantly lower cost. The availability is better, and writing code for the MCU is something Marine Technologies already has in-house competence to perform. FPGA technology is still more capable and powerful, but the microcontroller suits IOB's needs sufficiently at a considerably lower price point.

The proposed Microcontroller is the "STM32H743ZIT6" [3]. This microcontroller comes in a 144-pin package with sufficient general-purpose I/O, memory, and on-chip functionality such as I2C buses, SPI lines, UART channels and RMII support. All these capabilities are necessary for the chip to be useful to the IOB-MK3.

#### 3.2 Microcontroller Considerations

The microcontroller is a flexible piece of hardware that is essentially a microprocessor equipped with peripherals, such as RAM and ROM memory, timers, input/output ports (I/O) and often communication hardware such as I2C, SPI, CAN, UART. This combination of hardware makes a computer that is programmable to interface with many types of sensors and devices. The microcontroller can gather data from sensors, store the data, report information through a network connection, and use its own I/O to act upon gathered information as decided by the custom program running on it. It is a small chip with the capability to control local peripheral electronics according to custom specifications.

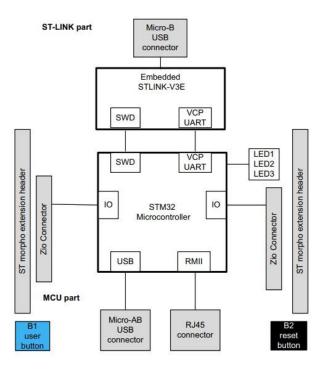

One important decision made was to utilize the ST Microelectronics Development board for the prototyping. Shown in Figure 3-1 is the demo board called "Nucleo-H743ZI2" and its circuit board reference is "MB1364" [4]. On this demo board, the microcontroller chip "STM32H743ZIT6" is mounted and it's I/O is made available on two connectors (CN11 and CN12). Rather than mounting the microcontroller directly onto the prototype board and testing the whole system, the development board itself would be mounted on a prototype PCB containing all the peripheral electronics needed to complete the IOB. In this way, the design is split into two stages, where the design and functionality of the peripherals could be tested with the certainty that any potential fault is not due to the MCU and its supporting electronics. The other significant advantage, especially considering the component shortage, is that one MCU can be used on multiple prototype boards to test different fixes and tweaks that are done in the testing phase.

Figure 3-1: Nucleo MB1364

#### 3.2.1 Pin Function Planning

The development team at Marine Technologies determined that the chosen STM32 has enough processing power, speed, memory, and available functions. However, there is a crucial difference between microcontrollers and FPGAs that complicates the task. In an FPGA there is freedom to configure what type of functionality a pin should have; mostly any pin can be used to implement functionality such as SPI, UART or I2C. In an FPGA based design one can simply configure the functions that you require a pin to have and assign that function to a pin that you deem appropriate, providing a large degree of flexibility.

A microcontroller on the other hand, hardwires certain functions to designated pins by design and this cannot be changed later by a user. To offer some flexibility to the designers, the MCU has several instances of the same peripheral connected to different pins, as well as multiple peripherals multiplexed onto the same pins. The latter implies that all peripherals offered by the MCU architecture cannot be used simultaneously. In other words, by selecting a set of pins for a specific interface, you are actively removing the use of the available peripherals from the MCU, and selecting pins becomes somewhat of a game of "microcontroller solitaire".

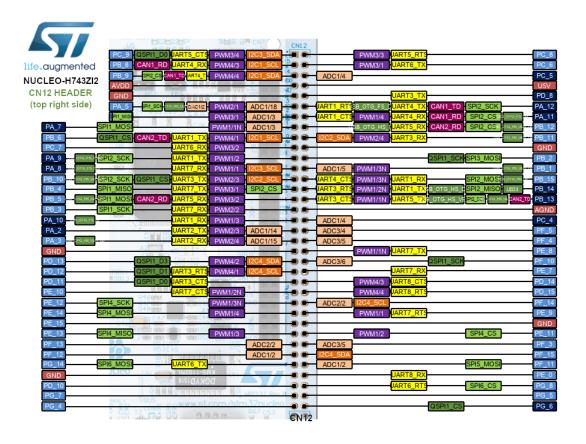

Figure 3-2: Nucleo Demo Board CN12 [5]

See Figure 3-2 for a visualization of the Nucleo connectors CN11 and CN12 and how the pin functions are overlayed. The first step in planning how to assign pins is to find out what pin functions must be present; defining the bare minimum function requirement and how many pins we can reduce our use to. Once the necessary pin types have been defined, the game of solitaire begins, using the map of pins from the figure and the microcontrollers datasheet.

Analyzing Marine Technologies hardware environment, I realized that there is an excess amount of I/O present in the IOB. MT hardware does not have physical wire connections to half of its analog input and output, as well as a few digital I/Os. This resulted in being able to reduce the requirement substantially by removing three SPI buses entirely. Additionally, some of the analog inputs (AI 27, 28, 29) were only used in one instance on a specific piece of hardware where they were the only AI present, thus they could also be redirected to be the same as AIs 13, 14 and 15.

The completed pin assignment of CN11 and CN12 can be found in the appendix along with the chart that shows I/O usage and simplification.

#### 3.3 EMC Minded Design

Taking EMC into account when making PCBs can be confusing. More often circuits will involve some sort of high frequency that will be able to radiate and cause disturbance. Every long cable attached can act as an antenna, every switching power supply in the circuit can result in radiated and conducted emissions and every high-speed data line requires careful EMC design considerations. Conducted emissions is noise that travels from the device and into the power grid that the device is connected to; this of course can affect other devices on the power network and is therefore important to regulate [6]. Radiated emissions are propagated as EMI through the air and can affect the function of instruments, communication, and devices in proximity to the radiating device and is therefore important that it is regulated.

#### 3.3.1 The Path of Least Inductance

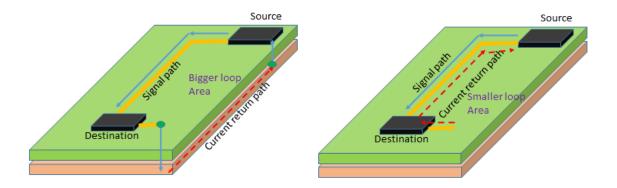

The main effect that will shape the design is the awareness of the behavior of electrical current when it is of a higher frequency. Frequencies emitted from devices start to be measured at 10kHz conducted and 150kHz radiated. It is often taught that electrical current will always seek to travel the path of the least resistance, which is somewhat true, but that's not the whole picture. Current will seek and travel the path of least impedance. Impedance equals resistance for low frequencies, but for higher frequencies, inductance comes into play as well. As a rule of thumb, the path of least inductance lies directly under the signal trace [7].

In Figure 3-3 you can see the difference between a low and high frequency return path. The image depicts a signal going between two components on the top routing path, with a solid and continuous ground plane beneath them.

Figure 3-3: Current return path visualization of a high frequency signal [8]

In the image to the left, the current return path follows the shortest, most direct path because of its low resistivity, which is indicative of its low frequency behavior. The key is to notice the loop that it creates and that all current exist as loops as per Kirchhoff's Current law. The area inside of any given current loop is important because it forms an antenna.

In a DC (Direct Current) environment this is not an issue since there are no frequencies to radiate, until noise is introduced to the loop or if the signal is a varying signal. The frequencies of the noise or signal that is tuned to the current-loop will use that loop as an antenna, because it is one, and it will radiate. Frequencies with a quarter of their wavelength matching the loop antennas length, will be able to make use of the antenna.

Figure 3-4: Circular Loop Antenna

However, following good design practices as the frequency increases, the path of least impedance will be determined by inductance rather than resistance, and the current's return path will seek itself directly under the signals outgoing trace wire.

This naturally closes the loop and restrains the loop antenna's ability to radiate. This is shown in the right side of Figure 3-3. In poorer designs, if the return path is restrained from directing itself under the trace wire, in which case the loop area and shape is maintained, and the antenna has access to higher frequencies to radiate.

#### 3.3.2 Layer Structure and Polygons

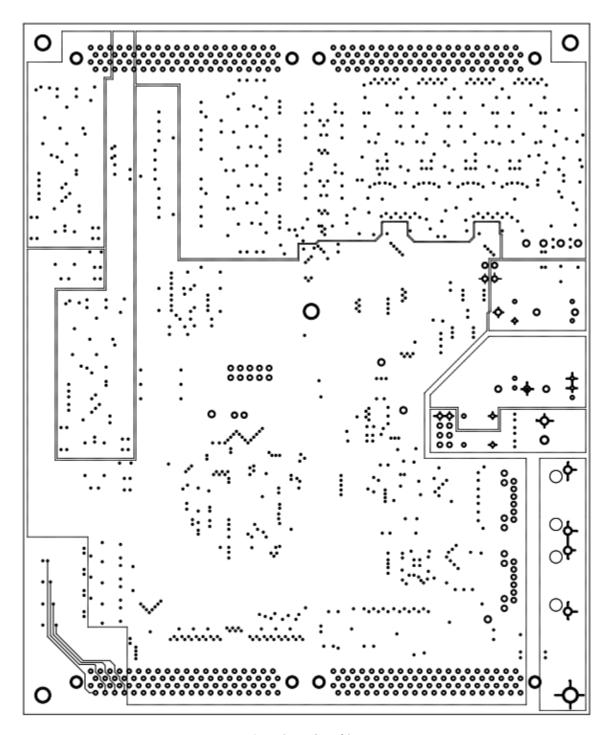

Having established that the best practice to reduce radiated EMI is to allow the current return path to have a way to follow directly under the outgoing trace. The best way to do this is by having dedicated power and ground planes and polygons for the current flow to use freely. In PCB design, copper pours are used to fill copper into polygon shapes defined in the design, which is very practical for designating zones of operation, such as separating the digital zone from the analog zone.

In a PCB stack up there are multiple possibilities to how you organize your layers. It is common to break the layers into three main categories; these are the grounding layer, the power layer and finally the signal layer. The fourth category, when relevant, is the high-speed signal layer. In this instance, I chose to work in 8 layers to afford myself some flexibility in routing and I chose to mount SMD (Surface Mounded Device) components on both sides of the PCB. With this configuration, the usual way to proceed with 8 layers is to delegate four of them to signal traces, two of them to power distribution and the remaining to for ground reference.

The next step is to order these layers in the stack up; and which configuration to choose is based on application and preference, but let's look at two examples [9].

Configuration Shielding **Power Coupling** SMD pads and Ground Layer 1 Signal 1 Layer 2 Signal 1 Ground Layer 3 Power Signal 2 Layer 4 Signal 2 Power Layer 5 Signal 3 Ground Layer 6 Power Signal 3 Layer 7 Signal 4 Ground Layer 8 SMD pads and Ground Signal 4

Table 3-1: PCB Layer Configuration Examples

The shielding configuration example in Table 3-1 presents a stack up order that prioritizes shielding the signals. However, one must be careful while routing, however tempting, to not utilize the top and bottom layer for routing, since this breaks the continuity of the ground plane and can then force returning current to take a non-optimal path.

In the power coupling configuration, the power and ground planes of layers 4 and 5 are close together, allowing for good signal integrity. Also, the ground planes are more intact due to not hosting all the SMD pads on the top and bottom layer.

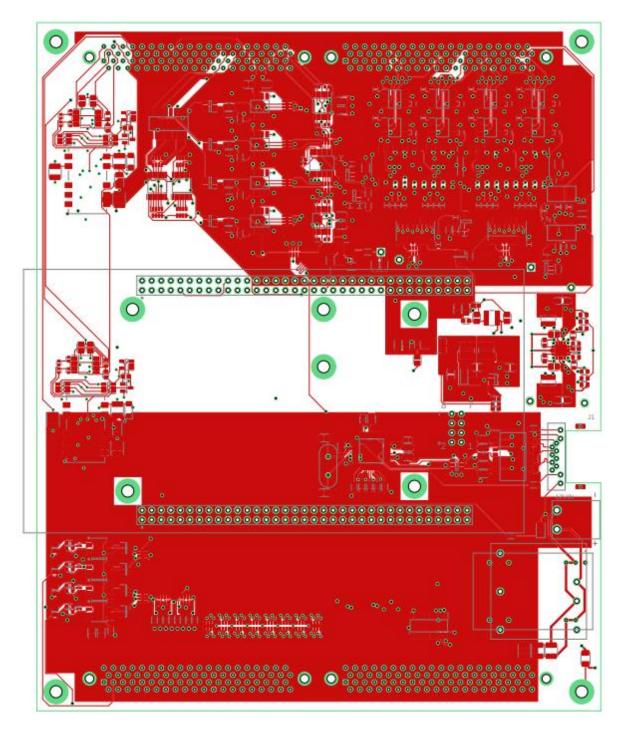

## 4 Design

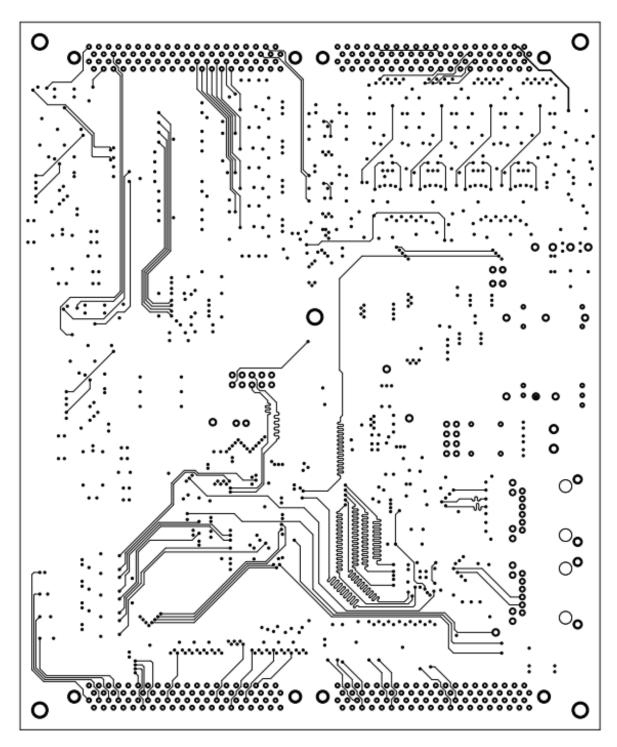

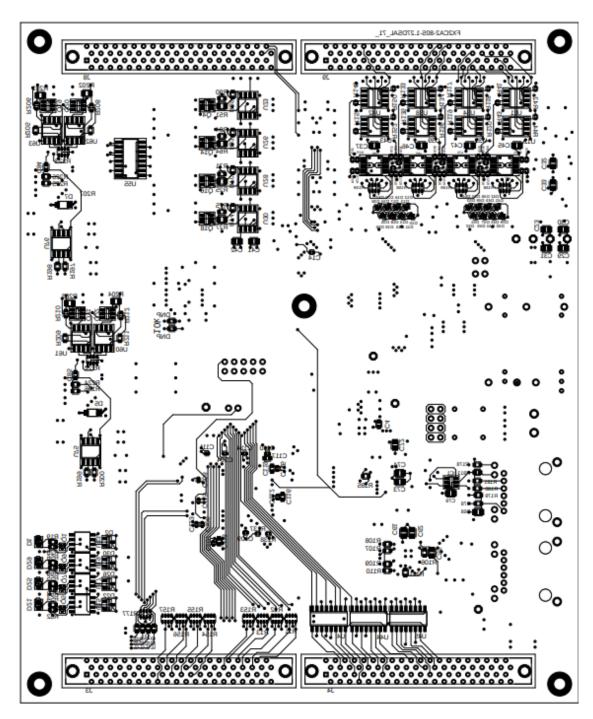

The PCB design presented in this chapter is called the IOB-Mk3-Transit Board (Figure 4-1). It is named so due to it being the peripheral board that sits between the Nucleo development board that holds the MCU and the target board that needs the I/O control. The name also marks the transition from FPGA based I/O control to MCU based I/O control. This board is distinctly different from the board that is covered in chapter 6, where the fully integrated MCU board will be referred to simply as IOB-Mk3. The IOB-Mk3-Transit and IOB-Mk3 are two different boards.

The design of the IOB-Mk3-Transit peripherals was a systematic approach based on looking at the different sections of the previous IOB iterations (IOB-Mk1 and IOB-Mk2) and analyzing their circuits by function and component choice. The goal is to reuse as much as possible due to the proven robustness of previous iterations. Each segment of the following chapter will contain an explanation of the function solutions of the IOB-Mk1 or IOB-Mk2 and whether I am directly adopting the solution and components; solutions that have been changed, along with the how and why they have been changed, follows where applicable.

Figure 4-1: IOB-Mk3-Transit Board

#### 4.1 The Digital Inputs and Outputs

The digital I/O section contains digital inputs (DI) and digital outputs (DO) and bases itself on the principle of a DO pulling down the DI to ground, therefore triggering it. Meaning that the DI is pulled up in a high state by default and the DI supplies the DO port with itself and a grounding wire. The DO then only has to connect these two wires, pulling the DI down to a low state, which is then registered as a DI trigger. The DO can do this with a dry-contact, which is just a potential-less switch, connecting two wires.

#### 4.1.1 Digital Inputs (DI)

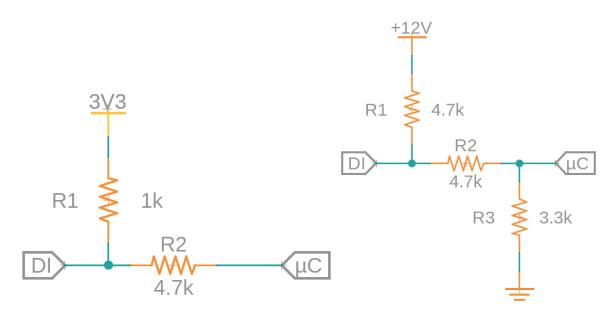

There are two implementations of the pullup network on the previous iterations of the IOB. One for the Mk1 and another for the Mk2 shown in Figure 4-2.

Figure 4-2: Mk1 DI (Left) and Mk2 DI (Right)

The reason for the difference in these two iterations is due to an issue on the Mk1 that can sometime occur where the input if falsely triggered, likely due to a sudden low resistance to ground on the data line. It has been noted over time that the suggested solution on the Mk2 did not improve performance in this matter and indeed made it somewhat worse.

Doing some testing with a simple potentiometer connected between the input and ground, I found that the Mk1's input configuration registered a trigger when the potentiometer reached a value of about  $600\Omega$  and below. Meanwhile the Mk2 input registered a trigger already at  $1k\Omega$ , making it easier to falsely trigger, which would explain the reports of Mk2's digital input performance.

To improve on Mk1's design while adapting the pullup structure to the STM32 microcontroller, the design for the Mk3 Transit card combined aspects of both previous iterations. The idea is to use a 12V

pullup to increase the amount of voltage that must be redirected for the digital input to register. Also, the higher resistance is to ensure that the microcontrollers pin is protected from stresses and injection currents; later and finer adjustments to the resistors can be made in following revisions of Mk3.

Figure 4-3: Mk3 Transit DI pullups

#### 4.1.2 Digital Output (DO)

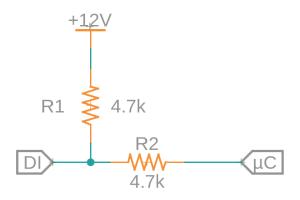

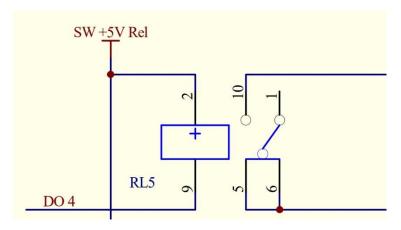

The digital output located on the IOB is a Darlington transistor pulldown type. This means that the microcontroller raises the voltage on the base of the Darlington component shown in Figure 4-4 as device U31. This pulls down the collector pin on the other end, acting like an inverter with a decent current sinking capability. However, this sinks current to its own local ground reference connection and is not the dry-contact referred to in section 4.1.1 Digital inputs.

Figure 4-4: IOB-Mk2 Digital Output Driver [10]

The Central-TB extends the IOB's digital output by using the current sinking capability of the Darlington component to power a mechanical relay component (Figure 4-5). Now the IOB is equipped with a potential free dry contact to toggle other external devices.

Figure 4-5: Central-TB Digital Output Relay

The relay is connected to the voltage "SW +5V Rel" which is only available if the IOB's watchdog signal is active, thus all digital outputs are disabled if the watchdog signal is in an alarm state. To clarify, a watchdog signal is fed into the B7 pin in Figure 4-4, which then controls the mechanical relay that allows the "SW +5V Rel" voltage to feed into all digital output relays, making them available to toggle.

#### 4.1.3 Watchdog

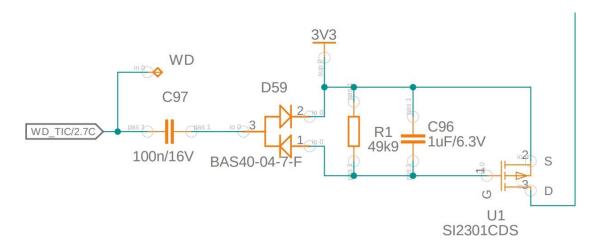

In the case of network connection loss, the IOB no longer receives updates to the digital output states. Digital outputs control external devices, or mechanical processes that in an event of connection loss should not be latched in active state. Therefore, the IOB is equipped with a watchdog that oversees the function of the digital output relays. In the case of the Central-TB, this watchdog circuit activates the mechanical relay that feeds the driving current to every digital output mechanical relay; whilst the watchdog is inactive, every digital output on the Central-TB becomes inactive.

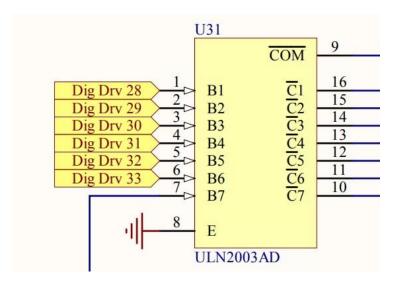

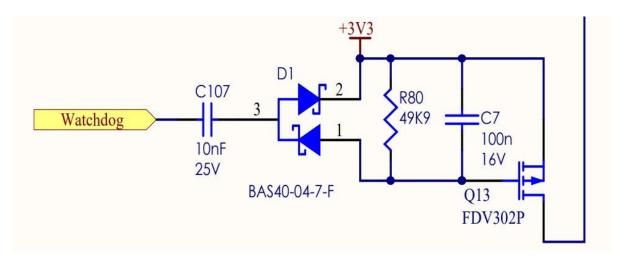

The watchdog circuit is driven by monitoring a heartbeat signal from the IOB, which in turn is only output when the IOB detects that it is connected to the network via NET A or NET B. In short, if the IOB is connected to the network, the heartbeat is enabled, and the digital output relays can be operated. In the IOB-Mk1 and Mk2, this is solved by using a charge pump that charges itself by using the heartbeat output generated by the processing unit. On the IOB-Mk2 that heartbeat is a 50kHz square wave signal.

Figure 4-6 shows the charge pump watchdog circuit on the IOB-Mk2. Capacitor C107 functions as an AC bypass capacitor for the heartbeat signal. The two diodes in Figure 4-6 act as one way charge valves; the diode on the bottom of the figure acting as the valve that lets capacitor C7 to receive a

charge current when the heartbeat is at 0V; the diode at top of the figure allows capacitor C107 to equalize itself when the heartbeat is at 3.3V.

Notice that the voltage over capacitor C7 is shared with the MOSFET's Gate-Source voltage, which decides if the MOSFET will be turned on or off. As the heartbeat continues to charge C7, the Gate-Source voltage increases, and at some point, the MOSFET's voltage threshold is met, turning the MOSFET on; with the MOSFET turned on, the IOB's digital output driver can power the relay that feeds current to all the digital output relays.

If the IOB loses connection, the heartbeat signal freezes to a static value of either OV or 3.3V, at which point the C107 capacitor will act as a break in the circuit, allowing capacitor C7 to equalize its charge though resistor R80, switching off the MOSFET, which then cuts off the power supply to all digital output relays.

Figure 4-6: IOB-Mk2 Watchdog

This is a solid and reliable method that relies on easy-to-acquire passive components, and it is easy to tweak its alarm time by adjusting the values of the of its resistor and two capacitors. However, the 50kHz heartbeat signal from FPGA is harder to reliably replicate and maintain by the microcontroller; there is no guarantee that the microcontroller could reliably keep the heartbeat stable at 50kHz without delays that would trigger an alarm.

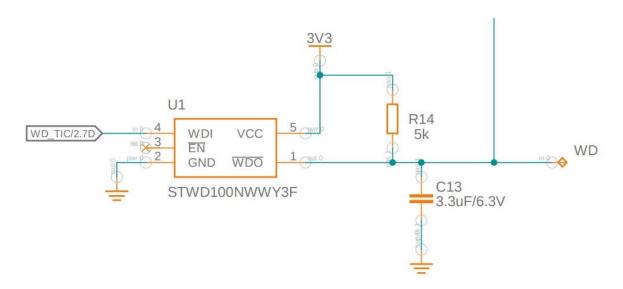

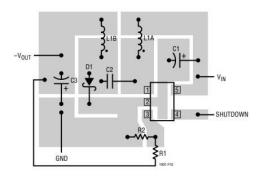

Often, a watchdog function overseen by a microcontroller is handled by an additional external component, like for example from the STWD100 component series [11]. The STWD100 is an IC (Integrated Circuit) component that only requires a toggle of the input signal state within an alarm period that is predefined by the component. A valid toggle of the input signal is both a falling and rising edge of the input signal, and the alarm time on the circuit chosen and shown in Figure 4-7 is 6.3ms. This is easy for the microcontroller to handle consistently without experiencing a delay of that would surpass the alarm time, making this a safe choice.

However, in future revisions and tweaks of the Mk3 board, after evaluating the performance and assessing if more processing capacity is available, the previous charge-pump solution could be calibrated for a slower and more manageable heartbeat signal and reintroduced as a solution.

As a sidenote, there is an annoyance to the function of the STWD100's alarm function. In the event of a dead input heartbeat signal, the STWD100's output alarm, which is an active low signal, repeatedly toggles high while in the alarm state. Usually, this component is used to reset a frozen processor, in which case having the alarm rise temporarily allows some time for the processor to reboot. However, in the IOB's case, this repeatedly activates the mechanical relays. Therefore, a pullup resistor and capacitor on the STWD100's output is used to effectively negate these output pulses.

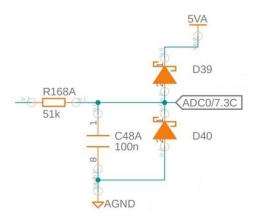

Figure 4-7: IOB-Mk3 Transit Watchdog circuit

#### 4.2 Analog Inputs (AI)

The analog input (AI) section of the IOB-Mk3-Transit deviates from Mk1 and Mk2 design quite a lot due to component shortages. Both ADCs (Analog to Digital Converter) used for the Mk1 (TLC2578IPW) and the Mk2 (ADS8638SRGER) were not available, as well as the operational amplifier (INA2132UA) used by both iterations.

#### 4.2.1 Mk1 and Mk2 Analog Input Design

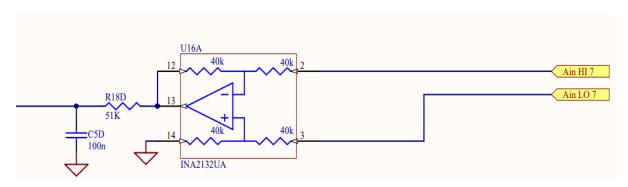

The analog input portion of the IOB is designed to read a current (4mA to 20mA) or a voltage (±10V). Figure 4-8 shows the circuit that is a standard differential amplifier follower by an RC circuit for low pass signal filtering. The analog input can read both differential and single ended outputs without needing to ground the negative differential wire, this is due to the virtual ground present in the case that the LO connection is left floating [12]. The circuit reads a current by sampling the voltage off a shunt resistor located on the Central-TB circuit board.

Figure 4-8: Stage 1 Analog Input IOB-Mk1 and Mk2

The input voltage is received by a differential operation amplifier configuration, which works by subtracting the voltage at the negative terminal from the voltage at the positive terminal. This configuration solves this elegantly by choosing all resistors in the circuit to be of an equal value, in this case the INA2132UA internal resistors are precision cut to  $40\text{k}\Omega$ . This simplifies the gain of the circuit by setting the gain ratio to  $\frac{R_2}{R_1}=1$ .

The positive component works as a standard non-inverting amplifier configuration except for that the input is halved before interacting with the gain of the amplifier. All resistors being equal allows the positive input to be connected to a voltage divider (R3 and R4) that exactly halves the input at the positive terminal, making the positive terminal contribution equal  $V_{O+} = V_{I+}$ .

The negative component is summarized as a standard inverting amplifier, with equal resistors, its contribution can be simplified to  $V_{O-} = -V_{I-}$ . Adding these two components gives us equation 1, that states that the circuit simply subtracts the negative input from the positive input and outputs the result.

$$V_O = V_{I+} - V_{I-} \tag{1}$$

The primary function of this circuit on the IOB is to be able to input either a single ended or a differential voltage input and leave us with a single ended output for further processing. It is always recommended to use differential mode for transferring the analog signal over long distances due to common-mode noise cancellation.

The IOB-Mk1 uses the TLC2578IPW ADC using an operational amplifier in the non-inverting voltage follower configuration (AKA buffer) as stage 2 of the analog input, feeding into the ADC [13]. This buffer allows the LP filter in stage one to benefit from the low leakage current into the buffer and eliminates operational amplifier loading effects due to the ADCs analog input currents; the buffer allows amplifier stage one to be unaffected by the current demands of the ADC.

The IOB-Mk2 uses the ADS8638SRGER ADC instead, which has a low current demand on its analog input ports, rated as a leakage current at 200nA [14]. This allows the IOB-Mk2 to forgo the buffer

circuit and have the subtracting amplifier in stage 1 to directly feed into the ADC since 200nA does not stand to have any substantial loading effect on the amplifier.

#### 4.2.2 Mk3-Transit Analog Input Design

The analog input of the Mk3-Transit required a different structure due to the lack of ADC availability. The ADC components used in the previous IOB iterations used ADCs capable of directly reading voltages spanning -10V to +10V, a span of 20V. The replacement that was the safest to rely on, component stock-wise, was the MCP3208 [15]. This ADC, however, can only read voltages in from 0V to 5V.

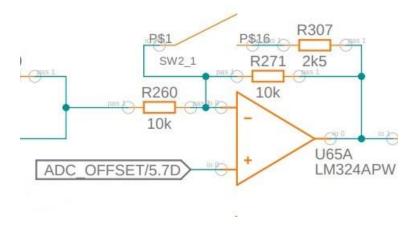

This poses a challenge when the desired function of the analog input is to read both a  $\pm 10V$  signal and a 0.88V - 4.4V signal (4mA to 20mA on a 220 $\Omega$  shunt resistor) on the same circuit. The solution decided for this issue is to have a second stage between the receiving op-amp and the ADC; the second stage's task is to dampen the signal and squeeze it into the 0V - 4V range, keeping a margin from the maximum voltage rating of the ADC's input pins. Figure 4-9 shows the second stage op-amp.

Figure 4-9: Mk3-Transit AI stage 2

Now there is a large reduction in readable voltage range, since the ±10V signal had to be dampened five times to attain the desired 4V range. This also damps the current-based signal by five times, and the already lower range is reduced to a mere 0.7V range total (0.176V at 4mA and 0.88V at 20mA). So, by adding a DIP switch on the PCB to add in an optional parallel resistor, I can change the damping and the offset to maximize the range and improve the reading for both modalities.

The "ADC\_OFFSET" seen in Figure 4-9 is set to 2.3V by a voltage reference, followed by a voltage follower. Now, with the switch turned on, the second stage dampens, and translates ±10V into a signal that is 2.76±2V; this is the voltage reading mode. With the switch turned off, the output offset changes from 2.76V to 4.6V, and the voltage that is input decreases the output voltage by the same value; the current reading mode now has a range that is 4.6V at 0mA, 3.72V at 4mA and 0.2V at 20mA. The

reason I specify and separate the 0mA value, is that it is specifically used as a broken loop detection function; the true range of the signal, is 4mA to 20mA.

#### 4.3 Analog Outputs (AO)

The analog output (AO) has two output modalities, a voltage (+-10V) mode and current (4mA – 20mA) mode, and they are both commanded simultaneously by the same DAC (Digital to Analog Converter) circuit which in this case is the TLV5608IPW. This device is an 8 channel DAC that is connected to the MCU via SPI communication and it outputs 0V to 5V on each of its 8 channels.

Each DAC output channel is connected both to a voltage output amplifier circuit and a current output amplifier circuit simultaneously, without multiplexing on the IOB. Multiplexing is not necessary since the Central-TB ensures that only one output modality can be used on a given analog output. The Central-TB board chooses an output's modality by physically disconnecting the other output mode option with a jumper strap, basically the output mode selection/multiplexing is done the user. See Figure 4-10, this is the analog output mode selection on the Central-TB, where jumper straps are used to select only one output mode to the respective analog output channel's designated wire terminal [16].

Figure 4-10: Central TB Analog Output mode selection [16]

#### 4.3.1 Voltage Output

Figure 4-11 shows the inverting amplifier used in voltage mode analog output. The amplifier has a gain of -5, as well as an offset. The offset is present because the purpose of the circuit is to provide an output of -10V up to +10V. Since the DAC feeding the input of this circuit is only of a positive voltage (0V to 5V), and since this is an inverting amplifier, it needs an offset voltage to be able to provide positive side of the output range.

The offset voltage works by providing a reference voltage of 1.7V, which is precisely maintained by a separate voltage reference IC followed by a voltage follower circuit. This 1.7V is input to the positive terminal of the circuit, where the gain is that of a non-inverting amplifier, which in this case becomes a gain of 6. In essence, the output of the amplifier is set to 1.7V\*6=10.2V by default and is then pushed downward by the DAC as shown in equation 2. Now, if the DAC outputs 4.04V, this would bring the output all the way down to -10V, giving the circuit the full range of  $\pm 10$  V.

$$V_0 = 10.2V - V_I * 5 (2)$$

Figure 4-11: IOB-Mk2 Analog Voltage Output Amp [10]

All necessary components required for this circuit were available and possible to acquire, so this design was directly reused and adapted to the IOB-Mk3 Transit design.

#### 4.3.2 Current Output

The current output is designed to be able to output 4mA to 20mA commanded from the same DAC output of 0V to 5V. The circuit design that is used in both IOB-Mk1 and IOB-Mk2 is shown in Figure 4-12. Firstly, notice the optocoupler which is labeled as U34D in this example. It has one function that does not affect the overall function of regulating the current output. The optocoupler acts as a status indicator for broken loop detection and will be discussed in 4.3.3.

The circuit that controls the current output requires a voltage source from the host product that will generate the current; the source is labeled in Figure 4-12 as "Out HI 7" and has been set to 12V for all its time in use, however raising the voltage does not affect the output. This will be demonstrated in the analysis.

The basic function of the circuit is that the operational amplifier operates the BJT transistor like a current valve, regulating the current through the output resistor R24. What happens is that the voltage from the DAC is directly applied as a voltage drop over the output resistor, which the current produced is divided between the circuits output and feedback. Interestingly, the negative feedback in this amplifier circuit utilizes the positive op-amp terminal. This works because the feedback current decreases as the voltage input increases, making the positive terminal function as a negative terminal.

All in all, the basic formula of the circuit for all practical uses is  $I_O = \frac{V_I}{R_O} - I_{FB}$ , where the feedback current can be ignored.

Looking at Figure 4-12 I name the following aspects of the circuit: Resistor R24 as output resistor  $R_O$ , Voltage source  $V_S$ , transistor collector voltage  $V_C$ , operational amplifier internal resistors  $R_i$ .

Figure 4-12: IOB-Mk2 Analog Current Output [10]

Before analyzing the circuit completely, it is useful to make some baseline observations. Firstly,  $V_S$  sees a voltage divider that is connected to the negative terminal of the operational amplifier; the voltage divider results in  $\frac{V_S}{2}$  being present on both the negative and positive terminal. Secondly, the voltage drop over  $R_O$  is equal to  $V_{RO} = V_S - V_C$ . Thirdly, the feedback current  $I_{FB}$  is defined as the current from the  $V_C$  node to the  $V_I$  node.

From that the analysis begins by approximating the feedback current as having no loss to the positive terminal and thus being equal though both internal resistors as shown in equation 3. Looking at the relationship of the voltage drop over both internal resistors, I simplify equation 3 to  $V_S - V_C = V_I$ . With this, observe that  $V_I$  has the same relationship as  $V_{RO}$  and that they must be equal.

Lastly, see equation 4 as it lays out how the output relates to the input and how the  $I_{FB}$  component lessens as  $V_I$  is increased. Also, observe that the value of  $V_S$  is not relevant to the set voltage drop  $V_{RO}$ , since is equates to and is only dependent by  $V_I$ .

$$I_{FB} = \frac{\frac{V_S}{2} - V_I}{R_i} = \frac{V_C - \frac{V_S}{2}}{R_i} \tag{3}$$

$$V_{I} = V_{Ro}$$

$$I_{O} = I_{Ro} - I_{FB}$$

$$I_{O} = \frac{V_{I}}{R_{O}} - \left(\frac{\frac{V_{S}}{2}}{R_{i}} - \frac{V_{I}}{R_{i}}\right)$$

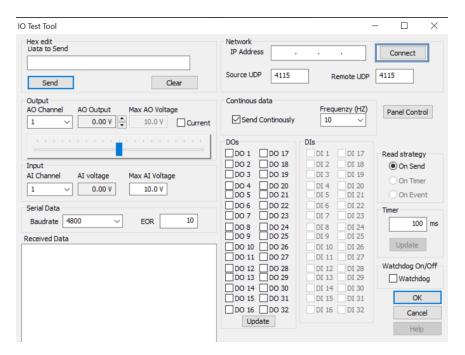

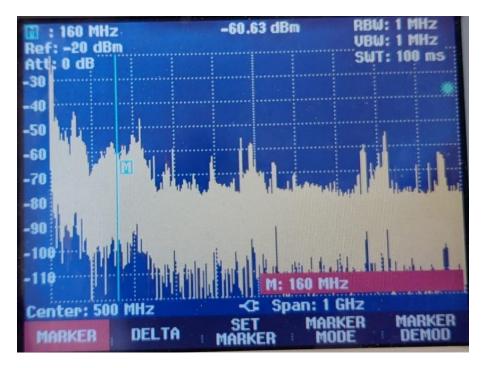

$$(4)$$