### UNIVERSIDAD COMPLUTENSE DE MADRID FACULTAD DE INFORMATICA

### **TESIS DOCTORAL**

User-defined execution relaxations for enhanced programmability in high-performance parallel computing

Relajaciones de ejecución definidas por el usuario para la mejora de la programabilidad en computación paralela de altas prestaciones

MEMORIA PARA OPTAR AL GRADO DE DOCTOR

PRESENTADA POR

Andrés Antón Rey Villaverde

**Directores**

Francisco Daniel Igual Peña Manuel Prieto Matías

Madrid

# **User-defined Execution Relaxations for Enhanced Programmability** in High-Performance Parallel Computing

\_

Relajaciones de Ejecución Definidas por el Usuario para la Mejora de la Programabilidad en Computación Paralela de Altas Prestaciones

TESIS DOCTORAL

Andrés Antón Rey Villaverde

Dirigida por:

Francisco Daniel Igual Peña y Manuel Prieto Matías

Facultad de Informática Universidad Complutense de Madrid

Madrid, 2019

# **User-defined Execution Relaxations for Enhanced Programmability** in High-Performance Parallel Computing

\_

Relajaciones de Ejecución Definidas por el Usuario para la Mejora de la Programabilidad en Computación Paralela de Altas Prestaciones

> Memoria que presenta para optar al título de Doctor en Informática Andrés Antón Rey Villaverde

Dirigida por los Doctores Francisco Daniel Igual Peña y Manuel Prieto Matías

> Facultad de Informática Universidad Complutense de Madrid

> > Madrid, 2019

## DECLARACIÓN DE AUTORÍA Y ORIGINALIDAD DE LA TESIS PRESENTADA PARA OBTENER EL TÍTULO DE DOCTOR

| D./Dña. Andrés Antón Rey Villaverde ,                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| estudiante en el Programa de Doctorado Doctorado en Ingeniería Informática (RD99/2011),                                                                                                                                                                                                                                                                                                                                                                                       |

| de la Facultad de Informática de la Universidad Complutense de                                                                                                                                                                                                                                                                                                                                                                                                                |

| Madrid, como autor/a de la tesis presentada para la obtención del título de Doctor y                                                                                                                                                                                                                                                                                                                                                                                          |

| titulada:                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| User-defined Execution Relaxations for Enhanced Programmability in High-Performance Parallel Computing                                                                                                                                                                                                                                                                                                                                                                        |

| Relajaciones de Ejecución Definidas por el Usuario para la Mejora de la Programabilidad en Computación Paralela de Altas Prestaciones                                                                                                                                                                                                                                                                                                                                         |

| y dirigida por: Francisco Daniel Igual Peña y Manuel Prieto Matías                                                                                                                                                                                                                                                                                                                                                                                                            |

| DECLARO QUE:  La tesis es una obra original que no infringe los derechos de propiedad intelectual ni                                                                                                                                                                                                                                                                                                                                                                          |

| los derechos de propiedad industrial u otros, de acuerdo con el ordenamiento jurídico vigente, en particular, la Ley de Propiedad Intelectual (R.D. legislativo 1/1996, de 12 de abril, por el que se aprueba el texto refundido de la Ley de Propiedad Intelectual, modificado por la Ley 2/2019, de 1 de marzo, regularizando, aclarando y armonizando las disposiciones legales vigentes sobre la materia), en particular, las disposiciones referidas al derecho de cita. |

| Del mismo modo, asumo frente a la Universidad cualquier responsabilidad que pudiera derivarse de la autoría o falta de originalidad del contenido de la tesis presentada de conformidad con el ordenamiento jurídico vigente.                                                                                                                                                                                                                                                 |

| En Madrid, a 3 de octubre de 2019                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Esta DECLARACIÓN DE AUTORÍA Y ORIGINALIDAD debe ser insertada en la primera página de la tesis presentada para la obtención del título de Doctor.

Fdo.:

# This work is licensed under the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/4.0/ or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

I hereby declare that all the content presented in this thesis entitled "User-defined Execution Relaxations for Enhanced Programmability in High-Performance Parallel Computing" has been developed by me, and all other content has been appropriately referenced.

Andrés Antón Rey Villaverde

This work has been supported by the Spanish Ministry of Innovation, Science and Universities under the grants TIN 2015-65277-R, RTI2018-093684-B-I00 and BES-2016-076806, and the Government of Madrid under the grant S2018/TCS-4423. The associated research internships have been supported by the Erasmus+ International Programme and the HiPEAC Network.

Este trabajo está disponible bajo los términos de la Licencia Internacional Creative Commons Atribución-NoComercial-SinDerivadas 4.0. Para ver una copia de esta licencia, visite http://creativecommons.org/licenses/by-nc-nd/4.0/ o envíe una carta a Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

Por la presente, declaro que todo el contenido presentado en esta tesis titulada "Relajaciones de Ejecución Definidas por el Usuario para la Mejora de la Programabilidad en Computación Paralela de Altas Prestaciones" ha sido desarrollado por mí, y cualquier otro contenido ha sido apropiadamente referenciado.

Andrés Antón Rey Villaverde

Este trabajo ha sido financiado por el Ministerio de Innovación, Ciencia y Universidades bajo los proyectos TIN 2015-65277-R, RTI2018-093684-B-I00 y BES-2016-076806, y por el Gobierno de la Comunidad de Madrid bajo el proyecto S2018/TCS-4423. Las estancias de investigación asociadas a este trabajo han sido financiadas por el programa de intercambio Erasmus+ Internacional y por la Red HiPEAC.

### Acknowledgements

I would like to thank my advisors Fran and Manuel for helping me and counting on me during these years, showing me their trust, support and giving me the proper advices at the proper moments. I also greatly thank their support during my research internships abroad, in which I learned so much, and also their trust to let me explore some rather tangential topics, in relation to the core thesis discipline, which however showed to be crucial during the exploratory scientific process. Thanks to Fran, specially for the valuable feedback received throughout this thesis, and for having helped me so much in the achievement of the thesis objectives, encouraging me to *get things done* in the most important moments. Thanks to Manuel, also for the accurate advices, specially for opening the ArTeCS doors for me, both the first and the second time, for showing me his trust throughout all of these years, not only during the Ph.D. years, and also for counting on me when Ph.D. sponsoring opportunities appeared.

Thanks to my family, for the constant support received not only during the development of this thesis, but also for supporting me in those personal decisions in which I prioritized *learning*, the *personal introspection*, and the *scientific training* over other options presumably more *ordinary*, *expected* and less *precarious* (and probably more boring). I want to thank my mother and father, from whom I learned personality traits very important in life and crucial to finish this Ph.D. degree, such as the culture of effort, the importance of education, persistence, and honesty; and also for having prioritized their sons and daughter over anything, always respecting our independence. I thank my brother for his influence in my education, and for passing his ambition on me, so important to visualize the *big picture* and to keep the motivation alive. I also thank my sister for the support received from the very beginning of these Ph.D. studies and for always passing her positivity on me.

Thanks to Amparo, specially for supporting me and bear me during these last stressful months, and for sharing with me such amazing vacations. Thanks to my Cisneros friends Javier, Juan Miguel, Antonio, Alejandro, Xabier, Pablo and Eliseo for keeping loyal to our (increasingly rare) meetings and (increasingly frequent) weddings. Thanks also to my childhood friends Victoria, Manuel, Valentín, Jaime, Iago and Domingo, for being *more closer than farther* after so many years. Thanks to Agathe, for having unconditionally stayed with me in the beginning of this thesis, both in the good and worse moments, and to Dominic, specially for those conversations (initiated at the end of the world five years ago and still maintained), for passing his idealism and motivation on me, and for his interest in the developments of this thesis. Thanks to my *industrial* friends Ángel Rosso, Elena Saiz, Elena Garzón, Mar Robledo, Alberto Palomar and Laura Vallejo and to my *Impanati / Jamadan* friends, Marco, Davide and Javier, for those meetings, beers and rehearsals that helped me so much to get away from the thesis when I needed it the most. Thanks also to the *Impanati* guys to bear with patience the rehearsal interruptions during my internships abroad.

Thanks to the people in the Computer Architecture division, starting from Iñaki and Manuel, who opened the ArTeCS doors for me, and specially to all those people I had the pleasure to meet throughout these years, such as Daniel Tabas, Jorge Quintás, Roberto Cano, Luis Costero, Nacho Gómez, Javier Setoain, Edgardo Mejía, Juan Carlos Sáez, Luis Piñuel, Christian Tenllado, Fernando Castro, Guillermo Botella, Katzalin Olcoz, Rafael Sánchez, Joaquín Recas and María Guijarro.

Thanks to Jan Prins for accepting to be my advisor in Chapel Hill, for inviting me to his home,

and for our discussions and his accurate insights that identified the limitations of my ideas, also helping me to address them. Thanks to the people I met in North Carolina, specially Joshua, Christian and Camila, for the interesting conversations and for making my internship so much fun. Thanks to the Codeplay people, Ruyman, Marya, Peter, Marios, Alex, Gordon, Uwe and Christopher for giving me the opportunity to work and learn from them, giving me such an excellent research experience in Edimburgh, which helped me so much to focus my further developments.

Recalling my beginnings in computation and simulation worlds, I want to thank the professors that helped me to get experience in numerical methods applied to computational physics. I want to thank Carlos Spa, for giving me the opportunity to work and learn from him in Chile, and for encouraging me to start the Ph.D. studies. I also want to thank Víctor Martín, who initiated me in the fascinating world of statistical mechanics (to which I will return); and Leo González, who initiated me in computational fluid dynamics, appreciating my motivation over my previous experience.

I also want to thank the best university professors I had, who have reinforced my passion for learning, also initiating me in *the ways of the science*, who have greatly inspired me during my studies of engineering and physics. Despite several years have passed, I still have vivid memories of their lectures and the sensations that they awakened on me back then, which years later have somehow guided me toward starting Ph.D. studies. They are Enrique Maciá, Estrella Alonso, Ángela Jiménez, Juan Pedro Villaluenga, Luis Garay, Felipe Llanes, José Ramón Pelaez and again Víctor Martín.

I want to thank the reviewers Aleksandar and Ricardo for their valuable suggestions that, together with my advisors, have greatly contributed toward enhancing the quality of the current dissertation. Moreover, I want to thank the anonymous reviewers of the published articles, as their feedback has also guided the research conducted in this thesis. I also want to thank in a general sense the developer communities that are constantly pushing computer technology to new heights in a passionate and idealistic way, either developing open source tools, contributing to programming language standardizations, and also producing documentation and disseminating it in open and free media. Specifically, the developments in this thesis depart to a great extent from the Standard C++ committee works, and some of the proposed ideas exposed in this thesis would not have been possible without all the new functionalities incorporated in modern C++ standards.

### Agradecimientos

Quisiera agradecer a mis directores Fran y Manuel haberme ayudado tanto y contar conmigo durante estos años, dándome la confianza, el apoyo y los consejos en los momentos adecuados. También agradezco enormemente su apoyo durante mis estancias de investigación en el extranjero en las que tanto he aprendido, así como su confianza para permitirme explorar temas a priori tangenciales a la disciplina central de la tesis, pero que han sido clave durante el proceso de exploración científica. Gracias a Fran, especialmente por el valioso feedback recibido a lo largo de esta tesis y haber influido tanto en la consecución de los objetivos, ayudándome a empujar hasta sacar el trabajo adelante en los momentos en los que más se necesitaba. Gracias a Manuel, también por los consejos acertados y especialmente por abrirme las puertas de ArTeCS, tanto la primera como la segunda vez, por la confianza demostrada durante todos estos años, no solamente durante la dirección de esta tesis, y también a la hora de contar conmigo para la financiación de la misma.

Gracias a mi familia, por el constante apoyo recibido no sólo durante el desarrollo de esta tesis, sino también por apoyarme en aquellas decisiones personales en las que prioricé el *aprendizaje*, la *exploración personal* y el *desarrollo científico*, por encima de otras opciones quizás más *habituales*, *esperables* y menos *precarias* (y probablemente más *aburridas*). Le doy las gracias a mi madre y a mi padre, de quienes he aprendido cualidades clave para la vida y para terminar este doctorado, como la practicar la cultura del esfuerzo, la valoración de la educación, la constancia y la honestidad; y también por haber puesto a sus hijos por encima de todo, siempre respetando y valorando nuestra independencia. Agradezco a mi hermano su influencia en mi formación, y por contagiarme su ambición, tan fundamental para visualizar el *big picture* y mantener la motivación viva. Agradezco también a mi hermana el apoyo recibido desde el *minuto cero* de este doctorado y por haberme transmitido siempre su positivismo.

Gracias a Amparo, especialmente por haberme apoyado y aguantado durante estos últimos meses de estrés, y por compartir tan geniales vacaciones. Gracias a mis amigos del Cisneros, Javier, Juan Miguel, Antonio, Alejandro, Xabier, Pablo y Eliseo por seguir fieles a nuestras (cada vez más ocasionales) quedadas y (cada vez más frecuentes) bodas. Gracias también a mis amigos de Coruña, Victoria, Manuel, Valentín, Jaime, Iago y Domingo, por seguir *más cerca que lejos* después de tantísimos años. Gracias a Agathe, por haberme acompañado incondicionalmente en los inicios de la tesis, tanto en los buenos como en los malos momentos, y a Dominic, especialmente por esas conversaciones (iniciadas en los confines del mundo hace cinco años y todavía mantenidas), por contagiarme su idealismo y motivación, y por su interés constante en el desarrollo de esta tesis. Gracias a mis amigos *industriales*, Ángel Rosso, Elena Saiz, Elena Garzón, Mar Robledo, Alberto Palomar y Laura Vallejo, y a mis amigos *Impanati / Jamadan*, Marco, Davide y Javier, por aquellas quedadas, cervezas y ensayos que me han ayudado tanto a desconectar de la tesis cuando más lo necesitaba. Gracias también a los *Impanati* por aguantar con paciencia los parones ensayísticos durante mis estancias en el extranjero.

Gracias a la gente del departamento de Arquitectura de Computadores y Automática empezando por Iñaki, que junto con Manuel me abrió las puertas de ArTeCS, y especialmente a toda la gente que he tenido el placer de conocer a lo largo de estos años, como Daniel Tabas, Jorge Quintás, Roberto Cano, Luis Costero, Nacho Gómez, Javier Setoain, Edgardo Mejía, Juan Carlos Sáez, Luis Piñuel, Christian Tenllado, Fernando Castro, Guillermo Botella, Katzalin Olcoz, Rafael Sánchez, Joaquín Recas y María Guijarro.

Gracias a Jan Prins, por aceptar ser mi supervisor en Chapel Hill, por abrirme las puertas de su casa, y por nuestras conversaciones y sus acertadas observaciones que identificaron con gran precisión las limitaciones de mis ideas, ayudando también a resolverlas. Gracias a la gente que conocí en Carolina del Norte, especialmente a Joshua, Christian y Camila, por las interesantes conversaciones y por hacerme mucho más divertida la estancia. Gracias a la gente de Codeplay, Ruyman, Marya, Peter, Marios, Alex, Gordon, Uwe y Christopher, por darme la oportunidad de trabajar y aprender tanto con ellos, dándome una experiencia de investigación inmejorable en Edinburgo, y que tanto me ha ayudado en focalizar mis desarrollos.

Recordando mis inicios en el mundo de la computación y la simulación, quiero agradecer a los profesores que me han ayudado a introducirme y desarrollarme en métodos numéricos aplicados a la física computacional. Quiero dar las gracias a Carlos Spa, por darme la oportunidad de trabajar y aprender con él en Chile, y por animarme a empezar el doctorado; así como a Víctor Martín, quien me ayudó a introducirme en el apasionante mundo de la mecánica estadística (al que volveré); y a Leo González, quién me introdujo en la dinámica de fluidos computacional valorando más mi motivación que mi experiencia previa.

También quiero dar las gracias a los mejores profesores y profesoras que he tenido en la universidad, que han reforzado mi pasión por aprender, introduciéndome en *los caminos de la ciencia*, y que más me han inspirado durante mis estudios de industriales y físicas. Aunque hayan pasado unos cuantos años, todavía tengo vívidos recuerdos de sus clases y de las sensaciones que me despertaron entonces, y que de algún modo, años después, me han llevado a iniciar los estudios de doctorado. Ellos son Enrique Maciá, Estrella Alonso, Ángela Jiménez, Juan Pedro Villaluenga, Luis Garay, Felipe Llanes, José Ramón Pelaez y de nuevo Víctor Martín.

Quiero agradecer a los revisores Aleksandar y Ricardo por su valiosos comentarios que, junto con mis directores, han contribuido enormemente a mejorar la calidad de la presente memoria. Así mismo, quiero agradecer a los revisores anónimos de los artículos publicados, ya que también han contribuido a guiar la investigación llevada a cabo en esta tesis. Quiero agradecer también de forma general a las comunidades de desarrolladores que constantemente, de forma apasionada e idealista, empujan la tecnología informática hacia nuevas cotas, ya sea mediante desarrollo de herramientas de código abierto, estandarización de lenguajes de programación, o generación de documentación y divulgación desinteresada en medios abiertos y gratuitos. En concreto, los desarrollos de esta tesis derivan en buena parte del trabajo del comité de estandarización del lenguaje C++, y parte de las propuestas planteadas en esta memoria no hubieran sido posibles sin todas las nuevas funcionalidades que han sido incorporadas en los nuevos estándares C++.

### Contents

| Li | st of I | Figures       |                                                              | xxiii |

|----|---------|---------------|--------------------------------------------------------------|-------|

| Li | st of T | <b>Tables</b> |                                                              | XXV   |

| Li | stings  | ;             |                                                              | xxvii |

| Al | bstrac  | :t            |                                                              | xxix  |

| Re | esume   | en            |                                                              | xxxi  |

| 1  | Intr    | oductio       | n                                                            | 1     |

|    | 1.1     |               | <br>mentals                                                  |       |

|    |         | 1.1.1         | Challenges in High-performance Parallel Computing            |       |

|    |         | 1.1.2         | Addressing complexity through abstractions and hierarchies   |       |

|    | 1.2     | Progra        | ımmability in HPC                                            |       |

|    |         | 1.2.1         | Paradigms                                                    |       |

|    |         | 1.2.2         | Models, systems and runtimes                                 |       |

|    | 1.3     | Motiva        | ation                                                        |       |

|    |         | 1.3.1         | HPC programmability is still unsolved                        |       |

|    |         | 1.3.2         | Currently runtime-driven work                                |       |

|    |         | 1.3.3         | Potentially runtime-delegable work                           | . 14  |

|    | 1.4     | Summ          | ary                                                          | . 17  |

|    |         | 1.4.1         | Objectives                                                   |       |

|    |         | 1.4.2         | Thesis organization                                          | . 17  |

| 2  | Stat    | ic relax      | ed execution. Motivation and limitations                     | 19    |

|    | 2.1     | Introdu       | uction                                                       | . 19  |

|    |         | 2.1.1         | Extensions to the classic task scheduling problem            | . 20  |

|    |         | 2.1.2         | A driving example: Cholesky factorization                    | . 20  |

|    | 2.2     | Hetero        | ogeneous scheduling-partitioning with HeSP framework         | . 22  |

|    |         | 2.2.1         | Features of the scheduling-partitioning simulation framework | . 22  |

|    |         | 2.2.2         | Performance results on heterogeneous architectures           | . 25  |

|    | 2.3     | A MIL         | LP framework for power-constrained variable threading        |       |

|    |         | 2.3.1         | Model                                                        | . 28  |

|    |         | 2.3.2         | Experimental results                                         | . 31  |

|    | 2.4     | Summ          | ary                                                          | . 36  |

|    |         | 2.4.1         | Related work                                                 |       |

|    |         | 2.4.2         | Limitations of static approaches                             |       |

|    |         | 2.4.3         | Application to runtimes                                      | . 38  |

| 3  | Dyn     |               | elaxed execution. A programming model architecture           | 39    |

|    | 3.1     | Core a        | bstractions                                                  |       |

|    |         | 3.1.1         | A Task-Executor taxonomy                                     |       |

|    |         | 3 1 2         | Executor typology                                            | 42    |

XX CONTENTS

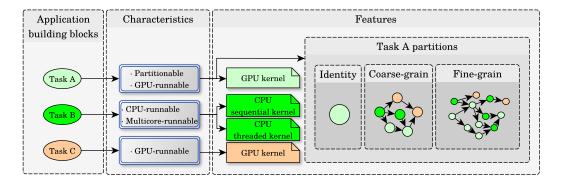

|   |     | 3.1.3    | User-defined task featurizations                                   | 44  |

|---|-----|----------|--------------------------------------------------------------------|-----|

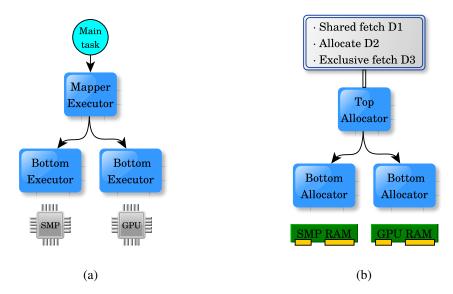

|   |     | 3.1.4    | Allocator typology                                                 | 46  |

|   |     | 3.1.5    | Hierarchical data-dependency resolution                            | 48  |

|   | 3.2 | Schedu   | uling execution expansions                                         | 48  |

|   |     | 3.2.1    | Execution expansions                                               | 49  |

|   |     | 3.2.2    | Generalized scheduling                                             | 49  |

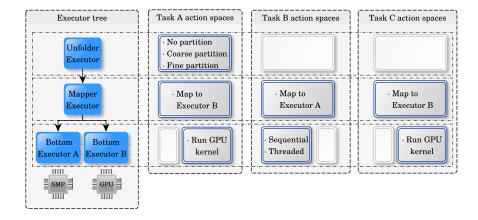

|   |     | 3.2.3    | Action spaces                                                      | 50  |

|   |     | 3.2.4    | State spaces                                                       | 51  |

|   | 3.3 | Summa    | ary                                                                | 55  |

|   |     | 3.3.1    | Related work                                                       | 55  |

|   |     | 3.3.2    | Contributions                                                      | 57  |

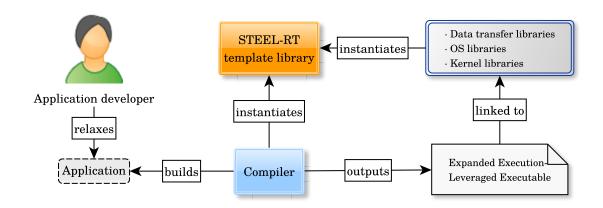

| 4 | STE | EL. Des  | sign principles and implementation                                 | 59  |

|   | 4.1 | Introdu  | action                                                             | 60  |

|   |     | 4.1.1    | Implementation requirements                                        | 60  |

|   |     | 4.1.2    | Current scope                                                      | 62  |

|   |     | 4.1.3    | STEEL implementation architecture                                  | 63  |

|   | 4.2 | STEEL    | L programming interface                                            | 65  |

|   |     | 4.2.1    | Prior definitions                                                  | 65  |

|   |     | 4.2.2    | Task definition                                                    | 66  |

|   |     | 4.2.3    | Executor deployment and use                                        | 72  |

|   |     | 4.2.4    | Definitions for custom data structures                             | 74  |

|   |     | 4.2.5    | Auxiliary interface                                                | 80  |

|   |     | 4.2.6    | Internal safety patterns                                           | 84  |

|   |     | 4.2.7    | Cases for user-defined relaxations                                 | 85  |

|   | 4.3 | Summa    | ary                                                                | 91  |

|   |     | 4.3.1    | STEEL-PM main characteristics                                      | 93  |

|   |     | 4.3.2    | Related work                                                       | 94  |

| 5 | Use | cases ar | nd experimental results                                            | 99  |

|   | 5.1 | Driving  | g examples                                                         | 99  |

|   |     | 5.1.1    | 2D buffers                                                         | 99  |

|   |     | 5.1.2    | Linear algebra kernels                                             | 100 |

|   | 5.2 | Data m   | nanagement. Visibility, access modes and OOC computation           | 101 |

|   |     | 5.2.1    | Dependency visibility                                              | 102 |

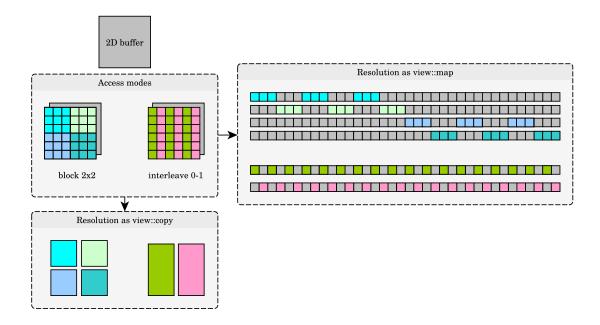

|   |     | 5.2.2    | 2D access modes                                                    | 102 |

|   |     | 5.2.3    | 2D data partitions                                                 | 104 |

|   |     | 5.2.4    | Out-of-core Computation (OOCC)                                     | 104 |

|   |     | 5.2.5    | Joint relaxation of visibility, granularity and precision          | 106 |

|   | 5.3 | Task m   | nanagement: parallelism and heterogeneity                          | 109 |

|   |     | 5.3.1    | Task- versus thread-parallelism                                    | 109 |

|   |     | 5.3.2    | Support for task moldability                                       | 110 |

|   |     | 5.3.3    | Support for heterogeneous computation                              | 112 |

|   | 5.4 |          | chical executor deployment                                         | 113 |

|   |     | 5.4.1    | STEEL implementation for the Cholesky factorization                | 113 |

|   | _   | 5.4.2    | Leveraging STEEL to exploit heterogeneity. A step-by-step use case | 115 |

|   | 5.5 | Summa    | ary                                                                | 121 |

| CONTENTE |     |

|----------|-----|

| CONTENTS | XX1 |

| COMILMID | AAI |

| 6           | STE    | EL as a  | functional model                                             | 123 |

|-------------|--------|----------|--------------------------------------------------------------|-----|

|             | 6.1    | Introdu  | action                                                       | 124 |

|             |        | 6.1.1    | Basic elements                                               | 124 |

|             |        | 6.1.2    | Data structures                                              | 127 |

|             | 6.2    | Functi   | onal relaxed execution model                                 | 130 |

|             |        | 6.2.1    | Execution path composition                                   | 130 |

|             |        | 6.2.2    | Asynchronous and data-flow computations                      | 135 |

|             |        | 6.2.3    | Scheduling and execution of tasks                            | 140 |

|             | 6.3    | Summ     | ary                                                          | 142 |

|             |        | 6.3.1    | Relation with STEEL-PM                                       | 142 |

|             |        | 6.3.2    | Model limitations                                            | 144 |

| 7           | Con    | clusions | S                                                            | 147 |

|             | 7.1    | Contri   | butions                                                      | 147 |

|             |        | 7.1.1    | Execution relaxations-leveraged programmability              | 148 |

|             |        | 7.1.2    | Performance portability                                      | 150 |

|             |        | 7.1.3    | Publications                                                 | 152 |

|             | 7.2    | Future   | work                                                         | 153 |

|             |        | 7.2.1    | Stateful, generalized and multi-objective expanded execution | 153 |

|             |        | 7.2.2    | Distributed layer and additional communication backends      | 153 |

|             |        | 7.2.3    | Support for resiliency                                       | 153 |

|             |        | 7.2.4    | ISO C++20 improvements                                       | 154 |

|             |        | 7.2.5    | Raising abstractions                                         | 154 |

|             |        | 7.2.6    | Benchmarking                                                 | 154 |

| Ap          | pend   | ices     |                                                              | 157 |

| A           | Prer   | eguisite | es of C++                                                    | 159 |

|             | A.1    | -        | ces                                                          | 159 |

|             | A.2    |          | ate specializations and constraints                          | 160 |

|             | A.3    | •        | ently used types                                             | 161 |

|             | A.4    |          | rce Acquisition Is Initialization                            | 161 |

| B Platforms |        |          | 163                                                          |     |

|             | B.1    | Масн     | IINE1                                                        | 163 |

|             | B.2    |          | IINE2                                                        | 164 |

| Bil         | bliogr | aphy     |                                                              | 164 |

| Ac          | ronyı  | ms       |                                                              | 177 |

| Gl          | ossar  | y of spe | cial terms                                                   | 179 |

*CONTENTS*

### List of Figures

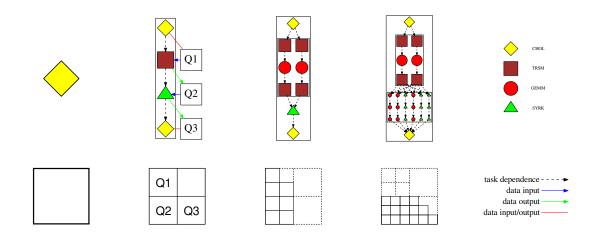

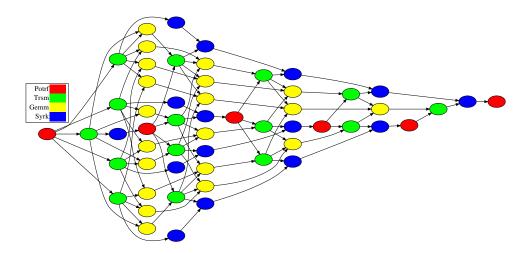

| 2.1  | Fine-grain Cholesky task DAG                                                         |

|------|--------------------------------------------------------------------------------------|

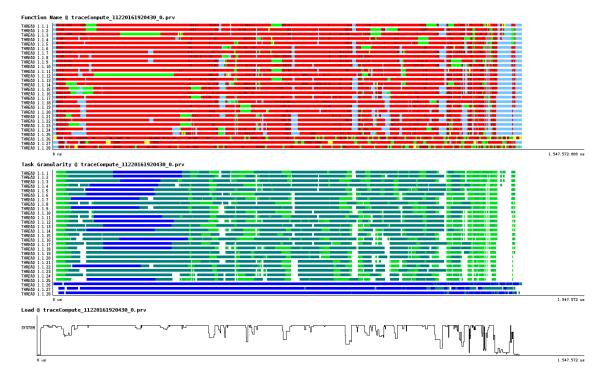

| 2.2  | Compute load trace of a Cholesky execution                                           |

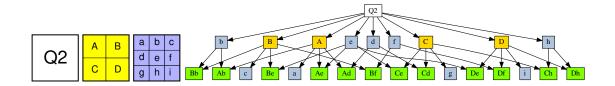

| 2.3  | Task DAG for the Cholesky factorization                                              |

| 2.4  | Example of task partitions and corresponding partitioned data blocks                 |

| 2.5  | Partitioning a data block according to different tilings                             |

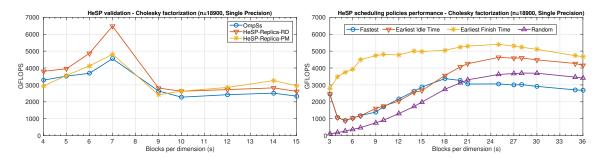

| 2.6  | Simulation validation and policy performance                                         |

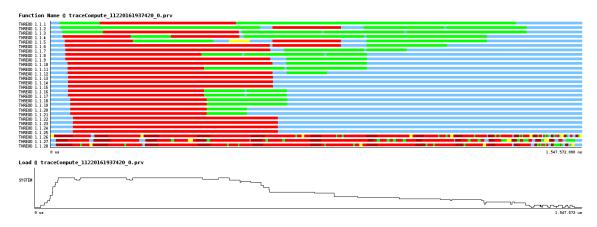

| 2.7  | Execution traces of best uniform partitioning on MACHINE1                            |

| 2.8  | Execution traces of best non-uniform partitioning on MACHINE1                        |

| 2.9  | DAG of a blocked Cholesky factorization induced from a $6 \times 6$ tiling 32        |

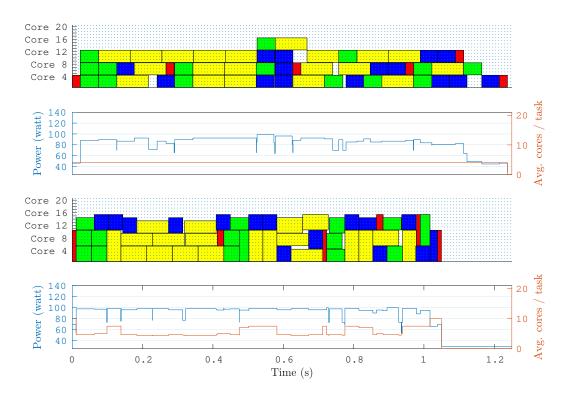

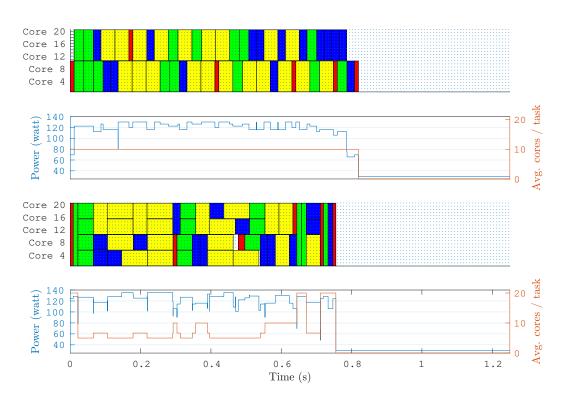

| 2.10 | Best found execution traces with variable threading                                  |

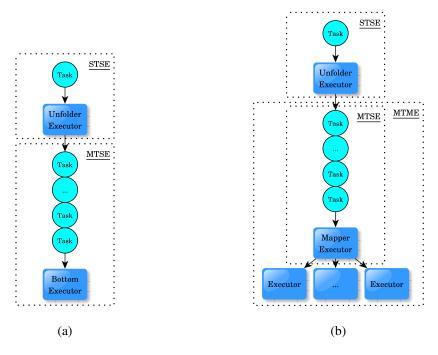

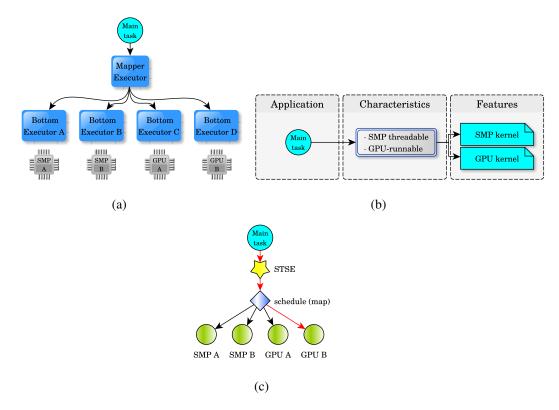

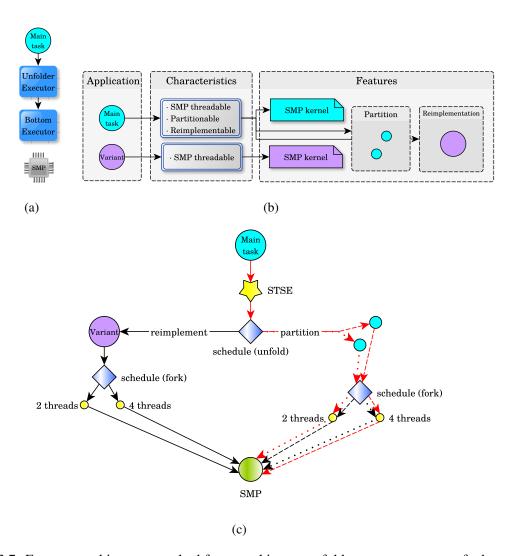

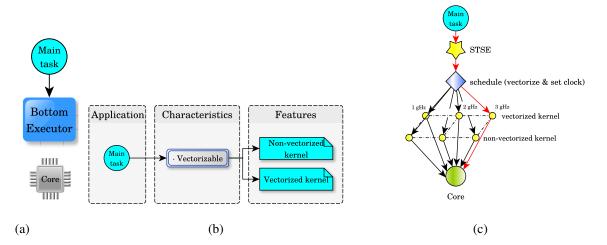

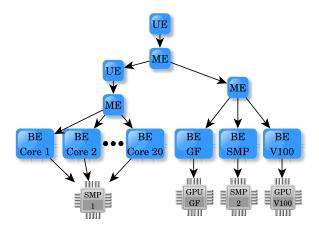

| 3.1  | Task-executor taxonomy                                                               |

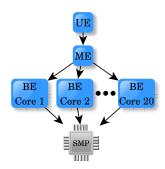

| 3.2  | STSE to MTSE and MTME scenarios                                                      |

| 3.3  | Example of task featurizations                                                       |

| 3.4  | Example of basic executor and allocator hierarchies                                  |

| 3.5  | Example of an executor tree and action spaces                                        |

| 3.6  | Example of execution paths in a mapper executor                                      |

| 3.7  | Example of execution paths in unfolder and bottom executors                          |

| 3.8  | Example of execution paths in a bottom executor                                      |

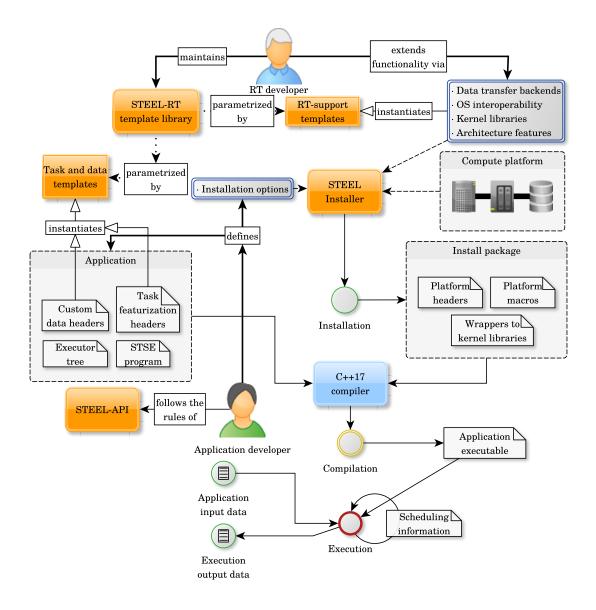

| 4.1  | STEEL-PM Brief implementation architecture                                           |

| 4.2  | STEEL-PM Full implementation architecture                                            |

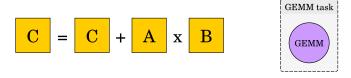

| 5.1  | GEMM operation                                                                       |

| 5.2  | Tiled GEMM $(2 \times 2)$                                                            |

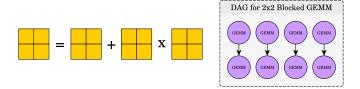

| 5.3  | Tiled GEMM $(4 \times 4)$                                                            |

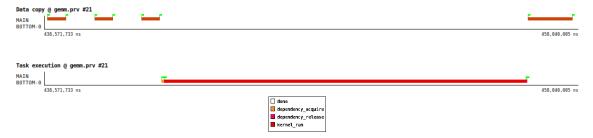

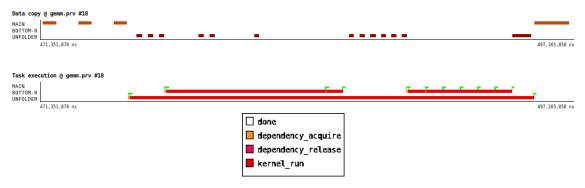

| 5.4  | Basic execution traces illustrating data copies and execution for impl::gemm . 103   |

| 5.5  | 2D accessibility modes                                                               |

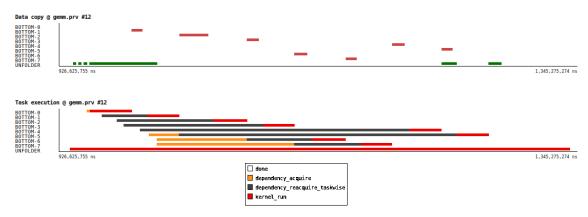

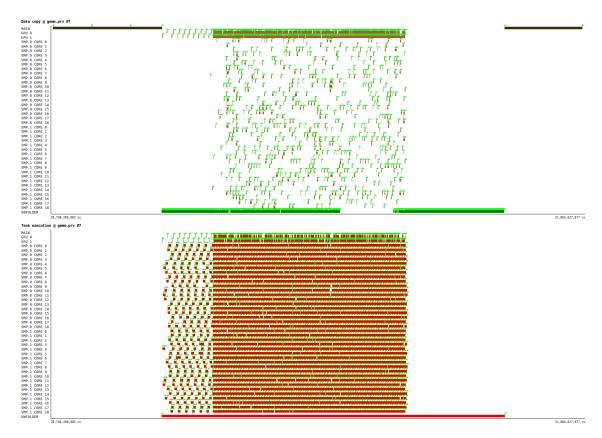

| 5.6  | Task/Data partition execution traces                                                 |

| 5.7  | Traces in a out-of-core execution                                                    |

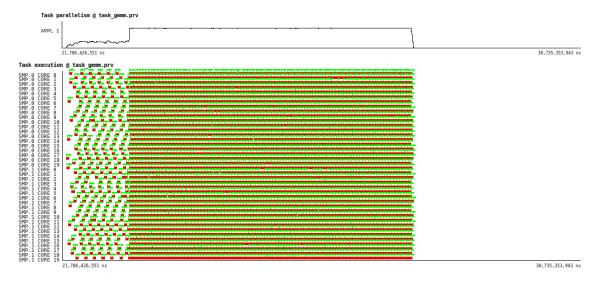

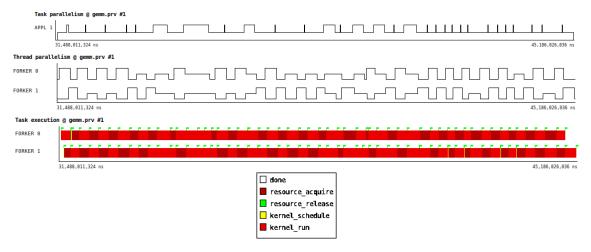

| 5.8  | Full task parallelism traces                                                         |

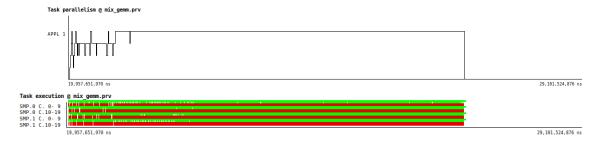

| 5.9  | Mixed task-thread parallelism traces                                                 |

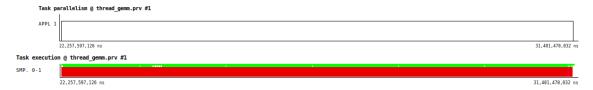

| 5.10 | Full thread parallelism traces                                                       |

| 5.11 | Executor hierarchy for the moldability case                                          |

| 5.12 | Execution traces with moldable tasks                                                 |

| 5.13 | CPU-GPU heterogeneous execution traces                                               |

| 5.14 | An executor hierarchy encompassing an uniform core pool                              |

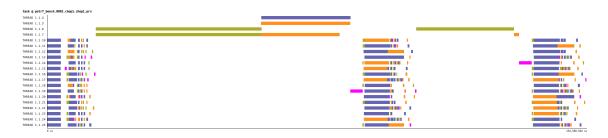

| 5.15 | Execution trace for a single-socket / multi-core execution                           |

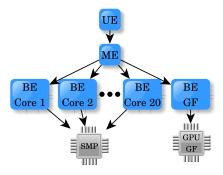

| 5.16 | An executor hierarchy with CPU-GPU platform with uniform partitioning 119            |

| 5.17 | Step 2. Execution trace for a heterogeneous CPU-GPU execution                        |

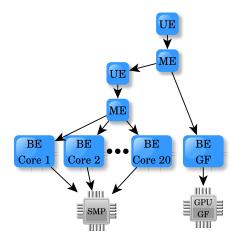

| 5.18 | An executor hierarchy with CPU-GPU platform with non-uniform partitioning 120        |

| 5.19 | Step 3. Excerpt of the factorization using a heterogeneous-partitioning strategy 120 |

| 5.20 | An exec, hierarchy with CPU-GPU platform with non-uniform part, and forking. 12      |

xxiv LIST OF FIGURES

| 5.21 | Step 4. Execution trace for a complex executor hierarchy | 121 |

|------|----------------------------------------------------------|-----|

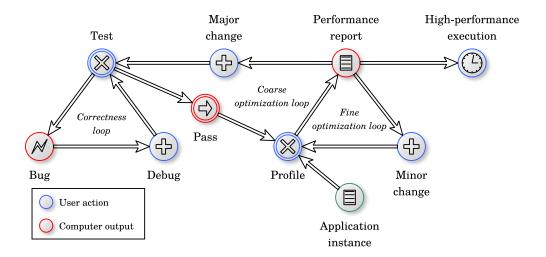

| 7.1  | Traditional development process                          | 149 |

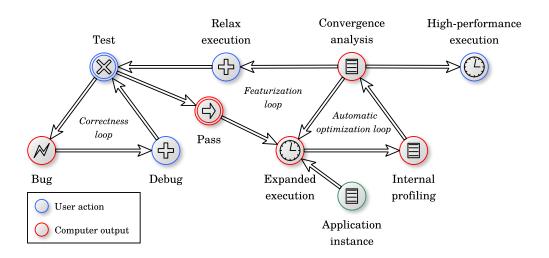

| 7.2  | STEEL-PM-based development process                       | 150 |

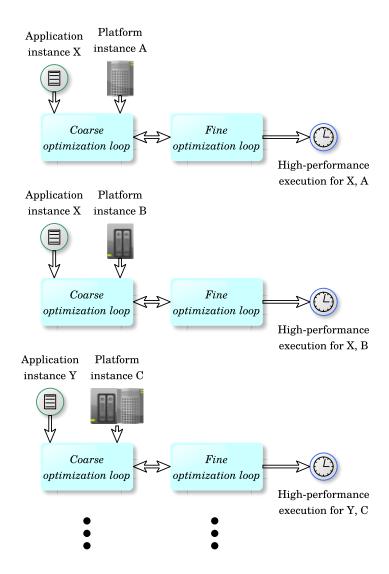

| 7.3  | Diagram exposing ad-hoc performance tuning               | 151 |

| 7.4  | Diagram exposing STEEL-PM-based performance tuning       | 152 |

### List of Tables

| 2.1 | Analysis characteristics for task scheduling relaxed granularity        | 20  |

|-----|-------------------------------------------------------------------------|-----|

| 2.2 | Performance comparison for MACHINE1                                     | 26  |

| 2.3 | Performances with different power constraints                           | 33  |

| 2.4 | Energy consumption with different power constraints                     | 36  |

| 3.1 | Task-Executor taxonomy                                                  | 41  |

| 3.2 | Compatibility requirements between tasks and executors                  | 45  |

| 3.3 | Data accessibility conditions                                           | 48  |

| 3.4 | Execution expansions in terms of executors and allocators               | 49  |

| 4.1 | Four scales regarding processing systems                                | 62  |

| 4.2 | Four scales regarding data storage systems                              | 62  |

| 4.3 | Data acquisition actions                                                | 77  |

| 4.4 | Data publication actions                                                | 78  |

| 6.1 | References to <i>Burst</i> function definitions and signatures          | 135 |

| 6.2 | Related functions for matching system platform with executor properties | 143 |

| 6.3 | Related functions during the application development process            | 144 |

| 6.4 | Related functions during runtime task scheduling                        | 144 |

| B.1 | Platform characteristics for MACHINE1                                   | 163 |

| B.2 | Current external dependencies                                           | 163 |

| B.3 | Platform characteristics for MACHINE2                                   | 164 |

| B.4 | Current external dependencies                                           | 164 |

xxvi LIST OF TABLES

### Listings

| 2.1  | C implementation of the blocked Cholesky factorization                               | 21 |

|------|--------------------------------------------------------------------------------------|----|

| 4.1  | Persistent enumerations                                                              | 66 |

| 4.2  | Enumerations for system-supported architectures and backends                         | 66 |

| 4.3  | Post-install system enumerations                                                     | 66 |

| 4.4  | Post-compile application enumerations                                                | 67 |

| 4.5  | Required type definitions for task traits                                            | 67 |

| 4.6  | Creation of task object of type X                                                    | 67 |

| 4.7  | Skeleton for user-defined task featurization                                         | 68 |

| 4.8  | Definition of a bottom executor kernel without expanding any option                  | 69 |

| 4.9  | Definition of a bottom executor kernel and expansion of scheduling options           | 69 |

| 4.10 | Skeleton for a bottom executor kernel and a expansion of multidimensional options.   | 70 |

| 4.11 | Definition of a bottom executor kernel using a built-in argument expansion           | 70 |

| 4.12 | Skeleton for a kernel to be run on an unfolder executor                              | 71 |

| 4.13 | Type and function definitions for feedback-based scheduling                          | 72 |

| 4.14 | Deployment of a bottom executor                                                      | 72 |

| 4.15 | Deployment of a Unfold executor                                                      | 73 |

| 4.16 | Deployment of different Mapper executors                                             | 73 |

| 4.17 | Deploy and group executors based on a condition                                      | 74 |

| 4.18 | Two possible ways for task construction and running                                  | 74 |

| 4.19 | Basic traits for a user-defined data structure with identifier DS                    | 75 |

| 4.20 | Internal runtime predicate to check whether a data object is allocatable             | 76 |

| 4.21 | Function types for copying and copy, copy_cast user definitions                      | 76 |

| 4.22 | Basic traits for a user-defined data structure with identifier DS                    | 77 |

| 4.23 | Interface for dependency initialization                                              | 77 |

| 4.24 | Dependency initialization from a string                                              | 78 |

| 4.25 | String conversions for DS data identifier                                            | 79 |

| 4.26 | Subregion access                                                                     | 79 |

| 4.27 | User definitions for subregion access                                                | 80 |

| 4.28 | Interface for context-aware RAII-based memory allocation                             | 80 |

| 4.29 | Context-aware RAII-based memory allocation from user side                            | 80 |

| 4.30 | Function for parsing program arguments                                               | 81 |

|      | Identification by mount-point of a persistent-storage memory space identified as MS. | 81 |

| 4.32 | Guarding a binary file as a data dependency                                          | 81 |

| 4.33 | Run of a STEEL program from command line                                             | 82 |

| 4.34 | Example of the main entry point of a STSE program                                    | 83 |

| 4.35 | Compile-time predicate to check application-processor compatibility                  | 84 |

| 4.36 | Compile-time verification for legal use of make_task                                 | 85 |

| 4.37 | Auxiliary template types for user-defined expand type                                | 86 |

| 4.38 | Relaxing number of threads for a OpenMP kernel                                       | 87 |

| 4.39 | Relaxing number of threads for a CUDA kernel                                         | 87 |

| 4.40 | Example calling a kernel library requiring a built-in type                           | 88 |

| 4.41 | Relaxing kernel execution via vector extension                                       | 89 |

| 4.42 | Relaxing a cuBLAS kernel execution via CUDA tensor cores                             | 89 |

xxviii LISTINGS

| 4.43 | Kernel for task partitioning                                                         | 90  |

|------|--------------------------------------------------------------------------------------|-----|

|      | User definitions for subregion access                                                | 91  |

| 4.45 | Allow different reimplementations for a task                                         | 92  |

| 4.46 | Example for floating point down-casting                                              | 92  |

| 5.1  | C implementation of the tiled Matrix-multiplication                                  | 100 |

| 5.2  | Definition of type characteristics (traits) for the gemm task                        | 101 |

| 5.3  | Definition of type characteristics (traits) for the potrf task                       | 101 |

| 5.4  | Main entry point of a impl::gemm program employing copy visibility                   | 102 |

| 5.5  | Example of data::access::block mode to partition a matrix into quadrants.            | 103 |

| 5.6  | Example of data::access::interleave mode to interleave matrix elements.              | 104 |

| 5.7  | Example of data::access::block mode to partition and cast quadrants                  | 106 |

| 5.8  | Unfolder kernel for impl::gemm                                                       | 107 |

| 5.9  | A synthetic example for composing data-dependent orthogonal relaxations              | 108 |

| 5.10 | Definition for moldable impl::gemm kernel targeting BLAS library                     | 112 |

|      | Definition for a GPU impl::gemm kernel targeting cuBLAS library                      | 114 |

|      | Main program running Cholesky factorization with STSE paradigm                       | 114 |

|      | Definition for a moldable impl::potrf kernel targeting LAPACK library                | 116 |

|      | Definition for a GPU impl::potrf kernel targeting cuSOLVER library                   | 116 |

| 5.15 | Implementation of the unfolder kernel for impl::potrf                                | 117 |

|      | Deployment of an unfolder on top of all available sequential processors (Fig. 5.14). |     |

|      | Deployment of a CPU-GPU hierarchy (Fig. 5.16)                                        | 119 |

| 5.18 | Deployment for heterogeneous partitioning (Fig. 5.18)                                | 119 |

|      | Deployment for heterogeneous partitioning and forking (Fig. 5.18)                    | 121 |

| A.1  | Basic example constexpr and interface constrained parametrization                    | 160 |

#### **Abstract**

This thesis proposes the **development and implementation of a new programming model based on execution relaxations, and focused on High-Performance Parallel Computing**. Specifically, the main goals of the thesis are:

- 1. Advocate a development methodology in which users define the basic computing units (tasks), together with a set of *relaxations* in, possibly, multiple dimensions. These relaxations will be translated, at execution time, into expanded (and complex) scheduling opportunities depending on the underlying architectural features, yielding improvements in terms of desired output metrics (e.g., performance or energy consumption).

- 2. Abstract away users from the complexity of the underlying heterogeneous hardware, delegating the proper exploitation of *expanded scheduling* choices to a system software component (typically referred as a *runtime*). This piece of software, armed with knowledge from static architectural characteristics and dynamic status of the hardware at execution time, will exploit those combinations considered optimal among those relaxations proposed by the user for each task ready for execution.

- 3. Extend this abstraction in order to describe both computing systems, by means of executor / allocator hierarchies that describe the heterogeneous computing architecture, and applications, in terms of sets of interdependent tasks. In addition, the relations between executors and tasks are categorized into a new task-executor taxonomy, which motivates ambiguity-free HPC programming frontends based on the STSE, Single Task Single Executor classification, distinguished from fully-automated runtime backends.

- 4. Propose a new programming model (STEEL) based on previous ideas, that gathers features considered to be basic for future task-based programming models, namely: performance, composability, expressivity and *hard-to-misuse* interfaces.

- 5. Specify an API to support the STEEL programming model, and a runtime implementation leveraging techniques and programming paradigms supported by modern C++, illustrating its flexibility, ease of use and performance impact by means of simple use cases and examples.

Hence, the proposed methodology stands for a clear and strict separation of concerns between the involved actors in a parallel executions: user / codes and underlying hardware. This kind of abstractions allows a delegation of the expert knowledge from the user toward the system software (runtime) in a systematic way, and facilitates the integration of mechanisms to automate optimizations, adapting performance to the specificities of the heterogeneous parallel architecture in which the code is instantiated and executed.

From this perspective, the thesis designs, implements and validates mechanisms to perform a so-called *complexity formalization*, classifying many actions that are currently done by the user and building a framework in which these complexities can be delegated to the runtime system. The delegation of these decisions is already a step forward to next generation of programming models seeking performance, expressivity, programmability and portability.

XXX LISTINGS

### Resumen

La presente tesis doctoral propone el diseño e implementación de un nuevo modelo de programación basado en relajaciones de ejecución y enfocado al ámbito de la Computación Paralela de Altas Prestaciones. Concretamente, los objetivos principales de la tesis son:

- 1. Abogar por una metodología de desarrollo en la que el usuario define las unidades básicas de cómputo (tareas), junto con un conjunto de *relajaciones* en, posiblemente, múltiples dimensiones. Estas relajaciones se traducirán, en tiempo de ejecución, en oportunidades expandidas (y complejas) de planificación en función de la arquitectura subyacente, impactando así en métricas como rendimiento o consumo energético.

- 2. Abstraer al usuario de la complejidad del hardware subyacente, delegando la correcta explotación de dichas posibilidades de planificación expandidas a un componente software de sistema (típicamente conocido como runtime). Dicho software, dotado de conocimiento tanto de las características estáticas de la arquitectura subyacente como del estado puntual de la misma en el momento de la ejecución, explotará las combinaciones consideradas óptimas de entre las relajaciones propuestas por el usuario para cada tarea lista para set ejecutada.

- 3. Extender dicha abstracción para describir tanto sistemas de cómputo, en forma de jerarquías de ejecutores y alojadores de memoria que en último término describen una arquitectura de cómputo heterogénea, como aplicaciones, en forma de un conjunto de tareas interrelacionadas. Además, las relaciones entre ejecutores y tareas son clasificadas en una nueva taxonomía tarea-ejecutor, la cual motiva frontends de programación HPC sin ambiguedad basados en la clasificación STSE, Single Task Single Executor, separada de backends runtime totalmente automatizados.

- 4. Proponer un nuevo modelo de programación (STEEL) basado en la clasificación STSE que aglutine ciertas características consideradas básicas de cara al éxito de los futuros modelos de programación basados en tareas: rendimiento, facilidad de composición, expresividad e interfaces no permisivos ante fallos.

- 5. Especificar una API que dé soporte al modelo de programación, así como una implementación *runtime* del mismo aprovechando técnicas y paradigmas soportados en el lenguaje C++ de última generación, e ilustrar su uso, flexibilidad e impacto en el rendimiento a través de ejemplos y casos de uso sencillos.

La metodología que se propugna aboga por una clara y estricta separación de conceptos entre los actores básicos que componen una ejecución paralela: usuario / código y *hardware* subyacente. Este tipo de abstracciones permite delegar el conocimiento experto desde el usuario hacia el *software* de sistema, proporcionando así mecanismos para mecanizar y automatizar su optimización, y adaptar su rendimiento a la arquitectura paralela sobre la que se instanciarán los códigos.

Desde este punto de vista, la tesis diseña, implementa y valida mecanismos para llevar a cabo una *formalización de la complejidad* inherente a la programación paralela heterogénea, clasificando aquellas acciones que en la actualidad se llevan a cabo por parte del usuario en el proceso de desarrollo y optimización de código, y proporcionando un marco de trabajo en el que dicha complejidad puede ser delegada, de forma eficiente y consistente, a un *runtime*.

xxxii LISTINGS

Against the sneakiest undead lock and hideous invisible bugs who hide and never talk.

Through the fire in the chip and bursts in the heap that oblige to swap.

Let's stand composed with strongly typed shields. Let's relax the parallel demon coding spells of STEEL.

#### 1.1 Fundamentals

In a world dominated by Information Technology and Computer Science, computers have been transforming the society since their first physical implementations at the beginning of the previous century, and it is likely that this transformation is not going to end anytime soon. Since the advent of programmable computers, High-performance Parallel Computing (HPC) in particular, and computer simulation in general, have played a crucial role supporting new developments in science and engineering, driving technology and industry toward efficiency, and pushing science to greater levels of knowledge in virtually all disciplines.

However, as it occurs in any technological human discipline, there are still a plethora of open problems in HPC that need to be solved in order to keep extending its applicability to increasingly important scientific and engineering challenges.

#### 1.1.1 Challenges in High-performance Parallel Computing

Since the advent of silicon-based transistors, hardware advances based on physical features – miniaturization, increasing transistor count and higher clock frequencies— and technical advances –branch prediction, deep pipelines, speculative and out-of-order execution, deep cache hierarchies, vector units— [69] managed to keep an exponential growth in microprocessor performance for several decades, while respecting a purely sequential programming paradigm. This trend started to show signs of stagnation when heat dissipation and energy efficiency in microprocessors became an ever-growing problem. This *power wall* [11] problem was circumvented by architects by means of parallelism, rather than clock frequency, which led to the popularization of *parallel* on-chip microprocessors.

However, this *multicore revolution* brought its own set of problems to solve. In contrast to the previous *gold sequential era* in which a two-fold increase of processing performance was just a matter of waiting 18 months [132], parallel processing came with its own limitations with regard to *applicability* and *development productivity*. Specifically, efficient parallel computation trivially requires (*i*) *application parallelizability* –i.e., the application must inherently expose a certain amount *divisible* work that can be computed independently (quantifiable with the Amdahl's Law [71])–, and (*ii*) parallel programming knowledge –i.e., the programmer must be able to partition and synchronize the workload– needed for the execution performance to scale with the number of processing cores.

There is little that can be done regarding the parallelizability of an application, as it is an

intrinsic property that cannot be circumvented. With respect to the latter requirement it is not a surprise that parallel programming is hard, and generally involves a thorough design that requires an advanced knowledge of (i) parallel actors (threads and processes) and (ii) synchronization tools (locks, mutexes, condition variables, barriers, latches, futures), to avoid generally hard to debug errors (deadlocks and livelocks) and race conditions.

Moreover, parallel architectures entail an additional (and typically harder to achieve) *parallel performance* requirement, which is not whatsoever guaranteed even though program correctness is attained. Parallel performance tuning typically requires an advanced knowledge about both the underlying parallel architecture and the abstraction layers in between the source code and the actual machine code that is being executed in the processor.

In addition, not only the sheer size of the underlying parallel platform makes the performance problem even harder to attain, but also its complexity in terms of deep, wide and distributed memory hierarchies, and parallel/heterogeneous processors interconnected in complex topologies. In particular, the *memory wall* problem [158] –illustrated by the fact that in many applications the data movement is a few orders of magnitude more expensive (in terms of time and energy) than computation— is aggravated in distributed systems, making it one of the major issues that limit the scalability and performance of modern large-scale applications running on high-end supercomputers.

Soon after the multicore chips became pervasive in practically every device, the increasing hardware advances in GPU technology driven by entertainment industry (gaming and 3D animation), led to the generalization of these previously domain-specific hardware architectures into a more general-purpose-oriented graphics processors. Nowadays, partly thanks to the development of programming models, interfaces and open standards designed to target them, and also thanks to its paramount performance-per-watt efficiency, general-purpose GPUs are already a common component in any parallel system used for HPC purposes. In a broader sense, and in analogy with the *multicore revolution*, the *heterogeneous revolution* was coined as other domain-specific hardware, apart from GPUs, like FPGAs, DSPs and TPUs, gained popularity in HPC applications and systems.

Motivated by the demands of large applications dealing with climate modeling, materials science, energy research, astrophysical research, data analytics, or medical research applied to drug discovery and protein folding, future exa-scale supercomputers aim at delivering a sustained performance peak of 10<sup>18</sup> floating point operations per second with power demands up to 20 MW [48]. In order to attain such numbers, the so-called exa-scale challenges require hardware and software innovations to enhance *performance/scalability*, *energy efficiency*, *programmability* and *resiliency*. With regard to execution performance, scalability and programmability, exa-scale computers will demand unprecedented levels of *scheduling complexity*: hierarchical and massive levels of parallelism will need to be automatically managed, and data movement will require a coherent orchestration across multiple and deep cache hierarchies. Moreover, the failure rate probability due to soft and hard errors is expected to rise to levels that may cause exa-scale executions not only be expensive, but also impractical. For this reason, *execution resiliency* is being considered as a topic with major research interest [25, 134].

#### 1.1.2 Addressing complexity through abstractions and hierarchies

Abstraction is used in this thesis as a mechanism to hide the complexity by means of *modeling* and *simplification*, aiming at generality at a cost of neglecting the details, when needed. Computer Science is a discipline deeply rooted in abstraction, and its success in society has partly derived from the engineering effort of stacking multiple levels of abstraction layers in deep hierarchies, so that highly abstract concepts in the human mind can be consistently instantiated as purely physical processes that represent those ideas.

Regarding the challenges in parallel programming, it is worth noting that several levels of parallelism are commonly handled in user-oriented applications running on devices such as smart-

phones, tables and laptops. For instance, microprocessor pipelining, vector units, and compiler technology can automatically enable instruction-level and data-level parallelism from a purely sequential program –i.e., the computer user does not need to learn parallel programming to benefit from it through faster and more responsive applications—. Also, modern processors provide support for automatic and efficient memory management mechanisms in a multicore context with deep memory hierarchies, not demanding the user to learn cache-coherent protocols. Similarly, in a higher level, Operating Systems hide system-wide management work to the user while exposing a simplified layer to developers to access some functionalities such as I/O, networking, file operations or memory management. All of these examples show how computers have evolved from expert-oriented machines to pervasive and essential working tools for non computer experts.

From the point of view of application and software developer experts, a plethora of standardized and general-purpose programming languages have been designed according to an abstract computation machine. Downstream, during compilation, a program is translated into more specific microarchitecture-dependent machine instructions. Syntactic rules of a programming language serve as a *contract* to be satisfied by both the programmer and the language implementation in the form of a compiler and possibly an underlying runtime, imposing restrictions to the user so that only syntactically-legal expressions are translated into an actual program. High-level languages are characterized by providing very clear, simple and readable syntactic rules while hiding details of the computer architecture. However, high-abstractions usually come at the price of lack of control and reduced performance.

Finally, from the point of view of parallel application developers, recalling the parallel programming challenges and the role of abstractions, this thesis goes in the same direction to which computer technology is going: toward greater levels of automatization and abstraction, to drive HPC in particular, and parallel programming in general, toward being a technology usable to non-HPC experts.

### 1.2 Programmability in HPC

In essence, Computer Engineering aims at automating some form of *information processing* –or in other words, it addresses the problem of how efficiently automatize *computation* under limited resources–. As mentioned, the percolation of computers into all areas of modern society has not only been based on the exponential growth in computation performance experienced during four decades (i.e., a *hardware* achievement), but also on the simplification of computer interfaces (i.e., a *software* achievement).

In particular, the impact of High-performance Computing has become paramount in many areas of science and engineering. Currently, it is a very specialized field with direct application in a plethora of disciplines. However, HPC users should not be experts in HPC, nor in the specificity of hardware or the underlying software infrastructure; as a technology meant to be used in such a diverse set of disciplines should abstract away the complexities of both aspects. Ideally, focusing on the programmability/portability perspective, a user of a parallel/heterogeneous resource should be exclusively in charge of specifying the input configuration and/or data of the problem and let the system seamlessly map the computation to the underlying parallel platform.

This is far from being the case in general HPC applications, in which computations are typically coupled in complex ways forming irregular parallel patterns, generating load-imbalanced executions, lack of efficiency, poor scaling and portability problems. Modern parallel programming models, languages, patterns and paradigms have been proposed during the last decades to tackle these issues, suggesting runtime-based solutions —in which some of the programming burden is shifted from the user to an automatic runtime system— as potentially ideal to boost performance while reducing development effort.

The following sections expose a non-comprehensive exposition of the characteristics of some programming paradigms, models, systems and runtimes. Some key characteristics, challenges,

appealing trends and limitations are presented to contextualize the developments presented in the following chapters.

#### 1.2.1 Paradigms

In this section, the *imperative* programming paradigm (in which *object-oriented* and *procedural* sub-paradigms are commonly included) is put in contrast with the *functional* paradigm (which is commonly included in the class of *declarative* paradigms), and their appeal and limitations are addressed under a HPC perspective.

#### 1.2.1.1 Functional paradigm

Lambda calculus (or  $\lambda$ -calculus) was developed as an alternative model of computation to the Turing machine model, and it focuses on *function abstraction* to model general computations, in contrast to the *state manipulation* of Turing machines [35, 36]. In relation to programming,  $\lambda$ -calculus is the theoretical cornerstone of the functional programming paradigm, implemented in many industry-standard popular languages such as C++ [138], Go [49], Scala [117], Clojure [70], Rust [106], Haskell [80], ML [110] and Erlang [28]. Also, other mathematical frameworks such as Type Theory [144] and Category Theory [96] have greatly influenced the design and implementation of modern functional programming languages toward a more clear, composable, verifiable and robust development style [109].

From a *closer-to-programming* perspective, there is a set of properties that characterize modern functional programming philosophy (see [42, 151]), which are briefly developed next.

**Pure function abstraction and referential transparency.** Functions without side-effects are referred as *pure*, so their unique effect is its return value. By favoring a programming style based on function purity, dependency tracking and state encapsulation becomes natural, while code readability is also improved. These characteristics are of great appeal in parallel programming.

Function purity will be repeatedly addressed in the developments of this thesis, also in a *less*-strict form, when considering third-party software interoperability. Specifically, a function may inter-operate with a third-party program or library whose functionality –and state– may be altered. Since its state may be hidden or *not observable* from the caller, it will be assumed that the third-party program is *well-behaved enough* to keep considering *purity* de facto preserved (i.e., the called third-party function is properly and safely encapsulating its state so that it cannot affect whatsoever the state of the caller).

In addition, following  $\lambda$ -calulus ideas, functions are considered *first-class citizens*, in the sense that functions are mere values of a certain type that can be passed to other functions.

Function purity yields *referential transparency* property, which states that a function outputs the same result regardless of the context. This permits the use of *result memoization* in runtime implementations of functional languages, by which the result of a function call is cached to prevent function recomputation.

**Strong typing.** Strongly-typed languages enforce strict rules in terms of what can be translated into actual machine code. Motivated behind theoretical frameworks of Type Theory and Category Theory, any data object belong to a specific abstract type that encompasses a finite or infinite set of values. Types are also possibly endowed with properties and constraints from which more complex *compositional* rules (to form composite types) and *transformation* rules (that limits the set of all functions able to map values from one type to the other) are derived. Strongly-typed languages favors robust interfaces, facilitates program verification, and enables the application of logic rules to mathematically prove program correctness.

**Immutable data objects.** Functional programming language implementations encourages –and even enforces– the use of immutable data objects / structures. Immutable data forbids the existence of shared and mutable states across parallel actors (e.g., threads or processes), thus thread-safety is naturally preserved and the chances for unwanted data races are greatly reduced.

The inexistence of mutable data does not necessarily imply that expensive copies of data objects are needed. With this regard, implementations of purely functional languages may employ internal mechanisms to store only the data differences (or *state changes*, or *deltas*) to allow memory-friendly run-time data transformations, ultimately yielding programs with less memory footprint.

**Implicit control flow and lazy evaluation.** Declarative-like paradigms (in which functional paradigm is commonly included), encourages a style of programming in which the properties of the different agents forming the program (e.g., data objects or functions) are declared. Loosely speaking, it favors a model of execution in which the computational needs are *pulled on demand* as the execution proceeds. In practice, it usually implies a clear separation between what the programmer expresses in the code and what is actually being computed. *Lazy evaluation* refers to function evaluation only if its result is needed, and it also permits to express infinite structures in computer programs regardless of the *finitude* of computers.

In relation to concurrency and parallelism, the previous ideas are reflected into an undefined execution order in general, and a *relaxed* (i.e., opposite to *user-specified*) parallel execution.

**Iteration via recursion.** Contrary to imperative-like languages that use loops to implement iteration —which requires some form of state in the form of a counter—, functional programming implements iteration by means of *recursion*. In practice, compiler and runtime implementations of functional languages implement *tail recursion* techniques to avoid an overflow of the stack in situations with deep recursions.

**Monad pattern.** Monads in Category Theory were applied to programming languages with the goal of formalizing general side-effectful computations within a functional programming context [111]. Applied to programming, monadic patterns are in essence a *generic glue* that enables function composition in a scalable and generic way, providing a framework to develop software handling side-effects without sacrificing functional purity. Several functional programming languages provide the most common built-in monads and also let the user to implement more complex or application-specific monadic patterns.

#### 1.2.1.2 Imperative paradigm

Imperative languages were first implemented matching actual hardware architecture implementations. In essence, the programmer writes commands that result into a program state change, which directly influences state change of the physical machine –i.e., the program commands closely resemble what the hardware actually executes—. Contrary to the functional paradigm, modularization, composability and separation of concerns are important *but not primary*, hence favoring *full control* of what the underlying hardware actually does. Some of the features of the imperative-like paradigm (specially in relation to low-level and non-interpreted imperative languages) are summarized next.

**Non-strict encapsulation for full control of program state.** Motivated by the need of modularization and composability requirements, mandatory in any mid or large-scale software projects, a set of *subparadigms* like *structured*, *procedural*, *modular* and *object-oriented* were distinguished under the umbrella of the *imperative* paradigm, and they differentiate with respect to the different

ways in which expressed computation is encapsulated (i.e., in terms of subroutines, modules, objects, etc.). In particular, object-oriented programming aroused as an approach for enhanced code reusability and modularization over structured and procedural paradigms, by means of encapsulation, inheritance and polymorphism.

In essence, imperative languages provide language semantics encouraging some form of *mild* encapsulation without sacrificing control, in the sense that high levels of modularization and separation of concerns can be achieved, yet full control over the program state is still available to the programmer.

**Execution is mainly user-driven, control flow is explicit.** Contrary to the declarative-style of the functional paradigm, the imperative paradigm conforms a programming style based on user-specified *commands* that explicitly define how the underlying execution is performed at run-time. Despite its proximity to the actual hardware architecture, there are still several abstraction layers that separate the computer code and the actual runtime execution. One of these layers is the compilation process, and some knowledge regarding compilation is usually mandatory to achieve high-performance executions.

With this regard, imperative languages are usually easier to learn and less abstract than functional languages, and compiler technology has been greatly improved to close the gap between simple and high-level imperative codes and high-performance runtime executions. Compiler-targeted commands aiming at performance such as inlining, loop unrolling, pre-compiled tables, and cache-friendly data layouts / memory allocations, are frequently employed by implementers in compiled / non-interpreted languages like C or Fortran.

**Fine-grained memory management.** Memory management – in the form of explicit memory allocations/deallocations and alignment, data layout design, and cache-aware data structures, is usually required when programming high-performance applications in imperative and low-level programming languages. Languages of this kind may also provide a memory model that abstracts the memory model implemented in hardware, so it is usually desirable for the programmer to know the specifications of this model, specially in concurrent and parallel applications meant to run on cache-coherent multiprocessing architectures.

#### 1.2.1.3 Generic paradigm