## Procesamiento de imágenes en vehículos autónomos sobre un RISC-V con acelerador Image processing in autonomous vehicles on a RISC-V with accelerator

### Trabajo de Fin de Máster Curso 2021–2022

Autora María José Belda Beneyto

Directores Katzalin Olcoz Herrero Fernando Castro Rodríguez

Máster en Internet de las Cosas Facultad de Informática Universidad Complutense de Madrid

# Procesamiento de imágenes en vehículos autónomos sobre un RISC-V con acelerador

Image processing in autonomous vehicles on a RISC-V with accelerator

Trabajo de Fin de Máster en Internet de las Cosas Departamento de Arquitectura de Computadores Y Automática

> Autora María José Belda Beneyto

Directores Katzalin Olcoz Herrero Fernando Castro Rodríguez

Convocatoria: Enero 2022 Calificación: 9.5

Máster en Internet de las Cosas Facultad de Informática Universidad Complutense de Madrid

7 de febrero de 2022

## Autorización de difusión

El abajo firmante, matriculado en el Máster en Internet de las Cosas de la Facultad de Informática, autoriza a la Universidad Complutense de Madrid (UCM) a difundir y utilizar con fines académicos, no comerciales y mencionando expresamente a su autor el presente Trabajo Fin de Máster: "Procesamiento de imágenes en vehículos autónomos sobre un RISC-V con acelerador", realizado durante el curso académico 2021-2022 bajo la dirección de Katzalin Olcoz Herrero y Fernando Castro Rodríguez en el Departamento de Arquitectura de Computadores Y Automática, y a la Biblioteca de la UCM a depositarlo en el Archivo Institucional E-Prints Complutense con el objeto de incrementar la difusión, uso e impacto del trabajo en Internet y garantizar su preservación y acceso a largo plazo.

María José Belda Beneyto

7 de febrero de 2022

# Agradecimientos

Este trabajo no habría sido posible llevarlo a cabo exitosamente sin la inestimable ayuda de las personas citadas a continuación.

En primer lugar, agradecer a Katzalin y Fernando, mis directores, todo el esfuerzo y las horas que han dedicado a resolver los obstáculos en forma de errores y falta de información con los que hemos topado. Así como los ánimos que siempre estaban dispuestos a darme. También agradecer al profesor Carlos García Sánchez su aportación de los códigos de tratamiento de imágenes y su paciencia al explicarnos su funcionamiento y contestar nuestras dudas y peticiones.

En segundo lugar, a mis padres y mi pareja, piezas fundamentales de mi día a día y mi bienestar, y apoyos a los que recurrir cuando no veía la luz al final del túnel. También, a mi familia y amigos de siempre, que por más kilómetros que nos separen siempre nos reencontramos cada poco tiempo para darme ánimos y ganas de seguir en la capital.

Finalmente, agradecer a los amigos que me ha dado mi trayectoria universitaria que son un ejemplo a seguir y siempre tienen un ratito en las noches duras para dejarme ganar al Catán o hacerme reír encontrando huecos "Aquí, donde estoy yo".

# Resumen

### Procesamiento de imágenes en vehículos autónomos sobre un RISC-V con acelerador

La conducción autónoma en vehículos terrestres es un campo emergente en el que el Internet de las Cosas (IoT) juega un papel importante en la actualidad. El correcto funcionamiento de este tipo de conducción sin intervención humana requiere el continuo procesamiento de las imágenes que capta el vehículo durante su viaje con la finalidad de determinar de modo preciso la trayectoria a seguir así como la posible presencia de obstáculos en la misma. Dada la elevada cantidad de datos a procesar y la necesaria respuesta del vehículo en tiempo real, es necesaria la exploración de nuevas arquitecturas que permitan la realización de estas tareas de un modo eficiente tanto en términos de latencia como de consumo energético. En este trabajo se propone el diseño y se realiza la evaluación de algunas arquitecturas para este fin en las que se hace uso de procesadores que utilizan el repertorio de instrucciones RISC-V así como de aceleradores y coprocesadores de propósito específico destinados a optimizar la realización de las tareas propias del vehículo autónomo. Para ello se hace uso de una amplia colección de herramientas, como Chipyard, FireSim FireMarshal y Amazon Web Services, necesarias para generar los diseños hardware específicos y ejecutar sobre ellos una aplicación de reconocimiento de líneas en imágenes como las empleadas en los vehículos de conducción autónoma.

### Palabras clave

Conducción autónoma, detección de líneas, acelerador, coprocesador, RISC-V, IoT, Hwacha, Gemmini, FireSim

## Abstract

# Image processing in autonomous vehicles on a RISC-V with accelerator

Currently, autonomous driving in land vehicles is an emerging research field where Internet of Things (IoT) plays a significant role. The right operation of this kind of driving – where no human intervention exists—, requires the continuous processing of the images that the vehicle collects as it travels, aimed to accurately determine the trajectory it must follow as well as the potential presence of obstacles. Given the huge amount of data to be processed and the real-time response required in the vehicle, the exploration of new architectures that allow the implementation of these tasks in an efficient fashion, both in terms of latency and energy consumption, is nowadays an open challenge. In this work several architectures, oriented to these goals, are proposed and evaluated. These architectures employ RISC-V processors and also specific-domain accelerators and coprocessors, aimed to optimize the tasks involving the autonomous vehicle. For this purpose, a wide toolset is used, including Chipyard, FireSim FireMarshal and Amazon Web Services. All of them make it possible to generate specific hardware designs and to execute a line-detection application as that employed in autonomous vehicles.

### Keywords

Autonomous driving, line detection, accelerator, coprocessor, RISC-V, IoT, Hwacha, Gemmini, FireSim

# Índice

| 1. | Intr | roducción                            | 1          |

|----|------|--------------------------------------|------------|

|    | 1.1. | Motivación                           | 2          |

|    | 1.2. | Objetivos                            | 2          |

|    | 1.3. | Plan de trabajo                      | 3          |

| 2. | Esta | ado de la Cuestión                   | 5          |

|    | 2.1. | RISC-V                               | 5          |

|    |      | 2.1.1. Cores                         | 6          |

|    |      | 2.1.2. Aceleradores y coprocesadores | 8          |

|    | 2.2. | Herramientas                         | 12         |

|    |      | 2.2.1. Chipyard                      | 12         |

|    |      | 2.2.2. FireSim                       | 15         |

|    |      | 2.2.3. FireMarshal                   | 15         |

|    |      | 2.2.4. Amazon Web Services           | 16         |

| 3. | Algo | oritmos de tratamiento de imágenes   | 17         |

|    | 3.1. | Algoritmo de Canny                   | 17         |

|    | 3.2. | Transformada de Hough                | 19         |

|    | 3.3. | Detección de líneas                  | 20         |

|    | 3.4. | Modificación de los tipos de datos   | 20         |

|    | 3.5. | Profiling del código                 | 21         |

|    | 3.6. | Vectorización del código             | 23         |

| 4. | Res  | ultados                              | <b>2</b> 5 |

|           | 4.1.                                                                                                                                  | Generación de diseños de arquitecturas                                                                                             |                                                                                                                                                                                         |    |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|           | 4.2.                                                                                                                                  | Arquit                                                                                                                             | ecturas generadas                                                                                                                                                                       | 27 |  |  |  |  |

|           | 4.3.                                                                                                                                  | Genera                                                                                                                             | Generación de los $workload$                                                                                                                                                            |    |  |  |  |  |

|           | 4.4.                                                                                                                                  | Workle                                                                                                                             | Workloads generados                                                                                                                                                                     |    |  |  |  |  |

|           | 4.5.                                                                                                                                  | Ejecuc                                                                                                                             | ción de una simulación                                                                                                                                                                  | 40 |  |  |  |  |

|           | 4.6.                                                                                                                                  | Experi                                                                                                                             | imentos                                                                                                                                                                                 | 45 |  |  |  |  |

|           |                                                                                                                                       | 4.6.1. Experimento 1: Ejecución de una aplicación multihilo sobre arquitecturas unicore y dualcore con el procesador Rocket y Boom |                                                                                                                                                                                         |    |  |  |  |  |

|           | 4.6.2. Experimento 2: Ejecución de la aplicación de detección de líneas sobre arquitecturas unicore con el procesador Rocket o Boom 4 |                                                                                                                                    |                                                                                                                                                                                         |    |  |  |  |  |

|           |                                                                                                                                       | 4.6.3.                                                                                                                             | Experimento 3: Ejecución de la aplicación de detección de líneas sobre arquitecturas heterogéneas con el procesador Rocket o Boom y el acelerador de multiplicación de matrices Gemmini | 47 |  |  |  |  |

| <b>5.</b> | Con                                                                                                                                   | clusio                                                                                                                             | nes y Trabajo Futuro                                                                                                                                                                    | 49 |  |  |  |  |

|           | 5.1.                                                                                                                                  | Conclu                                                                                                                             | asiones                                                                                                                                                                                 | 49 |  |  |  |  |

|           | 5.2.                                                                                                                                  | Traba                                                                                                                              | jo futuro                                                                                                                                                                               | 50 |  |  |  |  |

| 6.        | Intr                                                                                                                                  | oducti                                                                                                                             | on                                                                                                                                                                                      | 51 |  |  |  |  |

|           | 6.1.                                                                                                                                  | Motiva                                                                                                                             | ation                                                                                                                                                                                   | 52 |  |  |  |  |

|           | 6.2.                                                                                                                                  | Object                                                                                                                             | tives                                                                                                                                                                                   | 52 |  |  |  |  |

|           | 6.3.                                                                                                                                  | Workp                                                                                                                              | olan                                                                                                                                                                                    | 53 |  |  |  |  |

| 7.        | Con                                                                                                                                   | clusio                                                                                                                             | ns and Future Work                                                                                                                                                                      | 55 |  |  |  |  |

|           | 7.1.                                                                                                                                  | Conclu                                                                                                                             | isions                                                                                                                                                                                  | 55 |  |  |  |  |

|           | 7.2.                                                                                                                                  | Future                                                                                                                             | e work                                                                                                                                                                                  | 56 |  |  |  |  |

| Bi        | bliog                                                                                                                                 | rafía                                                                                                                              |                                                                                                                                                                                         | 57 |  |  |  |  |

# Índice de figuras

| 2.1.  | Pipeline del core Rocket [3]                                         | 6  |

|-------|----------------------------------------------------------------------|----|

| 2.2.  | Microarquitectura del core Rocket [36]                               | 7  |

| 2.3.  | Pipeline detallado del core Boom. [38]                               | 9  |

| 2.4.  | Pipeline del core Boom en sus distintas versiones [38]               | 10 |

| 2.5.  | Registros del coprocesador Hwacha [27]                               | 10 |

| 2.6.  | Posibles configuraciones de los registros vectoriales de Hwacha [34] | 11 |

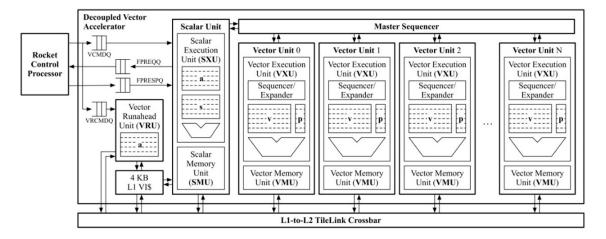

| 2.7.  | Microarquitectura del coprocesador Hwacha [34]                       | 11 |

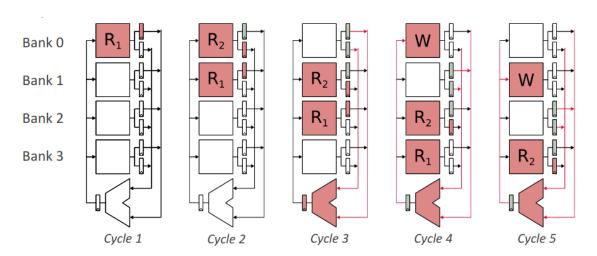

| 2.8.  | Microarquitectura de los vectores sistólicos de Hwacha [34]          | 12 |

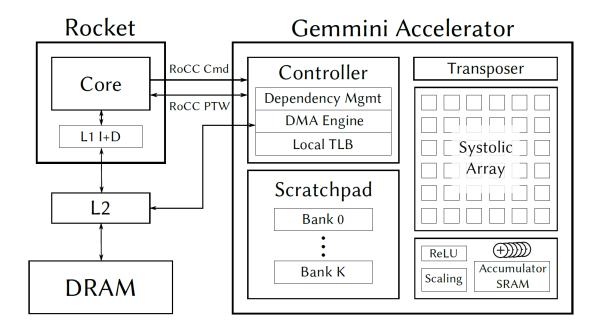

| 2.9.  | Arquitectura del acelerador Gemmini [15]                             | 13 |

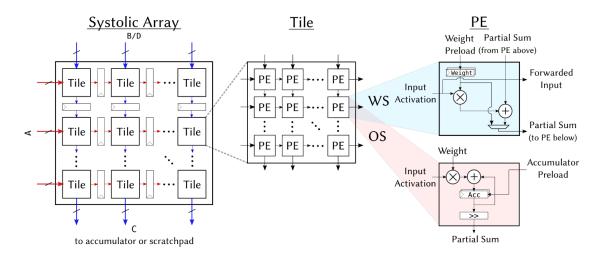

| 2.10. | Arquitectura del vector sistólico de Gemmini [15]                    | 13 |

| 2.11. | Componentes de Chipyard [28]                                         | 14 |

| 2.12. | Flujo de ejecución en Chipyard [28]                                  | 14 |

| 2.13. | Infraestructura de FireSim [18]                                      | 16 |

| 3.1.  | Ejemplo de detección de bordes con el algoritmo de Canny             | 18 |

| 3.2.  | Imagen de salida con las líneas detectadas en rojo                   | 21 |

| 3.3.  | Resultados de las ejecuciones de los distintos códigos               | 22 |

# Índice de tablas

| 3.1. | Profiling del código completo por etapas                                                                                 | 22 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

| 3.2. | Profiling del código sin imagen de salida por etapas                                                                     | 22 |

| 3.3. | Profiling de la etapa 2 por fases                                                                                        | 23 |

| 4.1. | Resultados de tiempo, ciclos e instrucciones retiradas en el experimento multihilo para $N\_times=1.$                    | 46 |

| 4.2. | Resultados de tiempo, ciclos e instrucciones retiradas en el experimento multihilo para $N\_times=4.$                    | 46 |

| 4.3. | Resultados de tiempo, ciclos e instrucciones retiradas en el experimento multihilo para $N\_times=8.$                    | 47 |

| 4.4. | Resultados de tiempo, ciclos e instrucciones retiradas en la simulación del algoritmo de detección de líneas sobre Linux | 48 |

| 4.5. | Resultados de tiempo y ciclos en la simulación del algoritmo de detección de lineas adaptado para Gemmini sobre Linux    | 48 |

## Introducción

En este capítulo se va a realizar una pequeña introducción al contexto en el que se desarrolla este trabajo y las motivaciones que nos llevan a realizarlo.

En la era tecnológica en la que vivimos, nos esforzamos cada día en conseguir que todas las tareas habituales sean lo más automáticas posible para dedicar nuestros esfuerzos a otras actividades. Es por esto que surge el Internet de las Cosas (IoT), pues necesitamos nuevas tecnologías para diseñar estos sistemas, habitualmente empotrados, que necesitan un equilibrio entre el bajo consumo y el alto rendimiento.

Algunas áreas han sido ya ampliamente estudiadas, como la automatización de las cadenas de producción o la domótica, pues ya es habitual encontrar casas completamente domotizadas que nos facilitan el día a día. Sin embargo, en el sector de transporte terrestre aún no contamos con estas novedades.

En este ámbito, el futuro parece indicar que también tendremos un modelo de transporte inteligente, conectado y autónomo, que haga uso de la inteligencia artificial. Si ahondamos en la tecnología que se utilizará, nos damos cuenta de que reúne diversas áreas. Por un lado, se necesitará una gran potencia de cómputo para ejecutar muchas operaciones simultáneas que se solapan en la conducción, por ejemplo la detección de las líneas de la carretera para determinar la trayectoria y la detección de obstáculos u otros vehículos, así como el reconocimiento de señales de tráfico.

Estas acciones son críticas para la seguridad en la conducción, por tanto, además de necesitar una gran capacidad de cómputo, necesitan ejecutarse a bordo, pues aún con una buena conexión a la red, la latencia sería demasiado grande. Sin embargo, otras operaciones como el seguimiento GPS y la extracción de datos de tráfico a partir del mismo, sí que se pueden enviar y procesar en la nube, ya que no son críticas o no requieren de inmediatez.

Dada la cantidad de operaciones críticas y simultáneas que se deben ejecutar para obtener un buen sistema de conducción autónoma, necesitamos diseñar SoCs empotrados eficientes y seguros [6] con distintos procesadores y aceleradores de carácter específico integrados en un mismo sistema.

### 1.1. Motivación

Este trabajo se encuadra en la intersección entre el ámbito IoT y el ámbito de los vehículos autónomos. En particular, los vehículos autónomos necesitan ser capaces de reconocer las líneas que delimitan los carriles en las calzadas para calcular la trayectoria deseada e implementar la conducción autónoma.

Esto se traduce en un problema de detección de líneas en imágenes que habitualmente se resuelve con redes neuronales. Ahora bien, las redes neuronales se basan en aplicar una matriz de pesos a una matriz de datos, es decir, en la multiplicación de matrices. Las multiplicaciones de matrices son conocidas por su costosa ejecución, aún mayor cuándo trabajamos con imágenes de alta resolución, ya que nos ofrecen una gran cantidad de píxeles.

Por tanto, en este trabajo, se pretende resolver el problema de la gran cantidad de cómputo desde un punto de vista arquitectónico. En particular, se van a diseñar distintas arquitecturas homogéneas y heterogéneas compuestas por los procesadores de ámbito general *Rocket* y *Boom* y los aceleradores *Gemmini* y *Hwacha* de propósito específico para la multiplicación de matrices y para el procesamiento vectorial, respectivamente.

Esta arquitectura estará diseñada para optimizar la ejecución de una aplicación de reconocimiento de líneas en imágenes, cuya ejecución en un escenario real sería a bordo de un vehículo autónomo. En esta ocasión, la aplicación hará uso de algoritmos conocidos para el procesamiento de imágenes en lugar de implementar una red neuronal para simplificar el código utilizado.

Tanto los procesadores como el acelerador y el coprocesador vectorial elegidos utilizan el repertorio RISC-V junto con algunas instrucciones personalizadas para el acelerador y el coprocesador. Se eligen ambos por ser RISC-V un repertorio de código libre, así como las herramientas que se encuentran a disposición para generar arquitecturas y realizar simulaciones. Además, las herramientas de generación de arquitecturas como Chipyard o FireSim que se van a utilizar, permiten modificar componentes de la arquitectura en detalle de forma sencilla y cómoda. Así, se pueden añadir o eliminar módulos para adaptar la arquitectura el máximo posible al caso de uso y conseguir el deseado equilibrio entre rendimiento y consumo que se persigue en IoT.

## 1.2. Objetivos

A continuación, vamos a describir los objetivos que se persiguen con este trabajo. En primer lugar, se persigue explorar el ecosistema RISC-V, tanto el repertorio de instrucciones como los cores, las opciones de hardware de propósito específico y las herramientas software para generar diseños hardware que se encuentran a disposición del usuario.

Del los primeros objetivo se desprende la necesidad de explorar las arquitecturas heterogéneas, para familiarizarnos con el uso de las instrucciones específicas que se añaden al repertorio RISC-V con algunos módulos y para poder conectar un procesador y un hardware de propósito específico en un mismo diseño hardware.

También, se persigue relacionarnos con el mundo de los vehículos autónomos, en particular, con el tratamiento de imágenes dad su importancia en dicho contexto. En este

trabajo, nos centraremos en la detección de líneas en imágenes, ya que es una tecnología cada vez más presente en los vehículos actuales así como en los prototipos de vehículos autónomos. Para ello, nos familiarizaremos con los algoritmos de tratamiento de imágenes que se utilizan en este escenario: el algoritmo de Canny y la transformada de Hough.

Todo esto nos lleva a cumplir nuestro objetivo final, que es conseguir una plataforma en la que podamos ejecutar aplicaciones personalizadas sobre arquitecturas diseñadas adhoc para dichas aplicaciones y conseguir en la ejecución de estas aplicaciones un gran rendimiento a un bajo coste energético, ya que la tecnología embarcada en un vehículo autónomo debe ser rápida pero barata en términos energéticos.

### 1.3. Plan de trabajo

El plan de trabajo que vamos a seguir para completar los objetivos que se han planteado empieza por realizar un primer acercamiento al código de tratamiento de imágenes y detectar pequeñas mejoras que se puedan aplicar de forma sencilla, como utilizar las variables de tamaño más pequeño que se adapten a la situación. A continuación, se realizará un estudio del rendimiento del código de tratamiento de imágenes mediante un *profiling* para averiguar en qué partes se consume un mayor tiempo y, por tanto, más recursos energéticos también. Así, sabremos qué operaciones debemos ejecutar a nivel hardware en la arquitectura.

A continuación, realizaremos una exhaustiva investigación de los procesadores, coprocesadores y aceleradores que actualmente implementan el repertorio de instrucciones RISC-V y son de código libre y abierto, para elegir aquellos que se adapten mejor a las necesidades de nuestra aplicación.

Una vez decidido el hardware necesario, utilizaremos los entornos de desarrollo Chipyard y FireSim para diseñar las arquitecturas que creamos más adecuadas y, posteriormente, generar imágenes de esas arquitecturas para volcarlas sobre una FPGA. Además, compilaremos el código de nuestra aplicación principal de detección de líneas utilizando el compilador cruzado de RISC-V y otras herramientas a nuestro alcance para finalmente, simular la ejecución del programa principal de detección de líneas sobre dichas arquitecturas.

Finalmente, discutiremos los resultados obtenidos en las ejecuciones de distintas aplicaciones sobre distintas arquitecturas con el objetivo de concluir qué arquitectura se adapta mejor a nuestro caso de uso.

A continuación, en el siguiente capítulo de este trabajo se detallarán las características principales tanto del hardware elegido como de los entornos de desarrollo que se van a utilizar. En capítulos sucesivos, se presentarán los algoritmos de procesamiento utilizados, y los resultados obtenidos. El trabajo finaliza con la exposición de las conclusiones derivadas de la realización del mismo.

# Estado de la Cuestión

En este capítulo vamos a presentar el repertorio de instrucciones RISC-V y los elementos hardware que utilizaremos en este trabajo, entre los que se incluyen los procesadores Rocket y Boom así como el acelerador Gemmini y el coprocesador Hwacha. A continuación, se presentan las herramientas empleadas en el desarrollo de este proyecto, como Chipyard, FireSim FireMarshal y Amazon Web Services, necesarias para generar los diseños hardware específicos y ejecutar sobre ellos una aplicación de reconocimiento de líneas en imágenes.

### 2.1. RISC-V

RISC-V es un repertorio de instrucciones de código libre y abierto, al contrario que la mayoría de repertorios, basado en un conjunto de instrucciones reducido (RISC), fruto de un proyecto en la Universidad de California en Berkeley, que empezó en el año 2010 con las aspiraciones de generar un repertorio de instrucciones para docencia [35]. Sin embargo, el proyecto generó curiosidad y tuvo éxito, de forma que, en la actualidad, el repertorio RISC-V es un repertorio completo y funcional que está en continuo desarrollo dada la gran comunidad de contribuyentes con la que cuenta y es mantenido por la fundación "RISC-V Foundation".

Actualmente, existen distintos repertorios RISC-V básicos que se diferencian en el tamaño de los registros de enteros. Estos son RV32I y RV64I con enteros de 32 y de 64 bits respectivamente. Además, existen las variantes RV32E y RV64E análogas a las anteriores pero con la mitad de registros de enteros, pensadas especialmente para microcontroladores que requieran pocas prestaciones y cuenten con un espacio limitado.

Vistos estos cuatro repertorios base, a cualquiera de ellos se les pueden añadir extensiones estándar y específicas para generar repertorios adaptados al caso de uso. Las más comunes son:

- M: extensión estándar para instrucciones de multiplicación y división de enteros.

- A: extensión estándar para instrucciones atómicas.

- F: extensión estándar para instrucciones en punto flotante de precisión simple.

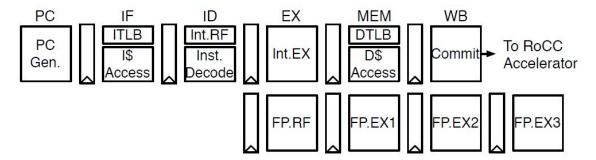

Figura 2.1: Pipeline del core Rocket [3].

• D: extensión estándar para instrucciones en punto flotante de doble precisión.

Estas extensiones junto con el repertorio base (IMAFD) se agrupan y se denotan con la opción "G" [35]. En este trabajo se utiliza el repertorio RV64GC que es el que implementan los cores y aceleradores que utilizaremos. La opción "C" proviene de *Compressed Instructions* y añade instrucciones especialmente cortas, de tan solo 16 bits de codificación, para las operaciones más comunes y, por tanto, permite generar un código ensamblador más corto [30].

#### 2.1.1. Cores

En la actualidad son numerosas las empresas e instituciones públicas que diseñan y producen cores que implementen el repertorio de instrucciones RISC-V. Entre ellos se encuentran los cores Rocket y Boom, diseñados por la universidad de Berkeley y producidos por SiFive. Los motivos por los que se han elegido estos dos cores en el desarrollo de este trabajo es que son de código libre y abierto y están parametrizados, de forma que es sencillo modificar su arquitectura. A continuación, vamos a ver en detalle las características de ambos cores.

#### 2.1.1.1. Rocket

El core Rocket es un procesador implementado en el lenguaje hardware Chisel (Constructing Hardware In a Scala Embedded Language) [8], compuesto por un pipeline de seis etapas que ejecuta instrucciones en orden. Las etapas se presentan en la Figura 2.1 y son las siguientes: generación del PC; Fetch, donde lee la siguiente instrucción de la caché de instrucciones; Decode, donde averigua de qué tipo es la instrucción leída y qué registros necesita como operandos para determinar posibles bloqueos; Execution, donde realiza la operación asociada a la instrucción; Memory, donde accede a la caché de datos; y Commit o Write Back, donde actualiza el estado de la arquitectura con los cambios generados por la instrucción.

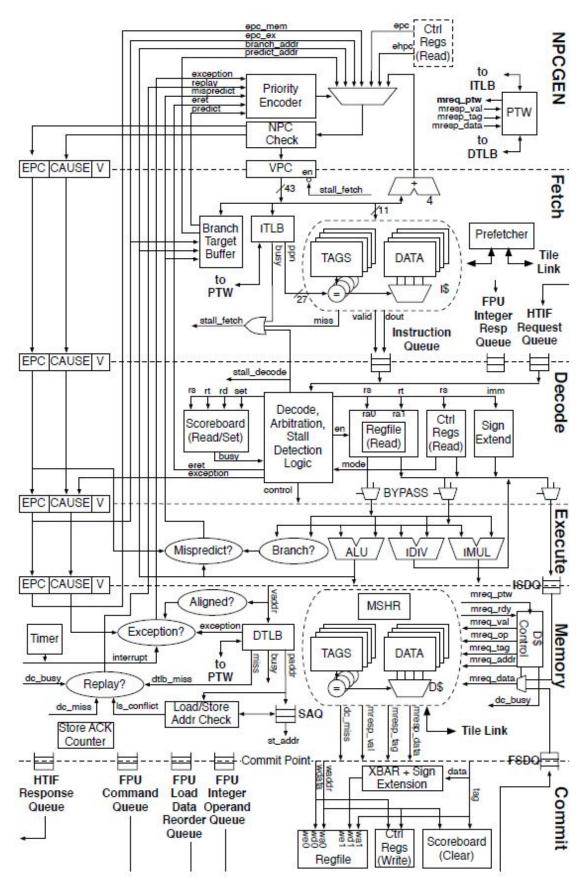

A continuación, en la Figura 2.2 vemos la microarquitectura del core Rocket. A pesar de ser un core de rendimiento limitado, dispone de algunas mejoras como un predictor de saltos o un prefetcher, este último destinado a aumentar la eficiencia en la búsqueda de datos en memoria.

2.1. RISC-V 7

Figura 2.2: Microarquitectura del core Rocket [36].

#### 2.1.1.2. Boom

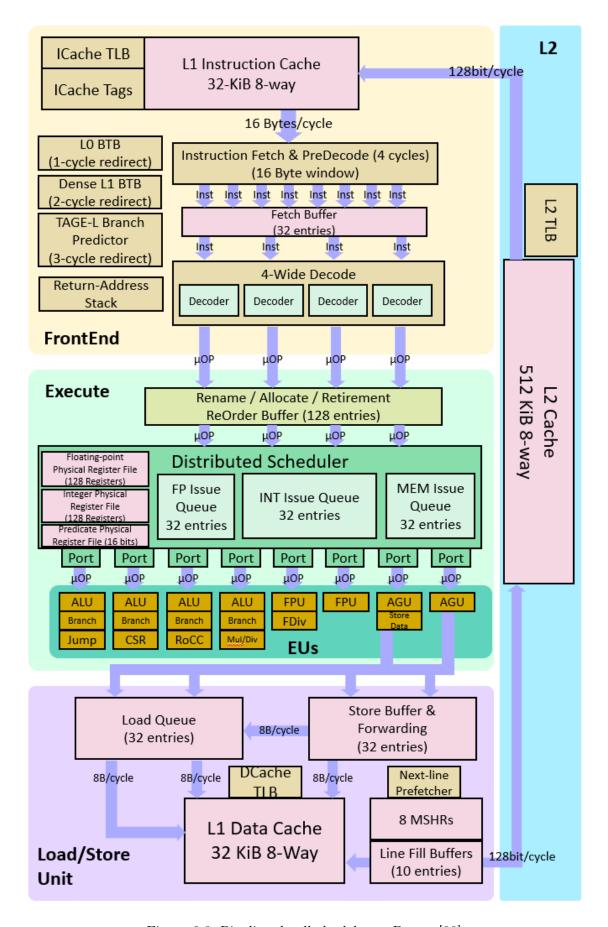

El core Boom (Berkeley Out-of-Order Machine) es un procesador implementado en Chisel con un pipeline de diez etapas que ejecuta instrucciones fuera de orden. Las etapas detalladas se presentan en la Figura 2.3.

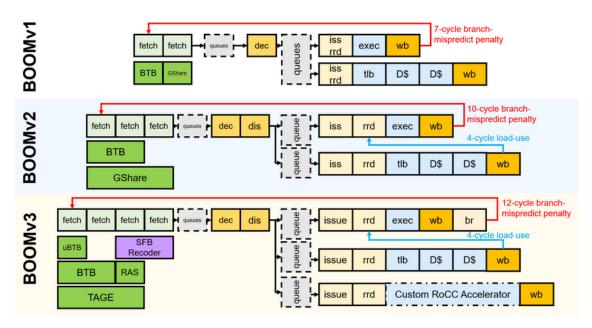

Actualmente, el core Boom cuenta con distintas versiones, cada una mejora de la anterior. En la Figura 2.4 vemos los rasgos generales del pipeline de cada una de ellas. La historia de BOOM [39] empieza con una primera versión BOOMv1, que se inspiró en los procesadores MIPS R10000 [37] y Alpha 21264 [19] y fue creada con la intención de usarse para docencia. Esta primera versión contaba con un pipeline muy simple de pocas etapas, que era físicamente imposible producir, así pues, con la siguiente versión BOOMv2 se buscó un diseño apto para producción. Algunos de los cambios apreciables entre versiones son el aumento del número de etapas en el pipeline y la separación de los registros y las unidades aritméticas para operaciones en punto flotante. Finalmente, la versión más reciente BOOMv3 presenta un mayor número de etapas en el pipeline para evitar cuellos de botella y un diseño específico para explotar la ejecución de instrucciones fuera de orden.

Dada la complejidad de las versiones BOOMv2 y BOOMv3, en la Figura 2.3 podemos ver en detalle cada etapa del pipeline. En este trabajo usaremos la version BOOMv2 que cuenta con un pipeline de diez etapas y la suficiente complejidad arquitectónica para obtener beneficios en términos de rapidez y eficacia respecto al core Rocket, tal y como se establece en [20] y [29], y como posteriormente comprobaremos en este trabajo.

### 2.1.2. Aceleradores y coprocesadores

El repertorio de instrucciones RISC-V cuenta con numerosos aceleradores de propósito específico, como el SHA3 [33] para encriptación o el Gemmini [15] para multiplicación de matrices, así como coprocesadores como el Hwacha para operaciones vectoriales [27]. A continuación, veremos en detalle el acelerador Gemmini y el coprocesador vectorial Hwacha que usaremos posteriormente en este trabajo.

#### 2.1.2.1. Hwacha

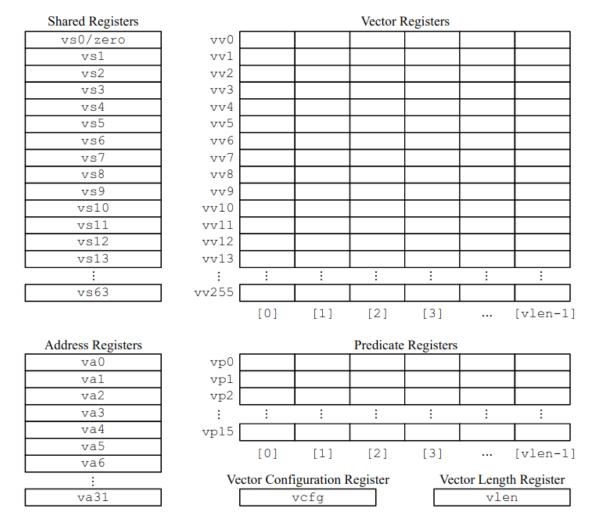

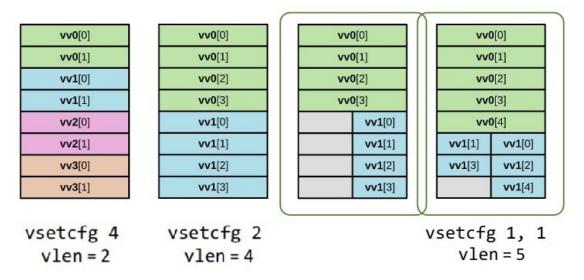

El coprocesador vectorial Hwacha está diseñado para ofrecer un alto rendimiento con un bajo consumo de energía [27]. Su diseño está inspirado en los primeros procesadores vectoriales como el Cray-1 [32] y en los anteriores componentes vectoriales diseñados para RISC-V como Scale [23] [24] o Maven [5] [25] [26]. La principal característica de Hwacha, que lo diferencia del resto de coprocesadores vectoriales del panorama actual, es el alto desacoplamiento entre el acceso a los datos vectoriales y la ejecución vectorial, pues a las operaciones vectoriales se les invoca desde el bucle de procesamiento por bloques y se ejecutan en paralelo al resto del bucle. Con esto, se consigue un gran rendimiento, dando lugar a un paradigma en el que los coprocesadores vectoriales de dimensiones relativamente pequeñas permiten sustituir a las GPUs en algunos casos de uso [9].

El coprocesador cuenta con 256 registros vectoriales configurables, 16 registros de predicado vectoriales también configurables, 32 registros escalares de dirección fijos de solo lectura y 64 registros escalares fijos de escritura y lectura, como podemos ver en la Figura 2.5.

2.1. RISC-V

Figura 2.3: Pipeline detallado del core Boom. [38]

Figura 2.4: Pipeline del core Boom en sus distintas versiones [38].

Figura 2.5: Registros del coprocesador Hwacha [27].

2.1. RISC-V

Figura 2.6: Posibles configuraciones de los registros vectoriales de Hwacha [34].

Figura 2.7: Microarquitectura del coprocesador Hwacha [34].

Cabe destacar que los registros vectoriales son configurables vía software. Por ejemplo, como vemos en los primeros elementos de la Figura 2.6, en una aplicación podemos fijar distintos valores para los parámetros vlen y vsetcfg y conseguir distintas configuraciones de los registros vectoriales. Además, también en esta figura observamos en los últimos dos elementos como Hwacha permite tener una organización con varios tamaños de vector simultáneos.

A continuación, en la Figura 2.7 vemos en detalle su microarquitectura. Observamos que Hwacha se comunica con la unidad de control del procesador para recibir las instrucciones a ejecutar y las guarda en las colas correspondientes. A continuación, las decodifica y las envía a la unidad escalar o a alguna de las unidades vectoriales que lo componen.

Uno de los componentes clave para el rendimiento del coprocesador vectorial Hwacha es, sin duda, los vectores sistólicos que tiene implementados para realizar las multiplicaciones vectoriales directamente con elementos hardware, cuya microarquitectura y localización de los datos por ciclos podemos ver en la Figura 2.8.

Figura 2.8: Microarquitectura de los vectores sistólicos de Hwacha [34].

#### 2.1.2.2. Gemmini

Gemmini es un acelerador especializado en la multiplicación de matrices integrado en el ecosistema de Chipyard e implementado en Scala, que ejecuta instrucciones personalizadas y no estándar del repertorio RISC-V. En un diseño heterogéneo, el acelerador se comunica con el procesador mediante el puerto RoCC y se conecta directamente a la memoria caché de nivel 2, como podemos ver en la Figura 2.9. Actualmente, es compatible con los cores Rocket y Boom.

El proceso de multiplicación de matrices se lleva a cabo en un vector matricial sistólico para obtener un alto rendimiento. Cada celda del array cuenta con registros entre cada tile que la compone, como vemos en la Figura 2.10. La implementación hardware de cada tile permite configurar en tiempo de compilación el flujo de las sumas parciales entre output-stationary (por filas) o weight-stationary (por columnas) [14].

Además, Gemmini cuenta con una memoria *scratchpad* para almacenar los valores intermedios de una multiplicación, una unidad especial para trasponer matrices y un controlador para gestionar la memoria, la comunicación con el core y el tipo de flujo de datos.

#### 2.2. Herramientas

En esta sección vamos a detallar las herramientas que se han utilizado en el desarrollo de este trabajo.

### 2.2.1. Chipyard

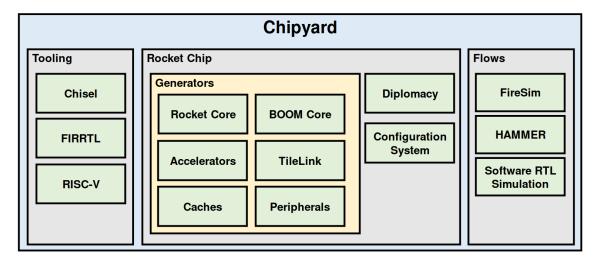

Chipyard [2] es un entorno para el diseño y evaluación de sistemas hardware que se compone de un conjunto de herramientas y librerías diseñadas para proporcionar una vía de integración entre las herramientas open-source y las herramientas comerciales para el desarrollo de sistemas on chip. El entorno está constituido por los componentes que vemos en la Figura 2.11. Por un lado, tenemos el repertorio de instrucciones RISC-V, el lenguaje FIRRTL para representar los modelos RTL y el lenguaje Chisel, en el que están escritos

2.2. Herramientas

Figura 2.9: Arquitectura del acelerador Gemmini [15].

Figura 2.10: Arquitectura del vector sistólico de Gemmini [15].

Figura 2.11: Componentes de Chipyard [28].

Figura 2.12: Flujo de ejecución en Chipyard [28].

los componentes. En cuanto a los componentes, Chipyard ha embebido y ampliado la herramienta Rocket Chip, ofreciendo algunos cores (Rocket, Boom y CVA6), aceleradores o coprocesadores (Gemmini, Hwacha, SHA3), así como las memorias caché y los sistemas periféricos necesarios para generar un SoC completo. Entre estos componentes se encuentran los cores Rocket y Boom, y los aceleradores Gemmini y Hwacha, que conforman los sistemas heterogéneos escogidos para este trabajo. Finalmente, para llevar estos diseños a un entorno de pruebas, cuenta con herramientas externas como FireSim, para ejecuciones sobre FPGAs en la nube, HAMMER (Higly Agile Masks Made Efforlessly from RTL), para transferir los diseños a VLSI y posteriormente producir el hardware, o la posibilidad de generar Verilog para simular el diseño en herramientas externas como Spike o Qemu.

Además, permite una alta personalización de los diseños hardware generados, ya que gran parte de los componentes de la arquitectura están parametrizados. Por ejemplo, podemos dar el valor deseado a parámetros como el número de entradas del ROB o el número de registros que forman la cola de decodificación.

2.2. Herramientas

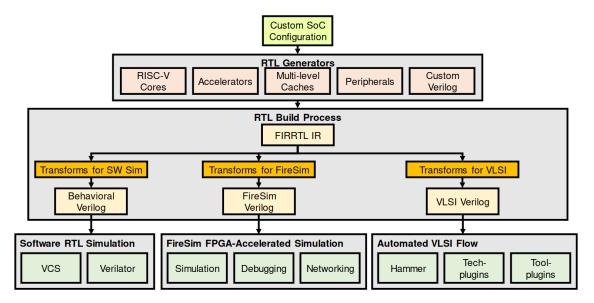

En el ámbito de simulación de la ejecución de una aplicación sobre un diseño de una arquitectura RISC-V, Chipyard nos ofrece varias posibilidades como vemos en la Figura 2.12. En primer lugar, utilizar un simulador del repertorio de instrucciones RISC-V, como la herramienta Spike, para simular la ejecución de las instrucciones RISC-V que corresponden a la aplicación sin necesitar hardware ni ninguna herramienta adicional. En segundo lugar, podemos integrar Chipyard con FireSim para ejecutar la aplicación en una FPGA en la nube. Finalmente, ofrece la posibilidad de generar el código Verilog para volcarlo sobre una FPGA que implemente RISC-V. La segunda opción es la más versátil y la elegida en este trabajo, ya que permite personalizar el diseño de la arquitectura y ejecutar el código en una FPGA real, encontrando una mayor precisión en la medición de tiempos que en una simulación.

### 2.2.2. FireSim

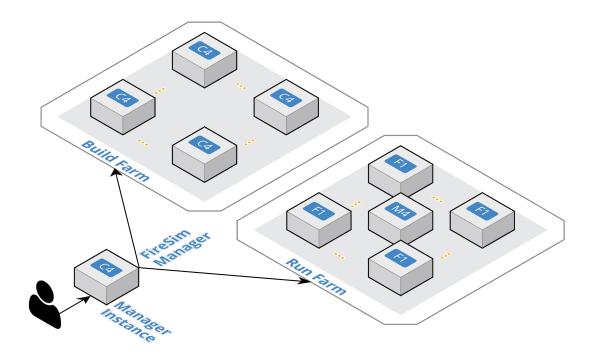

FireSim es una plataforma de simulación hardware acelerada por FPGA y con precisión de ciclos [17] enfocada a testear diseños hardware en FPGAs en la nube, en particular, soporta conexión con Amazon Web Services (AWS). FireSim ha sido creado en la Universidad de California en Berkeley y es software libre y abierto.

La plataforma permite tanto ejecutar sobre un nodo en paralelo, como simular centros de datos con distintas topologías de red conectando los nodos. La infraestructura que posee para esto podemos verla en la Figura 2.13. FireSim se instala y se ejecuta sobre una instancia de tipo C4 de AWS llamada *Manager Instance*, ya que desde esta misma se invocan todas las operaciones necesarias para crear y simular un diseño hardware. Sin embargo, esta instancia delegará el trabajo en otras en dos casos: a la hora de crear la imagen necesaria para reproducir un diseño hardware en una FPGA (AFI), y a la hora de simular una ejecución de una aplicación sobre un diseño.

En el primer caso, para cada diseño a generar se crea una instancia del tipo que se haya especificado en cada diseño generando la "Build Farm" que vemos en la Figura 2.13. En el segundo caso, el usuario configura qué tipos de instancias y cuántas de cada tipo se deben crear mediante un fichero de configuración, generando la "Run Farm". Y, posteriormente, se despliega la AFI del diseño hardware elegido en cada una de las instancias y se ejecuta el workload correspondiente.

Así, FireSim genera su propio código RTL y ejecuta diversas aplicaciones sobre estas FPGAs en la nube, obteniendo los mismos resultados que si el circuito estuviese implementado físicamente.

### 2.2.3. FireMarshal

FireMarshal es una herramienta de generación de tareas para sistemas RISC-V expresamente diseñada para integrarse con FireSim [31]. Esta herramienta genera los ficheros de configuración y los ficheros binarios que necesita FireSim para ejecutar una tarea sobre una FPGA. Para ello, necesita el código de una tarea que se quiera ejecutar sobre la FPGA y un fichero de configuración. Algunas de las opciones que se le pueden especificar en el fichero de configuración son las siguientes:

Base: especificamos la imagen base del sistema de entre tres posibles opciones: bare-

Figura 2.13: Infraestructura de FireSim [18].

metal, fedora o buildroot.

- Host-init: especificamos un script que se ejecutará en el equipo host antes de construir la imagen.

- Run: especificamos un script que se ejecutará en la FPGA una vez configurada.

- Outputs: especificamos una lista de ficheros que se copiarán desde la FPGA al administrador.

- Jobs: especificamos una lista de tareas que se ejecutarán cada una en un nodo en paralelo.

#### 2.2.4. Amazon Web Services

Amazon Web Services [1] es una plataforma de servicios en la nube que ofrece desde cursos de formación en nuevas tecnologías como la inteligencia artificial o el IoT hasta servicios de infraestructura como almacenamiento o cómputo en la nube. En este caso nos centramos en el cómputo en la nube, ya que nos ofrece una gran diversidad de plataformas hardware, entre ellas las instancias EC2 F1, que se corresponden con FPGAs, aportándonos la versatilidad que necesitamos para sintetizar diseños hardware y simular la ejecución de aplicaciones sobre ellos.

Ahora que hemos visto todas las herramientas y los elementos hardware que vamos a utilizar, pasamos a explicar los algoritmos de tratamiento de imágenes que utilizaremos y las modificaciones que les realizamos a los mismos para obtener un mejor rendimiento.

# Algoritmos de tratamiento de imágenes

En este capítulo, abordamos los algoritmos de tratamiento de imágenes¹ que se van a utilizar como casos de uso, tal como se ha mencionado anteriormente. Más específicamente, se detallarán en este capítulo los algoritmos utilizados para la detección de las líneas de la carretera a partir de las imágenes de la misma. En primer lugar, se presentarán los algoritmos básicos utilizados (algoritmo de Canny y transformada de Hough). A continuación, se mostrará el algoritmo completo para detección de líneas que se ha utilizado como punto de partida en este trabajo y, finalmente, se propondrán modificaciones al mismo que mejoran su eficiencia y rendimiento sin pérdida de precisión.

## 3.1. Algoritmo de Canny

El algoritmo de Canny se encarga de la detección de los bordes en una imagen [7], esta técnica permite extraer información estructural útil de la imagen en cuestión de forma que se reduce la cantidad de datos a procesar en los siguientes pasos del tratamiento. Sin embargo, una técnica de detección de bordes es útil solo si cumple los siguientes requisitos:

- Buena detección detectar los bordes con una baja tasa de error.

- Buena localización detectar los puntos de borde de una región con precisión respecto de la imagen real.

- Respuesta mínima detectar cada borde solo una vez, de forma que se elimine el ruido de los alrededores.

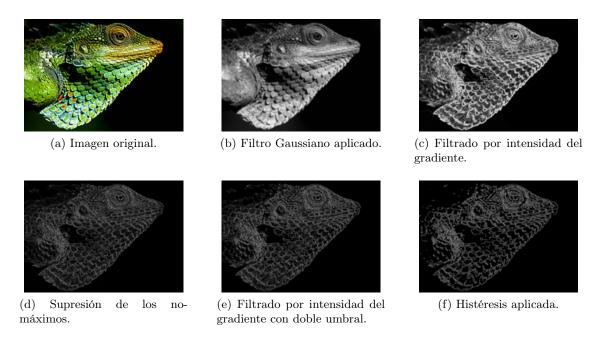

Todos estos requisitos los consigue el algoritmo Canny utilizando el cálculo de variaciones, una técnica matemática que permite encontrar una función analítica que aproxime la curva real con la mayor precisión posible. El procedimiento que sigue el algoritmo de Canny se puede separar en cinco bloques que se detallan a continuación, y se puede ver su efecto sobre una imagen original en la Figura 3.1.

<sup>&</sup>lt;sup>1</sup>El código correspondiente a los algoritmos de tratamiento de imágenes han sido desarrollados por el profesor Carlos García Sánchez garsanca@dacya.ucm.es de la Facultad de Informática de la UCM.

Figura 3.1: Ejemplo de detección de bordes con el algoritmo de Canny.

- 1. Reducción de ruido aplicar el filtro de Gauss para suavizar la imagen.

- 2. Encontrar el gradiente de intensidad de la imagen.

- 3. Umbral de magnitud al gradiente aplicar un umbral al gradiente para descartar los falsos positivos de borde.

- 4. Doble umbral aplicar nuevamente un umbral al gradiente para resaltar los bordes potenciales.

- 5. Histéresis eliminar los bordes débiles o inconexos.

Entre los métodos de detección de bordes desarrollados hasta ahora, el algoritmo de detección de bordes de Canny es uno de los métodos más estrictamente definidos que proporciona una detección buena y fiable. Debido a su optimización para cumplir los tres criterios de detección de bordes y a la sencillez del proceso de aplicación, se ha convertido en uno de los algoritmos más populares para la detección de bordes.

A continuación, vemos el pseudo-código que hemos utilizado para aplicar el algoritmo de Canny desglosado en cada una de las etapas anteriores. Principalmente se compone de multiplicaciones de matrices consecutivas y chequeo de condiciones para detectar los puntos de borde.

```

void canny(...){

// Paso 1: Reduccion de ruido

float NR = mask * image

//Paso 2: Intensidad del gradiente

float Gx = mask * NR

float Gy = mask * NR

float G = sqrt(Gx^2, Gy^2)

```

```

float phi = arctan(abs(Gy), abs(Gx))

10

11

//Paso 3: Umbral del gradiente

if(threshold(phi[*])){

13

float phi[*] in {0, 45, 90, 135}

14

15

//Paso 4: Doble umbral

17

if (condition(phi[*]) && condition(G)){

18

int edge[*] = 1;

19

20

21

//Paso 5: Histeresis

if (condition(G[*]) && edge[*]){

23

int image_out[*] = 255;

24

25

26 }

```

### 3.2. Transformada de Hough

La transformada de Hough es una técnica de extracción de características que se utiliza en numerosos campos que requieren el procesamiento de imágenes como la visión por ordenador o el procesamiento digital de imágenes. El objetivo del algoritmo es encontrar objetos imperfectos de entre unas determinadas clases de objetos mediante un procedimiento de votación. Este procedimiento consiste en crear un espacio con los valores asignados a cada píxel, de forma que los máximos locales resultantes en el espacio acumulador son los posibles objetos detectados.

La transformada de Hough clásica tan solo se aplicaba para la detección de líneas rectas, sin embargo, se ha ido modificando y actualmente se utiliza para la detección de curvas arbitrarias como elipses o círculos.

A continuación, vemos el código que hemos utilizado para aplicar la transformada de Hough. En este código para cada punto de borde que se ha detectado previamente con el algoritmo de Canny, traza un haz de líneas que pasan por él y guarda la cantidad de líneas que pasan por cada píxel de la imagen. De esta forma, los puntos por donde más líneas pasen se corresponderán con una línea en la imagen original.

```

void houghtransform(...){

//Para cada punto de borde

if( image[ (i*width) + j] > 250 ){

for(theta=0; theta<180; theta++) //Haz de lineas

{

float rho = ( center(j) * cos(theta) + center(i) * sin(theta);

accumulators[ (rho + cte) * 180 + theta]++;

}

}

}</pre>

```

### 3.3. Detección de líneas

Una vez vistos los algoritmos anteriores, vamos a utilizar una combinación de ambos junto con otro código específico para detectar con mayor precisión las líneas que delimitan los carriles en las carreteras convencionales.

Para ello, dada una imagen de entrada, aplicamos en primer lugar el algoritmo de Canny y, a continuación, la transformada de Hough, de forma que este último algoritmo nos devolverá una matriz de las mismas dimensiones de la imagen con unos valores de acumulación. Las celdas que se correspondan con un máximo local dentro de la matriz nos darán las coordenadas polares de una recta de la imagen original. A continuación, vemos el pseudo-código de dicha función que consiste en buscar los máximos locales de la imagen preprocesada y extraer las coordenadas de la recta que representa.

```

void getlines(...){

//Para cada punto de la imagen (rho, theta)

//Si es un maximo local

if(accumulators[*] >= threshold){

max = accumulators[*];

6

//Revisamos en su vecindad

if( accumulators[vecindad(*))] > max ){

max = accumulators[vecindad(*)];

8

9

10

//Guardamos dos puntos que delimitan la recta

11

lines.add(x1, y1, x2, y2);

13 }

```

### 3.4. Modificación de los tipos de datos

En los apartados anteriores, hemos presentado el código original de los algoritmos. Sin embargo, este código utiliza muchas variables en punto flotante cuyas operaciones son computacionalmente más costosas que las operaciones sobre enteros. Por tanto, es conveniente sustituir las variables de punto flotante por variables enteras siempre que no se pierda precisión.

Primero, notamos que el algoritmo de Canny es dónde se usan más variables en punto flotante que se pueden sustituir por enteras, de forma que utilizamos menos espacio en memoria. Además, hay más recursos de hardware empotrado preparados para operaciones con números enteros cortos que con punto flotante, por ejemplo [4] [22] [21]. Veamos a continuación las variables que se pueden sustituir sin la correspondiente pérdida de precisión.

NR: Esta variable es una matriz dónde se guarda la imagen resultante al aplicar una máscara dada por la matriz

$$\begin{pmatrix} 2 & 4 & 5 & 4 & 2 \\ 4 & 9 & 12 & 9 & 4 \\ 5 & 12 & 15 & 12 & 5 \\ 4 & 9 & 12 & 9 & 4 \\ 2 & 4 & 5 & 4 & 2 \end{pmatrix}$$

Figura 3.2: Imagen de salida con las líneas detectadas en rojo.

a las vecindades 5x5 de cada píxel de la imagen original. Dado que la máscara contiene números enteros y la imagen original viene dada por enteros, podemos declarar la variable como entera sin pérdida de precisión.

Gx y Gy: Estas variables son matrices donde se guardan las trasformaciones dadas por las siguientes matrices

$$\begin{pmatrix} 1 & 2 & -2 & -1 \\ 4 & 8 & -8 & -4 \\ 6 & 12 & -12 & -6 \\ 4 & 8 & -8 & -4 \\ 1 & 2 & -2 & -1 \end{pmatrix}, \begin{pmatrix} -1 & -2 & 2 & 1 \\ -4 & -8 & 8 & 4 \\ -6 & -12 & 12 & 6 \\ -4 & -8 & 8 & 4 \\ -1 & -2 & 2 & 1 \end{pmatrix}$$

aplicadas a las vecindades 5x4 de cada elemento de la variable NR anterior. Dado que NR la hemos transformado en entera y las máscaras contienen números enteros con signo, podemos declarar las variables Gx y Gy como enteras sin pérdida de precisión.

■ Phi: En el código original la variable phi recibe un valor flotante correspondiente al arctan  $\frac{Gy}{Gx}$ , que es un número flotante. Sin embargo, esta asignación es temporal y a continuación se le da un valor entero en  $\{0,45,90,135\}$  a cada elemento de la matriz phi. Por tanto, para optimizar el código, guardaremos los valores temporales flotantes en una variable auxiliar que posteriormente se eliminará, y se declarará la variable phi como entera.

Una vez realizados estos cambios en el código, comprobamos que no hemos perdido precisión en la detección de líneas en una imagen. En la Figura 3.2 vemos la imagen original con las líneas detectadas marcadas en rojo y en la Figura 3.3a vemos el resultado analítico correspondiente a dichas líneas. Comprobamos en la Figura 3.3b que el resultado de la ejecución del código modificado se corresponde con la ejecución del código anterior, y además ha sido ligeramente más rápida.

# 3.5. Profiling del código

A continuación, vamos a realizar un *profiling* del código para determinar en qué partes se emplea un mayor número de recursos y tiempo. Para ello, medimos el tiempo que se

```

(x1,y1)=(0,1163) (x2,y2)=(768,625)

(x1,y1)=(0,770) (x2,y2)=(768,593)

(x1,y1)=(960,644) (x2,y2)=(1920,1176)

CPU Exection time 652992.000000 ms.

```

```

(x1,y1)=(0,1163) (x2,y2)=(768,625)

(x1,y1)=(0,770) (x2,y2)=(768,593)

(x1,y1)=(960,644) (x2,y2)=(1920,1176)

CPU Exection time 618817.000000 us.

```

(a) Ejecución del código original.

(b) Ejecución del código modificado.

Figura 3.3: Resultados de las ejecuciones de los distintos códigos.

|                              | Etapa 1 | Etapa 2     | Etapa 3     | Total  |

|------------------------------|---------|-------------|-------------|--------|

| Tiempo ( $\mu$ s)            | 43803   | 98171       | 456030      | 598004 |

| Porcentaje respecto el total | 7,32 %  | $16,\!42\%$ | $76,\!26\%$ |        |

Tabla 3.1: Profiling del código completo por etapas.

emplea en cada uno de los algoritmos anteriores y lo comparamos respecto al tiempo total de la ejecución. Dado que el tiempo de ejecución depende de variables de entorno del sistema donde se ejecuta, los tiempos difieren entre ejecuciones. Para solucionarlo se toma la media de los tiempos de tres ejecuciones consecutivas.

El código a ejecutar se puede dividir en las siguientes tres etapas: carga de la imagen, donde se lee la imagen desde un fichero y se le aplica un filtro en blanco y negro utilizando la librería externa "libpng"; tratamiento de la imagen, donde se le aplican los algoritmos vistos anteriormente en esta sección; y, generación de la salida, donde se modifica la imagen inicial para añadirle las líneas encontradas.

En un primer profiling cuyos resultados vemos en la Tabla 3.1, apreciamos que la etapa 3 tiene el mayor consumo de tiempo, un 76,26 % del total. Esta etapa es la encargada de generar la imagen de salida con las líneas impresas en ella, sin embargo, en un entorno IoT, no necesitamos un resultado visual, nos basta con las coordenadas de las líneas. Por tanto, modificamos el código eliminando la creación de la imagen de salida.

De esta forma, la etapa 3 consume alrededor de  $4\mu s$ , como vemos en la Tabla 3.2, resultando irrelevante su papel en el rendimiento del programa. Ahora, abordamos la etapa 2, ya que consume casi el 70 % del tiempo de ejecución del nuevo programa sin salida gráfica. Esta etapa a su vez se subdivide en las siguientes tres fases: algoritmo de Canny, transformada de Hough y detección de líneas. Así pues, realizamos un profiling de la etapa 2 subdividida, que podemos ver en la Tabla 3.3. Con esto, nos damos cuenta de que la fase 1 que se corresponde con la aplicación del algoritmo de Canny supone la mayor parte del tiempo, un 87,64%.

Dado que el algoritmo de Canny se basa en la multiplicación de matrices, debemos diseñar un hardware específico para acelerar esta operación tan costosa computacionalmente.

|                              | Etapa 1 | Etapa 2     | Etapa 3 | Total  |

|------------------------------|---------|-------------|---------|--------|

| Tiempo ( $\mu$ s)            | 43485   | 98714       | 4       | 142203 |

| Porcentaje respecto el total | 30,58%  | $69,\!42\%$ | 0,00 %  |        |

Tabla 3.2: Profiling del código sin imagen de salida por etapas.

|                              | Fase 1  | Fase 2 | Fase 3     | Total  |

|------------------------------|---------|--------|------------|--------|

| Tiempo ( $\mu$ s)            | 90265   | 12275  | 459        | 102999 |

| Porcentaje respecto el total | 87,64 % | 11,92% | $0,\!45\%$ |        |

Tabla 3.3: Profiling de la etapa 2 por fases.

### 3.6. Vectorización del código

En esta sección vamos a vectorizar el código lo máximo posible para poder realizar las operaciones de multiplicación de vectores de forma más eficiente. En particular, se van a desarrollar y vectorizar las operaciones del algoritmo de Canny.

Este algoritmo, en su primera fase, calcula una matriz de forma que cada celda (i,j) es el resultado de la suma de la multiplicación elemento a elemento de su vecindad 5x5 por una máscara 5x5 definida previamente dividido por la constante 159. En el código original estas operaciones se realizan con dos bucles anidados que recorren la matriz original como podemos ver a continuación.

```

for(i=2; i<height-2; i++)</pre>

for(j=2; j<width-2; j++)</pre>

3

// Noise reduction

NR[i*width+j] =

(2*im[(i-2)*width+(j-2)] + 4*im[(i-2)*width+(j-1)] + 5*im[(i-2)*width+(j-1)]

width+(j)] + 4*im[(i-2)*width+(j+1)] + 2*im[(i-2)*width+(j+2)]

+ 4*im[(i-1)*width+(j-2)] + 9*im[(i-1)*width+(j-1)] + 12*im[(i-1)*width+(j-1)]

width+(j)] + 9*im[(i-1)*width+(j+1)] + 4*im[(i-1)*width+(j+2)]

+ 5*im[(i )*width+(j-2)] + 12*im[(i )*width+(j-1)] + 15*im[(i )*

width+(j)] + 12*im[(i )*width+(j+1)] + 5*im[(i )*width+(j+2)]

+ 4*im[(i+1)*width+(j-2)] + 9*im[(i+1)*width+(j-1)] + 12*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1)*im[(i+1

width+(j)] + 9*im[(i+1)*width+(j+1)] + 4*im[(i+1)*width+(j+2)]

+ 2*im[(i+2)*width+(j-2)] + 4*im[(i+2)*width+(j-1)] + 5*im[(i+2)*width+(j-1)]

width+(j)] + 4*im[(i+2)*width+(j+1)] + 2*im[(i+2)*width+(j+2)])

11

/159:

12

```

Sin embargo, para poder multiplicar vectores de un tamaño considerable hemos modificado el código como sigue: en primer lugar, se prepara un vector con la máscara replicada N veces y otro vector con las vecindades correspondientes a N celdas (i,j); a continuación, se multiplican dichos vectores mediante un hardware de propósito específico; y, finalmente, se suman los elementos del vector resultante de la multiplicación en grupos de 25 elementos, ya que el valor de cada celda (i,j) se corresponde con la multiplicación de su vecindad 5x5 y su máscara 5x5, y se divide por 159 para darle valor a la celda. Así, se calculan los valores de N celdas de la matriz con una operación de multiplicación de vectores. A continuación vemos el código resultante.

```

1 for(i=2; i<height-2; i++)

2     for(j=2; j<width-2; j++)

3     {

4         // Noise reduction

5         NR[i*width+j] =

6         (2*im[(i-2)*width+(j-2)] + 4*im[(i-2)*width+(j-1)] + 5*im[(i-2)*width+(j)] + 4*im[(i-2)*width+(j+1)] + 2*im[(i-2)*width+(j+2)]</pre>

```

```

+ 4*im[(i-1)*width+(j-2)] + 9*im[(i-1)*width+(j-1)] + 12*im[(i-1)*

width+(j)] + 9*im[(i-1)*width+(j+1)] + 4*im[(i-1)*width+(j+2)]

+ 5*im[(i )*width+(j-2)] + 12*im[(i )*width+(j-1)] + 15*im[(i )*

width+(j)] + 12*im[(i )*width+(j+1)] + 5*im[(i )*width+(j+2)]

+ 4*im[(i+1)*width+(j-2)] + 9*im[(i+1)*width+(j-1)] + 12*im[(i+1)*

width+(j)] + 9*im[(i+1)*width+(j+1)] + 4*im[(i+1)*width+(j+2)]

+ 2*im[(i+2)*width+(j-2)] + 4*im[(i+2)*width+(j-1)] + 5*im[(i+2)*

width+(j)] + 4*im[(i+2)*width+(j+1)] + 2*im[(i+2)*width+(j+2)])

/159;

}

```

El algoritmo de Canny contiene otra fase donde se realiza el mismo procedimiento para calcular nuevas matrices con valores auxiliares que se utilizan en el resultado final del tratamiento de la imagen. Luego, análogamente, se modifican sus bucles de multiplicaciones de elementos.

Ahora, estamos en disposición de pasar al siguiente capítulo, donde se generan distintas arquitecturas sobre las que ejecutar los algoritmos vistos de forma eficiente y se discuten los resultados obtenidos.

# Resultados

En este capítulo, vamos a presentar los resultados que hemos obtenido con las herramientas y los elementos hardware que hemos presentado anteriormente. En primer lugar, veremos cómo se generan las imágenes de los diseños de las arquitecturas y los diseños particulares que se han generado. En segundo lugar, veremos cómo se generan los workload que se ejecutarán sobre esos diseños. En tercer lugar, vemos el proceso a seguir para realizar una simulación de la ejecución de un workload sobre una arquitectura determinada. Finalmente, veremos los experimentos que se han realizado con distintos workload y sobre distintas arquitecturas y los resultados de rendimiento que se han obtenido. El código uitlizado para la generación de los diseños, así como el código de los workload y su correspondiente configuración pueden encontrarse en https://github.com/mbelda/Autonomous-vehicles-tests.

### 4.1. Generación de diseños de arquitecturas

En esta sección, detallamos los pasos a seguir para generar una imagen FPGA (AGFI) de un diseño de una arquitectura. Esta imagen será usada posteriormente para configurar una FPGA cloud de AWS que simule la arquitectura diseñada.

Estas arquitecturas se definen por partes utilizando las clases de FireSim y Chipyard. El primer paso es generar una configuración con el tipo y número de procesadores, los coprocesadores o aceleradores y la base de la arquitectura. Esta definición se encuentra en un módulo de Chipyard específico para ello en la ruta firesim/target-design/chipyard/generators/chipyard/src/main/scala/config. En esta ruta encontramos un fichero con nomenclatura [nombreProcesador]Configs.scala para cada procesador donde se definen sus arquitecturas. Por ejemplo, para nuestra arquitectura heterogénea unicore con un Rocket y el coprocesador vectorial Hwacha tenemos la siguiente configuración en el fichero Rocket-Configs.scala, donde vemos como añadimos cada módulo de menor a mayor relevancia: la configuración base, el procesador Rocket y el coprocesador vectorial Hwacha. Este orden es importante, ya que las configuraciones se sobreescriben las unas a las otras y predomina la que se encuentre más arriba.

```

class HwachaRocketConfig extends Config(

new chipyard.config.WithHwachaTest ++

new hwacha.DefaultHwachaConfig ++

```

```

new freechips.rocketchip.subsystem.WithNBigCores(1) ++

new chipyard.config.AbstractConfig)

```

A continuación, debemos definir la arquitectura completa en el módulo de FireSim correspondiente haciendo uso de la anterior configuración. En la ruta firesim/deploy encontramos todos los ficheros de configuración necesarios para una ejecución completa de un workload en una determinada arquitectura. En particular, para indicar la configuración de la arquitectura utilizamos el fichero config\_build\_recipes.ini donde añadimos una entrada con el formato que vemos a continuación para cada arquitectura.

En primer lugar, tenemos entre corchetes el nombre de la arquitectura, que deberá ser único. En segundo lugar, tenemos la variable *DESIGN* donde indicamos que se encargue de generar el diseño la herramienta FireSim. A continuación, contamos con las variables *TARGET\_CONFIG* y *PLATFORM\_CONFIG* donde indicamos las características específicas de la propia arquitectura. Presentamos el significado de las opciones relevantes que utilizamos:

- DDR3FRFCFSLLC4MB: Añade una memoria RAM L2 de 16GB y una L1 de 4MB asociativa con 8 vías.

- WithFireSimTestChipConfigTweaks: Añade un reloj con una frecuencia de 1 GHz para comunicarse con la memoria RAM que viene configurada con la misma frecuencia de reloj.

- WithDefaultFireSimBridges: Añade los circuitos hardware necesarios para establecer la comunicación con dispositivos como el puerto serie o el puerto UART.

- MCRams: Habilita un mecanismo para sustituir las memorias RAM multipuerto, tipicamente ineficientes, por un modelo desacoplado que simula la memoria RAM mediante accesos serializados a una implementación subyacente que se puede mapear a una RAM de bloque (BRAM) eficiente [18].

- FXMHz: Frecuencia de reloj del procesador fijada a X MHz. Debido a que algunos diseños heterogéneos son complejos a nivel de circuitos necesitamos elegir un valor de frecuencia bajo para que se pueda sintetizar el diseño. Así pues, elegimos 80MHz para la mayoría de las arquitecturas (veremos más adelante alguna excepción impuesta por limitaciones tecnológicas) con el fin de compararlas entre sí de la forma más justa posible.

- MTModels: Habilita una optimización que se encarga de separar los nodos y ejecutarlos en un hilo de ejecución independiente en una implementación física subyacente compartida. Obteniendo así los mismos resultados, pues se conserva la precisión ciclo

a ciclo y bit a bit, y se pueden generar diseños más grandes con mayor número de cores.

Finalmente, las variables *instancetype* y *deploytriplet* sirven para indicar configuraciones de la instancia de AWS. Simplemente destacamos que en la primera de ellas se indica el tipo de la instancia a utilizar para dicha arquitectura.

Llegados a este punto, contamos con la configuración completa de un diseño de una arquitectura. Ahora bien, para generarla debemos indicarlo en uno de los ficheros de configuración de FireSim. En particular, el fichero  $config\_build.ini$  contiene los nombres de las arquitecturas que se quieren generar. Por tanto, el procedimiento a seguir sería añadir el nombre de las arquitecturas que queremos generar por filas en dicho fichero y eliminar el resto de arquitecturas que pueda haber, pues en caso de no eliminar las restantes se volverían a generar y sobreescribirían la imagen anterior.

Para terminar, desde el propio directorio firesim/deploy en el que se encuentra tanto la herramienta firesim como los ficheros de configuración, ejecutamos el comando firesim buildafi para que se generen las AGFI de las arquitecturas que se han definido. Una vez finalizada la ejecución de este comando, obtenemos unos parámetros que se corresponden con el nombre de la imagen y sus características, similar al que vemos a continuación.

```

[ [firesim -rocket - singlecore - hwacha - no - nic - 12 - 11c4mb - ddr3 - MCRams - 80 MHz - no ILA]

agfi = agfi - 0 a08242b1ddef3f81

deploytripletoverride = None

customruntimeconfig = None

```

Para que la herramienta FireSim encuentre la imagen que se ha generado y se pueda utilizar en futuras ejecuciones, debemos añadir estas líneas al fichero  $config\_hwdb.ini$  en el propio directorio firesim/deploy. Este fichero, por tanto, debe contener la información de cada una de las imágenes generadas.

Una vez visto el proceso que hay que seguir para generar una imagen de un diseño de una arquitectura y el proceso de configuración que se debe llevar a cabo para poder utilizar la arquitectura en las simulaciones, pasamos a ver en detalle las arquitecturas que hemos generado.

# 4.2. Arquitecturas generadas

A continuación presentamos los diseños de las arquitecturas que se han utilizado en el desarrollo de este trabajo. Los componentes principales que se han utilizado para generar las arquitecturas son los procesadores Rocket y Boom, el acelerador de multiplicación de matrices Gemmini y el coprocesador vectorial Hwacha.

El resto de componentes de una arquitectura como la memoria, la frecuencia de reloj, los buses, etc serán los mismos para las distintas arquitecturas con el fin de compararlas de la forma más justa posible. Todas las arquitecturas utilizan las opciones DDR3FRFCFSLLC4MB, WithDefaultFireSimBridges y WithFireSimTestChipConfigTweaks en el campo  $TARGET\_CONFIG$  y las opciones MCRams y BaseF1Config en el campo  $PLATFORM\_CONFIG$ . Además, las arquitecturas homogéneas multicore incluyen también en este segundo campo la opción MTModels.

En cuanto a la frecuencia de reloj de la arquitectura, que se define mediante la opción FXMHz en el campo  $TARGET\_CONFIG$ , hemos generado arquitecturas a dos frecuencias distintas, a 80 y 50MHz. Esto es debido a que las arquitecturas que utilizan el acelerador Gemmini son más complejas a nivel de circuito y requieren 50MHz de frecuencia o menos para poder sintetizar el diseño. Sin embargo, el resto de arquitecturas heterogéneas y multicore se han podido generar a 80MHz. Por tanto, se han generado también las arquitecturas básicas homogéneas multicore a 50MHz, con el fin de comparar justamente los tiempos de las ejecuciones utilizando el acelerador Gemmini.

Una vez vistas las opciones generales del diseño, pasamos a ver en detalle las características de los procesadores, los aceleradores y los coprocesadores. Todos los componentes utilizados están escritos en Scala, lo que nos ofrece cierta facilidad para modificar propiedades básicas de los elementos hardware como el número de registros de cada tipo, el número de entradas en el ROB, etc. Las configuraciones particulares elegidas para estos valores se representan mediante una clase con nomenclatura [CaracteristicasDeLaArquitectura]Config, que extiende a su vez la clase genérica Config. Y es esta clase, que determina los detalles de la arquitectura, la que se utiliza en el campo TARGET\_CONFIG, como hemos visto anteriormente. Por tanto, pasemos a ver en detalle las clases que se han utilizado en cada arquitectura.

Arquitectura homogénea unicore con un procesador Rocket.

La configuración de esta arquitectura viene dada por la siguiente clase.

```

class RocketConfig extends Config(

new freechips.rocketchip.subsystem.WithNBigCores(1) ++

new chipyard.config.AbstractConfig)

```

El fragmento WithNBigCores es la parte relevante de esta configuración, pues define las características del procesador. En este caso vemos que se hace referencia a un core Big, sin embargo existen macros análogas para los tamaños Medium, Small y Tiny del procesador Rocket. La principal diferencia entre el resto de tamaños y el Big que utilizamos es que los restantes no cuentan con unidad de punto flotante (FPU) ni predictor de saltos (BTB). Por ejemplo, mostramos la configuración de WithNSmallCores dónde podemos observar como se indica en las líneas 6 y 7 que no contiene FPU ni BTB.

```

class WithNSmallCores(n: Int, overrideIdOffset: Option[Int] = None

) extends Config((site, here, up) => {

case RocketTilesKey => {

val prev = up(RocketTilesKey, site)

3

val idOffset = overrideIdOffset.getOrElse(prev.size)

4

val small = RocketTileParams(

5

core = RocketCoreParams(useVM = false, fpu = None),

6

btb = None,

dcache = Some(DCacheParams(

8

rowBits = site(SystemBusKey).beatBits,

9

nSets = 64.

11

nWays = 1,

nTLBSets = 1,

nTLBWays = 4,

13

nMSHRs = 0,

14

blockBytes = site(CacheBlockBytes))),

```

```

icache = Some(ICacheParams(

16

rowBits = site(SystemBusKey).beatBits,

17

nSets = 64,

18

nWays = 1,

19

nTLBSets = 1,

20

nTLBWays = 4,

21

blockBytes = site(CacheBlockBytes))))

22

List.tabulate(n)(i => small.copy(hartId = i + idOffset)) ++

23

prev

}

24

})

```

En cuanto al resto de configuración, la clase *AbstractConfig* se encarga de dar valores al resto de elementos de una arquitectura necesarios para su funcionamiento, como los buses, los elementos de entrada/salida, etc. Es por ello que esta clase estará presente en todas las configuraciones que generemos.

2. Arquitectura homogénea multicore con dos procesadores Rocket.

La configuración de esta arquitectura viene dada por la siguiente clase.

```

class DualRocketConfig extends Config(

new freechips.rocketchip.subsystem.WithNBigCores(2) ++

new chipyard.config.AbstractConfig)

```

Observamos que la definición de la clase es análoga a la anterior con la excepción de que el parámetro de número de cores que le pasamos a la clase WithNBigCores tiene el valor 2. Por tanto, generaremos una arquitectura con dos cores Rocket con las mismas características que el procesador de la arquitectura unicore, con el fin de poder comparar los resultados de las ejecuciones de las mismas aplicaciones sobre ambas.

3. Arquitectura heterogénea unicore con un procesador Rocket y el coprocesador vectorial Hwacha.

La configuración de esta arquitectura viene dada por la siguiente clase.

```

class HwachaRocketConfig extends Config(

new chipyard.config.WithHwachaTest ++

new hwacha.DefaultHwachaConfig ++

new freechips.rocketchip.subsystem.WithNBigCores(1) ++

new chipyard.config.AbstractConfig)

```

En esta arquitectura, observamos que además del core Rocket de tamaño Big añadimos el coprocesador vectorial Hwacha mediante la clase DefaultHwachaConfig y unos tests propios de Hwacha para comprobar su correcto funcionamiento al generar el diseño mediante la clase WithHwachaTest.

En el caso de Hwacha, la configuración también es fácilmente modificable como en los procesadores, ya que viene escrita en Scala y están todas las características parametrizadas. A continuación presentamos la configuración por defecto que utilizamos para Hwacha, donde vemos entre otras características que la memoria caché es directa y tiene 64 conjuntos, contamos con 256 registros vectoriales y 64 escalares y el tamaño máximo de vector es de 256 bytes.

```

class DefaultHwachaConfig extends Config((site, here, up) => {

1

case HwachaIcacheKey => ICacheParams(

2

nSets = 64,

nWays = 1,

4

rowBits = 1 * 64.

5

nTLBWays = 8,

6

fetchBytes = 8,

latency = 1

9

10

11

case HwachaCommitLog => true

12

// hwacha constants

13