## UNIVERSIDAD COMPLUTENSE DE MADRID FACULTAD DE INFORMÁTICA

### **TESIS DOCTORAL**

Rapid runtime power and performance profiling of large scale applications

Caracterización rápida y en tiempo de ejecución de grandes despliegues de aplicaciones

MEMORIA PARA OPTAR AL GRADO DE DOCTOR

PRESENTADA POR

Juan Carlos Salinas Hilburg

**DIRECTORES**

José Luis Ayala Rodrigo Marina Zapater Sancho José Manuel Moya Fernádez

### Universidad Complutense de Madrid

FACULTAD DE INFORMÁTICA.

### TESIS DOCTORAL

### Caracterización Rápida y en Tiempo de Ejecución de Grandes Despliegues de Aplicaciones

# Rapid Runtime Power and Performance Profiling of Large Scale Applications

Memoria para optar al grado de Doctor

PRESENTADA POR

Juan Carlos Salinas Hilburg

**DIRECTORES**

José Luis Ayala Rodrigo Marina Zapater Sancho José Manuel Moya Fernández

## Universidad Complutense de Madrid Facultad de Informática

### Caracterización Rápida y en Tiempo de Ejecución de Grandes Despliegues de Aplicaciones.

# Rapid Runtime Power and Performance Profiling of Large Scale Applications

# AUTHOR: JUAN CARLOS SALINAS HILBURG

### **ADVISORS:**

Dr. JOSÉ LUIS AYALA RODRIGO

Dr. MARINA ZAPATER SANCHO

Dr. JOSÉ MANUEL MOYA FERNÁNDEZ

# Rapid Runtime Power and Performance Profiling of Large Scale Applications

by Juan Carlos Salinas Hilburg

Thesis submitted to the Universidad Complutense de Madrid in fulfillment of the requirements for the degree of

### Doctor en Ingeniería Informática Facultad de Informática

#### Advisors:

Professor Dr. José Luis Ayala Rodrigo Professor Dr. Marina Zapater Sancho Professor Dr. José Manuel Moya Fernández

Universidad Complutense de Madrid Madrid

Declaration of authorship

The author, Juan Carlos Salinas Hilburg, hereby declares and confirms that this

thesis is entirely the result of the work carried out in the Department of

Architecture and Technology of Computing Systems of the School of Computer

Science at the Complutense University of Madrid. This thesis contains original

contribution by the author unless otherwise indicated.

Juan Carlos Salinas Hilburg,

November 24, 2020

V

# Acknowledgement

I would like to thank my family, friends and coworkers. Their support has been excellent through all these years.

Specially, I would like to thank my advisors. Thanks to them I have learned many things. They are not only great and wise professionals, they have a great human quality which is something that helped me to get through this experience. It has been a pleasure and an honor working with them.

Thank you Jose, Marina and Jose Manuel.

\* \* \*

#### Financial support

This thesis has been partially founded by a research grant from Complutense University of Madrid and Banco Santander, under grant CT45/15-CT46/15. Furthermore, this work has been partially supported by the following projects: i) the Spanish Ministry of Economy and Competitiveness, under contracts TEC2012-33892, IPT-2012-1041-430000 and RTC-2014-2717-3, ii) the EU (FEDER) and the Spanish MINECO, under grant TIN 2015-65277-R, iii) the EC H2020 MANGO project (GA No. 671668), and iv) by the Spanish MICINN, under grant PID2019-110866RB-I00.

# Table of Contents

| Ll           | st or | Table   | S                                                | XIII  |

|--------------|-------|---------|--------------------------------------------------|-------|

| Li           | st of | Figur   | es                                               | xvi   |

| $\mathbf{A}$ | bbre  | viation | 18                                               | xviii |

| $\mathbf{A}$ | bstra | ıct     |                                                  | XX    |

| $\mathbf{R}$ | esum  | ien     |                                                  | xxii  |

| 1            | Intr  | oduct   | ion                                              | 1     |

|              | 1.1   | Motiv   | ration                                           | . 1   |

|              | 1.2   | Proble  | em Formulation                                   | . 4   |

|              | 1.3   | Thesis  | s Contributions                                  | . 8   |

|              | 1.4   | Thesis  | s Structure                                      | . 10  |

|              | 1.5   | Public  | cations and Grants                               | . 11  |

|              |       | 1.5.1   | Journal papers                                   | . 11  |

|              |       | 1.5.2   | Conference papers                                | . 11  |

|              |       | 1.5.3   | Mobility Grants                                  | . 12  |

| 2            | Ene   | ergy Es | stimation with an Application Signature          | 13    |

|              | 2.1   | Applie  | cation Signature                                 | . 13  |

|              |       | 2.1.1   | Static Code Analysis                             | . 15  |

|              |       | 2.1.2   | Dynamic Profiling of the Application Signature   | . 16  |

|              |       | 2.1.3   | Energy Estimation                                | . 17  |

|              | 2.2   | Applie  | cation Signature for Multi-Threaded Applications | . 18  |

|              | 2.3   | Exper   | rimental Setup                                   | . 19  |

|              | 2.4   | Result  | ts                                               | . 21  |

|              | 2.5   | Concl   | usions                                           | . 25  |

| 3 | Rela | ated Work                                                  | <b>27</b> |

|---|------|------------------------------------------------------------|-----------|

|   | 3.1  | Application Signature                                      | 27        |

|   | 3.2  | Energy, Power and Performance Estimation                   | 31        |

|   | 3.3  | Server Power Modeling                                      | 35        |

|   | 3.4  | Dynamic Profiling                                          | 36        |

|   | 3.5  | Energy-Aware Task Scheduling                               | 37        |

| 4 | Fast | Energy Estimation Framework                                | 41        |

|   | 4.1  | Fast Energy Estimation Framework Modules                   | 41        |

|   |      | 4.1.1 Call Graph Set                                       | 44        |

|   |      |                                                            | 45        |

|   |      | 4.1.3 Application Signature                                | 49        |

|   |      |                                                            | 51        |

|   |      |                                                            | 54        |

|   |      |                                                            | 55        |

|   |      | 4.1.5.1 Execution Time Estimation                          | 55        |

|   |      | 4.1.5.2 Hardware Counter Profile Reconstruction            | 56        |

|   |      | 4.1.6 Energy Estimation                                    | 56        |

|   |      | 4.1.6.1 Power Models                                       | 56        |

|   |      |                                                            | 57        |

|   |      | 3.                                                         | 58        |

|   | 4.2  | •                                                          | 58        |

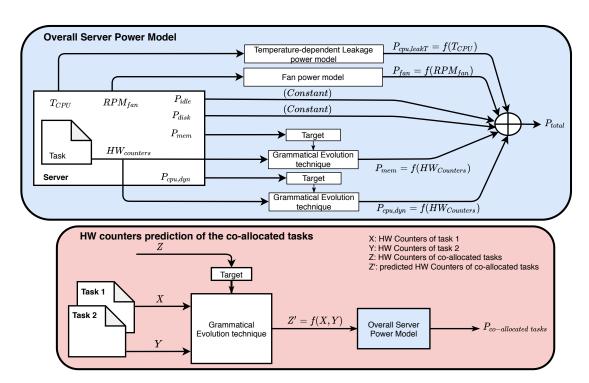

|   |      | 4.2.1 Server Power Models                                  | 59        |

|   |      |                                                            | 61        |

|   |      | v                                                          | 61        |

|   |      | 11                                                         | 62        |

|   |      |                                                            | 62        |

|   | 4.3  | <u> </u>                                                   | 64        |

|   |      | 1                                                          | 64        |

|   |      |                                                            | 65        |

|   | 4.4  | Results                                                    | 70        |

|   |      | 4.4.1 Fast Energy Estimation Framework                     | 70        |

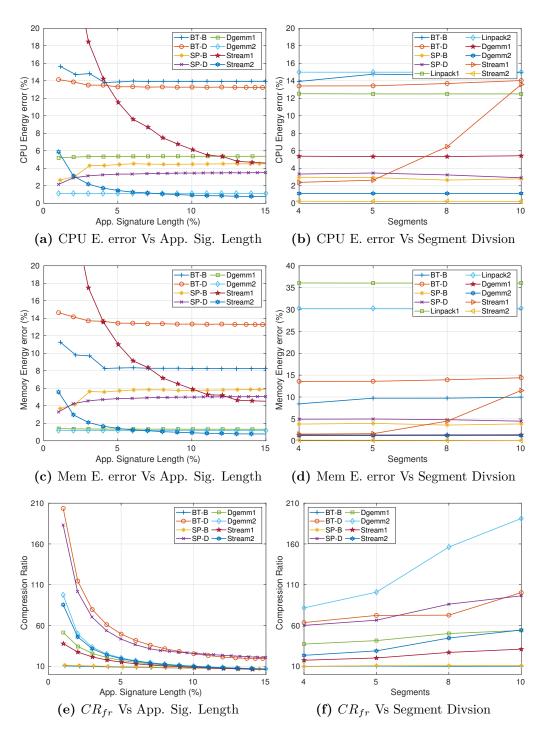

|   |      | 4.4.1.1 Compression Ratio and Energy Error vs              | • •       |

|   |      | Application Signature Length                               | 70        |

|   |      | 4.4.1.2 Compression Ratio and Energy Error vs Segment      | • •       |

|   |      |                                                            | 72        |

|   |      | 4.4.1.3 Evaluation of the Fast Energy Estimation Framework |           |

|   |      | 4.4.1.3.1 Energy Estimation for the Sequential             | . 0       |

|   |      |                                                            | 73        |

|   |      |                                                            |           |

|    |        |             | 4.4.1.3.2          | Energy       | Estimation          | for       | the         |

|----|--------|-------------|--------------------|--------------|---------------------|-----------|-------------|

|    |        |             |                    | Multi-Th     | readed Scenario .   |           | 75          |

|    |        | 4.4.2       | Server Power Mo    | deling       |                     |           | 77          |

|    |        |             | 4.4.2.1 Overall    | Server Pov   | ver Model           |           | 78          |

|    |        |             | 4.4.2.2 Overall    | Power of C   | Co-assigned Applie  | cations . | 79          |

|    | 4.5    | Concl       | usions             |              |                     |           | 80          |

| 5  | Tas    | k Sche      | duling with the    | Applicati    | on Signature        |           | 83          |

|    | 5.1    | Task S      | Scheduling with th | e Applicati  | on Signature        |           | 83          |

|    |        | 5.1.1       | Using the Apple    | ication Sign | nature for Energ    | y-Aware   | Task        |

|    |        |             | Scheduling         |              |                     |           | 85          |

|    |        | 5.1.2       | Compression Rat    | tio of the B | atch                |           | 85          |

|    | 5.2    | Task S      | Scheduling Approa  | ches         |                     |           | 86          |

|    |        | 5.2.1       |                    |              | amming Formulat     |           |             |

|    |        | 5.2.2       | Simulated Annea    | aling        |                     |           | 89          |

|    |        | 5.2.3       | Energy-Aware H     | euristic .   |                     |           | 91          |

|    | 5.3    | Exper       | Experimental Setup |              |                     |           |             |

|    |        | 5.3.1       |                    |              |                     |           |             |

|    |        |             | 5.3.1.1 Server     | Power Mod    | el and Overall Da   | ta Cente  | er Power 95 |

|    |        | 5.3.2       | Simulation Scena   | arios and Ta | ask Batch Compo     | sition .  | 96          |

|    | 5.4    | Result      | S                  |              |                     |           | 96          |

|    |        | 5.4.1       | Small Scale Scen   | ario         |                     |           | 97          |

|    |        | 5.4.2       | Large Scale Scen   | ario         |                     |           | 101         |

|    |        | 5.4.3       | Compression Rat    | tio of the B | atch                |           | 103         |

|    |        | 5.4.4       | Overall Results    |              |                     |           | 103         |

|    | 5.5    | Concl       | usions             |              |                     |           | 104         |

| 6  | Con    | clusio      | ns and Future V    | Vork         |                     |           | 105         |

|    | 6.1    | Summ        | ary and Conclusion | ons          |                     |           | 105         |

|    | 6.2    | Future Work |                    |              |                     | 108       |             |

|    |        | 6.2.1       |                    | 0            | f the Scope of th   |           | Oi.         |

|    |        | 0.00        |                    |              |                     |           |             |

|    |        | 6.2.2       |                    |              | 0                   |           |             |

|    |        | 6.2.3       | Supporting Anor    | naly Detect  | tion and Prediction | n         | 109         |

| Bi | ibliog | graphy      |                    |              |                     |           | 111         |

| A  | Gra    | mmat        | ical Evolution T   | echnique     |                     |           | 123         |

# List of Tables

| 2.1 | Hardware counters used as inputs to the power estimation models .   | 20 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | Coefficients values of the Speed-Up model                           | 20 |

| 2.3 | Results of the validation process                                   | 23 |

| 2.4 | Results of energy estimation using the application signature for    |    |

|     | multi-threaded applications $(Error_{CPU} (\%), Error_{Mem} (\%))$  | 24 |

| 3.1 | Comparison of our present work against other works                  | 34 |

| 4.1 | Hardware counters collected during the execution of the application |    |

|     | signature                                                           | 64 |

| 4.2 | Input dataset for each application                                  | 65 |

| 4.3 | HW counters collected to build the server power models              | 67 |

| 4.4 | Coefficient Values for all models                                   | 68 |

| 4.5 | Evaluation of the fast energy estimation framework. Sequential      |    |

|     | scenario                                                            | 74 |

| 4.6 | RMSE and MAE for training and test set in classical and             |    |

|     | grammatical evolution models                                        | 77 |

| 5.1 | Energy savings results for the small and large scale scenario when  |    |

|     | compared to the baseline Round-Robin policy                         | 97 |

# List of Figures

| 1.1  | Motivational Example: Comparison between traditional energy estimation techniques vs our proposed energy estimation approach. | 4  |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Comparison between Round-Robin policy vs an energy-aware task                                                                 |    |

|      | scheduling approach                                                                                                           | 7  |

| 2.1  | Overview of the application signature structure and execution                                                                 | 14 |

| 2.2  | Overview of the process for energy estimation using the application                                                           |    |

|      | signature                                                                                                                     | 16 |

| 2.3  | Application Signature for Multi-threaded applications                                                                         | 18 |

| 2.4  | Instructions per Cycle (blue) and the temporal evolution of the independent execution paths (green). Application signature    |    |

|      | samples (red). Benchmark: Calculix                                                                                            | 22 |

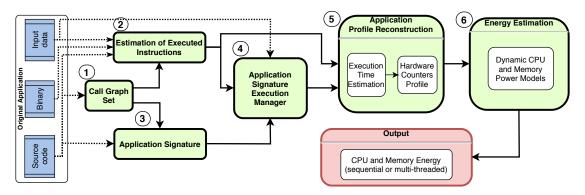

| 4.1  | Overview of the fast energy estimation framework modules                                                                      | 42 |

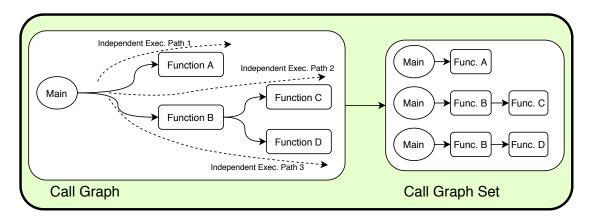

| 4.2  | Call Graph and Independent Execution Path                                                                                     | 44 |

| 4.3  | Overview of the estimation of executed instructions process (for the                                                          |    |

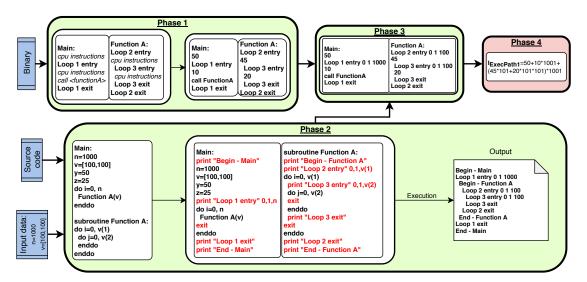

|      | independent execution path 1 obtained from the Call Graph Set)                                                                | 47 |

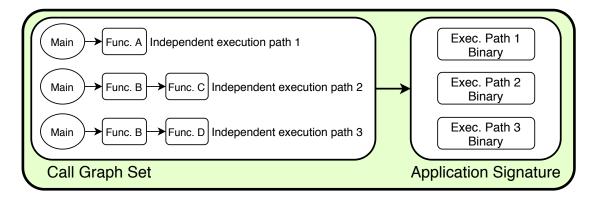

| 4.4  | Application Signature from the Call Graph Set                                                                                 | 49 |

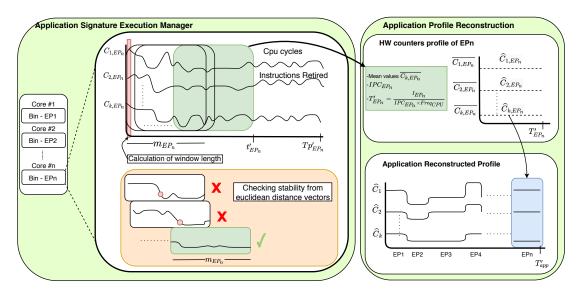

| 4.5  | Application signature execution manager and application profile                                                               |    |

|      | reconstruction                                                                                                                | 51 |

| 4.6  | Overview of the co-allocated tasks power model methodology                                                                    | 59 |

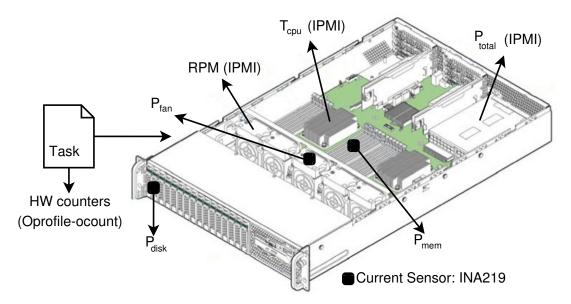

| 4.7  | Experimental Setup. Parameters collected during the experiments <sup>n</sup>                                                  | 66 |

| 4.8  | $CR_{fr}$ and Energy Est. Error vs (Application Signature Length -                                                            |    |

|      | Segment Division $(s)$ )                                                                                                      | 71 |

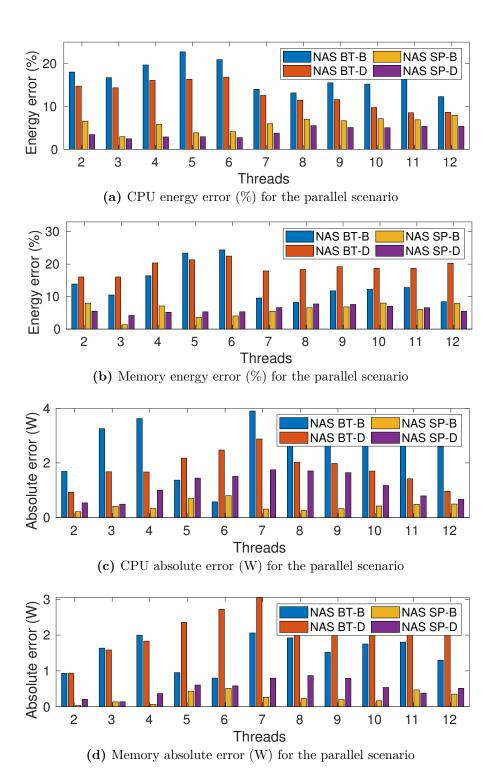

| 4.9  | Energy and absolute errors for the parallel scenario                                                                          | 76 |

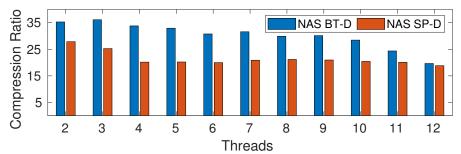

| 4.10 | Compression Ratio for the parallel scenario                                                                                   | 77 |

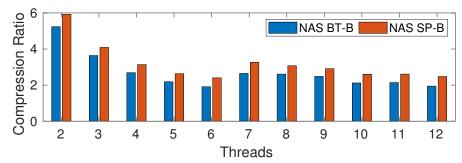

| 4.11 | RMSE of the overall server power model for each frequency                                                                     |    |

|      | configuration (Test set)                                                                                                      | 79 |

| 4.12 | Test set samples (subset). Power prediction of co-allocated tasks                                                             |    |

|      | using HW counter prediction                                                                                                   | 80 |

### $LIST\ OF\ FIGURES$

| 5.1 | Comparison between task scheduling approaches: Round-Robin vs   |

|-----|-----------------------------------------------------------------|

|     | Energy-Aware                                                    |

| 5.2 | Energy-Aware task scheduling approaches: input, output and task |

|     | allocation                                                      |

| 5.3 | Small scale scenario: Power profiles                            |

| 5.4 | Small scale scenario: Load profiles                             |

| 5.5 | Large scale scenario: Power profiles                            |

| 5.6 | Large scale scenario: Load profiles                             |

## Abbreviations

**BBV** Basic Block Vectors

**CFG** Control Flow Graph

CG Call Graph

**CGS** Call Graph Set

**CPU** Central Processing Unit

CR Compression Ratio

**DEVS** Discrete EVent Systems

**DIMM** Dual In-line Memory Module

**DVFS** Dynamic Voltage and Frequency Scaling

ETF Earliest Task First

**FIFO** First In First Out

**GA** Genetic Algorithms

**GE** Grammatical Evolution

GHGE Global Greenhouse Gas Emissions

**GPU** Graphics Processing Unit

**HPC** High Performance Computing

**HW** Hardware

ICT Information and Communications Technologies

**IPC** Instructions Per Cycle

IR Intermediate Representation

### ABBREVIATIONS

IRC In Row Cooling

IT Information Technology

LLC Last Level Cache

LTF Longest Task First

MAE Mean Absolute Error

MIC Many Integrated Cores

MILP Mixed Integer Linear Programming

NMRSE Normalized Root Mean Square Error

PCA Principal Component Analysis

**PSU** Power Supply Unit

PUE Power Usage Effectiveness

**RAPL** Running Average Power Limit

**RMS** Root Mean Square

**RMSE** Root Mean Square Error

**RPM** Revolutions Per Minute

**RR** Round-Robin

SaaS Software as a Service

**SVR** Support Vector Regression

## Abstract

Data centers are one of the most power hungry sections of the Information and Communications Technologies (ICT) sector. In the U.S in 2014, data centers consumed around the 1.8% of the total U.S electricity consumption. Worldwide data centers consumed in 2015 around 200 TWh of the global electricity usage. This electricity consumption is expected to increase to around 1200 TWh in 2025, which would represent 4.5% of the global electricity usage. One of the major contributors to the overall data center power is the IT or computing power, therefore there is a special interest to improve its energy efficiency. Scientific community has developed energy efficient techniques to reduce the energy consumption of IT equipment, such as resource management, power budgeting or power capping. These techniques assume the existence of a full dynamic power profiling, obtained through a previous full execution of the application. This full dynamic profiling is not viable in scenarios of long-running applications that are deployed in data centers, since performing a full dynamic profiling of a large batch of long-running applications is a time consuming process thus not energy-efficient. Therefore, in this work we propose the use of an application signature to estimate the energy in a fast way without the need to execute the application from beginning to end. The application signature is a reduced version, in terms of execution time, of the original application. developed a fast energy estimation framework that uses the application signature to make a quick energy estimation of long-running applications. The framework estimates, without performing a full profile of the application, the dynamic CPU and memory energy of both single-threaded and multi-threaded long-running application versions. Additionally, the fast energy framework is automatic and it has a modular design, allowing to change the functionality of each module without altering the functionality of the whole framework. We validated the accuracy of the fast energy estimation framework with a set of sequential and multi-threaded long-running applications. For the single-threaded version of the applications we obtained an RMS of 10.4% for the CPU energy estimation error and an RMS of 16.8% for the memory energy estimation error.

multi-threaded scenario, we used a subset of applications from the sequential version set. We achieved an RMS of 11.4% for the CPU energy estimation error and an RMS of 12.8% for the memory energy estimation error. We defined the concept of Compression Ratio (CR) as the ratio of total execution time of the original application, to the time it takes to estimate the energy through the fast energy estimation framework. A high CR value indicates that the energy is estimated much faster (CR times faster) than executing the whole application. We obtained Compression Ratios in the range from 10.1 to 191.2. Finally, we validated the usefulness of the energy estimation obtained from the application signature by applying three different energy-efficient task scheduling approaches: i) An optimal approach using a Mixed Integer Linear Programming (MILP) technique, ii) An energy-aware heuristic approach that uses a Longest Task First (LTF) algorithm together with an energy-efficient task allocation based on the current servers consumption, and iii) We proposed an implementation of a metaheuristic using a Simulated Annealing process. The results obtained through the energy estimation (obtained through the application signature) values are compared with the real energy values. We obtained energy savings from 8% to 19%, and more importantly the energy savings obtained with the application signature approach are similar to the values obtained with the real energy measurements, with an energy savings difference below 1.5%.

## Resumen

Los centros de datos son una de las secciones del sector de Tecnologías de la Información y Comunicaciones (TIC) que tienen mayor consumo energético. Durante el año 2014 en EE. UU., los centros de datos consumieron alrededor del 1.8% del consumo eléctrico total en dicho país. A nivel mundial, los centros de datos representaron en el año 2015 alrededor de 200 TWh respecto al consumo eléctrico mundial. Según estimaciones, este consumo eléctrico puede aumentar hasta unos 1200 TWh en el año 2025, lo que representaría el 4.5% del consumo eléctrico global. Uno de los mayores contribuidores al consumo global en los centros de datos es el representado por los equipos de computación o consumo de IT. A nivel computacional, se han desarrollado diversas técnicas para reducir el consumo de IT como pueden ser, la gestión de recursos, presupuestos de potencia y la limitación de consumo de los servidores ubicados en los centros de datos. Para poder aplicar estas técnicas se asume la existencia de un perfilado (profiling) previo obtenido a través de una ejecución completa de la aplicación. En escenarios donde se ejecutan grandes despliegues de aplicaciones de larga duración no resulta viable realizar un profiling previo debido a que es un proceso que demanda elevados tiempos de ejecución y, por lo tanto, no es eficiente energéticamente. Teniendo en cuenta la problemática expuesta anteriormente, en este trabajo se ha desarrollado el concepto de firma de la aplicación cuyo uso tiene la finalidad de estimar la energía sin tener que ejecutar la aplicación en su totalidad. La firma de la aplicación se define como una versión reducida, respecto al tiempo de ejecución, de la aplicación original. Se ha desarrollado un framework de estimación rápida de energía que utiliza la firma de la aplicación para estimar la energía sin tener que ejecutar completamente las aplicaciones. El framework estima la energía de CPU y memoria, tanto de aplicaciones secuenciales como de aplicaciones de tipo paralelas (multihilo). A su vez, el framework se ejecuta de forma automática y tiene un diseño modular, permitiendo de esta forma reemplazar la funcionalidad interna de un módulo sin necesidad de alterar la funcionalidad de todo el framework. Se ha validado la precisión del framework de estimación rápida de energía con un conjunto representativo de ejecuciones

secuenciales y paralelas, obteniendo unos errores RMS de 10.4% y 16.8% de estimación de energía de CPU y memoria respectivamente para el caso de aplicaciones secuenciales. En el caso de aplicaciones paralelas, se ha trabajado con un subconjunto de las aplicaciones del caso secuencial y se han obtenido errores RMS de 11.4% y 12.8% de estimación de energía de CPU y memoria respectivamente. Por otra parte, se ha definido el concepto Ratio de Compresión (CR) como el ratio de la ejecución total de la aplicación original respecto al tiempo que tarda el framework en estimar la energía de la aplicación. Un valor alto de Ratio de Compresión indica que el framework estima la energía de forma mucho más rápida (CR veces más rápida) que la ejecución total de la aplicación. Se obtienen Ratios de Compresión que están en el rango entre 10.1 hasta 191.2. Finalmente, se ha evaluado la utilidad de la información de energía obtenida mediante la firma de la aplicación gracias a la aplicación de tres propuestas de planificación de tareas: i) utilizando un modelo de Programación Lineal Entera Mixta (MILP), ii) haciendo uso de una heurística energéticamente eficiente que utiliza un algoritmo de tipo LTF (tareas de larga ejecución se ejecutan primero) junto con una eficiente colocación de tareas en los servidores del centro de datos y, iii) se propone una implementación de una metaheurística basada en un algoritmo de recocido simulado (Simulated Annealing). Los resultados de estimación de energía global del centro de datos obtenidos con los datos de la firma de la aplicación se han comparado con los datos reales de energía de las aplicaciones. Se han obtenido unos ahorros de energía entre el 8% y 19%, y lo que es más importante los valores de ahorro de energía obtenidos con la información de la firma son similares, con un error inferior al 1.5%, respecto a los ahorros de energía obtenidos con los valores reales de energía de las aplicaciones.

# Chapter 1

### Introduction

### 1.1 Motivation

Data center facilities are high power consumers. It was estimated that data centers already accounted for at least 1.5% of the worldwide total electricity consumption in 2010 [70]. In the U.S at the year 2014, data centers consumed about 70 billion kWh which represented the 1.8% of the total U.S electricity consumption. It is estimated that U.S data centers will consume, in the year 2020, approximately 73 billion kWh [111].

Moreover, worldwide data centers consumed in 2015 around 200 TWh of the global electricity usage and it is expected to increase its electricity consumption to around 1200 TWh in 2025, which would represent 4.5% of the global electricity usage [5]. The sector of Information and Communication Technology (ICT), including data centers, generates up to 2% of the global  $C0_2$  emissions [122]. In terms of the global greenhouse gas emissions (GHGE), data centers alone are projected to have the second fastest growing (behind Smart Phones) GHGE footprint from all of the ICT sector [14].

The overall energy use of the IT equipment (servers, storage devices, and network) has increased from 92 TWh (2010) to 130 TWh (2018) [87]. On the one hand, the energy efficiency solutions adopted in data centers in the last decade have enabled a large growth in services without a high increase of the energy use. On the other hand, there are estimations indicating that the computing resources of the data centers are going to double within the next 3 to 4 years. Therefore, the need to improve energy efficiency in data centers will be required to manage the possible energy growth [87]. This idea of improving energy efficiency is backed by several studies where they indicate the necessity of targeting energy efficiency as a key strategic initiative in data centers [120] [9] [13] [57].

There is an special interest to improve energy efficiency of computing (or IT) power since it is the major contributor to overall data center power (another important contributor is the cooling power) [12]. There are proactive approaches to reduce the overall energy consumption, such as, proactive thermal management techniques that are used to reduce the cooling energy and minimize the overheating of IT equipment, thus, minimizing the IT power consumption due to leakage [74]. Other energy-efficient techniques focus mainly in the IT power equipment, such as:

- i) **Resource management:** where an energy-efficient or energy-aware task scheduling approach is applied for an optimal task or job allocation [134] [1] [8].

- ii) **Power budgeting:** where policies or rules are established to distribute efficiently the power budget among all the servers from the data center [131] [108] [59].

- iii) **Power capping:** ensures that the maximum peak power consumption of each server remains below a cap value [107] [19] [86] [118].

Moreover, when data centers are integrated in the Smart Grid, the regulation capabilities of servers enable the participation in demand-response programs, allowing to reduce the energy costs in data centers [24]. The previous techniques are usually used proactively and assume the existence of either a full dynamic power profiling of the applications (obtained through a previous full execution of the application), or power models that predict the power consumption of the applications that are going to be executed in the servers.

The work of this thesis is focused on long-running, data-intensive and iterative applications. This type of application is usually found in many scientific computing or HPC scenarios. Additionally, besides taking too much time to finalize the execution, these applications are CPU and memory intensive, resulting in high energy consumption in data centers, characteristics that make this type of application interesting for energy efficiency purposes.

In scenarios of long-running applications deployed in data centers the process to perform a full dynamic power profiling is not viable since performing a full profile of a large batch of long-running applications is a time consuming process and therefore, is not energy-efficient. These long-running applications, as we have previously mentioned, have the characteristic to be iterative, data-intensive, and often they are formed by computational intensive kernels such as, matrix multiplication. These kernels can be found in scientific applications (e.g., fluid dynamics, climate modeling) [51] and more recently in artificial intelligence applications [135] [123]. Long-running applications are

executed in large-scale data centers, for example, the *Barcelona Supercomputing Center\** or in small-scale data centers such as *Madrid Supercomputing and Visualization Center†*.

Moreover, these types of applications can be executed with multiple instances of the same application in a single-threaded way, and also, can be executed in a multi-threaded way using multiple cores as occur in the High Performance Computing (HPC) scenario. Also, long-running applications can be found in non-cloud and cloud environments. In non-cloud environments the applications are executed directly in the server. This type of environment is usually present in HPC scenarios. In cloud environments the long-running applications can present themselves as a Software as a Service (SaaS) type of applications like in services such as Google Cloud<sup>‡</sup>.

Long-running applications are usually deployed in batches and they are commonly executed with different input datasets, hence these applications show a different behaviour each time their input changes. This would require to redo a full dynamic profiling every time that the input changes. Obviously, this is not an energy-efficient process.

Therefore, in this work we propose the use of an application signature to make a fast energy estimation of long-running single and multi-threaded applications without the need to perform a complete execution of the original application. We define the **application signature** as a reduced version, in terms of execution time, of the original application. Also, the **application signature** is used to make a **performance prediction**, which is a prediction of the execution time of the applications before they are executed in the servers of the data centers. We developed a fast energy estimation framework that uses the application signature to estimate in a fast way the energy without executing the application from beginning to end, thus allowing the development of proactive energy-efficient optimization policies adapted to the application.

Hence, in this work we use the information provided by the application signature to apply different energy-efficient task scheduling approaches (resource management) in order to reduce the **makespan** of the original batch, and therefore improve the energy efficiency in data centers. The **makespan** is defined as the total execution time of the batch of applications that will run in the data center. Without the application signature those energy-aware scheduling approaches would require a full dynamic profiling from the complete execution of the applications preventing them to be applied in an efficient way.

<sup>\*</sup>https://www.bsc.es/

<sup>†</sup>https://www.cesvima.upm.es/

<sup>&</sup>lt;sup>‡</sup>https://cloud.google.com/

In this work we do not address experimentally the problem of using other energy-efficient techniques such as power budgeting or power capping in an experimental way. Nonetheless, the fast energy estimation framework using the application signature can be used to solve the problems of such techniques.

Finally, although we have not used any stream processing applications, we consider that the fast energy framework should be able to work with them. Moreover, HPC over cloud applications could also be a potential target for the proposed framework. Finally, applications such as data-intensive interactive or latency-sensitive online applications would not be able to work with the developed framework.

### 1.2 Problem Formulation

(a) Traditional approach: Energy estimation through the execution of the original application

(b) Our approach: Energy estimation through the execution of the application signature

Figure 1.1: Motivational Example: Comparison between traditional energy estimation techniques vs our proposed energy estimation approach

To illustrate our proposed solution using the application signature we present the problem formulation as a motivational example. The code presented in Application 1 shows a simple loop-based application. The application starts by defining a set of variables (n, v, y and z) that represent the **input data**. The input data can be defined in the *Main* function of the source code (as in this example) or it can be read from an external source such as a file. The application continues with a main loop that iterates until the threshold set by the variable n.

Inside the loop, two functions (FunctionA and FunctionB) are called. We can see that the execution can be divided in three **execution paths**:

- $Main \rightarrow FunctionA$  (Path 1).

- $Main \rightarrow FunctionB \rightarrow FunctionC$  (Path 2).

- $Main \rightarrow FunctionB \rightarrow FunctionD$  (Path 3).

The iterative structure shown in Application 1 has been selected because it appears in many long-running applications [101] [81] [21].

#### **Application 1** Motivational Example: Long-running application

```

1: function Main

2:

n \leftarrow 1000

v \leftarrow [100, 100]

3:

4:

y \leftarrow 50

5:

z \leftarrow 25

6:

for i \leftarrow 0 to n do

FUNCTIONA(v)

7:

FunctionB(y,z)

8:

9:

end for

10: end function

11: function FunctionA

for i \leftarrow 0 to v(1) do

12:

Computation

13:

14:

for j \leftarrow 0 to v(2) do

15:

Computation

16:

end for

end for

17:

18: end function

function FunctionB

19:

20:

FUNCTIONC(y)

21:

FUNCTIOND(z)

22: end function

23: function FunctionC

24:

for i \leftarrow 0 to y do

25:

Computation

26:

end for

27: end function

28: function FunctionD

29:

for i \leftarrow 0 to z do

30:

Computation

31:

end for

32: end function

```

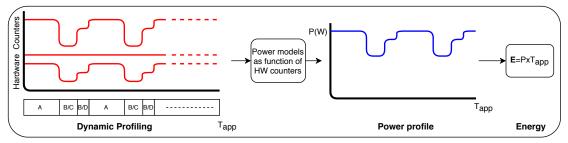

Figure 1.1a shows the traditional approach of energy estimation by doing a full profiling of the whole execution of the application. First, we execute the whole application and collect a set of hardware counters through a dynamic profiling.

Then, we obtain a power profile (P) by using power models as a function of the hardware counters previously collected. Finally, from the power profile and the execution time  $(T_{app})$  of the application we can calculate the energy. In the case of long-running applications this process is not efficient since the execution times are usually long (hours or days). To solve this problem we use an **application** signature.

We propose an energy estimation process through the application signature, as shown in Fig. 1.1b. First, we execute the application signature and collect a set of hardware counters. The application signature execution is composed by a shorter execution of each independent path, i.e we execute Path 1 for a short period of time, then execute Path 2, and so on. Therefore, the execution time of the application signature  $(T_{sig})$  is significantly lower than the execution time of the original application. The next step is to reconstruct the application profile. To reconstruct the profiles we extend in time the values of the hardware counters obtained through the execution of the application signature. Each hardware counter profile from each path is extended until it has a length equal to the **estimated execution time path**  $(t_a, t_{b/c})$  and  $(t_b)$ .

The execution time of each path is estimated through the **estimated** executed instructions (obtained from the source code and binary of the original application) and the Instructions per Cycle (IPC) of each path (obtained from the application signature). The total estimated execution time of the application  $(T'_{app})$  can be obtained by adding the estimated execution time of each path. To minimize error, the value of  $T'_{app}$  should be the closest possible to  $T_{app}$ .

Finally, we use power models as a function of hardware counters with the application reconstructed profile to obtain a power profile (P'). From the power profile we can calculate the energy (E') of the application. Since the application signature executes each independent execution path independently the power profile P' is not the same as the power profile P of the original application. However, the estimated energy E' is equal to the energy E estimated from the original application, since the area under the curve of both power profiles (P) and (P') should be the same.

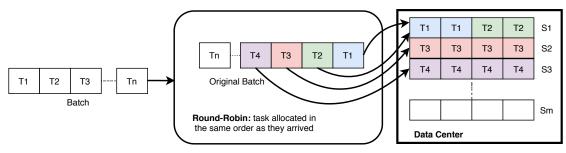

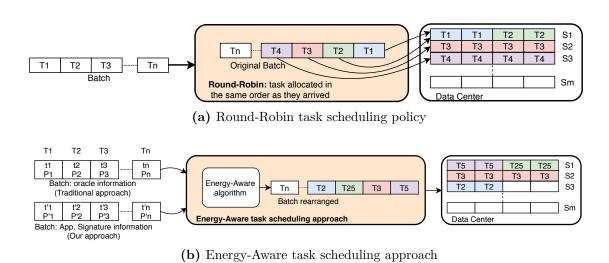

As we have previously commented, in order to apply energy-aware task scheduling approaches we need to extract information such as power or execution time from the applications before they are executed in the data center. When is not possible to gather these type of information a Round-Robin process is applied to the batch. Figure 1.2a shows the task allocation process of a batch of  $T_n$  tasks using the Round-Robin approach. Each task is allocated to an available server  $(S_m)$  in the same order as they originally arrived. The example shows a

(a) Traditional approach: Round-Robin policy

(b) Our approach: Energy-aware task scheduling approach using the application signature

Figure 1.2: Comparison between Round-Robin policy vs an energy-aware task scheduling approach

data center with m servers with each server equipped with 4 cores. The first  $T_1$  task requires 2 cores and is allocated to server  $S_1$ , similarly task  $T_2$  requires 2 cores and is allocated in server  $S_1$  since it has enough available resources. When a task can not be allocated in a server it goes into a waiting queue until there is enough resources available to be executed. The Round-Robin policy is simple and therefore, easy to implement. Although, the Round-Robin policy is not an energy-efficient task scheduling process since the tasks are not allocated aiming to reduce the makespan or the power consumption of the servers.

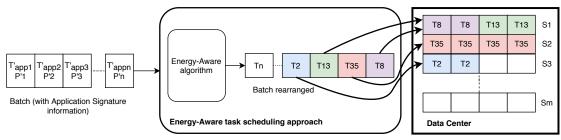

Energy-efficient proactive task scheduling approaches can be used to reduce the energy consumption in data centers by reducing the makespan of the original batch. Figure 1.2b shows that an energy-aware task scheduling approach is used to rearranged the original batch. By changing the tasks execution order the makespan can be minimized. In the figure we can see that the tasks are allocated differently when compared to the Round-Robin policy (tasks  $T_8$  and  $T_{13}$  are allocated in server  $S_1$ , and so on). This change in the tasks order of execution is the result of applying an energy-aware algorithm to minimize the makespan of the original batch. The energy-aware algorithm needs information, such as the execution time or the mean power consumption from the tasks that will be executed. This information can be obtained through a full dynamic profiling of each task (not very energy-efficient process). By executing the application signature we can obtain the information of

execution time  $T'_{app_i}$  and mean power consumption  $P'_i$  without the need to perform a full profiling of each task of the batch. Thus, allowing to apply an energy-aware task scheduling process in a more efficient way.

### 1.3 Thesis Contributions

The contributions of this PhD. thesis are described in 3 sections: i) the application signature as a proof of concept, ii) the implementation of a fast energy estimation framework that uses the application signature and, iii) using energy-aware task scheduling approaches with the information provided by the application signature.

- Application signature as a proof of concept:

- We present the concept of application signature and its use to obtain a

fast CPU and memory energy estimation of long-running applications.

A proof of concept of the use of the application signature is proposed

for single-threaded and multi-threaded applications.

- We obtain errors for the estimation of the dynamic CPU and memory energy consumption below 8.0% when the estimated energy is compared against the energy consumption of the complete execution of the application. For the multi-threaded applications we obtain an RMSE equal to 12.7% when we compare the dynamic energy estimated from the application signature against the dynamic energy from the whole multi-threaded execution of the application. We obtain an average value of almost 9.8 for the CR (Compression Ratio, defined as a relation between the total execution time and the time the application signature takes to estimate the energy consumption) of all the benchmarks, indicating that using the application signature we are able to make a dynamic energy consumption estimation almost 10 times faster than the original execution of the application.

- Fast energy estimation framework:

- We propose a fast energy estimation framework for long-running applications that uses the application signature to estimate the dynamic CPU and memory energy without the need to execute the whole application. The framework is able to estimate the energy for both sequential and multi-threaded applications.

- The framework estimates the energy in an automatic way. The design of the framework is modular, allowing to change the internal functionality of each module, due to preferences or technical availability, without affecting the functionality of the whole framework.

- We validate the accuracy of the fast energy estimation framework with a set of sequential and multi-threaded long-running applications. For the sequential version of the applications we obtain an RMS of 10.4% for the CPU energy estimation error and an RMS of 16.8% for the memory energy estimation error. In case of the multi-threaded scenario we use a subset of applications from the sequential version set. We achieve an RMS of 11.4% for the CPU energy estimation error and an RMS of 12.8% for the memory energy estimation error. We obtain Compression Ratios in the range from 10.1 to 191.2.

- We model dynamic CPU and memory power given the per-application hardware counters, using Grammatical Evolution techniques. We obtain absolute power errors equals to 4.4W and 3.7W, for the dynamic CPU and memory power model respectively. We use analytical fan and leakage power models to obtain overall server power. Our models are trained and tested using a wide range of sequential and parallel workloads, under various DVFS setups, improving error by a 32% when compared to a traditional approach.

- We show that our model is robust enough to predict the power consumption of two different tasks when they run co-assigned in the same server, given the hardware counters of the overall server. Also, we develop a methodology to, given the hardware counters of individual tasks, obtain the hardware counters when both applications are co-allocated (without executing the co-allocated applications).

- Energy-aware task scheduling using the application signature:

- We validate the usefulness of the energy estimation information (mean power and estimated execution time) obtained from the application signature by applying different energy-efficient task scheduling approaches. The results obtained through the energy estimation values are compared with the real energy values. The values of the energy estimation from the fast energy estimation framework are presented as the application signature information. The real energy values are presented as the oracle information.

- We use three different task scheduling approaches:

- i) An optimal approach using a Mixed Integer Linear Programming (MILP) technique.

- ii) An energy-aware heuristic approach that uses a Longest Task First (LTF) algorithm together with an energy-efficient task allocation based on the current servers consumption.

- iii) We propose an implementation of a metaheuristic using a Simulated Annealing process.

The resulting overall data center energy consumption from each task scheduling approach is compared against a Round-Robin (RR) approach.

- We obtain energy savings from 8% to 19%, and more importantly the energy savings obtained with the application signature information are similar as the values obtained with the oracle information, with energy savings difference below 1.5%.

- We define the Compression Ratio of the Batch of applications as the ratio of total execution time of the original batch using the Round-Robin approach to the total execution time of extracting and executing the Application Signature of the whole batch. We obtained Compression Ratios around 39.7 to 45.8.

### 1.4 Thesis Structure

The remainder of this work is organized as follows:

- Chapter 2 explains the application signature as a proof of concept. The concept of the application signature is explained and an experimental proof of concept is applied to validate the use of the application signature as a mean to estimate the energy of the applications. A proper understanding of the proof of concept presented in this chapter makes it easier to follow the content of Chapter 3, where we present the related work.

- Chapter 3 presents the related work associated with this PhD. thesis. We cover works associated with similar approaches that uses an application signature and different energy estimation process applied in data centers.

- Chapter 4 describes the fast energy estimation framework that uses the application signature. We show a full implementation of the framework and also, the results of applying the framework in an online manner with a set of long-running applications. Additionally, in this chapter we present a

methodology to obtain an overall server power model using Grammatical Evolution techniques.

- Chapter 5 shows the results of using the information provided by the application signature for energy-efficient task scheduling approaches.

- Chapter 6 provides the conclusions obtained from this work and also, presents a summary of the future research works derived from this PhD. thesis.

### 1.5 Publications and Grants

In this section we present the journal and conference publications associated with this work, as well as awarded grants.

### 1.5.1 Journal papers

We have presented our work in an international journal. Moreover, at the moment of writing this work there is one article in review process:

- J. C. Salinas-Hilburg, M. Zapater, J. M. Moya, J. L. Ayala, "Fast energy estimation framework for long-running applications", Future Generation Computer Systems (2021) (Chapter 4 of this PhD. thesis).

- J. C. Salinas-Hilburg, M. Zapater, J. M. Moya, J. L. Ayala, "Energy-Aware Task Scheduling in Data Centers using an Application Signature", Computers and Electrical Engineering (2020) (Review process) (Chapter 5 of this PhD. thesis).

## 1.5.2 Conference papers

Additionally, the results of this thesis were presented in the following international peer-reviewed conferences:

- J. C. Salinas-Hilburg, M. Zapater, J. M. Moya, J. L. Ayala, "Fast Energy Estimation Through Partial Execution of HPC Applications", International Conference on Application-specific Systems, Architectures and Processors (ASAP) (2018) (Chapter 2 of this PhD. thesis).

- J. C. Salinas-Hilburg, M. Zapater, J. L. Risco Martín, J. M. Moya, J. L. Ayala, "Unsupervised Power Modeling of Co-Allocated Workloads for Energy Efficiency in Data Centers", Design, Automation and Test in Europe (DATE) (2016) (Chapter 5 of this PhD. thesis).

• J. C. Salinas-Hilburg, M. Zapater, J. L. Risco Martín, J. M. Moya, J. L. Ayala, "Using grammatical evolution techniques to model the dynamic power consumption of enterprise servers", International Conference on Complex, Intelligent, and Software Intensive Systems (CISIS) (2015) (Chapter 5 of this PhD. thesis).

### 1.5.3 Mobility Grants

The author of this dissertation has been awarded with a mobility research grant from the European Network of Excellence on High Performance and Embedded Architecture and Compilation (HiPEAC), for a research stay of 3 months in the Performance and Energy Aware Computing lab (PeacLab) at Boston University (2017).

In the next chapter the reader will find a proof of concept of the application signature. We will show the technical details of how the application signature works and also, how is used to estimate the energy of the applications.

## Chapter 2

# Energy Estimation with an Application Signature

In this chapter we present a proof of concept where we show that is possible to estimate the energy of an application without the need to execute it completely. We define the concept of application signature and how it is used to estimate the energy of the applications in a fast way. Additionally, we present the results of energy estimation from the application signature of a large set of heterogeneous applications.

## 2.1 Application Signature

In this section we present our methodology to construct the application signature. The **application signature** is defined as a reduced version (in terms of the execution time) of the original application. The main purpose of the application signature is to estimate the energy and performance of the whole execution of the application without the need to execute it completely.

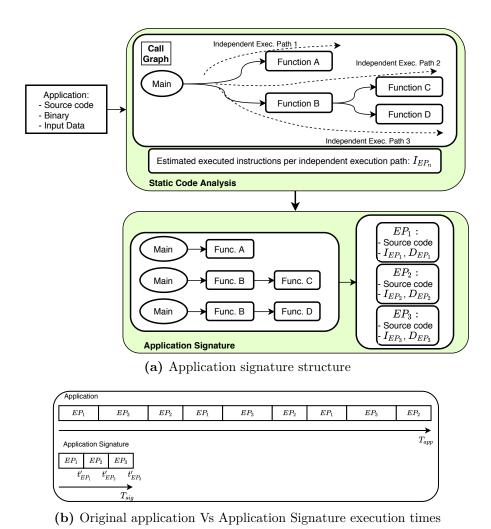

Figure 2.1a shows an overview of the application signature structure. The source code/binary of the application together with its correspondent input data is analyzed statically to extract information about the Call Graph (CG) and the estimated executed instructions per independent execution path. We define an *independent execution path* as a path from the Call Graph obtained through the following process: i) start the path search at the root node (main function), ii) if an edge can be followed, do so; iii) if not, stop the path search. The application signature presents a two layer architecture. The first layer is composed by the source codes from all the independent execution paths of the application; while the second layer contains static code analysis information

Figure 2.1: Overview of the application signature structure and execution

required for the energy consumption estimation. This information are the values of  $I_{EP_1}$ ,  $I_{EP_2}$ ,...,  $I_{EP_n}$  that represent the estimated executed instructions from each independent execution path and the values of  $D_{EP_1}$ ,  $D_{EP_2}$ ,...,  $D_{EP_n}$  indicate the input data to each independent execution path. An application signature execution manager creates the binaries of each source code and executes each independent execution path with their respective input data. The manager stops the execution of each independent execution path until a desired threshold criteria of executed instructions per path is reached. By doing this we can execute each independent execution path of the application separately and for a very short period of time, much shorter than the original execution. The application signature is directly associated with the input data of the original application, therefore when the application change its input data a new application signature is built.

Figure. 2.1b shows the comparison between the execution time of the application  $(T_{app})$  against the execution time of the application signature  $(T_{sig})$ , which must be lower by definition. The relation between the two execution times is the **Compression Ratio** (CR) and indicates the acceleration of the energy estimation process. The value of CR is defined in Eq. 2.1. The value of  $t'_{EP_j}$  represents the execution time of the partial execution of the  $j^{th}$  independent execution path of the application. By adding the partial execution of all the independent execution paths we estimate the total execution time of the application signature:  $T_{sig}$   $(T_{sig} << T_{app})$ .

$$CR = \frac{T_{app}}{T_{sig}}$$

where  $T_{sig} = \sum_{j=1}^{N} t'_{EP_j}$  (2.1)

## 2.1.1 Static Code Analysis

The main purpose of a static code analysis is to obtain information without the need to execute the application, such as the number of resources an application will use during runtime. The COSTA tool [3] [2] is a static code analysis tool that can perform such task. It can estimate an upper bound of the resource consumption of the application and, among other parameters, it can estimate the number of instructions executed per independent execution path considering the input data of the application. Also, COSTA builds the Call Graph listing all the functions and the calls between them. Although COSTA is a static code analysis tool intended to work for JAVA bytecode the concepts and techniques can be applied to the static code analysis of applications in other programming languages. Another tool called Mira [89] is a framework for static performance modeling and analysis and can estimate the number of executed instructions for large scale or HPC applications programmed in C/C++ languages.

In this chapter, we made use of the information that a regular static code analysis profiler (such as COSTA or the Mira framework) provides. In particular, we rely on the Call Graph extraction and the estimation of executed instructions per each independent execution path. The Call Graph allows us to know the number and the hierarchy of the whole set of paths. According to this, we can isolate each independent execution path to perform its partial execution.

The static code analysis process takes into account the input data of the application to estimate the number of executed instructions. An example of input data typically found in large scale or HPC applications is the number of timesteps. The number of timesteps usually determines the number of iterations of the main loop of the application which heavily affects the number of estimated executed

instructions. The estimated number of executed instructions together with the Instructions per Cycle calculated from each partial execution of each independent path is used to estimate the total execution time of each independent execution path  $(T'_{EP_n} = (I_{EP_n})/(IPC_{EP_n} \times Freq_{CPU}))$ , as can be seen in Section 2.1.2.

## 2.1.2 Dynamic Profiling of the Application Signature

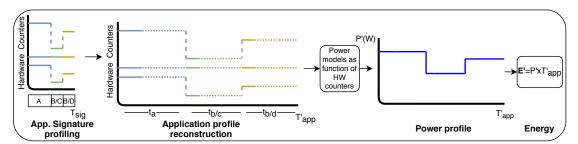

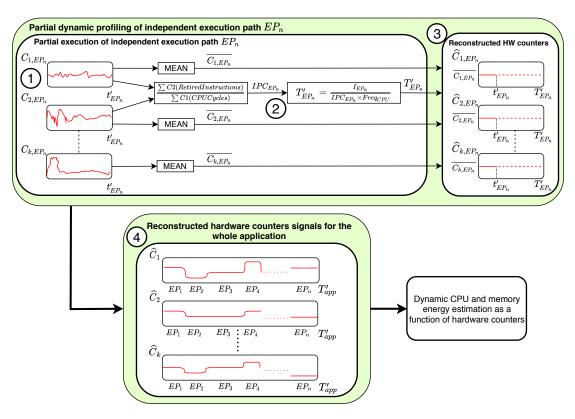

**Figure 2.2:** Overview of the process for energy estimation using the application signature

In order to estimate the energy consumption using the application signature we need to apply the process shown on Fig. 2.2. The first step is to perform a partial dynamic profiling of the application signature, which is formed by the partial execution of each independent execution path. This partial dynamic profiling takes much less time than the complete dynamic profiling of the whole application. The purpose of the dynamic profiling step is to make a quick acquisition of the hardware counters and calculate the Instructions per Cycle (IPC) of each partial execution. By combining the information of  $I_{EP_n}$  and the IPC from each partial execution we are able to estimate the total execution time  $T'_{app}$  (i.e. performance) and also obtain an equivalent temporal profile of hardware counters for the complete execution. As we can see in the dynamic profiling block from Fig. 2.2:

- 1. Each independent execution path is partially executed during a short amount of time  $t'_{EP_n}$  and the hardware counters  $(C_{1,EP_n}, C_{2,EP_n}, ..., C_{k,EP_n})$  are collected. Each independent execution path is partially executed by the application signature execution manager until the instructions retired reach a threshold equal to  $\alpha \times I_{EP_n}$ , where  $\alpha \in [0,1]$  and  $I_{EP_n}$  is the estimated executed instructions for the  $n^{th}$  independent execution path. The value of  $\alpha$  should be low enough to partially execute the path (providing the expected acceleration), while still targeting a significant amount of execution time to gather the hardware counters.

- 2. The IPC of the partial execution for the  $n^{th}$  independent execution path is obtained and then the estimated total execution time of the path  $EP_n$  is calculated as follows:  $T'_{EP_n} = (I_{EP_n})/(IPC_{EP_n} \times Freq_{CPU})$  (CPU equation time or basic performance equation).

- 3. The temporal profile of the hardware counters for the  $n^{th}$  independent execution path can be reconstructed by forming signals with duration  $T'_{EP_n}$  and amplitude equal to the mean value of each hardware counter  $(\hat{C}_{1,fn}, \hat{C}_{2,fn}, ..., \hat{C}_{k,fn})$ .

- 4. The temporal profiles of each hardware counter for the complete application are built by aligning the temporal profiles of the hardware counters from each independent execution path. These hardware counter profiles have a duration equal to the total estimated execution time  $T'_{app}$  and amplitude equal to the mean value of the respective hardware counters of each path. These reconstructed profiles of hardware counters for the whole application are equivalent, in terms of reflecting the dynamic CPU and memory energy, to the profiles of hardware counters obtained through a full dynamic profiling of the original application.

### 2.1.3 Energy Estimation

Figure 2.2 shows that the dynamic CPU and memory energy is estimated through the reconstructed hardware counter signals obtained with the execution of the application signature. The dynamic CPU and memory energy is estimated using the CPU and memory power models explained in Section 4.2. We have two separated power models for dynamic CPU and memory as a function of the hardware counters:  $\hat{P}_x = f(\hat{C}_1, \hat{C}_2, ..., \hat{C}_k)$ , where x is CPU for the dynamic CPU power or Mem for the dynamic memory power. The expression for the dynamic CPU and Memory power  $(\hat{P}_x)$  can be found in Section 4.2.

The energy is estimated by adding all the instantaneous dynamic CPU or memory power values and then multiplying by the sampling period sm, as shown in Eq. 2.2, where x is for CPU or Mem. The energy is calculated over a period equals to  $T'_{app}$  and for the set B formed by the temporal samples of the estimated power signal  $(\hat{P}_x)$ . These dynamic CPU and memory energies are obtained through the reconstructed hardware counters signals that comes from the application signature.

$$\hat{E}_x = \left[\sum_{n \in B} \hat{P}_x[n]\right] \times sm \tag{2.2}$$

## 2.2 Application Signature for Multi-Threaded Applications

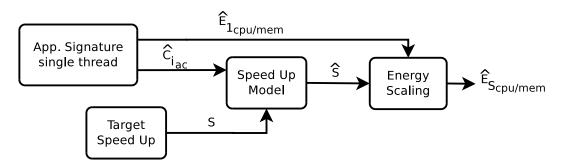

Figure 2.3: Application Signature for Multi-threaded applications

In order to obtain an estimation of the dynamic CPU and memory energy for multi-threaded applications without the need to run the entire application we apply the process shown in Fig. 2.3. First, we extract the application signature of the single-threaded version of the application to obtain the dynamic CPU and memory energy estimation  $(\widehat{E}_{1cpu/mem})$  and also the accumulative values of the estimated hardware counters  $(\widehat{C}_{i_{ac}})$ . As a next step, we use a speed-up model to obtain an estimated acceleration  $(\widehat{S})$  as a function of the accumulative values of the estimated hardware counters and the desired speed-up (S). The **speed-up** is defined as the ratio between the runtime of a single-threaded execution divided by the runtime of a multi-threaded execution (i.e, if we execute a parallel application with two threads we should expect that the runtime of the multi-threaded execution is half the runtime of the single-threaded execution, taking into account that the parallel execution has minimal synchronization delays). It should be noted that the target speed-up is equal to the numbers of threads the application will run in order to

perform a parallel execution. Finally, an energy scaling is made to estimate the dynamic CPU and memory energy for the multi-threaded run:

$$\widehat{E}_{Scpu/mem} = \frac{\widehat{E}_{1cpu/mem}}{\widehat{S}}$$

(2.3)

The process of estimating the dynamic CPU and memory energy for multi-threaded applications can be applied to applications that have a data parallelism form of parallelization, where the threads are executing the same task and the performance exhibited by each other is almost the same. This form of parallelization can be found in multiple large scale or HPC scenarios and has been addressed by other authors [124].

The speed-up model for the accelerations ranging from 1 to the number of cores (c) is a linear model where the estimated speed-up is equal to the target speed-up, while for accelerations from the number of cores plus one (c+1) to the total number of hardware threads (h) we develop a speed-up model as a function the accumulative values of the estimated hardware counters  $(\hat{C}_{iac})$  and the target speed-up (S), as shown in Eq. 2.4.

$$\widehat{S} = \begin{cases} S & S \in [1, c] \\ \beta_0 + \sum_{i=1}^{l} \widehat{C}_{i_{ac}} * \beta_i + S * \beta_{l+1} & S \in [c+1, h] \end{cases}$$

(2.4)

We assume that when a parallel application runs a number of threads equal to the number of cores each thread is going to run separately in each core, so the speed-up must be lineal as a function of the number of cores. In the case of running more than c+1 threads each thread is going to share core resources with another thread so this linear behaviour with the number of hardware threads cannot be assumed. The speed-up model for accelerations above c+1 is obtained offline by using a partial least-squares regression model taking as input the accumulative values of the hardware counters and the actual speed-up both obtained by running a set of benchmarks with a variable numbers of threads (from c+1 to h).

## 2.3 Experimental Setup

The validation of the aforementioned methodology takes place in an Intel server (S2600GZ) based on the Intel Decathlete 2.0 Open Compute Project server board. The server is equipped with one Intel 6-core SandyBridge-EP processor providing

Table 2.1: Hardware counters used as inputs to the power estimation models

|    | Description                 |

|----|-----------------------------|

| C1 | Clock cycles                |

| C2 | Instructions retired        |

| С3 | LLC misses                  |

| C4 | L2D Cache misses            |

| C5 | Branch instructions retired |

| C6 | Resource stalls             |

| C7 | $\mu$ ops dispatched        |

| C8 | L1D Cache misses            |

**Table 2.2:** Coefficients values of the Speed-Up model

| $\beta_0$ | $\beta_1$ | $\beta_2$ | $\beta_3$ | $\beta_4$ |

|-----------|-----------|-----------|-----------|-----------|

| 2.78      | 1.02e-11  | -4.34e-12 | -3.02e-10 | 0.18      |

up to 12 hardware threads, 8 4GB memory modules, 4 hard disk drives, 5 fans and 2 PSUs. The server runs a CentOS 6.5 Linux OS. We use *ocount*, an Oprofile tool, to gather hardware counters during runtime. The hardware counters are polled every second. Table 2.1 shows the hardware counters collected from the execution of the application signature. This set of hardware counters comes from the result of a feature selection method done during the power modeling process presented in Section 4.2. The Linux tool *pstack* is used to gather information about the temporal evolution of the independent execution paths of the running application. The *pstack* tool is executed with the applications *pid* as an input every second (i.e., in every second *pstack* displays a stack trace of the current execution of the application.).

It should be noted that for the experimental setup of the proof of concept presented in this chapter, the independent execution paths that showed data dependencies between them are merged into one execution path. In Chapter 4, a real implementation of the application signature is developed where the benchmarks used to evaluate the accuracy of the application signature are selected to not have data dependencies between the independent execution paths.

The set of workloads used in this chapter come from the SPEC CPU2006 [54] benchmark suite, the PARSEC suite [16] [17] and benchmarks from the NAS Parallel suite [11]. For the estimated executed instructions per independent execution path we make the assumption of having the executed instructions per independent execution path values with zero % estimation errors. It should be noted that the application signature is extracted from offline data acquired from a complete execution of the heterogeneous set of workloads.

In case of the speed-up model we performed a Principal Component Analysis (PCA) on the set of features (hardware counters and target speed-up) that are the inputs to the acceleration model. The final features selected to build the model are: Clock cycles (C1), Instructions Retired (C2), LLC misses (C3) and target speed-up (S). The values of the speed-up model linear regression coefficients are shown in Table 2.2, where  $\beta_0$  is the constant offset, the coefficients  $\beta_1$ ,  $\beta_2$  and  $\beta_3$  are the coefficients that multiply the hardware counters C1, C2 and C3, respectively, and the coefficient  $\beta_4$  multiplies the value of the The training set was formed by the following benchmarks: target speed-up. blackscholes, swaptions, frequine, streamcluster, BT, LU, FT, and CG. The benchmarks for the test set are the following: canneal, fluidanimate and SP. The benchmarks selected both for the train and test set were selected manually to represent an heterogeneous set of benchmarks with different speed-ups and accumulated hardware counters behaviours. In order to evaluate the accuracy of the speed-up model, we calculate the error of the estimated speed-up against the actual speed-up from each benchmark of the training and test set. The overall speed-up model RMSE for the training set and test set are 0.69 and 0.71, respectively.

#### 2.4 Results

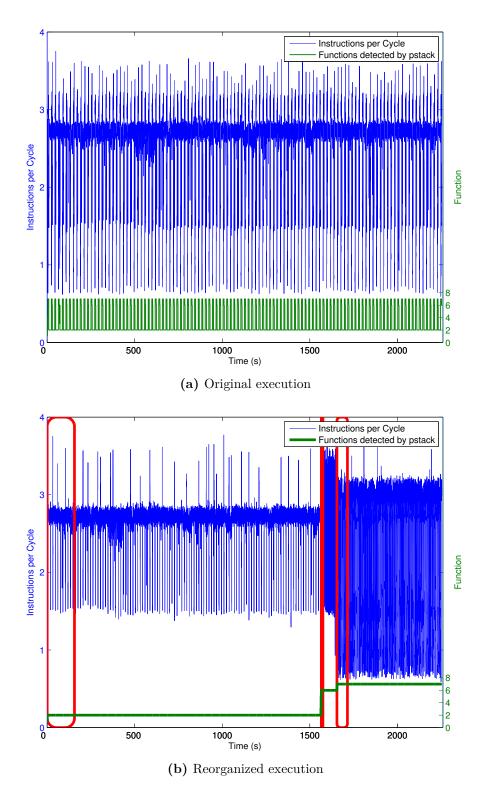

Figure 2.4a shows the Instructions per Cycle from the complete execution of the benchmark Calculix, where the green line shows the temporal evolution of the final functions of each independent execution path as given by the pstack output. Each different value of the green line represents a different running independent execution path from the benchmark. In order to ease the validation of the proof of concept using the application signature, the temporal profile of the complete execution is reorganized to group the execution of each function, as shown in Fig. 2.4b. For example, the independent execution path that leads to the function that goes from 0 seconds to 1500 seconds is formed by all the execution blocks from the original execution of the Calculix function e3cd. Although we are showing the values for the Instruction per Cycle this process is performed for all of the hardware counters. The application signature samples are represented by the red rectangles shown in Fig. 2.4b.

The Table 2.3 shows the complete set of benchmarks evaluated in this chapter. The benchmarks from bwaves to tonto are sequential applications from the SPEC CPU2006 suite, benchmarks from blackscholes to fluidanimate are parallel applications from the PARSEC suite and benchmarks from BT to SP are parallel applications from the NAS Parallel suite. For each benchmark, the

Figure 2.4: Instructions per Cycle (blue) and the temporal evolution of the independent execution paths (green). Application signature samples (red). Benchmark: Calculix

**Table 2.3:** Results of the validation process

|                      | Exec. Paths | Total runtime (s) | Signature runtime (s) | Error <sub>CPU</sub> (%) | $Error_{Mem}$ (%) | CR    |

|----------------------|-------------|-------------------|-----------------------|--------------------------|-------------------|-------|

| harrosson            | 4           | 1503              | 151                   | 6.11                     | 6.13              | 9.95  |

| bwaves               | _           |                   | -                     | -                        |                   |       |

| cactusADM            | 1           | 1657              | 166                   | 18.22                    | 18.25             | 9.98  |

| calculix             | 7           | 2253              | 226                   | 0.64                     | 0.64              | 9.96  |

| dealII               | 15          | 919               | 94                    | 1.62                     | 1.62              | 9.70  |

| GemsFDTD             | 10          | 1296              | 131                   | 0.66                     | 0.66              | 9.89  |

| gromacs              | 13          | 1408              | 142                   | 0.20                     | 0.20              | 9.91  |

| $_{ m lbm}$          | 1           | 756               | 76                    | 0.28                     | 0.28              | 9.94  |

| leslie3d             | 11          | 1674              | 169                   | 0.20                     | 0.20              | 9.90  |

| libquantum           | 10          | 966               | 98                    | 1.17                     | 1.17              | 9.85  |

| $\operatorname{mcf}$ | 13          | 628               | 64                    | 7.34                     | 7.34              | 9.81  |

| milc                 | 13          | 859               | 88                    | 4.15                     | 4.16              | 9.76  |

| namd                 | 15          | 1256              | 128                   | 0.37                     | 0.37              | 9.81  |

| omnetpp              | 21          | 771               | 80                    | 1.07                     | 1.08              | 9.63  |

| povray               | 27          | 520               | 56                    | 1.63                     | 1.63              | 9.28  |

| sjeng                | 26          | 1459              | 149                   | 1.36                     | 1.36              | 9.79  |

| tonto                | 15          | 1399              | 142                   | 1.35                     | 1.35              | 9.85  |

| blackscholes         | 2           | 479               | 48                    | 0.27                     | 0.27              | 9.97  |

| frequine             | 12          | 2114              | 213                   | 0.19                     | 0.20              | 9.92  |

| swaptions            | 4           | 824               | 83                    | 0.52                     | 0.52              | 9.92  |

| canneal              | 10          | 258               | 27                    | 2.42                     | 2.42              | 9.55  |

| streamcluster        | 4           | 964               | 96                    | 0.53                     | 0.54              | 10.04 |

| fluidanimate         | 5           | 800               | 80                    | 0.30                     | 0.31              | 10.00 |

| $\operatorname{BT}$  | 17          | 674               | 68                    | 0.20                     | 0.21              | 9.91  |

| CG                   | 2           | 240               | 24                    | 0.74                     | 0.74              | 10.00 |

| FT                   | 8           | 159               | 17                    | 3.65                     | 3.67              | 9.35  |

| LU                   | 6           | 610               | 61                    | 0.56                     | 0.57              | 10.00 |

| SP                   | 9           | 513               | 52                    | 0.76                     | 0.77              | 9.86  |

|                      | 1           |                   |                       |                          |                   |       |

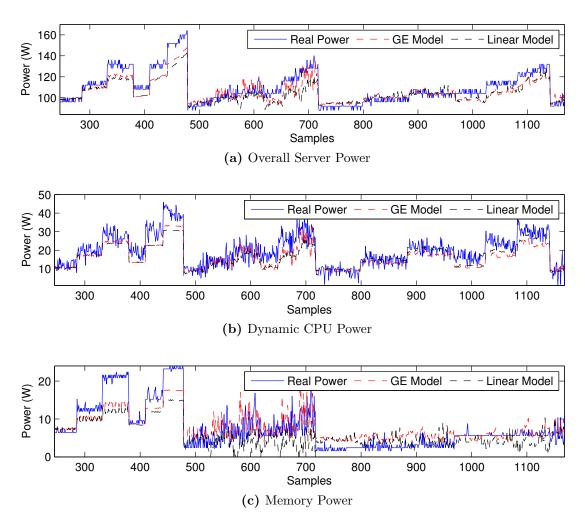

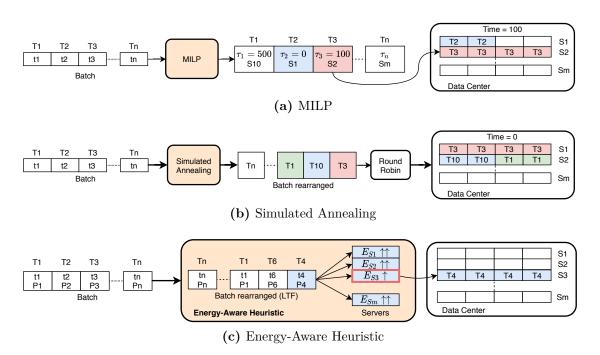

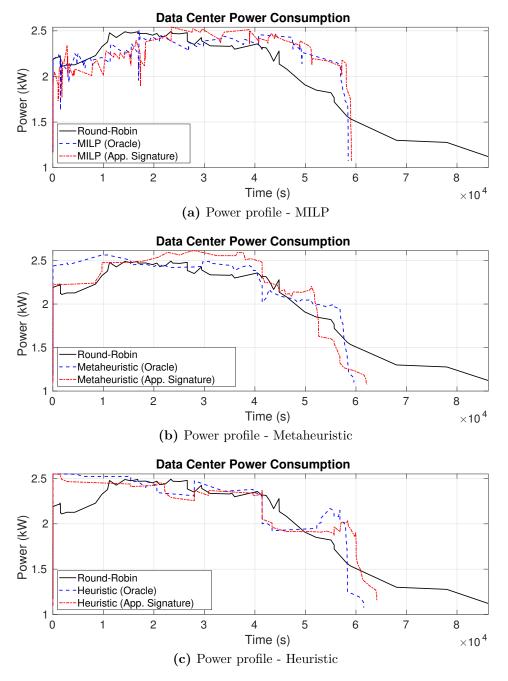

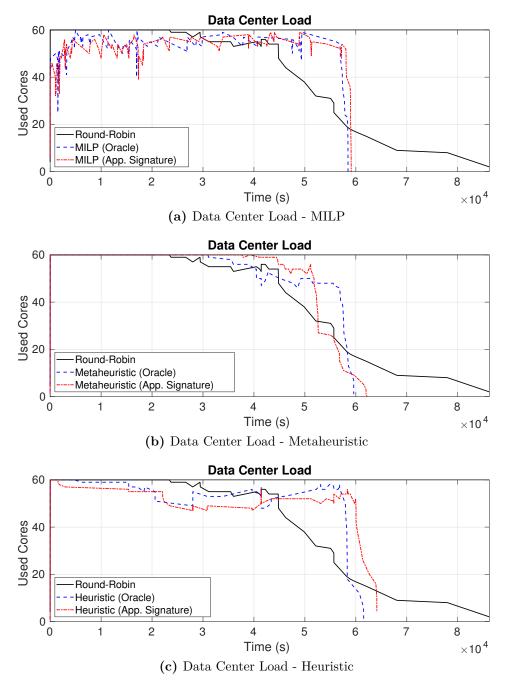

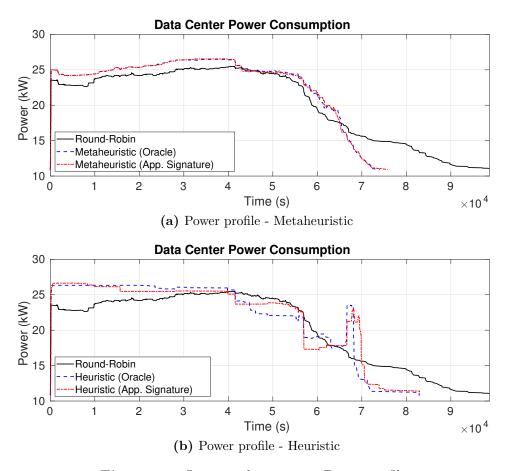

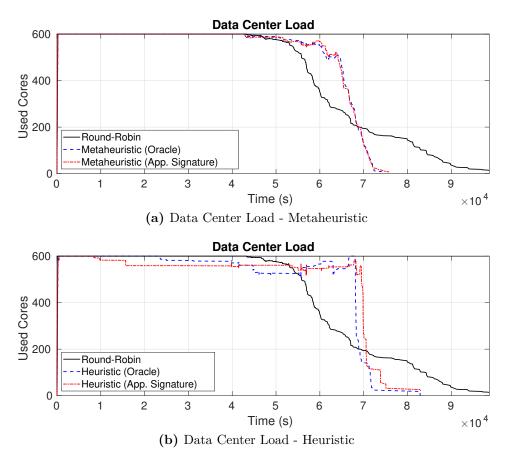

table shows the total execution time (T) in seconds, the number of independent execution paths detected by the pstack tool during runtime and the execution time of the application signature  $(T_{sig})$  in seconds. Attending to the number of paths detected, we observe a heterogeneous distribution, with benchmarks such as cactusADM and lbm with only 1 independent path detected, to benchmarks like povray with 27 paths detected.