#### UNIVERSIDAD COMPLUTENSE DE MADRID

### FACULTAD DE CIENCIAS FÍSICAS DEPARTAMENTO DE FÍSICA APLICADA III (ELECTRICIDAD Y ELECTRÓNICA)

#### **TESIS DOCTORAL**

# Growth of high permittivity dielectrics by high pressure sputtering from metallic targets

Crecimiento de dieléctricos de alta permitividad mediante pulverización catódica de alta presión a partir de blancos metálicos

MEMORIA PARA OPTAR AL GRADO DE DOCTORA

PRESENTADA POR

María Ángela Pampillón Arce

DIRECTOR

**Enrique San Andrés Serrano**

Madrid, 2017

# UNIVERSIDAD COMPLUTENSE DE MADRID FACULTAD DE CIENCIAS FÍSICAS

Departamento de Física Aplicada III (Electricidad y Electrónica)

# Growth of high permittivity dielectrics by high pressure sputtering from metallic targets

Crecimiento de dieléctricos de alta permitividad mediante pulverización catódica de alta presión a partir de blancos metálicos

A dissertation submitted in partial fulfillment of the requirements for the degree of **Doctor in Physics** by:

Ms. María Ángela Pampillón Arce

Supervisor:

Prof. Enrique San Andrés Serrano

Madrid, 2016

#### AGRADECIMIENTOS / ACKNOWLEGDMENTS

En primer lugar, me gustaría agradecer a mi director de tesis, Prof. Enrique San Andrés Serrano, la oportunidad que me ha brindado permitiéndome realizar este trabajo durante estos años. Gracias por todo su esfuerzo, dedicación, confianza y por todas sus enseñanzas. Su labor ha sido mucho más que la de un director. Muchísimas gracias por todo.

Querría también agradecer a todos los miembros del grupo de *Láminas delgadas y microelectrónica* por aceptarme desde el primer momento como una más. Gracias al Prof. Germán González Díaz, al Prof. Ignacio Mártil de la Plaza, a la Profa. María Luisa Lucía Mulas, a la Profa. Margarita Sánchez Balmaseda y al Prof. Álvaro del Prado Millán. Gracias a la Dra. María Toledano Luque, al Dr. David Pastor Pastor, al Dr. Javier Olea Ariza, al Dr. Eric García Hemme, a D. Rodrigo García Hernansanz y a D. Daniel Montero Álvarez. Unas gracias especiales al Dr. Pedro Carlos Feijoo Guerro por ayudarme desde el primer momento y por su simpatía. Gracias a todos por sus enseñanzas, por las charlas, por su dedicación, por su disposición siempre, por su generosidad y por las risas. He sido tremendamente afortunada de haber podido realizar mi tesis con todos ellos. Gracias por enseñarme tanto.

Gracias a los miembros del departamento de *Física Aplicada III* por el buen ambiente. Gracias en especial a Dña. Mar Gálvez Díez por toda su ayuda administrativa y por su buena energía por las mañanas.

Gracias a Dña. Rosa Cimas Cuevas y D. Pablo Fernández Sáez del *C.A.I. de Técnicas Físicas* por su ayuda y asistencia en la fabricación de muestras y por sus charlas. También gracias a la magia de D. Fernando Herrera Fernández y D. Antonio Paz López.

Este trabajo no hubiera sido posible sin la ayuda del Dr. José Emilio Fernández Rubio del *C.A.I. de Espectroscopía* por las medidas de FTIR; de D. Ignacio Carabias Sánchez del *C.A.I. de Difracción de Rayos X* por el GIXRD; del Dr. Nevenko Biskup y del Dr. Adrián Gómez Herrero del *Centro Nacional de Microscopía Electrónica* por la fabricación de las muestras de TEM y el análisis de las mismas; del Prof. José Luis

García Fierro del *Instituto de Catálisis y Petroleoquímica* por los análisis de XPS; de Dña. Laura Casado Zueras, del Dr. Alfonso Ibarra Galián y del Dr. Rodrigo Fernández-Pacheco Chicón del *Instituto de Nanocienca de Aragón* por la fabricación y análisis de TEM.

Gracias al *Grupo de Caracterización de Materiales y Dispositivos Electrónicos* de la Universidad de Valladolid, en especial a la Profa. Helena Castán Lanaspa, al Prof. Salvador Dueñas Carazo y al Prof. Héctor García García por las medidas eléctricas y la ayuda en la compresión del análisis de los resultados.

Thank you very much to all the people of the PGI-9 at *Forschungszentrum Jülich* to accept me during six months. It was a real pleasure to be with you those months, learning and sharing talks. I will never forget those lunches at 11:00 am. Mahlzeit! Vielen Dank!

No puedo olvidarme tampoco de mi "familia española" durante mi estancia en Jülih. Hicistéis que esos meses lejos de casa fueran especiales e inolvidables. ¡Gracias!

Quisiera agradecer de manera muy especial a mi familia: mis padres, Maique y Fernando, por permitirme hacer lo que he querido siempre y por todo su apoyo. Sin duda, no hubiera llegado a esto sin ellos. También a mis hermanos, Fernando y Joaquín, a mi cuñada Almudena y al pequeño de la familia (por el momento), Yago. Son la familia que me ha tocado, pero me siento muy afortunada por ello.

Por último, gracias a todos mis amigos, por ser la familia que se puede elegir. Y gracias a esas personas que se han ido cruzando en mi camino, porque de una manera u otra, habéis hecho que sea también la persona que soy y que haya llegado hasta aquí.

Y gracias también a todas esas personas que están por llegar...

Marián Pampillón Arce

# TABLE OF CONTENTS

| Agradecimientos / Acknowlegdments               | i    |

|-------------------------------------------------|------|

| Table of contents                               | iii  |

| List of figures                                 | vii  |

| List of tables                                  | xvii |

| List of abbreviations                           | xix  |

| List of symbols                                 | xxi  |

| Summary                                         | XXV  |

| Resumen                                         | xxix |

| Chapter I: INTRODUCTION                         | 1    |

| I.1 Historical evolution                        | 2    |

| I.2 CMOS devices scaling                        | 3    |

| I.3 High κ dielectrics                          | 5    |

| 3.1 Gadolinium oxide                            | 9    |

| 3.2 Scandium oxide                              | 10   |

| 3.3 Gadolinium scandate                         | 10   |

| I.4 Metal gate electrodes                       | 11   |

| 4.1 Scavenging effect                           | 11   |

| I.5 Alternative substrates                      | 13   |

| I.6 High pressure sputtering (HPS)              | 13   |

| I.7 Alternative structures                      |      |

| I.8 Outline of the thesis                       | 16   |

| References                                      | 17   |

| Chapter II: FABRICATION TECHNIQUES              | 27   |

| II.1 High pressure sputtering (HPS)             | 28   |

| II.2 Glow discharge optical spectroscopy (GDOS) | 31   |

| 2.1 System I (monocromator)                     | 32   |

| 2.2 System II (spectrometer)                    |      |

| II.3 Electron beam (e-beam) evaporation         | 34   |

| 3.1 SiO <sub>x</sub> acting as field oxide      | 37   |

| 3.2 Metallic electrodes                         | 37   |

| II.4 Lithography process                                                      | 37 |

|-------------------------------------------------------------------------------|----|

| 4.1 Positive photoresist                                                      | 38 |

| 4.2 Negative photoresist                                                      | 39 |

| II.5 Rapid thermal annealing (RTA)                                            | 40 |

| II.6 MIS fabrication                                                          | 41 |

| 6.1 Process without field oxide (FOX)                                         | 41 |

| 6.2 Process with FOX                                                          | 43 |

| II.7 Substrates                                                               | 45 |

| 7.1 Semiconductor materials                                                   | 45 |

| 7.1.A Si wafers                                                               | 45 |

| 7.1.B InP substrates                                                          | 46 |

| 7.2 Substrate surface cleaning                                                | 46 |

| 7.2.A Si wafers                                                               | 46 |

| 7.2.B InP wafers                                                              | 47 |

| References                                                                    | 48 |

| Chapter III: CHARACTERIZATION TECHNIQUES                                      | 51 |

| III.1 Structural characterization techniques                                  | 52 |

| 1.1 Fourier transform infrared spectroscopy (FTIR)                            | 52 |

| 1.2 Grazing incidence X ray diffraction (GIXRD)                               | 56 |

| 1.3 X ray reflectometry (XRR)                                                 | 58 |

| 1.4 X ray photoelectron spectroscopy (XPS)                                    | 58 |

| 1.5 Transmission electron microscopy (TEM)                                    | 60 |

| III.2 Electrical characterization techniques                                  | 61 |

| 2.1 MIS capacitors                                                            | 62 |

| 2.1.A Ideal MIS capacitor in equilibrium                                      | 62 |

| 2.1.B Ideal MIS capacitor under bias                                          |    |

| 2.1.C Real MIS structure                                                      | 64 |

| 2.2 Capacitive behavior of MIS devices: C-V <sub>gate</sub> characterization  | 64 |

| 2.2.A Effects of $Q_{INS}$ in the C-V <sub>gate</sub> characteristics         | 67 |

| 2.2.B Effects of $D_{it}$ in the C-V <sub>gate</sub> characteristics          | 67 |

| 2.2.C Effects of the oxide trapped charge in the $C-V_{gate}$ characteristics | 70 |

| 2.3 Interfacial state density ( $D_{it}$ ) determination                      | 70 |

| 2.3.A Conductance method                                                      | 70 |

| 2.3.B Deep level transient spectroscopy (DLTS)                                                          | 72     |

|---------------------------------------------------------------------------------------------------------|--------|

| 2.4 Leakage current density measurements                                                                | 73     |

| References                                                                                              | 74     |

| Chapter IV: THERMAL OXIDATION OF Gd <sub>2</sub> O <sub>3</sub>                                         | 79     |

| IV.1 Experimental method                                                                                | 80     |

| IV.2 Results and discussion                                                                             | 81     |

| 2.1. Plasma characterization of metallic Gd sputtered in Ar                                             | 81     |

| 2.2. Physical characterization of the thermally oxidized GdO <sub>x</sub> films                         | 83     |

| 2.3. Electrical characterization of MIS devices with thermally oxidized Gd <sub>2</sub> O <sub>3</sub>  | 3 88   |

| 2.4. TEM analysis of MIS devices                                                                        | 91     |

| IV.3 Summary and conclusions                                                                            | 94     |

| References                                                                                              | 94     |

| Chapter V: PLASMA OXIDATION OF Gd <sub>2</sub> O <sub>3</sub> AND Sc <sub>2</sub> O <sub>3</sub>        | 97     |

| V.1 Experimental method                                                                                 | 98     |

| V.2 Results and discussion                                                                              | 98     |

| 2.1 Feasibility of the two-step deposition process for $Gd_2O_3$ and $Sc_2O_3$                          | 98     |

| 2.1.A Plasma characterization of metallic Gd sputtered in Ar/O <sub>2</sub> atmosphe                    | ere 98 |

| 2.1.B Plasma characterization of metallic Sc sputtered in pure Ar and r $Ar/O_2$ atmospheres            |        |

| 2.1.C Structural characterization of the plasma oxidized Gd <sub>2</sub> O <sub>3</sub> films           | 103    |

| 2.1.D Structural characterization of the plasma oxidized $Sc_2O_3$ films                                | 106    |

| 2.1.E Electrical characterization of MIS devices with plasma oxidized C and $Sc_2O_3$                   |        |

| 2.2 Optimization of the two-step deposition process for Gd <sub>2</sub> O <sub>3</sub>                  | 109    |

| 2.2.A Oxidation power effect                                                                            | 110    |

| 2.2.B Initial metal deposition time influence                                                           | 113    |

| 2.2.C Oxidation time                                                                                    | 117    |

| 2.3 Effect of FGA temperature on optimized MIS devices with plasma oxi $Gd_2O_3$                        |        |

| 2.4 Electrical characterization of optimized MIS devices with plasma oxi Sc <sub>2</sub> O <sub>3</sub> |        |

| V.3 Summary and conclusions                                                                             |        |

| References                                                                                              |        |

| Chapter VI: GADOLINIUM SCANDATE                                                               | 141 |

|-----------------------------------------------------------------------------------------------|-----|

| VI.1 Experimental method                                                                      | 142 |

| VI.2 Results and discussion                                                                   | 143 |

| 2.1 Plasma characterization                                                                   | 143 |

| 2.2 Physical characterization                                                                 | 145 |

| 2.3 Electrical characterization                                                               | 150 |

| VI.3 Summary and conclusions                                                                  | 158 |

| References                                                                                    | 158 |

| Chapter VII: INTERFACE SCAVENGING                                                             | 161 |

| VII.1 Experimental method                                                                     | 162 |

| VII.2 Results and discussion                                                                  | 162 |

| 2.1 Thick Ti layers as top electrode with Gd <sub>2</sub> O <sub>3</sub>                      | 162 |

| 2.2 Optimization of the scavenging effect for plasma oxidized Gd <sub>2</sub> O <sub>3</sub>  | 165 |

| 2.3 Scavenging effect for plasma oxidized Sc <sub>2</sub> O <sub>3</sub>                      | 173 |

| 2.4 Scavenging effect for plasma oxidized Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub>  | 176 |

| VII.3 Summary and conclusions                                                                 | 179 |

| References                                                                                    | 179 |

| Chapter VIII: Gd <sub>2</sub> O <sub>3</sub> ON InP SUBSTRATES                                | 183 |

| VIII.1 Experimental method                                                                    | 184 |

| VIII.2 Results and discussion                                                                 | 184 |

| 2.1 Feasibility of plasma oxidized Gd <sub>2</sub> O <sub>3</sub> deposited on InP substrates | 184 |

| 2.2 Optimized devices with Gd <sub>2</sub> O <sub>3</sub> on InP                              | 188 |

| 2.3 Interface scavenging with InP                                                             | 193 |

| VIII.3 Summary and conclusions                                                                | 196 |

| References                                                                                    | 196 |

| Chapter IX: CONCLUSIONS AND FUTURE WORK                                                       | 201 |

| IX.1 Conclusions                                                                              | 202 |

| IX.2 Future work                                                                              | 204 |

| LIST OF PUBLICATIONS                                                                          | 205 |

| Journal papers                                                                                | 205 |

| Conference contributions                                                                      | 207 |

| Patent                                                                                        | 211 |

# LIST OF FIGURES

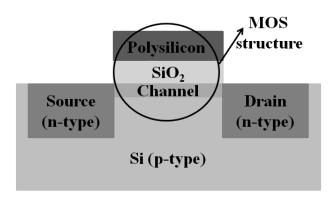

| Figure I.1: Cross sectional sketch of a traditional n-MOSFET. The MOS structure is                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| marked in this figure                                                                                                                                                                                                                                                                      |

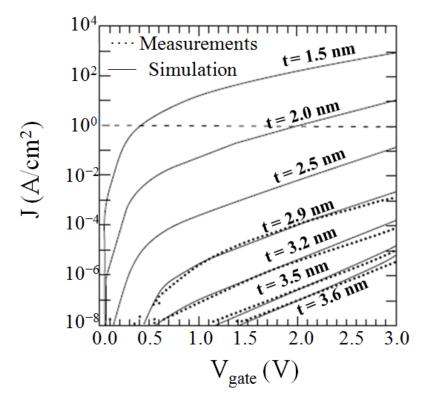

| Figure I.2: Leakage current density as a function of gate voltage for different SiO <sub>2</sub>                                                                                                                                                                                           |

| thicknesses. Data are extracted from Taur <i>et al.</i> 16                                                                                                                                                                                                                                 |

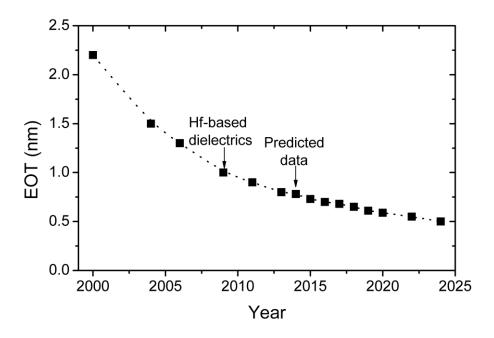

| <b>Figure I.3</b> : Data and predicted data of the EOT as a function of the year. Provided by the 2013 edition of ITRS                                                                                                                                                                     |

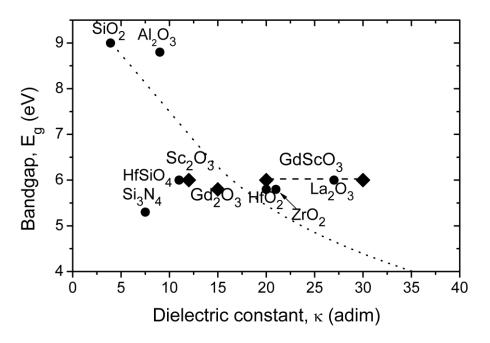

| <b>Figure I.4</b> : Bandgap as a function of the $\kappa$ value for different dielectric materials. In dotted line is shown the inverse dependence. Data have been extracted from several references. In diamond symbols are represented the data of the materials used along this thesis. |

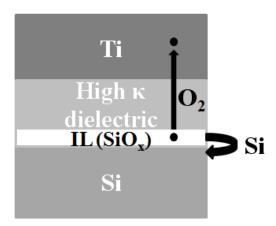

| <b>Figure I.5</b> : Schema of the scavenging process: the oxygen of the IL diffused through the high κ material and is dissolved by Ti, while the Si atoms are reincorporated to the substrate.                                                                                            |

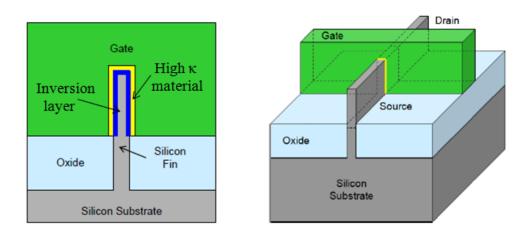

| <b>Figure I.6</b> : Schema of a tridimensional tri-gate transistor from <i>Intel</i> . 121                                                                                                                                                                                                 |

| <b>Figure II.1</b> : Picture of the high pressure sputtering used for high κ materials deposition.                                                                                                                                                                                         |

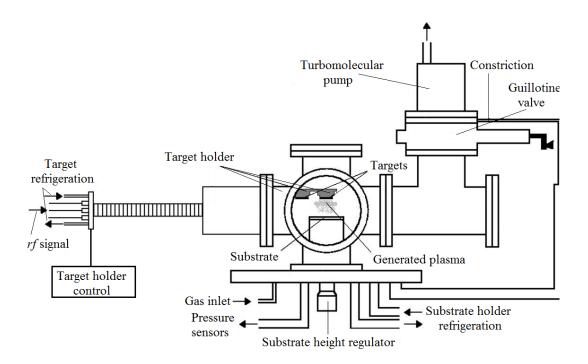

| <b>Figure II.2</b> : Scheme of the high pressure sputtering used. 29                                                                                                                                                                                                                       |

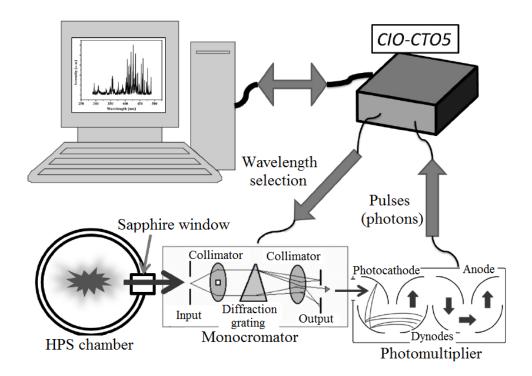

| Figure II.3: Scheme of the glow discharge optical spectroscopy system I (monocromator)                                                                                                                                                                                                     |

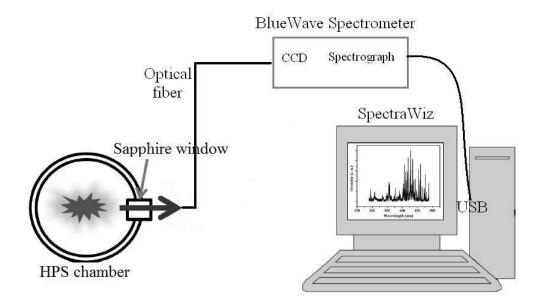

| <b>Figure II.4</b> : Scheme of the system II (spectrometer) to analyze the GDOS                                                                                                                                                                                                            |

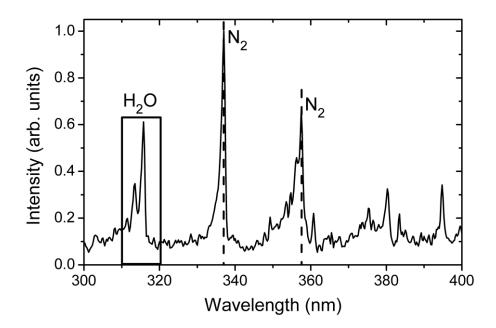

| <b>Figure II.5</b> : GDOS emission spectrum of a target sputtered in Ar during the conditioning process. H <sub>2</sub> O band and N <sub>2</sub> peaks are marked in the figure. The remaining peaks are related to Ar I and Ar II                                                        |

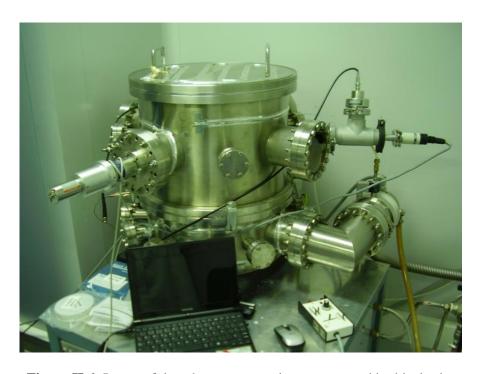

| <b>Figure II.6:</b> Image of the e-beam evaporation system used in this thesis                                                                                                                                                                                                             |

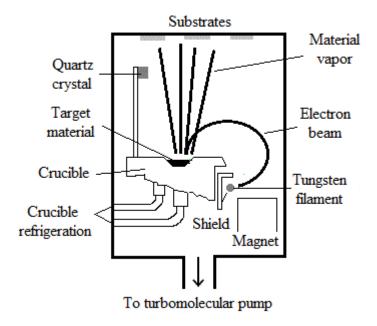

| <b>Figure II.7</b> : Scheme of the electron beam evaporation system                                                                                                                                                                                                                        |

| <b>Figure II.8</b> : Image of the <i>Headway Research</i> spinner (in the left hand side) and the <i>MJB3 UV400</i> alignment system (in the right hand side), used for the lithography process                                                                                            |

| Figure II.9: Image of the RTA system                                                                                                                                                                                                                                                       |

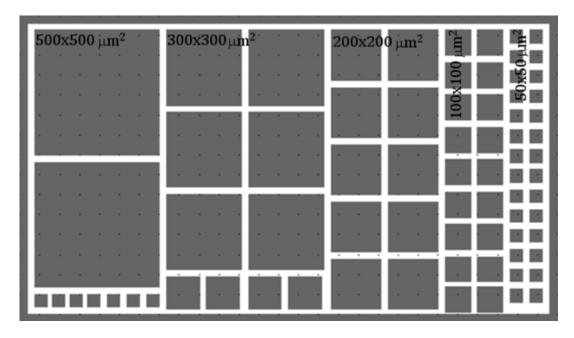

| Figure II.10: Dice of the lithography mask of the process without field oxide to define                                                                                                                                                                                                    |

| the top electrodes                                                                                                                                                                                                                                                                         |

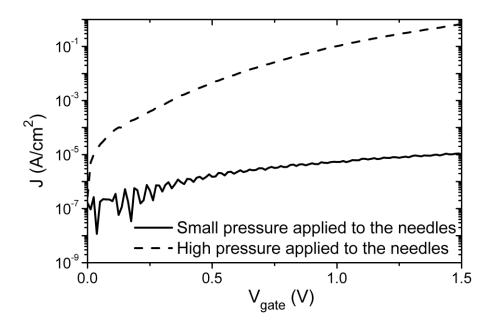

| <b>Figure II.11</b> : J-V <sub>gate</sub> characteristics for the same sample measured applying more or less pressure to the needles                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

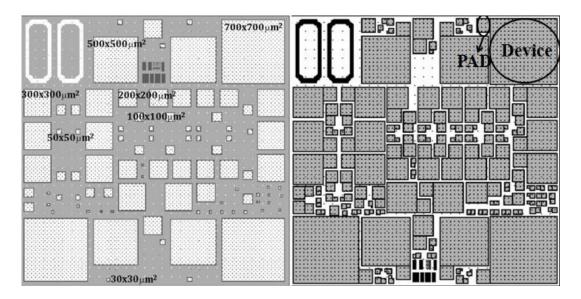

| <b>Figure II.12</b> : Lithography mask used for the process with field oxide. In the left hand side is the mask used for opening the SiO <sub>x</sub> windows and in the right hand side is for defining the top contacts. A pad and a device are marked in the figure                                                       |

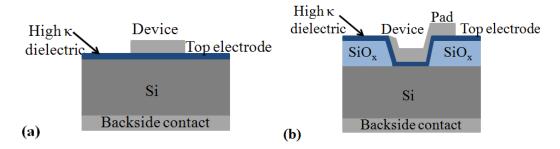

| pad) fabricated following the steps from subsection 6.1 and 6.2, respectively 45                                                                                                                                                                                                                                             |

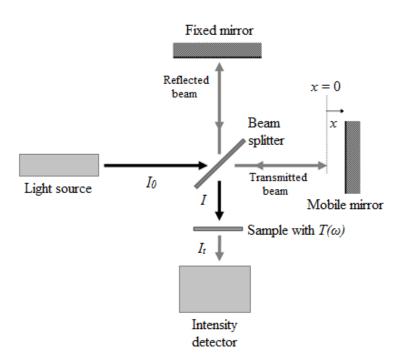

| <b>Figure III.1</b> : Schematic image of a Fourier transform infrared spectrometer 52                                                                                                                                                                                                                                        |

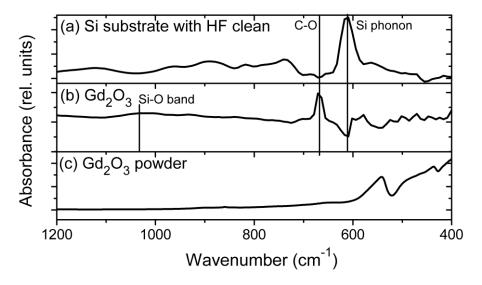

| <b>Figure III.2</b> : FTIR spectra for (a) Si substrate with HF clean used for corrections, (b) as deposited Gd <sub>2</sub> O <sub>3</sub> film (without the contribution of the Si substrate) and (c) Gd <sub>2</sub> O <sub>3</sub> powder                                                                                |

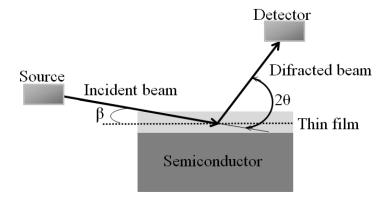

| <b>Figure III.3</b> : Schema of the GIXRD system used: $\beta$ is a fixed angle while the detector performs a scan in $2\theta$                                                                                                                                                                                              |

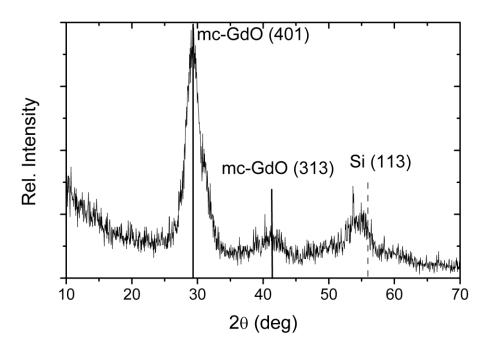

| <b>Figure III.4</b> : GIXRD spectra of a Si substrate sputtered with Gd in an Ar/O <sub>2</sub> atmosphere. The observed diffraction peaks have been identified as monoclinic gadolinium oxide and are marked with black solid lines. Also, a Si substrate contribution is observed and is indicated with a grey dashed line |

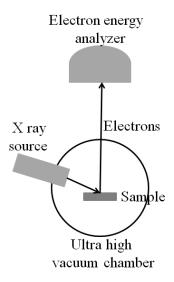

| Figure III.5: Schematic of the XPS system used                                                                                                                                                                                                                                                                               |

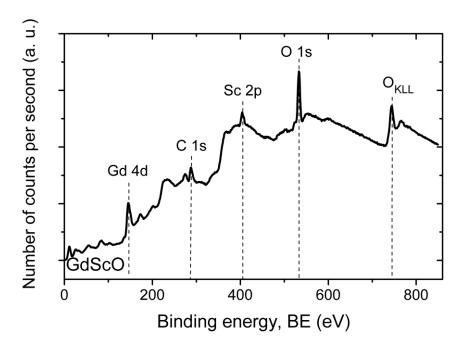

| <b>Figure III.6</b> : XPS wide scan or survey spectrum of Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample. The identified peaks are related to Gd, C, Sc and O and are marked in the figure                                                                                                                        |

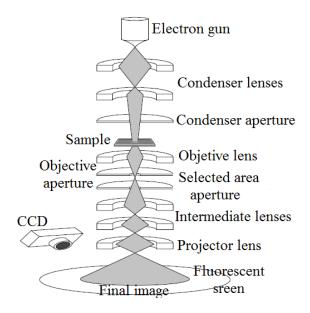

| Figure III.7: Schematic of the transmission electron microscope                                                                                                                                                                                                                                                              |

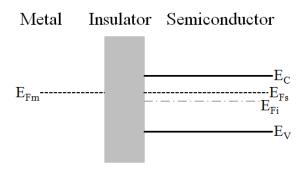

| Figure III.8: Band diagram of an ideal MIS structure in equilibrium                                                                                                                                                                                                                                                          |

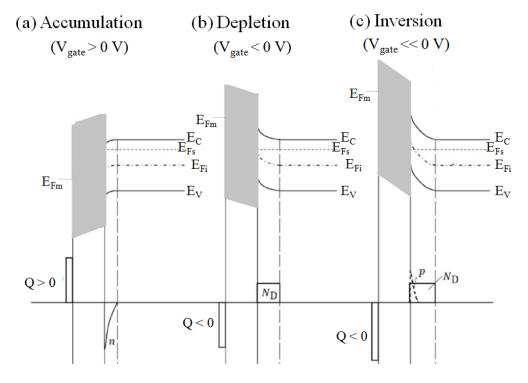

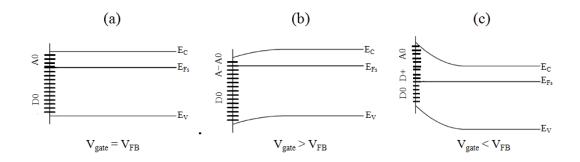

| <b>Figure III.9</b> : Band diagram (and charge concentration) of an ideal MIS structure under bias. The accumulation (in the left hand side), depletion (in the center) and inversion (in the right hand side) situations are presented                                                                                      |

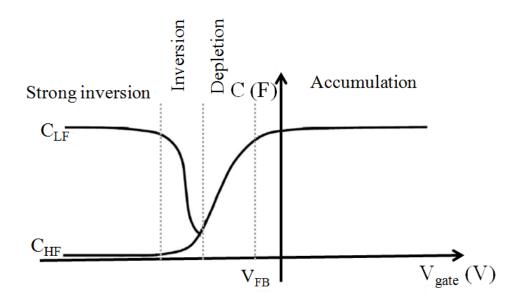

| <b>Figure III.10</b> : $C-V_{gate}$ curves for low and high frequencies. In the figure are marked the four different situations of the MIS structure depending on the applied gate voltage 66                                                                                                                                |

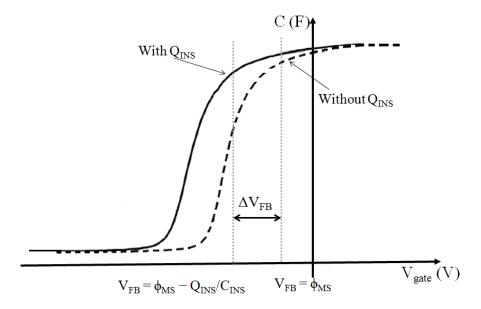

| <b>Figure III.11</b> : Shift produced in the C-V <sub>gate</sub> characteristics of a MIS structure as a consequence of the presence of $Q_{INS} > 0$                                                                                                                                                                        |

| <b>Figure III.12</b> : Interface states charge changes depending on the applied voltage to the MIS structure. A0 and D0 are neutral acceptors and donors, A– are the negatively charged acceptor states and D+ are the positive charged donor states                                                                         |

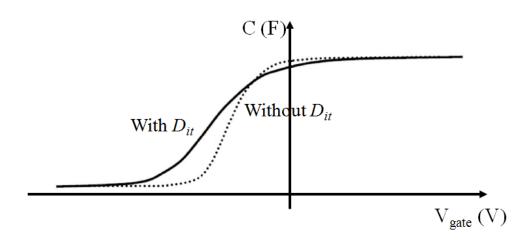

| <b>Figure III.13</b> : Stretch-out of the C-V <sub>gate</sub> curve as a consequence of the presence of a $D_{it}$ .                                                                                                                                                                                                         |

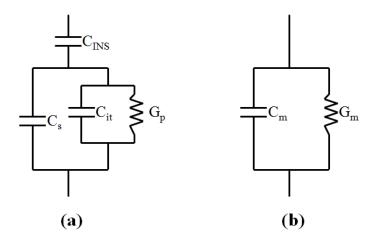

| Figure III.14: (a) Small signal equivalent circuit of a MIS device for conductance measurements and (b) measured circuit                                                                                                                                                                                                     |

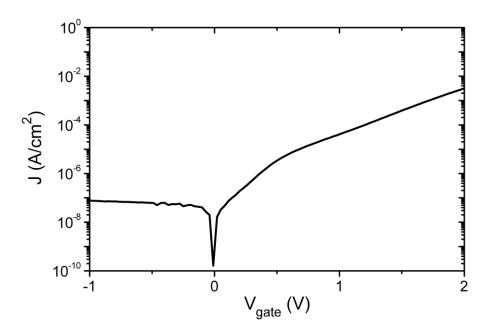

| <b>Figure III.15</b> : J-V <sub>gate</sub> characteristic of a MIS device measured from inversion (negative voltages) to accumulation (positive voltages)                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

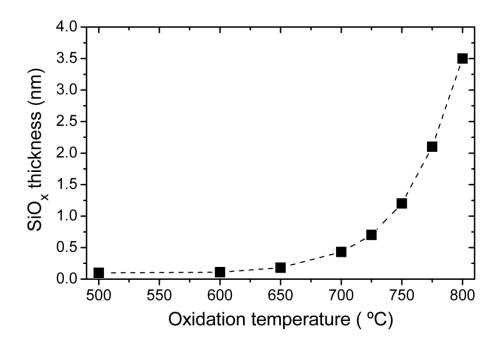

| <b>Figure IV.1</b> : Simulation of the SiO <sub>x</sub> thickness regrowth as a function of the oxidation temperature for bare-Si substrate implementing the Massoud oxidation model                                                                                                                                                                                                                                                                                |

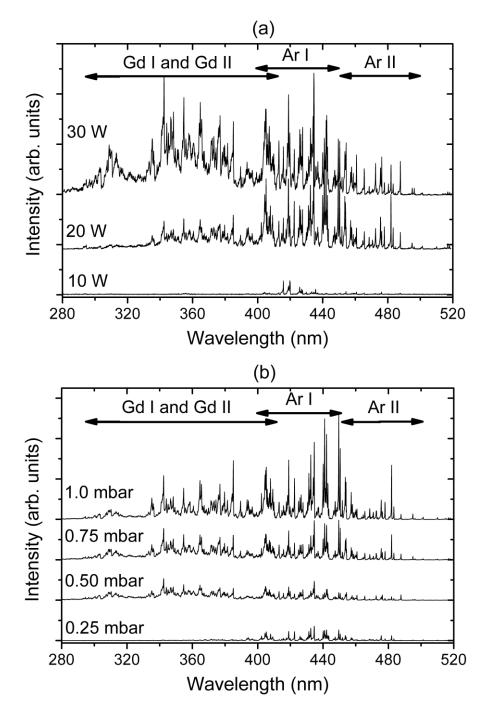

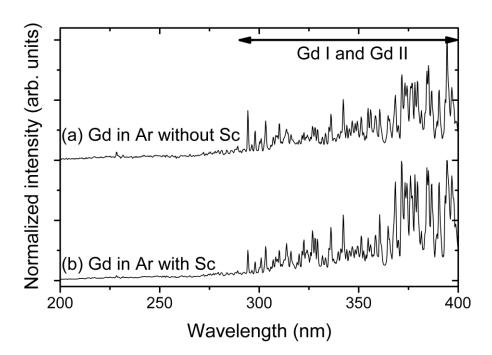

| <b>Figure IV.2</b> : Optical emission spectra of metallic Gd sputtered in an Ar plasma at room temperature with (a) <i>rf</i> power variation (from 10 to 30 W) and (b) an Ar pressure dependence (0.25-1.0 mbar). The ranges with the most important lines for Ar I, Ar II Gd I and Gd II are indicated in the figure                                                                                                                                              |

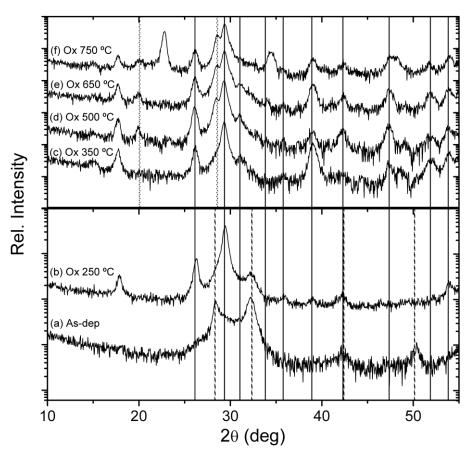

| <b>Figure IV.3</b> : Grazing incidence X-ray diffraction patterns of thick Gd layers (a) as-deposited and (b)-(f) oxidized at several temperatures (from 250 to 750 °C). The observed diffraction peaks have been identified as hexagonal metallic gadolinium (dashed lines), monoclinic gadolinium oxide (solid lines) or cubic gadolinium oxide (dotted lines).                                                                                                   |

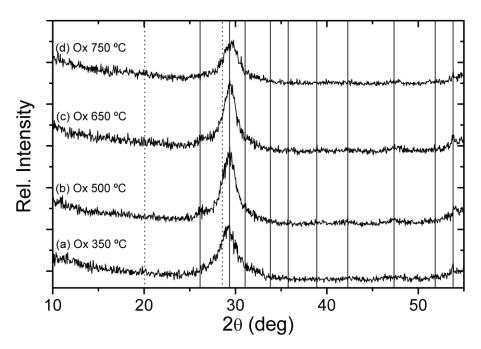

| <b>Figure IV.4</b> : (a)-(d) GIXRD patterns of thin Gd films oxidized at several temperatures (from 350 to 750 °C). The observed diffraction peaks have been identified as monoclinic gadolinium oxide (solid lines). The cubic gadolinium oxide is also shown (dotted lines)                                                                                                                                                                                       |

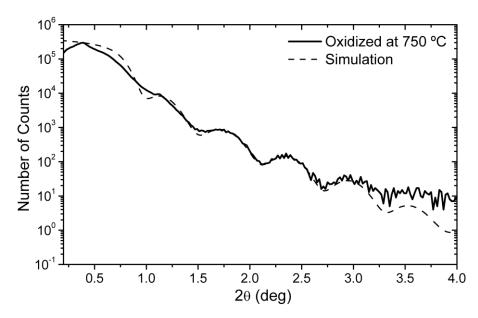

| <b>Figure IV.5</b> : X-ray reflection measurements of the Gd film oxidized at 750 °C (solid line), and fit to a $Gd_2O_3/SiO_2/Si$ model (dashed line)                                                                                                                                                                                                                                                                                                              |

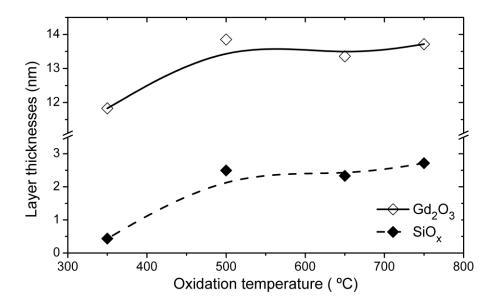

| <b>Figure IV.6</b> : Thickness result of the XRR simulations to a $Gd_2O_3/SiO_2/Si$ bilayer model: $Gd_2O_3$ thickness (open symbols) and $SiO_2$ thickness (closed symbols). The uncertainty of these values can be estimated as $\pm$ 1.0 nm                                                                                                                                                                                                                     |

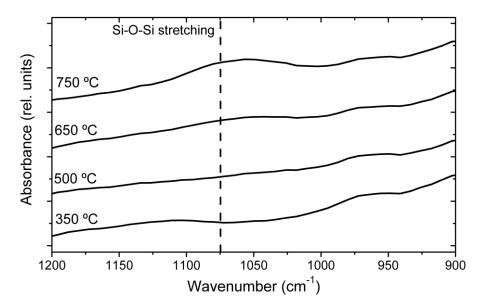

| <b>Figure IV.7</b> : FTIR spectra of thin Gd layers oxidized at several temperatures (from 350 to 750 °C). The wavenumber of thermal SiO <sub>2</sub> stretching is marked by the dashed line 88                                                                                                                                                                                                                                                                    |

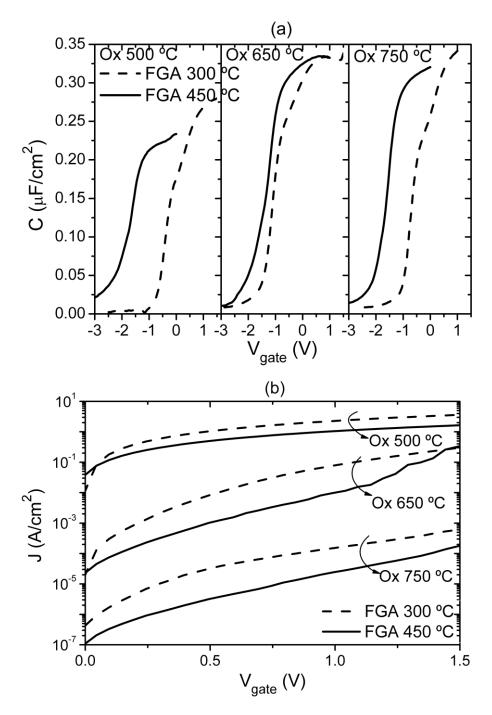

| <b>Figure IV.8</b> : (a) Representative normalized capacitance curves as function of gate voltage of the Al/Gd <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> /Si devices measured at 10 kHz for different oxidation temperatures (500-750 °C) and FGA temperatures (300 °C (with dashed lines) and 450 °C (solid lines)). (b) Gate current density as a function of gate voltage for the same samples                                                               |

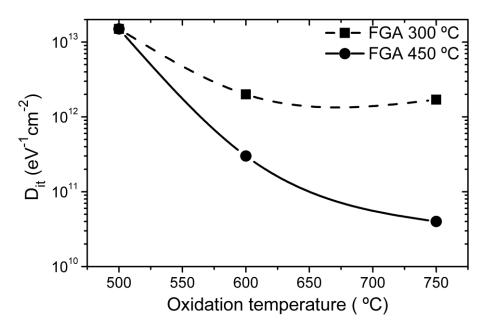

| <b>Figure IV.9</b> : $D_{it}$ values as a function of different oxidation temperatures for FGA a 300 °C (square symbols) and FGA at 450 °C (circle symbols)                                                                                                                                                                                                                                                                                                         |

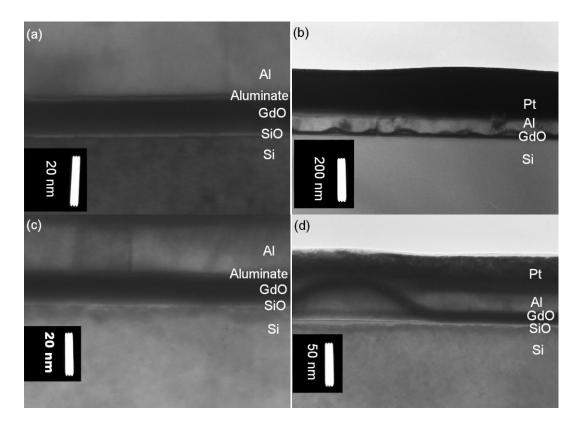

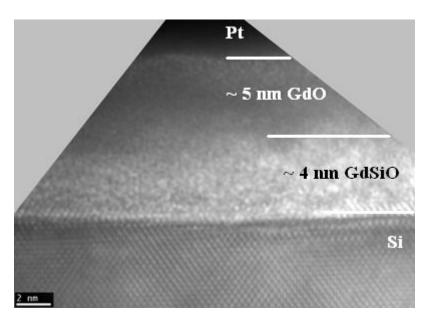

| <b>Figure IV.10</b> : (a) and (b) Cross-sectional TEM images of the Gd <sub>2</sub> O <sub>3</sub> films oxidized at 750 °C. (c) and (d) Images of the films oxidized at 500 °C. (a) and (c) high magnification images, used to measure Gd <sub>2</sub> O <sub>3</sub> and SiO <sub>x</sub> thickness and (b) and (d) low magnification images, where the density of domes can be observed. Samples were covered by Pt for protection during FIB sample preparation |

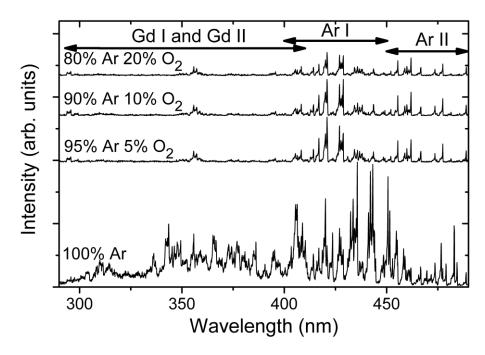

| <b>Figure V.1</b> : GDOS spectra of metallic Gd sputtered in an Ar/O <sub>2</sub> atmosphere at 0.50 mbar and at room temperature with different oxygen concentration (from 0 to 20%) at 30 W. The ranges with the most important lines for Ar I, Ar II, Gd I and Gd II are marked in the figure                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

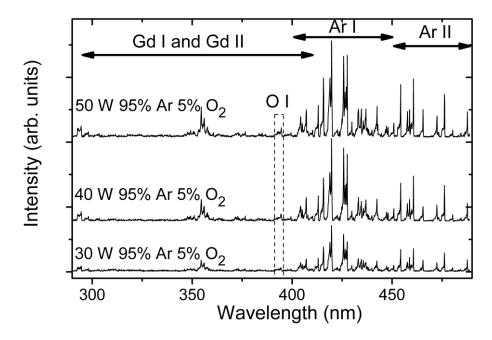

| <b>Figure V.2</b> : GDOS spectra of metallic Gd sputtered in a 95% Ar and 5% O <sub>2</sub> atmosphere at 0.50 mbar and at room temperature with different <i>rf</i> power varying from 30 to 50 W. The ranges with the most important lines for Ar I, Ar II, Gd I, Gd II and the most intense peak of O I are marked in the figure                                                            |

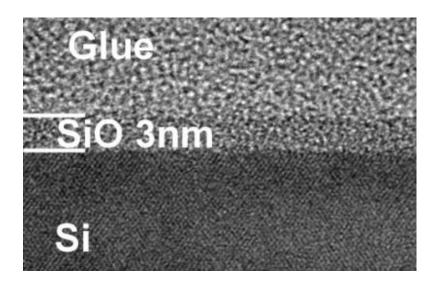

| <b>Figure V.3</b> : Cross-sectional TEM image of a bare Si substrate exposed to an Ar/O <sub>2</sub> plasma with 30 W and 0.50 mbar during 5 min at room temperature                                                                                                                                                                                                                           |

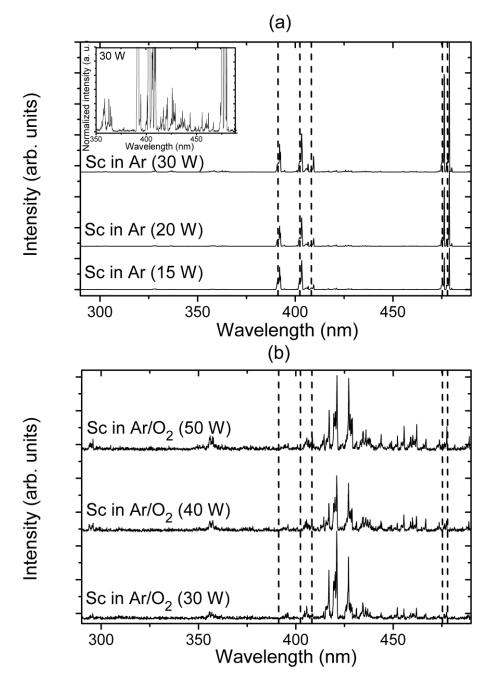

| <b>Figure V.4</b> : GDOS spectra of metallic Sc sputtered at 0.50 mbar and at room temperature for different <i>rf</i> powers in (a) a pure Ar atmosphere and (b) a 95% / 5% Ar/O <sub>2</sub> plasma. The most intense Sc I peaks are marked in the figure with dashed lines. In the inset of (a), an enlargement is made for the <i>rf</i> power of 30 W to observe the Ar I and Ar II peaks |

| <b>Figure V.5</b> : GIXRD spectra of bare Si substrates sputtered in Ar/O <sub>2</sub> atmosphere with Gd target and at different <i>rf</i> powers (from 30 to 50 W). The observed diffraction peaks have been identified as monoclinic gadolinium oxide and are marked with solid lines.                                                                                                      |

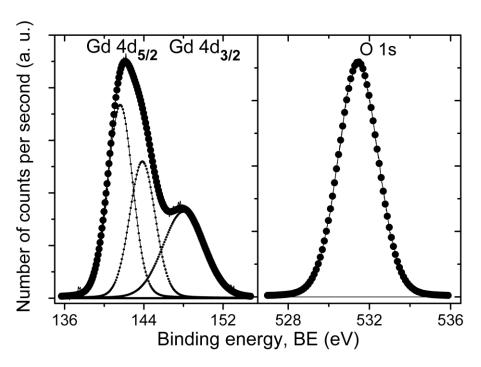

| <b>Figure V.6</b> : Gd 4d doublet (left) and O 1s (right) core-level peaks and their fits taken from the surface of a ~3 nm thick film of Gd <sub>2</sub> O <sub>3</sub> grown with a two-step method from a Gd target                                                                                                                                                                         |

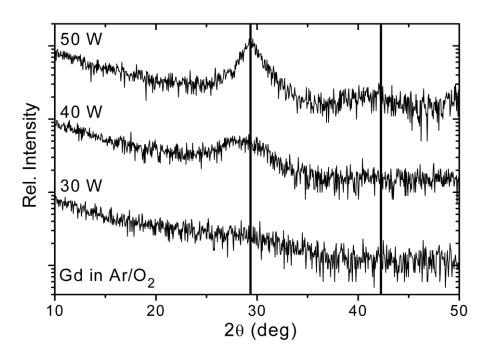

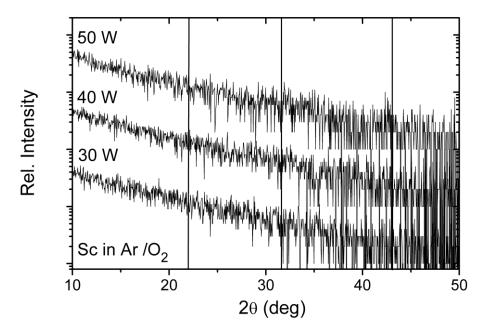

| <b>Figure V.7</b> : GIXRD spectra of bare Si substrates sputtered in Ar/O <sub>2</sub> atmosphere with Sc target and at different <i>rf</i> powers: 30, 40 and 50 W. The most intense peaks in the Sc <sub>2</sub> O <sub>3</sub> cubic phase are marked in solid lines                                                                                                                        |

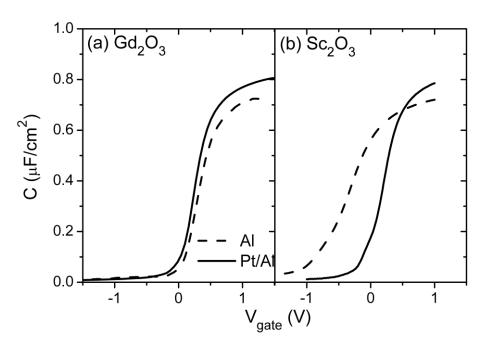

| <b>Figure V.8</b> : C-V <sub>gate</sub> curves of MIS devices using (a) Gd <sub>2</sub> O <sub>3</sub> and (b) Sc <sub>2</sub> O <sub>3</sub> as dielectric with two metallic gates: Al in dashed lines and Pt/Al in solid lines. The capacitors were measured at 10 kHz and after a FGA at 300 °C for 20 min                                                                                  |

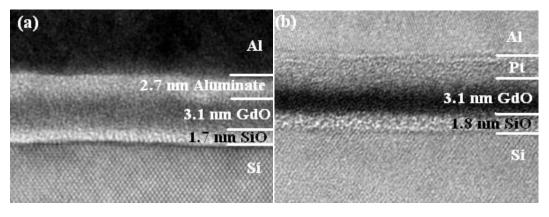

| <b>Figure V.9</b> : Cross-sectional TEM images of the Gd <sub>2</sub> O <sub>3</sub> films after a FGA at 300 °C using (a) Al and (b) Pt/Al gate stack                                                                                                                                                                                                                                         |

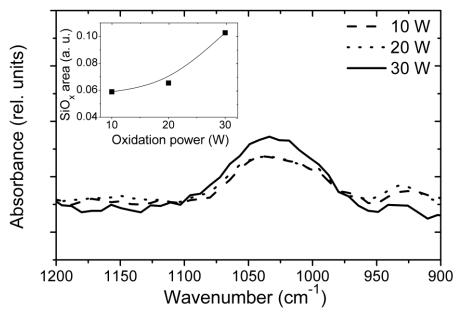

| <b>Figure V.10</b> : FTIR spectra for $Gd_2O_3$ samples with different oxidation $rf$ power: 10, 20 and 30 W. Inset: $SiO_x$ peak area as a function of the $rf$ power for the same samples 110                                                                                                                                                                                                |

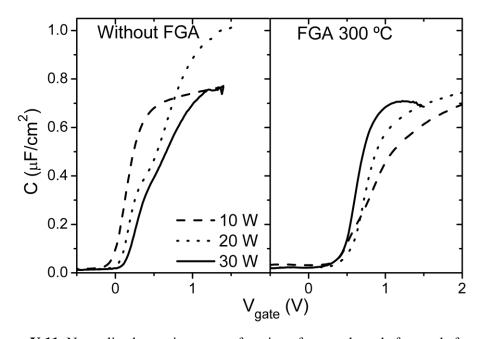

| <b>Figure V.11</b> : Normalized capacitance as a function of gate voltage before and after the FGA at 300 °C for samples with different <i>rf</i> oxidation power: 10, 20 and 30 W 111                                                                                                                                                                                                         |

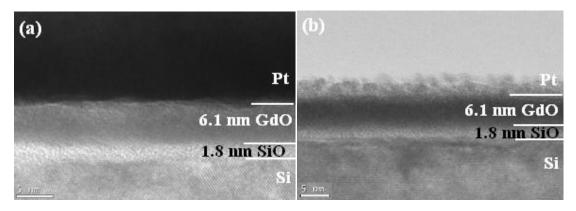

| <b>Figure V.12</b> : Cross-sectional TEM images of the Gd <sub>2</sub> O <sub>3</sub> films with 80 s of Gd and 300 s of plasma oxidation at (a) 30 W and (b) 20 W after a FGA at 300 °C using Pt/Al gate stack                                                                                                                                                                                |

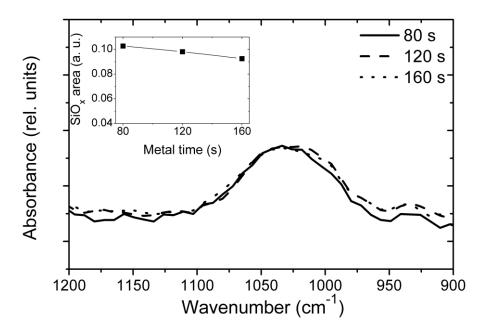

| <b>Figure V.13</b> : FTIR spectra for $Gd_2O_3$ samples with different metal deposition time: 80 120 and 160 s. Inset: $SiO_x$ area as a function of the metal deposition duration for the                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| same samples                                                                                                                                                                                                                                                                                                          |

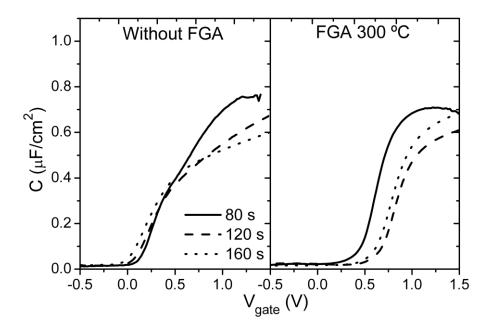

| <b>Figure V.14</b> : C-V <sub>gate</sub> characteristics for samples with different initial Gd deposition time (varied between 80 to 160 s) before and after the FGA at 300 °C                                                                                                                                        |

| <b>Figure V.15</b> : HRTEM image of the Gd <sub>2</sub> O <sub>3</sub> film with 160 s of Gd and 300 s of plasma oxidation at 30 W after a FGA at 300 °C using Pt/Al gate stack                                                                                                                                       |

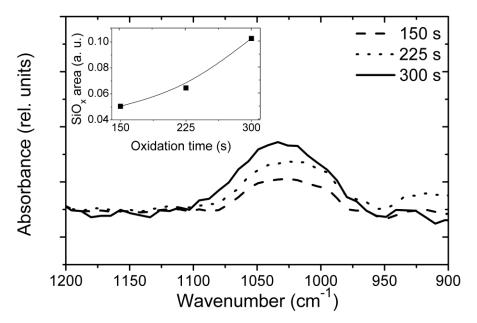

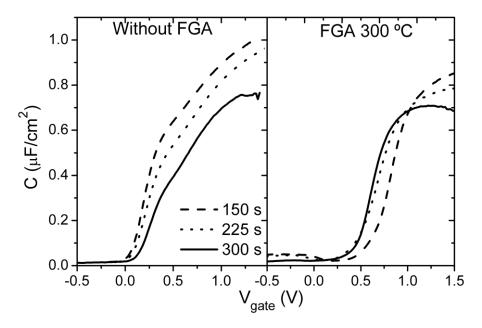

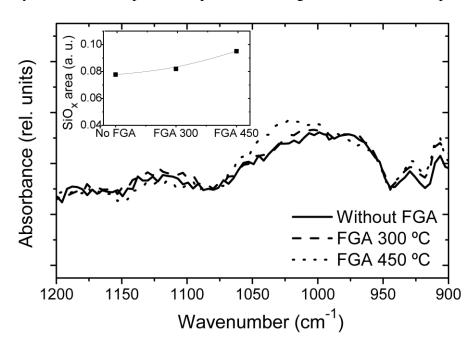

| <b>Figure V.16</b> : FTIR spectra for $Gd_2O_3$ samples with different oxidation time: 150, 225 and 300 s. Inset: $SiO_x$ area as a function of the oxidation time for the same samples . 118                                                                                                                         |

| <b>Figure V.17</b> : C-V <sub>gate</sub> before and after the FGA at 300 °C for samples with different oxidation duration: 150, 225 and 300 s                                                                                                                                                                         |

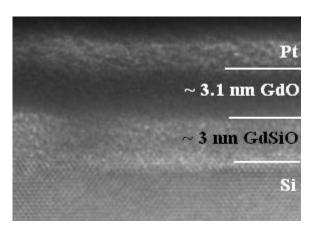

| <b>Figure V.18</b> : Cross-sectional HRTEM image of the Gd <sub>2</sub> O <sub>3</sub> film with 80 s of Gd and 150 s of plasma oxidation at 30 W after a FGA at 300 °C using Pt/Al gate stack 119                                                                                                                    |

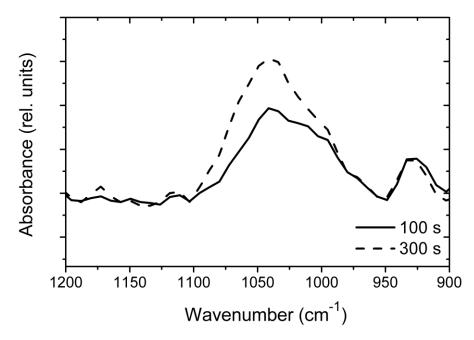

| <b>Figure V.19</b> : FTIR spectra for Gd <sub>2</sub> O <sub>3</sub> samples with 120 s of Gd and different duration of the plasma oxidation: 100 and 300 s                                                                                                                                                           |

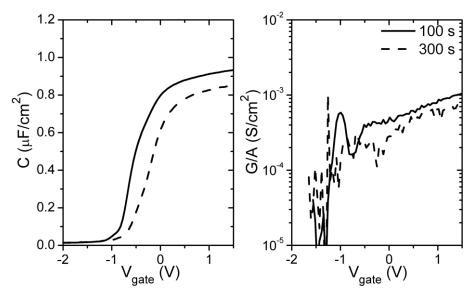

| <b>Figure V.20</b> : C-V <sub>gate</sub> and G-V <sub>gate</sub> curves measured at 10 kHz and after the FGA at 300 °C for samples with 120 s of Gd and 100 (solid lines) and 300 s (dashed lines) of plasma oxidation at 20 W                                                                                        |

| <b>Figure V.21</b> : J-V <sub>gate</sub> characteristic after FGA at 300 °C for samples with Gd deposition during 120 s and a plasma oxidation of 100 (solid lines) and 300 s (dashed lines). In grey is represented the sample with 120 s of Gd oxidized during 300 s at 30 W fabricated without FOX as a comparison |

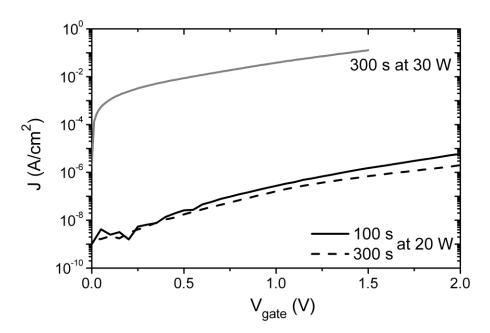

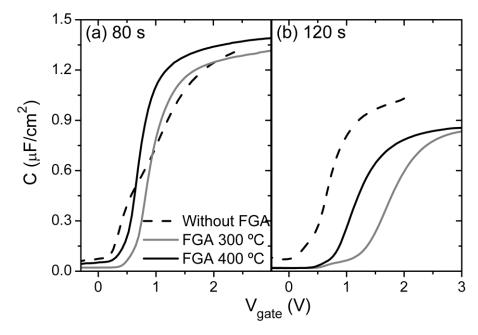

| <b>Figure V.22</b> : Normalized C-V <sub>gate</sub> curves measured at 10 kHz before and after the FGA at representative temperatures for samples with (a) 80 s and (b) 120 s of Gd with a plasma oxidation during 100 s                                                                                              |

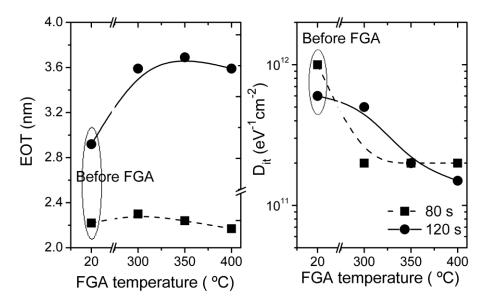

| <b>Figure V.23</b> : EOT (left) and $D_{it}$ (right) as a function of the annealing temperature for samples with 80 s (squares) and 120 s (circles) of Gd oxidized for 100 s                                                                                                                                          |

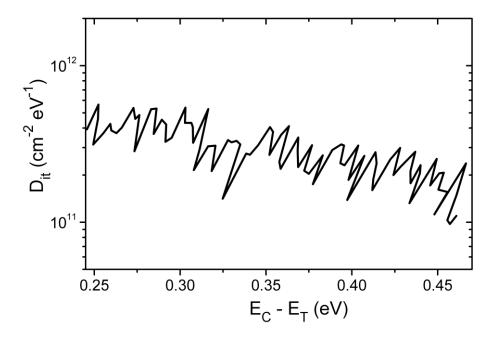

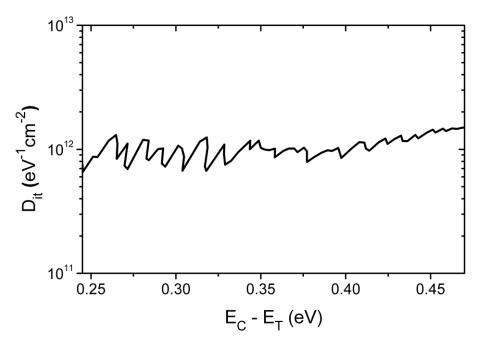

| <b>Figure V.24</b> : Interface trap density obtained by DLTS for sample with 80 s of Gd and 100 s oxidation measured after the FGA at 400 °C                                                                                                                                                                          |

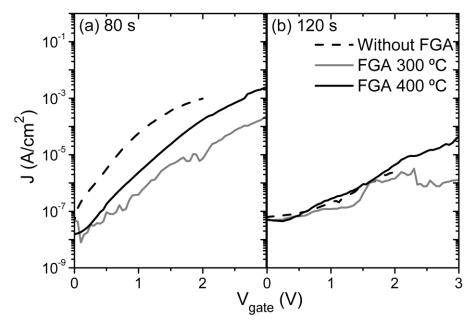

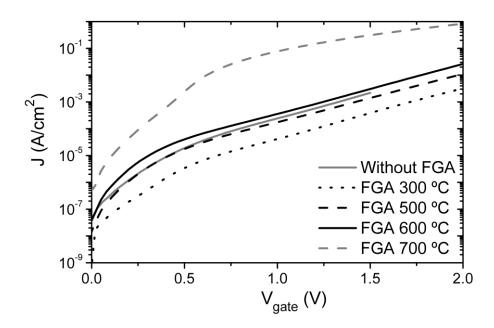

| <b>Figure V.25</b> : J-V <sub>gate</sub> characteristics before and after FGA at representative temperatures for (a) 80 s and (b) 120 s deposited Gd with a 100 s plasma oxidation                                                                                                                                    |

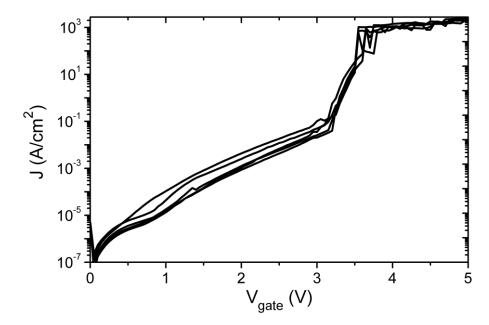

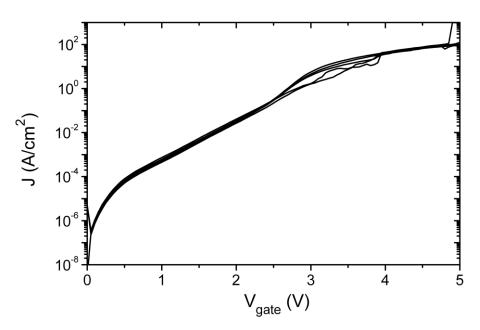

| <b>Figure V.26</b> : J-V <sub>gate</sub> curves for the sample with 80 s of Gd and 100 s of oxidation after FGA at 400 °C, measured in several devices to observe breakdown events and reproducibility                                                                                                                |

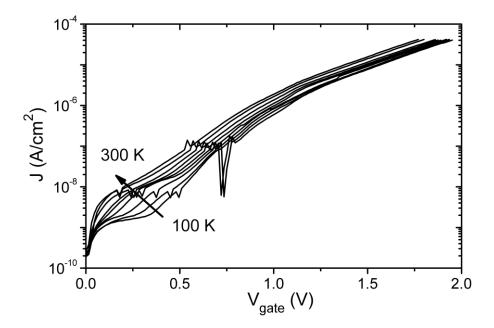

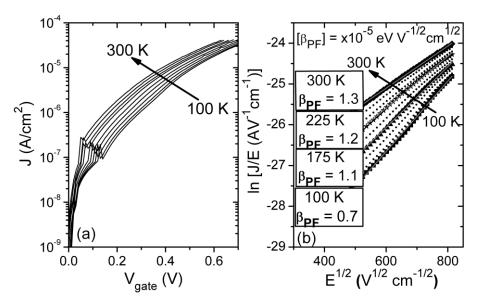

| <b>Figure V.27</b> : J-V <sub>gate</sub> characteristics measured at different temperatures (from 100 to 300 K) for the sample with 80 S of Gd and 100 s oxidation after the FGA at 300 °C. In the inset, the exponential slope of J at $V_{gate} > 1.3 \text{ V}$ as a function of the temperature is represented    |

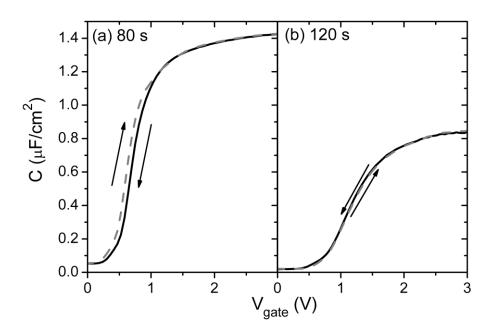

| <b>Figure V.28</b> : C-V <sub>gate</sub> hysteresis curves for (a) 80 s of Gd sample and (b) 120 s of Gd with 100 s of plasma oxidation at 10 kHz after FGA at 400 °C                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                           |

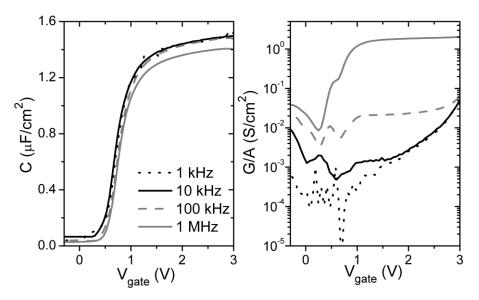

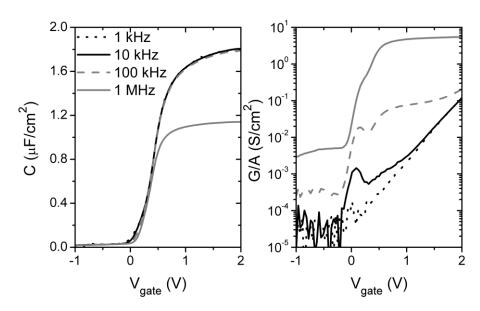

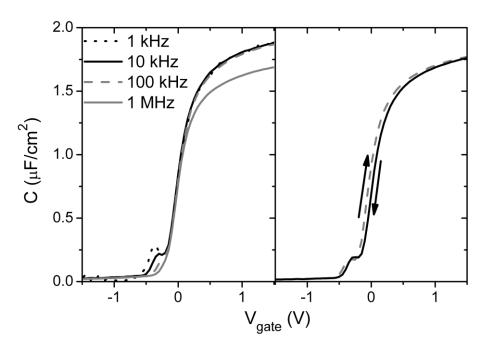

| <b>Figure V.29</b> : C-V <sub>gate</sub> and G-V <sub>gate</sub> curves measured at different frequencies after FGA at 400 °C for the sample with 80 s of Gd oxidized during 100 s with 20 W of $rf$ power. 129                                                                                                           |

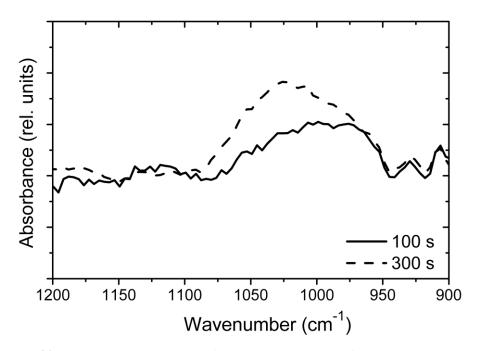

| Figure V.30: FTIR absorbance spectra for samples with 80 s of Sc and plasma                                                                                                                                                                                                                                               |

| oxidation duration of 100 and 300 s before the FGA                                                                                                                                                                                                                                                                        |

| <b>Figure V.31</b> : FTIR spectra of the $Sc_2O_3$ sample oxidized during 100 s before and after the FGA at 300 and 450 °C. Inset: $SiO_x$ band area as a function of the FGA                                                                                                                                             |

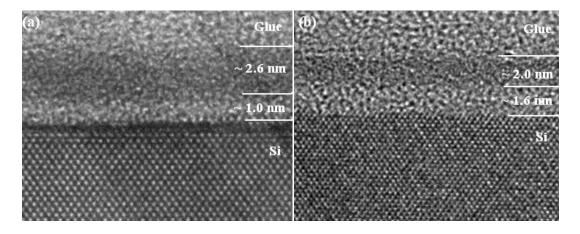

| <b>Figure V.32</b> : Cross-sectional HRTEM images of the ScO <sub>x</sub> samples with 80 s of Sc and plasma oxidation carried out during (a) 100 s and (b) 300 s after FGA at 450 °C 132                                                                                                                                 |

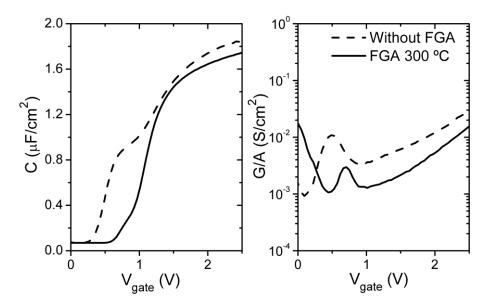

| <b>Figure V.33</b> : C and G as a function of $V_{gate}$ for samples with 80 s of Sc and are oxidation of 100 s before (dashed lines) and after the FGA at 300 °C (solid lines) 133                                                                                                                                       |

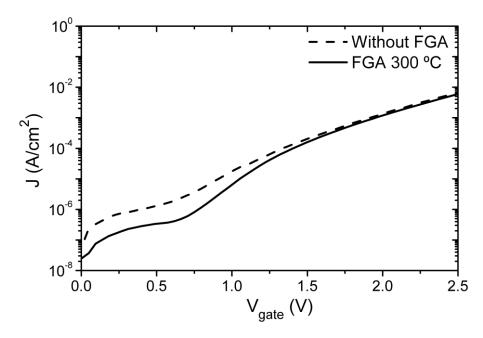

| <b>Figure V.34</b> : J vs $V_{gate}$ for the samples with Sc deposited for 80 s and a plasma oxidation for 100 and 300 s before and after the FGA at 300 °C                                                                                                                                                               |

| Figure VI.1: GDOS emission spectra of sputtered Gd in an Ar plasma at 30 W when                                                                                                                                                                                                                                           |

| the Sc rf power is (a) switched off and (b) on. The range where the most important lines of Gd I and Gd II are located is marked in the figure                                                                                                                                                                            |

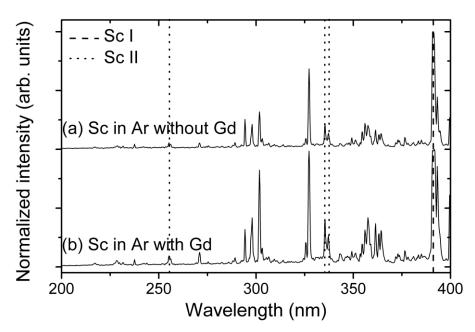

| <b>Figure VI.2</b> : GDOS emission spectra of sputtered Sc in an Ar atmosphere at 30 W when the Gd <i>rf</i> power is (a) switched off and (b) on. Sc I and Sc II lines are marked in the figure with dashed and dotted lines, respectively. The rest of the peaks presented in the spectra are related to Ar I and Ar II |

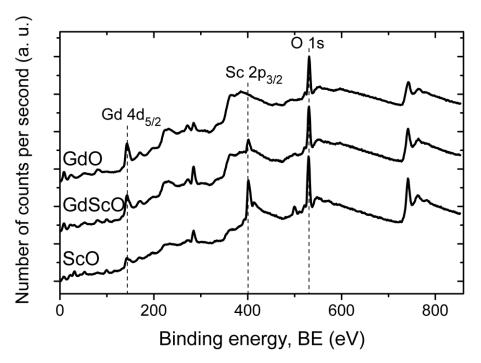

| <b>Figure VI.3</b> : XPS wide scan or survey spectra of $Gd_2O_3$ , $Gd_{2-x}Sc_xO_3$ and $Sc_2O_3$ samples after a FGA at 600 °C. $Gd_3O_3$ , $Gd_2O_3$ , $Gd_2O_3$ , $Gd_2O_3$ and $Gd_2O_3$ and $Gd_2O_3$ and $Gd_2O_3$ are marked in the figure                                                                       |

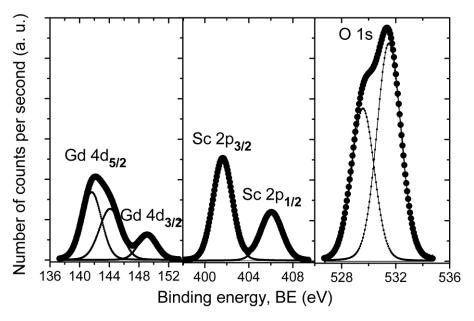

| <b>Figure VI.4</b> : High resolution XPS spectrum for $Gd_{2-x}Sc_xO_3$ sample after a FGA at 600 °C: Gd 4d (left) and Sc 2p (center) doublets and O 1s (right) together with their fits                                                                                                                                  |

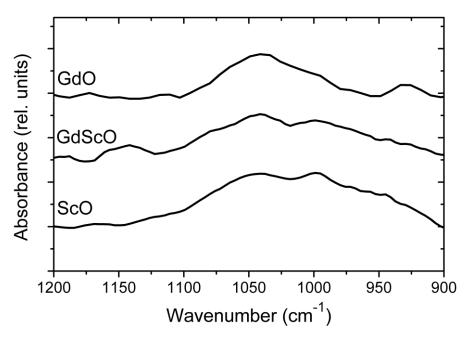

| <b>Figure VI.5</b> : FTIR absorbance spectra for the as deposited Gd <sub>2</sub> O <sub>3</sub> , Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> and Sc <sub>2</sub> O <sub>3</sub> samples                                                                                                                          |

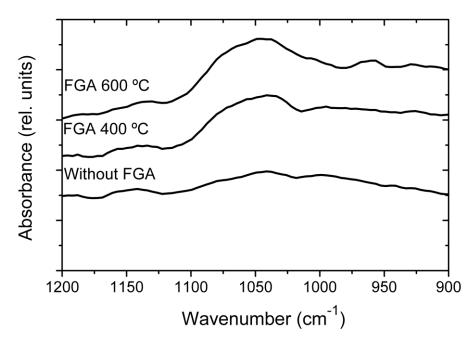

| <b>Figure VI.6</b> : FTIR spectra for the Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> film before and after different FGAs.148                                                                                                                                                                                     |

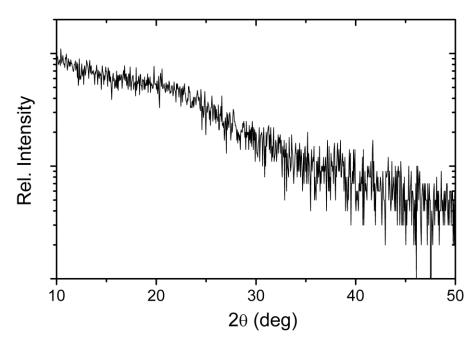

| <b>Figure VI.7</b> : Grazing incident XRD spectra of Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> film after a FGA at 600 °C was performed. No diffraction peaks are observed                                                                                                                                       |

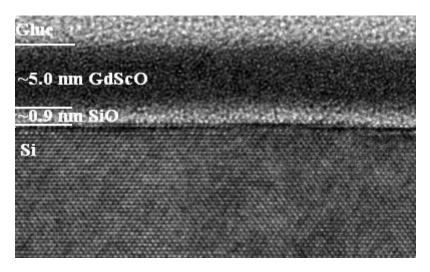

| <b>Figure VI.8</b> : HRTEM cross-sectional image of Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample obtained after the FGA at 600 °C                                                                                                                                                                            |

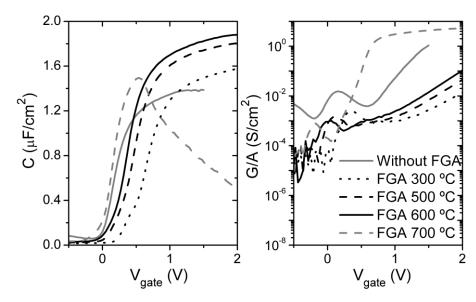

| <b>Figure VI.9</b> : Area normalized C and G as a function of $V_{gate}$ characteristics for the $Gd_{0.9}Sc_{1.1}O_3$ sample before and after several FGAs at different temperatures 151                                                                                                                                 |

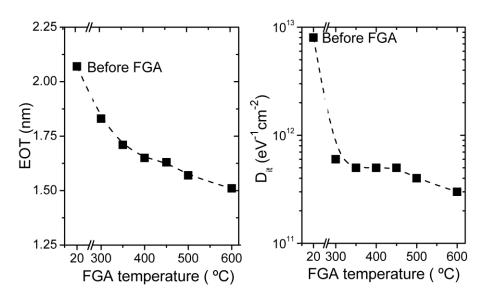

| <b>Figure V1.10</b> : EOT (left) and $D_{it}$ (right) values as a function of the annealing temperature for the sample fabricated with $Gd_{0.9}Sc_{1.1}O_3$ as dielectric                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

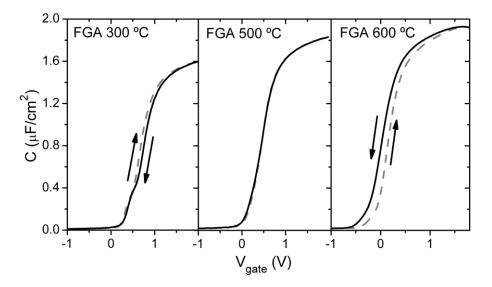

| <b>Figure VI.11</b> : Hysteresis C-V <sub>gate</sub> characteristics measured from inversion to accumulation and back again for the Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample after several FGAs at different temperatures.                                                                                                                   |

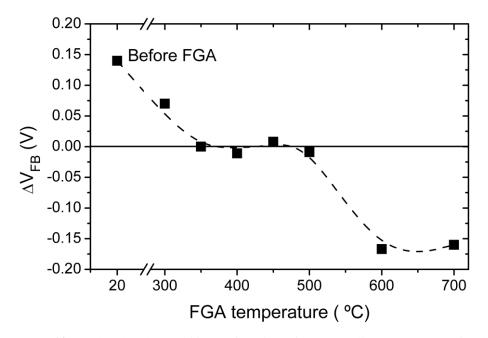

| <b>Figure VI.12</b> : Flatband voltage shift as a function of the annealing temperature for the $Gd_{0.9}Sc_{1.1}O_3$ sample                                                                                                                                                                                                                                  |

| <b>Figure VI.13</b> : C-V <sub>gate</sub> and G-V <sub>gate</sub> curves measured at different frequencies for the Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample after FGA at 600 °C                                                                                                                                                              |

| <b>Figure VI.14</b> : J-V <sub>gate</sub> characteristics for the Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample before and after different FGAs                                                                                                                                                                                                   |

| <b>Figure VI.15</b> : J-V <sub>gate</sub> curves for the Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> sample after an FGA at 600 °C, measured in several devices to observe breakdown events and reproducibility 157                                                                                                                                    |

| <b>Figure VII.1</b> : C-V <sub>gate</sub> curves for the sample with 80 s of Gd and a 300 s plasma oxidation at 30 W measured before (dashed lines) and after the FGA at 300 °C (solid lines) for two different top contacts: Pt/Al (as a reference) and thick Ti/Al                                                                                          |

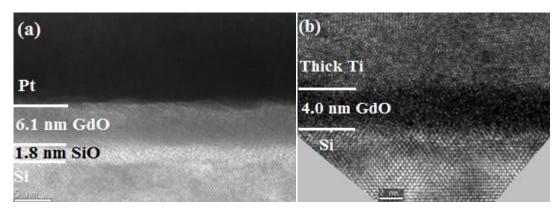

| <b>Figure VII.2</b> : HRTEM images for the samples with long oxidation (300 s at 30 W) with two metallic contacts: (a) Pt (as a reference) and (b) thick Ti                                                                                                                                                                                                   |

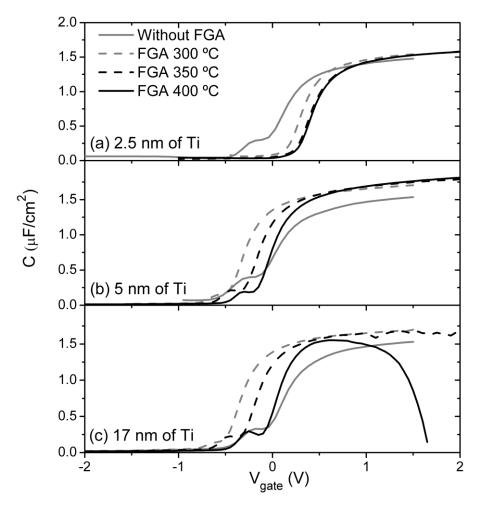

| <b>Figure VII.3</b> : C-V <sub>gate</sub> curves for the sample with 80 s of Gd and an 100 s plasma oxidation at 20 W measured before and after several FGAs with different thickness of Ti layers: (a) 2.5 nm, (b) 5 nm and (c) 17 nm                                                                                                                        |

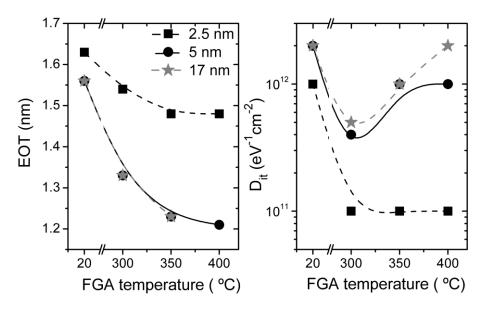

| <b>Figure VII.4</b> : EOT (left) and $D_{it}$ (right) values as a function of the annealing temperature for the samples fabricated with different Ti thicknesses: 2.5, 5 and 17 nm.                                                                                                                                                                           |

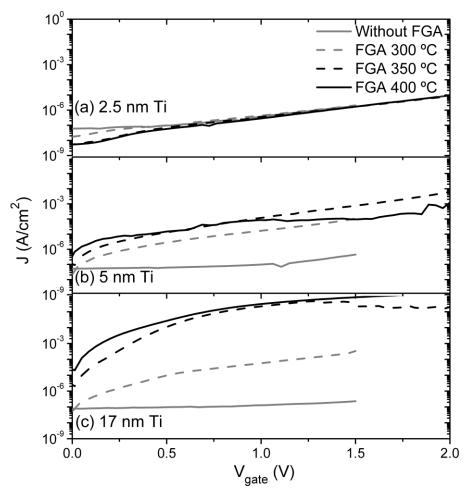

| <b>Figure VII.5</b> : J-V <sub>gate</sub> curves for the sample with 80 s of Gd and 100 s plasma oxidation at 20 W measured before and after several FGAs with different thickness of Ti layers:  (a) 2.5 nm, (b) 5 nm and (c) 17 nm                                                                                                                          |

| <b>Figure VII.6</b> : Interface trap density obtained by DLTS for sample with 80 s of Gd and 100 s oxidation at 20 W with 5 nm of Ti measured after the FGA at 400 °C                                                                                                                                                                                         |

| <b>Figure VII.7</b> : (a) J-V <sub>gate</sub> characteristics measured at different temperatures (from 100 K to 300 K) and (b) current electric field dependency fitting following the Poole-Frenkel model at several temperatures for the Si sample with 5 nm of Ti and after the FGA at $400 ^{\circ}$ C. The $\beta_{PF}$ parameter is shown in the figure |

| <b>Figure VII.8</b> : C-V <sub>gate</sub> frequency dispersion curves measured from 1 kHz to 1 MHz (left) and hysteresis measured at 10 kHz (right) for the sample fabricated with 5 nm of Ti and after the FGA at 400 °C                                                                                                                                     |

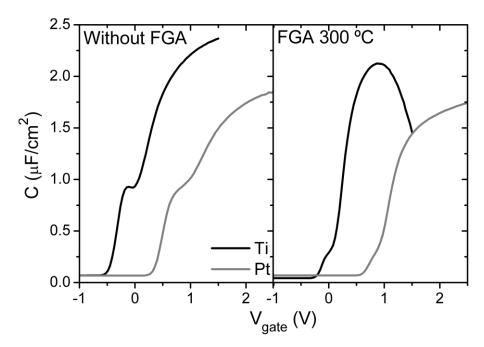

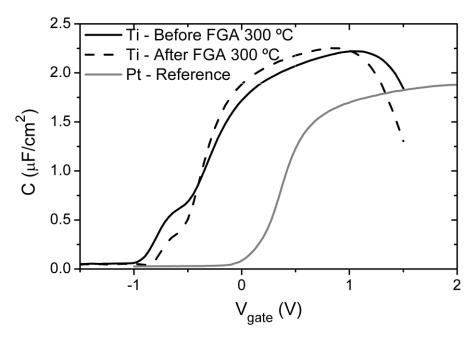

| <b>Figure VII.9</b> : C-V <sub>gate</sub> curves for the sample with 80 s of Sc and 100 s plasma oxidation at 20 W measured before (left) and after the FGA at 300 °C (right) for two different                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| electrodes: 5 nm of Ti capped with Pt (in black) and Pt (in grey as a reference) 174                                                                                                                                                                                                                                                                                                                            |

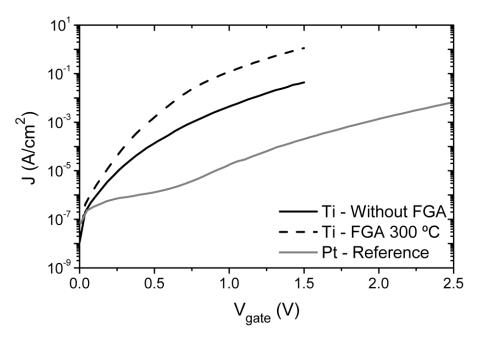

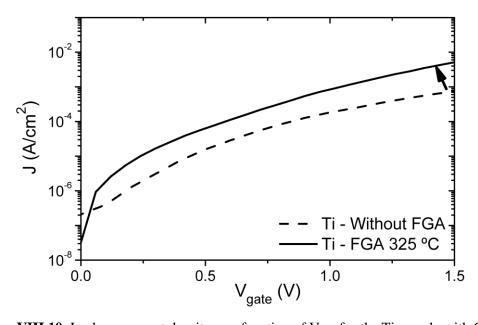

| <b>Figure VII.10</b> : J-V $_{gate}$ characteristics for the Sc $_2O_3$ sample (80 s of Sc and 100 s oxidation at 20 W) measured before (solid lines) and after the FGA at 300 °C (dashed lines) for 5 nm of Ti capped with Pt (in black). As a reference, the Pt sample is represented in grey                                                                                                                 |

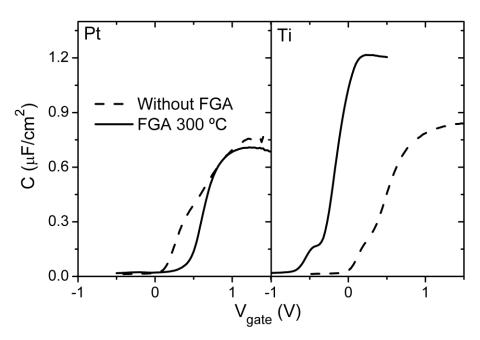

| Figure VII.11: C-V <sub>gate</sub> characteristics of capacitors with Gd <sub>0.9</sub> Sc <sub>1.1</sub> O <sub>3</sub> formed after a                                                                                                                                                                                                                                                                         |

| FGA at 600 °C using Ti as top electrode (in black) before (solid line) and after a second                                                                                                                                                                                                                                                                                                                       |

| FGA at 300 °C (dashed line). The same dielectric with Pt is represented as a reference in grey                                                                                                                                                                                                                                                                                                                  |

| Figure VII.12: J-V $_{gate}$ curves for the $Gd_{0.9}Sc_{1.1}O_3$ sample formed after a FGA at 600 $^{\circ}C$                                                                                                                                                                                                                                                                                                  |

| measured before (solid line) and after a second FGA at 300 $^{\circ}\text{C}$ (dashed line) with 5 nm                                                                                                                                                                                                                                                                                                           |

| of Ti capped with Pt (in black). As a reference, the Pt sample is represented in grey . 178                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                 |

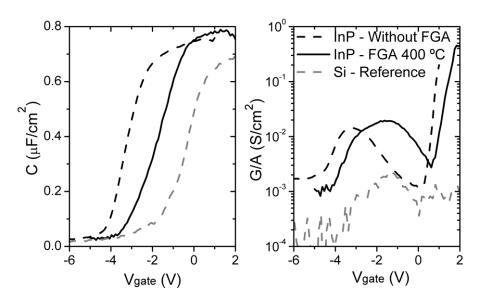

| <b>Figure VIII.1</b> : Normalized C-V <sub>gate</sub> and G-V <sub>gate</sub> curves measured at $10\text{kHz}$ before (dashed lines) and after the FGA at $400^{\circ}\text{C}$ (solid lines). In black is represented the InP sample with $120\text{s}$ of Gd and $200\text{s}$ of plasma oxidation (performed at $20\text{W}$ ) with Pt/Al. Also, Si sample as a reference is depicted in the figure in grey |

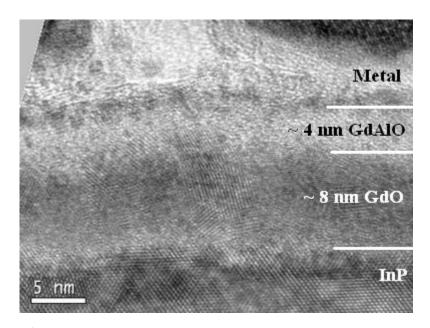

| Figure VIII.2: High resolution TEM image of a MIS device with 120 s of Gd and                                                                                                                                                                                                                                                                                                                                   |

| plasma oxidized during 200 s after the annealing at 400 °C                                                                                                                                                                                                                                                                                                                                                      |

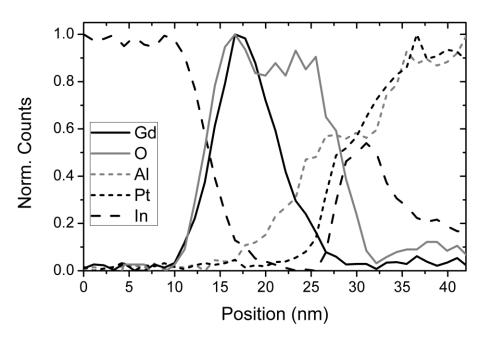

| <b>Figure VIII.3</b> : Depth profile of a MIS device (120 s of Gd and 200 s plasma oxidation) with Pt/Al electrode after FGA at 400 °C obtained from the EELS spectra during STEM measurements. Each emission line was normalized to its maximum value                                                                                                                                                          |

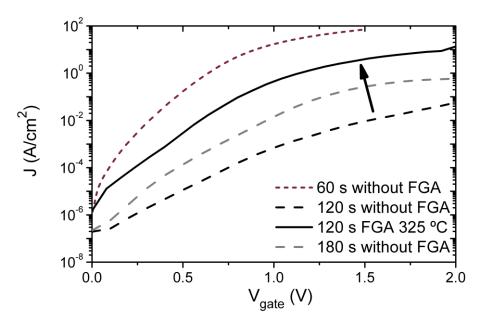

| <b>Figure VIII.4</b> : Gate leakage as a function of gate voltage of the InP devices with pure Pt gate electrode and different Gd sputtering times before (dashed lines) and after the FGA at 325 °C (solid line)                                                                                                                                                                                               |

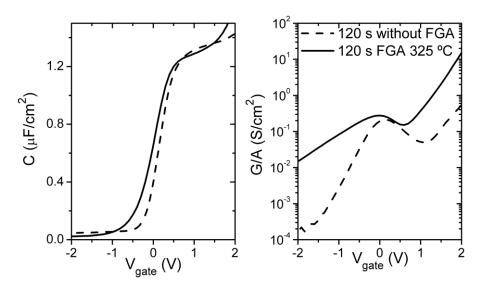

| <b>Figure VIII.5</b> : Gate normalized capacitance (left) and conductance (right) vs gate voltage of the devices with 120 s of Gd and a plasma oxidation of 100 s (at 20 W) with pure Pt electrode measured before and after the FGA at 325 °C                                                                                                                                                                  |

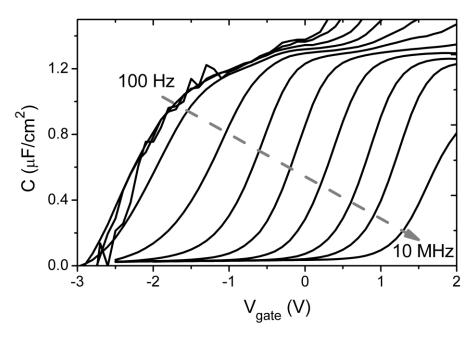

| <b>Figure VIII.6</b> : Frequency dispersion $C\text{-}V_{gate}$ curves measured from 100 Hz to 10 MHz for the InP sample with 120 s of Gd and 100 s oxidation after a FGA at 325 °C for 30 min                                                                                                                                                                                                                  |

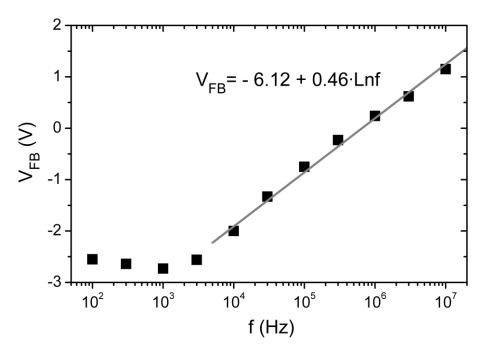

| <b>Figure VIII.7</b> : Experimental data for $V_{FB}$ as a function of the frequency measured for the InP sample with 120 s of Gd and a plasma oxidation of 100 s with Pt after the FGA at 325 °C and its linear fit                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                 |

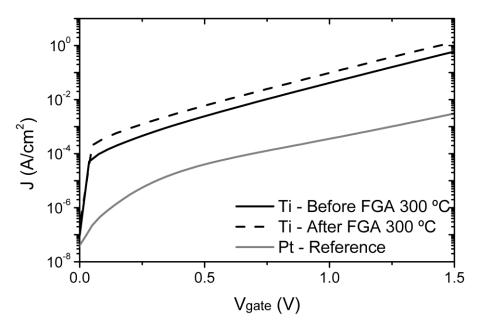

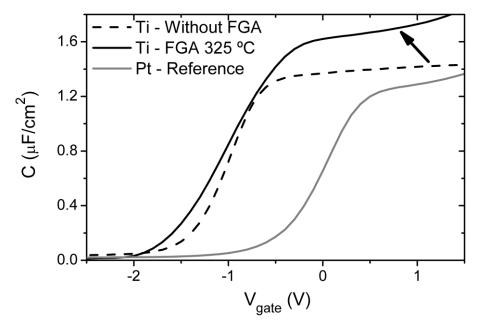

| Figure VIII.8: Normalized C-V <sub>gate</sub> characteristics for the InP sample with 120 s of Gd |

|---------------------------------------------------------------------------------------------------|

| and 100 s of plasma oxidation at 20 W measured at 10 kHz with 5 nm of Ti before and               |

| after the FGA at 325 °C. The Pt sample is also shown as a reference in grey 193                   |

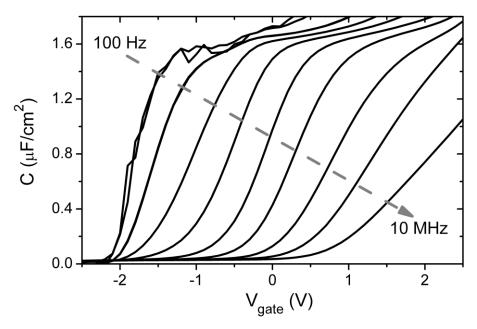

| Figure VIII.9: C-V <sub>gate</sub> curves measured at several frequencies (from 100 Hz to         |

| 10 MHz) for the InP sample with Ti after the FGA at 325 °C                                        |

| Figure VIII.10: Leakage current density as a function of V <sub>gate</sub> for the Ti sample with |

| GdO <sub>x</sub> measured before and after the FGA at 325 °C                                      |

#### LIST OF TABLES

| Table IV.1: EOT values extracted from electrical measurements after FGA at 450 °C                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and $\kappa_{GdO}$ obtained from XRR and TEM thicknesses                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                    |

| <b>Table V.1</b> : EOT and $D_{it}$ values extracted from electrical measurements after the FGA at                                                                                                                                                                                                                                 |

| 300 °C for samples with different dielectrics obtained with the two-step method ( $Gd_2O_3$ and $Sc_2O_3$ ) and two metallic contacts: Al and Pt/Al                                                                                                                                                                                |

| <b>Table V.2</b> : EOT values and $D_{it}$ extracted from electrical measurements before and after the FGA at 300 °C for samples with different oxidation power. "" means that the $D_{it}$ value is under the detection limit of the method                                                                                       |

| <b>Table V.3</b> : EOT values and $D_{it}$ extracted from electrical measurements before and after                                                                                                                                                                                                                                 |

| the FGA at 300 °C for samples with different metal deposition duration. "" means that the $D_{it}$ value is under the detection limit of the method                                                                                                                                                                                |

| <b>Table V.4</b> : EOT values and $D_{it}$ extracted from electrical measurements before and after the FGA at 300 °C for samples with different oxidation duration step. "" means that the $D_{it}$ value is under the detection limit of the method                                                                               |

| <b>Table V.5</b> : EOT values and $D_{it}$ extracted from electrical measurements before and after the FGA at 300 °C for samples with 120 s of Gd and different plasma oxidation duration                                                                                                                                          |

| <b>Table VII.1</b> : EOT and $D_{it}$ values extracted from electrical measurements before and after the FGA at 300 °C for samples with 80 s of Gd and a plasma oxidation of 300 s (at 30 W) with two different top electrodes: Pt/Al and thick Ti/Al. "" means that the $D_{it}$ value is under the detection limit of the method |

|                                                                                                                                                                                                                                                                                                                                    |

# LIST OF ABBREVIATIONS

| Abbreviation | Meaning                                          |

|--------------|--------------------------------------------------|

| ALD          | Atomic layer deposition                          |

| BOE          | Buffer oxide etching                             |

| CCD          | Charge coupled device                            |

| CMOS         | Complementary metal-oxide-semiconductor          |

| CZ           | Czochralski                                      |

| DI           | Deionized                                        |

| DLTS         | Deep level transient spectroscopy                |

| DMSO         | Dimethyl sulfoxide                               |

| DSP          | Double side polished                             |

| e-beam       | Electron beam                                    |

| EDX          | Energy dispersive X ray spectroscopy             |

| EELS         | Electron energy loss spectroscopy                |

| FGA          | Forming gas anneal                               |

| FIB          | Focused ion beam                                 |

| FOX          | Field oxide                                      |

| FTIR         | Fourier transform infrared spectroscopy          |

| FZ           | Float zone                                       |

| GDOS         | Glow discharge optical spectroscopy              |

| GIXRD        | Grazing incidence x ray diffraction              |

| HPS          | High pressure sputtering                         |

| HRTEM        | High resolution transmission electron microscopy |

| IC           | Integrated circuit                               |

| IL           | Interlayer                                       |

| IPA          | Isopropyl alcohol                                |

ITRS International Technology Roadmap for

Semiconductors

MBE Molecular beam epitaxy

MFC Mass flow controller

MIS Metal-insulator-semiconductor

MOCVD Metal-organic chemical vapor deposition

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field effect transistor

PLD Pulsed laser deposition

PVD Physical vapor deposition

RCA Radio Corporation of America

rf Radiofrequency

RTA Rapid thermal annealing

SC Standard clean

SMU Source measuring unit

SSP Single side polished

STEM Scanning transmission electron microscopy

TCAD Technology computer aided design

TEM Transmission electron microscopy

ULSI Ultra large-scale integration

USB Universal serial bus

VLSI Very large-scale integration

XPS X ray photoelectron spectroscopy

XRD X ray diffraction

XRR X ray reflectivity

#### LIST OF SYMBOLS

| Symbol                  | Unit                | Description                                                       |

|-------------------------|---------------------|-------------------------------------------------------------------|

| $\alpha(\omega)$        | $\mathrm{m}^{-1}$   | Absorbance in FTIR                                                |

| β                       | deg or rad          | Incident angle in GIXRD                                           |

| $eta_{PF}$              | $eVm^{1/2}/V^{1/2}$ | Poole-Frenkel coefficient                                         |

| $\Delta C$              | C                   | Capacitance difference                                            |

| $\Delta G$              | J/mol               | Change in the Gibbs energy                                        |

| $\Delta V_{FB}$         | V                   | Flatband voltage shift                                            |

| $\mathcal{E}_0$         | F/m <sup>2</sup>    | Permittivity of free space                                        |

| $	heta_{hkl}$           | deg or rad          | Diffracted angle in GIXRD                                         |

| $2\theta$               | deg or rad          | Angle of the scan in GIXRD                                        |

| κ                       | Adim.               | Relative permittivity                                             |

| $\kappa_{ m eff}$       | Adim.               | Effective relative permittivity                                   |

| $K_{s}$                 | Adim.               | Semiconductor relative permittivity                               |

| К <sub>high к</sub>     | Adim.               | Relative permittivity of the high $\kappa$ material               |

| $\kappa_{\mathrm{SiO}}$ | Adim.               | Relative permittivity of SiO <sub>2</sub>                         |

| λ                       | m                   | Wavelength                                                        |

| $\mu$                   | $m^2/Vs$            | Mobility                                                          |

| v                       | $\mathrm{m}^{-1}$   | Wavenumber                                                        |

| $	au_e$                 | S                   | Emission time constant in DLTS                                    |

| $arPhi_{MS}$            | eV                  | Work function differences between the metal and the semiconductor |

| ω                       | rad/s               | Angular frequency                                                 |

| BE                      | eV                  | Binding energy                                                    |

| С                       | m/s                 | Light velocity                                                    |

C  $\mu F/cm^2$  Capacitance per area unit

C F Capacitance

$C_0$  F Capacitance at t = 0

$C_{accum}$  Measured accumulation capacitance per unit

area

C<sub>HF</sub> F High frequency capacitance

$C_{INS}$  F Insulator capacitance

$C_{it}$  F Interface capacitance

C<sub>LF</sub> F Low frequency capacitance

$C_m$  F Measured capacitance

$C_{m,a}$  F Measured capacitance in accumulation

$C_{m,corr}$  F Corrected measured capacitance

$C_{ox}$   $\mu F/cm^2$  Oxide capacitance density

$C_s$  F Semiconductor capacitance

CET nm Capacitance equivalent thickness

$d_{hkl}$  m Interplanar distance

$D_{it}$  eV<sup>-1</sup>m<sup>-2</sup> Interface trap state density

E V/m Electric field (Poole-Frenkel equation)

E<sub>C</sub> eV Conduction band energy

E<sub>Fi</sub> eV Intrinsic Fermi level

$E_{Fm} \hspace{1.5cm} eV \hspace{1.5cm} Metal \; Fermi \; level$

E<sub>Fs</sub> eV Semiconductor Fermi level

$E_g$  eV Bandgap energy

$E_k$  eV Kinetic energy

E<sub>V</sub> eV Valence band energy

EOT nm Equivalent oxide thickness

| $EOT_{high\;\kappa}$                                    | nm                         | EOT related to the high $\kappa$                                                                                                                                                                                             |

|---------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathrm{EOT}_{\mathrm{IL}}$                            | nm                         | EOT related to the IL                                                                                                                                                                                                        |

| f                                                       | Hz                         | Frequency                                                                                                                                                                                                                    |

| $F_{ox}$                                                | V/m                        | Electric field oxide                                                                                                                                                                                                         |