## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2022

# Efficient Evaluation of Probability and Reliability with Digital Integrated Circuits

Suoyue Zhan University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Zhan, Suoyue, "Efficient Evaluation of Probability and Reliability with Digital Integrated Circuits" (2022). *Electronic Theses and Dissertations*. 9125. https://scholar.uwindsor.ca/etd/9125

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

## Efficient Evaluation of Probability and Reliability with Digital Integrated Circuits

By

### SUOYUE ZHAN

A Dissertation Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario, Canada

2022

© 2022 Suoyue Zhan

## Efficient Evaluation of Probability and Reliability with Digital Integrated Circuits

by

Suoyue Zhan

APPROVED BY:

J. Han, External Examiner

University of Alberta

H. Zhang

Department of Biomedical Sciences

H. Wu Department of Electrical and Computer Engineering

M. Azzouz Department of Electrical and Computer Engineering

C. Chen, Advisor Department of Electrical and Computer Engineering

August 30, 2022

#### DECLARATION OF CO-AUTHORSHIP / PREVIOUS PUBLICATION

#### I. Co-Authorship

I hereby declare that this thesis incorporates material that is result of joint research, as follows:

- "Chapters 4 and 5 of the thesis include the outcome of publications which have the following other co-authors: Chunhong Chen (academic advisor). In all cases only my primary contributions towards these publications are included in this thesis, and the contribution of co-author Chunhong Chen was primarily through methodology development, algorithm design, simulation results analysis and manuscript editing".

- "Chapter 3 incorporates unpublished material under the supervision of professor Chunhong Chen. In all cases the primary contributions, experimental designs, MATLAB coding, data analysis, interpretation, and writing were performed by myself; The contribution of Chunhong Chen was through the key ideas, interpretation and manuscript writing/editing".

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my thesis, and have obtained written permission from each of the co-author(s) to include the above material(s) in my thesis.

I certify that, with the above qualification, this thesis, and the research to which it refers, is the product of my own work.

II. Previous Publication

This thesis includes 3 original papers that have been previously published/submitted to journals/conference for publication, as follows:

| Thesis Chapter                                                                                                                                                                                                                                | Thesis Chapter Publication title/full citation                                                                                                                                                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Chapter [3]                                                                                                                                                                                                                                   | <i>Chapter [3]</i> S. Zhan and C. Chen, "A Hybrid Method for<br>Signal Probability and Reliability Estimation with<br>Combinational Circuits," <i>Integration, the VLSI</i><br><i>Journal</i> , 2022 |             |

| Chapter [4]<br>S. Zhan and C. Chen, "An Efficient Method for<br>Sequential Circuit Reliability Estimation," Proc.<br>65 <sup>th</sup> IEEE International Midwest Symposium on<br>Circuits and Systems (MWSCAS), Japan, August 7-<br>10, 2022. |                                                                                                                                                                                                      | "Published" |

| Chapter [5]<br>S. Zhan and C. Chen, "Circuit Reliability Analysis<br>with Consideration of Aging Effect," Proc. 35 <sup>th</sup><br>Symposium on Integrated Circuits and Systems<br>Design (SBCCI), Brazil, August 22-26, 2022.               |                                                                                                                                                                                                      | "Published" |

I certify that I have obtained a written permission from the copyright owner(s) to include the above published material(s) in my thesis. I certify that the above material describes work completed during my registration as a graduate student at the University of Windsor.

#### III. General

I declare that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

#### ABSTRACT

As complementary metal-oxide-semiconductor (CMOS) devices shrink to nanoscale, digital integrated circuits (ICs) are more susceptible to various environmental parameters, such as temperature, supply voltage, wiring, noise, and fabrication process variations. This would reduce the circuit operation reliability (i.e., the probability that a circuit or component is performing its intended logic function). Signal probability (the probability that a digital signal is producing logic 1) is another factor that measures circuit's dynamic behavior and power dissipation. Research shows that signal probability and reliability within ICs may interact with each other in a complicated way. Generally speaking, as signal probability changes due to input probability variations, so does the signal reliability, and vice versa. This motivates simultaneous evaluation of both for digital ICs towards their performance improvement. However, this evaluation could be a challenge especially for large-scale circuits, due to signal correlations caused by reconvergent fanouts within circuits. Out of two existing evaluation methods, i.e., numerical and analytical methods, the former can give high accuracy level at the cost of expensive computation, while the latter does exactly the opposite.

This thesis provides a hybrid solution by taking advantage of both numerical and analytical methods to achieve fast and accurate evaluation for signal probability and reliability for ICs (including both combinational and sequential circuits). First, we develop a categorization-based analytical model for combinational circuits to deal with a variety of signal correlations. For strongly correlated or independent cases, analytical solutions are applied for accurate results. For cases with moderate correlation strength, we use local bitstream simulations for fast estimation. Our simulation results show that the proposed method is hundreds of times faster than Monte-Carlo (MC) simulation, while keeping almost same level of accuracy.

We then extend the above method to sequential circuits (with finite-statemachine model) for probability and reliability evaluation. Since sequential circuits can be viewed as an unfolded network of combinational logic, our focus is on how both probability and reliability converge to a final stable state over a certain number of cycles/iterations. To improve the efficiency of this convergence process, we propose a two-step-convergence (TSC) model instead of using traditional step-size based convergence. Simulation results show that the proposed method speeds up the process by around 30% on average compared to traditional method while maintaining a high level of accuracy.

Finally, we study the impact of device aging on circuit reliability. After years of operation, CMOS (especially PMOS) devices would experience an increase in their threshold voltage, a phenomenon called Negative Bias Temperature Instability (NBTI). This aging effect leads to the increased gate delay with late arrival time of signals, making circuits temporally unreliable. Threshold voltage changes may also negatively affect the probability that transistors perform intended logical operations, causing them spatially more unreliable. Our investigation focuses on evaluation of the overall reliability at circuit-level by considering both spatial (solely considering the correctness of signal logic values) and temporal (considering the signal arrival time to catch up sampling action) aspects of it. This would help circuit designers predict the circuit lifetime. Simulations on benchmark circuits show that the reliability degradation rate due to aging effect ranges from 1.5% to 8.2% over one-year period, depending on specific circuits.

#### ACKNOWLEDGEMENTS

I would like to express my deep sense of gratitude towards my academic advisor Prof. Chunhong Chen for the continuous support of my PhD study and related research. This thesis, as well as the publications, would never be possible without the expertise. He has been extremely patient guiding me into the research world and demonstrating me all the qualities a researcher should have. I could not image having a better mentor than him.

I would like to extend my sincere appreciation to the committee members. Thanks for their valuable comments and advice throughout my PhD study.

Meanwhile, a debt of gratitude is owed to University of Windsor as well as the Department of Electrical and Computer Engineering. Thanks for providing such incredible chance to study here.

Last but not least, I would like to offer my thanks to my family, especially my wife and my parents, for their consistent support and encouragement during the years of my research.

| TABLE OF C | ONTENTS |

|------------|---------|

|------------|---------|

| DECLARATION OF CO-AUTHORSHIP / PREVIOUS PUBLICATION                         | iii  |

|-----------------------------------------------------------------------------|------|

| ABSTRACT                                                                    | v    |

| ACKNOWLEDGEMENTS                                                            | vii  |

| LIST OF TABLES                                                              | xi   |

| LIST OF FIGURES                                                             | xii  |

| LIST OF ABBREVIATIONS/SYMBOLS                                               | xiii |

| LIST OF APPENDICES                                                          | xiv  |

| CHAPTER 1 INTRODUCTION                                                      | 1    |

| 1.1 Research Background                                                     | 1    |

| 1.2 Objectives                                                              | 2    |

| 1.3 Main Contributions                                                      | 3    |

| 1.4 Thesis Organization                                                     | 4    |

| CHAPTER 2 LITERATURE REVIEW                                                 | 5    |

| 2.1 Evaluation of Signal Probability and Reliability Under Zero-delay Model | 5    |

| 2.1.1Evaluation for Combinational Circuits                                  | 5    |

| 2.1.2 Evaluation for Sequential Circuits                                    | 9    |

| 2.2 Evaluation of Signal Probability and Reliability Considering Delay and  |      |

| Aging Effect                                                                |      |

| 2.2.1 Aging Effect on Spatial Reliability                                   |      |

| 2.2.2 Aging Effect on Temporal Reliability                                  | 13   |

| CHAPTER 3 PROBABILITY AND RELIABILITY ESTIMATION FOR                        |      |

| COMBINATIONAL CIRCUITS                                                      |      |

| 3.1 Signal Probability and Joint Probability Vector                         |      |

| 3.1.1 Signal Probability                                                    | 14   |

| 3.1.2 Joint Probability Vector                                              | 15   |

| 3.2 Signal Reliability and Joint Conditional Probability Matrix (JCPM)      | 15   |

| 3.2.1 Signal Reliability                                                    | 15 |

|-----------------------------------------------------------------------------|----|

| 3.2.2 Joint Conditional Probability Matrix                                  | 16 |

| 3.3 Gate Level Probability and Reliability Propagation                      | 18 |

| 3.4 Correlation Categorization and JCPM Estimation                          |    |

| 3.4.1 Category 'S'                                                          | 20 |

| 3.4.2 Category 'N'                                                          | 25 |

| 3.4.3 Category 'I'                                                          | 25 |

| 3.4.4 Multi-level Category                                                  | 26 |

| 3.5 Bitstream Simulation for JPV and JCPM Estimation                        | 29 |

| 3.5.1 Bitstream Simulation for Single-level Category                        | 29 |

| 3.5.2 Bitstream Simulation for Multi-level Category                         | 36 |

| 3.6 Algorithm Description                                                   | 39 |

| 3.7 Simulation Results and Performance Comparison                           | 42 |

| 3.8 Summary                                                                 | 50 |

| CHAPTER 4 PROBABILITY AND RELIABILITY ESTIMATION FOR<br>SEQUENTIAL CIRCUITS | 51 |

| 4.1 Combinational Equivalent of Sequential Circuits                         | 51 |

| 4.2 Convergence Process Analysis and Two-Step-Convergence (TSC) Method      | 51 |

| 4.2.1 Convergence Process for Sequential Circuit                            | 51 |

| 4.2.2 Two-Step-Convergence Method                                           | 52 |

| 4.3 Simulation Results and Performance Comparison                           | 54 |

| 4.4 Summary                                                                 | 58 |

| CHAPTER 5 RELIABILITY ESTIMATION WITH CONSIDERATION OF AGING EFFECT         | 59 |

| 5.1 Spatial Reliability and Temporal Reliability                            |    |

| 5.1.1 Spatial Reliability and Spatial Probability of Failure (SPF)          |    |

| 5.1.2 Temporal Reliability and Temporal Probability of Failure (TPF)        | 60 |

| 5.2 Threshold Variation under Aging Effect                                  |    |

| 5.3 Estimation of SPF                                                       |    |

| 5.3.1 Estimation of SPF for MOSFETs                                         |    |

| 5.3.2 Estimation of SPF for Logic Gates and Integrated Circuits             |    |

| 5.4.1 Gate Delay Distribution                       |     |

|-----------------------------------------------------|-----|

|                                                     | 64  |

| 5.4.2 Circuit Delay Distribution and TPF Estimation |     |

| 5.5 Algorithm Description                           | 65  |

| 5.6 Error Analysis                                  | 66  |

| 5.7 Simulation Results                              | 69  |

| 5.8 Summary                                         | 72  |

| CHAPTER 6 CONCLUSION AND FUTURE WORK                | 73  |

| REFERENCES/BIBLIOGRAPHY                             | 75  |

| APPENDICES                                          | 80  |

| Appendix A. Important MATLAB Code                   | 80  |

| VITA AUCTORIS                                       | 132 |

## LIST OF TABLES

| Table I. CONDITIONAL RELIABILITIES FOR CIRCUIT C432 WITH $r_g = 0.99917$                                           |

|--------------------------------------------------------------------------------------------------------------------|

| Table II. Statistics on Frequency of Occurrences (%) for Different      Correlation Categories                     |

| Table III. PROBABILITY AND RELIABILITY ESTIMATION RESULTS BY PROPOSEDMETHOD AND CC-SPRA                            |

| Table IV. OUTPUT RELIABILITY ESTIMATION ERRORS, CPU TIME AND SPEEDUPFACTOR FOR THE PROPOSED METHOD WITH COMPARISON |

| Table V. COMPARISON OF NUMBER OF ITERATIONS TO CONVERGE       55                                                   |

| Table VI. S27 Convergence Process Information                                                                      |

| Table VII. ACCURACY AND SPEED COMPARISON OF TSC AND SEQ-RE       57                                                |

| Table VIII. DETAILED PERFORMANCE OF THE PROPOSED TSC    57                                                         |

| Table IX. Comparison of $pf_{NAND}$ Evaluated by Proposed Method and MCSIMULATION                                  |

| Table X. MEAN OF SIGNAL DELAY FOR C1769                                                                            |

| Table XI. Spatial PFs for Elements in C1769                                                                        |

| Table XII. CIRCUIT RELIABILITY SIMULATIONS ON SOME ISCAS'85 AND ISCAS'89         CIRCUITS WITH 1-YEAR OPERATION    |

## LIST OF FIGURES

| Figure 1. Sequential circuit and its combinational equivalent10                                                             | 0 |

|-----------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2. Examples of correlation category 'S'2                                                                             | 1 |

| Figure 3. Examples of correlation category ' <i>N</i> '2'                                                                   | 7 |

| Figure 4. Examples of 2-level correlation category                                                                          | 8 |

| Figure 5. Benchmark Circuit C1732                                                                                           | 2 |

| Figure 6. An example circuit with 5-level category of 'N3-N3-N3-S1' being         treated as category 'I' for approximation | 4 |

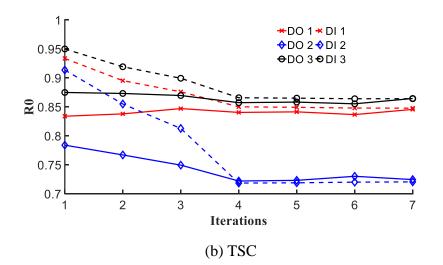

| Figure 7. Convergence process of $R^0$ in circuit S27 with 3 DFFs                                                           | 4 |

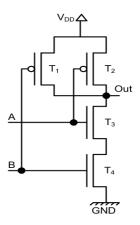

| Figure 8. NAND logic gate63                                                                                                 | 3 |

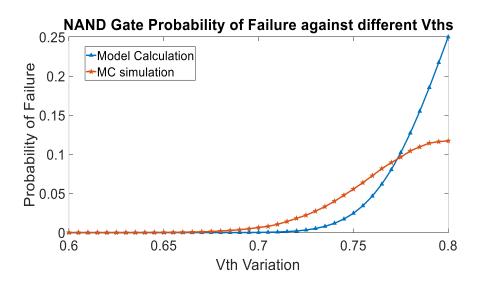

| Figure 9. $pf_{NAND}$ trends as $V_{th}$ changes                                                                            | 8 |

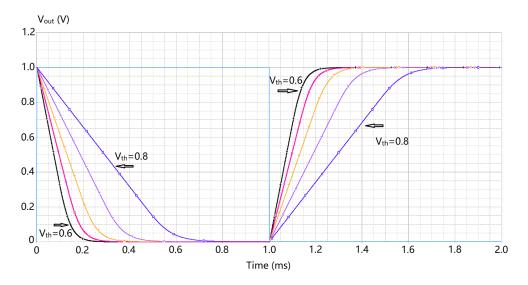

| Figure 10. The transient process of output voltage for NAND gate68                                                          | 8 |

## LIST OF ABBREVIATIONS/SYMBOLS

| CMOS    | Complementary metal-oxide-semiconductor                                             |

|---------|-------------------------------------------------------------------------------------|

| IC      | Integrated circuits                                                                 |

| MC      | Monte-Carlo                                                                         |

| TSC     | Two-step-convergence                                                                |

| NBTI    | Negative bias temperature instability                                               |

| PTM     | Probabilistic transfer matrices                                                     |

| ITM     | Ideal transfer matrix                                                               |

| PGM     | Probabilistic gate matrix                                                           |

| ER      | Equivalent reliability model                                                        |

| CC-SPRA | Correlation coefficients approach for signal probability-based reliability analysis |

| DI      | Dummy input                                                                         |

| DO      | Dummy output                                                                        |

| VDD     | Supply voltage                                                                      |

| P*      | Error-free signal probability                                                       |

| Р       | Signal probability                                                                  |

| PF      | Probability of failure                                                              |

| JPV     | Error-free joint probability vector                                                 |

| JCPM    | Joint conditional probability matrix                                                |

| PV      | Error-free probability vector                                                       |

| RV      | Reliability vector                                                                  |

| CGSP    | Cross-gate signal pairs                                                             |

| DFF     | D-flip-flop                                                                         |

| SPF     | Spatial probability of failure                                                      |

| TPF     | Temporal probability of failure                                                     |

| CLK     | Clock signal                                                                        |

| CDF     | Cumulative density function                                                         |

| PDD     | Probabilistic decision diagram                                                      |

| CC      | Circuit clustering                                                                  |

| STA     | Static timing analysis                                                              |

|         |                                                                                     |

## LIST OF APPENDICES

| Appendix 1. Important MATLAB code | 73 | 3 |

|-----------------------------------|----|---|

|-----------------------------------|----|---|

## CHAPTER 1 INTRODUCTION

#### 1.1 Research Background

Downscaling of CMOS devices to nanometers raises quite a few new challenges for digital integrated circuit designers [1]. Among them is circuit reliability. With the imprecision of nanoscale fabrication, device reliability can be affected by many hard defects (such as shorts and opens [2-3]) and soft errors which may occur due to environmental variations. High integration density and unsaturated voltage/current are increasingly compounding the problem [4]. The unreliability of fundamental devices will then negatively affect circuit performance at high levels. Thus, it becomes necessary to keep track of not only signal probability, but also signal reliability (or faulty ratio). For large circuits, the difficulties in finding either signal probability or reliability stem from signal correlations due to numerous reconvergent fanouts within circuits. Since the reliability and probability may affect each other, it would make much sense to estimate both of them simultaneously in a circuit. More specifically, for given unreliable circuits, the output reliability depends on their input signal probabilities. Take a two-input AND gate for example. When both inputs have a lower signal probability (i.e., most of time they are logic '0'), the output signal would have a higher reliability (i.e., high probability of being a correct value of '0') due to the nature of AND logic. On the other hand, signal probability depends on reliability as well, as will become clear later in the thesis. Since signal reliability is essentially a conditional signal probability (refer to next section for details), evaluating signal reliability is generally more difficult than estimating signal probability.

These challenges, along with the high circuit density, bring up two main requirements for the probability and reliability evaluation method: high accuracy when dealing with correlation, and high efficiency (scalability) when applied to integrated circuits. Currently, there exist numerical and analytical solutions, which are mainly under the zero-delay model and assume gate reliability is a constant. The numerical method can provide high accuracy results statistically at a cost of extremely long processing time, which makes it a good way to provide benchmark results for probability and reliability evaluation. Analytical methods, different from numerical ones, tend to use some fast models to calculate/estimate signal probability and reliability. Although it is much more efficient and practical to be implemented on integrated circuits, the accuracy level is not satisfying. The major error source is coming from imperfect solutions to signal correlation estimation. Meanwhile, some works' scalability, such as [5], is not good enough with a time complexity of  $O(M^2)$ , where M is the number of gates.

#### **1.2 Objectives**

The goal of this thesis is to assist designers in evaluating digital integrated circuit performance accurately and efficiently so that effective adjustments can be applied immediately. More specifically, the performance evaluation includes estimations for signal probability, reliability, and device reliability variations after a certain operation time, which is called the aging effect. All these factors are directly related to critical issues such as size, power consumption, lifetime, etc. Ideally, designers are expecting this evaluation to be accurate and efficient.

However, it is unrealistic to search for an absolute accurate model with maximum efficiency for signal probability and reliability estimations. The best researchers can do is to find a reasonable balance between accuracy and efficiency. Any proposed model should be well-designed to handle signal correlations correctly, and the processing time should be preferably linear/quasi-linear proportional to number of logic gates. Otherwise, the efficiency of the proposed method will be a big concern when applied to integrated circuits.

Due to the lack of full circuit aging effect analysis, we are also trying to introduce a model to help designers evaluate circuit reliability changes with consideration of long-term intense operation. The model should be straightforward, easy to follow and implement to any digital circuit.

#### **1.3 Main Contributions**

Main contributions of this thesis are as follows:

• developing a new, hybrid approach for signal correlation evaluation, unlike others which are either pure numerical or analytical.

• introducing a categorization system for correlations based on circuit connectivity.

• achieving linear time complexity to circuit size by evaluating reliability in terms of conditional signal probabilities, which allows the use of gate propagation model

• achieving accurate evaluation for error-free probability (the probability that a signal is 'expected' to produce logic '1' with given inputs) and reliability simultaneously during analytical and numerical analysis, getting rid of extra time obtaining signal probability from other methods/tools/software.

• proposing a new convergence method (Two-step convergence) for sequential circuit analysis, reducing the number of iterations required by around 30%

• covering the shortage of circuit-level aging effect evaluation by extending existing device-level analysis.

• creating a new index to describe circuit overall reliability by considering the cross-impact of spatial and temporal reliability simultaneously.

The basic idea of the hybrid model is to categorize signal correlations by investigating a local circuit topology, and then apply specific solution methods accordingly (including analytic computation, bitstream simulation, or their combination). All category solutions, along with the conditional-probability-based gate propagation model, are well-designed to obtain signal error-free probability and reliability simultaneously. It should be noted that actual signal probability can be easily obtained using error-free probability and reliability, but not vice versa. With this strategy, the proposed model achieves not only linear time complexity to circuit size efficiency (benefits from the propagation-based model), but also further efficiency improvement by saving the processing time for signal error-free probabilities. Meanwhile, the simulation shows decent accuracy for the proposed model. When this model is applied to sequential circuits, instead of using traditional step-size convergence, we use the first few iterations as a trial, and obtain a farbetter initial value for the following iterations by regression analysis. For evaluations considering the aging effect, we propose a model to look at circuit reliability from a logic perspective (or spatial viewpoint) as well as a delay aspect (or temporal viewpoint), in order to build a single index to evaluate the overall reliability of circuit outputs. We also extend and combine some existing models to accomplish reliability analysis, starting from transistor level to gate level and finally to full circuit reliability estimation.

#### 1.4 Thesis Organization

The rest of the thesis is organized as follows. Chapter 2 reviews the existing methods on above mentioned topics and their pros and cons. Chapter 3 presents the hybrid model in detail. Chapter 4 illustrates how the proposed hybrid model could be applied onto sequential circuits, as well as introduces the newly developed convergence technique. Chapter 5 focuses on circuit-level aging effect analysis. Finally, chapter 6 concludes the thesis.

#### CHAPTER 2

#### LITERATURE REVIEW

Models for signal probability and reliability evaluation on combinational and sequential circuits are well discussed, but there is still space for improvement for better accuracy and/or efficiency. For aging effect evaluation, although there are numerous works on device (transistors, gates) reliability changes, little has been done on circuit-levels.

## 2.1 Evaluation of Signal Probability and Reliability Under Zerodelay Model

Gate and wire delay are important factors in circuit design and cannot be ignored in real circuit analysis. However, when obtaining output probability and reliability from a logical values perspective, researchers tend to assume that gate and wire delays are zeros. This zero-delay model allows direct investigation to circuit logical functionality without disturbance coming from temporal issues such as delay and glitches, and the reliability evaluated under zero-delay model is called spatial reliability, meaning that it is only related to circuit connectivity/structure without considering any temporal factors.

#### 2.1.1Evaluation for Combinational Circuits

Evaluation of signal reliability is mainly achieved by two methods: numerical method and analytical method. The numerical method, such as Monte-Carlo simulation [6] is to estimate circuit reliability by randomly generating input vectors (with logic values 0 or 1 only) and evaluating the outputs. This approach is straightforward and easy to implement, and its accuracy is generally proportional to the number of iterative simulations. The major drawback of this method is that it requires long processing times, making it almost impossible for large integrated circuits. Therefore, it usually serves as a tool to provide standard results for evaluating the accuracy of other methods.

Analytical methods, on the other hand, represent a class of approaches that use analytical models with gate reliability, which is inspired by Von Neumann's work [7]. This reliability, assigned to each gate independently, represents a probability that a given gate maintains output logic value correctly after any logic functions, or equivalently, the probability that bit flip (from 0 to 1 or 1 to 0) event will not happen. These analytical models using gate reliability are much more efficient than numerical methods at a cost of accuracy reduction since the correlations between signals are difficult to evaluate. Another challenge for analytical methods is how to increase the efficiency as much as possible for probability and reliability evaluation.

In 2008, S. Krishnaswamy et al. proposed a probabilistic transfer matrix model (PTM) [8]. This work brings up the idea that all logic gates can be assigned by a pair of transfer matrix ITM and PTM (ideal transfer matrix and probabilistic transfer matrix), encountering error-free and erroneous environment respectively. The entire propagation procedure from input to output is then transferred into matrices multiplications, which speed up the evaluation process significantly. However, since the matrix tensor product is required during computation, the memory capacity needed to store the intermediate results is extremely high. On the other hand, signal correlations are handled by storing all multi-output gates and all correlated signals are considered simultaneously (maximum 10 correlated signals) regarding joint probability. These greatly increases the time complexity of the algorithm, especially for circuits with complex connectivity. Besides, considering the high difficulty level of estimating joint probability accurately for multiple (more than 2) signals, algorithm accuracy can still be a secondary concern in general.

Another work [9] presented a model using Boolean difference calculus to calculate circuit output reliability. Although the time complexity to number of gates is linear, the computational process is based on an assumption that spatial correlation coefficients are already available/obtained from some other methods, which means this method itself is not capable for correlation evaluation. Thus, the

accuracy level is entirely based on the accuracy of the applied correlation coefficients.

To better evaluate signal correlations, a multiple-state strategy has been used by [10-12]. The main idea is to generate a set of 'copies' circuits and each of them represents a specific logic state (0 or 1) for the reconvergent-fanouts. This method is usually accurate enough since when reconvergent-fanouts are fixed to certain logic values, the other signals' probability and reliability can be easily calculated accurately. However, the major drawback of this idea is that when multiple reconvergent-fanouts exist, the number of input pattern considered will be increasing exponentially, making the evaluation process much less efficient.

In a following milestone work called "probabilistic gate matrix" (PGM) [13], the signal correlations are handled by investigating output reliability for specific reconvergent fanout input pattern j (with n inputs) and take weighted summation as follows:

$$R_{out} = \sum_{j=0}^{2^{n}-1} P_j R_{out_j}$$

(2.1)

where  $R_{out}$  is output reliability,  $P_j = P\{inputs = j\}$ , and  $R_{out_j}\{output = 1|inputs = j\}$ . This approach is pretty accurate but requires a certain amount of time to list all possible input patterns, resulting in a time complexity of  $O(M2^{M_f})$ , where M is the number of gates and  $M_f$  is the number of correlated signals. It should be noted that if we ignore the extra processing time for signal correlations, the fundamental propagation-based model achieves a linear time complexity regarding the number of gates, which is the best in expectation so far. Therefore, this framework is widely used in the following years.

Meanwhile, researchers tried to find solutions based on probabilistic decision diagrams (PDD) [14] as well. This is a good attempt to study circuit probability, reliability, and correlation topologically. Again, the main drawback of the proposed model is that the time complexity is not linear, but highly related to the number of reconvergent-fanouts. For example, from [14], the CPU time for the circuit 'duke2' with only 88 gates takes 14.76 seconds, and for the circuit '9symml' with 108 gates it becomes 0.22 seconds. The instability of efficiency greatly reduces the scalability of PDD. A similar problem has been observed in [15] as well.

Bayesian network [16] is another attempt using graphical method for probability and reliability evaluation. However, it is quite hard to address signal correlations using the Bayesian network, and the accuracy level becomes a concern. The efficiency and accuracy are both moderate, but the scalability of this work is still questionable since the processing time to build up corresponding networks can be unacceptably long for integrated circuits.

To make the evaluation method more scalable, [17] has bring up a model using correlation coefficient  $C_{AB}$  for signal pair (A, B) which is defined as:

$$C_{AB} = \frac{P(AB)}{P(A)P(B)}$$

(2.2)

where  $P(k) = \Pr\{k = 1\}, k = A, B, AB$ . This model requires only one-pass to the circuit, making it very fast. However, considering the fact that reliability correlation is different from probability correlation, this method becomes less accurate for circuit reliability evaluation. More recently, a similar idea has been used in equivalent reliability model (ER) [18]. With a different definition of the correlation coefficient, the accuracy level of estimation for signal reliability has been improved, but still not enough.

Another example of using correlation coefficients is the bitstream simulation model (CC-SPRA) [5]. Although the big framework is still a propagation-based analytical method, the evaluation of all correlation coefficients is achieved by 'bitstream simulation', which is a small-scale Monte-Carlo simulation instead. More specifically, for any given signal pair, bit value sequences are generated using available information. The correlation coefficient is then calculated using information obtained by 'counting' the bit values from generated sequences for signals of interest. With a good choice of the length of the bitstream, it provides accurate results without sacrificing too much efficiency. A major drawback of this work is that bitstream generation requires a circuit connectivity analysis from primary inputs. When a signal pair of interest is approaching outputs within integrated circuits, this investigation process will be time-consuming.

In 2011, circuit clustering (CC) [19] has been introduced as a speed-up technique. The main idea is to separate a circuit into multiple clusters following its topological order and calculate conditional signal probabilities based on given values of its previous cluster only. The output probability can then be obtained by multiplying these conditional probabilities all together. Since the maximum size of matrices used to describe conditional probabilities is smaller, the algorithm efficiency has been improved a lot. However, this model is too optimistic since any interconnect signal between clusters will increase the difficulty of finding the individual conditional probability. Therefore, it is only capable for circuits with simple connectivity and clear hierarchy.

#### 2.1.2 Evaluation for Sequential Circuits

Since most of the real-world circuits are sequential, there is much research work on this area. From a hardware and design perspective, for example, [20] has developed a low-power, non-volatile and radiation-hardened latch against single event upsets and [21] takes advantage of reconfigurable pulsed latches to achieve low-power design with reliability enhancement.

As for software simulation-based work, a soft-error detection and correction system has been introduced in [22], and [23] has investigated the critical path identification technique for sequential circuit reliability analysis. However, neither of their discussions mentioned how to improve the efficiency for sequential circuit probability and reliability directly.

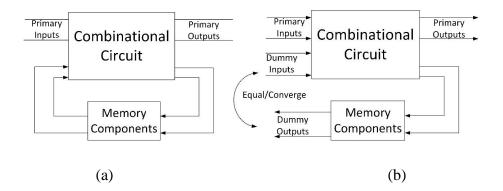

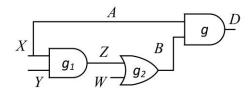

Figure 1. (a) Sequential circuit, (b) combinational equivalent of (a)

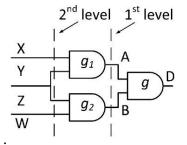

As discussed before, most of the introduced methods for combinational circuit evaluation can be expanded to sequential circuits. Generally, as shown in [24], a sequential circuit can be transferred into a combinational equivalent by unlooping the memory component as shown in Fig. 1.

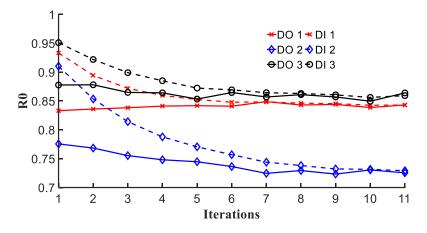

It should be noted that this combinational equivalent requires the probability and reliability of the dummy inputs (DIs) are exactly the same as those of the dummy outputs (DOs) since they are initially connected. However, since this information is not given initially, we have to assign certain probability and reliability to DIs first and let the DIs and DOs converge to each other. This brings up a higher efficiency requirement for efficiency of combinational evaluation models since they are applied continuously until circuits' stable status is found.

The current convergence process is mostly driven by the following equation:

$$Q_{DI}^{n+1} = Q_{DI}^n + \eta \cdot (Q_{DO}^n - Q_{DI}^n)$$

(2.3)

where Q represents either the probability or reliability element of DIs and DOs,  $\eta$  is the step size, and n is the number of iterations. The step size is the key to determining how fast this convergence process is. Larger  $\eta$  means a faster approach from DIs to DOs, while smaller  $\eta$  are usually used during the fine-tuning process. In the extreme case, if  $\eta = 1$ , the new DI value is directly substituted by

the current DO value. However, the optimal  $\eta$  is difficult to find, and for each circuit the best  $\eta$  can be different as well.

In [24-26],  $\eta = 0.1$  is applied for the entire convergence process without any change, which leads to extremely tedious convergences. In fact, there is no reason to keep  $\eta$  to such a small value for the first few iterations, where the probability and reliability of DIs and DOs are still far from each other. Such discussions on the choices of  $\eta$  have been done in [27], but no exact solution was given. The only conclusion is that  $\eta$  should be a dynamic value, starting with a relatively large one, such as 0.5, and gradually decreasing as DIs and DOs are getting closer.

The tricky part about choosing  $\eta$  is that it is sensitive to circuit structure as well as input probability and reliabilities. For any given circuit, the optimal value of  $\eta$  is unique, which is also extremely difficult to find. Therefore, it is understandable that current researchers tend to use a universal model for all sequential circuits at a cost of reduction of efficiency.

Another important parameter, which is ignored by researchers, is the initial value of  $Q_{DI}^1$ . A good initial value can significantly reduce the number of iterations required. In most work, DIs shares the same probability and reliability as primary inputs at the beginning of convergence. Although this setup is easy to follow, it is never the best choice. This thesis will discuss how to find a better initial value to speed up the entire convergence process as well.

## 2.2 Evaluation of Signal Probability and Reliability Considering Delay and Aging Effect

In real world circuits, gate delay will affect output probability and reliability, which cannot be ignored. For instance, there is a great chance for the sampled output data to be incorrect if the expected logic value arrives later than the designed guard band, even if the logic value is correct. In contrast to spatial reliability, temporal reliability is used to describe the probability that a signal arrives on time. Besides, gate reliability is usually not a constant either. In fact, after operating

intensively for years, transistor threshold voltages tend to increase (especially for PMOS). The reason is that accumulated opposite charges during operation will cancel the upcoming gate voltage and increase the threshold voltage if there is not enough 'rest' time to let the charges release, which is known as Negative Bias Temperature Instability (NBTI). Considering many other performance (such as power and area) requirements, circuits are usually designed to have their critical path delays around 10-30% shorter than the required clock period [28]. However, an accurate evaluation of the performance degradation caused by NBTI would be less likely since it strongly depends on dynamic operation conditions, such as supply voltage (VDD), environmental temperature (T), and signal probability (Pin) [29]. Even if a guard band is designed using extreme environmental parameters (such as high temperatures and high supply voltages), the uncertainty of signal probabilities makes it hard to accurately evaluate the aging effect.

Some prior work has successfully built up short-term and long-term estimation models for the change in threshold voltage  $\Delta V_{th}$  due to NBTI effect through experiments, as shown in [30, 31, 32]. Based on their results, [33] further simplified the proposed model assuming the environmental conditions (such as supply voltage and temperature) were fixed.

#### 2.2.1 Aging Effect on Spatial Reliability

The spatial reliability refers to the probability that a signal will produce the correct logic value, in contrast to the temporal reliability which is related to delay. With the information of  $\Delta V_{th}$ , researchers in [33] have proposed models for gate-level reliability aging analysis by looking into transistor performance. [33] shows that the designed transistor threshold voltages  $V_{th}$  can fluctuate due to oxide thickness variations [34], line edge roughness [35], polysilicon granularity, and the combined effects of all these factors. Simulations and some sample analysis [36-49] conclude that  $V_{th}$  fluctuations will lead to unexpected behavior (turning on/off at incorrect gate-to-source voltage), which can be treated as a Gaussian distribution. The probability of failure (PF) for transistors is then calculated by assuming that transistors are ideal switches at its actual threshold voltage. The logic gates, formed

by these transistors, are found to be experiencing a certain probability to fail to produce the correct logic function, which has been discussed in [40]. Therefore, the output logic value could be incorrect.

#### 2.2.2 Aging Effect on Temporal Reliability

The increased threshold voltage will make the transistors harder to be turned on and reduce drain current, leading to a longer gate propagation delay ([41, 42]). With the extra delay accumulated, there is a chance that the output signal may miss the sampling action of the current clock cycle and produce an incorrect sampling result for the output value, which is called temporal unreliability. Fortunately, it is possible to efficiently calculate gate delay variation using  $\Delta V_{th}$  with the linear approximation model for logic gates delay approximation developed in [43]. The output delay is found using static timing analysis (STA) [44, 45], which can be done easily using SPICE tools, as indicated in [46]. The temporal reliability of output can be obtained by comparing the obtained output delay with the designed CLK frequency requirement.

The above-mentioned work provides a clear picture of how aging effects can change single device performance with respect to spatial and temporal reliability. However, it is still a big challenge for designers to accurately determine the lifetime of designed circuits due to the lack of full circuit estimations for reliability aging issues while considering both types of reliability.

#### CHAPTER 3 PROBABILITY AND RELIABILITY ESTIMATION FOR

#### COMBINATIONAL CIRCUITS

In this chapter, we first describe some background of digital signal probability and reliability, and then introduce the joint probability vector (JPV) and joint conditional probability matrix (JCPM) for any given signal pair. With this information, we propose a hybrid model based on correlation categorization and show the corresponding solutions. The simulation results and summary are followed.

#### 3.1 Signal Probability and Joint Probability Vector

#### 3.1.1 Signal Probability

For any signal D in a digital circuit, its error-free probability is defined as follows:

$$\begin{cases} P_D^{0^*} = \Pr\{D^* = 0\} \\ P_D^{1^*} = \Pr\{D^* = 1\} \end{cases}$$

(3.1)

where D<sup>\*</sup> is the error-free version of D (throughout the thesis, the symbol '\*' is used to indicate 'error-free', which refers to the condition where all gates and input signals are reliable), and  $P_D^* = (P_D^{0^*} P_D^{1^*})$  is called the error-free probability vector (PV) of signal D with  $P_D^{0^*} + P_D^{1^*} = 1$ . In an unreliable circuit, the reliability of signal D, (denoted by  $r_D$ ) is defined as the probability that the signal generates an intended logic value, i.e.,  $r_D = Pr\{D = D^*\}$ . Similarly, for a logic gate g, its reliability (denoted by  $r_g$ ) is defined as the probability that an intended logic value at its output is produced for given inputs (either erroneous or error-free). It should be mentioned that the reliability for gate output may not necessarily be lower than its input signal reliabilities for given  $r_g$  due to logic masking. For instance, if one input of a reliable AND gate has a reliability of 1 but is fixed to logic 0, the output reliability will always be 1 no matter how low the reliability of the other input could be.

#### **3.1.2 Joint Probability Vector**

For any input pair (A, B) of a logic gate g, we define the joint (error-free) probability vector (JPV) and joint conditional probability matrix (JCPM) as follows:

$$JPV: \mathbf{P}_{AB}^{*} = \left(P_{AB}^{00^{*}} P_{AB}^{01^{*}} P_{AB}^{10^{*}} P_{AB}^{11^{*}}\right)$$

(3.2)

where  $P_{AB}^{ij^*} = \Pr\{(AB)^* = 'ij'\}, i, j = 0 \text{ or } 1$ ,  $\sum P_{AB}^{ij^*} = 1$ . If (A, B) are independent, we have  $P_{AB}^{ij^*} = P_A^{i^*} \cdot P_B^{j^*}$ . If (A, B) are correlated, this value is evaluated otherwise.

## 3.2 Signal Reliability and Joint Conditional Probability Matrix (JCPM)

#### 3.2.1 Signal Reliability

The reliability  $r_D$  for signal D can be expressed in terms of probabilities of error-free signal  $D^*$  and conditional probabilities of signal D as follows:

$$r_{D} = Pr\{D = D^{*}\}$$

$$= Pr\{D = 1 \cap D^{*} = 1\} + Pr\{D = 0 \cap D^{*} = 0\}$$

$$= Pr\{D = 1 \mid D^{*} = 1\} \cdot P_{D}^{1^{*}} + Pr\{D = 0 \mid D^{*} = 0\} \cdot P_{D}^{0^{*}}$$

$$= R_{D}^{1} \cdot P_{D}^{1^{*}} + R_{D}^{0} \cdot P_{D}^{0^{*}}$$

(3.3)

where  $R_D^1$  and  $R_D^0$  are conditional probabilities:

$$\begin{cases} R_D^1 = \Pr\{D = 1 \mid D^* = 1\} \\ R_D^0 = \Pr\{D = 0 \mid D^* = 0\} \end{cases}$$

(3.4)

Let  $\mathbf{R}_{D} = (R_{D}^{0} \ R_{D}^{1})$ , which is known as the reliability vector (RV) of signal D. In other words, the reliability of the signal D is associated with a pair of conditional probabilities  $(R_{D}^{0} \ R_{D}^{1})$ .

#### 3.2.2 Joint Conditional Probability Matrix

Similar to JPV definition, we have Joint Conditional Probability Matrix defined as follows:

$$JCPM: \mathbf{C}_{AB} = \begin{pmatrix} P_{00}^{00} & P_{00}^{01} & P_{00}^{10} & P_{00}^{11} \\ P_{01}^{00} & P_{01}^{01} & P_{01}^{10} & P_{01}^{11} \\ P_{10}^{00} & P_{10}^{01} & P_{10}^{10} & P_{10}^{11} \\ P_{11}^{00} & P_{11}^{01} & P_{11}^{10} & P_{11}^{11} \end{pmatrix}$$

(3.5)

where the element  $P_{ij}^{kl} = \Pr\{(AB) = 'kl' \mid (AB)^* = 'ij'\}$ , i, j, k, l = 0 or 1, and summation of the four elements in each row is 1 unless  $P_{AB}^{ij^*} = 0$  for a specific value of *i* and *j*, in which case  $P_{ij}^{kl}$  (k, l = 0, 1) in (3.5) is simply defined as 0. Once both  $P_{AB}^*$  and  $C_{AB}$  in the above (3.4) and (3.5) are available, the PV and RV for the output of gate *g* can be derived through a probability propagation to be presented in the next section.

| Node #  | RV under Independent | RV Considering      | Errors in      |

|---------|----------------------|---------------------|----------------|

|         | assumption           | signal correlations | percentage (%) |

| 1       | (0.9977, 0.9862)     | (0.9958, 0.9778)    | (0.19, 0.86)   |

| 2       | (0.9932, 0.9218)     | (0.9866, 0.9681)    | (0.67, 4.78)   |

| 3       | (0.9953, 0.9346)     | (0.9785, 0.9645)    | (1.72, 3.10)   |

| 4       | (0.9256, 0.9290)     | (0.9673, 0.9927)    | (4.31, 6.42)   |

| 5       | (0.9101, 0.9751)     | (0.9692, 0.9813)    | (6.10, 0.64)   |

| 6       | (0.9032, 0.9574)     | (0.9700, 0.9832)    | (6.89, 2.63)   |

| 7       | (0.8719, 0.9870)     | (0.9684, 0.9786)    | (9.97, 0.86)   |

| Average | -                    | -                   | (4.26, 2.75)   |

Table I. Conditional Reliabilities for Circuit C432 with  $r_g = 0.999$

For small circuits, both PVs and RVs for all signals can be found using MC simulation. However, for large circuits with signal correlations, it would be impractical to do so by MC simulation which would be too time-consuming. Generally speaking, the PV and RV for any signal depends on input signal probabilities, signal correlations and/or gate reliabilities. Intuitively, if a circuit contains no signal correlations, the conditional reliability pair ( $R_D^0 R_D^1$ ) can be easily propagated through gates from circuit inputs to its outputs. Unfortunately, most circuits have quite a few reconvergent fanouts which lead to signal correlations. To get a sense of what could happen if we ignore these correlations, we did MC simulations for benchmark circuit C432 with 160 gates under the assumption that all signals are independent with gate reliability of 0.999, and that all primary inputs are reliable with their signal probability of 0.5. The results are summarized in Table I, where the errors in evaluating the RV go up to 10%. This indicates that the signal correlations play an important role in circuit reliability evaluation.

#### 3.3 Gate Level Probability and Reliability Propagation

In this section, we first show how to obtain the (error-free) probability vector (PV) and reliability vector (RV) for the output D of an unreliable logic gate assuming the availability of  $P_{AB}^*$  and  $C_{AB}$ , where A and B are the two inputs of the gate. We then present detailed analysis (either analytic or statistic simulation) by considering various correlations with the signal pair (A, B) to find both  $P_{AB}^*$  and  $C_{AB}$ . It should be mentioned that the above obtained PV and RV for the signal D will be required and used to find both JPV and JCPM for other signal pairs (if they are the signal D's transitive fanouts). Thus, the whole computation is a recursive gate-by-gate propagation process, as will become clear later in the thesis. Finally, the pseudo-codes of the overall algorithm are provided with some discussions.

Assume both  $P_{AB}^*$  and  $C_{AB}$  are available and that the logic gate under consideration is an AND gate with reliability of  $r_g$ . To obtain the PV of its output D (i.e.,  $P_D^*$ ), we partition the  $P_{AB}^*$  as follows:

$$\boldsymbol{P}_{\boldsymbol{A}\boldsymbol{B}}^{*} = \left(P_{AB}^{00^{*}} P_{AB}^{01^{*}} P_{AB}^{10^{*}} \vdots P_{AB}^{11^{*}}\right) = (\boldsymbol{P}\boldsymbol{0} \ \vdots \ \boldsymbol{P}\boldsymbol{1})$$

(3.6)

where  $P0 = (P_{AB}^{00^*} P_{AB}^{01^*} P_{AB}^{10^*})$  and  $P1 = (P_{AB}^{11^*})$ . Under zero-delay model, the  $P_D^{0^*}$  and  $P_D^{1^*}$  are the sum of all elements in P0 and P1, respectively, i.e.,

$$\begin{cases} \boldsymbol{P}_{\boldsymbol{D}}^{\mathbf{0}^{*}} = SUM(\boldsymbol{P}\mathbf{0}) \\ \boldsymbol{P}_{\boldsymbol{D}}^{\mathbf{1}^{*}} = SUM(\boldsymbol{P}\mathbf{1}) \end{cases}$$

(3.7)

The  $C_{AB}$  is partitioned accordingly as follows:

$$\boldsymbol{C}_{AB} = \begin{pmatrix} P_{00}^{00} & P_{00}^{01} & P_{00}^{10} & | & P_{00}^{11} \\ P_{01}^{00} & P_{01}^{01} & P_{01}^{10} & | & P_{01}^{11} \\ P_{10}^{00} & P_{10}^{01} & P_{10}^{10} & | & P_{10}^{11} \\ - & - & - & + & - \\ P_{11}^{00} & P_{11}^{01} & P_{11}^{10} & | & P_{11}^{11} \end{pmatrix} = \begin{pmatrix} \boldsymbol{CP1} & \boldsymbol{CP2} \\ \boldsymbol{CP3} & \boldsymbol{CP4} \end{pmatrix}$$

(3.8)

If  $r_g = 1$ , the RV for the output D is expressed as  $\mathbf{R'_D} = (R_D^{0'} R_D^{1'})$ , where:

$$\begin{cases} R_D^{0'} = SUM(\mathbf{P0} * \mathbf{CP1}) / P_D^{0^*} \\ R_D^{1'} = SUM(\mathbf{P1} * \mathbf{CP4}) / P_D^{1^*} \end{cases}$$

(3.9)

When  $r_g < 1$  in general, consider the following two cases which would lead to a reliable output D: (a) both D' (i.e., D when  $r_g = 1$ ) and the gate are reliable, and (b) both D' and the gate are unreliable, which also produces a correct (reliable) value of D. The probability of case (a) is given by  $r_g \cdot R_D'$ , while the probability of case (b) is given by  $(1 - r_g) \cdot (1 - R_D')$ . The summation of these two probabilities gives the output reliability, i.e.,  $R_D = r_g \cdot R_D' + (1 - r_g) \cdot (1 - R_D') = (2r_g - 1) \cdot R_D' + (1 - r_g)$ . Applying this result to both  $R_D^0$  and  $R_D^1$  gives the RV for D in a vector form as follows:

$$\boldsymbol{R}_{\boldsymbol{D}} = (2r_g - 1) \cdot \boldsymbol{R}_{\boldsymbol{D}}' + \boldsymbol{I}_{\boldsymbol{g}}$$

(3.10)

where

$$I_g = (1 - r_g \quad 1 - r_g) \tag{3.11}$$

For any 2-input gates other than AND logic, similar derivations can be done to find the PV and RV of its output for given  $P_{AB}^*$  and  $C_{AB}$ , except that (3.6) through

(3.8) shall be partitioned in different ways accordingly. The question to ask now is how to find both JPV and JCPM (i.e.,  $P_{AB}^*$  and  $C_{AB}$ ) as defined in (3.4) and (3.5), which will be answered in the following section III.B.

#### 3.4 Correlation Categorization and JCPM Estimation

For any signal pair of (A, B), finding its JPV and JCPM requires considerations of the correlations between A and B, which depends on the connectivity of themselves and/or their transitive fan-ins and deserves detailed analysis. In what follows, we first define three different categories, i.e., categories 'S', 'N' and 'I', to represent 'strong', 'not-strong' and 'independent' correlations, respectively, before calculating or estimating both JPV and JCPM.

#### 3.4.1 Category 'S'

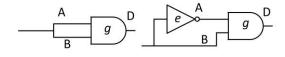

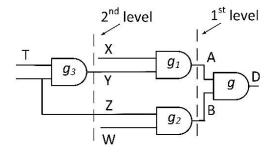

There are three sub-categories in this strong-correlation category 'S'. They are named as 'S1', 'S2', and 'S3', as shown in Fig. 2. 'S1' refers to a situation where A and B are the same signal (Note that 'S1' rarely happens for any two-input gate as it would be degenerated to an inverter or buffer. However, we still define it for completeness of correlation categorization).

'S2' represents the case where one of A and B is an immediate fan-in of the other. If A and B are driven by two different gates which share same inputs, then it is defined as 'S3'. Throughout the thesis, gates (such as g,  $g_1$  and  $g_2$ ) in all figures represent any type of 2-input logic gate unless otherwise stated. Also, inverter or buffer would be ignored because they have no effect on correlation category. Therefore, both cases shown in Fig.2 (a) are considered as 'S1'. The characteristic of the category 'S' is that the correlation between A and B is so strong that their JPV and JCPM can be calculated directly, as discussed below. It should be noted that only JCPMs of input pairs in previous levels of gates are treated as 'available', which are obtained before the propagation reaches the current gate.

(a) *SI* '

(b) '*S2* '

(c) '*S3* '

Figure 2. Examples of correlation category 'S'.

For category '*S1*' in the left of Fig. 2 (a) where A and B are a same signal, the JPV and JCPM for (A, B) are given by:

$$\boldsymbol{P}_{\boldsymbol{A}\boldsymbol{B}}^{*} = \begin{pmatrix} P_{A}^{0^{*}} & 0 & 0 & P_{A}^{1^{*}} \end{pmatrix}$$

(3.12)

$$\boldsymbol{C}_{AB} = \begin{pmatrix} R_A^0 & 0 & 0 & 1 - R_A^0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 1 - R_A^1 & 0 & 0 & R_A^1 \end{pmatrix}$$

(3.13)

For category 'S2' of Fig. 2 (b), the JPV of (A, B) is given by:

$$\boldsymbol{P}_{\boldsymbol{A}\boldsymbol{B}}^* = \boldsymbol{P}_{\boldsymbol{X}\boldsymbol{Y}}^* \cdot \boldsymbol{M}_{\boldsymbol{S}_2}^* \tag{3.14}$$

where  $P_{XY}^*$  is the JPV of (X, Y), which is assumed to be available, and  $M_{S_2}^*$  is a gate-dependent probability propagation matrix for gate  $g_1$ . For instance, if  $g_1$  is an AND gate, the corresponding  $M_{S_2}^*$  is given by:

$$\boldsymbol{M}_{\boldsymbol{S}_{2}}^{*} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

(3.15)

The JCPM of (A, B) in Fig. 2(b) can also be calculated by using the JPV and JCPM of (X, Y) as well as the information about gate  $g_1$ . To make the calculation easier, this can be done by initially assuming the  $g_1$ 's reliability of  $r_g = 1$  and then extending it to the general case with any value of  $r_g$ . First, with  $r_g = 1$ , one can find the JCPM of (A, B), denoted as  $C_{AB}'$ , depending on the gate type of  $g_1$ . For instance, if  $g_1$  is an AND gate,  $C_{AB}'$  is expressed as:

$$\boldsymbol{C}_{\boldsymbol{A}\boldsymbol{B}}' = \begin{pmatrix} P_{00}^{00} & 0 & P_{00}^{10} & P_{00}^{11} \\ 0 & 0 & 0 & 0 \\ P_{10}^{00} & 0 & P_{10}^{10} & P_{10}^{11} \\ P_{11}^{00} & 0 & P_{11}^{10} & P_{11}^{11} \end{pmatrix}_{\boldsymbol{A}\boldsymbol{B}}$$

(3.16)

where all elements can be calculated from both JPV and JCPM of (X, Y). For example,

$$\begin{cases} (P_{00}^{00})_{AB} = \frac{P_{XY}^{00^*}[(P_{00}^{00})_{XY} + (P_{00}^{01})_{XY}] + P_{XY}^{01^*}[(P_{01}^{00})_{XY} + (P_{01}^{01})_{XY}]}{P_{XY}^{00^*} + P_{XY}^{01^*}} \\ (P_{00}^{10})_{AB} = \frac{P_{XY}^{00^*} \cdot (P_{00}^{10})_{XY} + P_{XY}^{01^*} \cdot (P_{01}^{10})_{XY}}{P_{XY}^{00^*} + P_{XY}^{01^*}} \\ (P_{00}^{11})_{AB} = \frac{P_{XY}^{00^*} \cdot (P_{00}^{10})_{XY} + P_{XY}^{01^*} \cdot (P_{01}^{11})_{XY}}{P_{XY}^{00^*} + P_{XY}^{01^*}} \end{cases}$$

(3.17)

The other elements can be found similarly. For simplicity, (3.16) is rewritten in matrix as:

$$\boldsymbol{C}_{\boldsymbol{A}\boldsymbol{B}}' = (\boldsymbol{M}_{\boldsymbol{S}_2}^*)^T \cdot \boldsymbol{T}_{\boldsymbol{S}_2} \cdot \boldsymbol{C}_{\boldsymbol{X}\boldsymbol{Y}} \cdot \boldsymbol{M}_{\boldsymbol{S}_2}^*$$

(3.18)

where  $(\boldsymbol{M}_{S_2}^*)^T$  represents the transpose of  $\boldsymbol{M}_{S_2}^*$ ,  $\boldsymbol{T}_{S_2}$  is a transition matrix for category 'S2', depending on the gate type of  $g_1$ . For instance, if  $g_1$  is an AND gate, the  $\boldsymbol{T}_{S_2}$  is given by

$$\boldsymbol{T}_{S_2} = diag\left(\frac{P_{XY}^{00^*}}{P_{XY}^{00^*} + P_{XY}^{01^*}}, \frac{P_{XY}^{01^*}}{P_{XY}^{00^*} + P_{XY}^{01^*}}, 1, 1\right)$$

(3.19)

Secondly, for a general case with unreliable g1 (i.e.,  $r_g < 1$ ), the JCPM of (A, B) is modified to

$$\boldsymbol{C}_{\boldsymbol{A}\boldsymbol{B}} = \boldsymbol{C}_{\boldsymbol{A}\boldsymbol{B}}' \cdot \boldsymbol{M}_{\boldsymbol{g}_1}^{\boldsymbol{B}} \tag{3.20}$$

where  $C_{AB}$  is given by (3.18), and  $M_{g_1}^B$  represents the modification due to the unreliable  $g_1$  and is given by

$$\boldsymbol{M}_{g_{1}}^{B} = \begin{pmatrix} r_{g} & 1 - r_{g} & 0 & 0\\ 1 - r_{g} & r_{g} & 0 & 0\\ 0 & 0 & r_{g} & 1 - r_{g}\\ 0 & 0 & 1 - r_{g} & r_{g} \end{pmatrix}$$

(3.21)

For category 'S3' of Fig. 2 (c), the computation procedure for the JPV and JCPM is similar to the above category 'S2' except that an extra gate  $g_2$  shall be considered. More specifically, the JPV of (A, B) in this case is given by:

$$P_{AB}^{*} = P_{XY}^{*} \cdot M_{S_{3}}^{*}$$

(3.22)

where  $M_{S_3}^*$  is the joint propagation matrix defined by both  $g_1$  and  $g_2$ . In Fig. 2 (c), if the gates  $g_1$  and  $g_2$  are AND and OR logic, respectively, the corresponding  $M_{S_3}^*$  is given by:

$$\boldsymbol{M}_{\boldsymbol{S}_{3}}^{*} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

(3.23)

Similar to the derivation of (3.18) and (3.20), we define a transition matrix for category 'S3' as  $T_{S_3}$ , and express the JCPM of (A, B) for category 'S3' of Fig. 2 (c) as:

$$\boldsymbol{C}_{AB} = \left[ \left( \boldsymbol{M}_{S_3}^* \right)^T \cdot \boldsymbol{T}_{S_3} \cdot \boldsymbol{C}_{XY} \cdot \boldsymbol{M}_{S_3}^* \right] \cdot \boldsymbol{M}_{g_1}^A \cdot \boldsymbol{M}_{g_2}^B$$

(3.24)

where  $M_{g_2}^B$  takes the form of (3.21) while  $M_{g_1}^A$  is given by

$$\boldsymbol{M}_{g_{1}}^{A} = \begin{pmatrix} r_{g} & 0 & r_{g} & 0\\ 0 & 1 - r_{g} & 0 & 1 - r_{g}\\ 1 - r_{g} & 0 & 1 - r_{g} & 0\\ 0 & r_{g} & 0 & r_{g} \end{pmatrix}$$

(3.25)

#### 3.4.2 Category 'N'

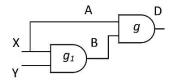

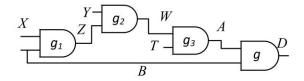

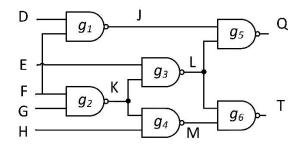

Category 'N' refers to the 'not-strong' or relatively weak correlation cases for the pair (A, B), including 3 sub-categories, i.e., 'N1', 'N2' and 'N3', as shown in Fig. 3 where all gates are again generic. More specifically, N1 and N2 shown in Fig. 3 (a) and (b), respectively, represent two specific correlations where A or B is the reconvergent fanout with more than one gates involved in the reconvergent path, which weaken the strength of correlation and make it more difficult to find the JPV and JCPM of signal pair (A, B). A more general case for 'not-strong' correlations is the category 'N3', as shown in Fig. 3 (c) where the dotted lines stand for some possible correlations/connections. It should be noticed that the above category 'S3' of Fig. 3 (c) is an exception of 'N3' where X=W and Y=Z, which is considered as a strong correlation.

Unlike category 'S', accurate evaluation of both JPV and JCPM for (A, B) under category 'N' is generally difficult. For example, to find the JPV of (A, B) in 'N1', the three-signal joint probability of (X, Z, W) is required, which is unknown (only JCPMs for input pairs are available). To address this issue, a bitstream simulation technique, which is a statistical method proposed by [12], can be used instead (see Section III-C for details).

#### 3.4.3 Category 'I'

Category 'I' generally represents any topological structures other than the above categories 'S' and 'N' (primary inputs are assumed to be independent). In particular, if a reconvergent fanout does not exist or is too far away from the signal pair (A, B), the correlation can be treated as the category 'I', which refers to "independent". This is because of the fact that when the reconvergent fanout stays

further away from A or B, their correlation is getting weaker. One could do bitstream simulation [12] to evaluate both JPV and JCPM for (A, B), but it would be very time-consuming. Our simulations showed that when the reconvergent fanout is more than 4 levels away, the correlation strength would be negligibly weak and can thus be treated as an independent case with negligible errors (refer to Section IV for detailed results). For this category 'I', the JPV (or JCPM) for (A, B) can be obtained easily and efficiently without simulations, and is given approximately by simply taking the product of individual signal probabilities (or reliabilities) for both A and B as:

$$\boldsymbol{P}_{\boldsymbol{A}\boldsymbol{B}}^{*} = \begin{pmatrix} P_{A}^{0^{*}} \cdot P_{B}^{0^{*}} & P_{A}^{0^{*}} \cdot P_{B}^{1^{*}} & P_{A}^{1^{*}} \cdot P_{B}^{0^{*}} & P_{A}^{1^{*}} \cdot P_{B}^{1^{*}} \end{pmatrix}$$

(3.26)

$$C_{mn} = R_A^{mn} \cdot R_B^{mn} \tag{3.27}$$

where  $C_{mn}$  is the element in the *m*-th row and *n*-th column of  $C_{AB}$ , and  $R_A^{mn}$  and  $R_B^{mn}$  are given by:

$$R_{A}^{mn} = \begin{cases} R_{A}^{0}, & \text{if } m, n = 1 \text{ or } 2\\ 1 - R_{A}^{0}, & \text{if } m = 1 \text{ or } 2 \text{ and } n = 3 \text{ or } 4\\ 1 - R_{A}^{1}, & \text{if } m = 3 \text{ or } 4 \text{ and } n = 1 \text{ or } 2\\ R_{A}^{1}, & \text{if } m, n = 3 \text{ or } 4 \end{cases}$$

(3.28)

$$R_B^{mn} = \begin{cases} R_B^0, & \text{if } m, n = 1, 3\\ 1 - R_B^0, & \text{if } m = 1 \text{ or } 3 \text{ and } n = 2 \text{ or } 4\\ 1 - R_B^1, & \text{if } m = 2 \text{ or } 4 \text{ and } n = 1 \text{ or } 3\\ R_B^1, & \text{if } m, n = 2 \text{ or } 4 \end{cases}$$

(3.29)

#### 3.4.4 Multi-level Category

In terms of correlation strength, all above categories can be listed in a descending order from the strongest to the weakest as: 'S1', 'S2', 'S3', 'N1', 'N2',

(a) '*N1* '

(b) '*N2* '

(c) '*N3* '

Figure 3. Examples of correlation category 'N'.

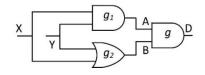

'N3', and 'I'. In all these categories with exception of 'N3', a reconvergent fanout, which significantly contributes to the correlation of (A, B), is known (or no such a reconvergent fanout exists when it is the category 'I'). For category 'N3', further investigation is required to find possible correlations among signals X, Y, Z and W (refer to Fig. 3 (c)) by locating any potential reconvergent fanouts. Considering the fact that the correlation between X and Y (or between Z and W) does not directly lead to the correlation between A and B, we are interested only in looking at possible correlations within the four cross-gate signal pairs (CGSPs), i.e., (X, Z),

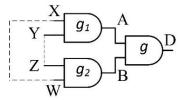

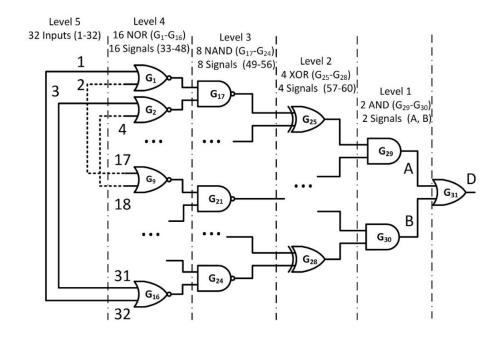

(X, W), (Y, Z) and (Y, W). Like (A, B), each of these pairs has their own category, but is one gate away from (A, B). In order to differentiate these CGSPs from (A, B), we define the correlation for (A, B) as the 1<sup>st</sup>-level correlation, and those for CGSPs as the 2<sup>nd</sup>-level correlation. The strongest correlation category among these four CGSPs defines the 2<sup>nd</sup>-level category. For example, in Fig. 4 (a) where (Y, Z) is category '*S1*' which is the strongest among all CGSPs, the correlation of (A, B) has the 1<sup>st</sup>-level category of '*N3*' followed by the 2<sup>nd</sup>-level category of '*S1*'.

Therefore, the correlation of (A, B) belongs to 2-level category, expressed as 'N3-

(a) *'N3-S1'*

(b) '*N3-S2*'

Figure 4. Examples of 2-level correlation category.

S1'. Fig. 4 (b) shows another example with a 2-level category of 'N3-S2'.

Following the above definition, we further proceed to the 3<sup>rd</sup>-level if the 2<sup>nd</sup>-level category is '*N*3' again, in order to check if any reconvergent fanout stem can be found in the 3<sup>rd</sup>-level. It is noted that only CGSP pairs with category '*N*3' in the 2<sup>nd</sup>-level proceed to the 3<sup>rd</sup> level. The maximum number of CGSPs at the 3<sup>rd</sup>-level is  $4\times4 = 16$ . If the 3<sup>rd</sup>-level category is still '*N*3', then we move to the 4<sup>th</sup> level to check, and so on. The maximum number of CGSPs on level *K* would be up to  $4^{K-1}$ . However, considering that the correlations due to reconvergent fanouts at the 5<sup>th</sup> or higher level is increasingly weak, we go only up to 4 levels for computational efficiency. In case the 4<sup>th</sup>-level category is '*N*' which represents any category of '*N*1', '*N*2' or '*N*3', the correlation of (A, B) is approximately treated as category '*I*' instead of a 4-level category is '*I*', it would be simply equivalent to single-level category '*I*'.

## 3.5 Bitstream Simulation for JPV and JCPM Estimation

As discussed before, there are no analytical methods available to compute the probability and reliability for category 'N'. We resort to a local bitstream simulation technique instead to estimate the JPV and JCPM of (A, B). We will start with a single-level category 'N1' and 'N2', then extend our discussions to a general multi-level category.

#### 3.5.1 Bitstream Simulation for Single-level Category

Prior to simulation, all the JPV and JCPMs for transitive fan-ins of (A, B), along with signal probabilities and reliabilities, are assumed to be available. We take single-level category 'N1' for example to show how the bitstreams are generated. Similar procedure also applies to single-level category 'N2' with considerations of just one more gate on the reconvergent path.

For category '*N1*' (refer to Fig. 2 (a)), we first generate an error-free bitstream sequence for the reconvergent fanout X (or A), denoted as  $Seq_X^*$  (with length of *L*), using the error-free probability vector  $P_X^*$ , and then generate the corresponding error-free bitstream sequence for Y, denoted as  $Seq_Y^*$ , based on  $Seq_X^*$  and  $P_{XY}^* = (P_{XY}^{00^*} P_{XY}^{01^*} P_{XY}^{10^*} P_{XY}^{11^*})$ . More specifically, if X = '0' is first generated, then the bit-value of Y is generated using the following conditional probability vector:

$$Pr\{\boldsymbol{Y}|\boldsymbol{X}=0\} = \left(\frac{P_{XY}^{00^*}}{P_{XY}^{00^*} + P_{XY}^{01^*}} \quad \frac{P_{XY}^{01^*}}{P_{XY}^{00^*} + P_{XY}^{01^*}}\right)$$

(3.30)

If X = '1' otherwise, we use the following conditional probability vector instead to generate the bit-value for Y:

$$Pr\{\mathbf{Y} \mid X = 1\} = \begin{pmatrix} \frac{P_{XY}^{10^*}}{P_{XY}^{10^*} + P_{XY}^{11^*}} & \frac{P_{XY}^{11^*}}{P_{XY}^{10^*} + P_{XY}^{11^*}} \end{pmatrix}$$

(3.31)

With the above  $Seq_X^*$  and  $Seq_Y^*$ , we then generate the (erroneous) bit-value sequence for 'XY' using the JCPM of (X, Y):

$$\boldsymbol{C}_{\boldsymbol{X}\boldsymbol{Y}} = \begin{pmatrix} P_{00}^{00} & P_{00}^{01} & P_{00}^{10} & P_{00}^{11} \\ P_{01}^{00} & P_{01}^{01} & P_{01}^{10} & P_{01}^{11} \\ P_{10}^{00} & P_{10}^{01} & P_{10}^{10} & P_{10}^{11} \\ P_{11}^{00} & P_{11}^{01} & P_{11}^{10} & P_{11}^{11} \end{pmatrix}_{\boldsymbol{X}\boldsymbol{Y}}$$

(3.32)

For instance, if  $(XY)^* = 00$  at a certain bit of  $Seq_X^*$  and  $Seq_Y^*$ , then 'XY' is generated using the joint conditional probability from the first row of  $C_{XY}$ , i.e.,

$$Pr\{XY \mid (XY)^* = 00\} = (P_{00}^{00} \ P_{00}^{01} \ P_{00}^{10} \ P_{00}^{11})_{XY}$$

(3.33)

For any other values of (XY)\*, simply take the corresponding row from  $C_{XY}$ . This process is repeated *L* times to obtain two bitstream sequences for (erroneous) X and Y, denoted as  $Seq_X$  and  $Seq_Y$ , respectively. Once  $Seq_X^*$ ,  $Seq_Y^*$ ,  $Seq_X$  and  $Seq_Y$ are available, the bitstream sequence for the signal Z (denoted as  $Seq_Z^*$  and  $Seq_Z$ ) can be obtained accordingly by propagating (X, Y) through  $g_I$  to its output Z:  $Seq_Z^*$ is generated by applying the logic operation on  $Seq_X^*$  and  $Seq_Y^*$ , while  $Seq_Z$  is generated by applying the logic operation on  $Seq_X^*$  and  $Seq_Y^*$ . It should be noted that  $g_I$  is assumed to be reliable when producing  $Seq_Z^*$ , while its gate reliability of  $r_g$  is taken into considerations for producing  $Seq_Z$ .

To further generate the bitstream sequence of B in Fig. 2 (a), we need to use the JPV and JCPM of (Z, W). First,  $Seq_W^*$  can be easily obtained by following the similar procedure of generating the above  $Seq_Y^*$ . The  $Seq_W$  can be generated by taking two elements from  $C_{ZW}$ , depending on the specific bit-values in  $Seq_W^*$ ,  $Seq_Z^*$  and  $Seq_Z$  and  $C_{ZW}$ . The bit-values in  $Seq_W^*$  and  $Seq_Z^*$  define the row of the two elements, while the bit-value in  $Seq_Z$  define their column. For instance, if  $(ZW)^* = 00$  and Z = 0, the conditional probability vector of W is given by:

$$Pr\{\boldsymbol{W} \mid (ZW)^* = 00 \ \cap \ Z = 0\} = (P_{00}^{00} \ P_{00}^{01})_{ZW}$$

(3.34)

where  $P_{00}^{00}$  and  $P_{00}^{01}$  are the two elements in the 1<sup>st</sup> row and 1<sup>st</sup> two columns of  $C_{ZW}$ . Thus, the bit-value of W is generated by using the probability vector of  $\left(\frac{P_{00}^{00}}{P_{00}^{00} + P_{00}^{01}} - \frac{P_{00}^{01}}{P_{00}^{00} + P_{00}^{01}}\right)$ . Once  $Seq_Z^*$ ,  $Seq_W^*$ ,  $Seq_Z$  and  $Seq_W$  are available, the bitstream sequence for the signal B (denoted as  $Seq_B^*$  and  $Seq_B$ ) can be finally obtained by propagating the bitstream sequences of both Z and W through  $g_2$  to its output.