## **Aalborg Universitet**

## A Fully Coupled Model of Multi-Chip Press-Pack IGBT for Thermo-Mechanical Stress Distribution Prediction

Zhan, Cao; Zhu, Lingyu; Zhang, Yaxin; Dai, Jiangang; Hou, Ting; Song, Ying; Ji, Shengchang; lannuzzo, Francesco

Published in:

IEEE Transactions on Industry Applications

DOI (link to publication from Publisher): 10.1109/TIA.2022.3160412

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhan, C., Zhu, L., Zhang, Y., Dai, J., Hou, T., Song, Y., Ji, S., & lannuzzo, F. (2022). A Fully Coupled Model of Multi-Chip Press-Pack IGBT for Thermo-Mechanical Stress Distribution Prediction. *IEEE Transactions on* Industry Applications, 58(3), 3852-3862. [9737398]. https://doi.org/10.1109/TIA.2022.3160412

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# A Fully Coupled Model of Multi-Chip Press-Pack IGBT for Thermo-Mechanical Stress Distribution Prediction

Cao Zhan, *Student Member IEEE*, Lingyu Zhu, *Member IEEE*, Yaxin Zhang, Jiangang Dai, Ting Hou, Ying Song and Shengchang Ji, *Member IEEE*, Francesco Iannuzzo, *Senior Member IEEE*

Abstract—In this paper, a fully coupled multi-physical model of multi-chip press-pack IGBT (PPI) considering surface roughness is proposed. This model realizes the coupling of the electrical-, thermal- and mechanical domains through contact resistance. The simultaneous prediction of temperature and stress under various surface roughness is achieved. Firstly, the fully coupled model and the contact resistance model are established. Secondly, both thermo-mechanical stress under the clamping phase and heating phase are analyzed. The influence of the surface roughness on the thermo-mechanical stress distribution is also investigated based on the proposed model. Results show that the surface roughness does not affect the thermo-mechanical stress distribution under the heating phase, while the amplitudes increase with surface roughness. Thirdly, the correctness of the model is verified by the temperature measurement and deterioration observation results. The observed fretting scratches on the additional metallization area after the power cycling test validates the correctness of the deformation prediction. Finally, the strain-life fatigue model of PPI is established, it turns out that the surface roughness has an impact on the fatigue life of the chip metallization area.

Index Terms—Multi-chips PPI, multi-physical model, surface roughness, thermo-mechanical stress, fatigue life

#### I. INTRODUCTION

MODULAR multilevel converter (MMC) is one of the most important equipment in MMC-based high voltage direct current (HVDC) [1-3] applications. Very often, MMC submodules consist of insulated gate bipolar transistors (IGBTs) and capacitors [4-5]. Compared with bonding-wire IGBTs, press-pack IGBTs (PPIs) are widely used in MMC-HVDC transmission systems due to their merits of high voltage endurance, high power density, and short-circuit failure mode [6-7]. However, PPI suffers fatigue thermo-mechanical stress during its long-term operation in MMC [8]. Thermo-

Manuscript received June 11, 2021. Paper EC-1031, presented at the 2020 IEEE Energy Conversion Congress and Exposition, Detroit, Michigan, October 11-15, approved for submission in the IEEE Transaction on Industrial Applications by the Industrial Power Converter Committee of the IEEE Industrial Applications Society. This work was supported in part by the State Key Laboratory of HVDC Transmission Technology: SKLHVDC-2019-KF-05. (Corresponding author: Lingyu Zhu)

Cao Zhan, Lingyu Zhu, Yaxin Zhang, Jiangang Dai and Shengchang Ji are all with the State Key Laboratory of Electrical Insulation and Power Equipment, Xi'an Jiaotong University, Xi'an, 710049, China. (e-mail:

mechanical stress and fatigue analysis are very important for the reliability improvement of PPI.

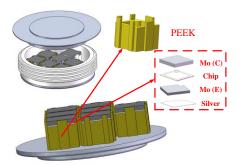

PPI consists of several parallel submodules that share the same collector and emitter plates to achieve a large current capacity. The packaging structure is shown in Fig. 1. Each submodule has the same multi-layered structure, which has two molybdenum plates, a silicon chip, and a soft silver layer. The silicon chip is clamped between two molybdenum plates. In addition, a poly-ether-ether-ketone (PEEK) framework is utilized as the insulating structure.

Fig. 1. The Packaging structure of PPI.

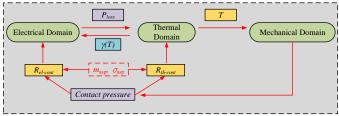

The electrical domain, thermal domain, and mechanical domain inside the PPI are coupled with each other inside PPI [9]. Temperature (T) and contact resistance ( $R_{\rm el-cont}$  and  $R_{\rm th-cont}$ ) are the most important coupling parameters of the model. The conductivity ( $\gamma(T)$ ) of the chip and load current are the key parameters that affect the power losses profile, and link the electrical- and thermal domains. The thermal model has to take into account many factors, such as power distribution, uneven thermal conductivity, and heat dissipation. Mechanical pressure distribution is mainly influenced by the original clamping force and dynamic thermal stress. Moreover, contact resistance influenced by surface roughness and contact pressure affects

zhancao@stu.xjtu.edu.cn, zhuly1026@xjtu.edu.cn, yaxinz@stu.xjtu.edu.cn dai844239399@stu.xjtu.edu.cn, jsc@xjtu.edu.cn).

Ting Hou is with the State Key Laboratory of HVDC Transmission Technology, China Southern Power Grid, Electric Power Research Institute, Guangzhou, 510080, China (e-mail: houting@csg.cn).

Ying Song is with the College of Water Resources and Architectural Engineering, Northwest A&F University, Yangling, 712100, China (e-mail: ysong0321@nwafu.edu.cn).

F.Iannuzzo is with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (email: fia@et.aau.dk).

both the thermal- and mechanical domain. The average height of asperities  $\sigma_{\rm asp}$  and average slope of asperities  $m_{\rm asp}$  are used to determine the value of both electrical- and thermal contact resistance. The distribution of contact electrical resistance influences the distribution of load current, while the change of contact thermal resistance affects the heating dissipation ability.

Fig. 2. The fully coupled relationship inside PPI.

Reliability analysis of PPI by the utilization of the finiteelement (FE) model is very important. De-coupled models were proposed to analyze the mechanical distribution firstly. A. Pirondi et al. simulated the stress and strain distribution in a PPI by thermo-mechanical simulation in 1998 and 2000 [10-11]. In the model, a uniform contact pressure was considered and the friction coefficient in the friction model was set at 0.5 between the contact surfaces. In 2000, P. Cova et al. created a thermomechanical simulation model to investigate the chip stress and strain due to power cycling conditions [12]. A. Hasmasan established a FE model to calculate the stress distribution inside the PPI device under different clamping conditions and found the uneven stress distribution phenomenon [13]. T. Poller et al. analyzed the pressure distribution inside multi-chip PPI during both the clamping phase and heating phase. The temperature distribution was derived firstly by an electro-thermal model, then the mechanical simulation was performed to calculate the mechanical stress generated by the power cycle condition [14]. Although the model is not fully coupled, the uneven distribution of temperature and pressures in the device was found. The thermal domain and the mechanical domain were not coupled in the above models. The coupled model should be proposed to investigate the thermo-mechanical stress since the uneven stress distribution becomes more serious due to the coupling relationship. In 2013, T. Poller et al. proposed a fully coupled model for the first time to analyze the influence of clamping pressure on the electrical, thermal and mechanical characteristics of PPI devices [15]. The fully coupled relationship was realized by using contact resistance, which was identified by combining the FE method and the experimental method [16]. In 2015, P. Rajaguru et al. built a fully coupled model of a press-packaged SiC schottky diode with a single chip. Different from T. Polle's model, the empirical formulas were used to describe the contact resistance behaviors [17].

Since the fully coupled models were available, the reliability analysis of PPI was widely conducted. Siyang Dai et al. analyzed the influence of the clamping area on the thermal and mechanical characteristics in PPI[18]. E. Deng et al. studied the influence of temperature on PPI pressure distribution by establishing a fully coupled multi-physical model [19]. The contact resistance was obtained through the combination of

experiment and simulation methods. Since the contact resistance parameters of the model depend on the experiment result, it cannot be used to study the temperature and pressure distribution under various surface roughness. W. Lai et al. studied the influence of uneven pressure on the thermal distribution through FE simulation [20]. The clamping force was not applied on the collector external plate, resulting in the temperature distribution among the chip emitter surfaces were not in good agreement with the actual situation. Besides, the stress distribution among chip emitter surfaces was not investigated. The fatigue life analysis of the IGBT device was also significant in the field of reliability research. Coffin-Manson model was used in the fatigue life investigation of IGBTs for its bonding wires lifting-off fatigue [21]. Y. Huang et al. proposed an energy-based physical life model for dieattach joints in IGBTs under low-amplitude temperature swings [22]. Besides, H. Li et al. calculated the fatigue life of singlechip PPI and derived the distribution of fretting wear lifetime on an IGBT chip [23]. As of the time of writing, the expected life of multi-chip PPIs has not been investigated yet.

In conclusion, the influence of surface roughness on the thermo-mechanical stress distribution and fatigue life is less investigated in the research area of PPI reliability. To tackle this problem, this paper establishes a fully coupled multi-physical model of multi-chip PPI to predict the temperature and pressure distribution simultaneously. The surface roughness of the contact surfaces is considered in the contact resistance model, so the influence of the surface roughness on the temperature and pressure distribution can be investigated. Moreover, the fatigue life of chip additional metallization area is also studied by the utilization of the strain-life fatigue model based on the stress and strain results from the fully coupled model. The influence of the surface roughness on the fatigue life is then analyzed. This investigation is an important supplement for the existing PPI reliability research works.

The rest of this paper is organized as follows. Section II introduces a fully coupled multi-physical model and the contact resistance model of PPI. Section III introduces the temperature and pressure simulation results under both the clamping phase and heating phase. The influence of surface roughness is also investigated in this section. Section IV is the validation of the proposed model. Section V introduces a strain-life fatigue model for the number of cycle to failure prediction of the chip additional metallization area. The last section is the conclusion of this paper. The discussion about the limitation of the research work and the promising directions worthy of further study is also presented in this section.

## II. FULLY COUPLED MODEL OF PPI

## A. Governing equation of various domains

(1) Electrical domains. Power losses mainly consist of conduction losses and switching losses. Since this paper only researches the steady-state of PPIs under power cycling tests, the power loss model only considers the conduction loss. In the heating phase, the power loss results from joule heating generated by the load current flowing through the device. The

heat source per unit volume is calculated in equation (1).  $Q_e$  is the volumetric heat source, J is the current density,  $\gamma$  is the conductivity, and T is the temperature.

$$Q_e = JE = \frac{1}{\gamma(T)} |J|^2 \tag{1}$$

(2) Thermal domain. The thermal conductivity of the material differs significantly inside the PPI, leading to a temperature gradient from the chip to the collector and emitter plates. The heat conduction in the PPI includes natural heat convection between the solid material and the insulating air, and heat conduction in the solid material. Compared with the heat conduction in the solid material, the heat dissipation through the air is very small and can be neglected. Therefore, the heat conduction in the solid material is the only one considered in the thermal domain. The partial differential equation (PDE) of the thermal domain is shown in (2), where k is the thermal conductivity,  $\rho$  is the material density,  $C_p$  is the constant pressure-specific heat capacity.

$$\nabla \cdot (k \nabla T) + Q_{\rho} = \rho C_{P} \nabla T \tag{2}$$

(3) Mechanical domain. Linear elastic materials are used in the mechanical domain. The thermal stress caused by the temperature swing is the critical mechanism of the fatigue failure of PPI. Based on the linear thermal expansion theory, the total strain includes a thermal strain caused by the temperature swing and a static strain caused by the clamping stress. The thermal strain is represented by equation (3), where  $\alpha$  is the coefficient of thermal expansion, and  $T_{\text{ref}}$  is the referenced temperature.

$$\mathcal{E}_{th} = \alpha (T - T_{ref}) \tag{3}$$

#### B. Contact resistance

The surface of the contact area is rough from the microscopic perspective. The small air gap between the contact areas hinders the transfer of heat since the thermal conductivity of air is relatively small. The temperature of the contact area is not continuous due to contact thermal resistance. It is necessary to establish a contact thermal resistance model since the equation of the bulk thermal resistance cannot describe the thermal behavior at the contact area. Equation (4) shows the thermal behavior.

$$-n_{dst} \cdot q_{dst} = -h(T_{stc} - T_{dst})$$

$$-n_{sc} \cdot \overrightarrow{q}_{sc} = -h(T_{dst} - T_{sc})$$

(4)

Where,  $q_{\rm dst}$ ,  $q_{\rm src}$ ,  $T_{\rm dst}$ , and  $T_{\rm src}$  denote the heat flux by conduction and the temperature of the destination and source layers, respectively.  $n_{\rm dst}$  and  $n_{\rm src}$  are the normal vectors of destination and source layers respectively. The average thermal conductivity h, which coincides with the constriction thermal conductivity  $h_{\rm c}$  at the contact spots, evaluates the joint conductance.

$$h = h \tag{5}$$

$h_{\rm c}$  is defined by equation (6), where  $k_{\rm dst}$  and  $k_{\rm src}$  are the thermal conductivity of the destination and source layers respectively. P is the contact pressure between the various layers, and  $H_{\rm c}$  is the micro-hardness. The average height of asperities  $\sigma_{\rm asp}$  and average slope of asperities  $m_{\rm asp}$  are the root mean square values

of the two contacting surface roughness values. The relationship between  $\sigma_{\rm asp}$  and  $m_{\rm asp}$  is shown in equation (7) when  $\sigma_{\rm asp}$  ranges from 0.216  $\mu m$  to 9.6  $\mu m$ .

$$h_{c} = 2.5 \frac{k_{ds} k_{sr}}{k_{dst} + k_{sr}} \frac{m_{asp}}{\sigma_{asp}} (\frac{P_{contact}}{H_{c}})^{0.95}$$

(6)

$$m_{\rm asp} = 0.125(\sigma_{\rm asp} \times 10^6)^{0.402}$$

(7)

Compared with the contact thermal resistance, the air gap cannot conduct current and the load current only flows through the point contact area. The contact electrical resistance can be described by equation (8), where  $h_{\rm e}$  is the shrinkage conductance determined by the surface characteristics and contact pressure,  $\gamma_{\rm dst}$  and  $\gamma_{\rm src}$  are the electrical conductivity of the destination and source layers respectively.

$$h_{\rm e}=2.5\frac{\gamma_{\rm dst}\gamma_{\rm src}}{\gamma_{\rm dst}+\gamma_{\rm src}}\frac{m_{\rm asp}}{\sigma_{\rm asp}}(\frac{P_{\rm contact}}{H_{\rm c}})^{0.95}$$

(8)

## C. Physical parameters

The physical parameters of the materials in the model are summarised in Table I.

TABLE I PHYSICAL PARAMETERS OF MATERIALS

| Parameters                                               | Ag     | Cu   | Mo     | Chip        |

|----------------------------------------------------------|--------|------|--------|-------------|

| $\rho$ (kg/m <sup>3</sup> )                              | 10500  | 8690 | 10220  | 2329        |

| CTE (10 <sup>-6</sup> )                                  | 18.9   | 17   | 4.8    | 2.6         |

| Young's Modulus (Gpa)                                    | 83     | 110  | 312    | 170         |

| Possion's Ratio (1)                                      | 0.37   | 0.35 | 0.30   | 0.28        |

| $k \left( W/(m \cdot K) \right)$                         | 429    | 400  | 138    | 130         |

| $C_p\left(\mathbf{J}(\mathbf{kg}\cdot\mathbf{K})\right)$ | 235    | 385  | 250    | 700         |

| $\gamma$ (S/m)                                           | 6.17e7 | 6e7  | 1.89e7 | $\gamma(T)$ |

| Relative permittivity (1)                                | 1e-6   | 1e-6 | 1e-6   | 11.5        |

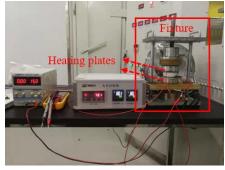

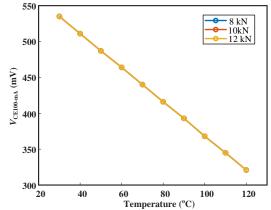

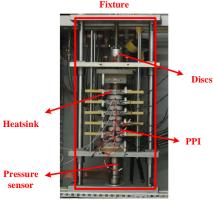

The chip was regarded as a temperature-dependent resistance during the turn-on state. We measured the saturation voltage under various junction temperatures by a specialized PPI fixture shown in Fig.3. The clamping force is adjustable from 2-20 kN and the two heating plates can be heated up from 30 °C to 150 °C. After enough heating time to make sure the PPI under thermal equilibrium state, 350 A current is injected into the device and the saturation voltage  $V_{\rm CE}$  under various junction temperatures is measured. The temperature-dependent conductivity is shown in equation (9).

$$\gamma(T) = -0.129 * T + 65.838 \tag{9}$$

Fig. 3. The saturation voltage measurement platform

## D. Size of the model

A PPI (T0360NB25A [24]) contains five IGBT chips and two free-wheeling diode (FWD) chips, the number is shown in Fig. 4. Physical dimensions are shown in Table II. Each chip has a sandwich structure, where the top layer and bottom layer are composed of thin sintered silver plates. The thickness of each thin sintered silver plate is 50  $\mu$ m. The thin silver layer of the chip emitter side is called the additional metallization area.

TABLE II SIZE OF PPI STRUCTURE

| Name          | Shape    | High (mm) | Side or radius (mm) |

|---------------|----------|-----------|---------------------|

| Collector     | Cylinder | 9         | 28                  |

| Emitter       | Cylinder | 5         | 32                  |

| Mo (C)        | Square   | 1.8       | 12.6                |

| Chip          | Square   | 0.35      | 12.38               |

| Mo (E)        | Square   | 1.1       | 10                  |

| Copper pillar | Square   | 8.6       | 10                  |

Fig. 4. The number of IGBT and FWD chips.

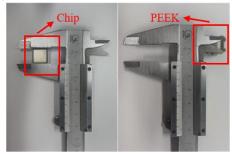

The length of the chip external side and the PEEK frame internal side are 12.38 mm and 12.56 mm respectively, which were measured by a Vernier caliper with 50 divisions, as shown in Fig.5. The gap between the PEEK frame and chip is around 180  $\mu$ m. However, the deformation of the chip is less than 50  $\mu$ m according to the simulation result in reference [19]. The existence of the PEEK frame does not modify the stress level and distribution of the chip. To simplify the finite-element model and reduce the computation burden, the PEEK frame (see Fig.1) was eliminated in the model.

Fig. 5. Length measurement.

## E. Boundary conditions and initial conditions

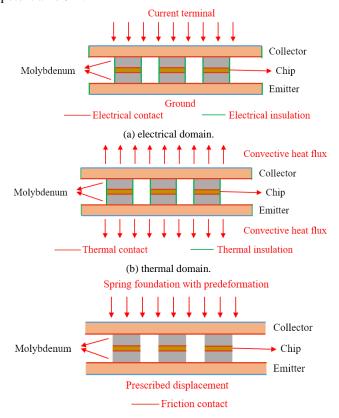

(1) The boundary condition and initial value of the electrical domain are shown in Fig. 6(a). The applied current amplitude

in the model is 350 A on the collector external surface and the emitter external surface is set as ground. The electrical connection between the various layers takes place through a contact electrical resistance, and the other surfaces are set as electrical insulation surfaces. The initial value of the electrical potential is 0 V.

(c) mechanical domain. Fig. 6. Boundary conditions and initial conditions.

(2) The boundary condition and initial value of the thermal domain are shown in Fig. 6(b). The heatsinks at both the collector and emitter external surfaces are not considered in this model to reduce the computation complexity. The convective heating flux boundary condition is used to simulate the heat transfer between the heatsinks and the PPI device. The heating transfer behavior is described by equation (10)

$$-k\nabla T = hht(T_{\text{ext}} - T) \tag{10}$$

Where k is the thermal conductivity,  $T_{\rm ext}$  is the ambient temperature, hht is the convective heat transfer coefficient. The convective heat transfer coefficient of the collector and emitter sides are both set to 10000 W/(m<sup>2</sup>\*k) [18, 20].  $T_{\rm ext}$  is set as 20°C since the temperature of the cooling water remains 20 °C. The initial value of temperature is 20 °C as well. Also, in this model, the thermal connection between the various layers is through thermal contact, and the other surfaces are set as thermal insulation surfaces.

(3) The boundary condition and initial value of the mechanical domain are shown in Fig. 6 (c). PPI is clamped in the fixture between two heatsinks, the height of the heatsinks is larger than the radius of PPI to diminish the height effects on the stress distribution among the chips. There are two options

to apply the boundary condition on the collector external surface in the elastic mechanical domain. One is the boundary load, the other is the spring foundation with predeformation. During the heating phase, the thermal expansion causes the increment of the normal force, so the boundary load cannot reflect the variable force load. Moreover, discs are used in the fixture to offset the thermal expansion and obtain a relative uniform displacement inside PPI. In this consideration, the spring foundation with predeformation is more suitable at the collector external surface to simulate the function of discs. The spring foundation is described by equation (11)

$$F = -k_{\text{spring}} \Delta u \tag{11}$$

Where F is the normal force,  $k_{\rm spring}$  is the total spring constant,  $\triangle$  u is the deformation variation. The direction of the predeformation is shown in Fig. 6 (c). The emitter external plate is bonded with a rigid metal heatsink, so the normal deformation is restricted. The normal prescribed displacement is set at zero at the emitter external surface. Multi-layers inside the PPI are connected with fictional contact pairs with the coefficient of 0.5 [10-11], and the augmented Lagrange method is chosen to calculate the contact pressure in the mechanical domain since it yields a more accurate result.

## F. Mesh method and solver settings

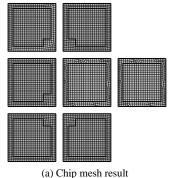

The mesh results of the chip and the whole device are shown in Fig. 7(a) and Fig. 7(b) respectively. The number of body elements and nodes is 107142 and 110019 respectively. A swept mesh is created on the chip domain with the 0.5 mm element size while a free tetrahedral mesh is applied on the collector and emitter poles with the 1 mm element size. The mesh element of molybdenum plates is the coarsest since the hardness of molybdenum is the largest than other materials in the PPI submodule.

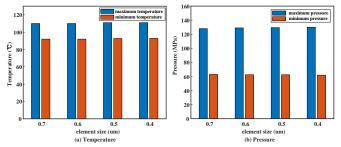

The mesh result has a big influence on the temperature and stress distribution if the element size is too coarse. To validate the mesh result, the maximum and minimu chip temperatures and pressures under the heating phase are compared in Fig. 8 with element size ranging from 0.4 mm to 0.7 mm. The chip mesh fineness has little influence on the calculation results in this element size scope. In the stationary solver, a segregated solution approach is utilized since the fully coupled model with contact surfaces is very difficult to obtain a direct convergence result. The relative tolerance in the stationary solver is 2.5.

(a) Device mesh result

Fig. 7. Mesh results.

Fig. 8. Temperature and pressure results under various element sizes.

#### III. SIMULATION RESULTS ANALYSIS

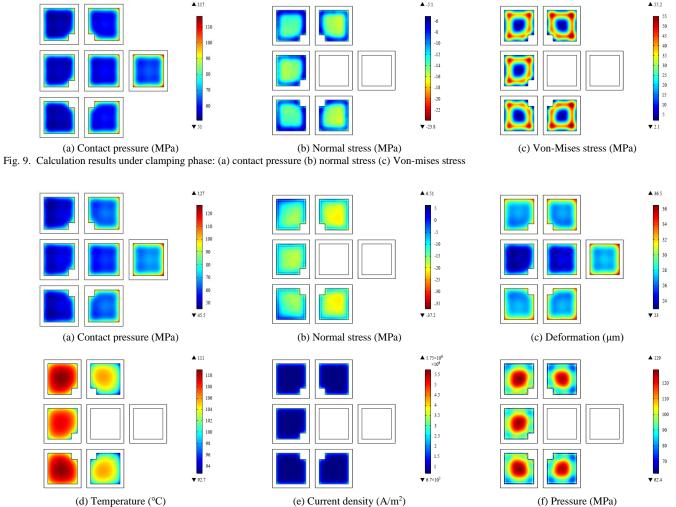

## A. Mechanical stresses distribution under clamping phase

In the clamping phase, the PPI is clamped in the fixture under a preset clamping force to ensure good electrical and thermal contact. No current flows through the PPI. The contact pressure, normal stress, and Von-Mises stress distribution on the chip additional metallization area are shown in Fig. 9(a), 9(b), and 9(c) respectively. The contact pressure has the larger value at the five corners within a single chip and the distribution among five IGBT chips is similar. The normal stress has a gradient distribution within a single chip from the edge of the additional metallization area to the middle area. The maximum value is 23.5 MPa. However, the Von-Mises stress within a single chip shows a contrary distribution compared with the normal stress. The Von-Mises stress within a single chip shows that the value at the edge is much higher than that in the middle area.

## B. Thermo-mechanical stresses distribution under heating phase

Under the heating phase, the contact pressure, normal stress, deformation, temperature, current density, pressure distribution are shown in Fig. 10(a), 10(b), 10(c), 10(d), 10(e), and 10(f) respectively. The maximum contact pressure increases only 10 MPa after heating up, which explains the discs have good performance in offsetting the thermal expansion effect. It shows that the distribution of contact pressure on the five IGBT chips is uneven due to the thermal expansion. The contact pressure of the left area of the #1 IGBT and #3 IGBT chips decreases apparently. After heating up, the temperature of IGBT chips is much higher than that of FWD chips. With the thermal expansion generated by the high temperature on the IGBT chips, the collector poles warps, which results in less contact on the left area of #1 IGBT and #3 IGBT. The normal stress distribution shares a similar change with the contact pressure. The distribution of the deformation within a single chip also

shows a gradient from the edge area to the middle area and the five corners of a single chip have a larger deformation.

Within a single chip, the temperature increases from the edge area to the middle area. The current density within a single chip shows that the amplitude at the edge of the additional metallization area is much higher than that in the middle area, so the power loss is high at the edge area within a single chip. There is a reverse relationship between contact pressure and contact resistance. The contact electrical resistance is smaller at the edge area, so the current density and power loss are larger at this area. However, the contact thermal resistance is also smaller at the edge area, which indicates that the edge area has better heat dissipation capacity. This phenomenon explains that the contact thermal resistance has a larger impact on the temperature distribution than the contact electrical resistance. Among the five IGBT chips, the temperature on the five IGBT chips is different, i.e. the left three IGBT chips have a higher temperature. The thermal across-coupling effect between the multi-chips is the main reason for the temperature uneven distribution. Moveover, due to the thermal expansion generated by the high temperature on the IGBT chips, the pressure on the left area of #1 IGBT and #3 IGBT is loss of contact. The less contact on this area induces the increment of contact thermal

resistance and increases the temperature distribution on the two chips.

The pressure distribution is similar to the temperature distribution within a single chip. The middle area has larger amplitude since the higher temperature induced higher thermal expansion. Among the five IGBT chips, due to the warpage effect, the pressure distribution on the corner areas is also larger compared with that of the edge area. Based on the pressure and deformation on the additional metallization area, the reliability of the corner areas is relatively low.

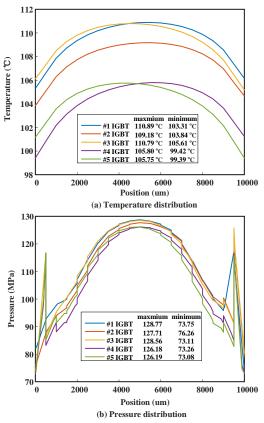

To compare the temperature and pressure on the five IGBT chips. A vertical profile has been selected on each of the IGBT chips, as shown in Fig. 4. The results are shown in Fig. 11(a) and 11(b) respectively. The maximum and minimum values are also listed in the figure insets. The temperature profiles of the five IGBT chips are similar, although the maximum values differ. The maximum temperature variation is around 5 °C, which is a 4.7 % variation. The variation of maximum pressure reaches 2.59 MPa, and the variation reaches 2.1 %. The temperature and pressure distribution is uneven and the #1 IGBT chip and #3 IGBT chip has larger temperature and pressure distribution.

Fig. 10. Calculation results under heating phase: (a) contact pressure (b) normal stress (c) deformation (d) temperature (e) current density (f) pressure

Fig. 11. The calculation result of the selected vertical profile on five IGBT chips under the same surface roughness: (a) temperature (b) Pressure

#### C. Influence of the surface roughness

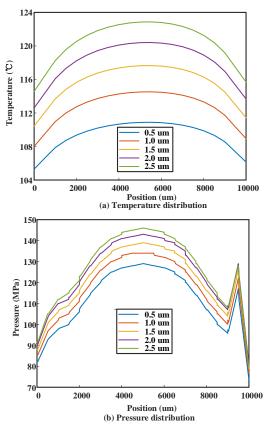

To investigate the influence of various surface roughness on the temperature and pressure distribution of multi-chip PPI under the heating phase, the surface roughness of the five IGBT chip is changed from 0.5 µm to 2.5 µm in the model. On one hand, the empirical formula shown in equation (8) to estimate the surface roughness is regulated in the scope of 0.216 µm to 9.6 µm. On the other hand, the measurement of the surface roughness of the healthy new chips is around 0.1 µm. The molybdenum plate is above 1 µm. Thus, the surface roughness is selected in the scope from 0.5 µm to 2.5 µm. The temperature and pressure of the selected vertical profile on the #1 IGBT chip are shown in Fig. 12(a) and 12(b) respectively. The temperature and pressure both increase with the increment of surface roughness, and the variations decrease gradually. Since the change of the surface roughness is assumed even on the IGBT chips, in this case, the temperature and pressure distribution remains similar on these five chips.

#### IV. EXPERIMENTAL VERIFICATION

## A. Verification of chip temperature under heating phase

Since the IGBT chips are sealed inside the package structure as shown in Fig. 1, the direct measurement of the chip temperature distribution with optical or infrared sensors is not available. Actually, the saturation voltage  $V_{\rm CE-100mA}$  under 100mA direct current has a linear relation with the junction temperature of IGBT. In this paper, the average chip

Fig. 12. The calculation result of the selected vertical profile on #1 IGBT chip surface under various surface roughness: (a) temperature (b) pressure

temperature was considered as the junction temperature. Thus, the temperature calculation result could be verified under the measurement of  $V_{\rm CE-100mA}$ . The linear relation between the  $V_{\rm CE-100mA}$  and temperature is shown in Fig. 13.  $V_{\rm CE-100mA}$  shows a negative linear correlation with temperature and the slope remains 2.6 mV/°C under various clamping pressures.

Fig. 13. Calibration curve.

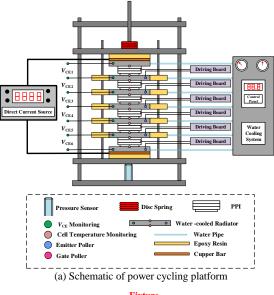

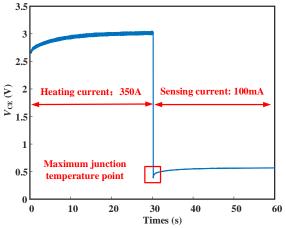

The stationary calculation is the interest of this paper, so it is essential to test the chip temperature under a thermal equilibrium state. Power cycling test was performed on a PPI with a long heating time to achieve the thermal equilibrium state. Since the transient thermal impedance in the datasheet shows that the heating time was longer than 18 s to obtain the steady-state, we tested the device under 350 A loading current with 30 s heating time and 30 s cooling time. The schematic and

physical picture of the claming fixture are shown in Fig. 14(a) and Fig. 14(b) respectively.

(b) The physical picture of the clamping fixture Fig. 14. power cycling platform: (a) Schematic of power cycling platform (b) physical picture of the clamping fixture.

Fig. 15. The collector to emitter on-state voltage during a power cycle.

100 mA sensing current was injected into the device to measure the junction temperature after the heating phase. The sampling frequency was set at 50 MHz to capture the minimum value of  $V_{\text{CE-}100\text{mA}}$  which could be utilized to reflect the maximum junction temperature. The collector to emitter onstate voltage during a power cycle is shown in Fig. 15. The

minimum value of the voltage under 100 mA is 0.369 V, which reflects the maximum junction temperature is 99.16 °C. The average temperature is 101.72 °C result of the fully coupled model. The experiment confirms the model result within 2.6 %.

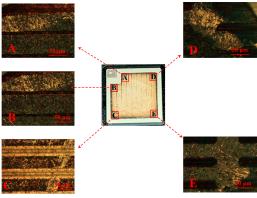

## B. Verification of deformation under heating phase.

After the power cycling test, the PPI device was disassembled utilizing a grinder [9]. The surface morphology of the emitter was investigated through a metallurgical microscope (Axio Scope A1). Some fretting scratches were found on the additional metallization area, which is shown in Fig. 16. Fretting scratches spread mostly on the corners of the additional metallization area. As a conclusion of the failure analysis, the corners of the additional metallization area suffer larger microdeformation and induce the fretting wear damage in this area. The observation result qualitatively supports the prediction correctness of deformation distribution.

Fig. 16. Fretting scratches.

## V. FATIGUE ANALYSIS OF MULTI-CHIP PPI

The fatigue life can be estimated by a strain-life model combining Basquin and Coffin-Manson relation [25], as shown in equation (12).

$$\varepsilon_{\rm a} = \varepsilon_{\rm ea} + \varepsilon_{\rm pa} = \frac{\sigma_{\rm f}}{E} (2N_{\rm f})^b + \varepsilon_{\rm f} (2N_{\rm f})^c \tag{12}$$

Where  $\sigma_f$  is the fatigue strength coefficient;  $\varepsilon_f$  is the fatigue ductility coefficient; b is the fatigue strength exponent; c is the fatigue ductility exponent;  $\varepsilon_{ea}$  is the elastic strain component and  $\varepsilon_{pa}$  is the plastic strain component; E is Young's modulus;  $2N_f$  is the number of load reversals; two reversals are equal to one cycle, thus  $N_f$  is the number of full cycles to failure as a strain amplitude of  $\varepsilon_a$ . The strain  $\varepsilon_a$  is regulated by the equation (13-14)

$$\varepsilon_{\rm a} = \Delta \varepsilon / 2 \tag{13}$$

$$\varepsilon = \begin{cases} \varepsilon_1, \varepsilon_1 \ge |\varepsilon_3| \\ \varepsilon_3, \varepsilon_3 \ge |\varepsilon_3| \end{cases}$$

$$\tag{14}$$

Where  $\varepsilon_1$  and  $\varepsilon_3$  are the largest principal strain and the smallest principal strain. However, due to the asymmetric stress cycle of PPI under the power cycling test, the equation (12) is not applicable. Morrow conducted the linear correction of elastic stress to improve the Coffin-Manson equation, as shown in (15).

$$\varepsilon_{a} = \frac{\sigma_{f}^{'} - \sigma_{m}}{E} (2N_{f})^{b} + \varepsilon_{f}^{'} (2N_{f})^{c}$$

(15)

Where  $\sigma_m$  is the mean stress of the load cycle. Since stress is a second-order tensor and the mean stress is a scalar, the evaluation of the mean stress is based on the principal stress according to equation (16).

$$\sigma = \begin{cases} \sigma_1, \sigma_1 \ge |\sigma_3| \\ \sigma_3, \sigma_3 \ge |\sigma_3| \end{cases}$$

(16)

Where  $\sigma_1$  and  $\sigma_3$  are the largest principal stress and the smallest principal stress respectively. The most commonly used method to estimate the fatigue performance parameters is the universal slope method, the four-point correlation method, and the improved four-point correlation method. In this paper, the universal slope method is utilized to determine the value of the four fatigue performance parameters. The fatigue performance parameters of Ag are shown in Table III.

TABLE III

FATIGUE PERFORMANCE PARAMETERS OF AG  $\sigma_{

m f}^{\dot{c}}$  (Mpa)  $\varepsilon_{

m F}^{\dot{c}}$  b c700 0.949 -0.12 -0.6

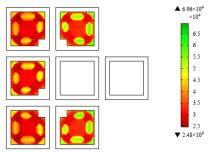

Since the electrical- and thermal contact resistance are the key parameters, and the contact pressure shows strong nonlinearity in the fully coupled model, the transient calculation of the stress and strain distribution is very difficult. In this paper, the mechanical simulation results from the steady-state model under both 0 A and 350 A input are utilized to calculate the fatigue life of the PPI chip's additional metallization area. When the input current is 0 A, the device is under the clamping phase. When the input current is 350 A, the device is under the heating phase. Then, with the simulation results under both 0 A and 350 A input, the fatigue life of the PPI is calculated according to equation (12-16). The number of cycles to failure which evaluates the fatigue of the additional metallization area is shown in Fig. 17. The minimum number of cycles to failure area locates at areas near the corners. It indicates that these parts are the weakest in the metallization area.

Fig. 17. The calculation result of the number of cycles to failure on additional metallization area of IGBT chips.

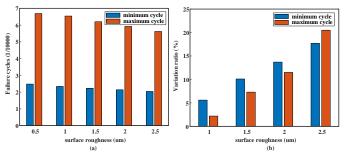

The influence of the surface roughness on the fatigue failure life is also calculated, which is shown in Fig. 18. Fig. 18(a) shows that both the minimum fatigue failure cycle and maximum fatigue failure cycle decrease with the increment of surface roughness. The minimum fatigue failure cycle decreases from 24800 to 20400, with a variation of 17.7 %. The maximum fatigue failure cycle decreases from 69600 to 56200, with a variation of 20.5 %. Thus, the increase of surface roughness of the chips can decreases the lifetime. This result is

important for the evaluation of PPI fatigue life and reliability research.

Fig. 18. Calculation result on additional metallization (a) maximum and minimum fatigue failure cycles (b) variation ratio compared with the healthy condition

## VI. CONCLUSIONS

The influence of surface roughness on thermo-mechanical stress distribution has been analyzed with a newly proposed fully coupled model in this paper. Four important conclusions are drawn in this work:

- (1) A fully coupled multi-physical model of multi-chip PPI taking into account the temperature and pressure distribution simultaneously is proposed. The influence of surface roughness is considered.

- (2) The distributions of temperature and stress on the surface of various chips are different inside multi-chip PPIs. For one single chip, the corners reliability of the additional metallization area is relatively low.

- (3) The even increment of surface roughness results in the increment of temperature and pressure on the additional metallization area, while the distribution of these parameters on each chip surface remains the same.

- (4) Based on the strain-life model of PPI, the number of cycles to failure on the additional metallization area is calculated with the purely elastic mechanical domain. The increase of surface roughness can induce the decrease of fatigue failure life on the metallization area.

The analysis provides a solid foundation for reliability improvement of PPI. However, there is still some work worthy of further study.

- (1) Only a purely elastic mechanical domain is considered in this paper. The plastic behavior of the additional metallization area of the chips is also very important for the reliability analysis. This issue will be addressed in further work.

- (2) The simulation of the multi-chip PPI device under the transient state is very useful in the reliability research and fatigue life estimation area. However, since the contact resistance is the critical coupling parameter in the fully coupled model and the calculation of the contact pressure is very difficult due to the strong nonlinear characteristics, the establishment of the PPI transient simulation model still needs effort.

- (3) According to the existing research result, fretting wear is the main fatigue failure mechanism of PPI. The fatigue analysis model for bond-wire IGBT is not sufficient for PPI devices in terms of fretting fatigue. A novel fatigue model for the fatigue

failure life estimation of PPI should be proposed.

(4) Due to the lack of exact measurement methods for chip temperature and pressure, the validation of the fully coupled model is qualitative, which results in the conclusions mainly focus on the thermo-mechanical distribution but not the numerical accuracy. Advanced sensors should be utilized for the measurement of temperature and pressure in PPI.

The utilization of the transient stress load in the novel fatigue model to estimate the PPI lifetime will be the next work of the authors.

#### REFERENCES

- S. Ji, X. Huang, J. Palmer, et al., "Modular Multilevel Converter (MMC) Modeling Considering Submodule Voltage Sensor Noise," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 1215-1219, Feb. 2021.

- [2] T. Bandaru, D. Samajdar, P. B. S. Varma, et al., "Optimum Injection of Second Harmonic Circulating Currents for Balancing Capacitor Voltages in Hybrid MMC during Reduced DC Voltage Conditions," *IEEE Transactions on Industry Applications*, vol. 56, no. 2, pp. 1649-1660, March-April 2020.

- [3] M. Alharbi and S. Bhattacharya, "Scale-Up Methodology of a Modular Multilevel Converter for HVDC Applications," *IEEE Transactions on Industry Applications*, vol. 55, no. 5, pp. 4974-4983, Sept.-Oct. 2019.

- [4] S. Chen, S. Ji, L. Pan, et al., "An ON-State Voltage Calculation Scheme of MMC Submodule IGBT," *IEEE Transactions on Power Electronics*, vol. 34, no. 8, pp. 7996-8007, Aug. 2019.

- [5] B. Wang, L.Wang, F.Yang, et al., "Air-Cooling System Optimization for IGBT Modules in MMC Using Embedded O-shaped Heat Pipes," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, DOI: 10.1109/JESTPE.2021.3054918.

- [6] H. Y. Long, M. R. Sweet, E. M. S. Narayanan, et al., "Reliability study and modeling of IGBT press-pack power modules," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 2017, pp. 2711-2717.

- [7] H. Li, H.Long, R.Yao, et al., "A Study on the Failure Evolution to Short Circuit of Nanosilver Sintered Press-Pack IGBT," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 10, no. 1, pp. 184-187, Jan. 2020.

- [8] K. B. Pedersen and K. Pedersen, "Dynamic Modeling Method of Electro-Thermo-Mechanical Degradation in IGBT Modules," *IEEE Transactions* on *Power Electronics*, vol. 31, no. 2, pp. 975-986, Feb. 2016.

- [9] C. Zhan, L. Zhu, J. Dai, et al., "A Novel Multi-Physical Coupled Model of Press-Pack IGBT in Steady Conducting State Considering Fretting Wear," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2020, pp. 4937-4942.

- [10] A. Pirondi, G.Nicoletto, P. Cova, et al., "Thermo-mechanical Simulation of a Multichip Press-packed IGBT", Solid-state Electronics, Vol. 42, no.12, pp. 2303-2307, 1998.

- [11] A. Pirondi, G.Nicoletto, P. Cova, et al., "Thermo-mechanical Finite Element Analysis in press-packed IGBT design", *Microelectronics Reliability*, Vol. 40, no.7, pp. 1163-1172, 2000.

- [12] P. Cova, G.Nicoletto, P. Cova, et al., "Power Cycling on Press-pack IGBTs: Measurements and thermomechanical simulation", *Microelectronics Reliability*, Vol. 39, no.7, pp. 1165-1170, 1999.

- [13] A. Hasmasan, C. Busca, R. Teodorescu, et al., "Modelling the clamping force distribution among chips in press-pack IGBTs using the finite element method," 2012 3rd IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aalborg, Denmark, 2012, pp. 788-793.

- [14] T. Poller, T. Basler, M. Hernes, et al., "Mechanical analysis of press-pack IGBTs," *Microelectronics Reliability*, vol. 52, no. 9, pp. 2397-2402, Jul. 2012.

- [15] T. Poller, S. DArco, M. Hernes, et al, "Influence of the clamping pressure on the electrical, thermal and mechanical behavior of press-pack IGBTs," *Microelectronics Reliability*, vol. 53, no. 9-11, pp. 1755-1759, Jul. 2013.

- [16] T. Poller, J. Lutz, S. D'Arco, et al, "Determination of the thermal and electrical contact resistance in press-pack IGBTs," 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2013, pp. 1-9.

- [17] P. Rajaguru, J. A. Ortiz-Gonzalez, H. Lu, et al., "A Multiphysics Modeling and Experimental Analysis of Pressure Contacts in Power Electronics Applications", *IEEE Transactions on Components*, *Packaging and Manufacturing Technology*, vol. 7, no. 6, pp. 893-900, June 2017.

- [18] S. Dai, Z. Wang, H. Wu, et al., "Thermal and Mechanical Analyses of Clamping Area on the Performance of Press-Pack IGBT in Series-Connection Stack Application," *IEEE Transactions on Components*, *Packaging and Manufacturing Technology*, vol. 11, no. 2, pp. 200-211, Feb. 2021.

- [19] E. Deng, Z. Zhao, Z. Lin, et al. "Influence of Temperature on the Pressure Distribution Within Press Pack IGBTs," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 6048-6059, Jul. 2018.

- [20] W. Lai, H. Li, M. Chen L, et al, "Investigation on the Effects of Unbalanced Clamping Force on Multi-chip Press Pack IGBT Modules," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 4, pp. 2314-2322, Dec. 2019.

- [21] Y. Huang, Y. Jia, Y. Luo, et al, "Lifting-Off of Al Bonding Wires in IGBT Modules Under Power Cycling: Failure Mechanism and Lifetime Model," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 3, pp. 3162-3173, Sept. 2020.

- [22] Y. Huang, H. Deng, Y. Luo, et al, "Fatigue Mechanism of Die-Attach Joints in IGBTs Under Low-Amplitude Temperature Swings Based on 3D Electro-Thermal-Mechanical FE Simulations," *IEEE Transactions on Industrial Electronics*, vol. 68, no. 4, pp. 3033-3043, April 2021.

- [23] H. Li, R. Yao, W. Lai, et al, "Modeling and Analysis on Overall Fatigue Failure Evolution of Press-Pack IGBT Device," *IEEE Transactions on Electron Devices*, vol. 66, no. 3, pp. 1435-1443, March 2019.

- [24] (2011) [online]. Available at: http://www.ixysuk.com/igbt1.html.

- [25] Masson S S. Behaviour of Materials under Conditon of the Thermal Stress [R]. NACA TN-2933, 1953.

Cao Zhan was born in Hubei, China, in 1993. He received the B.S. Degrees in electrical engineering from Xi'an Jiaotong University, Xi'an, China, in 2015. He is currently working toward the Ph.D. degree in electrical engineering at Xi'an Jiaotong University, Xi'an, China. His research interests cover reliability of power devices,

including failure mechanism, condition monitoring, and life estimation.

Lingyu Zhu was born in Shandong, China in 1988. He received the B.Sc. degree from Xi'an Jiaotong University, Xi'an, China in 2009 and the Ph.D. degree from Xi'an Jiaotong University in 2014. He is currently an Associate Professor in Xi'an Jiaotong University, Xi'an, China. His research interests include condition

monitoring of power equipment in HVDC application.

Yaxin Zhang was born in Hebei, China, in 1998. She received the B.S. Degrees in electrical engineering and automation from North China Electric Power University, Beijing, China, in 2020. She is currently working toward a master's degree in electrical engineering at Xi'an Jiaotong University, Xi'an, China. Her research

interests include failure mechanism and condition monitoring technology of power devices.

Jiangang Dai was born in Henan, China, in 1997. He received the B.S. Degree in electrical engineering from Sichuan University, Chengdu, China, in 2019. He is currently working toward the M.S. degree in electrical engineering at Xi'an Jiaotong University, Xi'an, China. His research interests include condition monitoring and

fault diagnosis of key components in charging piles.

Ting Hou was born in Shaanxi province, China, in 1981. She received the master degree in Power electronics from Huazhong University of science and technology, China, in 2007. Her main research focuses on HVDC transmission technology and reliability of converter valve.

Ying Song was born in Shaanxi, China, in 1992. She received the B.Sc. and Ph.D. degrees in electrical engineering from Xi'an Jiaotong University, Xi'an, China, in 2013 and 2020, respectively. She was a Visiting Scholar with the School of Electrical and Computer Engineering, Georgia Institute of Technology from 2016

to 2018. She is currently a Lecturer at Northwest A&F University. Her main research interests include transient characteristics of HVdc systems, modular multilevel converters, and its application in HVdc systems.

Shengchang Ji was born in Shandong, China in 1976. He received the B.Sc. and Ph.D. degrees in electrical engineering from Xi'an Jiaotong University, China in 1998 and 2003, respectively. Presently he is a Professor in Xi'an Jiaotong University, Xi'an, China. His research work covers condition monitoring of

power equipments in HVDC application.

**Francesco. Iannuzzo** received the M.Sc. degree in Electronic Engineering and the Ph.D. degree in Electronic and Information Engineering from the University of Naples, Italy, in 1997 and 2002, respectively. He is currently a professor of reliable power electronics at the Aalborg University, Denmark, where he is also part

of CORPE, the Center of Reliable Power Electronics. His research interests are in the field of reliability of power devices, condition monitoring, failure modelling and testing up to megawa`tts under extreme conditions. He is author or co-author of +250 publications on journals and international conferences,

three book chapters and four patents, and has edited a book on Modern Power Electronic Devices (2020, IET). Besides the publication activity, over the past years he has been contributing +20 technical seminars about reliability at top-tier conferences as ISPSD, IRPS, EPE, ECCE, PCIM and APEC. Prof. Iannuzzo currently serves as the vice-chair of the IEEE IAS Power Electronic Devices and Components Committee. In 2018 he was the general chair of the 29<sup>th</sup> ESREF, the first European conference on the reliability of electronics, and has recently been appointed general chair for the 2023 EPE-ECCE Europe conference in Aalborg.