# **Aalborg Universitet**

Medium-Voltage Megawatt Power-Electronic-Based Grid Emulators: Testing Capability Requirements and Dynamics Challenges – A Review

Li, Zejie; Zhao, Fangzhou; Wang, Xiongfei; Munk-Nielsen, Stig; Geske, Martin; Grune, Rayk; Bo Rønnest Andersen, Daniel; Garnelo Rodriguez, Miguel

I E E E Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2023.3268449

Publication date: 2023

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Li, Z., Zhao, F., Wang, X., Munk-Nielsen, S., Geske, M., Grune, R., Bo Rønnest Andersen, D., & Garnelo Rodriguez, M. (2023). Medium-Voltage Megawatt Power-Electronic-Based Grid Emulators: Testing Capability Requirements and Dynamics Challenges – A Review. *I E E Journal of Emerging and Selected Topics in Power Electronics*, 1-15. https://doi.org/10.1109/JESTPE.2023.3268449

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Medium-Voltage Megawatt Power-Electronic-Based Grid Emulators: Testing Capability Requirements and Dynamics Challenges – A Review

Zejie Li, *Student Member, IEEE*, Fangzhou Zhao, *Member, IEEE*, Xiongfei Wang, *Fellow, IEEE*, Stig Munk-Nielsen, *Member, IEEE*, Martin Geske, Rayk Grune, Daniel Bo Rønnest Andersen and Miguel Garnelo Rodriguez

Abstract- Power-electronic-based grid emulators are emerging as a promising way to test the grid-code compliance of renewable energy resources. Yet, the ever-increasing power and voltage levels of device under test pose new requirements and challenges to power-electronic-based grid emulators. This paper first gives an overview of testing capability requirements based on the recent grid codes and standards, then discusses the resulted dynamic interactions and solutions for power-electronic-based grid emulators. Perspectives on the open issues and emerging trends of grid emulators are finally shared.

Index Terms—Grid emulator, grid-code requirements, testing, dynamic interactions.

### I. INTRODUCTION

P OWER-electronic-based grid emulators are increasingly used to test the grid-code compliance of renewable energy resources, energy storage systems, and power-to-x systems, etc. Over the past years, the power and voltage levels of these devices under test (DUTs) have been continuously increasing. For instance, beginning in 1980s with tens of kilowatts (kW) wind turbines (WTs), 16 megawatt (MW) WTs are deployed today in offshore wind power plants [1], [2], where the voltage level of collector systems increases up to 66 kV [3]. The rapid growth of renewable energy resources has driven the evolution of grid codes with more stringent requirements, e.g., DUTs may need to ride through the overvoltage up to 160% of the nominal grid voltage and 15 consecutive grid faults [4], [5]. These trends demand a

This work was supported by the Energy Technology Development and Demonstration Program (EUDP) for the project MERGE - Megawatt Scalable Versatile Grid Emulation System. (Corresponding author: Xiongfei Wang)

Zejie Li, Fangzhou Zhao, and Stig Munk-Nielsen are with the Department of Energy (AAU Energy), Aalborg University, Aalborg 9220, Denmark (e-mail: zl@energy.aau.dk; fzha@energy.aau.dk; smn@energy.aau.dk).

Xiongfei Wang is with the Division of Electric Power and Energy Systems, KTH Royal Institute of Technology, Stockholm 11428, Sweden, and also with the Department of Energy (AAU Energy), Aalborg University, Aalborg 9220, Denmark (e-mail: xiongfei@kth.se; xwa@energy.aau.dk).

Martin Geske is with GE Power Conversion, Berlin, Germany (e-mail: martin.geske@ge.com).

Rayk Grune is with R&D Test Systems A/S, Berlin, Germany (e-mail: rgr@rdas.dk).

Daniel Bo Rønnest Andersen and Miguel Garnelo Rodriguez are with R&D Test Systems A/S, Hinnerup, Denmark (e-mail: dra@rdas.dk; mgr@rdas.dk).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org

scalable and versatile grid emulator, which not only can accommodate the increasing voltage and power levels of DUTs but is also able to test compliances of DUTs with the evolving grid-code requirements.

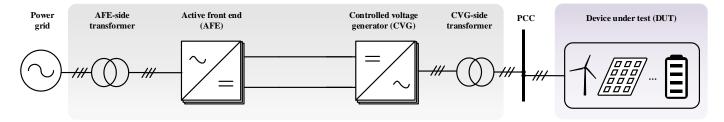

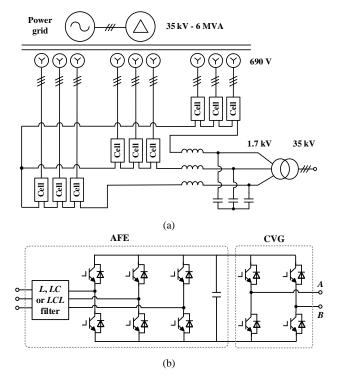

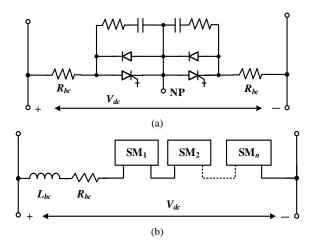

Fig. 1 shows a general diagram of power-electronic-based grid emulators, which is commonly built on a back-to-back power conversion system with an active-front end (AFE) and a controlled voltage generator (CVG) [3]. For scalability, AFE and CVG are generally composed by series/ parallel connected modular power converters, such as the cascaded or interleaved neutral point clamped (NPC) converter [6]-[10], the cascaded H-bridge (CHB) converter [11]-[13], and the modular multilevel converter (MMC) [14]-[17]. Those topologies typically employ several neutral-point (NP), cell or submodule (SM) capacitors as the energy buffer of the power conversion, where low-frequency fluctuations of capacitor voltages are actively regulated, introducing internal dynamics into grid emulators [13], [14], [18]. The internal dynamics can interact with the external dynamics of CVG when emulating transient events, causing voltage imbalance or even over-/under-voltage of the internal capacitors, which may, in turn, adversely affect the testing capabilities of CVG, such as the synthesis of harmonic voltages and the emulation of varying grid impedance during a fault ride-through (FRT) test [16].

Besides the dynamic interactions within CVG, the external control of CVG may also interact with the AFE through the dc link of grid emulators, and with the control dynamics of DUT, posing multifold challenges to the dynamics of grid emulators. In [12], [19], [20], it has been reported that an FRT test by CVG may result in the over-/ under-voltage at the common dc link, which can cause the overmodulation or even instability of CVG. In addition, the time delay involved in the digital control system can introduce a negative resistance into the output impedance of CVG and DUT, which may destabilize their interactions [3], [21].

This paper thus provides a review of testing capability requirements and dynamics challenges for power-electronic-based grid emulators. First, the testing capability requirements for a versatile grid emulator are formulated based on the latest updates of grid codes and standards. Following the testing capability requirements, a systematic discussion is then presented on dynamic interactions that may occur within the grid emulator, as well as between the grid emulator and DUT.

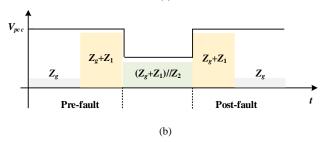

Fig. 1. General system diagram of power-electronic-based grid emulators.

Fig. 2. Testing capability requirements of grid emulators, which are built on the latest updates of grid codes and standards.

The challenges posed by these dynamic interactions and the state-of-the-art solutions to address them are thoroughly examined. The open issues that require further research to overcome the dynamic challenges are then identified. Lastly, insights on the future prospects of testing capabilities for grid emulators are shared.

# II. TESTING CAPABILITY REQUIREMENTS

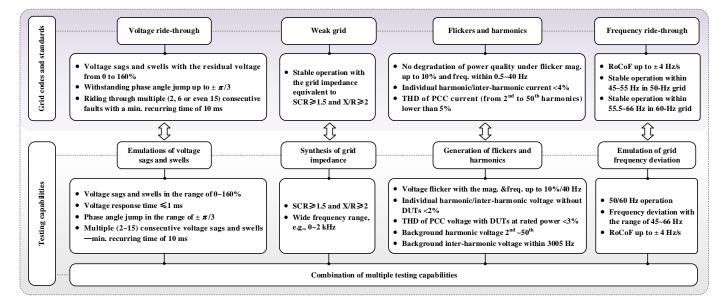

This section discusses the testing capability requirements of grid emulators in five aspects, as illustrated in Fig. 2. All are built on the latest updates of grid codes and standards.

# A. Emulations of Voltage Sags and Swells

1) Depth, duration time and response time: DUTs should ride through undervoltage and overvoltage faults following the recent requirements, e.g., IEC 61400-21 [22], IEEE 1547.1 [23], IEEE 2800 [24], FGW TR3 [25], DNV-GL TN066 [26] and national grid codes [4], [27]-[33]. Table I summarizes these low-voltage ride-through (LVRT) and high-voltage ride-through (HVRT) requirements with regards to the minimum time duration of DUTs operating under different residual voltages at the point of common coupling (PCC). It is important for a grid emulator to cover the full range of voltage sags/swells and operate continuously with DUTs within the required duration time.

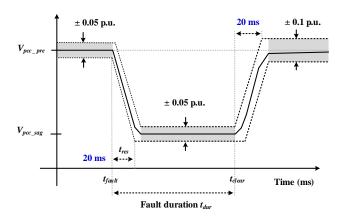

Fig. 3 depicts the allowed tolerances on the root-mean-

TABLE I LVRT AND HVRT REQUIREMENTS FOR DUTS

| Types | Residual voltage ( $V_{pcc}/V_N$ ) | Duration time [ms] |  |

|-------|------------------------------------|--------------------|--|

|       | < 0.05                             | ≥150               |  |

| LVRT  | 0.20-0.30                          | ≥625               |  |

|       | 0.45-0.60                          | ≥1371              |  |

|       | 0.70-0.80                          | ≥2389              |  |

|       | 0.85-0.90                          | ≥60000             |  |

| HVRT  | 1.10-1.15                          | ≥10000             |  |

|       | 1.20-1.25                          | ≥1000              |  |

|       | 1.25-1.30                          | ≥500               |  |

|       | 1.30-1.60                          | ≥50                |  |

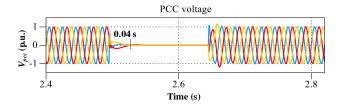

square (RMS) value of the positive sequence voltage at the PCC in an LVRT test [22]. This requirement is commonly followed by the existing grid emulators to generate voltage sags within the response time of  $t_{res}$ =20 ms. Similarly, the response time of reproducing voltage swells for HVRT tests is also within 20 ms [22]. Yet, to reproduce a real-world fault, a more stringent requirement on the response time of  $t_{res}$ =1 ms is imposed by DNV for grid emulators [6], [26].

Fig. 3. The allowed tolerances on the RMS value of the positive sequence voltage for grid emulators in an LVRT test [22].

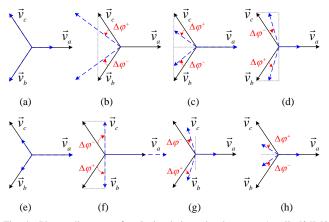

Fig. 4. Phasor diagrams of typical unbalanced voltage sags/swells [34]-[36]. (a) Single-phase-to-ground fault. (b) Single-phase-to-ground fault in the isolated neutral system. (c) Phase-to-phase fault. (d) Single-phase-to-ground fault after two  $\Delta\text{-Y}$  transformers. (e) Two-phase-to-ground fault. (f) Two-phase-to-ground fault in the isolated neutral system. (g) Two-phase-to-ground fault after one  $\Delta\text{-Y}$  transformer. (h) Two-phase-to-ground fault after two  $\Delta\text{-Y}$  transformers.

- 2) Phase jump: Fig. 4 shows the phasor diagrams of eight typical unbalanced voltage sags/swells [34]-[36], where  $\vec{v}_a$ ,  $\vec{v}_b$  and  $\vec{v}_c$  are three-phase voltage vectors.  $\Delta \phi^+$  and  $\Delta \phi^-$  represent the angles of phase jump. The phase jump often occurs in a phase-to-phase fault and during fault propagation of phase-to-ground faults. The maximum angle of phase jump in an unbalanced fault is  $\pm \pi/3$ . For the phase jump in balanced faults, DUTs must also be able to ride through a maximum angle of phase jump of  $\pm \pi/3$  [5]. Therefore, a grid emulator should be able to reproduce the phase-jump angle in the range of  $\pm \pi/3$ .

- 3) Multiple consecutive voltage sags and swells: Table II lists typical multiple-fault ride-through (MFRT) requirements for DUTs [5], [29], [37]. In the Danish grid codes, DUTs must withstand at least two/six consecutive faults during 2-min/5-min intervals, with each fault lasting 100 ms and followed by a new fault after 300-500 ms [29]. Recently, a more stringent requirement is imposed by AEMO, i.e., DUTs must ride through 15 consecutive balanced and unbalanced faults, of which, the recurring time between the first 8 faults is as low as 10 ms [5], [37]. Thus, grid emulators should operate stably

TABLE II MFRT REQUIREMENTS FOR DUTS

| Grid<br>codes | Numbers of faults                |   | Duration of each fault [ms] | Recurring time [ms]                  |

|---------------|----------------------------------|---|-----------------------------|--------------------------------------|

| Danish        | At least 2 times<br>within 2 min |   | 100                         | 300-500                              |

|               | At least 6 times<br>within 5 min |   | 100                         | 300-500                              |

| AEMO          | 15 times<br>within 1 min         | 8 | 120                         | 2*10, 2*200<br>2*500, 750<br>1000    |

|               |                                  | 6 | 220                         | 1500, 2*2000,<br>3000, 5000,<br>7000 |

|               |                                  | 1 | 430                         | 10000                                |

when reproducing 15 consecutive voltage sags and swells, even if the minimum interval between each fault is lower than 10 ms.

# B. Synthesis of Grid Impedance

The power grid is generally emulated as a voltage source behind a grid impedance, which is either constant or frequency-dependent, composed by resistance, inductance or capacitance (*RLC*), or various combinations of *RLC* [10]. DUTs can interact with a weak (high-impedance) grid, causing harmonic instability issues [38]. Hence, grid operators specify several metrics to reflect the grid strength for assessing the stability of DUTs in weak grids [22], [24].

The short-circuit ratio (SCR) is a commonly used metric [24], which is defined as

$$SCR = \frac{S_f}{P_{dN}} = \frac{V_g^2}{P_{dN}} \times \frac{1}{Z_g} = \frac{1}{Z_{g \text{ p.u.}}}$$

(1)

where  $S_f$  and  $P_{dN}$  represent the short-circuit power of grid and the active power rating of grid-connected devices.  $V_g$  and  $Z_g$  denote the ideal grid voltage and grid impedance.  $Z_{gp.u.}$  is the per-unit (p.u.) value of grid impedance.

In addition, the X/R ratio is another critical parameter for the grid impedance. In the FGW TR3, DUTs are required to stably operate at a minimum SCR of 2 and an X/R ratio of at least 3 [7], [39]. Recently, a more stringent requirement has been introduced by AEMO, i.e., the minimum SCR and X/R ratio are reduced to 1.5 and 2, respectively [40].

Therefore, a grid emulator should be able to synthesize the grid impedance with  $SCR \ge 1.5$  and  $X/R \ge 2$ . However, differing from synchronous generators, the short-circuit capacity of a power-electronic-based grid emulator is limited by the overloading capability of power semiconductor devices. As a result, the short-circuit capacity of grid emulator may not fully reflect the grid strength. Instead, the  $SCR = 1/Z_{gp.u.}$  is merely used to indicate the impedance synthesized by grid emulators in practice. For example, an "infinite" SCR, i.e., the ideally stiff grid, is realized in a 7 MVA grid emulator by setting  $Z_{gp.u.} = 0$  [6].

It is worth noting that a common practice is to use the SCR and the X/R ratio to define the impedance profile at the

fundamental frequency. However, to fully reproduce the grid-DUT interactions, the grid impedance emulation needs to cover a wide frequency range, e.g., 0~2 kHz [10], [41], due to the wide-timescale control dynamics of DUT.

# C. Generation of Flickers and Harmonics

1) Voltage flickers: When low-frequency (i.e., 0.5 Hz~40 Hz) voltage fluctuations within 10% of normal voltage occur at the PCC, DUTs are required to maintain stable operation without deteriorating the power quality of the power grid [22], [42]. To assess the impact of such voltage flicker on DUTs, a typical voltage reference for a grid emulator is given by

$$V_{j_{-ref}} = \left[1 + A_m \sin(2\pi f_m t)\right] V_N \sin(2\pi f_1 t + \varphi_j)$$

(2)

where  $A_m$  and  $f_m$  are the magnitude of voltage fluctuation and flicker frequency, respectively.  $f_1$  and  $\varphi_j$  are the fundamental frequency and initial phase angle. Generally,  $f_m$  ranges from 0.5 Hz to 40 Hz and  $A_m$  is lower than 10% [22], [42].

- 2) Total harmonic distortion (THD) with and without DUTs: The current harmonic emissions of DUTs should comply with grid-code requirements, which specify that the individual harmonic distortion and the THD (from  $2^{nd}$  to  $50^{th}$  harmonics) of PCC current must be lower than 4% and 5%, respectively [24]. In addition, the non-integer harmonic (inter-harmonic) current between  $hf_1\pm 5$  Hz should be also within 4%, where h is the individual harmonic order [24]. However, the switching operation of a power-electronic-based grid emulator may lead to additional current harmonics. Thus, IEEE 1547.1 requires that the individual harmonic and inter-harmonic voltage distortion of the grid emulator without DUTs must not exceed 2% [23]. Further, when a grid emulator is operating with DUTs in steady state at rated power, the THD of PCC voltage should be lower than 3% [23].

- *3) Background harmonic voltage:* For on-site operation of a DUT, the THD of PCC current is influenced by dynamic interactions between the DUT and the power grid [24]. To reproduce this impact of background grid voltage harmonics on DUTs, a grid emulator should be able to synthesize the harmonic voltages covering 2<sup>nd</sup>~50<sup>th</sup> and inter-harmonic voltages up to 3005 Hz [22], [24]. The specific harmonic magnitudes are commonly provided by grid operators.

# D. Emulation of Grid Frequency Deviation

Table III summarizes the typical requirements of operating frequency range and maximum rate of change of frequency (RoCoF) that DUTs shall not trip [4], [29]. To evaluate the active power responses of DUTs under the grid-frequency dynamics, a grid emulator needs to operate continuously at  $45\sim66$  Hz and generate a RoCoF up to  $\pm4$  Hz/s.

# E. Combination of Multiple Testing Capabilities

In actual power grids, the simultaneous changes of voltage magnitude, impedance, frequency, phase angle and harmonics may occur. The combination of multiple testing capabilities is, therefore, important for a grid emulator.

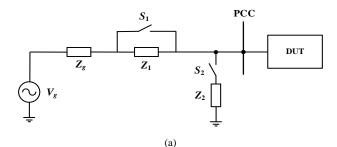

A conventional solution is based on the shunt impedance as shown in Fig. 5(a) [22], where  $Z_g$ ,  $Z_1$  and  $Z_2$  are the grid impedance, series impedance and fault impedance. Fig. 5(b) shows the time sequence of the voltage-magnitude changes and the impedance variation [7], [43], [44]. Hence, the MFRT

TABLE III

OPERATING FREQUENCY RANGE AND MAX ROCOF FOR DUTS

| Fundamental frequency (Hz) | Operating frequency range (Hz) |     | Max RoCoF |

|----------------------------|--------------------------------|-----|-----------|

|                            | Min                            | Max | (Hz/s)    |

| 50                         | 45                             | 55  | ±4        |

| 60                         | 55.5                           | 66  | ±4        |

test can be realized by shunting multiple impedances [5]. The drawback of this method is the extensive energy loss as the power capacity of DUT increases. In contrast, a power-electronic-based grid emulator can reduce the loss with more controllability to follow the principle shown in Fig. 5(b).

For three-phase balanced fault emulation, the relationship between emulated impedance and residual voltage at the PCC is expressed as [5]

$$\frac{V_{pcc\_sag}}{V_g} = \frac{Z_2}{Z_g + Z_1 + Z_2} \tag{3}$$

where  $V_{pcc\_sag}$  is the residual voltage at the PCC.

Further, the voltage-magnitude change and impedance variation are often accompanied by a phase jump in unbalanced faults [44]. In Fig. 5(a), the fault depth and phase jump are inherently dependent on the size and X/R ratio of  $Z_g$ ,  $Z_1$  and  $Z_2$ . For a power-electronic-based grid emulator, correct input references of voltage and impedance are critical to the emulation of unbalanced faults. Taking the phase-to-phase fault in Fig. 4 (c) as an example, the three-phase voltage vectors and angles of phase jump are given by [45]

$$\begin{cases} \vec{v}_{a} = V_{g} \\ \vec{v}_{b} = 0.5 \left( -1 - j\sqrt{3}K_{f} \right) V_{g} \\ \vec{v}_{c} = 0.5 \left( -1 + j\sqrt{3}K_{f} \right) V_{g} \end{cases}$$

(4)

Fig. 5. Typical co-emulation of voltage sags with impedance variation. (a) Shunt-impedance-based grid emulator [22]. (b) Time sequence of impedance variation and voltage-magnitude changes [7].

$$\Delta \varphi^+ = -\arctan\left(\sqrt{3}K_f\right) + \pi/3 \tag{5}$$

$$\Delta \varphi^{-} = \arctan\left(\sqrt{3}K_{f}\right) - \pi/3 \tag{6}$$

where  $K_f$  is the fault factor related to the depth of voltage sags. Consequently, the input voltage-magnitude references for a grid emulator are derived as

$$\begin{cases} v_a(t) = V_g \cos\left(2\pi f_1 t\right) \\ v_b(t) = 0.5\sqrt{1 + 3K_f^2} V_g \cos\left[2\pi f_1 t + \arctan\left(\sqrt{3}K_f\right) - \pi\right] \\ v_c(t) = 0.5\sqrt{1 + 3K_f^2} V_g \cos\left[2\pi f_1 t - \arctan\left(\sqrt{3}K_f\right) + \pi\right] \end{cases}$$

(7)

Besides, according to the sequence decomposition theory [46], the relationship between the required input reference of fault impedance and fault factor is expressed as

$$Z_{2} = \frac{K_{f}}{1 - K_{f}} \left( Z_{g} + Z_{1} \right) \tag{8}$$

The combination of other testing capabilities, e.g., the emulation of impedance, frequency deviation and harmonics, is of important for next-generation versatile grid emulators.

### III. DYNAMIC INTERACTIONS AND SOLUTIONS

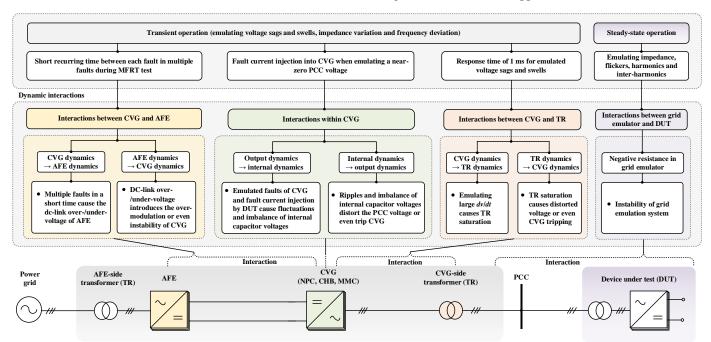

Fig. 6 illustrates four types of dynamic interactions that challenge the dynamic performance of grid emulators. This section first describes how the latest testing capabilities give rise to these dynamic interactions, and then thoroughly discusses state-of-the-art solutions to address them.

A. Interactions Within CVG Caused by Fault Current Injection of DUT

In FRT tests, the fault current injected by the type-4 WTs and the type-3 WTs can be up to 2 p.u. and 7 p.u., respectively [47]. The fault-current injection brings internal-external

dynamic interactions in three typical grid emulators, i.e., the cascaded/interleaved NPC-, CHB- and MMC-based grid emulators. The emulated PCC voltage and fault current may result in distorted and different charging/ discharging currents of NP/cell/SM capacitors, causing their voltage fluctuations and imbalance. In turn, the ripple and imbalance of these internal capacitor voltages may further disturb ac output dynamics or even trip the CVG.

The impact of internal capacitor voltage fluctuations on the external output of CVG can be mitigated by feeding these capacitor voltages forward to the modulation link of CVG [12], [15], [16]. In respect to the voltage imbalance in the internal capacitors, the NPC-, CHB-based grid emulators differ from the MMC-based grid emulators.

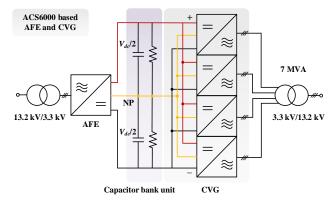

- 1) Cascaded/ interleaved NPC: The commercial ACS6000 [6], [48], [49] or MV7000 [8], [50] converters are generally employed in NPC-based grid emulators. The NP capacitors in these converters are often paralleled with resistors to balance capacitor voltages. Further, the vector regulation and injecting zero-sequence voltage in modulation are common practices in NPC converters to mitigate voltage imbalance in the NP capacitors [18]. Fig. 7 shows a commercial grid emulator [49], where both the AFE and CVG share a single NP, enhancing the control flexibility of NP capacitor voltages [51]. Hence, the problems driven by voltage imbalance of NP capacitors have not been previously reported in commercial NPC-based grid emulators [6]-[10], [48]-[50].

- 2) CHB: Fig. 8 shows a commercial CHB-based grid emulator, which is composed by an input multi-winding transformer, nine H-bridge cells, ac filters and an output transformer [12]. Each cell is supported by an individual three-phase AFE converter, utilizing the same dc-link voltage control. Thus, each AFE converter can be equivalent as a dc voltage source, which can suppress the common-mode current

Fig. 6. Dynamic interactions for a scalable and versatile power-electronic-based grid emulator.

Fig. 7. A commercial NPC-based grid emulator [49].

Fig. 8. A commercial CHB-based grid emulator [12]. (a) General structure. (b) Cell topology.

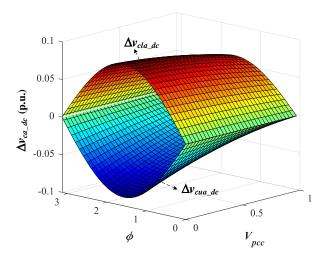

Fig. 9. Relationship among dc component variations of SM capacitor voltages, PCC voltage  $V_{pcc}$  and power factor angle  $\varphi$  [17].

sharing between the H-bridge arms [51], [52]. Therefore, the voltage imbalance issues in cell capacitors can be addressed in CHB-based grid emulators [11]-[13], [53].

3) MMC: The MMC is emerging as a promising topology for the medium-voltage MW grid emulator, thanks to its modularity and scalability. The MMC-based grid emulator typically employs 5~20 floating SMs per arm to achieve a 3.3 kV~13.8 kV output at the inverter side [17], [54]. In [17], an average model of the floating SM capacitor voltages during the LVRT test has been established. The SM capacitor voltages of upper arm and lower arm in phase-a are expressed as [17]

$$v_{cua} = V_c + \frac{1}{C_{sm}} \int_{t_0}^{t} n_{ua} i_{ua} dt$$

$$= V_c + \frac{V_{dc}}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} \frac{I_o}{2} \sin(\omega_1 t - \varphi) - \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{f_{cua}(t)}{\Delta v_{cus_- ac}} \int_{\Delta v_{cus_- ac}}^{t} n_{la} i_{la} dt$$

$$v_{cla} = V_c + \frac{1}{C_{sm}} \int_{t_0}^{t} n_{la} i_{la} dt$$

$$= V_c + \frac{V_{dc}}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{f_{cla}(t)}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{f_{cla}(t)}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{f_{cla}(t)}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{f_{cla}(t)}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

$$= V_c + \frac{V_{cla}(t)}{2NV_c \omega_1 C_{sm}} \begin{bmatrix} -\frac{I_o}{2} \sin(\omega_1 t - \varphi) + \frac{m^2 I_o \cos \varphi}{4} \sin(\omega_1 t) \\ -\frac{mI_o}{8} \sin(2\omega_1 t - \varphi) \end{bmatrix}_{t_0}^{t}$$

where  $n_{ua}/n_{la}$  and  $i_{ua}/i_{la}$  are the insertion index of SMs and arm current in upper and lower arms, respectively.  $V_c$  and  $C_{sm}$  denote the rated voltage and capacitance of SM capacitors. N and  $V_{dc}$  represent the number of SMs per arm and the dc-link voltage. m is the modulation index, which is dependent on the emulated  $V_{pcc}$ .  $I_o$  and  $\varphi$  are the PCC current and power factor angle.  $t_0$  is the instant of maximum transient fault current.  $\Delta v_{cua\_ac}/\Delta v_{cla\_ac}$  and  $\Delta v_{cua\_dc}/\Delta v_{cla\_dc}$  denote the ac fluctuation and the dc component variation of SM capacitor voltages, respectively.

Fig. 9 shows the relationship among  $\Delta v_{cua\_dc}/\Delta v_{cla\_dc}$ ,  $V_{pcc}$  and  $\varphi$  [17]. The sign of  $\Delta v_{cua\_dc}$  and  $\Delta v_{cla\_dc}$  is converse, which means the voltage imbalance of SM capacitors between the upper and lower arms. Further, the difference between  $\Delta v_{cua\_dc}$  and  $\Delta v_{cla\_dc}$  becomes larger as the emulated  $V_{pcc}$  decreases, causing over-/under-voltage of SM capacitors or even tripping the grid emulator.

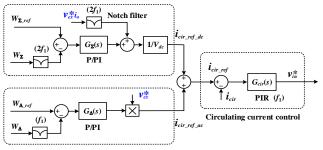

To handle the imbalance and fluctuation of SM capacitor voltages on the output dynamics of MMC-based CVG, the closed-loop modulation is a practical solution, i.e., the controlled arm voltage divided by the sum of SM capacitor voltage per arm [55]. Yet, the energy-based phase and arm balancing control have to be employed to ensure system stability, as shown in Fig. 10 [14]. The phase balancing control is used to produce the dc component of the circulating current to regulate the average SM capacitor voltage. By multiplying the external control output  $v_{ex}^*$ , the arm balancing

#### Energy-based phase balancing control

Energy-based arm balancing control

Fig. 10. Energy-based internal control scheme for MMC-based CVG [14].

Fig. 11. CHIL-based experimental setup.

Table IV PARAMETERS OF THE MMC-BASED GRID EMULATOR

| Symbol             | Meaning                                         | Realistic value         | CHIL value              |

|--------------------|-------------------------------------------------|-------------------------|-------------------------|

| $V_{pccll}$        | PCC voltage (l-l, rms)                          | 11 kV (1 p.u.)          | 11 kV (1 p.u.)          |

| $V_{dc}$           | DC-link voltage                                 | 12 kV                   | 12 kV                   |

| $P_o$              | Rated power of DUT                              | 4 MVA<br>(1 p.u.)       | 4 MVA<br>(1 p.u.)       |

| $L_{arm}$          | Arm inductance                                  | 9.8 mH<br>(0.1 p.u.)    | 9.8 mH<br>(0.1 p.u.)    |

| N                  | SM number per arm                               | 16                      | 4                       |

| $C_{sm}$           | SM capacitance                                  | 4 mF                    | 1 mF                    |

| $C_{eq}$           | Equivalent capacitance of each arm $C_{sm}/N$   | 0.25 mF                 | 0.25 mF                 |

| $f_{sa}$           | Sampling frequency                              | 10 kHz                  | 10 kHz                  |

| $f_c$              | Carrier frequency                               | 500 Hz                  | 2 kHz                   |

| $f_{sw}$           | Equivalent switching frequency 2Nf <sub>c</sub> | 16 kHz                  | 16 kHz                  |

| $a_{\nu}$          | Bandwidth of ac voltage control                 | $3000\pi \text{ rad/s}$ | $3000\pi \text{ rad/s}$ |

| $lpha_\Sigma$      | Bandwidth of phase balancing control            | $80\pi \text{ rad/s}$   | $80\pi \text{ rad/s}$   |

| $lpha_{\Delta}$    | Bandwidth of arm balancing control              | $40\pi \text{ rad/s}$   | $40\pi \text{ rad/s}$   |

| $\alpha_{cir\_dc}$ | Bandwidth of $i_{cir\_dc}$ control              | $600\pi \text{ rad/s}$  | $600\pi \text{ rad/s}$  |

| $\alpha_{cir\_ac}$ | Bandwidth of $i_{cir\_ac}$ control              | $100\pi \text{ rad/s}$  | $100\pi \text{ rad/s}$  |

control can generate a fundamental-frequency circulating current to balance the SM capacitor voltages between the upper and lower arms [14], [15]. In this case, the insertion index and arm currents can be expressed as

$$n_{ua} \approx \frac{V_{dc}}{2NV} \left[ 1 - m\cos(\omega_{l}t) \right]$$

(11)

$$n_{la} \approx \frac{V_{dc}}{2NV} \left[ 1 + m\cos(\omega_1 t) \right]$$

(12)

$$i_{ua} = I_{cir\_dc} + \frac{1}{2}I_o\cos(\omega_1 t + \varphi) + I_{cir\_ac}\cos(\omega_1 t + \varphi_c) \quad (13)$$

$$i_{la} = I_{cir\_ac} - \frac{1}{2} I_o \cos(\omega_1 t + \varphi) + I_{cir\_ac} \cos(\omega_1 t + \varphi_c)$$

(14)

where  $I_{cir\_ac}$  and  $\varphi_c$  are the magnitude and phase angle of injected fundamental-frequency circulating current.  $I_{cir\_dc}$  is the dc component of circulating current.

The charging and discharging current of SM capacitors in the upper and lower arms are given by

$$n_{ua}i_{ua} = \frac{V_{dc}}{2NV_c} \begin{bmatrix} I_{cir\_dc} - \frac{mI_o}{4}\cos(\varphi) - \frac{mI_{cir\_ac}}{2}\cos(\varphi_c) \\ + \frac{1}{2}I_o\cos(\omega_l t + \varphi) + I_{cir\_ac}\cos(\omega_l t + \varphi_c) \\ -mI_{cir\_dc}\cos(\omega_l t) - \frac{mI_o}{4}\cos(2\omega_l t + \varphi) \\ - \frac{mI_{cir\_ac}}{2}\cos(2\omega_l t + \varphi_c) \end{bmatrix}$$

(15)

$$n_{la}i_{la} = \frac{V_{dc}}{2NV_{c}} \begin{bmatrix} I_{cir\_ac} - \frac{mI_{o}}{4}\cos(\varphi) + \frac{mI_{cir\_ac}}{2}\cos(\varphi_{c}) \\ -\frac{1}{2}I_{o}\cos(\omega_{1}t + \varphi) + I_{cir\_ac}\cos(\omega_{1}t + \varphi_{c}) \\ +mI_{cir\_ac}\cos(\omega_{1}t) - \frac{mI_{o}}{4}\cos(2\omega_{1}t + \varphi) \\ +\frac{mI_{cir\_ac}}{2}\cos(2\omega_{1}t + \varphi_{c}) \end{bmatrix}$$

(16)

Thus, the injected ac circulating current exhibits opposite dc charging/discharging currents to balance the SM capacitor voltages of the upper and lower arms. According to Fig. 10, injected  $I_{cir\_ac}$  becomes to zero once the SM capacitor voltages are balanced. However, the balancing effect is weaker as the emulated voltage, i.e., m and  $v_{ex}^*$ , decreases.

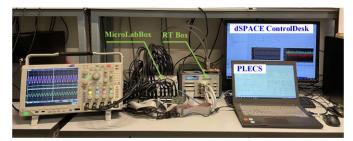

Fig. 11 depicts a controller-hardware-in-the-loop (CHIL)-based experimental setup and Table IV shows an example of parameters for both realistic and simulated MMC-based grid emulators [17]. The control system of MMC is distributed in the MicroLabBox, while the power circuit of MMC with 4 full-bridge submodules per arm and a grid-following DUT system are arranged in the RT Box.

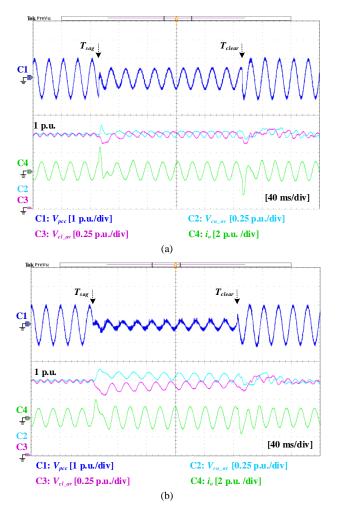

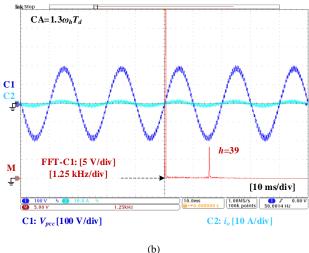

Fig. 12 shows experimental results of an MMC-based grid emulator during LVRT tests [17].  $V_{cu\_av}$  and  $V_{cl\_av}$  are the average SM capacitor voltages of the single-phase upper and lower arms.  $i_o$  is the output current of the DUT. It is clear that the transient fault current injected by DUT causes the voltage imbalance of SM capacitors. The balancing effect of SM capacitor voltages between upper and lower arms becomes weaker as the emulated PCC voltage decreases. Addressing this issue requires a deliberate tuning of parameters for the

Fig. 12. The CHIL experimental results of an MMC-based grid emulator during LVRT tests. (a)  $V_{pcc}$ =0.5 p.u. during fault. (b)  $V_{pcc}$ =0.2 p.u. during fault.

arm balancing control or the injection of the fundamental-frequency circulating current [55].

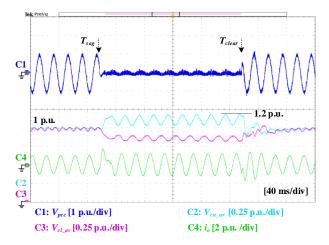

# B. Interactions Between CVG and AFE During MFRT Test

In FRT tests, the DUT should inject reactive current within 20 ms to support the PCC voltage, while the active current delivered to the grid emulator is immediately reduced [29]. Consequently, the dc current flowing into the AFE drops correspondingly, causing an overvoltage of the dc link due to the inability of power to suddenly change, at the instant of the emulated fault [13], [20]. Similarly, the dc-link voltage of AFE generally shows undervoltage after clearing the emulated fault. An over-/under-voltage at the dc link may cause overmodulation of the CVG, leading to the voltage distortion at the PCC or even instability [56].

To mitigate the over-/under-voltage, the dc-link voltage control and ac current control are commonly adopted in AFE [12], [13], [53]. Due to the limitation of the AFE control bandwidth, the settling time of dc-link voltage in grid emulators generally ranges from 20 ms to hundreds of milliseconds [13], [53]. By increasing the control bandwidth of AFE control for a settling time of 20~100 ms, it is possible to reproduce 6 consecutive faults, due to the fact that the time duration of a single fault is larger than 100 ms and the

Fig. 13. An LVRT test considering saturation of CVG-side transformer.

Fig. 14. Anti-saturation control configuration of transformer.

recurring time of each fault is greater than 300 ms [29].

# C. Interactions Between CVG and CVG-Side Transformer When Emulating Large dv/dt

To achieve a response time of voltage sag/swell less than 1 ms, the grid emulator should ensure that the slew rate (SR) of PCC voltage, i.e., dv/dt, can be up to 20 p.u./cycle (e.g., for a 50 Hz system) [6]. This high SR gives rise to the CVG-side transformer saturation due to the dc offset of magnetic flux [20], [57].

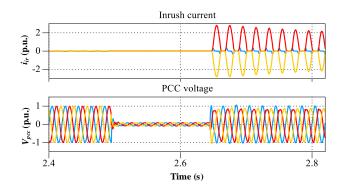

Fig. 13 demonstrates an LVRT test considering the core saturation of the CVG-side transformer. The magnetizing current of transformer, i.e., the inrush current, can be much higher than the nominal value, distorting the output voltage of CVG or even tripping the system.

Fig. 14 illustrates two anti-saturation control methods for grid emulators. They are 1) adding the flux estimator to inject the dc voltage component to counteract the dc offset [6], [48], [58], and 2) using a current feedforward control, e.g., based on a moving average filter with a proportional-integral (PI) controller, to eliminate the dc component of the transformer excitation current [59]. Although effective, the nonlinear dynamics of transformer and overlarge dv/dt during transient events complicate the design of these anti-saturation controls.

# D. Interactions Between Grid Emulator and DUT Under Steady-State Operation

For steady-state emulation of voltage magnitude, impedance, flickers, harmonics and inter-harmonics, the time delay in the digital control system can introduce a negative resistance (-R) of output impedance for a grid emulator [60], [61]. The -R may interact with the control system of DUT, causing harmonic instability problems [16], [38], [61].

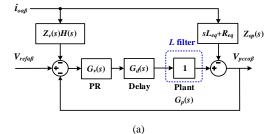

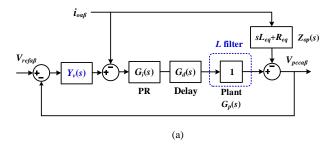

To regulate the voltage magnitude at PCC, a single-loop voltage-controlled inverter based on a fundamental-frequency resonant controller is adopted in [60], [61], where the sign of real part of output impedance  $Z_o$  is expressed as

$$\operatorname{sgn}\left\{\operatorname{Re}\left\{Z_{o}(j\omega)\right\}\right\} \approx \operatorname{sgn}\left\{-L_{s}K_{r_{1}}\cos\left(\omega T_{d}\right)\right\} \tag{17}$$

where sgn  $\{\cdot\}$  represents the sign function.  $L_s$  is the inductance of L filter.  $T_d$  and  $K_{r1}$  are the time delay and resonant gain. It implies a negative-resistance frequency region within  $1/(4T_d)$ . To address this issue, the dual-loop voltage control is usually used, where the sign of real part of output impedance is simplified as [60], [62]

$$\operatorname{sgn}\left\{\operatorname{Re}\left\{Z_{o}(j\omega)\right\}\right\} \approx \operatorname{sgn}\left\{K_{pc}\left(1 - K_{r1}L_{s}\right)\cos\left(\omega T_{d}\right)\right\} \quad (18)$$

where  $K_{pc}$  is the proportional gain of inner current control. Since  $K_{r1}L_s$  needs to be lower than 1 for internal stability [60], the -R appears in [1/(4 $T_d$ ),  $f_s$ /2], where  $f_s$ /2 is the Nyquist frequency. Thus, the inner current control can counteract the -R within 1/(4 $T_d$ ).

Similarly, the virtual impedance (VI) and single-loop voltage control (VC) are used for synthesizing impedance [43], [63], which can also provide damping to mitigate the -R within  $1/(4T_d)$ . However, as emulated impedance increases, -R within  $[1/(4T_d), f_s/2]$  becomes larger, which exacerbates the risk of high-frequency instability [64].

Regarding the emulation of voltage flickers, the reference in (2) can be expanded as [12]

$$V_{j_{-}ref} = V_{N} \sin(2\pi f_{1}t + \varphi_{j}) + 0.5V_{N}A_{m}\cos[2\pi(f_{1} - f_{m})t + \varphi_{j}] - 0.5V_{N}A_{m}\cos[2\pi(f_{1} + f_{m})t + \varphi_{j}]$$

$$(19)$$

Thus, a grid emulator must have accurate voltage control at the fundamental frequency  $(f_1)$  and two inter-harmonics  $(f_1-f_m)$  and  $f_1+f_m$  [12]. To emulate harmonics and inter-harmonics, resonant controllers are usually used with grid emulators [15], [65], [66]. Yet, the phase response of a resonant controller steps from  $\pi/2$  to  $-\pi/2$  at the harmonic frequency [67]. Consequently, the phase angle of output impedance at the harmonic frequency will shift  $\pi$  radians [61]. Considering the extra phase lag caused by  $T_d$ , -R is usually introduced around the harmonic frequency [61], [68].

To handle these control interactions posed by the -R, the impedance-passivity-based design method is an effective solution [69]. The general idea is to shape the output impedance with a non-negative real part, such that the control of a grid emulator does not destabilize system.

Several efforts have been made on the impedance passivity-based design of a single-loop voltage-controlled inverter, the active damping (AD) control based on the feedforward of output current is a simple solution. Yet, its effect relies on the ac filters. For instance, in the LC-filtered inverter, the passive region of output impedance can be extended to  $f_s/2$  [60]. Conversely, for the L-filtered inverter, the -R within  $[1/(4T_d), f_s/2]$  is not mitigated [61]. Additionally, the -R also appears within  $[1/(4T_d), f_s/2]$  for the voltage-magnitude emulation by the dual-loop voltage control [60] and the impedance emulation [63]. Thus, reducing time delay is a direct method to mitigate -R.

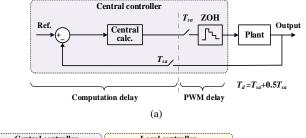

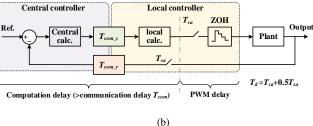

Fig. 15 shows the time-delay distribution of typical grid emulators, where two control structures are used, i.e., the

Fig. 15. Time-delay distribution of typical grid emulators [12], [49], [53], [54]. (a) Time delay in the centralized control structure. (b) Time delay in the distributed control structure.

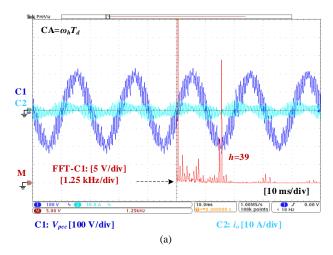

Fig. 16. Down-scaled experimental results of harmonic voltage emulation based on the resonant controller with different design of CAs. (a) Conventional design of CA. (b) Designed CA in [61].

centralized control and the distributed control [12], [49], [53], [54].  $T_{sa}$  and  $T_{com}$  are the sampling period and communication

delay [70]. The time delay consists of the computation delay  $(T_{sa})$  and the pulse width modulation (PWM) delay  $(0.5T_{sa})$  [71]. The difference of time delay in two control structures lies in different sampling periods. To reduce the time delay, increasing the sampling frequency is a simple way [72], [73]. Yet, it is limited by the computation of control algorithms and the communication delay. As a consequence, methods for compensating time delay are inevitable [74].

However, the time delay cannot be eliminated, which still introduces -R at certain harmonic frequencies when grid emulators perform the harmonic emulation based on resonant controllers [69]. To address this issue, the harmonic resonant controllers with phase-lead compensation angles (CAs) are commonly used [61], [68], [75]. However, the conventional design of CAs  $(\omega_h T_d)$  are not always effective to ensure the impedance passivity around harmonic frequencies, especially when the AD control is used. Fig. 16 presents experimental results of the harmonic voltage emulation based on resonant controllers with different design of CAs [61]. A conventional design of CA cannot guarantee system stability when passive loads are connected to the grid emulator. In [61], the alternative CAs for each resonator are selected based on the theory of linear fitting, which can achieve passive harmonic impedance till the critical frequency  $1/(4T_d)$ .

### IV. OPEN ISSUES AND EMERGING TRENDS

Following the review of state-of-the-art solutions, four open issues that require further research to address the challenges with dynamic interactions are discussed in this section. Then, perspectives on two emerging trends, i.e., the reproduction of low-frequency oscillations during FRT tests and the coemulation of multiple testing capabilities, are further shared.

# A. Open Issues

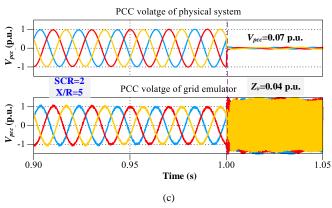

- 1) Balancing SM capacitor voltages of MMC-based grid emulators when emulating a zero voltage: Fig. 17 shows a CHIL experimental result for the MMC-based grid emulator during the zero-voltage ride-through test [17]. According to (15) and (16), injecting circulating current cannot introduce dc charging/ discharging current for SM capacitor voltages when emulating a zero voltage, i.e., m=0. The effective methods for balancing SM capacitor voltages are still missing.

- 2) Mitigation of dc-link over-/under-voltage during the emulation of 15 consecutive faults: In 15 consecutive faults, the recurring time in the first 8 faults is 10 ms, lower than the settling time for the dc-link voltage regulated by AFE, which trends to cause consecutive over-/under-voltage in the dc link [37], [40].

Enabling a dc-link chopper is a simple solution to prevent the dc-link overvoltage. Fig. 18(a) shows a commercial chopper based on an integrated gate commutated thyristor (IGCT) and resistors, which is generally used in NPC-based grid emulators [49]. Fig. 18(b) shows a modular chopper composed of series-connected SMs, a resistor and an inductor, which may be used in the MMC-based grid emulator [76]. Yet, installing a chopper in each cell of a CHB-based grid emulator is infeasible from the perspective of volume and footprint.

Increasing dc-link capacitance is a practical, albeit costly, solution to mitigate both overvoltage and undervoltage. Yet,

Fig. 17. The CHIL experimental result of the MMC-based grid emulator when emulating a zero voltage [17].

Fig. 18. DC-link choppers. (a) Commercial chopper for cascaded NPC-based grid emulators [49]. (b) Modular chopper for MMC-based grid emulators [76].

for the NPC- and CHB-based grid emulators, how to quantify dc-link capacitance to avoid undesired overdesign remains unclear.

In addition, there are no common dc-link capacitors in the MMC-based grid emulator [17], [54] and its equivalent dc-link capacitance  $C_{eq\_dc}$  is proportional to the SM capacitance divided by the number of SMs per arm [77]. Generally, dozens of SMs are typically employed to increase the number of output voltage levels for achieving low THD at the PCC [76], but it comes at the cost of a significant reduction in  $C_{eq\_dc}$ . To increase  $C_{eq\_dc}$ , larger capacitances of SMs may be required, which can dramatically increase the cost, footprint and volume of the grid emulator.

3) Anti-saturation of CVG-side transformer: Fig. 19 depicts the PCC voltage of CVG after using the anti-saturation control that is based on a current feedforward control. Limited by the bandwidth of anti-saturation control and the emulated high SR, the magnetic flux deviation is usually reduced within 40 ms to mitigate the transformer saturation [6], [48]. Yet, this causes the response time of voltage sag longer than the required 1 ms. There is, thus, a tradeoff between the speed of desaturating transformer-core and the required response time of voltage during the FRT test.

Fig. 19. PCC voltage of CVG after using the anti-saturation control based on a current feedforward control.

4) Mitigation of negative resistance when emulating multi-harmonics: The multi-resonant controller is often employed to synthesize multiple voltage harmonics [15], [65], [66]. It is shown in [67] that the lower-order resonant controller can introduce an additional phase lag to adjacent higher-order resonant controller. To address this issue, using a small and identical resonant gain for multi-harmonic resonant controller is a simple solution, yet it weakens the transient dynamics of harmonic voltage control [78]. Thus, a recursive design approach of resonant gains based on the gain margin of openloop gain is reported in [67]. Unfortunately, the -*R* may still appear around the harmonic frequencies [68]. A co-design the resonant gains and CAs of the multi-resonant controller is needed to prevent the -*R*.

# B. Emerging Trends

1) Reproduction of low-frequency oscillations during FRT tests: In actual grid faults, the transient overvoltage and low-frequency (<100 Hz) oscillations often occur at the PCC, especially for the grid with a low SCR at the post-fault process [64]. To reproduce these phenomena, it is important for a grid emulator to guarantee the accuracy of synthesized low-frequency impedance with low SCR.

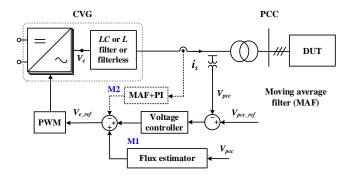

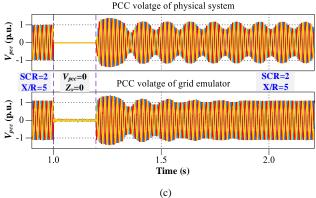

However, a grid emulator based on conventional VC and VI control commonly exhibits the inaccuracy of low-frequency impedance emulation [10], [63], [64]. Fig. 20 shows the control diagram and simulation results of a grid emulator with an L filter [64].  $Z_{op}(s)$  and  $Z_{v}(s)$  represent the open-loop impedance and VI.  $G_{v}(s)$  and H(s) denote the VC based on a proportional-resonant (PR) controller and a low-pass filter (LPF). The open-loop gain of the VC loop is

$$G_{opvc}(s) = \left(K_{pv} + \frac{K_{rv}s}{s^2 + \omega_1^2}\right) e^{-sT_d}$$

(20)

where  $K_{pv}$  and  $K_{rv}$  are the proportional gain and resonant gain of voltage controller.

To guarantee the internal stability of system, the gain margin (GM) and phase margin (PM) of  $G_{opvc}(s)$  should be larger than zero. Thus,  $K_{pv}$  and  $K_{rv}$  should satisfy

$$\begin{cases}

GM \approx -20 \lg \left[ \sqrt{\left(K_{pv}\right)^2 + \left(\frac{K_{rv}}{2\pi f_{cv}}\right)^2} \right] > 0 \\

PM \approx \pi - \arctan \left(\frac{K_{rv}}{2\pi K_{pv} f_{cv}}\right) - 2\pi f_{cv} T_d > 0

\end{cases} \Rightarrow \begin{cases}

K_{pv} < 1 \\

K_{rv} < \frac{\pi}{2T_d}

\end{cases} (21)$$

The output impedance of system is expressed as

$$Z_{GE}(s) = Z_{op}(s) + \frac{G_{opvc}(s)}{1 + G_{opvc}(s)} \left[ Z_{v}(s)H(s) - Z_{op}(s) \right]$$

(22)

At the low-frequency range, the time delay  $G_d(s)$  is close to

Fig. 20. The VC and VI control for impedance emulation in [64]. (a) Control diagram. (b) An LVRT test with post-fault SCR=3. (c) An LVRT test with post-fault SCR=2.

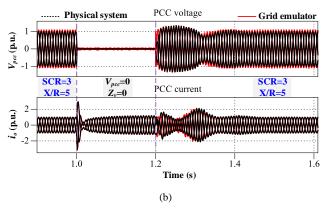

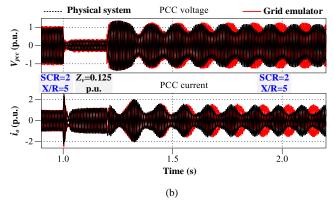

1 and  $G_v(s)$  approaches to  $K_{pv}$ . In (21), since  $K_{pv}<1$ , system closed-loop gain  $G_{opvc}(s)/[1+G_{opvc}(s)]$  is less than 1, which results in  $Z_{GE}(s)\neq Z_v(s)$ . The error of emulating impedance increases as the SCR decreases. Fig. 20 (b) and Fig. 20 (c) illustrate two LVRT tests with post-fault SCR=3 and SCR=2, respectively. Compared to the shunt-impedance-based LVRT test, the low-frequency oscillations under a lower SCR cannot be fully reproduced by the converter-based grid emulators.

To address this issue, the virtual admittance (VA) control and current control (CC) is introduced in [63], [64]. Fig. 21 shows the control diagram and simulation results of LVRT tests for the grid emulator with an L filter.  $Y_{\nu}(s)$  and  $G_{i}(s)$  represent the VA and PR controller based current control. The open-loop gain of the VA control is given by

$$G_{opva}(s) = \frac{1}{R_{o} + sL_{o}} \left( K_{pc} + \frac{K_{rc}s}{s^{2} + \omega_{1}^{2}} \right) e^{-sT_{d}}$$

(23)

where  $R_{\nu}$  and  $L_{\nu}$  are the virtual resistance and inductance.  $K_{pc}$  and  $K_{rc}$  are the proportional gain and resonant gain of CC.

Fig. 21. The CC and VA control for impedance emulation in [64]. (a) Control diagram. (b) An LVRT test with post-fault SCR=2. (c) Emulating  $V_{pcc}$ =0.07 p.u. with small impedance during fault.

Generally,  $K_{rc}$  exhibits minimal phase delay at the phase-crossover frequency  $f_{cva}$ , i.e.,  $K_{rc}/(2\pi f_{cva})=K_{pc}/(10\sim20)$  [79]. To assure internal stability of system,  $K_{pc}$  should satisfy

$$\begin{cases}

GM \approx -20 \lg \left[ \frac{K_{pc}}{2\pi f_{cva} L_{v}} \right] > 0 \\

PM \approx \pi - \frac{\pi}{2} - 2\pi f_{cva} T_{d} > 0

\end{cases} \Rightarrow K_{pc} < \frac{\pi L_{v}}{2T_{d}}$$

(24)

The output impedance of system is given by

$$Z_{GE}(s) = Z_{v}(s) \frac{Z_{op}(s) + G_{i}(s)G_{d}(s)}{Z_{v}(s) + G_{i}(s)G_{d}(s)} \stackrel{Lowf}{\approx} Z_{v}(s) \frac{R_{eq} + K_{pc}}{R_{v} + K_{pc}}$$

(25)

Due to  $K_{pc}>>R_v$ ,  $Z_{GE}(s)=Z_v(s)$  can be guaranteed at the low-frequency range. Fig. 21(b) shows an LVRT test with post-fault SCR=2. Although the instability phenomenon is reproduced, the oscillating frequency in the converter-based grid emulation system cannot match that of the physical system. This is because the fundamental-frequency PR controller of the grid emulator cannot achieve the zero-error control of voltage fluctuation with divergent oscillating

frequencies. The uncertainty of oscillations can further complicate the accurate emulation of grid impedance. Fig. 21(c) shows an LVRT test with  $Z_v$ =0.04 p.u. during fault. Emulating a small impedance by VA control tends to enlarge the open-loop gain  $G_{opva}(s)$ , causing the internal instability.

Similarly, in the *LC*-filtered grid emulator, the inaccurate low-frequency impedance emulation based on VC and VI control has been demonstrated in [10], [63]. Although the CC and VA control can also enhance the accuracy of the emulated impedance with a low SCR, emulating nearly zero impedances remains a challenge.

2) Co-emulation of multiple testing capabilities: Besides the co-emulation of voltage sags/swells and impedance variation, several studies also have explored the combination of other testing capabilities, e.g., flicker with frequency deviation [12], unbalance fault with harmonics [80], etc.

Generally, combining the control schemes required for individual testing capability can achieve the simultaneous emulation of multiple testing capabilities. Yet, two testing scenarios may complicate the parameterization of resonant controllers widely used in grid emulators. First, to combine the frequency deviation and other testing capabilities, the center frequencies of resonant controllers may need to vary with the frequency of reference signals [12]. The controller parameters based on the small-signal modeling may not work under large disturbances [81], [82]. Second, to simultaneously emulate flicker and inter-harmonics/harmonics, the center frequencies of resonant controllers may be close to each other, which may aggravate dynamic interactions among the adjacent resonant controllers, introducing more -R around harmonic frequencies.

# V. CONCLUSION

This paper has discussed the testing capability requirements of power-electronic-based grid emulators, based on the recent developments of grid codes and standards. It has been pointed out that simultaneously realizing multiple testing capabilities can challenge the controllability and dynamic performance of converter-based grid emulators. Four types of dynamic interactions and corresponding solutions in the cascaded/interleaved NPC-, CHB- and MMC-based grid emulators has been thoroughly discussed. Open issues and emerging trends with the component design (e.g., NP/cell/SM capacitors and CVG-side transformer) and control improvement of converter-based grid emulators have been identified.

#### REFERENCES

- F. Blaabjerg and K. Ma, "Future on power electronics for wind turbine systems," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 3, pp. 139-152, Sept. 2013.

- [2] Powerinfo Today. "Mingyang smart energy launches new 16 MW offshore wind turbine," Accessed. Available: https://www.powerinfotoday.com/wind-energy/.

- [3] B. Nouri, Ö. Göksu, V. Gevorgian, and P. E. Sørensen, "Generic characterization of electrical test benches for AC- and HVDC-connected wind power plants," *Wind Energy Science*, vol. 5, no. 2, pp. 561-575, 2020.

- [4] Cigre, Guide on new generator-grid interaction requirements, 2018.

- [5] AEMO, Model acceptance test guideline, 2021.

- [6] P. Koralewicz, V. Gevorgian, R. Wallen, W. van der Merwe and P. Jörg, "Advanced grid simulator for multi-megawatt power converter testing

- and certification," in *Proc. IEEE Energy Convers. Congr. Expo.*, Milwaukee, WI, USA, 2016, pp. 1-8.

- [7] A. Frehn, S. Azarian, G. Quistorf, S. Adloff, F. Santjer, and A. Monti, "First comparison of the electrical properties of two grid emulators for UVRT test against field measurement," *Forschung im Ingenieurwesen*, vol. 85, no. 2, pp. 373-384, Apr. 2021.

- [8] C. Saniter and J. Janning, "Test bench for grid code simulations for multi-MW wind turbines, design and control," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1707-1715, Jul. 2008.

- [9] N. R. Averous et al., "Development of a 4 MW full-size wind-turbine test bench," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 2, pp. 600-609, Jun. 2017.

- [10] P. Borowski, G. Quistorf, T. Jersch, "Pq4wind a novel test bench for component- level wind turbine converter testing," in *Proc. Wind. Solar Integration Workshop*, Hague, Netherlands, 2022, pp. 1-7.

- [11] J. C. Fox and B. Gislason, "Introduction to the Clemson university 15 MW hardware-in-the-loop grid simulator," in *Proc. Clemson Univ. Power Syst. Conf.*, Clemson, SC, USA, 2014, pp. 1-5.

- [12] Y. Li et al., "Distributed generation grid-connected converter testing device based on cascaded H-bridge topology," *IEEE Trans. Ind. Electron.*, vol. 63, no. 4, pp. 2143-2154, Apr. 2016.

- [13] N. Hildebrandt, M. Luo, and D. Dujic, "Robust and cost-effective synchronization scheme for a multicell grid emulator," *IEEE Trans. Ind. Electron.*, vol. 68, no. 3, pp. 1851-1859, Mar. 2021.

- [14] M. Jia, S. Cui, K. Hetzenecker, J. Hu, and R. W. De Doncker, "Control of a three-phase four-wire modular multilevel converter as a grid emulator in fault scenarios," in *Proc. IEEE Energy Convers. Congr. Expo.*, Vancouver, BC, Canada, 2021, pp. 624-631.

- [15] M. Jia, S. Cui, P. Joebges, and R. W. D. Doncker, "A modular multilevel converter as a grid emulator in balanced and unbalanced scenarios using a delta-wye transformer," in *Proc. IEEE Energy Convers. Congr. Expo.*, Vancouver, BC, Canada, 2021, pp. 2950-2957.

- [16] Z. Li et al., "Testing requirements and control strategies of next-generation grid emulator: a review," in Proc. Int. Power Electron. Conf. (IPEC-Himeji 2022- ECCE Asia), Himeji, Japan, 2022, pp. 1560-1566.

- [17] Z. Li, F. Zhao, X. Chen, S. Munk-Nielsen, M. Geske, R. Grune and X. Wang, "Analysis and mitigation of submodule capacitor overvoltage for MMC-based grid emulator under LVRT test," in *Proc. Wind. Solar Integration Workshop*, Hague, Netherlands, 2022, pp. 1-8.

- [18] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219-2230, Jul. 2010.

- [19] A. Uphues, K. Notzold, R. Griessel, R. Wegener, and S. Soter, "Overview of LVRT-capability pre-evaluation with an inverter based test bench," in *Proc. Int. Symp. Ind. Electron. (ISIE)*, Buzios, Brazil, 2015, pp. 748-753.

- [20] R. Pöllänen, L. Kankainen, M. Pääkkönen, J. Ollila and S. Strandberg, "Full-power converter based test bench for low voltage ride-through testing of wind turbine converters," in *Proc. Euro. Conf. Power Electron.* Applica., Birmingham, UK, 2011, pp. 1-10.

- [21] K. Ma, J. Wang, X. Cai and F. Blaabjerg, "AC grid emulations for advanced testing of grid-connected converters-an overview," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1626-1645, Feb. 2021.

- [22] IEC, Wind turbines Part 21: Measurement and assessment of power quality characteristics of grid connected wind turbines, IEC Std. 61 400-21, 2019.

- [23] IEEE, Equipment interconnecting distributed energy resources with electric power systems and associated interfaces, IEEE Std. 1547. 1, 2020.

- [24] IEEE, Interconnection and interoperability of inverter-based resources (IBRs) interconnecting with associated transmission electric power systems, IEEE Std. 2800, 2022.

- [25] FGW TR3, Bestimmung der elektrischen eigenschaften von erzeugungseinheiten und -anlagen, speicher sowie für deren komponenten am mittel-, hoch- und höchstspannungsnetz, 2018.

- [26] Technical Note (TN 066), Certification of grid code compliance (GCC) test procedure for low voltage ride through (LVRT), 2013.

- [27] ESO, The grid code issue 6 revision 14, National Grid ESO, 2022.

- [28] H. T. Mokui, M. A. S. Masoum, and M. Mohseni, "Review on Australian grid codes for wind power integration in comparison with international standards," in *Proc. Austral. Univ. Power Engine. Conf.* (AUPEC), Perth, WA, Australia, 2014, pp. 1-6.

- [29] M. Tsili and S. Papathanassiou, "A review of grid code technical requirements for wind farms," *IET Renew. Power Genera.*, vol. 3, no. 3, pp. 308, 2009.

- [30] VDE, Technical requirements for the connection and operation of customer installations to the high-voltage network (TCC high-voltage), document VDE-AR-N 4120, VDE, 2015.

- [31] VDE, Technical requirements for the connection and operation of customer installations to the medium-voltage network (TCC mediumvoltage), document VDE-AR-N 4110, VDE, 2017.

- [32] GBT, Technical requirements for photovoltaic grid-connected inverter, GBT 37408, 2019.

- [33] GBT, Technical specification for connecting wind farm to power system—part 1: on shore wind power, GBT 19963.1, 2021.

- [34] M. H. J. Bollen and R. A. A. de Graaff, "Behavior of ac and dc drives during voltage sags with phase-angle jump and three-phase unbalance," in *Proc. IEEE Power Engineer. Society*, New York, NY, USA, 1999, pp. 1225-1230.

- [35] X. Xiao, S. Tao, "Voltage sags types under different grounding modes of neutral and their propagation: part I," *Trans. China Electro. society*, vol. 22, no. 10, pp. 156-159, Sept. 2007.

- [36] M. R. Alam, K. M. Muttaqi, and A. Bouzerdoum, "Characterizing voltage sags and swells using three-phase voltage ellipse parameters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 4, pp. 2780-2790, Jul./Aug. 2015.

- [37] AEMO, Multiple voltage disturbance ride-through capability, 2018.

- [38] X. Wang and F. Blaabjerg, "Harmonic stability in power electronic-based power systems: concept, modeling, and analysis," *IEEE Trans. Smart Grid*, vol. 10, no. 3, pp. 2858-2870, May 2019.

- [39] A. Frehn, R. Grune, H. Röttgers, and A. Monti, "Influence of the grid parameters during under voltage ride through (UVRT) testing," Forschung im Ingenieurwesen, vol. 85, no. 2, pp. 559-566, Mar. 2021.

- [40] AEMO, Recommended technical standards for generator licensing in south Australia, 2017.

- [41] P. Koralewicz, "Power electronic grid simulator platform of drives and power quality products for power electronics testing", in *Proc. Workshop. Grid Simulator Testing. Wind Turbine Drivetrains*, Tallahassee, Florida, 2015.

- [42] Electromagnetic Compatibility (EMC), Testing and measurement techniques, flickermeter-function and design specifications-part 4-15, IEC Standard 61000-4-15, Edition 2.0, 2010.

- [43] N. Espinoza, M. Bongiorno, and O. Carlson, "Novel LVRT testing method for wind turbines using flexible VSC technology," *IEEE Trans. Sustain. Energ.*, vol. 6, no. 3, pp. 1140-1149, Jul. 2015.

- [44] S. Azarian, T. Jersch, S. Khan, and S. Azarian, "Comparison of impedance behavior of UVRT container with medium voltage grid simulator in case of unsymmetrical voltage dip," in *Proc. Conf. Wind Power Drives (CWD)*, Aachen, Germany, 2019, pp. 1-12.

- [45] M. H. J. Bollen, "Characterization of voltage sags experienced by three phase adjustable-speed drives," *IEEE Trans. Power Deliver.*, vol. 4, no. 12, Oct. 1997.

- [46] M. H. J. Bollen, "Understanding power quality problems: voltage sags and interruptions," Wiley-IEEE Press, 2000.

- [47] J. Morren and S. W. H. de Haan, "Short-circuit current of wind turbines with doubly fed induction generator," *IEEE Trans. Energy Conver.*, vol. 22, no. 1, pp. 174-180, Mar. 2007.

- [48] C. Mehler, T. Jersch, P. Koralewicz and B. Tegtmeier, "Advanced grid simulator topology for testing of renewable energy supply units especially wind energy converters (WECs) under laboratory conditions," in *Proc. Euro. Conf. Power Electron. Applica. (EPE'16 ECCE Europe)*, Karlsruhe, Germany, 2016, pp. 1-9.

- [49] S. Lambert, V. Gevorgian, S. Dana, and R. Wallen, "Phase 1 integrated systems test and characterization report for the 5-megawatt dynamometer and controllable grid interface," *Technical Report*, Mar. 2018.

- [50] R. Schelenz, "Center for wind power drives—Competence in system design and testing of wind power drives," *Technical Report*, Jan. 2017.

- [51] S. Kouro et al., "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [52] M. Petković and D. Dujić, "Hardware-in-the-loop characterization of source-affected output characteristics of cascaded H-bridge converter," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 3083-3094, Jun. 2021.

- [53] D. Rimorov, O. Tremblay, K. Slimani, R. Gagnon, and B. Couillard, "Gain scheduling control design for active front end for power

- hardware-in-the-loop application: an LMI approach," *IEEE Trans. Energy Convers.*, vol. 37, no. 4, pp. 2974-2983, Dec. 2022.

- [54] M. M. Steurer et al., "Multifunctional megawatt-scale medium voltage dc test bed based on modular multilevel converter technology," *IEEE Trans. Transp. Electrification*, vol. 2, no. 4, pp. 597-606, Dec. 2016.

- [55] L. Harnefors, A. Antonopoulos, S. Norrga, L. Angquist, and H. Nee, "Dynamic analysis of modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2526-2537, Jul. 2013.

- [56] A. Uphues et al., "Inverter based test setup for LVRT verification of a full-scale 2 MW wind power converter," in Proc. Euro. Conf. Power Electron. Applica. (EPE'13 ECCE Europe), Lille, France, 2013, pp. 1-5.

- [57] P. Cheng, W. Chen, Y. Chen, C. Ni and J. Lin, "A transformer inrush mitigation method for series voltage sag compensators," *IEEE Trans. Power Electron.*, vol. 22, no. 5, pp. 1890-1899, Sept. 2007.

- [58] Y. Chen, C. Lin, J. Chen, and P. Cheng, "An inrush mitigation technique of load transformers for the series voltage sag compensator," *IEEE Trans. Power Electron.*, vol. 25, no. 8, pp. 2211-2221, Aug. 2010.

- [59] M. Biskoping, S. Richter, and R. W. De Doncker, "Inverter based testbench for photovoltaic inverters in compliance with medium-voltage grid codes," in *Proc. Int. Conf. Renew. Energy Res. Applica. (ICRERA)*, Nagasaki, Japan, 2012, pp. 1-6.

- [60] Y. Liao, X. Wang, and F. Blaabjerg, "Passivity-based analysis and design of linear voltage controllers for voltage-source converters," *IEEE Open J. Ind. Electron. Soc.*, vol. 1, pp. 114-126, Jun. 2020.

- [61] Z. Li, F. Zhao and X. Wang, "Passivity-based design for high-order harmonic voltage emulation of grid emulators," in *Proc. Int. Power Electron. Conf. (IPEC-Himeji 2022- ECCE Asia)*, Himeji, Japan, 2022, pp. 2394-2399.

- [62] H. Wu and X. Wang, "Passivity-based dual-loop vector voltage and current control for grid-forming VSCs," *IEEE Trans. Power Electron.*, vol. 36, no. 8, pp. 8647-8652, Aug. 2021.

- [63] J. Wang et al., "Dual-frequency-bands grid impedance emulator for stability test of grid-connected converters," *IEEE Trans. Power Electron.*, vol. 37, no. 11, pp. 13070-13080, Nov. 2022.

- [64] Z. Li, F. Zhao, X. Chen, S. Munk-Nielsen and X. Wang, "Issues of impedance emulation of converter-based grid emulator for LVRT test," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Orlando, FL, USA, 2023, pp. 2741-2746.

- [65] S. A. Richter, J. von Bloh, C. P. Dick, D. Hirschmann and R. W. De Doncker, "Control of a medium-voltage test generator," in *Proc. IEEE Power Electron. Spec. Conf.*, Rhodes, Greece, 2008, pp. 3787-3793.

- [66] Cinergia, "Grid emulator (GE+ AC&DC) —Installation and operation manual," *Technical Report*.

- [67] F. Hans, W. Schumacher, S. Chou, and X. Wang, "Design of multifrequency proportional-resonant current controllers for voltagesource converters," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13573-13589, Dec. 2020.

- [68] L. Harnefors, A. G. Yepes, A. Vidal and J. Doval-Gandoy, "Passivity-based stabilization of resonant current controllers with consideration of time delay," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6260-6263, Dec. 2014.

- [69] L. Harnefors, A. Antonopoulos, S. Norrga, L. Angquist, and H. Nee, "Dynamic analysis of modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2526-2537, Jul. 2013.

- [70] S. Yang, Y. Tang, and P. Wang, "Distributed control for a modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5578-5591, Jul. 2018.

- [71] J. Yang et al., "Carrier-based digital PWM and multirate technique of a cascaded H-bridge converter for power electronic traction transformers," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 2, pp. 1207-1223. Jun. 2019.

- [72] S. He, D. Zhou, X. Wang, Z. Zhao, and F. Blaabjerg, "A review of multisampling techniques in power electronics applications," *IEEE Trans. Power Electron.*, vol. 37, no. 9, pp. 10514-10533, Sept. 2022.

- [73] Z. Li, F. Zhao, S. He, S. Munk-Nielsen and X. Wang, "Multi-sampling with real-time update PWM for time-delay minimization of FPGA-based voltage-controlled converters," in *Proc. IEEE Appl. Power Electron.* Conf. Expo., Houston, TX, USA, 2022, pp. 1444-1449.

- [74] P. Koralewicz, V. Gevorgian, and R. Wallen, "Multi-megawatt-scale power-hardware-in-the-loop interface for testing ancillary grid services by converter-coupled generation," in *Proc. Workshop. Control. Model. Power Electron. (COMPEL)*, Stanford, CA, USA, 2017, pp. 1-8.

- [75] L. Harnefors, X. Wang, A. G. Yepes, and F. Blaabjerg, "Passivity-based stability assessment of grid-connected VSCs—an overview," IEEE

- Trans. Emerg. Sel. Topics Power Electron., vol. 4, no. 1, pp. 116-125, Mar. 2016.

- [76] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, and P. Barbosa, "Operation, control, and applications of the modular multilevel converter: a review," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 37-53, Jan. 2015.

- [77] H. Yang, Y. Dong, W. Li, and X. He, "Average-value model of modular multilevel converters considering capacitor voltage ripple," *IEEE Trans. Power Deliver.*, vol. 32, no. 2, pp. 723-732, Apr. 2017.

- [78] A. G. Yepes, F. D. Freijedo, Ó. Lopez and J. Doval-Gandoy, "Analysis and design of resonant current controllers for voltage-source converters by means of Nyquist diagrams and sensitivity function," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5231-5250, Nov. 2011.

- [79] X. Wang, P. C. Loh, and F. Blaabjerg, "Stability analysis and controller synthesis for single-loop voltage-controlled VSIs," *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 7394-7404, Sept. 2017.

- [80] T. Liu, D. Wang, and K. Zhou, "High-performance grid simulator using parallel structure fractional repetitive control," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2669-2679, Mar. 2016.

- [81] D. G. Holmes, T. A. Lipo, B. P. Mcgrath, and W. Y. Kong, "Optimized design of stationary frame three phase ac current regulators," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2417-2426, Nov. 2009.

- [82] D. M. Van de Sype, K. De Gusseme, A. P. Van den Bossche, and J. A. Melkebeek, "Small-signal Laplace-domain analysis of uniformly-sampled pulse-width modulators," in *Proc. Power Electron. Special. Conf.*, Aachen, Germany, 2004, pp. 4292–4298.

Zejie Li (Student Member, IEEE) received the B.S. degree in electrical engineering and automation from Yanshan University, Qinhuangdao, China, in 2017 and the M.S degree in electrical engineering from Beijing Jiaotong University, Beijing, China, in 2020. He is currently pursuing the Ph.D. degree in electronic engineering with the Department of Energy, Aalborg University, Aalborg, Denmark.

From April 2023, he has been serving as a threemonth visiting researcher with Fraunhofer IWES, Bremerhaven, Germany. His current research

interests include modeling and control of modular multilevel converters, grid emulation systems and grid-following/ grid-forming converters.

Martin Geske received the Dipl.-Ing. degree in electrical engineering from Otto von Guericke University Magdeburg, Germany, in 2009. He received his Ph.D. degree in electrical engineering from Chemnitz University of Technology, Chemnitz, Germany, in 2021.

From 2009 to 2011, he worked as a Research Associate at the Fraunhofer IFF and Otto von Guericke University, Magdeburg, Germany. Since 2011, he has been working at Converteam GmbH (changed later to GE Energy Power Conversion),

Berlin, Germany as a Development Engineer for power electronics on low-voltage and medium-voltage converters. In 2021, he joined R&D Test Systems A/S as a Senior Project Engineer for test systems using high-power converters. He currently works at GE Energy Power Conversion as a Principal Engineer for power electronics. He currently holds more than 20 granted patents.

Fangzhou Zhao (Member, IEEE) received his B.S. degree in Electrical Engineering and Automation from University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2014, and Ph.D. degree in Electrical Engineering from Xi'an Jiaotong University (XJTU), Xi'an, China, in 2019.

He is currently an Assistant Professor with AAU Energy, Aalborg University. He was a Postdoctoral Researcher with Aalborg University from 2020 to 2022. His research interests include modeling and stability analysis of power electronics-based power systems,

grid-forming control design and grid emulation system.

Rayk Grune received the Dipl.-Ing. and Dr.-Ing. degrees both in electrical engineering from Berlin Institute of Technology, Germany, in 2005 and 2012 respectively.

From 2005 to 2012 he worked as a research associate for Electrical Drives Group at Berlin Institute of Technology. In 2012 he joined GE Energy Power Conversion as a development engineer, with focus on converter control and electrical power system design. Since 2020 he is with R&D Test Systems as Senior Specialist Electrical, where his

focus is on design, modelling, and control of electrical test equipment mainly for wind industry applications.

**Xiongfei Wang** (Fellow, IEEE) received the B.S. degree from Yanshan University, China, in 2006, the M.S. degree from Harbin Institute of Technology, China, in 2008, both in electrical engineering, and the Ph.D. degree in energy technology from Aalborg University, Denmark, in 2013.

From 2009 to 2022, he was with Aalborg University where he became an Assistant Professor in 2014, an Associate Professor in 2016, a Professor and Leader of Electronic Power Grid (eGRID) Research Group in 2018. From 2022, he has been a Professor

with KTH Royal Institute of Technology, Stockholm, Sweden, and a part-time Professor with Aalborg University, Denmark. His research interests include modeling and control of power electronic converters and systems, stability and power quality of power-electronics-dominated power systems, and high-power converters.

Dr. Wang currently serves as Executive Editor (Editor in Chief) for the IEEE Transactions on Power Electronics Letters and as Associate Editor for the IEEE Journal of Emerging and Selected Topics in Power Electronics. He received ten IEEE Prize Paper Awards, the 2016 AAU Talent for Future Research Leaders, the 2018 Richard M. Bass Outstanding Young Power Electronics Engineer Award, the 2019 IEEE PELS Sustainable Energy Systems Technical Achievement Award, the Clarivate Highly Cited Researcher during 2019-2021, and the 2022 Isao Takahashi Power Electronics Award.

power quality testing.

**Daniel Bo Rønnest Andersen** received the B.Sc. degree in Electrical Power Engineering from Aarhus University (AU), Aarhus, Denmark, in 2018, and the M.Sc. degree in Electrical Engineering – Power Electronics and Drives from AAU Energy, Aalborg University, Aalborg, Denmark, in 2021.

Since 2018, he has been with R&D Test Systems A/S as an electrical engineer focusing on high power converters and control in electrical test applications for wind turbines and other renewables sources intended for grid compliance, grid stability, and

Miguel Garnelo Rodriguez received his B.Sc. degree in Industrial Electronics and Automation from the University of Oviedo, Spain, in 2018, and his M.Sc. degree in Energy Engineering from Aalborg University, Denmark, in 2021, with specialization in Power Electronics and Drives.

From 2017 to 2019, he was with the Efficient Energy Conversion, Industrial Electronics and Lighting Research Group (CE3I2), University of Oviedo, where he was a Research Assistant and worked in different power electronics applications

such as LED lighting, electric vehicle (EV) chargers, and Vehicle-to-Grid (V2G). Since 2020, he has been with R&D Test Systems A/S, Denmark, where he works as Project Engineer – Electrical. His research interests include modeling and control of power electronic converters, multilevel and modular multilevel converters, grid-following/grid-forming converters, grid emulation, grid compliance testing of wind turbines, and drive applications.

**Stig Munk-Nielsen** (S'92–M'97) received the M.Sc. and Ph.D. degrees from Aalborg University, Denmark, in 1991 and 1997, respectively.

He is currently a Professor with the Department of Energy, Aalborg University and research interests include Si, SiC and GaN components operating in soft and hard switching circuits, design challenges for low and medium voltage power modules and converters with intended application in the industry.