FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **Code Specialization for Targeting FPGAs via High-Level Synthesis Tools**

Vitória Alexa Maciel Correia

Mestrado em Engenharia Eletrotécnica e de Computadores

Supervisor: João Cardoso

July 27, 2023

© Vitória Alexa Maciel Correia, 2023

## Resumo

Os "Field-programmable gate arrays" (FPGA) ganharam uma popularidade significativa nos últimos anos devido à sua flexibilidade, alto desempenho e eficiência energética. Isto é particularmente importante pois existe uma procura crescente de computação de alto desempenho e a proliferação de aplicações embebidas. Ferramentas de Síntese de Alto Nível, do inglês "High-Level Synthesis" (HLS), permitem aos programadores escrever software em linguagens de programação de alto nível, tais como C/C++, e gerar automaticamente circuitos de hardware que podem ser implementados em FPGA. Este processo oferece muitos benefícios, incluindo a capacidade de conceber circuitos de hardware de forma mais eficiente e rápida, a capacidade de aproveitar o conhecimento e as capacidades dos programadores de software, e a capacidade de alcancar um alto desempenho em FPGA. Embora as ferramentas HLS tenham melhorado nos últimos anos, numerosos estudos demonstraram que a passagem de uma linguagem de alto nível, do inglês "High-Level Language" (HLL), para uma linguagem de descrição de hardware, do inglês "Hardware Description Language" (HDL) pode muitas vezes resultar num pior desempenho em relação a implementações que são executadas num processador convencional. Como o uso de FPGA traz alguns benefícios fundamentais, é necessário investigar técnicas capazes de tornar este processo mais eficiente. O principal objectivo deste trabalho é expor e propor técnicas eficientes, mais especificamente, especialização de código, que é uma técnica importante para optimizar o desempenho de sistemas de hardware concebidos com HLS e implementados em FPGA. Para alcancar os nossos objectivos, foram analisadas algumas das abordagens mais recentes que incluem técnicas como a avaliação parcial, a multiversão, algoritmos de alocação de recursos, e abordagens de co-projeto de software e hardware. As abordagens analisadas foram capazes de demonstrar a sua eficácia quando aplicadas a um FPGA alvo, utilizando ferramentas de alto nível. Para facilitar a compreensão da nossa abordagem, expomos alguns dos seus principais benefícios e desafios, exemplificamos um caso de aplicação simples e real, e apresentamos uma primeira abordagem que não só permite a identificação de uma série de etapas de implementação, mas também permite a avaliação da sua eficácia.

ii

# Abstract

Field-programmable gate arrays (FPGAs) have gained significant popularity in recent years due to their flexibility, high performance, and energy efficiency. This is particularly important as there is an increasing demand for high performance computing and the proliferation of embedded applications. High Level Synthesis (HLS) tools allow programmers to write software in high-level programming languages such as C/C++ and automatically generate hardware circuits that can be implemented in FPGAs. This process offers many benefits, including the ability to design hardware circuits more efficiently and quickly, the ability to leverage the knowledge and skills of software programmers, and the ability to achieve high performance on FPGAs. Although HLS tools have advanced rapidly in recent years, numerous studies have shown that moving from an High Level Languages (HLL) to Hardware Description Languages (HDL) can often result in worse performance than when implementations are run on a conventional processor. As the use of FP-GAs brings some fundamental benefits, it is necessary to investigate techniques capable of making this process more efficient. This work's main objective is to expose and propose efficient techniques, more specifically, code specialization, which is an important technique to optimize the performance of hardware systems designed with HLS and implemented in FPGAs. To achieve our objectives, some of the most recent approaches that include techniques such as partial evaluation, multiversioning, resource allocation algorithms, and hardware software co-design approaches were analyzed. The analyzed work has shown the effectiveness of some techniques when applied to a target *FPGA* using high-level tools. To facilitate the understanding of our approach, we expose some of its main benefits and challenges, exemplify a simple, real-world application case, and present a first approach that not only allows the identification of a series of implementation steps but also allows the evaluation of its effectiveness.

iv

# Acknowledgments

The past five years of my life have been a time of growth, learning, and personal development, but they have also been defined by obstacles and failures. Knowing that this chapter of my life is drawing to a close, I cannot help but feel a feeling of accomplishment and relief as I write these acknowledgments. This project has been a significant element of this journey, and I am happy for the opportunity to work on it. As I reflect on the past, I recall the people who have always supported me. Their consistent support, encouragement, and guidance have been invaluable, and I would want to use this opportunity to acknowledge them.

I would want to acknowledge my family's unwavering support throughout my academic life. It has not been easy to be a student, especially in terms of financial and emotional support. I am so grateful for the sacrifices they have made to help me.

I am grateful to my boyfriend. During the ups and downs of this period, he has been a continuous source of support and encouragement, and I will be eternally thankful for his presence in my life.

I would want to thank my friends and colleagues, who have supported, assisted, and kept me inspired throughout the years. Their assistance and companionship were essential to my academic success.

I acknowledge my supervisor's, Professor João Cardoso, guidance, patience, and constant support over the duration of this project. His expertise and constructive feedback helped me improve my work and develop my skills.

Vitória Alexa Maciel Correia

vi

"Start Somewhere."

Unknown

viii

# Contents

| 1 | Intr                                          | oduction 1                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|---|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|   | 1.1                                           | Context                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|   | 1.2                                           | Motivation                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|   | 1.3                                           | Goals and Objectives                                                                                                                                                                                                                               |  |  |  |  |  |  |

|   | 1.4                                           | Dissertation's Structure                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 2 | State                                         | e of the Art 5                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|   | 2.1                                           | Background                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|   |                                               | 2.1.1 Field-Programmable Gate Array                                                                                                                                                                                                                |  |  |  |  |  |  |

|   |                                               | 2.1.2 High Level Synthesis                                                                                                                                                                                                                         |  |  |  |  |  |  |

|   |                                               | 2.1.3 Code optimizations                                                                                                                                                                                                                           |  |  |  |  |  |  |

|   |                                               | 2.1.4 Code Specialization                                                                                                                                                                                                                          |  |  |  |  |  |  |

|   |                                               | 2.1.5 Value Profiling                                                                                                                                                                                                                              |  |  |  |  |  |  |

|   |                                               | 2.1.6 Partial Evaluation                                                                                                                                                                                                                           |  |  |  |  |  |  |

|   |                                               | 2.1.7 Multiversioning                                                                                                                                                                                                                              |  |  |  |  |  |  |

|   | 2.2                                           | Related Work                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|   |                                               | 2.2.1 Related approaches using HLS with a target FPGA                                                                                                                                                                                              |  |  |  |  |  |  |

|   |                                               | 2.2.2 Partial Evaluation                                                                                                                                                                                                                           |  |  |  |  |  |  |

|   |                                               | 2.2.3 Multiversioning                                                                                                                                                                                                                              |  |  |  |  |  |  |

|   | 2.3                                           | Summary 15                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 3 | Арр                                           | roach Description 19                                                                                                                                                                                                                               |  |  |  |  |  |  |

|   | 3.1                                           | Workflow                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|   | 3.2                                           | The San Diego Vision Benchmark Suite: Map Disparity    21                                                                                                                                                                                          |  |  |  |  |  |  |

|   | 3.3                                           | Taskmark (working title)   21                                                                                                                                                                                                                      |  |  |  |  |  |  |

|   | 3.4                                           | Gprof and Gprof2dot                                                                                                                                                                                                                                |  |  |  |  |  |  |

|   | 3.5                                           | Value Counter Monitor                                                                                                                                                                                                                              |  |  |  |  |  |  |

|   | 3.6                                           | Multiversion: Relationship with the degree of similarity                                                                                                                                                                                           |  |  |  |  |  |  |

|   | 5.0                                           | $2\tau$                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|   | 3.7                                           |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|   |                                               | Design Flow                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|   |                                               | Design Flow         26           3.7.1         Vitis HLS 2022.2         26                                                                                                                                                                         |  |  |  |  |  |  |

|   |                                               | Design Flow       26         3.7.1       Vitis HLS 2022.2       26         3.7.2       Vivado 2022.2       27                                                                                                                                      |  |  |  |  |  |  |

|   | 3.7                                           | Design Flow       26         3.7.1       Vitis HLS 2022.2       26         3.7.2       Vivado 2022.2       27         3.7.3       PYNQ <sup>TM</sup> -Z2 board       27                                                                            |  |  |  |  |  |  |

|   |                                               | Design Flow       26         3.7.1       Vitis HLS 2022.2       26         3.7.2       Vivado 2022.2       27                                                                                                                                      |  |  |  |  |  |  |

| 4 | <ul><li>3.7</li><li>3.8</li><li>3.9</li></ul> | Design Flow       26         3.7.1       Vitis HLS 2022.2       26         3.7.2       Vivado 2022.2       27         3.7.3       PYNQ <sup>TM</sup> -Z2 board       27         Motivation Example: Pow Function       27         Summary       29 |  |  |  |  |  |  |

| 4 | <ul><li>3.7</li><li>3.8</li><li>3.9</li></ul> | Design Flow       26         3.7.1       Vitis HLS 2022.2       26         3.7.2       Vivado 2022.2       27         3.7.3       PYNQ <sup>TM</sup> -Z2 board       27         Motivation Example: Pow Function       27         Summary       29 |  |  |  |  |  |  |

## CONTENTS

|    |       | 4.1.2 kNN Optimizations                                                         | 32             |

|----|-------|---------------------------------------------------------------------------------|----------------|

|    | 4.2   | Disparity                                                                       | 12             |

|    |       | 4.2.1 Disparity Analysis                                                        | 13             |

|    |       | 4.2.2 Disparity Optimizations                                                   | 15             |

|    | 4.3   |                                                                                 | 56             |

| 5  | Expo  | erimental Results 6                                                             | 51             |

|    | 5.1   | Experimental Setup                                                              | 51             |

|    | 5.2   | HLS Synthesis Results                                                           | 52             |

|    |       | 5.2.1 <i>Pow</i> function                                                       | 52             |

|    |       | 5.2.2 k-Nearest Neighbors                                                       | 66             |

|    |       | 5.2.3 Disparity                                                                 | 71             |

|    | 5.3   | Analysis of the Relationship between Degree of Similarity and Performance in    |                |

|    |       | Multiversion Technique                                                          | 75             |

|    |       | 5.3.1 Relative Percentage of Resources Used                                     | 75             |

|    |       |                                                                                 | 76             |

|    | 5.4   | Value Counter Monitor: Extended Version    7                                    | 78             |

|    | 5.5   | 5 6                                                                             | 31             |

|    |       | 1                                                                               | 31             |

|    |       |                                                                                 | 32             |

|    | 5.6   | 11                                                                              | 32             |

|    |       | 5.6.1 Benchmark Selection                                                       | 33             |

|    |       | 6 6                                                                             | 33             |

|    |       | 5.6.3 Specialized and Multiversion Versions                                     | 34             |

|    |       | 6                                                                               | 35             |

|    |       | 5.6.5 Relationship between Degree of Similarity and Performance in Multiver-    |                |

|    |       | 1                                                                               | 35             |

|    |       |                                                                                 | 36             |

|    | 5.7   | Summary                                                                         | 36             |

| 6  |       |                                                                                 | <b>39</b>      |

|    | 6.1   |                                                                                 | 39             |

|    | 6.2   |                                                                                 | 91             |

|    | 6.3   |                                                                                 | 91             |

|    |       |                                                                                 | 92             |

|    |       |                                                                                 | 92             |

|    |       | 6                                                                               | 92             |

|    |       |                                                                                 | 92             |

|    |       | 6.3.5 Study on the Suitable Tool for Assessing the Relationship between Simi-   |                |

|    |       | 5                                                                               | <del>)</del> 3 |

|    |       | 6.3.6 Impact Study of Multiversion Versions for Different Benchmark Scenarios 9 | 93             |

| Re | feren | ces 9                                                                           | 95             |

# **List of Figures**

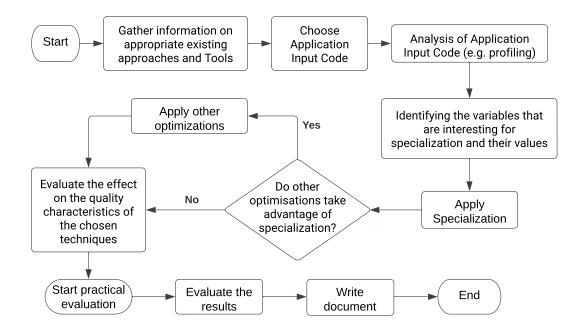

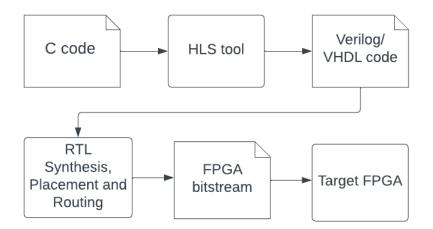

| 3.1 | Approach workflow Diagram                                                                         | 20 |

|-----|---------------------------------------------------------------------------------------------------|----|

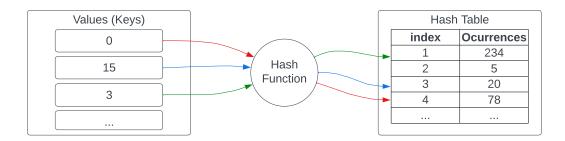

| 3.2 | "monitor" library hashtable                                                                       | 23 |

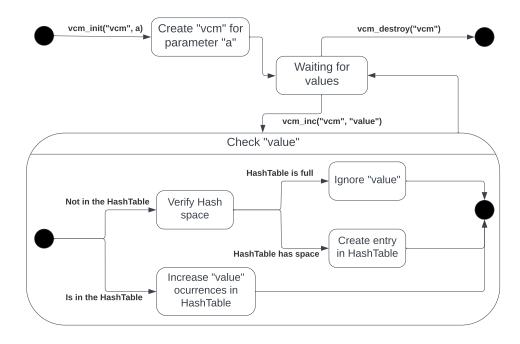

| 3.3 | "monitor" library state diagram                                                                   | 23 |

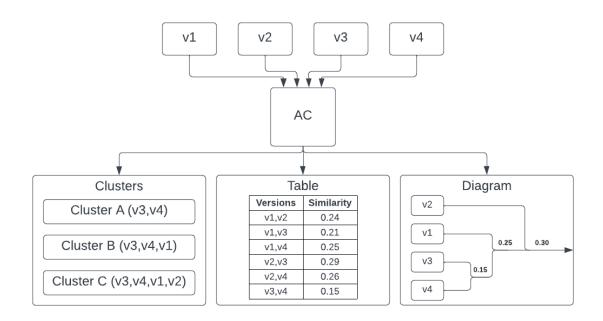

| 3.4 | AC results example                                                                                | 25 |

| 3.5 | Design Flow Main Stages                                                                           | 26 |

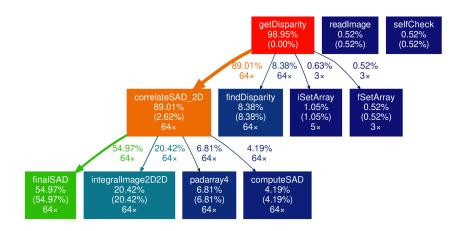

| 4.1 | Disparity Benchmark Profiling Results.                                                            | 44 |

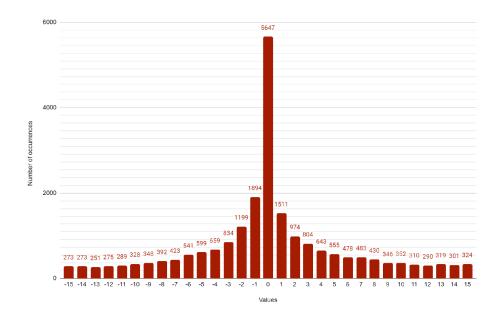

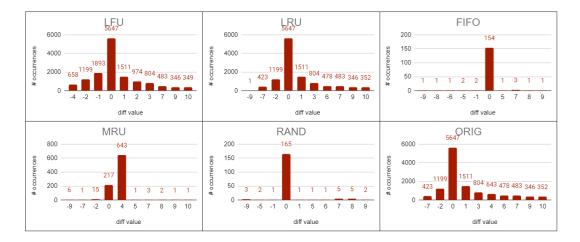

| 4.2 | Histogram of variable "diff", from computeSAD function, possible values and number of ocurrences. | 45 |

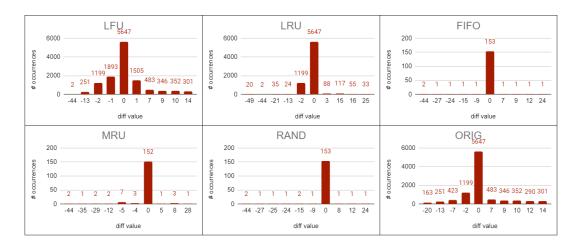

| 5.1 | Results of executing the disparity algorithm for each substitution policy without                 |    |

|     | 8                                                                                                 | 79 |

| 5.2 | Results of simulating the disparity algorithm for each substitution policy with a                 |    |

|     | value range between [-10,10]                                                                      | 80 |

# **List of Tables**

| <ul> <li>3.1 Examples of scenarios that may occur in pow() function specialization</li></ul>                                                                                                                                                                                                                                                  | 16                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <ul> <li>4.2 HLS directives applied to the kNN algorithm.</li> <li>4.3 Disparity possible scenarios and respective input data sizes.</li> <li>4.4 HLS directives applied to the Disparity algorithm.</li> <li>5.1 Total available resources of the Zynq-7000 SoC XC7Z020-1CLG400C FPGA, present in the PYNQ<sup>TM</sup>-Z2 board.</li> </ul> | 28<br>30             |

| present in the PYNQ <sup>TM</sup> -Z2 board. $\ldots$                                                                                                                                                                                                                                                                                         | 33<br>42<br>43<br>57 |

| with a target of 10ns and uncertainty of 2.70 ns. (single-precision float (SPF);                                                                                                                                                                                                                                                              | 62                   |

| <ul> <li>maximum frequency (Fmax); multiversion (MV); specialized (SPEC))</li> <li>5.3 Speedups resulting from comparing the number of latency cycles of each <i>pow</i> version against the generic version v1, and the related specialized (SPEC) version.</li> </ul>                                                                       | 63<br>64             |

| <ul> <li>5.4 Result number of resources used by each <i>pow</i> version after synthesis.</li> <li>5.5 Comparison of the number of resources used by each <i>pow</i> version compared to the</li> </ul>                                                                                                                                        | 64<br>65             |

| <ul><li>generic version (%).</li><li>5.6 Results of the area-delay product (ADP) of each <i>pow</i> version and their comparison</li></ul>                                                                                                                                                                                                    | 66                   |

| <ul><li>(%) with the generic version, v1</li></ul>                                                                                                                                                                                                                                                                                            | 67                   |

| <ul> <li>multiversion (MV); specialized (SPEC))</li></ul>                                                                                                                                                                                                                                                                                     | 68                   |

| version.                                                                                                                                                                                                                                                                                                                                      | 68                   |

| 5.9 Result number of resources used by each kNN version after HLS synthesis                                                                                                                                                                                                                                                                   | 69                   |

| 5.10 Comparison of the number of resources used by each kNN version compared to                                                                                                                                                                                                                                                               | - ^                  |

| the generic version (%)                                                                                                                                                                                                                                                                                                                       | 70                   |

| 5.11 Results of the area-delay product (ADP) of each kNN version and their comparison (%) with the generic version, v2.                                                                                                                                                                                                                       | 70                   |

| 5.12 Results after Disparity versions simulations of the values referring to the execu-                                                                                                                                                                                                                                                       | 70                   |

| tion time with a target of 10 ns and uncertainty of 2.70 ns. (maximum frequency                                                                                                                                                                                                                                                               |                      |

| (Fmax); multiversion (MV); specialized (SPEC))                                                                                                                                                                                                                                                                                                | 72                   |

| 5.13 Speedups resulting from comparing the number of latency cycles of each Dispar-                                                                                                                                                                                                                                                           |                      |

| ity version against the Disparity generic version v1, and the related specialized                                                                                                                                                                                                                                                             |                      |

| (SPEC) version                                                                                                                                                                                                                                                                                                                                | 73                   |

| 5.14 | Result number of resources used by each Disparity version after synthesis                  | 74 |

|------|--------------------------------------------------------------------------------------------|----|

| 5.15 | Comparison of the number of resources used by each Disparity version compared              |    |

|      | to the generic version (%)                                                                 | 74 |

| 5.16 | Results of the area-delay product of each Disparity version and their comparison           |    |

|      | (the generic version, v1                                                                   | 75 |

| 5.17 | Results obtained for <i>Disparity</i> from the analysis of the degree of similarity be-    |    |

|      | tween each of the two possible combined individual versions and the correspond-            |    |

|      | ing results of the multiversion versions                                                   | 76 |

| 5.18 | Results obtained for <i>Disparity</i> from clusters resulting from the analysis of the de- |    |

|      | gree of similarity between each of the two possible combined individual versions           |    |

|      | and the corresponding results of the multiversion versions                                 | 76 |

| 5.19 | , e ,                                                                                      |    |

|      | each of the two possible combined individual versions and the corresponding re-            |    |

|      | sults of the multiversion versions                                                         | 77 |

| 5.20 | Results obtained for <i>kNN</i> from clusters resulting from the analysis of the degree    |    |

|      | of similarity between each of the two possible combined individual versions and            |    |

|      | the corresponding results of the multiversion versions                                     | 77 |

| 5.21 | 81 8                                                                                       |    |

|      | monitored variable that entered the hashtable and the total number of values sub-          |    |

|      | stituted in the table of simulating the disparity algorithm for each substitution policy   | 79 |

| 5.22 | Resulting parameter values indicating the total number of values assigned to the           |    |

|      | monitored variable that entered the hashtable and the total number of values substi-       |    |

|      | tuted in the table of simulating the disparity algorithm for each substitution policy      | 00 |

|      | with a value range between [-10,10]                                                        | 80 |

# Listings

| 2.1 | Partial Evaluation Example: original function                                     | 8  |  |  |  |

|-----|-----------------------------------------------------------------------------------|----|--|--|--|

| 2.2 | Partial Evaluation Example: specialized function                                  |    |  |  |  |

| 3.1 | Example of using the pow() function in the C programming language                 | 28 |  |  |  |

| 3.2 | Example of the application of specialization with multiversioning with respect to |    |  |  |  |

|     | pow() function                                                                    | 29 |  |  |  |

| 4.1 | Original code (v1)                                                                | 34 |  |  |  |

# Abbreviations

| ADP    | Area-Delay Product               |

|--------|----------------------------------|

| AO     | Adaptive Optimization            |

| AP     | All Programmable                 |

| BF     | Belief Function                  |

| BRAM   | Block Random Access Memory       |

| CLB    | Configurable Logic block         |

| CPU    | Central Processing Unit          |

| DAE    | Decoupled Access Execution       |

| DSL    | Domain-Specific Language         |

| DSP    | Digital Signal Processing        |

| ELM    | Extreme Learning Machine         |

| FF     | Flip-Flop                        |

| FPGA   | Field-Programmable Gate Array    |

| GNU    | GNU's Not Unix                   |

| GPU    | Graphics Processing Unit         |

| HDL    | Hardware Description Language    |

| HLL    | High-Level Language              |

| HLS    | High-Level Synthesis             |

| HW     | Hardware                         |

| LSTM   | Long-Short-Term Memory           |

| PE     | Partial Evaluation               |

| PGO    | Profile-Guided Optimization      |

| PL     | Programmable logic               |

| PP&R   | Post-place and route             |

| QoR    | Quality of Results               |

| RTL    | Register-Transfer Level          |

| SAD    | Sum of Absolute Differences      |

| SD-VBS | San Diego Vision Benchmark Suite |

| SoC    | System-on-Chip                   |

| SPF    | Single-Precision-Float           |

| SVM    | Support Vector Machine           |

| SW     | Software                         |

| VCM    | Value Counter Monitor            |

## **Chapter 1**

## Introduction

In this chapter, the context and motivation behind the problem addressed in this work is introduced. The main objectives of the work and the way the dissertation is organized are also described.

## 1.1 Context

As the complexity of digital circuits has increased over time, there is currently a tendency to focus on specific hardware applications, which allows a more efficient and faster execution of software programs on the hardware as a whole [1]. As a result, manual hardware design has become more complex, and the use of *Hardware Description Languages (HDL)*, such as *Verilog* [2] and *VHDL* [2], has become more prevalent.

*Field-programmable gate arrays (FPGAs)* [3] are reprogrammable hardware devices, which have come to prominence over the last few years as computational accelerators (see, e.g. [4]), and by offering a number of key benefits, such as their higher performance compared to conventional software (Central Processing Unit, *CPU*), in certain situations, at lower costs, with better energy efficiency, and by being commercially available to a wide range of users.

Thus, *FPGAs* have been growing as a new platform in different areas, which include their use in autonomous vehicle driving [5], computer vision [6], automation and safety technology at work [7], in cybernetics [8, 9], automation in vehicles [10, 11, 12], medical equipment [6], computer hardware, networking, digital communication [13, 14] and radio devices [15], bioinformatics [6], voice recognition technology [16], secure communication systems, and a variety of scientific, medical and other electronic products.

The advantages of using *FPGAs*, however, continue to be influenced by *HDLs*, used to specify their computational data path as well as their detailed programming. The use of *HDLs*, despite being able to provide efficient designs, is inefficient in terms of human efficiency, i.e., a great deal of knowledge is required by developers about hardware design, and even then, there is a high propensity for errors [4]. In this context, i.e., making the development process simpler for software programmers/developers, *High Level Synthesis (HLS)* [17, 18] tools have emerged, (see, e.g., [19, 20, 21]).

*High Level Synthesis (HLS)* [17, 18] provides an automated design process that, starting from an abstract behavioral specification, similar to software, generates an equivalent *register-transfer level (RTL)* structure capable of generating a circuit, which implements the input behavioral specification [22]. In other words, an *HLS* tool takes as input a function written in a *high-level language (HLL)* such as C/C++, and converts it to a *RTL HDL* kernel, thus being able to automatically generate an *FPGA* accelerator. *HLL* implementations can be developed more quickly and succinctly, which lowers the likelihood of programmer mistakes and increases readability and reuse of the code.

Although *HLS* tools have advanced rapidly in recent years, numerous studies have shown that switching from an *HLL* to *HDL* can often result in worse performance than when implementations are run on a conventional processor. In addition, there is input code that is, as yet, not synthesizable with current *HLS* tools, such as the use of pointers, memory management and recursion.

As an attempt to address such issues, the makers of the technology have released a collection of best practices and programming, inside this guidelines, to help programmers maximize the potential of the *HLS* tools. Researchers have shown the benefit of rewriting code, typically manually, in line with these directives [4], according to the *HLS* tool and target *FPGA*. However, there are cases where using the aforementioned guidelines has no effect or, in some cases, even worse results [4]. Furthermore, the task of manually rewriting the code is complex, time consuming, error prone, can only be performed by programmers specialized in hardware knowledge and also requires a great effort in order to optimize the synthesis, taking into account the operating frequency, parallelization and energy efficiency.

As a result, and taking into account the benefits of using *FPGA* implementations, industry and research communities are focusing on the development of tools used as supplementary steps in the design process, in particular, code optimization and code specialization techniques for *HLS* and *FPGAs*, in order to overcome these challenges.

### **1.2** Motivation

In order to significantly improve energy efficiency, future processors should include architectural support for customization, allowing systems to adapt to various application domains [23]. In particular, it is expected that future architectural designs will make extensive use of accelerators in hardware, such as *FPGAs*, given the opportunities they entail. However, such architectures still present numerous challenges, namely the task of refactoring, specializing and optimizing code in *HLL*, for hardware. The reality is that, despite recent advances, our understanding of how programmers perform code specialization in the real world derives mainly from research that focuses on a small number of software projects [24].

Thus, our main motivation comes from the impact of customization via code specialization in hardware and lack of information regarding the same process, taking into account the advantages introduced by *FPGA* implementations integrating specialized execution flows. It is, therefore, important to try to expose, explore and develop efficient application code specialization techniques, in a *HLL*, in particular, via *HLS* tools and targeting *FPGAs*.

### **1.3 Goals and Objectives**

Given the aspects presented above, the main objective of this work is to propose efficient techniques for specializing the application input code, *C*, so that it becomes more suitable for the target *HLS* tool and *FPGA* and performance is improved. In some cases, multiversioning techniques are be used to guarantee the existence of very efficient accelerators in more common scenarios, but with the ability to accelerate the application in the context of other scenarios. All this depends on the identification of the most common scenarios, which can be done by profiling the code.

In summary, it is expected that this work achieves increased performance improvements by reviewing current techniques for efficient C code for *HLS* (as well as the possibility of discovery of new techniques), proposing efficient specialization techniques.

### **1.4 Dissertation's Structure**

This dissertation consists of four chapters and is organized as follows:

- Chapter 2, Realated Work, presents some background regarding better-known optimization techniques, and discusses studies already carried out on several specialization techniques for code in *HLL*. In this way, based on previous studies, it is possible to obtain a perspective on existing techniques and what they involve, facilitating learning and giving an idea of which methods can be applied in our proposal, and what results to expect from them;

- In Chapter 3, Approach Description, our approach is presented, emphasising its principal stages and components. Its underlying concepts and principles are explored, along with its integration with high-level optimization and synthesis tools.

- In Chapter 4, Benchmark Analysis and Optimizations, a study of benchmarks is conducted in order to identify potential areas to apply specialization techniques. Examining the results of multiple benchmarks also allows us to identify optimization opportunities, e.g., for reducing energy consumption, increasing speed, or enhancing scalability, and establish the optimal strategy for our application.

- In Chapter 5, Experimental Results, the main goal is to describe the experimental setup and expose, analyse, and justify the results achieved by the proposed approach when applied to the benchmarks.

- Finally, in Chapter 6, Conclusions, an overview of the results obtained from the work carried out, a review of our approach, our contributions and, finally, future work are addressed.

Introduction

## **Chapter 2**

## State of the Art

This chapter aims to address the topics considered relevant for understanding the problems presented in Chapter 1 and covers the research and analysis conducted on the most recent approaches and solutions related to the dissertation's main topics. It is organized into three main sections:

- Section 2.1: where a brief introduction is carried out on some important concepts for the understanding of the work to be carried out;

- Section 2.2: where work done on existing compilation techniques that specialize the *C* input application code to become more suitable for *HLS* and the target *FPGA* is discussed;

- Section 2.3: where a review on the concepts covered in the previous two points is carried out.

### 2.1 Background

Several key concepts that are necessary for a better understanding of the subject matter of this paper are introduced in this section.

#### 2.1.1 Field-Programmable Gate Array

An *FPGA* [3] is a type of reprogrammable hardware device that is used in a wide range of electronic systems and devices. It consists of an array of configurable logic blocks (*CLBs*) and interconnects that can be programmed by the user to implement a wide range of digital circuits and systems. The resources of an *FPGA* are the programmable logic blocks (such as Lookup tables (*LUTs*), and *Flip-Flops*), input/output blocks, and programmable connections that make up the device. Some contemporary *FPGAs* also provide block random access memory (*BRAM*) which provides a more significant data armazenament and digital signal processing (*DSP*) components. *FPGAs* have several advantages over other types of programmable hardware devices, and in recent years, they have gained prominence as computational accelerators [4], managing to provide higher performance than conventional software (*CPU*) in several situations. The main advantages

of *FPGAs*, in relation to previous ones, include: greater flexibility, higher speed, determinism, energy efficiency, re-programmability, parallelism, which in turn allows to improve performance, and customizability, considering that *FPGAs* can be customized for specific applications, allowing users to optimize their designs for their specific needs. For these reasons, they are commonly used in a wide range of applications, including high-performance computing, communications [13, 14], networking [8, 9], aerospace, military [12], medical [6], automotive [11], and industrial systems [7].

*FPGAs* are, however, still limited by the complexity and detail of the *HDLs*, used to specify their computational data path.

#### 2.1.2 High Level Synthesis

*HLS* tools [17, 18] arise in the context of making the use of *HDLs* a simpler development process for software programmers/developers. *HLS* [17, 18] is a design methodology for automatically generating hardware implementations of programs written in high-level languages like C or C++. *HLS* tools analyze the program and automatically generate specialized hardware implementations of the program's functions and algorithms, which can be synthesized into hardware circuits using *HDLs*, such as *VHDL* or *Verilog*.

In recent years, *HLS* has been increasingly studied by industry because it offers several advantages over traditional design methodologies, such as *RTL* design, higher productivity, quality, portability, and design exploration. Even though *HLS* tools have come a long way in recent years, more research and development is still needed in this area so that the change from a high-level language to an *HDL* is more efficient and leads to better performance than when implementations run on a regular processor.

#### 2.1.3 Code optimizations

Code optimization is the process of improving the performance, efficiency, and reliability of a program by modifying its code without changing its functionality.

In the context of *HLS*, code optimization involves using *HLS* tools to automatically optimize the hardware implementations of a program that are generated by the *HLS* tool. This can involve a wide range of techniques, including improving the algorithms used in the program, reducing the amount of memory and other resources used by the hardware implementation, and improving the utilization of the *FPGA* and other hardware resources. The specific optimizations that are used depend on the target *FPGA* and the goals of the optimization.

There are several types of code optimizations that can be performed in the context of *HLS*. Some of the main types of code optimizations in *HLS* include:

• Loop pipelining [25]: This technique involves breaking a loop into smaller parts and running each part in parallel, which increases the amount of parallelism;

#### 2.1 Background

- Loop unrolling [26]: This technique involves duplicating the body of a loop and then unrolling it. This reduces the overhead of the loop control logic;

- Data flow optimization [27]: This technique involves identifying data dependencies in the hardware implementation and then rearranging the hardware loops to improve data flow. It reduces the amount of data that needs to be stored in memory;

- Function inlining [28]: This optimization technique involves replacing a function call with the body of the function itself, thereby reducing function call and return overheads and allowing the compiler to perform further optimization of the code within the function;

- Data Reuse [29]: Data reuse is a code optimization technique that involves reusing the same data in multiple computations rather than storing and accessing it multiple times, reducing the amount of memory and other resources that are used by the program, and allowing hardware circuits to operate more efficiently.

#### 2.1.4 Code Specialization

When developing a function, programmers may sometimes declare a variable that turns out to be "quasi-invariant" [30] or even constant. In such cases, the variable can be assigned to a literal value as soon as it is appropriate. This may eliminate the overhead added by computation and helps the compiler detect the variable value at compile time. This last advantage, can facilitate the implementation of other optimizations such as constant propagation, constant folding, dead code elimination, loop unrolling, and pipelining [31, 28].

There are two types of specialization: dynamic and static specialization. Static specialization makes use of data that is expected to be used frequently, while dynamic specialization uses the actual values at runtime [31]. Code specialization is performed more effectively at runtime due to the unavailability of input values. The main difficulties related to specialization are: 1) detecting which variables are interesting to specialize and their values, and 2) minimizing the number of variables to specialize while maintaining a generic code and having good performance results [32].

Code specialization in the context of *HLS* is a technique that allows designers to write more general, high-level code, such as C or C++, for their digital circuits and then use *HLS* tools to automatically generate lower-level, more efficient *RTL* code that can be used to program target hardware, such as *FPGAs*. This approach can help speed up the design process and make it more flexible, as it allows designers to focus on the high-level functionality of their circuits without worrying so much about the low-level details. In addition, code specialization can help improve the performance and energy efficiency of the resulting hardware by allowing *HLS* tools to explore a larger space of possible *RTL* implementations and choose the one that is best suited for the target hardware platform.

There are several types of code specialization techniques that can be used in the context of *HLS*. Some examples of code specialization techniques in *HLS* include: parameter specialization,

loop specialization, path specialization, architecture specialization, mode specialization, data type specialization, memory specialization, and task specialization. The specific techniques that are used depend on the target *FPGA* and the optimization objectives.

#### 2.1.5 Value Profiling

Value profiling [33] is a technique for analyzing and collecting data regarding the distribution of a program's inputs or values during its execution (during runtime) in order to improve its performance.

This is achieved by repeatedly executing the program and collecting data on the inputs, variables, and expressions whose values are calculated by the program. This data can then be used to direct the optimization process by identifying numbers and areas of the code that are often used and run, responsible for the majority of the computation, and where performance improvements are anticipated to have the most impact. With this data, it is possible to develop code variations that are optimized for the most frequent inputs or values.

This technique could have a substantial impact on the context of code specialization in *HLS* tools for *FPGAs*, since the collected information can be used to drive the code specialization process by optimizing the implementation for the most frequent values. By focusing the implementation on the most frequent values, the design can be optimized for both performance and area, resulting in a more effective *FPGA* implementation. Moreover, value profiling can help uncover performance bottlenecks in the code, which can then be solved via code specialization.

#### 2.1.6 Partial Evaluation

According to [34], partial evaluation of a computer program is, by definition, the "specialization of a general program based on its operating environment into a more efficient program".

Partial evaluation is a technique in which the computation is evaluated with respect to the value of a particular operand. That is, instead of treating an operand as a variable, its value becomes "fixed" [35, 28]. This can be useful in situations where a function or program is called multiple times with the same arguments, as it allows partial evaluation to be performed once the resulting simplified function or program is used in subsequent calls, saving computational time and resources.

Based on the example in [34] and [28], let us imagine a function, f, that takes two arguments, a and b, i.e., f(a,b), as shown in listing 2.1.

1 int f(int a, int b) { return b \* (a - b) + a; }

Listing 2.1: Partial Evaluation Example: original function

Now suppose we want to use this function several times in our program, but always with the same value for *b*, for example, b = 2. In this case, we can do a partial evaluation of the function *f* to generate a new specialized function *g* (see listing 2.2):

| 1 | <b>int</b> g( <b>int</b> a) { <b>return</b> 3 * a - 4 ;} |

|---|----------------------------------------------------------|

|   |                                                          |

Listing 2.2: Partial Evaluation Example: specialized function

This transformation can save computational time and resources since function g becomes simpler and more efficient than function f for this specific set of input arguments.

In the context of *HLS*, partial evaluation is a technique that can be used to optimize the generated *RTL* code by simplifying it for a particular set of input arguments. This can be useful because the high-level code that is input to an *HLS* tool is often more general and abstract, and may not make use of all the input arguments available in a particular application.

#### 2.1.7 Multiversioning

Multiversion is a well-known technique in code optimization for generating code that can adapt to a changing execution context: at compile-time, numerous versions of the original code are generated as the consequence of distinct optimization modifications. When the resultant code is executed, decisions are taken at runtime to select the appropriate version based on particular criteria, such as input data or runtime behavior. There are numerous approaches to implement multiversion, depending on the system's unique requirements and limits.

When all future execution contexts are known, static multiversion, i.e. several versions generated during compilation, can be efficient. These execution contexts may be associated with the hardware execution platform on which the code is actually executed or with target attributes of the code that influence the validity or performance of the generated versions. This method becomes unworkable when execution contexts are largely unknown at compile time and cannot be predicted. The same holds true for specialization and unpredictable values. The generation of runtime versions of code where execution contexts are evidently understood might be one solution to these limits. Nonetheless, this method requires multiple time-consuming steps: profiling, analysis, transformation, and just-in-time compilation. Runtime multiversioning can be especially advantageous due to the fact that parameter values are frequently unknown at compile time and only discovered during execution.

### 2.2 Related Work

Code specialization, in the context of *HLS*, is a technique used to optimize the hardware implementation generated for a specific target device. It involves selecting and customizing hardware components and optimizing their interconnections based on the requirements and constraints of the target device. In recent years, there has been an increase in the use of code specialization techniques in *HLS* for *FPGA* targets. These techniques aim to improve the performance and resource

utilization of the generated hardware implementation and can be applied at various stages of the *HLS* flow, including instruction selection and other optimizations.

This section is mainly aimed at discussing the work presented on some of the most recent approaches in compilation techniques for code specialization using *HLS* and a target *FPGA*, which include the use of machine learning-based optimization methods and the incorporation of domain-specific knowledge in the optimization process. Additionally, techniques will be addressed, which, despite presenting a view directed towards software performance improvement and not particularly on *HLS* tools or the use of hardware devices, may have utility for the development of new ideas for solution formulation and technique development.

#### 2.2.1 Related approaches using HLS with a target FPGA

#### HeteroRefactor

Lau et al. [36] make an innovative end-to-end proposal, known as *HeteroRefactor*, which combines dynamic invariant analysis, automated refactoring, and selective offload for *FPGAs*.

*HeteroRefactor* focuses mainly on the following *HLS* refactoring techniques: rewriting a recursive data structure to a finite-sized array, reducing the bit-width of integers, and tuning variablewidth floating-point operations. These techniques are based on the expectation that dynamic *a-priori* analysis improves *FPGA* synthesizability, resource efficiency, and input-dependent offloading can guarantee correctness. For rewriting recursive data structures, the *HeteroRefactor* implementation is based on the ROSE [37] compiler framework. Whereas to reduce the bit-width of integers, it uses an approach based on the dynamic invariant detection tool, *Daikon* [38] using *Kvasir* [38] as a *C/C*++ front-end. The implementation of these first two types of refactorings is performed in a similar way for selective offloading, using a guard condition check. For floatingpoint operations, on the other hand, a dynamic analysis was performed that provides a probabilistic guarantee that the loss of precision is within a certain limit, this is because unlike the bit-width reduction of integers, when the bit-width of floating point variables is reduced, it can lead to a loss of precision.

HeteroRefactor consists of three main steps, which occur in the following order:

1) After a programmer implements his kernel code, code is then executed on existing tests where it is verified the existence of *FPGA*-specific dynamic invariants, i.e., bit-width needed for floating-point and integer variables, stack size and recursive data structures;

2) From the information obtained in 1), it automatically refactors the kernel in order to make programs *HLS* compatible, and at the same time, optimize the clock frequency and resource usage of the accelerator.

3) If the input fits the dynamic invariant, selectively offloads computation from the *CPU* to the *FPGA*, ensuring the preservation of correctness behavior. Otherwise, it keeps the computation on the *CPU*.

To evaluate this approach, ten diverse and suitable for different situations programs were used as benchmarks. The kernels were generated from C/C++ and targeted a *Xilinx Virtex UltraScale+XCVU9p FPGA* [39] on a *VCU1525* reconfigurable acceleration platform [40]. Using *Vivado Design Suite 2018.03* [41] the refactored programs are synthesized for *RTL*.

Based on experimental results, it was concluded that *HeteroRefactor* is able to automate the transformation (no need to change the code) of a recursive program into an *HLS* compatible version, identifying the empirical limit for the size of the recursive data structure, avoiding the effort of an experienced *FPGA* programmer. Furthermore, for recursive programs, the results showed that this approach had a great impact in reducing the resource usage of the target *FPGA*.

#### AnyHLS

It is common for programmers to write pragma-annotated C/C++ programs to define a hardware architecture of an application. Given that, each hardware vendor uses its own set of specific pragmas and the challenge of portability between different vendors arises. Additionally, the difficulty of using pragmas in a modular way (as they are resolved by the preprocessor) or performing proper abstractions, contributes to the difficulty of using existing *HLS* languages.

Thus, in [42] is presented AnyHLS, which unlike existing HLS approaches, focuses mainly on the challenges mentioned above by synthesizing FPGA designs in a modular and abstract way. To do so, it resorts to exploiting concepts of partial evaluation and programming language features (higher-order types and functions). AnyHLS is built on top of AnyDSL [43]. AnyDSL provides partial evaluation, which means there is no need to modify the compiler when adding support for a new application domain as developers can design custom control structures. AnyDSL is a compilation framework able to create high-performance, domain-specific libraries (DSLs) [44], and provides the Impala [34] language. Impala allows programmers to evaluate their programs partially at compile time by controlling the partial evaluator through filters. In addition, it provides syntactic sugar for invoking certain higher-order functions/generators, which are very powerful when combined with partial evaluation. In this paper, using the Impala functional language and its partial evaluation it has been possible to realize the abstractions required for FPGA synthesis in the form of a library. The partial evaluation is necessary to combine the abstractions and remove the respective overheads. After optimization of the user application based on a library of abstractions and partial evaluation, the AnyDSL compiler [43] synthesizes the optimized HLS code (C++ or OpenCL) from a given functional description of an algorithm. Subsequently, the generated code is input to the selected HLS tool.

To evaluate this approach, seven programs were used as benchmarks, diversified and according to the image processing application domain. The generated *HLS* codes were compiled using *Intel FPGA SDK* [45] for *OpenCL 18.1* [45] and *Xilinx Vivado HLS 2017.2* [41] targeting *Cyclone V GT 5CGTD9 FPGA* [46] and *Zynq XC7Z020 FPGA* [47], respectively. The results of *AnyHLS*, after *PP&R* ( post-place and route), were compared with the results of other domain-specific approaches, *Halide-HLS* [48] and *Hipacc* [49].

This approach, besides solving the challenge of portability (avoiding, in the source code, vendor-specific pragmas) and modularity, shows that the combination of high-order abstractions and partial evaluation is powerful enough to make the design of a library with different *HLS* compilers as targets. Furthermore, when compared to other *DSLs* (*Hipacc* and *Halide-HLS*), *AnyHLS* was able to generate equally efficient designs without creating a backend compiler entirely, outperforming them in terms of productivity.

#### **FPGA-based SVM acceleration**

Tsoutsouras et al. [6] present a systematic, two-level methodology and prototype structure for developing high-performance *FPGA*-targeted hardware Support Vector Machine *SVM* accelerator projects. The initial step of optimization in the presented methodology entails restructuring the *SVM* source code to expose greater levels of data- and instruction-level parallelism. According to the authors of the article, this level of optimization involves "reorganizing the data and instruction relationships in the source code to enable a greater degree of parallel execution." To expose more parallelism in the code, this may require techniques such as loop pipelining, loop unrolling, array split, and array reshaping, among others. This level of optimization is crucial because it permits the *SVM* code to be tailored to the exact hardware platform on which it will be deployed. By exposing additional parallelism in the code, the hardware accelerator can use the parallelism existing in the *SVM* algorithm and potentially achieve greater performance than with a non-specialized version of the code.

At level one of optimization, they also concentrate on minimizing hardware resource use. In order to investigate the design space of multiple hardware architectures and configurations that can implement *SVM* algorithms, they use an *HLS* tool. They employ a set of parameters, including area, power, and performance, to assess the efficiency of the developed hardware projects.

At level two of optimization, they use the results from level one to select the most efficient hardware design in terms of execution time for the *SVM* algorithms. In addition, they explain strategies for fine-tuning the hardware's design to increase its efficiency.

This methodology targets *SVM*-based system-on-chip systems, notably *Zynq* [47], which offers an *ARM Cortex-A9* and *SVM* fabric. All layers of accelerator optimization are performed using the *Vivado-HLS* tool [41], which gives the user directive-based control over the synthesis process. A case study of an ECG-based arrhythmia detection flow proved the efficiency of this methodology for producing efficient accelerator designs.

In general, this methodology can result in very efficient *SVM* accelerator implementations that deliver great performance with less area than manually optimized designs. Therefore, the application of this methodology can be advantageous for code specialization in the context of hardware acceleration.

#### 2.2.2 Partial Evaluation

As described in Section 2.1.6, partial evaluation is a technique that optimizes the performance of a program by evaluating it with some of its inputs predetermined.

Dong et al. [50] suggested a new hierarchical activity recognition method based on the theory of belief functions (BFs) [51, 52]. The theory of belief functions provides a mathematical framework for the representation and manipulation of uncertain data. It is a non-probabilistic approach to uncertainty based on the concept of a mass of beliefs, which expresses the degree of confidence that an event will occur. The theory of belief functions is especially relevant for dealing with complex systems and circumstances when knowledge is incomplete or ambiguous. Using approximations or heuristics, partial evaluation approaches can be utilized to optimize system performance by decreasing the computational burden of belief function calculations. This can be accomplished by precalculating and storing certain features of the belief function computations in a table or other data structure for reuse at runtime. The method provided in [50] employs a longshort-term memory (LSTM) model [53] to classify specified activities and a confusion matrix to determine similarities between each pair of activities. On the basis of hierarchical clustering [54], the activities are then structured into a hierarchical structure, and an Extreme Learning Machine (ELM) model [55] is trained for each non-leaf node. During the testing phase, a novel, efficient, tree-based matching rule is proposed to combine the findings of all ELMs that have been trained. UCI Smartphone [56] and mHealth [57] datasets are used to evaluate the hierarchical activity recognition algorithm presented. The results demonstrated this method surpassed all advanced algorithms.

The authors in [44] offer a technique for shallow embedding domain-specific languages (*DSLs*) into a host language via online partial evaluation [58]. The partial evaluation technique is intended to enhance the efficiency of *DSLs* implemented with shallow embedding by providing optimized host language code that can be performed directly, as opposed to interpreting or compiling the *DSL* code each time it is executed. The authors implement this technique by combining static analysis with runtime analysis. They begin by conducting a static analysis of the *DSL* code to determine which areas can be partially assessed and which cannot. This is accomplished by examining the *DSL* code's types and dependencies at compile-time. This partial evaluation technique analyzes the *DSL* code at runtime in order to generate the optimal host language code. The generated code for the host language is then compiled and executed, avoiding the need to interpret or compile the *DSL* code each time it is executed. Using several case studies, the authors demonstrate the efficiency of this technique and discuss its challenges and limitations, such as the difficulty of statically analyzing the *DSL* code to determine which portions can be partially evaluated and the overhead of generating and compiling the optimized host language code.

#### 2.2.3 Multiversioning

Lazcano et al. [59] designed a memoized speculative loop optimizer, a technique that aims to improve code by detecting computationally costly loops and executing numerous versions of

these loops in parallel. The objective is to discover the quickest version of the loop for the current hardware setup and record the result for future reference. A multiversion runtime technique was created as an extension of the Speculative Polyhedral Loop Optimizer (Apollo) framework [60, 61] to enable specialization and execution of many versions. The proposed multiversion runtime system is divided into two distinct phases: training and operation. During the training phase, modifications are made to the loop core, and the optimal version is chosen depending on runtime. Based on the kernel settings, this version is kept and indexed (memoized). In the operational phase, the saved version is re-released anytime the identical parameters are detected, resulting in optimal performance without the need for additional analysis or transformation. If a kernel with changed parameters is released, a new training phase is initiated.

Using heuristic methods, the method presented in [62] selects a minimal collection of representative optimization alternatives (function versions) for multiversioning structures while avoiding performance loss across accessible datasets and code size explosion. The method employs a novel mapping mechanism that utilizes decision trees or machine learning-based rule induction techniques to efficiently select the optimal code version at runtime depending on dataset features and to minimize selection overhead. This allows the production of static self-adjusting binaries or adaptive libraries that may modify their behavior and adapt to changing runtime settings without the need for complex recompilation structures. Thus, this methodology might efficiently pick the best versions of code at runtime while minimizing selection overheads, resulting in increased performance and code size efficiency, as well as higher adaptability and flexibility in comparison to standard static compilation techniques. The authors evaluated their strategies using the Open64 compiler [63].

"Multiversioning with Dynamic Access Edition" (*SMVDAE*) is the term given by the authors to a novel strategy proposed in [64]. This innovative approach aims to convert sequential code automatically at compile time in order to enable energy-efficient execution via decoupled access execution (*DAE*) [65]. This multiversion technique generates many access versions of a software application, ranging from lightweight versions that may be less efficient at preloading cached data to more complicated versions that may be more efficient but incur greater overhead. The optimal access version is chosen dynamically at runtime, thus bypassing the restrictions of static analysis. The main advantages of *SMVDAE* are the fact that it can effectively explore the space of optimized access versions at runtime, since multiversion is performed statically, and the fact that dynamic selection of the optimized version incurs minimum overhead. The method also contains a mechanism for identifying memory access patterns to determine which access phases are most effective for each task, which is useful for optimizing code in general.

"Cooperative Profile-Guided Optimization" [66] is a new technique that includes a new multiversion approach and code specialization method that can improve the performance of *GPUs* in interactive applications. This technique combines Profile-Guided Optimization (*PGO*) and Adaptive Optimization (*AO*). Cooperative *PGO*, like *AO*, functions most effectively in the context of a just-in-time (*JIT*) compilation virtual machine, as it is based on the dynamic construction of instrumented program variations for the collecting of profile data. *Cooperative PGO*, like *PGO*, employs previously gathered runtime profiles to guide future compilations. With *Cooperative PGO*, programmers do not need to guess which inputs are representative for their applications. *Cooperative PGO* considerably increases the number of versions that may be compared, which is the primary distinction between this method and conventional multi-versioning methods.

A methodology for implementing a *RegionSeeker* framework together with its extension Multiversioning has been developed in [67], which adds to the advancement of the *HW/SW* co-design field. The authors present effective solutions to the problem of choosing automatically which portions of an application should be synthesized to *HW*, given a particular area budget. The RegionSeeker-identified accelerators regularly beat those obtained by data stream-level methods and solely evaluating function-level possibilities, regardless of application size or area limits. The multiversioning strategy expands the initial set of possibilities by offering numerous optimized variants. Given an initial set of *HW* accelerators, i.e. a set of regions determined using the RegionSeeker framework, several variants of each area with the same functionality can be generated. Each version may utilize one or a mix of the optimizations determined by the writers.

Cardoso et al. [28] discuss the use of autotuning techniques to maximize the performance of a program automatically by modifying parameters or factors that affect program performance. This can be accomplished offline (i.e. statically at compile-time) utilizing heuristics and profiling to guide parameter settings for compile-time optimizations and code transformations, or online (i.e. dynamically at runtime) utilizing a combination of static analysis and profiling to create models and make code execution decisions. In the context of multiversion approaches, autotuning can be used to generate and tune several versions of a program for specific hardware and software platforms, thereby enhancing the performance of the program on those systems. Autotuning can be used within the framework of code specialization to generate and optimize automatically specialized versions of a program for particular input data or use cases. It is crucial to note that the efficacy of autotuning might vary depending on the application and platform being used, and that autotuning can be time-consuming and demand large computational resources.

### 2.3 Summary

In recent years, research into code optimization techniques for *HLS* and *FPGA* targets has increased. One of the primary advantages of code specialization for *HLS* and *FPGA* targets is that it permits designers to tailor the performance of their hardware systems for certain applications and/or workloads. This can be particularly beneficial for applications with demanding performance requirements, such as those found in multimedia, communications, and high-performance computing. Code specialization can also be used to reduce the size and complexity of hardware systems, which is useful for applications with resource limitations such as power, area, or cost.

In Section 2.2, we discussed the work presented on some of the most recent compilation techniques for code specialization using *HLS* and targeting *FPGAs*, as well as techniques that, despite presenting a vision aimed at enhancing software performance, can be useful for the development of new ideas for formulating solutions and developing other approaches. After analyzing the