FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Improving Safety of an Automotive AES-GCM Core and its Impact on Side-Channel Protection

Dany José Correia Teixeira

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor at FEUP: Prof. José Carlos Alves Second Supervisor at FEUP: Prof. Manuel Cândido Duarte dos Santos Supervisor at Synopsys: Eng. Pedro Costa

July 28, 2020

© Dany José Correia Teixeira, 2020

# Resumo

O incremento do número de componentes eletrónicos e o correspondente aumento do fluxo de dados no setor automóvel levou a uma preocupação crescente com a garantia de segurança dos sistemas eletrónicos, especialmente em sistemas críticos cuja violação seja passível de colocar em causa a integridade do sistema e a segurança das pessoas. A utilização de sistemas que implementam o Advanced Encryption Standard (AES) foi vista como uma solução para este problema, impedindo o acesso indevido aos dados dos veículos, através da sua encriptação.

O algoritmo AES não possui atualmente nenhuma vulnerabilidade efetiva, mas o mesmo não acontece com as suas implementações, as quais estão sujeitas a ataques ditos side-channel, onde informações que resultam da operação destas implementações são exploradas na tentativa de descobrir os dados encriptados. A aplicação de núcleos IP no setor automóvel requer que estes estejam em conformidade com a norma ISO-26262 de forma a garantir que a sua operação não compromete a segurança do veículo e dos ocupantes. Este cumprimento implica alterações na arquitetura dos sistemas que podem influenciar as características de operação que são normalmente exploradas em ataques para obter informação que eventualmente permita ganhar conhecimento sobre os dados encriptados. Assim, o desenvolvimento das componentes de segurança, na perspetiva da segurança informática da informação e no que se refere à segurança de operação do veículo e dos seus ocupantes, que são ainda consideradas como componentes independentes, podem na verdade estar relacionadas, já que as melhorias introduzidas para incrementar a resiliência a falhas e consequentemente a integridade de operação dos sistemas, podem aumentar a fragilidade do sistema a ataques que comprometam a segurança informática dos dados.

O presente trabalho tem como objetivo desenvolver uma arquitetura capaz de atingir as métricas para o nível mais alto de certificação em segurança de acordo com a norma ISO-26262 (certificação ASIL-D), a partir de uma arquitetura já existente, e comparar as duas arquiteturas em termos de vulnerabilidade a ataques ditos side-channel que exploram o seu consumo de potência dinâmica. Os resultados demonstram que para a arquitetura ASIL-D a identificação de pontos de interesse e de dados relevantes no consumo de potência é mais evidente, o que sugere existir uma maior vulnerabilidade da arquitetura desenvolvida a ataques desenvolvidos por esse processo. ii

# Abstract

The increase in electronic components and the corresponding increment in the data flow among electronic systems in automotive applications made security one of the main concerns in this sector. The use of IP cores that implement the Advanced Encryption Standard (AES) was seen as a solution to this problem, preventing improper access to vehicle data, through its encryption.

The AES algorithm does not currently have any effective vulnerability, but the same does not happen with its implementations, which are subject to side-channel attacks, where information that results from the operation of these implementations is exploited in an attempt to discover the encrypted data. The application of IP cores in the automotive sector requires the compliance of the implementations with the ISO-26262 standard in order to ensure that their operation does not compromise the vehicle's safety. For this compliance it is required changes in the core architecture that can influence the characteristics of operation that are normally exploited in attacks. Thus, the development of safety and security components in the automotive sector, which are still considered as independent processes, may be related since safety improvements may cause changes in the system's vulnerability to attacks that can compromise its security.

This work aims to develop an architecture capable of reaching the metrics for the highest level of safety certification (ASIL-D), based on an existing architecture, and compare the two architectures in terms of vulnerability to side-channel attacks that exploit their dynamic power consumption. The results show that for the ASIL-D architecture, the identification of points of interest and relevant data on the power consumption traces is more evident, which suggests greater effectiveness of the attacks performed in this architecture.

iv

# Acknowledgements

I would like to express my gratitude to my supervisor at FEUP, Professor José Carlos Alves, for all his interest, ideas and suggestions throughout this entire project and for always being available to help me. I am also grateful to Professor Manuel Cândido dos Santos for introducing me this opportunity and for the assistance he provided to make this project possible.

I would like to thank my supervisor at Synopsys, Eng. Pedro Costa, for his continued guidance, advice and help during the development of this dissertation. I would also like to thank Eng. Hugo Santos for all the support he provided me and for always being available to give me a hand. To both, Eng. Pedro Costa and Eng. Hugo Santos, I express my gratitude for helping me in this introduction to the FuSa world.

Finally, a special thanks to Inês Honrado for being there for me at all good and less good moments throughout these years, always willing to share the thoughts and kindness of an incredible person she is. To all my friends, colleagues and family, my sincere thanks. I deeply believe that every person in our life influences our development and, without them, I would not be the person I am.

Dany José Correia Teixeira

vi

"A ship in harbor is safe, but that is not what ships are built for."

John A. Shedd

viii

# Contents

| 1 | Intr       | oduction 1                                    |

|---|------------|-----------------------------------------------|

|   | 1.1        | Context                                       |

|   | 1.2        | Motivation                                    |

|   | 1.3        | Objectives                                    |

|   | 1.4        | Thesis Structure   3                          |

| 2 | Adv        | anced Encryption Standard 5                   |

|   | 2.1        | Introduction                                  |

|   | 2.2        | Algorithm Specification                       |

|   |            | 2.2.1 Introduction to Galois fields           |

|   |            | 2.2.2 Cipher                                  |

|   |            | 2.2.3 Inverse cipher                          |

|   | 2.3        | Galois/Counter Mode of Operation              |

|   | 2.4        | Automotive Applications                       |

| 3 | Side       | -Channel Attacks 15                           |

|   | 3.1        | Introduction                                  |

|   | 3.2        | Power Analysis                                |

|   |            | 3.2.1 Power Consumption in CMOS Devices       |

|   |            | 3.2.2 Power Analysis Attacks                  |

| 4 | Auto       | omotive Functional Safety 21                  |

|   | 4.1        | The ISO-26262 standard                        |

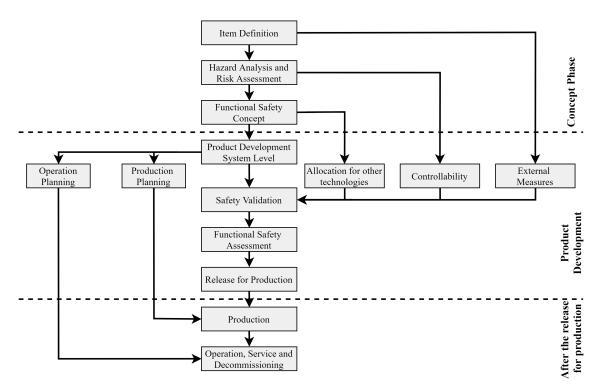

|   |            | 4.1.1 Safety Lifecycle                        |

|   |            | 4.1.2 Item Definition                         |

|   |            | 4.1.3 Hazard Analysis and Risk Assessment     |

|   |            | 4.1.4 Safety Element out of Context (SEooC)   |

|   |            | 4.1.5 Safety Concepts                         |

|   |            | 4.1.6 Hardware Evaluation Metrics             |

|   | 4.2        | Functional Safety and Security                |

| 5 | AES        | -GCM Safety Improvement 29                    |

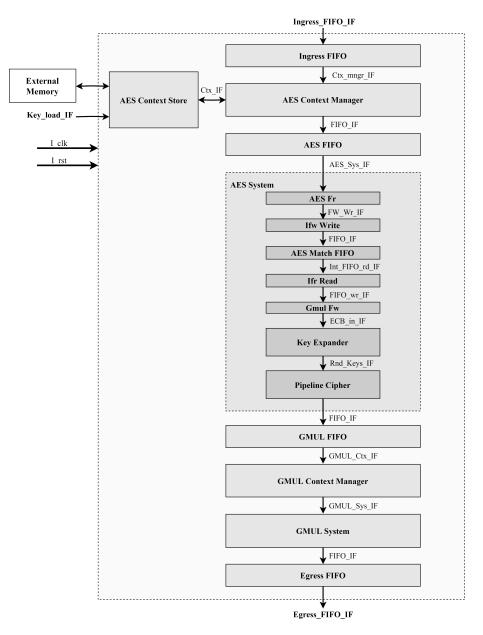

|   | 5.1        | AES-GCM IP Core                               |

|   | 0.11       | 5.1.1 Part Allocation for each Function       |

|   |            | 5.1.2         Core Configuration         31   |

|   | 5.2        | SEooC Definition                              |

|   | 5.2<br>5.3 | Functional Safety Concept       32            |

|   | 5.5        | 5.3.1       Safety Related Functions       32 |

|   |            | $J_{J_1}$ Juncty related 1 directoris         |

## CONTENTS

| Re | eferen             | ces     |                                                          | 63              |  |  |  |

|----|--------------------|---------|----------------------------------------------------------|-----------------|--|--|--|

| A  | Failu              | ure Mod | les, Effects, and Diagnostic Analysis (FMEDA)            | 59              |  |  |  |

| 8  | Con                | clusion | and Future Work                                          | 57              |  |  |  |

|    |                    | 7.3.2   | Plaintext Variation Effect                               |                 |  |  |  |

|    | , 10               | 7.3.1   | Key Variation Effect                                     |                 |  |  |  |

|    | 7.3                |         |                                                          |                 |  |  |  |

|    | 7.2                | -       | l Key Leaking Points Analysis                            |                 |  |  |  |

| 7  | <b>Resu</b><br>7.1 |         | evel Power Traces Analysis                               | <b>47</b><br>47 |  |  |  |

|    | 6.2                | Power   | Traces Processing                                        | 46              |  |  |  |

|    |                    | 6.1.3   | Power Estimation                                         |                 |  |  |  |

|    |                    | 6.1.2   | Simulation Environment                                   |                 |  |  |  |

|    |                    | 6.1.1   | Timing Information                                       |                 |  |  |  |

|    | 6.1                | Power   | Traces Extraction                                        |                 |  |  |  |

| 6  | Pow                | er Anal |                                                          | 43              |  |  |  |

|    |                    | 5.5.3   | FMEDA Results                                            | 41              |  |  |  |

|    |                    | 5.5.2   | Probabilistic Metric for Random Hardware Failures (PMHF) | 41              |  |  |  |

|    |                    | 5.5.1   | Single-Point Fault (SPFM) and Latent Fault Metrics (LFM) |                 |  |  |  |

|    | 5.5                |         | Modes, Effects, and Diagnostic Analysis (FMEDA)          |                 |  |  |  |

|    |                    | 5.4.3   | Assumptions of Use                                       | -               |  |  |  |

|    |                    | 5.4.2   | Safety Mechanisms                                        | -               |  |  |  |

|    | Э.т                | 5.4.1   | Failure Modes                                            | -               |  |  |  |

|    | 5.4                |         | cal Safety Concept                                       |                 |  |  |  |

|    |                    | 5.3.2   | Functional Safety Requirements                           |                 |  |  |  |

|    |                    | 5.3.2   | Safety Goals                                             | 32              |  |  |  |

# **List of Figures**

| Encryption and decryption in the AES algorithm.Representation of the ShiftRows transformation.Galois Counter Mode (GCM).                                                                                                                                                                     | 7<br>9<br>12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Side-channel leakage information.          Target Data DPA Attack.                                                                                                                                                                                                                           | 16<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Safety Lifecycle.                                                                                                                                                                                                                                                                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

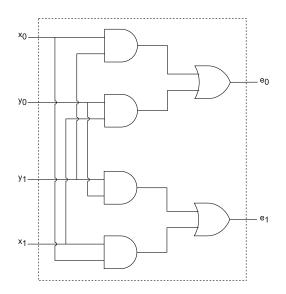

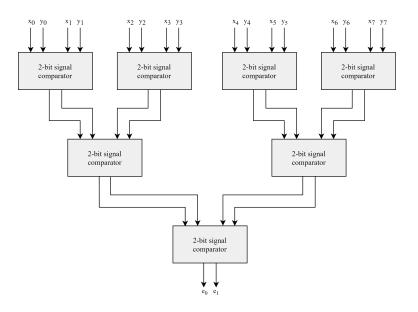

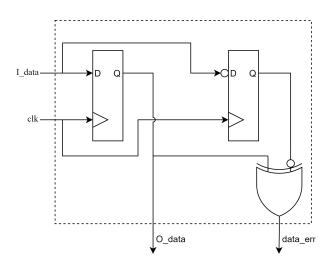

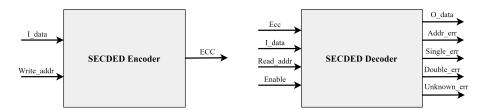

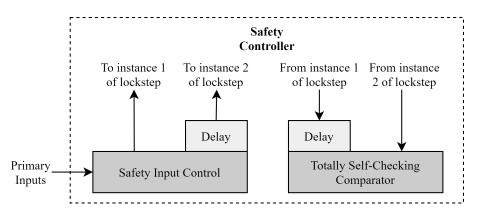

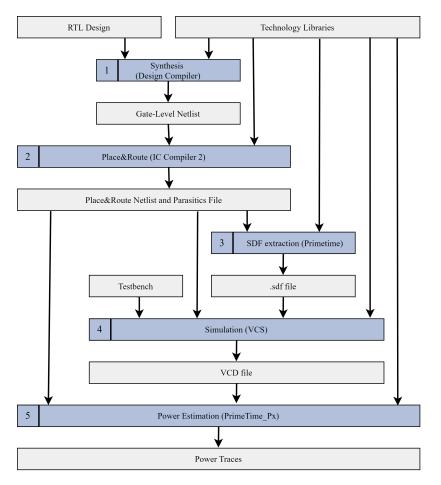

| AES-GCM IP Core Block Diagram.Totally Self-Checking 2-bit equality comparator.Totally Self-Checking 8-bit equality comparator.Concept of Safety Flip-Flop.Module Interface of SECDED Encoder and Decoder Modules.Safety Controller with data input control for the dual lock-step operation. | 30<br>36<br>36<br>37<br>38<br>38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Power Traces Extraction Flow.                                                                                                                                                                                                                                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

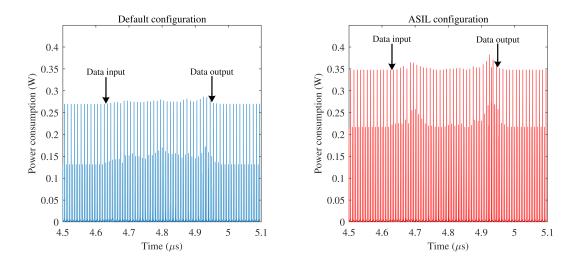

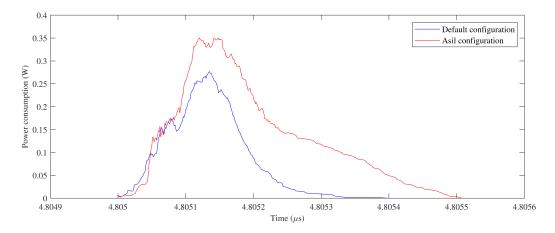

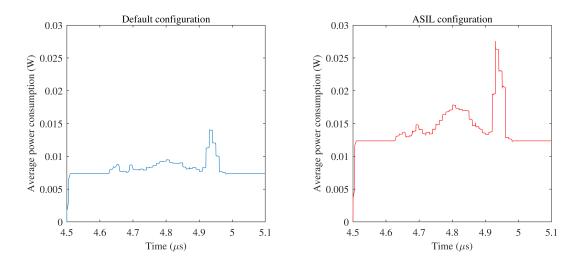

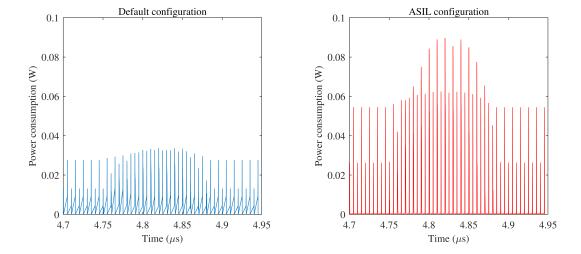

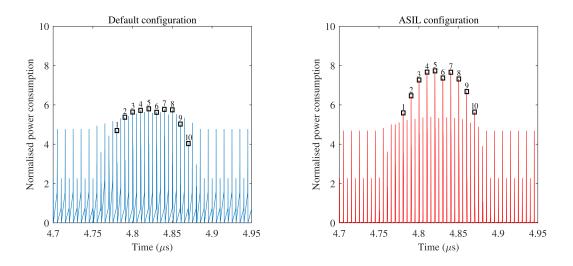

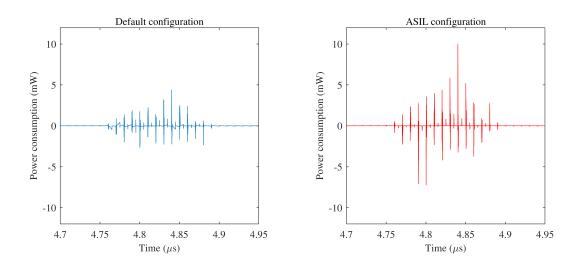

| AES-GCM power consumption for default and ASIL-D configurations Power peak comparison between default and ASIL-D configurations AES-GCM power consumption trace with a transformation of a moving-average window of 10 ms                                                                    | 48<br>49<br>50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

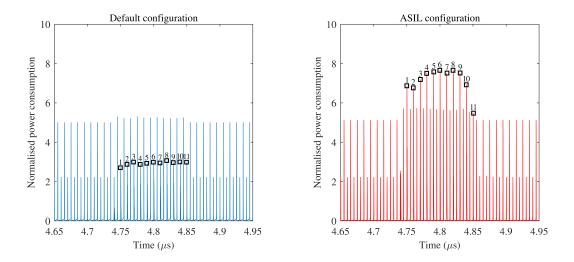

| Pipeline Cipher power consumption for default and ASIL-D configurations Pipeline cipher normalised power consumption for default and ASIL-D configurations                                                                                                                                   | 50<br>51<br>52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

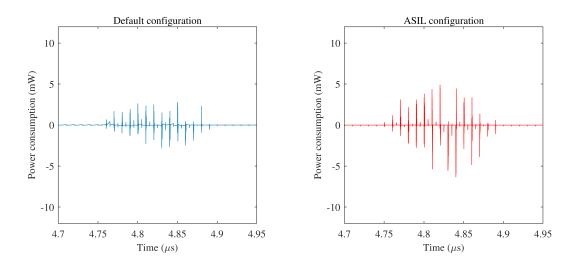

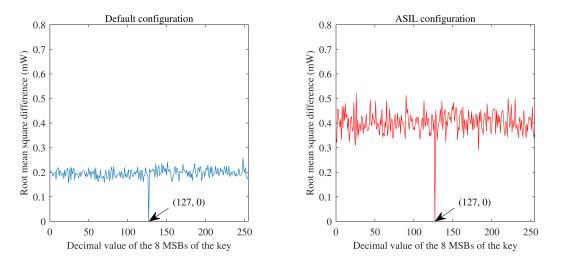

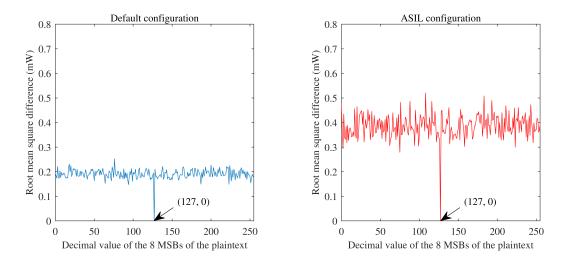

| tions                                                                                                                                                                                                                                                                                        | 52<br>53<br>54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| plaintext, for each configuration.                                                                                                                                                                                                                                                           | 55<br>55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                              | Representation of the ShiftRows transformation.       Galois Counter Mode (GCM).         Side-channel leakage information.       Target Data DPA Attack.         Safety Lifecycle.       Safety Lifecycle.         AES-GCM IP Core Block Diagram.       Totally Self-Checking 2-bit equality comparator.         Totally Self-Checking 8-bit equality comparator.       Totally Self-Checking 8-bit equality comparator.         Concept of Safety Flip-Flop.       Module Interface of SECDED Encoder and Decoder Modules.         Safety Controller with data input control for the dual lock-step operation.       Safety Controller with data input control for the dual lock-step operation.         Power Traces Extraction Flow.       AES-GCM power consumption for default and ASIL-D configurations.         Power peak comparison between default and ASIL-D configurations.       Pipeline Cipher power consumption for default and ASIL-D configurations.         Pipeline Cipher power consumption for default and ASIL-D configurations.       Pipeline cipher power consumption for default and ASIL-D configurations.         Pipeline cipher normalised power consumption for default and ASIL-D configurations.       Pipeline cipher normalised power consumption for default and ASIL-D configurations.         Pipeline cipher normalised power consumption for default and ASIL-D configurations.       Pipeline cipher power consumption difference due to a variation of one byte in the encryption key, for each configuration.         Pipeline cipher power consumption difference due to a variation of one byte in the |

# **List of Tables**

| 4.1 | ASIL determination based on the Probability of Exposure (E), Severity (S) and   |    |

|-----|---------------------------------------------------------------------------------|----|

|     | Controllability (C).                                                            | 24 |

| 4.2 | Reference target values defined by ISO 26262 for SPF, LF and PHMF metrics       | 27 |

| 4.3 | Examples of ASIL ratings for different vehicle systems                          | 28 |

| - 1 |                                                                                 |    |

| 5.1 | Safety Goals (SG) for the AES-GCM ASIL-D.                                       | 33 |

| 5.2 | Functional Safety Requirements (FSR) derived from the Safety Goals (SG) for the |    |

|     | AES-GCM ASIL-D.                                                                 | 33 |

| 5.3 | Results for the SPFM, LFM and PMHF metrics                                      | 41 |

|     |                                                                                 |    |

# Abbreviations

| AAD        | Additional Authenticated Data                   |

|------------|-------------------------------------------------|

| AES        | Advanced Encryption Standard                    |

| ASIC       | Application-Specific Integrated Circuit         |

| ASIL       | Automotive Safety Integrity Level               |

| CBC        | Cipher Block Chaining Mode                      |

| CFB        | Cipher Feedback Mode                            |

| CTR        | Counter Mode                                    |

| DES        | Data Encryption Standard                        |

| DES<br>DPA | Differential Power Analysis                     |

| ECB        | Electronic CodeBook Mode                        |

| ECU        | Electronic Codebook Mode                        |

| ECO        | Electronic Design Automation                    |

|            | -                                               |

| FIPS       | Federal Information Processing Standard         |

| FIT        | Failure In Time                                 |

| FMEDA      | Failure Modes, Effects, and Diagnostic Analysis |

| FPGA       | Field-Programmable Gate Array                   |

| GCM        | Galois Counter Mode                             |

| GF         | Galois Field                                    |

| HARA       | Hazard Analysis and Risk Assessment             |

| HSM        | Hardware Secure Module                          |

| IBM        | International Business Machines                 |

| IEC        | International Electrotechnical Commission       |

| IP         | Intellectual Property                           |

| ISO        | International Organization for Standardization  |

| IV         | Initialization Vector                           |

| MAC        | Message Authentication Code                     |

| MCU        | Micro-controller Unit                           |

| NIST       | National Institute of Standards and Technology  |

| NSA        | National Security Agency                        |

| OFB        | Output Feedback Mode                            |

| RTL        | Register Transfer Level                         |

| SDF        | Standard Delay Format                           |

| SEooC      | Safety Element out of Context                   |

| SHE        | Secure Hardware Extension                       |

| SPA        | Simple Power Analysis                           |

| TCL        | Tool Command Language                           |

| UVM        | Universal Verification Methodology              |

| VCD        | Value Change Dump                               |

|            |                                                 |

## Chapter 1

# Introduction

## 1.1 Context

The technology evolution implied a considerable increase in the information exchanged between systems. As a result, the need to preserve the integrity, availability and confidentiality of systems has become not only a priority for governments and their military purposes but all businesses, organisations and the general population, leading to the creation of multiple encryption systems by private organisations. These systems were found to have considerably different characteristics between them, making their usage and interoperability a problem. In order to solve this, the National Institute of Standards and Technology (NIST) (at that time called National Bureau of Standards) started, in 1973, a public request for proposals of cryptography algorithms that could be used to create a cryptography standard. An algorithm, based on Lucifer cypher, was proposed by IBM and analysed and adjusted by the National Security Agency (NSA), resulting in a federal standard that was used for over 20 years, the Data Encryption Standard (DES) [1]. The DES was, however, only empirically secure and the progressive increase in the computational processing power of the technology evidenced some vulnerabilities in the standard, as shown in [2].

The NIST started then, in 1997, a process to select the most suitable algorithm for a new standard that could solve the flaws of the previous one and establish a new reference in the security domain. The selection criteria were not only the algorithm's security but also its performance, efficiency, ease of implementation (in hardware, software and firmware) and flexibility [3]. The algorithm that was selected to establish the new Federal Information Processing Standard (FIPS) was Rijndael, and the standard was named the Advanced Encryption Standard (AES).

Despite the apparent absence of vulnerabilities in the algorithm, the same does not seem to happen with the respective implementations. The security of the implementations has been largely exploited through side-channel attacks, where the implementation characteristics such as the power consumption or the electromagnetic emission are analysed, in an attempt to extract hints that allow the identification of the data being processed. In the case of the AES, these attacks focus in reveal the key which will allow the decryption of all data that has been encrypted using that key. Since implementations of the AES are used in the automotive industry to protect sensitive data that flows through communications and, consequently, to protect against attacks critical safety elements, these weaknesses in security can also create vulnerabilities in the safety domain.

The automotive sector defines the ISO-26262 as the leading standard for granting a qualitative assessment of the risk of hazardous operational events that may induce safety failures, expressed in the form of an Automotive Safety Integrity Level (ASIL), which reveals if the component meets the imposed safety requirements.

## **1.2** Motivation

The automotive industry is one of the sectors where the developed systems require compliance with specific safety metrics to ensure that in case of a system malfunction or failure, the people and the environment involved do not suffer an increase in their level of risk. This awareness of the importance of safety for the automotive industry is well described by ISO-26262 standard, which defines all the regulations and recommendations for the development of a safe system along all the development phases, including the definition of risk classes that are attributed to components according to the exposure, controllability and severity of the risks. The first edition of this standard that dates from 2011 has, however, a considerable flaw in the approach of security concerns and its implications in the safety domain. With the increase in the information that is necessary to store and transfer to support all the features present in modern vehicles, concerns about the unauthorised access and modification of this data are gaining a relevant consideration. Proof of this is that a revision to the ISO-26262 standard published in 2018, already considers some references to cyber security and a new part only about the application of the standard to semiconductors.

The AES has been used in the last few years as one of the data encryption mechanisms in the automotive industry to protect sensitive data, usually in the form of hardware implementations. Due to the complexity of the operations executed in each data decryption and considering the processing power of today's computers, brute force attacks, which are normally the simplest way to break a cryptographic algorithm, would take billions of years, even considering millions of computers working in parallel, to test the  $2^{128}$  possible key combinations for a key of 128 bits, making this method impracticable. Thus, the algorithm itself still provides a substantial level of protection for the system. The flaws arise only in the hardware that implements the algorithm, either through debug mechanisms, which exist in current integrated circuits due to their complexity (and which open the possibility for fault injection attacks) or by analysis of the physical parameters of the core, which can provide information about the encryption key.

The implementations for the automotive industry present, therefore, two main limitations in the security domain. On the one hand, a standard that defines in detail the safety demands for a safety-critical system but that does not fully address the relationship between a safe system and a secure system and, on the other hand, the existence of exposure to attacks that these systems present, due to their implementation properties, and which can compromise them. Those two limitations do not seem although to be completely independent, as shown in [4], with the possibility to interconnect them, analysing the actual existence of exposure to attacks in the IP core and the impact that the

## 1.3 Objectives

Synopsys currently has an IP core which implements the AES in the Galois Counter Mode (GCM) of operation, used in automotive applications but without any safety integrity level (ASIL) certification according to ISO-26262. The first objective of this dissertation is to implement safety measures in the current design in order to meet the metrics for an ASIL-D certification, following the specifications of the ISO-26262 standard. Then, the objective is to analyse both systems (with and without safety mechanisms) in terms of exposure to power consumption based side-channel attacks. A comparison between both systems will provide an assessment of the impact of the safety mechanisms on security, from where conclusions between the safety and security domains may be extracted. These conclusions can provide useful information for future works that require safety enhancements so that they are developed without increase the security vulnerabilities of the design.

## **1.4 Thesis Structure**

This introduction in chapter 1 provides a contextualisation about the development of the Advanced Encryption Standard (AES) and the problems that this security solution is facing with its adaptation for automotive safety applications.

Chapter 2 explains the principles of operation of the AES and chapter 3 details how AES implementations are exploited in an attempt to find the information being protected.

Chapter 4 describes the process to ensure functional safety in the automotive industry, according to the international standard ISO-26262, and chapter 5 describes how this process was applied in this work to develop an AES IP core compliant with the highest automotive safety integrity level.

Chapter 6 explains the approach used to compare the security vulnerabilities of the original configuration and the developed safety enhanced configuration. Chapter 7 presents the results of this comparison and a discussion of their meaning.

Chapter 8 presents the conclusions about the work developed and provides a brief discussion of possible future work.

Introduction

## **Chapter 2**

# **Advanced Encryption Standard**

This chapter presents an introduction to the Advanced Encryption Standard (AES), where the cipher and inverse cipher processes are explained. Then, a detailed description of the Galois/Counter mode is provided along with a summary of the advantages of this operation mode. At the end of the chapter, some applications of the AES for the automotive industry are identified, which justify the relevance of the algorithm for this sector.

### 2.1 Introduction

The AES is, since 2001, a federal government standard established by the U.S. National Institute of Standards and Technology (NIST) for the encryption of electronic data. The cryptographic algorithm used in the standard was the result of a four-year selection process, which involved cooperation between the U.S. government and private organisations from the entire world to obtain a publicly disclosed algorithm, available in a royalty-free basis worldwide. The minimum restrictions imposed on candidates were the use of symmetric key cryptography as a block cipher, with support for 128 bits size blocks and key sizes of 128, 192 and 256 bits. From the selection came out five finalists: MARS, RC6<sup>TM</sup>, Rijndael, Serpent and Twofish. All finalists are iterated block ciphers, which means that the same transformations are applied a given number of times, either for encryption or decryption, where each one of these iterations is called a round. The evaluation criteria for the finalists were mainly focused on three domains: the algorithm's security, computational cost and implementation characteristics. Security was the most relevant factor, and all five algorithms met the security needs established by NIST. In the cost domain, computational performance metrics such as the efficiency in terms of speed and memory usage were assessed. Finally, the third domain evaluated the flexibility, the suitability for hardware and software implementations and the simplicity of the implementations. The final decision was for algorithm Rijndael, which adopted the designation of AES algorithm [3].

The AES allows both encryption and decryption operations. In the encryption, a message (plaintext) is converted into encrypted code (ciphertext), using a secret encryption key. In the

decryption, the plaintext is recovered from the ciphertext using the same key that was used for the encryption.

### 2.2 Algorithm Specification

The operations performed in the AES algorithm use blocks of 128 bits, where the input data is arranged in a two-dimensional array of bytes called State. The AES was designed to allow different block sizes than 128 bits, and this difference is reflected in the number of columns of the State since this number is given by the block size divided by 32. The number of rows is independent of the block size and is equal to four. Thus, in the AES, the operations are performed in a 4x4 matrix, where s[r, c] identifies each position of the array. The conversions from the input array to the State and from the State, after the operations, to the output array are given by equations 2.1 and 2.2, respectively, which were extracted from [5].

$$s[r,c] = in[r+4c]$$

for  $0 \le r \le 3$  and  $0 \le c \le 3$  (2.1)

$$out[r+4c] = s[r,c]$$

for  $0 \le r \le 3$  and  $0 \le c \le 3$  (2.2)

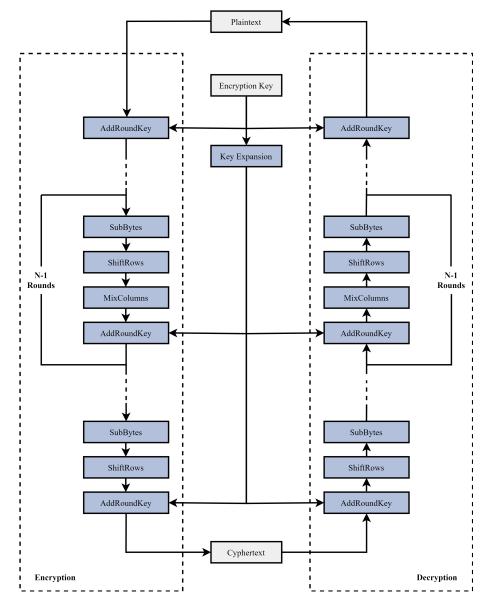

The number of rounds in the encryption and decryption is dependent on the key size. For the key sizes 128, 192, 256 the number of rounds is 10, 12 and 14, respectively. Each round, with the exception of the final round, is composed of four functions: AddRoundKey, SubBytes, ShiftRows and MixColumns. The final round does not have the MixColumns function, which permits symmetrical executions for the encryption and decryption. Thus, the decryption can be considered as the inverse process of the encryption, as shown in figure 2.1.

For the sake of clarity, we consider an application scenario where the encryption of the plain data is done by a system (the transmitter) to send securely data to another system (the receiver) that will decrypt the received secure data to gain access to the plain data.

#### 2.2.1 Introduction to Galois fields

In the data encryption process, the AES algorithm interprets each byte as an element from a finite field, also known as Galois Field (GF), which corresponds to a set with a finite number of elements were the mathematical operations (additions, subtractions, inversions and multiplications) can be easily and effectively computed when the operands are represented in binary forms. In the AES, the finite field considers polynomials of degree seven and is denoted by  $GF(2^8)$ , where each set contains 256 elements. The AES only uses the addition and multiplication operations between finite fields. However, these two operations are more complex and require more steps than the same operations in the euclidean space.

The addition in finite fields is an exclusive-OR (XOR) between the coefficients of the corresponding powers of the operands. Due to the nature of the operation, the result, which is represented with eight bits, is never affected by overflow events.

Figure 2.1: Encryption and decryption in the AES algorithm.

The multiplication in finite fields is more complex than the addition and the entire operation cannot be represented by a simple operator. The operation consists of the multiplication between the polynomials, modulo an irreducible polynomial of degree 8, which ensures that, as in the addition, the result is always a polynomial with a degree less than 8 and, therefore, can be represented using only one byte. Considering a(x) and b(x) as the operands and m(x) as the irreducible polynomial, the result c(x) can be determined by equation 2.3.

$$c(x) = (a(x) \cdot b(x)) \mod(m(x))$$

(2.3)

The irreducible polynomial m(x) is defined in the AES specification and is given by:

$$m(x) = x^8 + x^4 + x^3 + x + 1$$

(2.4)

#### 2.2.2 Cipher

Each AES round computed during the encryption phase consists of the four functions already mentioned, which describe three main transformations that are applied to the State matrix in each iteration:

- A key addition, in which a round key is XORed to the State in the function AddRoundKey.

- A byte substitution that performs a nonlinear transformation on each byte of the State using the function SubBytes.

- A bit diffusion of all State bits, first using the ShiftRows function and then the Mixcolumns function.

Each function processes a complete block of data (128 bits) at a time, but the functions are applied at a byte level, making the AES a byte-oriented cipher [6].

#### 2.2.2.1 SubBytes

The SubBytes function uses a transformation table, called S-Box, to map and replace each byte of the State with a value in the table. This is a non-linear transformation and each one of the 256 possible inputs is one-to-one mapped with an output. The S-Box results from two steps: first from the multiplicative inverse in the finite field  $GF(2^8)$  and then from an affine transformation in GF(2). This affine transformation is expressed in equation 2.5, extracted from [5], where  $b_i$  is the  $i^{\text{th}}$  bit of the byte and  $c_i$  is the  $i^{\text{th}}$  bit of a fixed byte with value {63}, in hexadecimal. The  $b'_i$  is the new value that will replace  $b_i$  in the State.

$$b'_{i} = b_{i} \oplus b_{(i+4) \mod 8} \oplus b_{(i+5) \mod 8} \oplus b_{(i+6) \mod 8} \oplus b_{(i+7) \mod 8} \oplus c_{i}$$

$$(2.5)$$

The S-Box applied in the AES for the 16 bytes of the State is the same and is defined in the AES specification [5].

#### 2.2.2.2 ShiftRows

The ShiftRows function applies a specific cyclic shift to each row of the State. This shift is equal to the index of the row minus one and cyclically moves the elements to the left. Thus, the positions on the first row remain the same (zero positions shift), the second row moves one position to the left and the third and fourth rows move two and three positions, respectively. This transformation is illustrated in Figure 2.2.

#### 2.2 Algorithm Specification

| S <sub>0,0</sub> | S <sub>0,1</sub> | S <sub>0,2</sub> | S <sub>0,3</sub> |           | S <sub>0,0</sub> | S <sub>0,1</sub> | S <sub>0,2</sub> | S <sub>0,3</sub> |

|------------------|------------------|------------------|------------------|-----------|------------------|------------------|------------------|------------------|

| S <sub>1,0</sub> | S <sub>1,1</sub> | S <sub>1,2</sub> | S <sub>1,3</sub> | ShiftRows | S <sub>1,1</sub> | S <sub>1,2</sub> | S <sub>1,3</sub> | S <sub>1,0</sub> |

| S <sub>2,0</sub> | S <sub>2,1</sub> | S <sub>2,2</sub> | S <sub>2,3</sub> |           | S <sub>2,2</sub> | S <sub>2,3</sub> | S <sub>2,0</sub> | S <sub>2,1</sub> |

| S <sub>3,0</sub> | S <sub>3,1</sub> | S <sub>3,2</sub> | S <sub>3,3</sub> |           | S <sub>3,3</sub> | S <sub>3,0</sub> | S <sub>3,1</sub> | S <sub>3,2</sub> |

Figure 2.2: Representation of the ShiftRows transformation.

#### 2.2.2.3 MixColumns

The MixColumns function operates over each column of the State, mixing each byte of the column with the other three bytes. Each column is converted in a polynomial and multiplied by a fixed 4x4 matrix, where each row is the polynomial given in 2.6 with a cyclic shift of three, two, one and zero positions to the left for the first, second, third and fourth row, respectively. Thus, the new values for each State column can be calculated using the equation in 2.7, extracted from [5].

$$a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$$

(2.6)

$$\begin{bmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix} \quad \text{for } 0 \le c \le 3$$

$$(2.7)$$

#### 2.2.2.4 AddRoundKey

The AddRoundKey function performs a bitwise XOR (which is the same as a Galois Field addition) between the State and a round key. Each round key is obtained from the original key in a process known as Key Expansion. This process generates a number of keys equal to the number of rounds plus one, where the first key is used at the beginning of the algorithm, before the initialisation of the first round. Each key expansion generates a 4-byte word (32 bits), denoted by  $[w_i]$ . These words are aligned in an array called key schedule. Considering that the algorithm requires four words of key data to XOR with each data block (that is also composed of four words), for  $N_r$  rounds, the dimensions of the key schedule is given by  $4(N_r+1)$  rows per one column. The number of words in the key is denoted by  $N_k$  and, as said earlier, is equal to 4, 6 or 8, depending on whether the key size is 128, 192 or 256 bits, respectively.

The first words in the key schedule are the words of the original key, and so, the first key generated is the same as the original key. The generation of words for the remaining keys is given by one of the following cases:

1. If the word is in a position multiple of  $N_k$ , the result will be given by an XOR between the previous word modified (w[i-1]) and a round constant. The modification done to the word

[i-1] is a cyclic shift of one byte to the right followed by the application of the S-Box to the four bytes in the word. The round constant is given by  $[x^{i-1}, \{0,0\}, \{0,0\}, \{0,0\}]$ , where *x* is equal to  $\{02\}$  and  $x^{i-1}$  are powers of *x*.

2. Otherwise, the word w[i] is simply the result of the XOR between the previous word (w[i - 1]) and the word  $N_k$  positions before ( $w[i - N_k]$ ).

#### 2.2.3 Inverse cipher

The AES decryption is done with the inverse of the functions in the reverse order of the encryption. Thus, in the decryption, the ShiftRows, SubBytes, MixColumns functions are designated by InvShiftRows, InvSubBytes and InvMixColumns. The AddRoundKey function does not need an inverse version, as it applies only an XOR operation between two terms, and then, the function and its inverse are the same.

#### 2.2.3.1 InvShiftRows

In the InvShiftRows, each row of the State is cyclically shifted in the opposite direction that was used during the ShiftRows function. Thus, the bytes in the first row remain in the same position and the bytes in the second, third and fourth rows shift one, two and three positions to the right, respectively.

#### 2.2.3.2 InvSubBytes

The InvSubBytes apply the inverse of the S-Box that was used during the SubBytes function, to each byte. The inverse of the S-Box is generated using the inverse of the affine transformation stated above, followed by the multiplicative inverse in  $GF(2^8)$ .

#### 2.2.3.3 InvMixColumns

The InvMixColumns is also the inversion of the MixColumns function, where instead of the polynomial referred in 2.6, is used its inverse, described in 2.8.

$$a^{-1}(x) = \{0b\}x^3 + \{0d\}x^2 + \{09\}x + \{0e\}$$

(2.8)

From this, results a different matrix from the one illustrated in 2.7, that gives rise to the expression in 2.9.

$$\begin{bmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{bmatrix} = \begin{bmatrix} 0e & 0b & 0d & 09 \\ 09 & 0e & 0b & 0d \\ 0d & 09 & 0e & 0b \\ 0b & 0d & 09 & 0e \end{bmatrix} \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix}$$

for  $0 \le c \le 3$  (2.9)

#### 2.2.3.4 AddRoundKey

The operations of the AddRoundKey during the encryption and the decryption are similar with the exception for the key schedule, which in the decryption is in the reverse order of the one used during the encryption. This means that, before the decryption initialisation, it is necessary to compute all the Nr+1 round keys and store them in memory. Then, the last computed key will be the first to be used.

### 2.3 Galois/Counter Mode of Operation

The AES, as a block cipher algorithm, has different modes of operation that were designed to complement the algorithm or adapt it for specific purposes. Initially, NIST proposed four modes of operation: the Electronic CodeBook (ECB) mode, the Cipher Block Chaining (CBC) mode, the Cipher Feedback (CFB) mode and the Output Feedback (OFB) mode. The Counter (CTR) mode was added later and received considerable interest in the industry due to its potential for applications in the domains of Network and IP Security [2]. These modes, however, only provide data confidentiality, preventing unauthorised access to the information, but do not guarantee authentication and data integrity. To establish a connection between both characteristics, another mode of operation called the Galois Counter Mode (GCM) has been proposed [7]. This algorithm results from an adaptation of the CTR mode, with the advantages of authenticating and certifying data integrity.

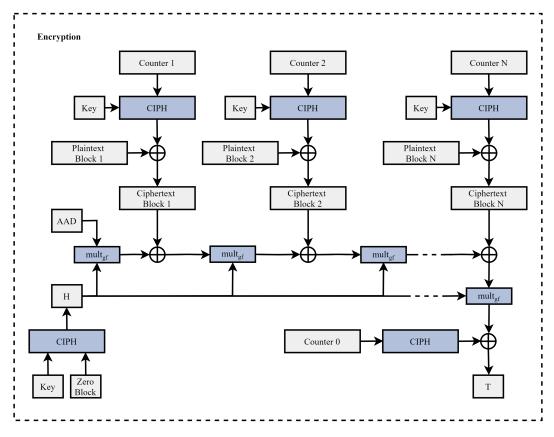

To perform the encryption, the GCM requires an additional set of inputs called counters, where each one of these counters must have a unique value for each plaintext block that is encrypted. Usually, only one initial random value for the counter is provided to the system and the other counters result from a sequential increment by one, for each new plaintext block [8].

The encryption process starts then with the increment of the initial counter and the resulting value is encrypted using the AES algorithm and XORed with the first block of plaintext. The subsequent blocks of plaintext follow the same procedure: before the XOR, the associated counters are incremented and then encrypted. In the decryption, the operations involved are the same but blocks of ciphertext substitute the plaintext blocks and the result of the operation are blocks of plaintext.

In the authentication, the objective is to protect another string known as Additional Authenticated Data (AAD), which is introduced in the system as an input and normally contains information about the plaintext and how it should be interpreted. The authentication requires a hash subkey (H) that results from the encryption of the zero block (a block composed by 128 zeros). The authentication is then executed through a chain of Galois field multiplications: for each block of plaintext, an intermediate authentication parameter  $g_i$  is generated from an XOR between the block of ciphertext from the encryption and the parameter  $g_{i-1}$  multiplied by the subkey H. The final result of this chain is the authentication tag (T), also called the Message Authentication Code (MAC). The authenticity of the data is verified in the decryption when the receiver computes the authentication tag from the data received (T) and compares it with the authentication tag from the encryption (T). If both match, the information was not modified in the transmission and the sender authenticity is guaranteed [6]. Figure 2.3 shows the block diagram of the GCM mode of operation, where the *CIPH* operation denotes the AES cipher, and the *mult<sub>gf</sub>* denotes a Galois field multiplication.

Figure 2.3: Galois Counter Mode (GCM).

The use in the GCM mode of the same encryption methodology as the CTR mode confers the GCM the same advantages that the CTR has when compared to the other modes of operation:

- A higher efficiency, since the encryption and decryption of data blocks is not dependent on the previous ones. This allows the computation in parallel of multiple blocks, which is particularly attractive for increasing the throughput in hardware implementations.

- The possibility for pre-processing, considering that the operation before each XOR is not dependent from the plaintext (for the encryption) or the ciphertext (for the decryption), allowing the computation of these values before the arrival of the plaintext. With pre-processing, the inverse blocks can be obtained from a simple XOR operation.

- The random access to each ciphertext (for the encryption) or plaintext (for the decryption) is possible and depends only on knowing the counter value that was used and the inverse block.

• The similarity between the encryption and the decryption that only differs in the type of input block (plaintext or ciphertext), allowing the use of the same logic for encryption and decryption.

### **2.4** Automotive Applications

In today's world, automobiles became tremendously essential in our quotidian, which caused the automotive industry to evolve in the way of transforming the traditional and purely mechanical vehicles, in environments capable of fulfilling their purpose of locomotion but with more comfort, entertainment, safety and with the ability to automate and integrate some of our daily tasks. This improvement was possible due to the technological innovation that allowed the integration of a large number of embedded systems called Electronic Control Units (ECU) in the vehicles and which, through their interconnection, made possible all the features that the modern vehicles provide us. The drawback of these improvements was the additional security risks that came from the inclusion and communication of multiple electronic devices, which led to the application of the AES to the automotive industry.

This increase in security awareness tends to continue to grow, as several developments (which require data protection) are still expected in the automotive market, as stated in [9], and which include:

- The usage of reprogrammable ECUs which implies the protection of the reprogramming process to avoid unintended access and, consequently, improper operation of these devices.

- The evolution of autonomous driving which implies the wireless communication of the cars with the involving environments and other cars, requiring strong protection of these communications.

- The evolution of the vehicles' infotainment systems which will probably evolve towards the remote access to contents and which will require updates to continue working according to the needs of those contents.

- The evolution of remote monitoring systems for vehicles such as highway tolls, tachographs and emergency systems that need to be protected to avoid non-legal uses.

- The advance of electronic systems for localisation of vehicles in case of theft, for example, which will imply strict measures of privacy and confidentiality.

In the literature there are already multiple approaches for some of these concerns that use the AES as a solution for data protection: in [10], a hardware implementation of AES is suggested for message encryption in real-time for on-board networking automotive systems; in [11] the AES algorithm is used to secure the exchange of multimedia messages (such as voice commands) between vehicles, using communication infrastructures that are located aside the roads (Road-Side units) and in [12] a remote keyless system for vehicles is proposed using the AES to secure the

communication between the key fob (handled by the driver) and the radio device located in the vehicle, which receives commands and distributes instructions for other components.

The problem of security has also been addressed by the automakers and the automotive engineering community, and diverse specifications, standards and guidelines have been proposed over the time, normally in the form of hardware security modules that were intended to be included in vehicles. Of all the proposals, two were considered as having good potential: the Secure Hardware Extension (SHE) specification [13] and the E-safety Vehicle Intrusion proTected Application (EVITA) project [14]. In both, the AES algorithm was suggested to ensure the privacy, integrity and authenticity of data.

Thus, the evolution of the automotive industry increasingly requires data protection in vehicles to prevent unauthorised access to data. Moreover, since the AES is currently the most recommended standard for this purpose, it is likely that its use will be more and more frequent in the future.

## Chapter 3

# **Side-Channel Attacks**

In this chapter, it is introduced the concept of side-channel attacks and explained how implementations are vulnerable to this type of attacks. A detailed description of side-channel attacks based on power consumption is also presented, as well as the attack methodologies that are normally used to extract information from the power consumption.

## 3.1 Introduction

The main purpose of cryptography is to maintain the data confidentially from third parties who do not have the right to access it. However, cryptography is an area that requires constant improvement since a system that is secure at this time, may not be in the future. The development of a cryptographic algorithm takes into account the vulnerabilities of the current algorithms and predicts some flaws that may arise from the evolution of the techniques and processing of computers but, at some point, the algorithms and respective implementations begin to evidence vulnerabilities that can be exploited in attacks. This implies that, over time, the algorithms need to be revised or, if not possible, replaced by new and more secure algorithms. In the case of the AES, its proposal came from the need to address existing vulnerabilities in the DES and therefore, it was developed so that obvious and simple attacks such as using brute force to test all the possible key combinations were not feasible [15].

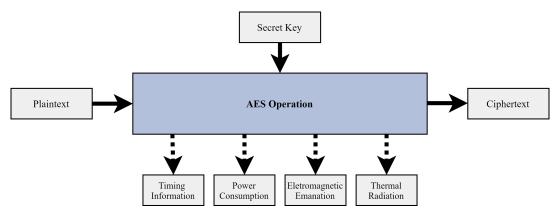

The attention to flaws that exist in the extensive and rigorous processes of selection and refinement of the algorithms is not possible, however, in their implementations. The implementation of an algorithm can be done by diverse entities, using diverse techniques that can comply with the official specification of the algorithm, but which can be compromised by their operation. There are complementary standards such as the FIPS 140-3 [16] which define requirements and procedures that must be followed when implementing the algorithm, to reduce the obvious weaknesses that can compromise the security of the system. Nevertheless, it is not possible to cover and solve all possible flaws that may exist in the implementations and the solution for some of them may even enhance others. For this reason, most attacks do not focus on the vulnerabilities of the algorithm, but on the characteristics of the implementation, as it happens in the side-channel attacks. The side-channel attacks are based on the leakage of physical information which results from the operation of the implementations and which is dependent on the input data, as illustrated in 3.1. This relation between the leakage information and the input data can be used to extrapolate the sensitive data of the system, such as the encryption key, giving access to all the encrypted data. Side-channel attacks typically focus on timing information, electromagnetic emanations, thermal radiation or power consumption patterns, since this is information that can be extracted externally from the device, using non-invasive methods, and without interfering with the device operation. These characteristics allow the execution of theses attacks without the need for expensive equipment and the possibility of harm to the device under attack [17].

Figure 3.1: Side-channel leakage information.

## 3.2 Power Analysis

The power analysis takes advantage of the power consumption patterns that result from the operation of the device and its dependency on the instructions executed and the input values. From the power consumption traces of a device, it is possible to detect the different phases of encryption and from their variations is possible to extract information about the encryption key. The predominance of CMOS gates in digital circuits and their respective typical dynamic power consumption are the main justification for this variability in power traces [17].

The low complexity and low cost to execute these attacks, associated with its high potential of success when compared with other side-channel attacks, made these attacks the main focus of investigation leading to the development of multiple methodologies to extract information from the power traces. The most common attacks are the Simple Power Analysis (SPA), the Differential Power Analysis (DPA), the Correlation Power Analysis (CPA) and the template attacks.

#### 3.2.1 Power Consumption in CMOS Devices

The power consumption in CMOS devices can be divided in two main components: the static and the dynamic power consumption. The static power consumption corresponds to leakage currents that flow in the device even when it is not switching. These leakage currents are essentially due to

subthreshold leakage and gate leakage currents. The dynamic power consumption comprehends the energy consumed charging and discharging the circuit capacitances during the switching activity and the small short-circuit currents that flow through the low impedance paths that are created between the supply and the ground when switching [18]. The equation 3.1 specifies the components of the total power consumption which includes the contribution of the three types of dissipation described. In the switching component, the  $C_L$  is the load capacitance of the circuit,  $f_{clk}$  is the clock frequency and the  $\alpha_{0\rightarrow 1}$  is a factor associated with the node transition activity. In the short-circuit component the  $I_{SC}$  is the average short-circuit current during a transition and in the leakage component  $I_{leakage}$  is the leakage current.

$$P_{\text{total}} = P_{\text{switching}} + P_{\text{short-circuit}} + P_{\text{leakage}} = \alpha_{0 \to 1} \cdot C_{\text{L}} \cdot V_{\text{dd}}^2 \cdot f_{\text{clk}} + I_{\text{sc}} \cdot v_{\text{dd}} + I_{\text{leakage}} \cdot V_{\text{dd}} \quad (3.1)$$

Each one of these components of the power consumption in CMOS devices will then be reflected in the power traces. The power traces can also be divided into components, which are: an operation-dependent component ( $P_{op}$ ), a data-dependent component ( $P_{data}$ ), a constant component ( $P_{const.}$ ) and a noise component ( $P_{noise}$ ). The  $P_{switching}$  and  $P_{short-circuit}$  of CMOS devices can be associated with the  $P_{op}$  and  $P_{data}$  and the  $P_{leakage}$  can be associated with the  $P_{const}$ . Thus, since only the  $P_{op}$  and  $P_{data}$  can provide valuable information for power analysis attacks, only the components of  $P_{switching}$  and  $P_{short-circuit}$  can expose sensitive information of the implementations.

#### 3.2.2 Power Analysis Attacks

#### 3.2.2.1 Simple Power Analysis

The Simple Power Analysis, as the name suggests, is a simple way to extract valuable information from the power traces through their direct interpretation or simple manipulation techniques as comparing pairs of power traces. Power consumption measurements that do not present high levels of noise, often provide power traces where characteristics of the device, the algorithm structure, data-dependent power variations and other operation characteristics are easily identified and which can be used to infer sensitive information of the system [19].

The SPA attacks are really complex to perform through a black box evaluation, that is, situations in which the internal implementation and algorithm operation are unknown. However, for situations where an attacker has detailed knowledge of the algorithm, it is possible, for example, to detect all phases of the encryption and extract the hamming weight of the computed data values [20]. Even in cases where the SPA is not successful and is not capable of completely reveal the expected information, they can still be used to facilitate the execution or help in preparation for other attacks, allowing the identification of the relevant power consumption samples and the points in time that are conducive to the application of attacks. As an example, in [21], a SPA attack is used to considerably reduce the number of keys that needs to be considered in a brute-force search to find out the secret encryption key.

#### 3.2.2.2 Differential Power Analysis

The Differential Power Analysis is a more effective and common attack than the SPA since due to the use of statistical analyses it allows the extraction of information about the encryption key even in very noisy environments or in cases where the SPA does not evidence any relevant characteristic in the power traces. The DPA comprehends the same two phases of attack than SPA (data collection and data analyses), but instead of focusing only in one power trace, it usually requires the collection of multiple power traces.

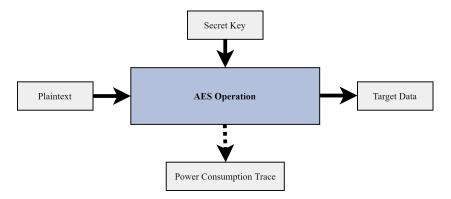

To execute a DPA attack, it is necessary to understand in detail the complete operation of the algorithm or, at least, the phase of encryption where the attack will be executed, to identify a relationship between the secret encryption key and the collected power traces. A possible solution for this is to explore the known data for which we have access (the input data) and, from the knowledge we have from the algorithm, make predictions about the expected data that is directly associated with the power traces. This expected data is the basis for the manipulation of the power traces for DPA, and so it is normally called target data. This relation is shown in Figure 3.2.

Figure 3.2: Target Data DPA Attack.

Since an attacker is only capable of modifying the plaintexts for the encryption and has no control over the encryption key, the calculation of the target bits is normally based on key guesses. The target bits are used to divide the power traces collected from simulations with the known plaintexts in groups, where each group corresponds to a different value of the target. Since the target bits were calculated assuming a key guess, if the key guess is correct, the power traces inside the same group shall have the same target bits and so, shall have a common point in the power traces. If the key guess is wrong, the division of the power traces was made using an incorrect assumption and therefore, the power traces will probably have no common point. The use of multiple power traces for each group aims to eliminate variations in power traces due to non-relevant data, through an average of the power traces. So, for each group, the final result is one single averaged power trace. The subtraction of those averaged power traces from different groups shall demonstrate significant spikes due to the different common points inside each group, if the correct key guess was used. If the key guess was wrong, the difference between the averaged power traces, the variations were removed with the average.

The more power traces are used in the DPA attacks, the clearer the correct key guess will be. In [22] a successful DPA attack in an ASIC implementation without any protection against DPA required 25000 power traces but when the implementation had countermeasures to reduce the vulnerability to DPA attacks this number increased to 130000 power traces. Thus, although DPA attacks constitute a serious risk to the security of the system, execute them is not easy and requires a high investment in terms of time for attack optimisation and data extraction.

#### 3.2.2.3 Correlation Power Analysis

The correlation power analysis is a variant of DPA that in some cases can exploit information in power traces with a higher efficiency than DPA but which also requires more detailed knowledge and comprehension about the implementation under attack, being essentially used in the white-box analysis where the device is well known. The CPA requires the development of a model of the device's power consumption, for a specific and small target execution sequence, which needs to be dependent from the values of intermediate results in the algorithm execution [19]. The model will then be used for comparisons with the power consumption patterns of the device under test. If the expected target for the model and the real device is the same, it is expected a high correlation between both power traces.