# Efficient Design Techniques of Switches for Optical Networks and Data Centers

Angelos Kyriakos Physics Department School of Science National and Kapodistrian University of Athens

Dionysios Reisis

Supervisors: Hector Nistazakis

Anna Tzanakaki

A thesis presented for the degree of Doctor of Philosophy

Athens 2023

## Efficient Design Techniques of Switches for Optical Networks and Data Centers

Τεχνικές Αποδοτικής Σχεδίασης Μεταγωγών Οπτικών Δικτύων και Κέντρων Δεδομένων

> Angelos Kyriakos Physics Department School of Science National and Kapodistrian University of Athens

### **Dissertation Committee:**

Dionysios Reisis<sup>1</sup>, Prof. Anna Tzanakaki<sup>1</sup>, Assoc.Prof. Antonis Paschalis<sup>1</sup>, Prof. Hector Nistazakis<sup>1</sup>, Prof. Dimitrios Soudris<sup>2</sup>, Prof.

George Tombras<sup>1</sup>, Prof.

Markos Anastasopoulos<sup>1</sup>, Assoc.Prof.

The research work was supported in part by the Hellenic Foundation for Research and Innovation (HFRI) Fellowship Number: 29

<sup>1</sup>NKUA <sup>2</sup>NTUA

Copyright © 2023 by Angelos Kyriakos All Rights Reserved

## Acknowledgements

I would like to express my sincere gratitude to my professor and supervisor Dionysios Reisis for his invaluable advice, patience and support during my PhD study. Additionally, this endeavor would not have been possible without the generous support from the Hellenic Foundation of Research & Innovation, who founded in part my research. I would also like to thank all the members of the Digital Systems Team of the Physics Department for the successful collaboration. Lastly, I'd like to express my appreciation to my parents, without their tremendous understanding and encouragement in the past few years, it would be impossible for me to complete my studies.

#### Abstract

The latest design approach for Data Centers follows the direction of exploiting optical switching to interconnect Top-of-Rack (ToR) switches that serve thousands of data storing and computing devices. Optical switching provided the means for the development of Data Centers with high throughput interconnection networks. A significant contribution to the advanced optical Data Centers designs is the Nephele architecture that employs optical data planes, optical Points of Delivery (PoD) switches and ToR switches equipped with 10 Gbps connections to the PoDs and the servers. Nephele follows the Software Defined Network (SDN) paradigm based on the OpenFlow protocol and it employs an Agent communicating the protocol commands to the data plane. A ToR's usual function is the Virtual Output Queues (VOQs), which is the prevalent solution for the head-of-line blocking problem of the Data Center switches. An effective VOQs architecture improves the Data Center's performance by reducing the frames communication latency and it is efficient with respect to the implementation cost. The current thesis introduces a VOQs architecture for the Data Center's ToR switches that function with Time Division Multiple Access (TDMA). The proposed VOQs architecture contains a bounded number of queues at each input port supporting the active destinations and forwarding the input Ethernet frames to a shared memory buffer. An efficient mechanism of low latency grants each queue to an active destination. The VOQs constitutes a module of a ToR development, which is based on a commercially available Ethernet switch and two FPGA Xilinx boards, the Virtex VC707 and the Xilinx NetFPGA. The VOQs architecture's implementation and validation took place on the NetFPGA board. Moreover, the current thesis presents a management tool for the control plane's Agent of the Data Center. The Graphical User Interface (GUI) of the Agent's management tool is utilized to configure the Agent, create commands, perform step operations and monitor the results and the status. When used as a testing and validation tool, it plays

a significant role in the improvement of the Agent's design as well as in the upgrade of the entire Data Center's organization and performance. Furthermore, aiming to improve the Quality of Service (QoS) for diverse applications of the Data Center, recent works utilize advanced Deep Learning techniques. The plethora of Machine and Deep Learning applications involve complex processes that impose the need for hardware accelerators to achieve real-time performance. Among these, notable are the Machine Learning (ML) tasks using Convolutional Neural Networks (CNNs) for classification applications. Aiming at contributing to the CNN accelerator solutions, the current thesis focuses on the design of FPGA Accelerators for CNNs of limited feature space to improve performance, power consumption and resource utilization, merits that ultimately enable the use of CNNs locally at the Data Center's ToR switches. The proposed CNN design approach targets the designs that can utilize the logic and memory resources of a single FPGA device and benefit numerous applications like the Edge, Mobile, Data Center and On-board satellite (OBC) Computing. This work exploits the proposed approach to develop an Example FPGA Accelerator for Vessel Detection, on a Xilinx Virtex 7 XC7VX485T FPGA device. The resulting architecture achieves an operating frequency of 270 MHz, while consuming 5 watts, it validates the approach.

Keywords: FPGAs - Data Centers - Virtual Output Queues -GUI- CNN - Parallel Processing

#### Περίληψη

Η σύγχρονη σχεδίαση των Κέντρων Δεδομένων εχμεταλλεύεται τις δυνατότητες που προσφέρει η οπτιχή μεταγωγή με στόχο την διασύνδεση των μεταγωγών ιχριώματος μεταξύ τους, οι οποίοι εξυπηρετούν χιλιάδες συσκευές αποθήκευσης και υπολογιστικά συστήματα. Οι καινοτομίες στον τομέα τον οπτικών επικοινωνιών και της οπτικής μεταγωγής συνέβαλλαν σημαντικά στην ανάπτυξη των Κέντρων Δεδομένων με υψηλής διεκπεραιωτικότητας δίκτυα διασύνδεσης. Σημαντική συνεισφορά στα προηγμένα οπτικά Κέντρα Δεδομένων παρουσιάζει η αρχιτεκτονική Nephele, η οποία χρησιμοποιεί οπτικά επίπεδα δεδομένων, οπτικούς μεταγωγούς στα Σημεία Παράδοσης και μεταγωγούς Ιχριώματος με δυνατότητα διασύνδεσης της τάξης των 10 Gpbs μεταξύ των Σημείων Παράδοσης και των εξυπηρετητών. Η αρχιτεκτονική Nephele ακολουθεί την Δικτύωση Βασισμένη σε Λογισμικό, χρησιμοποιεί το πρωτόκολλο OpenFlow και στηρίζεται σε έναν Πράχτορα Λογισμικού, ο οποίος υλοποιεί την μεταφορά των εντολών του πρωτοχόλλου στους μεταγωγούς του επιπέδου δεδομένων. Ένας μεταγωγός Ικριώματος καλείται συνήθως να υποστηρίζει την λειτουργία των Εικονικών Ουρών Εξόδου, οι οποίες αποτελούν την επικρατέστερη λύση στο πρόβλημα του αποκλεισμού μετάδοσης παχέτων που προέρχονται από την ίδια είσοδο σε πολλαπλές εξόδους του μεταγωγού. Μία αποτελεσματική αργιτεκτονική Εικονικών Ουρών Εξόδου βελτιώνει την επίδοση του Κέντρου Δεδομένων μειώνοντας την λανθάνουσα χαθυστέρηση της επικοινωνίας πλαισίων δεδομένων και ειναι αποδοτική όσον αφορά το κόστος υλοποίησης. Η συγκεκριμένη διατριβή εισάγει μία αρχιτεκτονική Εικονικών Ουρών Εξόδου για μεταγωγούς Ιχριώματος Κέντρων Δεδομένων τα οποία λειτουργούν σύμφωνα με την μέθοδο πολλαπλής πρόσβασης διαίρεσης χρόνου. Η προτεινόμενη αρχιτεκτονική Εικονικών Ουρών Εξόδου περιλαμβάνει έναν περιορισμένο αριθμό ουρών σε κάθε πόρτα εισόδου που υποστηρίζουν τους ενεργούς προορισμούς και αποθηκεύουν προσωρινά τα πακέτα Ethernet σε δυναμική μνήμη τυχαίας προσπέλασης. Ένας

αποδοτικός μηγανισμός χαμηλής λανθάνουσας καθυστέρησης αντιστοιχεί κάθε ουρά σε έναν ενεργό προορισμό. Οι Εικονικές Ουρές Εξόδου αποτελούν ένα δομικό στοιχείο του μεταγωγού Ικριώματος, ο οποίος βασίζεται σε ένα εμπορικά διαθέσιμο μεταγωγό Ethernet και σε δύο κάρτες Xilinx FPGA, την Virtex VC707 και την NetFPGA. Η αρχιτεκτονική των Εικονικών Ουρών Εξόδου υλοποιήθηκε και επαληθεύτηκε μέσω δοκιμών στην κάρτα NetFPGA. Επιπλέον, η συγκεκριμένη διατριβή παρουσιάζει ένα εργαλείο διαχείρισης για τον Πράκτορα Λογισμικού του Κέντρου Δεδομένων. Η Γραφική Διεπαφή Χρήστη του εργαλείου διαχείρισης του Πράκτορα Λογισμικού χρησιμοποιείται για την διαμόρφωση του Πράκτορα Λογισμικού, την δημιουργία εντολών, την εκτέλεση λειτουργιών σε βήματα και την παρακολούθηση των αποτελεσμάτων και της κατάστασης των μεταγωγών. Χρησιμοποιούμενο ως εργαλείο δοχιμών χαι επαλήθευσης, διαδραματίζει ένα σημαντιχό ρόλο στην βελτίωση της σχεδίασης του Πράκτορα Λογισμικού καθώς επίσης και στην αναβάθμιση ολόκληρης της οργάνωσης του Κέντρου Δεδομένων και των επιδόσεων του. Επιπρόσθετα, με στόχο την Διασφάλιση της Ποιότητας Υπηρεσιών για τις ποιχίλες εφαρμογές των Κέντρων Δεδομένων πρόσφατες έρευνες αξιοποιούν σύγχρονες τεχνικές Βαθιάς Μάθησης. Η πληθώρα από εφαρμογές Μηγανικής και Βαθιάς Μάθησης περιλαμβάνουν πολύπλοκες διεργασίες που επιβάλλουν την ανάγκη των Επιταχυντών Υλικού για την εκτέλεσή τους σε πραγματικό χρόνο. Μεταξύ αυτόν, αξιοσημείωτα είναι τα Συνελικτικά Νευρωνικά Δίκτυα για εφαρμογές κατηγοριοποίησης. Με στόχο την συνεισφορά στον τομέα των Επιταχυντών Υλικού Συνελικτικών Νευρωνικών Δικτύων, η παρούσα διατριβή επικεντρώνεται σε νευρωνικά δίκτυα περιορισμένου αριθμού χαρακτηριστικών για να βελτιώσει τις επιδόσεις, την κατανάλωση ενέργειας και την αξιοποίηση των πόρων, στοιχεία που τελικά θα δώσουν την δυνατότητα για την χρήση τους τοπικά στους μεταγωγούς ενός Κέντρου Δεδομένων. Η προτεινόμενη σχεδιαστική προσέγγιση Συνελικτικών Νευρωνικών Δικτύων στοχεύει στην αξιοποίηση των πόρων λογικής και μνήμης ενός FPGA, και ωφελεί πολυάριθμες εφαρμογές όπως Αποκεντρωμένες και Φορητές εφαρμογές, Κέντρα Δεδομένων και Δορυφορικές εφαρμογές. Η συγκεκριμένη διατριβή εκμεταλλεύεται την προτεινόμενη σχεδιαστική προσέγγιση, ώστε να αναπτύξει ένα Παράδειγμα Επιταχυντή για Αναγνώριση Πλοίων, στην κάρτα Xilinx Virtex 7 XC7VX485T FPGA.Η παραχθείσα αρχιτεκτονική επιτυγχάνει συχνότητα λειτουργίας 270 MHz, καταναλώνοντας 5 watt επαληθεύοντας την σχεδιαστική προσέγγιση.

Λέξεις-κλειδιά:FPGAs - Κέντρα Δεδομένων - Εικονικές Ουρές Εξόδου - Γραφική Διεπαφή Χρήστη - Συνελικτικά Νευρωνικά Δίκτυα - Παράλληλη Επεξεργασία

## Table of Contents

| 1 | Intr                    | n         | 1                                        |      |  |  |  |

|---|-------------------------|-----------|------------------------------------------|------|--|--|--|

|   | 1.1                     | Thesis    | Outline                                  | . 5  |  |  |  |

| 2 | 2 Virtual Output Queues |           |                                          |      |  |  |  |

|   | 2.1                     | Introdu   | uction                                   | . 6  |  |  |  |

|   | 2.2                     | Backg     | round on the Nephele Data Center         | . 6  |  |  |  |

|   | 2.3                     | The A     | rchitecture of the Top-of-Rack Switch    | . 9  |  |  |  |

|   | 2.4                     | Virtua    | l Output Queues                          | . 12 |  |  |  |

|   | 2.5                     | FPGA      | Implementation Details                   | . 21 |  |  |  |

| 3 | Too                     | ls for Da | ata Center Control                       | 22   |  |  |  |

|   | 3.1                     | Introdu   | uction                                   | . 22 |  |  |  |

|   | 3.2                     | Backg     | round on Nephele's Data Center Control   | . 23 |  |  |  |

|   | 3.3                     | The M     | lanagement Tool of the Agent             | . 26 |  |  |  |

|   |                         | 3.3.1     | The GUI Architecture                     | . 26 |  |  |  |

|   |                         | 3.3.2     | Usability of the Agent's Management Tool | . 31 |  |  |  |

|   |                         | 3.3.3     | Back-End of the Agent's Management Tool  | . 33 |  |  |  |

| 4 | Neu                     | ral Netv  | works on FPGA                            | 36   |  |  |  |

|   | 4.1                     | Introdu   | uction                                   | . 36 |  |  |  |

|   | 4.2                     | 6         |                                          |      |  |  |  |

|   | 4.3                     |           |                                          |      |  |  |  |

|   |                         | 4.3.1     | CNN Design Space Exploration             | . 39 |  |  |  |

|   |                         | 4.3.2     | Bit-Accurate Model Development           | . 40 |  |  |  |

|   |                         | 4.3.3     | VHDL Blocks                              | . 41 |  |  |  |

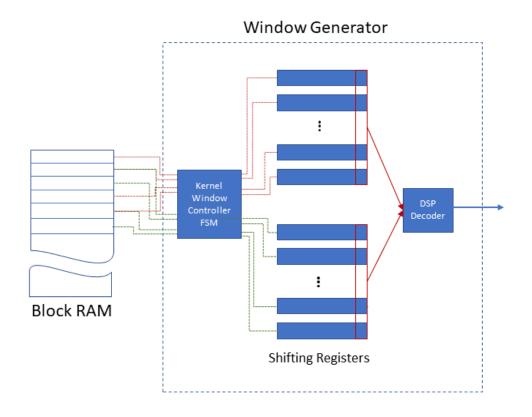

|   |                         |           | 4.3.3.1 Input Block                      | . 41 |  |  |  |

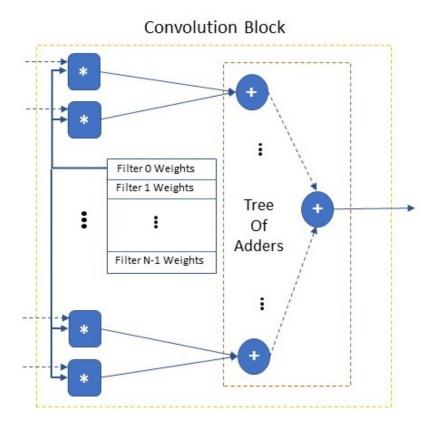

|                               |     |        | 4.3.3.2                                              | Convolution Block                        | 42 |  |

|-------------------------------|-----|--------|------------------------------------------------------|------------------------------------------|----|--|

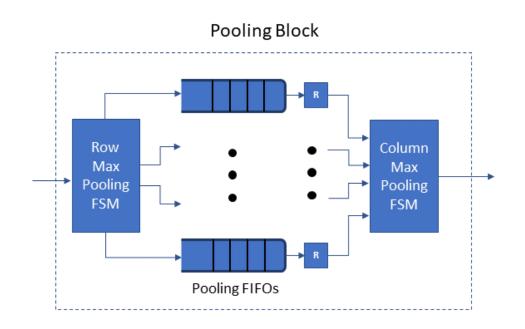

|                               |     |        | 4.3.3.3                                              | Pooling Block                            | 43 |  |

|                               |     |        | 4.3.3.4                                              | Vector Multiplier                        | 44 |  |

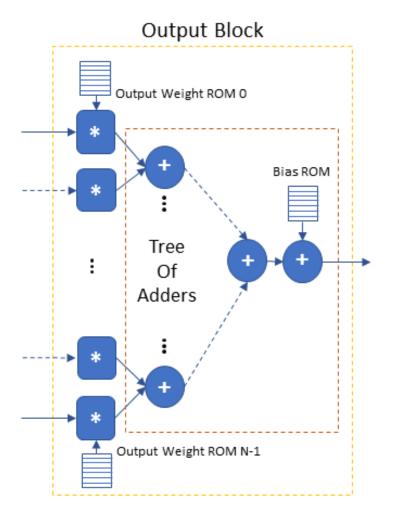

|                               |     |        | 4.3.3.5                                              | ReLU and Output Block                    | 45 |  |

|                               |     | 4.3.4  | Methodo                                              | logy for Mapping the CNN on the FPGA     | 45 |  |

|                               | 4.4 | Vessel | FPGA Accelerator Example                             | 49                                       |    |  |

|                               |     | 4.4.1  | Backgrou                                             | and on Vessel Detection                  | 50 |  |

|                               |     | 4.4.2  | Model A                                              | rchitecture and Training                 | 52 |  |

|                               |     | 4.4.3  | Bit-Accu                                             | arate Model (BAM)                        | 53 |  |

|                               |     | 4.4.4  | The Exa                                              | mple CNN FPGA Accelerator                | 54 |  |

|                               |     | 4.4.5  | Vessel Detection CNN FPGA Accelerator Results & Com- |                                          |    |  |

|                               |     |        | parison                                              |                                          | 58 |  |

|                               |     |        | 4.4.5.1                                              | FPGA Implementation Results              | 58 |  |

|                               |     |        | 4.4.5.2                                              | Comparison to Edge Devices and Low Power |    |  |

|                               |     |        |                                                      | Processors                               | 60 |  |

|                               |     |        | 4.4.5.3                                              | Comparison to Other FPGA Accelerators    | 62 |  |

| 5 Conclusions and Future Work |     |        |                                                      |                                          | 65 |  |

| Bibliography                  |     |        |                                                      |                                          |    |  |

| Appendix A Publications       |     |        |                                                      |                                          |    |  |

# List of Figures

| 2.1 | The Nephele Data Center Network Architecture                    | 8  |

|-----|-----------------------------------------------------------------|----|

| 2.2 | The Nephele Top-of-Rack (ToR) Switch Architecture Overview .    | 10 |

| 2.3 | VOQs Controller Architecture Overview                           | 14 |

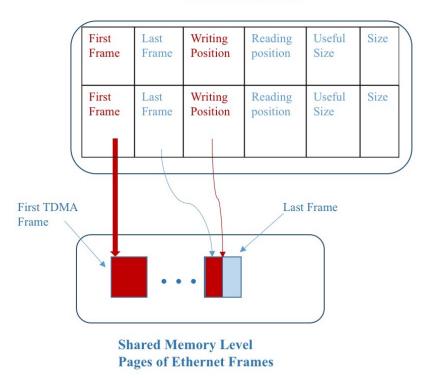

| 2.4 | Memory Map Organization while Buffering                         | 19 |

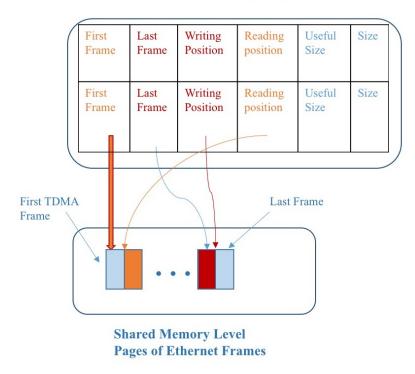

| 2.5 | Memory Map Organization Concurrent Write & Read Operations      | 20 |

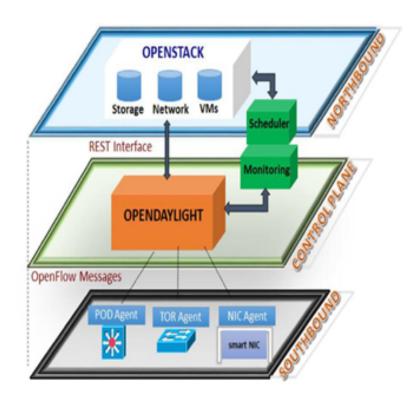

| 3.1 | Nephele SDN Control Plane                                       | 25 |

| 3.2 | The Format of the Scheduling Table                              | 26 |

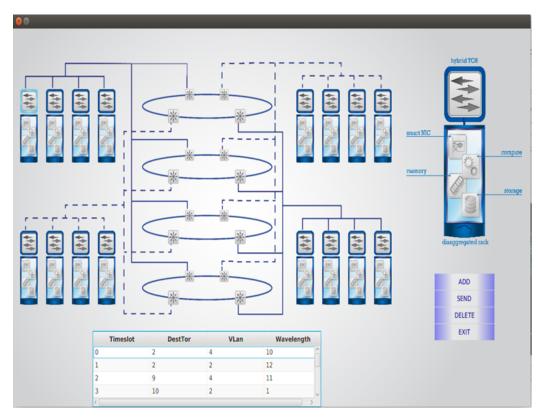

| 3.3 | The GUI Main Scene                                              | 28 |

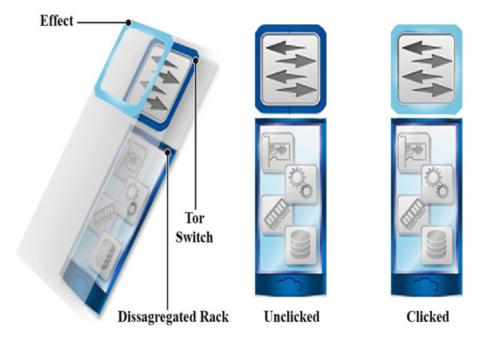

| 3.4 | Effect of clicking the ToR                                      | 30 |

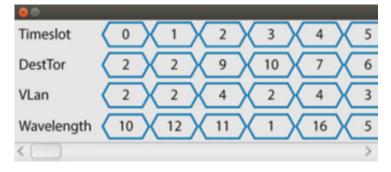

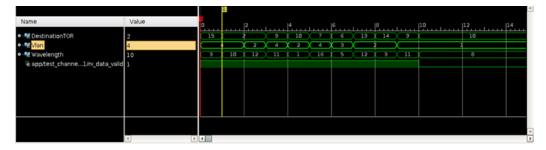

| 3.5 | Pop-up Window with the Values sent to FPGA                      | 31 |

| 3.6 | Output of the Logic Analyzer                                    | 31 |

| 3.7 | Nephele Data Plane Development                                  | 32 |

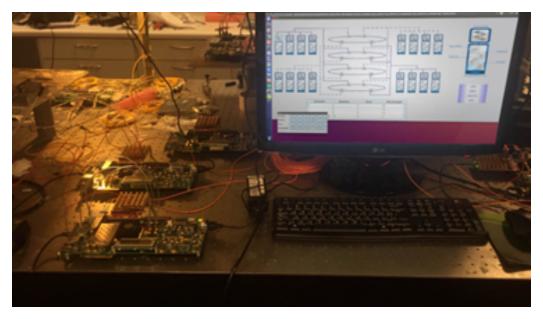

| 3.8 | Live Demo of the Management Tool                                | 34 |

| 4.1 | Input Block Architecture                                        | 42 |

| 4.2 | Convolution Block Architecture                                  | 43 |

| 4.3 | Pooling Block Architecture                                      | 44 |

| 4.4 | Output Block Architecture                                       | 46 |

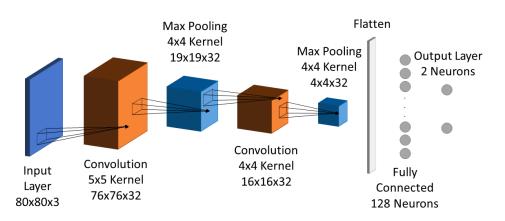

| 4.5 | Model Architecture                                              | 54 |

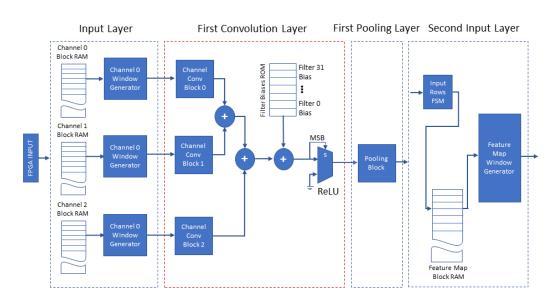

| 4.6 | FPGA Architecture of the Input Layer, First Convolution & Pool- |    |

|     | ing Layers and the Second Input Layer.                          | 55 |

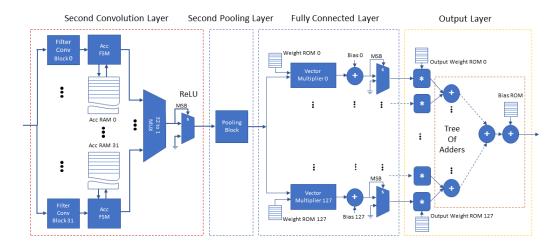

| 4.7 | FPGA Architecture of the Second Convolution & Pooling Layers,   |    |

|     | Fully Connected Layer and Output Layer.                         | 58 |

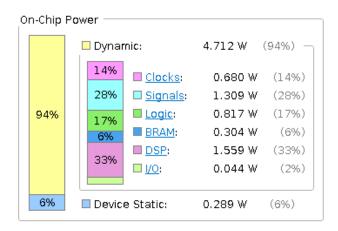

| 4.8 | Power Utilization                                               | 60 |

## List of Tables

| 2.1 | Resource Utilization of VOQs Controller        | 21 |

|-----|------------------------------------------------|----|

| 4.1 | Resource Utilization                           | 59 |

| 4.2 | Performance Comparison to CPU & GPU            | 59 |

| 4.3 | Performance & Power Comparison to Edge Devices | 62 |

| 4.4 | Reporting the Features of Related Results      | 63 |

## List of Abbreviations

- AMBA ..... Advanced Microcontroller Bus Architecture

- API ..... Application Programming Interface

- AXI ..... Advanced eXtensible Interface

- BAM ..... Bit-accurate Model

- BRAM ..... Block Random Access Memory

- CMX ..... Connection Matrix

- CNN ..... Convolutional Neural Network

- CPU ..... Central Processing Unit

- CSV ..... Comma Separated Values

- CUDA ..... Compute Unified Device Architecture

- **DDR** ..... Double Data Rate

- DMA ..... Direct Memory Access

- DRAM ..... Dynamic Random Access Memory

- DSP ..... Digital Signal Processor

- FF ..... Flip-Flop

- FIFO ..... First-In First-Out

- FPGA ..... Field-programmable Gate Array

- FSM ..... Finite-State Machine

- GFLOPS ..... Giga Floating Point Operations Per Second

- GOPS ..... Giga Operations Per Second

- GPU ..... Graphics Processing Unit

- GTX ..... Giga Texel Shader

- GUI ..... Graphical User Interface

- HLS ..... High-level Synthesis

- IP ..... Intellectual Property

- IT ..... Information Technology

- JVM ..... Java Virtual Machine

- LSTM ..... Long Short-Term Memory

- LUT ..... Lookup Table

- LUTRAM ..... Lookup Table Random Access Memory

- MAC ..... Media Access Control

- MIG ..... Memory Interface Generator

- ML ..... Machine Learning

- **OBC** ..... On-board Computing

- ONF ..... Open Networking Foundation

- PC ..... Personal Computer

- PCI ..... Peripheral Component Interconnect

- PCIe ..... Peripheral Component Interconnect Express

- PCS ..... Physical Coding Sublayer

- PMA ..... Physical Medium Attachment

- PoD ..... Point of Delivery

- QoS ..... Quality of Service

- RAM ..... Random Access Memory

- **R-CNN** ..... Region-based CNN

- ReLU ..... Rectified Linear Unit

- RGB ..... Red Green Blue

- **RIFFA** ..... Reusable Integration Framework for FPGA Accelerators

- **RNN** ..... Recursive Neural Network

- **ROM** ..... Read-Only Memory

- SDN ..... Software Define Networking

- SHAVE ...... Streaming Hybrid Architecture Vector Engine

- SRAM ..... Static Random Access Memory

- SSD ..... Single Shot MultiBox Detector

- TDMA ..... Time Division Multiple Access

- ToR ..... Top of Rack

- USB ..... Universal Serial Bus

- VHDL ..... VHSIC Hardware Description Language

- VLAN ..... Virtual Local Area Network

- VM ..... Virtual Machine

- **VOQ** ..... Virtual Output Queue

- WDM ..... Wavelength Division Multiplexing

YOLO ..... You Only Look Once

### 1 Introduction

The ongoing research and innovation in the area of telecommunication networks has enabled the development of data centers, comprising of very large numbers of interconnected servers. The widespread availability of cloud applications to billions of users and the emergence of software-, platform- and infrastructure-asa-service models led to the reliance on data centers. As traffic within a data center (east-west) is higher than incoming/outgoing traffic (Cisco, 2014-2019), data center's interconnection networks play a crucial role in its performance. Stateof-the-art data center networks are based on electronic switches connected in fat-tree topologies using optical fibers, with electro-opto-electrical transformation at each hop (Al-Fares, Loukissas, & Vahdat, 2008). However, fat-trees tend to under-utilize resources, require a large number of cables and switches, suffer from poor scalability and upgradability, and they result in very high energy consumption (Benson, Akella, & Maltz, 2010), (Roy, Zeng, Bagga, Porter, & Snoeren, 2015). The introduction of optical switching in data centers plays a key role in solving these shortcomings. Many recent works proposed hybrid electrical/optical switched data center networks (Farrington et al., 2010), (G. Wang et al., 2010), (Singla, Singh, Ramachandran, Xu, & Zhang, 2010), (Saridis et al., 2016), (Kachris & Tomkos, 2012), (Bakopoulos et al., 2018). Optical switches are mostly used in telecom networks as circuit switches. They passively redirect light from any port to another (full cross-bar), but have high reconfiguration times (tens of ms for high radix and tens of µs for low radix switches), posing barriers to their applicability in data centers.

The significant increase in the available throughput in optical transmission supports the development of data center networks, optical transceivers achieve throughput in the order of 10 Gbps and state of the art solutions aim at 100 Gbps (Zilberman, Audzevich, Covington, & Moore, 2014). The design of hybrid data center nodes that operate in the electrical domain aim to support the high throughput optical interconnection and they have to sustain the same level of throughput in their electrical and computational systems. Moreover, the design has to be efficient regarding the implementation cost and the power consumption. Furthermore, all aforementioned challenges are proportional to the size of the data center network (Vahdat et al., 2010), (Han et al., 2013), thus the provided solutions must present high scalability, in order to be suitable for the constantly growing in size data centers (Cisco, 2014-2019). The current thesis focuses in the study and development of new techniques for the design and implementation of switches in the electrical domain, utilized in state of the art optical interconnection data center networks.

First, the use of optical switches in data center networks introduces various challenges in the design of the data center switches, which has to compromise between their size and the reconfiguration speed and also be able to scale for large data center networks without increased cost. Top-of-Rack (ToR) switches must accommodate the incoming traffic of Ethernet Frames originating at the servers of the data center to packets suitable to be transmitted through the optical data center network, adhering to the scheduling of the central data center controller (H. Liu et al., 2013), (Moor, 2013), (Patronas, Kyriakos, & Reisis, 2016). Moreover, data center nodes have to internally minimize blocking probability, transmission latency and eliminate the head of line blocking, packets originating from the same input port destined to multiple output ports can be held up in a queue by the first packet. The model of the Virtual Output Queues (VOQs) is the most prevalent solution to the head of line blocking (Yébenes, Maglione-Mathey, Escudero-Sahuquillo, García, & Quiles, 2016) however, the implementation is a challenge in large scale data centers because of the need of large shared memory buffers, usually realized in external Dynamic Random Access Memory (DRAM).

Second, hybrid data center networks typically use centralized control following the Software Defined Network (SDN) paradigm (Christodoulopoulos, Lugones, Katrinis, Ruffini, & O'Mahony, 2015), (Saridis et al., 2016), (Bakopoulos et al., 2018). The working time is divided in time slots according to the method of Time Division Multiple Access (TDMA) (Tokas et al., 2016), (Vattikonda, Porter, Vahdat, & Snoeren, 2012). The control plane is based on a Central Controller/Scheduler necessary for the scheduling of the data center network operation with the following steps. First, it gathers the status information of the traffic from every data center switch second, it computes the allocation of the resources/timeslots for the next scheduling period, and third it configures the switches. The distribution of the schedule has to be synchronized and executed as fast as possible, so that the remaining time between the scheduling periods can be allocated to the computation of the schedule, a very challenging task to be solved in real-time. A software Agent of the data center supervises the execution of the schedule and it acts as a bridge between the Central SDN Controller and the data center switches.

The current thesis also considers the design and implementation of Convolutional Neural Networks for classification applications in FPGAs. The Machine and Deep Learning applications include complicated calculations that require large amounts of memory and call for the use of FPGA accelerators (Abdelouahab, Pelcat, Sérot, & Berry, 2018), in order to achieve real-time performance. The goal of this work is to propose a CNN design approach for the limited feature space classification tasks that benefit various applications in the Data Center (Lim et al., 2019), (P. Wang, Ye, Chen, & Qian, 2018), Edge (Choi & Sobelman, 2022), Mobile (Howard et al., 2017) and OBC computing (Rapuano et al., 2021),(Pitonak, Mucha, Dobis, Javorka, & Marusin, 2022), while utilizing the resources of a single FPGA device with only on-chip memories, omitting the use of external DRAM. This fact enables the possible integration of the CNN accelerator in data cen-

ter switches that use an external DRAM as a buffer for the incoming packets in VOQs.

The use of High Level Synthesis (HLS) is prevalent in modern CNN FPGA Accelerators mainly due to the short development time and the provided hardware abstraction (Kim, Grady, Lian, Brothers, & Anderson, 2017), (Solovyev, Kalinin, Kustov, Telpukhov, & Ruhlov, 2018), (Zhang et al., 2015), (Sankaradas et al., 2009), (Peemen, Setio, Mesman, & Corporaal, 2013), (B. Liu et al., 2019). Although, the HLS design approach impede the FPGA designers/engineers to develop an efficient FPGA architecture with respect to resource utilization, energy consumption and the achievable performance (Pelcat, Bourrasset, Maggiani, & Berry, 2016). Few authors present solutions for CNN application with FPGA accelerators developed with VHSIC Hardware Description Language (VHDL). (Rapuano et al., 2021) present an On-board satellite FPGA accelerator for CNN inference, implemented with VHDL which utilizes a single processing unit with external DRAM memory. The current thesis focuses on streamline architectures, developed with VHDL, that implement the contiguous CNN layers in a pipeline fashion that differs to the implementation of a systolic array. The advantages of the proposed design is first the avoidance of idle computing time by extensive pipelining and second the reduced memory resources (Y. Zhao et al., 2019), leading to the use of only on-chip (FPGA) memory, features that combined improve resources utilization, reduced latency and power consumption (Sze, Chen, Yang, & Emer, 2017), (Lamoureux & Luk, 2008).

The proposed CNN design approach is divided into three phases. The first phase introduces guidelines for the design stage of the CNN with a tool like TensorFlow (Abadi et al., 2015), adhering to them produces a CNN model that is friendlier to a hardware implementation, because the resulting CNN model has reduced memory requirements but keeps the same levels of classification accuracy. The second

phase transforms the CNN model into a fixed-point Bit-accurate Model (BAM) performing the same calculations but in an arithmetic representation that can be efficiently implemented in hardware that does not decrease classification accuracy. The third phase utilizes an already developed library of VHDL Blocks, in order to save developing time, and along with the proposed approach's mapping methodology results in a streamline architecture FPGA accelerator with improved performance, reduced power consumption and resource utilization.

### **1.1 Thesis Outline**

The remainder of this thesis is organised as follows:

**Chapter 2**— introduces the study and implementation of the Virtual Output Queues architecture and its integration in the Top of Rack switch of the Nephele data center.

**Chapter 3** — demonstrates the management tool for the optical interconnected data center Nephele, how is developed, the Graphical User Interface, its usecases as well as its advantages.

**Chapter 4** — presents the CNN design approach for real-time classification FPGA accelerators that can be realised in a single FPGA device and it proves its merits by developing an Example FPGA Accelerator for Vessel Detection.

**Chapter 5** — concludes this thesis and presents the major paths for future work.

### 2.1 Introduction

Data centers are comprised of a large number of servers running Virtual Machines (VMs) and storage resources, which are installed in racks and communicate via the local data center network. The data center's performance depends on the available computing and data storing capacity, the architecture, the features as well as the performance of the underlying network and the Top-of-Rack (ToR) switches connecting the servers to the data center. A key factor in improving the performance of the ToR switches is the solution of the head-of-line blocking issue that is most often settled by embedding Virtual Output Queues architectures (Yébenes et al., 2016), (Kyriakos, Patronas, Tzimas, Kitsakis, & Reisis, 2017).

The motivation for designing the proposed VOQs architecture came by the requirements of the ToR switch included in the Nephele project but it can serve any network, that receives an input of Ethernet frames and particularly those networks which operate under TDMA scheme, are software defined and their nodes may have to overcome the head-of-line blocking. The following section briefly highlights the Nephele data center architecture then section 2.3 introduces the architecture of the Nephele ToR switch. Section 2.4 presents the organization of the VOQs. Finally, Section 2.5 presents the details of the VOQs Controller FPGA implementation.

### 2.2 Background on the Nephele Data Center

The performance of the data center networks depends on their interconnection scheme, which usually adhered to the multi-layer approach, and they were based

on the Fat Tree or the folded Clos architectural schemes (Al-Fares et al., 2008), (Greenberg et al., 2009), (Farrington, Rubow, & Vahdat, 2009). These approaches nevertheless, are not efficiently scalable and also, in the case of data centers with a large number of nodes, lead to the use of a considerable number of switches, cables and transceivers, which increase power consumption.

In an effort to overcome these deficiencies researchers and engineers have introduced data center interconnections including an optical circuit switching as well as an electrical packet switching networks (Bazzaz et al., 2011), (Farrington et al., 2010), (Tokas et al., 2016). A notable design is the all optical data center proposed by the Nephele project (Bakopoulos et al., 2018).

The Nephele data center involves a slotted hybrid electrical/optical interconnection network that is advantageous with respect to the dynamic allocation of resources. The network includes PoDs of racks that communicate with the so-called innovation zones, which are the devices dedicated for the disaggregated computing, storage and memory resources. The innovation zones are connected to ToR switches (Patronas et al., 2016). Each innovation zone can communicate to other innovation zones through an all optical or an electro-optical channel.

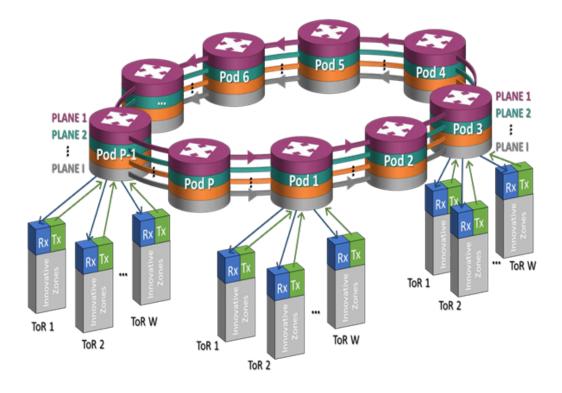

The Nephele design adopts the Time Division Multiple Access (TDMA) mode of operation in the optical data center network. Consequently, the transmissions are completed within fixed time segments, namely the slots; each slot is assigned for sending a TDMA frame on a specific path that connects a transmitter node to a receiver node. The Nephele data center network is a Software Defined Network (SDN) and all the arrangements regarding its operation are dictated by a central data center controller. The controller is responsible for generating the TDMA Schedule, which defines which nodes communicate during each time-slot (Christodoulopoulos, Kontodimas, Yiannopoulos, & Varvarigos, 2016). The first version of the scalable, high capacity Nephele network is able to accommodate up to 1600 Top-of-Rack (ToR) switches and each ToR uses 20 links to connect to the data center optical network.

Figure 2.1: The Nephele Data Center Network Architecture

The overall system topology of the data center network is depicted in Figure 2.1. The network includes I ( $I \le 20$ ) parallel planes, each consisting of I ( $I \le 20$ ) unidirectional optical rings. The rings interconnect P ( $P \le 20$ ) Points of Delivery (PoDs). A PoD comprises of I Wavelength Selective Switches (WSS) to connect the I rings, and is connected to W ( $W \le 80$ ) ToRs, through W pod-switches, one for each ToR switch. Each ToR switch has I north ports, such that the ith north port is directed to the ith PoD of each plane (each port is connected to a different PoD switch). The south ports of the ToR switch connect the servers, through network interface cards (NICs), with the data center network. The performance of the ToR switch contributes significantly to the operation of the entire data center and it depends on the utilization of its resources as well as on the efficiency of the algorithms and the techniques that it employs. Among the techniques that are critical with respect to the ToR's performance is the handling of the Virtual Output Queues (VOQs). VOQs is an attractive technique for overcoming the head-of-line blocking cases (Yébenes et al., 2016).

### 2.3 The Architecture of the Top-of-Rack Switch

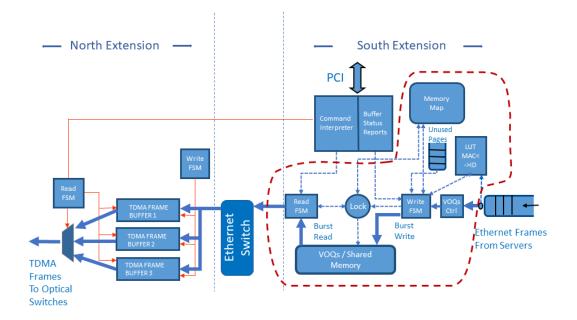

The ToR design is a switch and its ports are divided in two sets: a) the south ports, which are 16 10GEthernet ports connecting the ToR with the servers b) the corresponding 16 10Gbps north ports that are connected to the optical data center network. The ToR switch consists of three fundamental blocks. The first is an Ethernet 16×16 switch having all ports as 10GEthernet (Mellanox-Technologies, May 2013). The second is the North Extension. It is implemented on an FPGA and its role is: a) the formation of TDMA frames that consist of Ethernet frames and b) to implement the interface of the ToR to the network's optical (PoD) switches by using its north ports. The third block is the South Extension. This FPGA based block connects the servers to the ToR. It has increased complexity and its functionality includes: a) the execution of the scheduling commands, b) to be responsible for the communication of the ToR to the data center's control plane, c) to implement the VOQs design and d) to control all the functions of the ToR. The prototype Nephele ToR switch includes a commercially available Ethernet switch (Mellanox SX1024 (Mellanox-Technologies, May 2013)) and two Xilinx boards: one Virtex VC707 and one NetFPGA SUME (Zilberman et al., 2014). The implementation and validation of the VOQs architecture took place on the NetFPGA board. This section briefly highlights the architecture of the Nephele ToR switch

Figure 2.2: The Nephele Top-of-Rack (ToR) Switch Architecture Overview

Figure 2.2 presents the ToR switch's architecture as well as the functional blocks dedicated to the upstream traffic. In the part of the South Extension the figure shows the LUT MAC-ID that assigns a tag to each incoming Ethernet frame. These 11 bit tags will be used within the ToR for addressing the Ethernet frames and saving on the required resources for address bits with respect to the bits required for the MAC addresses of the destinations of the incoming frames. The next action is to forward the Ethernet frames to the VOQs/Shared Memory block. This block stores the Ethernet frames in pages. Each page includes a large number of Ethernet frames and its length matches the length of a TDMA frame (also called Nephele frame). All the pages that belong to a destination are arranged in a linked list. The pointers required for keeping the information of each destination's linked list are managed by the Memory Map block.

The Command Interpreter block (Figure 2.2) is responsible for the translation of the SDN controller commands: it provides to this ToR the destination ToR, which

has to receive data in the upcoming TDMA slot. The ToR complies to this command and it retrieves the first page with Ethernet frames that belongs to the linked list associated to the commanded destination and sends this page to the Ethernet switch. There is a Lock mechanism (Figure 2.2) that grants either the storing operation of the input Ethernet frames to the shared memory or the reading operation from that memory of the TDMA frames. In more detail, the Lock mechanism divides the time into small time windows  $T_L$ . Each  $T_L$  is dedicated for either writing to the shared buffer or reading from it. Hence, when the ToR reads from the shared buffer it will continue buffering in the small size queues the incoming traffic from the servers. The length of the  $T_L$  is computed at design time to balance: first, the throughput of the shared buffer, which requires long burst transactions for improved performance and second, the need of the ToR operation for writing/reading to/from the shared buffer at close time instances.

The role of the Ethernet switch in the upstream direction, is to forward the Ethernet frames to the North Extension and particularly to the buffer of the corresponding destination's north port. In that buffer the Ethernet frames formulate the final TDMA/Nephele frame, to which are also added first, the preamble and second, a word required for each device synchronization. The Command Interpreter follows the schedule received from the control plane servers and it specifies (the red control signal of Figure 2.2) the slot that the ToR will transmit that TDMA frame. For the downstream direction, the Nephele design mandates the Ethernet switch to just forward the frame from the north input port to the corresponding south port. That is, the design complexity of the ToR is mostly related to the upstream path.

The communication of the ToR switch with the control plane is accomplished through the PCI Express interconnection. The PCI Express interface in the proposed architecture is implemented by the use of the Xilinx IP Core for PCIe and RIFFA (Reusable Integration Framework for FPGA Accelerators) (Jacobsen, Richmond, Hogains, & Kastner, 2015). The RIFFA framework consists of an API (Application Programming Interface), a driver/kernel module for the host PC and an IP core for the FPGA, all of which are open-source. The module provided by RIFFA for the FPGA is designed as an extension to the Xilinx IP core for PCIe, which handles the physical layer of the PCIe interface. The control of the ToR switch is presented in the next Chapter, more specifically in subsection 3.3.3, in which the implementation of the PCIe interface is presented in more detail.

### 2.4 Virtual Output Queues

This Section presents an efficient VOQ organization regarding the resource utilization and the latency needed to assign the incoming Ethernet Frames to the queues of matching destinations. The VOQ architecture introduced in this chapter is advantageous due to the following: first, it is efficient with respect to the required implementation area, because it reduces the resources needed to a single shared buffer per output port. This buffer stores all the queues of data that this output port will transmit. Second, the architecture is efficient with respect to the utilization of the shared buffer's bandwidth; this is because it maximizes the throughput utilization of the buffer's interface by utilizing for storing and reading a paging organization, with each page containing a large number of Ethernet frames. Third, the proposed VOQ architecture is scalable, which is an advantage considering the scalability of the entire data center.

The proposed technique achieves the aforementioned goals based on the following ideas. The receiving Ethernet Frames with the same destination are collected at the input of the switch into pages of frames. This operation is accomplished by using small sized queues positioned at each input Ethernet port. In the proposed design the number of these small sized queues at the input is bounded by the sum

of the connections that are: a) serviced by each input Ethernet port and b) active during a small window of time. The latency is minimized with respect to the time required to associate each input Ethernet Frame to one of the queues. This is accomplished by employing a mechanism that maps each small size queue to one of the active destinations each time an Ethernet Frame arrives at the ToR.

The proposed VOQ design improves the required hardware resources based on the following concept. During a narrow time window TB, the ToR switch receives Ethernet frames at its south ports for various destinations in the data center network, which we define as active destinations. We consider that for all practical purposes, the number of active destinations, during a narrow time window TB, has an upper limit, which can be an outcome of statistical measurements of the network traffic patterns across the data center. The active destinations' upper limit is significantly smaller compared to the number of all the possible destinations in the data center. Hence, letting a queue to keep all the incoming Ethernet frames during TB that have the same active destination and prepare in this queue a burst to be written to the shared buffer, leads to an architecture that includes a set of queues with a cardinal number equal to that of the active destinations, while it still keeps the high throughput at the shared buffer.

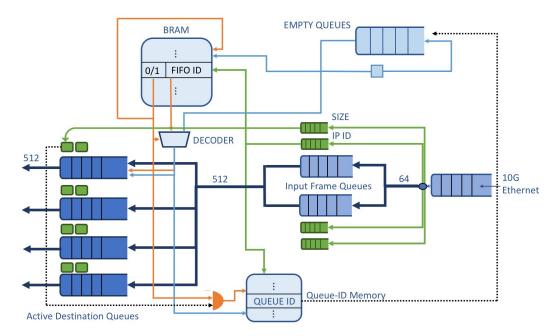

Considering the above, the VOQs architecture is comprised of: first, the Shared Memory (buffer), second the Memory Map depicted in Figure 2.2 and third, the VOQs controller. The detailed architecture of the VOQs controller is shown in Figure 2.3: it is a design of the VOQs controller that includes four (4) active destinations and the corresponding queues, based on a hypothesis that the application asks for four active destination and as shown in Figure 2.3 there is one queue to support each active destination. In order to define the length of the time window TB we consider the following facts. The design of the shared buffer employs a Dynamic Random Access Memory (DRAM) that can reach the consid-

erable throughput of 80 Gbps at its interface; this performance will be feasible if the entire VOQs architecture can operate with burst transactions for reading and writing from/to the shared buffer, thus exploiting the DRAM interface, which requires a minimum burst time  $t_m b$  depending on the DRAM specifications. The performance of the DRAM organization degrades significantly when the size of the burst size decreases. We note here that, this performance degradation cannot be expressed (defined) as a function of the burst size, e.g. proportional. Therefore, reading and writing from/to a page in the shared buffer (in the linked list assigned to a destination) must be performed in bursts and each burst has to consist of multiple Ethernet frames, in the order of Kbytes. Therefore, we need an architecture of queues able to gather into a single queue all the incoming Ethernet frames that have the same destination; in that queue, the controller will formulate a burst of these Ethernet frames. Finally, it will operate in burst mode to store these frames into the page of the linked list of that destination.

Figure 2.3: VOQs Controller Architecture Overview

We consider the time window  $T_B$  and the number of queues for active destinations k to be calculated by the following reasoning. At a clock cycle  $T_0$ , given that are available k queues storing Ethernet frames of k different IPs, there will be Ethernet frames arriving to at most all of these queues and at the clock cycle  $T_b$  that at least one of these queues has completed a burst, and this queue can write the burst to the buffer. Therefore, this queue can formulate another burst either for the IP that it was supporting up to  $T_b$  or the queue can be reassigned by the controller to serve another IP. Thus, in this scenario, the worst case is that we have to keep the k queues serving their IPs for as long as no queue has completed a burst: assuming that each queue receives an Ethernet frame in a round robin fashion  $T_B$  is at most equal to  $k \times t_m b$ .

According to the above, the efficiency of the VOQs architecture is defined as the maximization of the utilization of the available resources and the DRAM buffer throughput. For this purpose, the design has to: a) include k queues for preparing the bursts, so that each queue prepares a burst that will be stored in an active destination's linked list of pages; b) minimize latency and c) minimize the number of the k queues along with their size. The succeeding paragraphs describe how we achieve the above goals and they describe in detail the operations of the VOQs Controller as well as its functional blocks and components.

The ToR switch is connected with 10G Ethernet to the servers through its south ports. First, the Ethernet Frames that arrive from the servers at the rate of 10G are buffered in the port queue of the 10G Ethernet module and then are forwarded and buffered to the two *Input Frame Queues* (Figure 2.3) in the following way: we start counting the incoming frames and depending on the arrival sequence the odd numbered incoming Ethernet Frames are stored in the first *Input Frame Queue* (the upper queue on Figure 2.3) and the even Ethernet Frames to the second queue. This dual queue architecture gives us the necessary time in order to perform in

real-time the two following operations on the Ethernet Frames: while we store a frame in one of the *Input Frame Queues*, we calculate its size and extract its destination's IP, which then are stored to two queues of significantly lesser size, the *IP ID* queue and the *SIZE* queue, which are positioned close to each *Input Frame Queue* in the design of Figure 2.3.

Each frame's IP stored in the *Input Frame Queues* is passed as input (address) to a LUT, named BRAM in Figure 2.3. The LUT will specify (will give as output) the id of an Active Destination Queue (on Figure 2.3 we show an example design with four queues): in the specified Active Destination Queue we will buffer all the Ethernet Frames with the current active destination IP, in order to form a burst that it will be stored in the linked list of pages of that destination in the DRAM buffer. Apart from the id of the Active Destination Queue in that BRAM location is also stored a flag (0/1). When the flag is equal to "1", it specifies the case in which the Active Destination Queue id (stored in the LUT) is granted to the active destination IP. Alternatively, the case when the flag equals to "0" indicates that the frame's destination IP is not yet served by any of the Active Destination Queues and hence, the controller has to assign an Active Destination Queue to this IP. Now, we consider the case of an Ethernet frame arriving at the ToR and its IP address does not correspond to any of the Active Destination Queues. If we have correctly calculated (during the design of the ToR) the minimum required number of the Active Destination Queues that it is sufficient to serve the application demands, the VOQs controller will have an empty Active Destination Queue available for assignment to a newly arrived Ethernet frame that requests an Active Destination Queue to buffer the following frames with the same IP destination. All the id (numbers) of the unused Active Destination Queues are buffered in the queue named *Empty Queues* in Figure 2.3. At the same clock cycle that we read from the BRAM the id of the Active Destination Queue that serves the frame's IP along

with the "1/0" (assigned to a queue or not) flag, we also read the first empty queue id from the *Empty Queues*. The multiplexer shown at Figure 2.3 bellow the *BRAM* is controlled by the flag in order to select: a) the *BRAM* output when the flag equals "1" and b) the *Empty Queues* output if the flag is "0". In the first case where we will use the *BRAM* output, the empty queue id that was just extracted from *Empty Queues* will be returned back in the *Empty Queues*, since it was not used. The above design minimizes the latency for the assignment of an active queue to the new destination.

We have to mention that in order to exploit the high throughput of the DRAM interface, we have to write the Ethernet Frames in the shared buffer as a burst of contiguous words of a significant length (512 bits in the example implementation of the proposed architecture). We note here that, in a writing burst of Ethernet frames the last 512-bit word might not be completely filled with Ethernet frames payload and for completing the burst we add 0xFF as padding. The simple padding provides the advantage of simplifying the control and it reduces the latency at the cost of the dummy data overhead in many pages in the shared buffer. This padding overhead becomes larger for small Ethernet frames and it is reduced significantly in the case of full Ethernet frames. Note here that, when it's time to transmit a TDMA frame the shared memory will provide us with a page: we must be informed regarding the exact number of the useful data in this page in order to remove the padding. For this purpose, we store in the header of each page the useful size along with the actual page size, which is the overall sum of the useful size and the size of the padding stored in the shared buffer.

A small size dual port memory shown in Figure 2.3 as *Queue-ID Memory*, stores the IP that it is currently served by each *Active Destination Queue*. Each address X of the *Queue-ID Memory* corresponds to the *Active Destination Queue* with id X. The data at that address X of the *Queue-ID Memory* is the destination's IP that is accommodated by this Active Destination Queue. When it is the first time that an Ethernet Frame is stored in an empty Active Destination Queue the id of this queue is used as the address to the Queue-ID Memory, and in that address, we store the frame's IP. During the whole time that this Active Destination Queue serves the IP, the Queue-ID Memory keeps the IP in that address. Only when an Active Destination Queue is left with all its data forwarded to the shared buffer, we will: first, erase the contents of the served destination in the BRAM by acquiring the address (IP) from the Queue-ID Memory and second, write the queue id to the Empty Queues to refresh the Active Destination Queues that are vacant and they can be granted to another destination IP. Consequently, the location in the Queue-ID Memory will be overwritten by the new IP, which will be served by the corresponding Active Destination Queue.

The proposed design minimizes the time required to perform all the previously mentioned operations with respect to clock cycles. The architecture can achieve the time minimization due to the parallelization of the operations and as a result, the VOQ architecture diminishes the latency of each stage. Consequently, the *Active Destination Queues* can be as many as the application dictates as upper bound. Moreover, the length of each queue doesn't need to grow beyond the size of the burst that it is specified by the DRAM controller for reaching its maximum throughput.

The block called *Memory Map* stores all the information related to each linked list in the shared buffer associated to each destination IP. The memory map entries are shown in Figure 2.4, 2.5 in two working examples. Each entry of the *Memory Map* block has the following pointers: one at the address of the first page of the list noting from what page we are currently reading data to transmit; one to the last page, required to inform the VOQs that this is the page, which currently stores all the Ethernet frames for the associated destination; one for the "next to write"

#### LUT Memory Map

Figure 2.4: Memory Map Organization while Buffering

address of the last page (writing position in Figure 2.4), one for the "next to read" address of the first page (reading position in Figure 2.5). Moreover, the *Memory Map* entry provides the exact number of useful data in the page: this information is used to compute the total volume of data of the Ethernet frames with or without the padding.

The pointers at each *Memory* Map block location are refreshed during each burst write/read transaction. Thus, at the beginning of a write/read operation to/from the DRAM buffer we know the exact number of the data (bytes) that will be written/read. We operate the linked list of pages as a queue since we always transmit the head page of the list. The memory map architecture is able to concurrently

#### **LUT Memory Map**

Figure 2.5: Memory Map Organization Concurrent Write & Read Operations

write and read from the same linked list of pages as shown in Figure 2.5.

A noteworthy advantage of the novel VOQ technique is the scalability of the architecture, which can be easily configured to accommodate various numbers of *Active Destination Queues*, the size of the DRAM shared buffer and the size of the *Memory Map* block. The pointers and the size of the linked list of pages for each destination are stored in block rams (BRAM) in the FPGA. The required size of the BRAMs is proportional to: first, the DRAM memory size, and second the number of destinations in the data center network. In case the size of the mapping information is relatively large, hence constraining the implementation of the Memory Map block with internal BRAM memory, the proposed Memory Map can be stored on external Static Random Access Memory (SRAM).

# 2.5 FPGA Implementation Details

We have realized an example VOQs design with four (4) active destinations (k = 4 is adequate for most applications in accordance with our  $T_B$  and k calculations). The development of the example implementation was made on the NetF-PGA SUME board using the Xilinx Vivado development tool. The design includes 3 Intellectual Property (IP) hardware Cores from Xilinx: a) 10GbE Subsystem, which includes the MAC and the 10GbE PCS/PMA b) Integrated Block for PCI Express c) Memory Interface Generator (MIG) for the shared DRAM buffer. The NetFPGA board receives the scheduling commands from the host desktop PC, which is running Linux and communicates with the data center's controller, which runs on a different PC in the same local network.

The resources occupied in the NetFPGA SUME for the VOQs Controller are presented in the Table 1, reported by the Vivado tool. The input small sized queues are all performing at 156 Mhz clock and use 64 bits word length, in order to comply with the 10G Ethernet physical layer standard. The Active Destination Queues and memories alongside of them in our implementation are performing at 200 MHz with 512-word length to match the bus width of the Advanced Microcontroller Bus Architecture (AMBA) Advanced eXtensible Interface 4 (AXI4) of the Double Data Rate 3 (DDR3) DRAM controller.

| Resource | Utilization |  |

|----------|-------------|--|

| LUT      | 2639        |  |

| LUTRAM   | 1285        |  |

| FF       | 4848        |  |

| BRAM     | 62          |  |

| DSP      | 50743       |  |

Table 2.1: Resource Utilization of VOQs Controller

# 3 | Tools for Data Center Control

# 3.1 Introduction

Currently, the integration of Information Technology (IT) activities and applications takes place in data centers, which also include the necessary devices for communication, high performance computing and data storage. Data centers play an important role in organizations based on IT services, as they provide the means for fast responses to business demands, they facilitate the IT operations and their utilization leads to the reduction of the capital expenditures and the operating costs. Targeting the improvement of data centers, researchers and engineers focus on the use of optical switching due to the bandwidth capabilities that it provides. A significant contribution to this design effort features optical links connected through optical PoD switches to the ToR switches, SDN with OpenFlow organization, an Agent connecting the SDN controller and the data plane and an enhanced agent management tool (Kyriakos, Tsavalos, & Reisis, 2017), which all integrate in the Nephele data center (Bakopoulos et al., 2018).

The current Chapter presents a management tool for the Agent of the Nephele's data center. The advantage of creating and using the proposed management tool is that the data center designers and engineers can create their own schedule as the tool's GUI users and then transfer that schedule to each data plane ToR switch. The user can control graphically in real time the transmission of Nephele frames originating at the ToR switch to the other Nephele ToRs in the data center network. Moreover, the management tool can be of even further use if it will be extended to create the scheduling tables of a PoD switch in the Nephele network. The first Section of the Chapter highlights the Control of the Nephele data center and the Agent. The second Section presents the Agent's management tool.

### **3.2** Background on Nephele's Data Center Control

The Nephele is based on a dynamic optical network infrastructure for scale-out, disaggregated datacenters that leverages optical switching with SDN control and orchestration to overcome current datacenter limitations. The Nephele design follows vertical end-to-end development approach extending from the data center architecture to the overlaying control plane and its interface to the application, in order to deliver a fully-functional networking solution, extending network virtualization to the optical layer. The Nephele design achieves dynamic reconfiguration by utilizing the slotted operation of the network based on the Time-Division Multiple Access (TDMA). Moreover, the SDN control can effectively manage the data plane elements. The OpenFlow protocol communicates the SDN control's messages to the data plane (McKeown et al., 2008). Nephele uses an Agent to realize the communication between the SDN controller and the data plane. The Agent includes functions filtering the control plane (SDN controller and the Agent) instructions that are transmitted through the OpenFlow messages; the Agent translates these messages and forwards them to the corresponding ToR switch. Although, the Agent can be classified as a back-end process, there is a need for an interactive management tool that allows the interaction of the designers and the future users with the Agent. The need for the above tool appeared in the course of the data center's design and implementation phase, it became more emphatic during the integration and finally the validation and testing phases. Similar interactive tools are reported in the literature as important tools for the management, testing and evaluation of networks (Lin & Geigel, 1997), (Turon, 2005), (Corazza & Reale, 1992).

Focusing on providing an effective tool mainly for advancing, testing and monitoring the Agent's functionality and performance (Landi et al., 2017), the current Chapter presents a management tool for the Nephele Agent. The proposed Agent's tool is able to access all the information that it is directed to the data plane. Moreover, it can be used to create the commands for the data plane, monitor the commands transmission to the devices and also, the corresponding responses of the devices to the Agent. Furthermore, it provides the ability to request all the information with respect to the status of the devices. The use of the proposed management tool contributed significantly to the development of the entire Nephele data center and consequently the testing phase. Additionally, it benefits the entire system because it will still be most suitable for effectively monitoring the Agent's performance during normal operation and also it provides the means for realizing scenarios in the cases of demonstrations and presentations (Landi et al., 2017).

The architecture of the Nephele data center is presented in Chapter 2, in this chapter we will elaborate on the control plane of the data center. The Nephele data center is designed for an operation that includes dynamic and efficient sharing of the optical resources and a collision free network operation by using Time Division Multiple Access (TDMA). The control plane is based on a Software Defined Network (SDN). The SDN controller is divided in two distinct interfaces, namely the Northbound Interface and the Southbound Interface. A high-level view of the Nephele control plane architecture is presented on Figure 3.1.

The Application to Controller Plane Interface defined by ONF (Open Networking Foundation) in the SDN architecture is realized by the Northbound Interface of the Nephele SDN controller. This interface allows the interaction between the core services of the Nephele SDN controller and the upper layer network applications, which implement the logic of the network resource allocation in the data center. The Nephele's design follows the approach of an overall centralized architecture. For this purpose, all the scheduling plans are carried out according to the algorithms that are performed by the central controller's Traffic Offline Schedul-

Figure 3.1: Nephele SDN Control Plane

ing Engine (Christodoulopoulos et al., 2016). Considering the optimization of the utilization of the entire network the Offline Scheduling Engine is equipped with mechanisms able to allocate resources of the data center network in the long term.

The data-controller plane interface defined by ONF in the SDN architecture is realized by the Southbound Interface of the Nephele SDN controller. The commonly used in these cases OpenFlow has been chosen as a standardized communication channel for this interface. It executes two main tasks: to command and configure the data plane devices via the device specific Agents. A device specific Agent performs as a proxy for the data plane switching devices. Consequently, the Agent should have two communication interfaces the Agent-Controller interface and the Agent-FPGA interface. The Nephele Agent's is mainly devoted to filter the control plane instructions, that are included in the OpenFlow messages. Additionally, the Agent translates these instructions and then, it forwards them to the corresponding FPGA via a PCI Express interconnection. The Agent is a back-end process. It is activated at the beginning of each Nephele scheduling period and it will communicate the new schedule instructions in order to configure the data plane switches. The instructions come in the form of scheduling tables; the format of these scheduling tables is presented by Figure 3.2.

| Timeslot | Destination | VLAN | Wavelength |

|----------|-------------|------|------------|

| 1        |             |      |            |

|          |             |      |            |

|          |             |      |            |

| 80       |             |      |            |

|          |             |      |            |

Figure 3.2: The Format of the Scheduling Table

# 3.3 The Management Tool of the Agent

The present section describes first the graphical user interface (GUI) architecture of the management tool of the Agent; second, the tool's usability and third, the back-end of the management tool.

#### 3.3.1 The GUI Architecture

The Agent's management tool is implemented by using the JavaFX software platform of the Java programming language; JavaFX consists of a set of graphics and media packages, which provide the means to the developers for the design, creation, testing, debugging, and deployment of rich client applications that operate consistently across diverse platforms. The management tool includes a GUI that presents to the user a Nephele network of smaller size as an image-map. This image-map includes clickable areas, which are illustrated graphics created on a raster graphics editor and enhanced with interactive attributes. This design has led to the implementation of a graphic environment, which, considering the interaction of the user with the management tool, ensures both, optimized usability and user experience, compared to an environment using the standard widgets, provided by JavaFX.

The user of the management tool sees the data center network, the scheduling table, an explanatory image and a menu, which are brought to her/him as the main scene of the GUI. This main scene is shown in Figure 3.3. The smaller scale network includes four PoDs residing in the network and connected via four WDM (Wavelength Division Multiplexing) rings. Each of the PoDs includes four PoD elements; these are divided into the disaggregated rack and the ToR switch.

The GUI includes an explanatory image, that is located over the menu in the right top corner. The image presents an enlargement of a PoD element in higher resolution and it is augmented with annotations, so that the user is able to understand what the image portrays.

In order to present the graphic display of the PoD elements three objects of the ImageView class were stacked in a StackPane object (Johan Vos, 2014). This design has been implemented as follows: three image layers have been aligned one over another (depicted by Fig. 3.4), so that they appear as a single solid object and at the same time the developer can handle each one independently. The ImageView object is a type of Node object in the JavaFX Scene Graph that is used for painting a view; the painting is carried out by using data contained in an Image object. The StackPane is also a type of Node object acting as the layout container and it contains the ImageView objects. The three ImageView objects include the images that represent the ToR switch, the disaggregated rack and a visual effect.

In the GUI, the ToR switches are the interactive parts of the management tool: the

Figure 3.3: The GUI Main Scene

user can select by clicking on them and she/he can create the scheduling table of the data center. Each ToR is a clickable area and it can be used by the user as the source and/or the destination in the scheduling table entry. In our case, the upper left ToR is chosen by default as the host Agent PC scheduling engine. This is the source ToR and the remaining ToRs are the destinations. The interactive feature is accomplished by registering an event handler on the ImageView object that includes the ToR image. An event handler is an implementation of the EventHandler interface. The handle() method of this interface will let the code filling the entries in the scheduling table to perform if the ToR image is clicked. Upon the cursor click event, all the necessary code is executed to fill in the required fields of a scheduling table's entry. The management tool fills the Destination field with the identity (id) of the ToR switch where the event occurred. The Timeslot field takes the value of the time sequence of the event, which is calculated based on a counter. The Wavelength field is filled with a value selected from a closed interval of integer values. Finally, the VLAN (Virtual LAN) field entry represents the identification number that is assigned to the WDM ring, through which the data transmission will occur. Furthermore, when the ToR is clicked, as depicted in Figure 3.4, it will trigger the effect displaying that it is the selected ToR. The effect is represented by a brighter image enclosing the ToR switch. The effect is set not to be visible at first, it will be set to full opacity if the ToR is selected and it will return to zero opacity with a two seconds lasting fade transition. The fade transition is an instance of the FadeTransition class, which is a subclass of the JavaFX Animation class and it changes the opacity of a node over a given time. The same effect has been implemented similarly to the WDM rings and it indicates graphically what WDM ring is chosen based on the VLAN field in the scheduling table entry.

All the aforementioned elements of the tool's design let the user to construct the scheduling table and provide the option of editing it; this operation can be carried out by the use of the menu. The menu consists of four buttons and inherits its attributes from the Vbox class, which is a container that sorts its contents into a single vertical column. The menu buttons were created as a separate class. It is distinct from the Button class of JavaFX and is created by stacking a TextField object over a filled Rectangle object. This object's filling is colored by an instance of the LinearGradient class, in order to apply effects that are suitable to the entire design of the GUI and preserve the uniformity to the user eye. These effects are triggered by the events originating from the mouse cursor and their implementation is based on switching the order of the colors in the gradient fill. Each time the user clicks the Add menu button she/he will start a new session of constructing a scheduling table and the source ToR will be automatically selected

Figure 3.4: Effect of clicking the ToR

and indicated. A scheduling period of the Nephele network can accommodate up to eighty entries, as the corresponding allowed time slots. If the user exceeds that ceiling, a pop-up dialog box will emerge with the corresponding message, prompting her/him to stop importing entries. The dialog box prevents the user from interacting with the main application window but it keeps the window visible in the background. When the user has completed the creation of the scheduling table, she/he is able to review it and delete any misplaced entries by using the delete button from the menu. If the key is pressed and no entry is selected or the scheduling table is empty, a pop-up window will be called informing the user of the corresponding case. As a final step the user presses the send button, an action which transmits the scheduling table to the FPGA data plane devices.

The conclusion of the transaction is marked by the appearance of a pop-up window that it will be shown to the user. The window includes all the values that were sent

Figure 3.5: Pop-up Window with the Values sent to FPGA

to the FPGA in a format that resembles that of a logic analyzer. The pop-up window is shown in Figure 3.5 and the corresponding output of the logic analyzer is depicted in Figure 3.6. The logic analyzer exports the output as a CSV file (Comma-Separated Values); this file can be processed by the management tool and in this case, the file's values will be forwarded to the pop-up window. The pop-up window incorporates the graphical theme of the management tool and is designed to model the layout of the logic analyzer.

### 3.3.2 Usability of the Agent's Management Tool

Figure 3.6: Output of the Logic Analyzer

The use of the management tool is of great importance to the development and operation of the data center, since the users can create their own traffic schedule and then transfer that schedule to the data plane ToR switch. The engineers are able to control the data plane switches, during the development and testing phase of the physical layer of the data center network as shown in Fig 3.7. The tool's GUI allows to construct the commands directly in the format of the scheduling tables of the FPGAs (instead of using the OpenFlow protocol). Additionally, it is straightforward to extend the management tool for creating the scheduling tables of a PoD switch in the Nephele network. Given the fact that there is a ToR Agent PC for each ToR switch in the network, the tool is executed on the Agent computer and it provides the user with the means for the scheduling of the network from the view point of the specific ToR switch. The user can control graphically and more importantly in real-time the transmission of Nephele frames originating at the ToR switch (that is controlled by the Agent computer) to the other Nephele ToRs in the data center network (Chen JW, 2007).

Figure 3.7: Nephele Data Plane Development

The benefit of designing, developing and effectively using the proposed management tool has already been proven during test procedures and demonstrations. An illustrious example is the application, which has been shown during a presentation of the control plane of the Nephele data center. The scenario for this demonstration has as follows: the control plane includes parts of the FPGA's implementations of the data plane, the Agent, and the SDN controller. Given that a functional data center Agent was not available, we presented the control plane by dividing it into two experiments. The first experiment demonstrates the SDN controller and the second the FPGA's operation controlled by the management tool. The management tool has successfully imitated the functions of the Agent; the majority of the people that interacted with the management tool understood the concepts behind the architecture of the Nephele network and the function of the Agent in the Nephele data center. The demonstration as shown in Figure 3.8 consists of the SDN controller software presentation, the FPGA that represents the ToR switch, and the Desktop PC that executes the management tool, which is connected to the FPGA board via PCI Express. The user can interact with the management tool and give his/her own commands to the demonstration system.

#### 3.3.3 Back-End of the Agent's Management Tool

In the Nephele data center the ToR switch design includes multiple FPGAs; all the FPGAs that belong to a single ToR implementation use PCI Express to communicate with the host ToR Agent computer. The management tool divides the scheduling information into distinct parts, so that each part corresponds to the scheduling information concerning the corresponding FPGA; then it creates distinct threads to complete the entire operation. We use a single thread to communicate with a single FPGA and transfer the respective part of the ToR switch traffic schedule. Note here that, the communication is performed in parallel for all the FPGAs belonging to the same ToR switch.

In order to develop the PCI Express interface of the FPGAs we used the Xilinx IP Core for PCI Express and the RIFFA (Reusable Integration Framework for FPGA Accelerators) framework (Jacobsen et al., 2015). The framework consists of an

Figure 3.8: Live Demo of the Management Tool

API (Application Programming Interface), a driver/kernel module and an IP core for the FPGAs. All the above parts are open-source. It is designed to perform with the Xilinx IP core that handles the physical layer of the PCI Express interface. The API is designed to support multiple languages like C/C++, Java and Python. Moreover, it includes the necessary function/methods that the management tool needs to invoke, in order to communicate with the FPGA. The entire API is designed to be executed by threads and the design of the management tool takes full advantage of this capability.

The communication that is directed from the Agent PC to a FPGA operates according to the following steps. In the first, the application initiates the transaction by calling the fpga\_send method. Then, the thread invokes the operation of the kernel driver, which writes to the FPGA configuration registers the necessary information to begin the transaction. The FPGA uses DMA (Direct Memory Access) to read the scatter gather elements (Jacobsen et al., 2015) that the driver instructed. At the time that the transaction will be completed the driver will read the final count of the data passed, the amount of the data is then returned to the management tool as the return value of the fpga\_send method.

In the design of the tool special attention was paid to the operation of the RIFFA API, because the RIFFA's driver requires all the data in contiguous memory locations (in an array). Note here that, the Java's Array object can't be used in this case. An attractive solution to this problem is the employment of the ByteBuffer Class of Java, which is a class that is created to handle a stream of raw data. The operations on the buffer can be carried out byte by byte, but casting is also supported for the user to be able to write a whole Java data type, like an integer.

Finally, the endian of the data has been tackled as follows. The JVM (Java Virtual Machine) stores class files in big endian byte order, where the high byte comes first. Multibyte data items are always stored in big-endian order. Given that the Xilinx FPGAs operate in little-endian byte order, the change of the endianness could be arranged either during the construction of the ByteBuffer or at the receiving buffer in the FPGA. The latter choice has been proven more efficient and gave us the advantage of the ByteBuffer casting, which would not be useful in the case of changing the order of the byte inside the ByteBuffer in the Java application.

# 4 Neural Networks on FPGA

# 4.1 Introduction