## Western University Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2009

# High-Performance Hardware and Software Implementations of the Cyclic Redundancy Check Computation

Christopher E. Kennedy

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Kennedy, Christopher E., "High-Performance Hardware and Software Implementations of the Cyclic Redundancy Check Computation" (2009). *Digitized Theses*. 4161. https://ir.lib.uwo.ca/digitizedtheses/4161

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# HIGH-PERFORMANCE HARDWARE AND SOFTWARE IMPLEMENTATIONS OF THE CYCLIC REDUNDANCY CHECK COMPUTATION (SPINE TITLE: HARDWARE AND SOFTWARE IMPLEMENTATIONS OF THE CRC COMPUTATION)

(THESIS FORMAT: MONOGRAPH)

by

Christopher E. Kennedy

Faculty of Engineering Department Electrical and Computer Engineering

> Submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada April, 2009

© Christopher E. Kennedy 2009

## Abstract

The Cyclic Redundancy Check (CRC) is an error detection code used in many digital transmission and storage systems. The two major research areas surrounding CRCs concern developing computation approaches and studying error detection properties. This thesis aims to explore the various aspects of the CRC computation, with the primary objective being to propose novel computation approaches which outperform the existing ones. The work begins with a thorough examination of the formulations found throughout the literature. Then, their subsequent realizations as hardware architectures and software algorithms are investigated. During this investigation, some improvements are presented including optimizations of the state-space transformed and primitive architectures. Afterward, novel formulations are derived and the most significant contribution consists of a matrix decomposition that gives rise to a high-performance software algorithm. Simulation and implementation results are gathered for both hardware and software deployments of the investigated computation approaches. The theoretical results obtained by simulations are validated with implementation experiments. The proposed algorithm is shown to outperform the existing comparable low-memory algorithm in terms of time complexity.

**Keywords:** Cyclic Redundancy Check (CRC), computer arithmetic, hardware architecture, software algorithm, field-programmable gate array (FPGA), applicationspecific integrated circuit (ASIC).

## Dedication

To my parents, Peter and Maureen, for their love, guidance, and everlasting support.

### Acknowledgements

This project would not have been possible without the thoughtful and creative insight of my supervisor, Dr. Reyhani-Masoleh. His experience and encouragement kept me motivated and focused throughout this thesis project. I wish to acknowledge our research group for their positive feedback and constructive criticisms of the work. The assistance which they provided with the various tools that were required to complete the project was invaluable. The comments received from the anonymous external reviewers of our journal manuscript and conference papers were quite helpful in identifying weak areas of our work and giving praise to others. Finally, I cannot fully express my gratitude towards my parents for all the assistance and guidance that they have provided throughout my studies.

# Contents

**M**.

| Ce  | ertific | ate of Examination      | ii           |

|-----|---------|-------------------------|--------------|

| Ał  | ostra   | ct                      | iii          |

| De  | edicat  | tion                    | iv           |

| Ac  | knov    | vledgements             | $\mathbf{v}$ |

| Co  | onten   | $\mathbf{ts}$           | vi           |

| Lis | st of   | Tables                  | x            |

| Lis | st of   | Figures                 | xi           |

| Lis | st of   | Algorithms x            | iv           |

| No  | omen    | clature                 | xv           |

| Pr  | eface   | x                       | vii          |

| 1   | Intr    | oduction                | 1            |

|     | 1.1     | Preview                 | 1            |

|     |         | 1.1.1 Organization      | 2            |

|     | 1.2     | Cyclic Redundancy Check | 2            |

|     | 1.3     | Motivation              | 3            |

|     | 1.4     | Approach                | 3            |

|     | 1.5     | Objectives              | 4            |

| 2   | Prel    | iminaries               | 5            |

|     | 2.1     | Preview                 | 5            |

|     |         | 2.1.1 Organization      | 5            |

|   | 2.2  | Binary  | Polynomial Arithmetic                | 6  |

|---|------|---------|--------------------------------------|----|

|   |      | 2.2.1   | Binary Fields                        | 6  |

|   |      | 2.2.2   | Binary Polynomials                   | 7  |

|   | 2.3  | CRC E   | Basics                               | 9  |

|   |      | 2.3.1   | Mathematics                          | 9  |

|   |      | 2.3.2   | Generator Polynomials                | 11 |

|   |      | 2.3.3   | Sample Computation                   | 13 |

|   |      | 2.3.4   | Serial Implementations               | 14 |

|   |      | 2.3.5   | Error Detection                      | 15 |

|   | 2.4  | Summa   | ary                                  | 18 |

| 3 | Lite | rature  | Analysis                             | 19 |

|   | 3.1  |         | w                                    | 19 |

|   |      | 3.1.1   | Organization                         | 20 |

|   | 3.2  | Paralle | el Formulation Fundamentals          | 20 |

|   |      | 3.2.1   | Binary Polynomial Approach           | 20 |

|   |      | 3.2.2   | State-Space Approach                 | 25 |

|   | 3.3  | Hardw   | are Architectures                    | 28 |

|   |      | 3.3.1   | Primitive Architectures              | 29 |

|   |      | 3.3.2   | Two-Step Architecture                | 31 |

|   |      | 3.3.3   | Cascade Architecture                 | 35 |

|   |      | 3.3.4   | Look-Ahead Architecture              | 37 |

|   |      | 3.3.5   | State-Space Transformed Architecture | 42 |

|   |      | 3.3.6   | Retimed Architectures                | 45 |

|   | 3.4  | Softwa  | re Algorithms                        | 45 |

|   |      | 3.4.1   | Assumptions                          | 46 |

|   |      | 3.4.2   | Bit-wise Algorithm                   | 48 |

|   |      | 3.4.3   | Table Look-up Algorithm              | 49 |

|   |      | 3.4.4   | Reduced Table Look-up Algorithm      | 51 |

|   |      | 3.4.5   | On-the-Fly Algorithm                 | 52 |

|   |      | 3.4.6   | Tea-Leaf Reader Algorithm            | 54 |

|   |      | 3.4.7   | Joshi-Dubey-Kaplan Algorithm         | 54 |

|   |      | 3.4.8   | Slicing Algorithms                   | 55 |

|   |      | 3.4.9   | Distributed Table Look-up Algorithm  | 56 |

|   |      | 3.4.10  | Look-up Table Generation             | 57 |

|   | 3.5  | Summ    | ary                                  | 59 |

ł

ä......

| 4 | Nov                                                                                      | vel Computation Approaches               | 61                                                                                                                                                                  |

|---|------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1                                                                                      | Preview                                  | 61                                                                                                                                                                  |

|   |                                                                                          | 4.1.1 Organization                       | 61                                                                                                                                                                  |

|   | 4.2                                                                                      | Binary Polynomial to Matrix Approach     | 62                                                                                                                                                                  |

|   |                                                                                          | 4.2.1 Formulation                        | 62                                                                                                                                                                  |

|   |                                                                                          | 4.2.2 Realization                        | 64                                                                                                                                                                  |

|   | 4.3                                                                                      | Lambda Gamma Approach                    | 68                                                                                                                                                                  |

|   |                                                                                          | 4.3.1 Formulation                        | 68                                                                                                                                                                  |

|   |                                                                                          | 4.3.2 Matrix Decomposition               | 70                                                                                                                                                                  |

|   |                                                                                          | 4.3.3 Algorithm Realization              | 75                                                                                                                                                                  |

|   |                                                                                          | 4.3.4 Architecture Realization           | $77^{\circ}$                                                                                                                                                        |

|   | 4.4                                                                                      | Extended Binary Polynomial Architecture  | 78                                                                                                                                                                  |

|   |                                                                                          | 4.4.1 Formulation                        | 78                                                                                                                                                                  |

|   |                                                                                          | 4.4.2 Realization                        | 83                                                                                                                                                                  |

|   | 4.5                                                                                      | Message Splitting Architecture           | 86                                                                                                                                                                  |

|   |                                                                                          | 4.5.1 Formulation                        | 86                                                                                                                                                                  |

|   |                                                                                          | 4.5.2 Realization                        | 88                                                                                                                                                                  |

|   | 4.6                                                                                      | Summary                                  | 90                                                                                                                                                                  |

|   |                                                                                          |                                          |                                                                                                                                                                     |

| 5 | Sim                                                                                      | ulations and Implementations             | 91                                                                                                                                                                  |

| 5 |                                                                                          | nulations and Implementations<br>Preview | <b>91</b><br>91                                                                                                                                                     |

| 5 | <b>Sim</b><br>5.1                                                                        | Preview                                  | 91                                                                                                                                                                  |

| 5 | 5.1                                                                                      | Preview                                  |                                                                                                                                                                     |

| 5 |                                                                                          | Preview                                  | 91<br>92                                                                                                                                                            |

| 5 | 5.1                                                                                      | Preview                                  | 91<br>92<br>92                                                                                                                                                      |

| 5 | 5.1<br>5.2                                                                               | Preview                                  | 91<br>92<br>92<br>93<br>102                                                                                                                                         |

| 5 | 5.1                                                                                      | Preview                                  | 91<br>92<br>92<br>93<br>102<br>104                                                                                                                                  |

| 5 | 5.1<br>5.2                                                                               | Preview                                  | 91<br>92<br>93<br>102<br>104<br>105                                                                                                                                 |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                            | Preview                                  | 91<br>92<br>92<br>93<br>102<br>104                                                                                                                                  |

| 5 | 5.1<br>5.2                                                                               | Preview                                  | 91<br>92<br>93<br>102<br>104<br>105<br>107<br>109                                                                                                                   |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                | Preview                                  | <ul> <li>91</li> <li>92</li> <li>93</li> <li>102</li> <li>104</li> <li>105</li> <li>107</li> <li>109</li> <li>110</li> </ul>                                        |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                | Preview                                  | <ul> <li>91</li> <li>92</li> <li>93</li> <li>102</li> <li>104</li> <li>105</li> <li>107</li> <li>109</li> <li>110</li> <li>110</li> </ul>                           |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Cor</li> </ul>              | Preview                                  | <ul> <li>91</li> <li>92</li> <li>93</li> <li>102</li> <li>104</li> <li>105</li> <li>107</li> <li>109</li> <li>110</li> <li>111</li> </ul>                           |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Cor</li> </ul>              | Preview                                  | 91<br>92<br>93<br>102<br>104<br>105<br>107<br>109<br><b>110</b><br>111<br>111                                                                                       |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Cor</li> <li>6.1</li> </ul> | Preview                                  | <ul> <li>91</li> <li>92</li> <li>93</li> <li>102</li> <li>104</li> <li>105</li> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>111</li> </ul> |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Cor</li> <li>6.1</li> </ul> | Preview                                  | 91<br>92<br>93<br>102<br>104<br>105<br>107<br>109<br><b>110</b><br>111<br>111                                                                                       |

1

i.

|                        | 6.3   | Future Work                          | 113 |

|------------------------|-------|--------------------------------------|-----|

|                        |       | 6.3.1 Hardware Architectures         | 113 |

|                        |       | 6.3.2 Software Algorithms            | 114 |

| $\mathbf{A}$           | CRO   | C-32 Hardware Architecture Equations | 115 |

|                        | A.1   | Parallel LFSR Architectures          | 116 |

|                        | A.2   | Lambda Gamma Architecture            | 118 |

|                        | A.3   | State-Space Transformed Architecture | 120 |

|                        | A.4   | Two-Step Architecture                | 123 |

| В                      | CRO   | C-32 Software Algorithm Data         | 128 |

|                        | B.1   | Table Look-up Algorithm              | 129 |

|                        | B.2   | Reduced Table Look-up Algorithm      | 131 |

|                        | B.3   | Slicing-by-4 Algorithm               | 132 |

|                        | B.4   | Lambda Gamma Algorithm               | 138 |

|                        | B.5   | On-the-Fly Algorithm                 | 138 |

| $\mathbf{C}$           | z-Tr  | ansform Approach                     | 139 |

| D                      | Lite  | rature Errata                        | 145 |

| Bi                     | bliog | raphy                                | 150 |

| $\mathbf{V}\mathbf{i}$ | ta    |                                      | 157 |

1

# List of Tables

| 2.1  | CRC binary polynomials                                              | 10  |

|------|---------------------------------------------------------------------|-----|

| 2.2  | Generator polynomials                                               | 12  |

| 2.3  | Gamma sets                                                          | 12  |

| 3.1  | Two-Step Architecture multiple polynomials                          | 32  |

| 3.2  | Two-Step Architecture multiplicand polynomials.                     | 34  |

| 3.3  | Look-Ahead Architecture polynomial relationships.                   | 38  |

| 3.4  | Optimum state-space transform vectors                               | 44  |

| 3.5  | Optimum state-space transform comparison                            | 44  |

| 3.6  | Hexadecimal representations of generator polynomials.               | 47  |

| 4.1  | Lambda sets.                                                        | 77  |

| 5.1  | Non-pipelined hardware architecture comparison.                     | 93  |

| 5.2  | Optimum degrees of parallelism and hardware complexity              | 95  |

| 5.3  | Computation time for optimum degrees of parallelism.                | 96  |

| 5.4  | Optimum $ps$ for the CRC LFSR $p$ Architecture                      | 99  |

| 5.5  | LFSR hardware architecture delay comparison                         | 99  |

| 5.6  | State-Space Transformed Architecture coupling matrix logic hardware |     |

|      | comparison.                                                         | 101 |

| 5.7  | State-Space Transformed Architecture hardware comparison            | 101 |

| 5.8  | Two-Step Architecture hardware comparison                           | 102 |

| 5.9  | State-Space Transformed Architecture ASIC implementation results.   | 103 |

| 5.10 | Non-pipelined architecture FPGA implementation results              | 104 |

| 5.11 | Software algorithm comparison.                                      | 106 |

# List of Figures

| 1.1  | Different stages of the approach                            | 4  |

|------|-------------------------------------------------------------|----|

| 2.1  | Modulo-2 truth tables.                                      | 7. |

| 2.2  | Example CCITT-4 binary polynomial long division computation | 13 |

| 2.3  | Generalized serial LFSR Architectures.                      | 15 |

| 2.4  | Example CCITT-4 serial hardware computation.                | 16 |

| 3.1  | Illustration of the message polynomials                     | 22 |

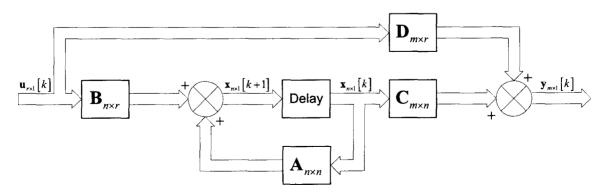

| 3.2  | General state-space model                                   | 25 |

| 3.3  | Delay diagram of the serial CRC LFSR2 Architecture          | 26 |

| 3.4  | Delay diagram of the serial CRC LFSR1 Architecture          | 27 |

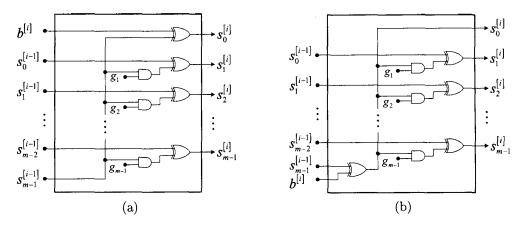

| 3.5  | Generalized parallel LFSR2 Architecture                     | 29 |

| 3.6  | Generalized parallel LFSR1 Architecture                     | 31 |

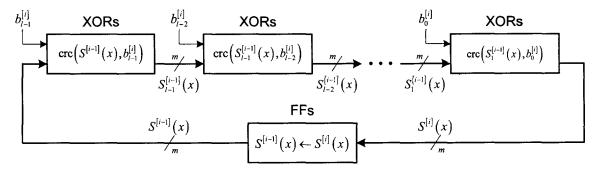

| 3.7  | Generalized Two-Step Architecture.                          | 34 |

| 3.8  | Generalized Cascade Architecture                            | 36 |

| 3.9  | Generalized cascade combinational logic blocks.             | 37 |

| 3.10 | Non-optimized parallel CRC computation architecture.        | 39 |

| 3.11 | Generalized look-ahead combinational logic block.           | 41 |

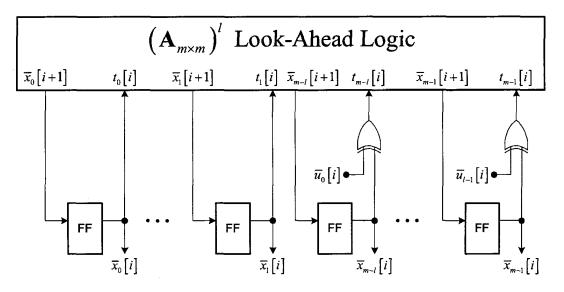

| 3.12 | Generalized Look-Ahead Architecture.                        | 41 |

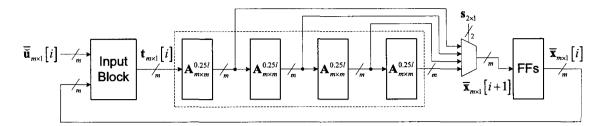

| 3.13 | Design of the Flexible Look-Ahead Architecture.             | 42 |

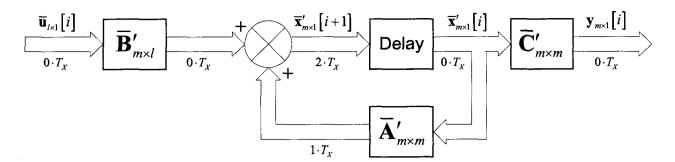

| 3.14 | Generalized State-Space Transformed Architecture.           | 45 |

| 3.15 | Illustration of the message array.                          | 47 |

| 3.16 | Illustration of CRCB Endianness.                            | 49 |

| 4.1  | Matrix $G_{32\times 32}$ for CRC-32                         | 64 |

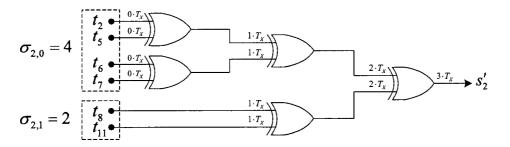

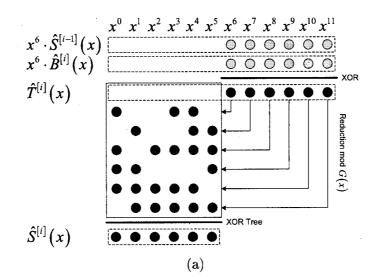

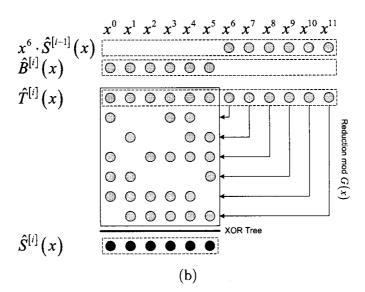

| 4.2  | Example DARC-8 XOR tree architecture                        | 66 |

| 4.3  | Generalized optimized parallel LFSR2 Architecture           | 67 |

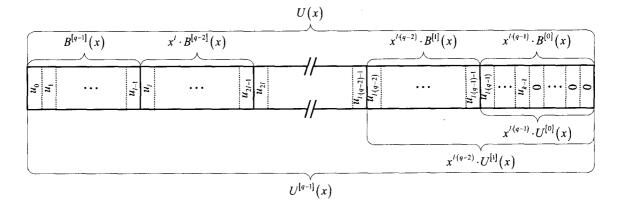

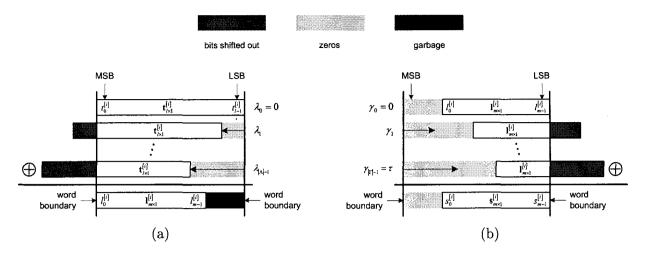

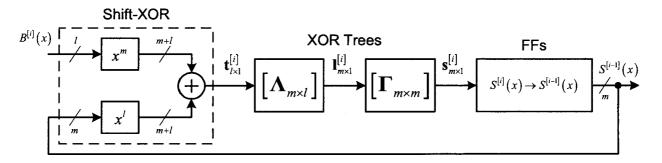

| 4.4  | Illustration of the Lambda Gamma Algorithm                  | 76 |

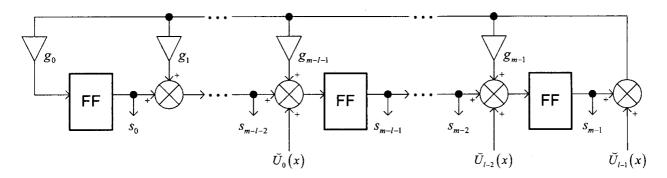

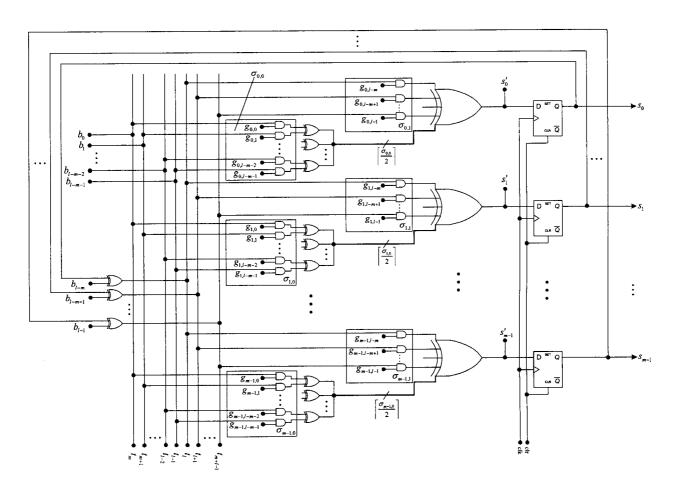

| 4.5  | Generalized Lambda Gamma Architecture                       | 78 |

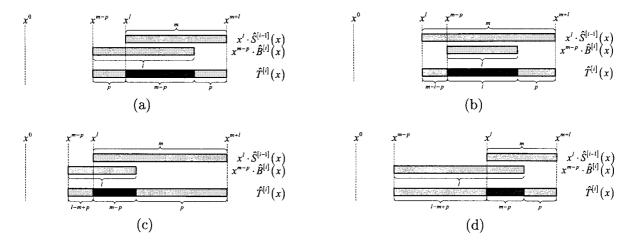

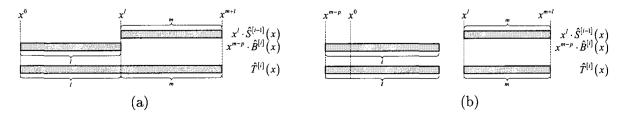

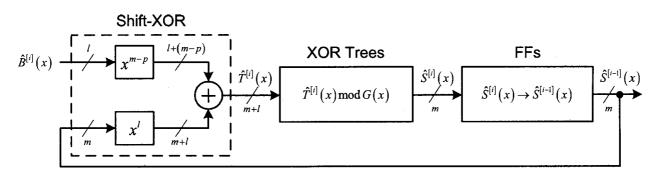

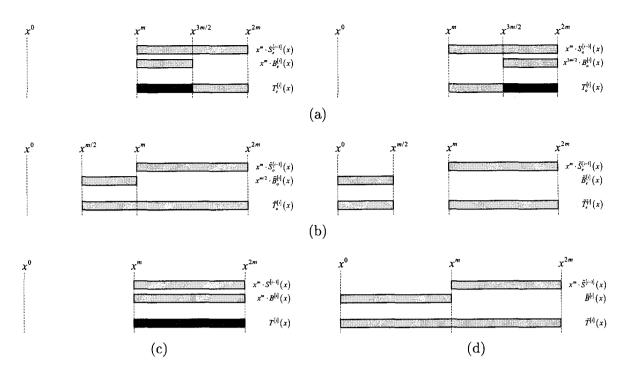

| 4.6  | Illustrations of the LFSR $p$ overlapping polynomial situations            | 80  |

|------|----------------------------------------------------------------------------|-----|

| 4.7  | Illustrations of the $LFSRp$ non-overlapping polynomial situations         | 81  |

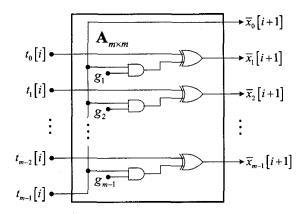

| 4.8  | Generalized parallel LFSR $p$ Architecture                                 | 83  |

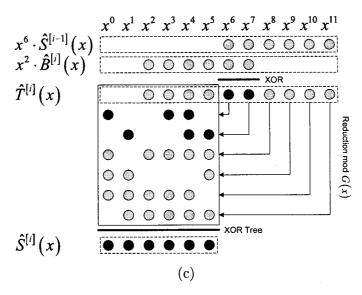

| 4.9  | Example DARC-6 dot notation for the parallel $LFSRp$ Architecture.         | 85  |

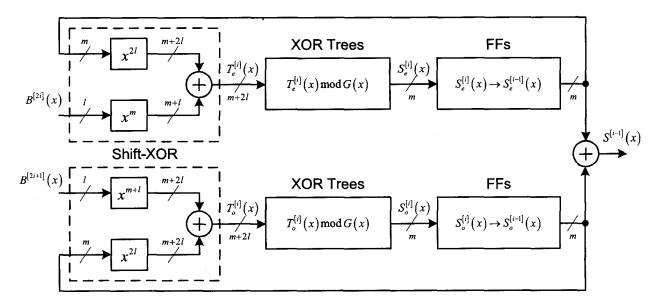

| 4.10 | Generalized parallel Message Splitting Architecture                        | 88  |

| 4.11 | Illustrations of the Message Splitting Architecture overlapping polyno-    |     |

|      | mial situations.                                                           | 89  |

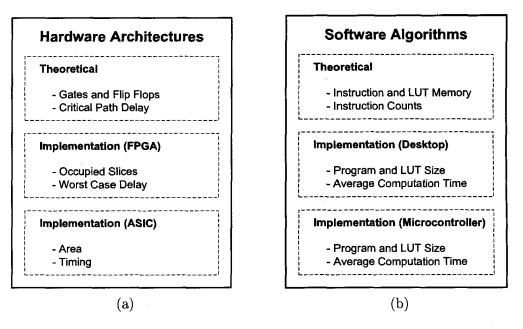

| 5.1  | Different quantitative comparison metrics.                                 | 92  |

| 5.2  | LFSR2 Architecture plot of the delay and hardware complexity               | 95  |

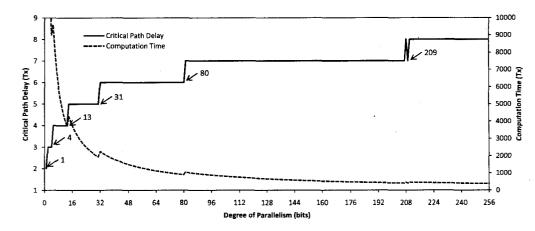

| 5.3  | LFSR2 Architecture plot of the delay and computation time                  | 96  |

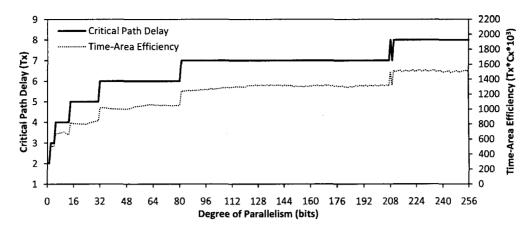

| 5.4  | LFSR2 Architecture plot of the delay and time-area product                 | 97  |

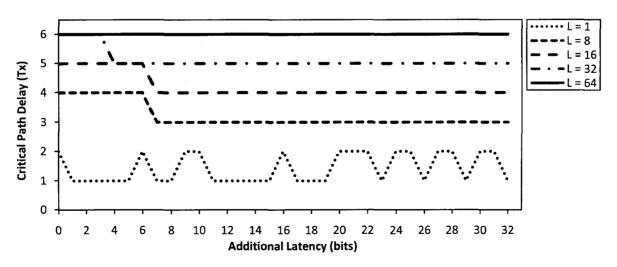

| 5.5  | LFSR $p$ Architecture plot of the delay versus latency                     | 97  |

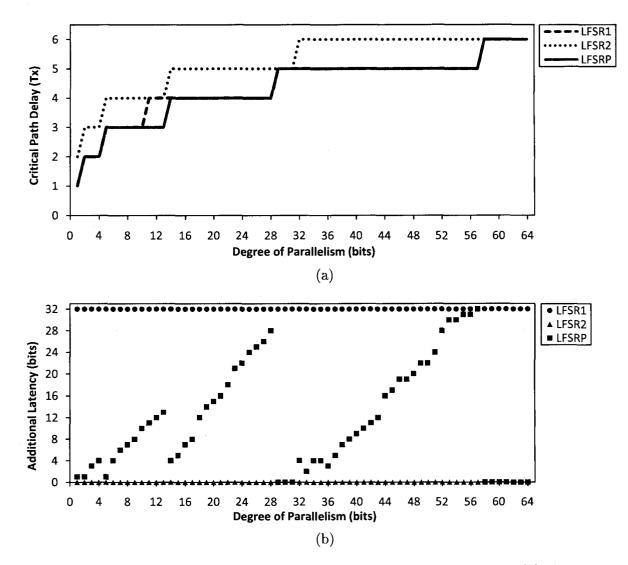

| 5.6  | LFSR Architecture plot of the delay and latency.                           | 98  |

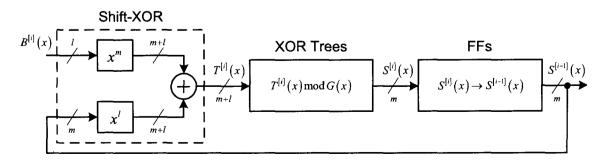

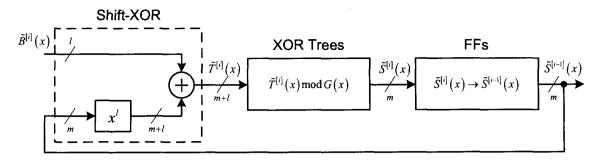

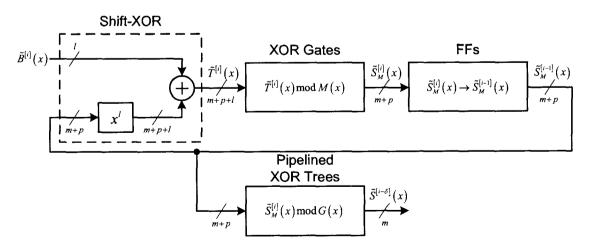

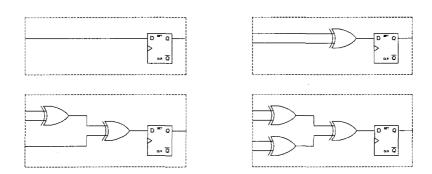

| 5.7  | State-Space Transformed Architecture pipelining blocks.                    | 100 |

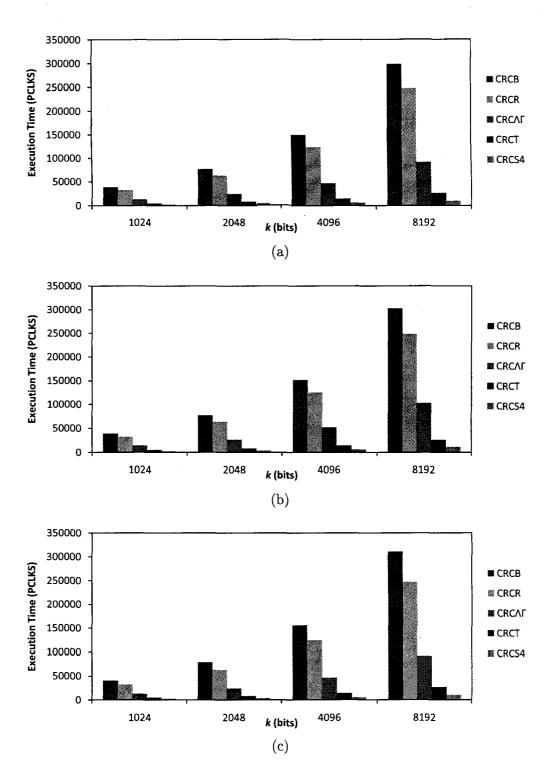

| 5.8  | Algorithm timing plots                                                     | 108 |

| A.1  | Parallel LFSR2 Architecture $\mathbf{G}_{32 \times 32}$ equations          | 116 |

| A.2  | Parallel LFSR1 Architecture $G_{32\times 32}$ equations                    | 117 |

| A.3  | Lambda Gamma Architecture $\Lambda_{32 \times 32}$ equations               | 118 |

| A.4  | Lambda Gamma Architecture $\Gamma_{32 \times 32}$ equations                | 119 |

| A.5  | State-Space Transformed Architecture $\mathbf{A}'_{32\times 32}$ equations | 120 |

| A.6  | State-Space Transformed Architecture $\mathbf{B}'_{32\times 32}$ equations | 121 |

| A.7  | State-Space Transformed Architecture $C'_{32\times 32}$ equations          | 122 |

| A.8  | Two-Step Architecture first step equations.                                | 123 |

| A.9  | Two-Step Architecture second step equations (1 of 4)                       | 124 |

| A.10 | Two-Step Architecture second step equations (2 of 4)                       | 125 |

| A.11 | Two-Step Architecture second step equations (3 of 4)                       | 126 |

| A.12 | 2 Two-Step Architecture second step equations (4 of 4)                     | 127 |

| B.1  | CRCT(8) LUT entries (1 of 2)                                               | 129 |

| B.2  | CRCT(8) LUT entries (2 of 2).                                              | 130 |

| B.3  | CRCR(32) LUT entries.                                                      | 131 |

| B.4  | CRCS4(32) LUT_56 entries (1 of 2)                                          | 132 |

| B.5  | CRCS4(32) LUT_56 entries (2 of 2)                                          | 133 |

| B.6  | CRCS4(32) LUT_48 entries (1 of 2)                                          | 134 |

| B.7  | CRCS4(32) LUT_48 entries (2 of 2)                                          | 135 |

ke.

| B.8  | CRCS4(32) LUT_40 entries (1 of 2). $\ldots$ $\ldots$ $\ldots$       | 136 |

|------|---------------------------------------------------------------------|-----|

| B.9  | $CRCS4(32)$ LUT_40 entries (2 of 2)                                 | 137 |

| B.10 | CRCA $\Gamma$ (32) LUT entries: (a) $\Lambda$ LUT, (b) $\Gamma$ LUT | 138 |

| B.11 | CRCF(8) equations                                                   | 138 |

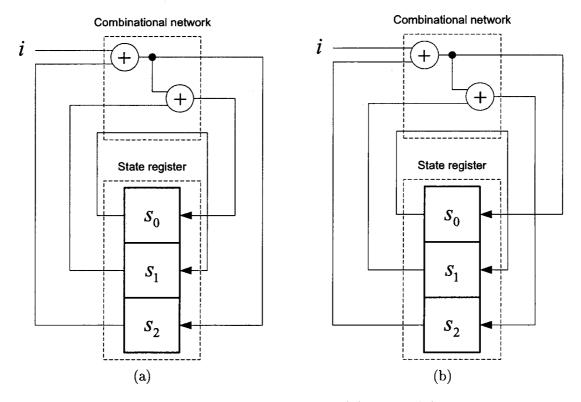

| C.1  | Discrete-time system illustration of the serial LFSR2 Architecture  | 139 |

| D.1  | Cascade literature error.                                           | 148 |

| D.2  | State-Space Transformation literature error.                        | 149 |

.

# List of Algorithms

| 3.1 | Bit-wise Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Table Look-up Algorithm.    .    .    .    .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51 |

| 3.3 | Reduced Table Look-up Algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53 |

| 3.4 | Slicing-by-4 Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56 |

| 3.5 | Table Look-up LUT Generation Algorithm.         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | 57 |

| 3.6 | Reduced Table Look-up LUT Generation Algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58 |

| 3.7 | Slicing LUT Generation Algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59 |

| 4.1 | Lambda Gamma Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

| 4.2 | Lambda LUT Generation Algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 77 |

# List of Acronyms

| Δ                  | critical path delay of an architecture       |  |  |

|--------------------|----------------------------------------------|--|--|

| $\Phi$             | computation time of an architecture          |  |  |

| Θ                  | hardware cost of an architecture             |  |  |

| $C_F$              | hardware cost of a flip-flop                 |  |  |

| $C_X$              | hardware cost of a two-input XOR gate        |  |  |

| $T_X$              | hardware delay of a two-input XOR gate       |  |  |

| AND                | logical and                                  |  |  |

| ARQ                | automatic repeat request                     |  |  |

| ASIC               | ASIC application-specific integrated circuit |  |  |

| ATM                | Asynchronous Transfer Mode                   |  |  |

| CMOS               | complementary metal-oxide semiconductor      |  |  |

| CPD                | critical path delay                          |  |  |

| CRC                | Cyclic Redundancy Check                      |  |  |

| $CRC\Lambda\Gamma$ | Lambda Gamma Algorithm                       |  |  |

| CRCB               | Bit-wise Algorithm                           |  |  |

| CRCD               | Distrubuted Table Look-up Algorithm          |  |  |

| CRCF               | On-the-Fly Algorithm                         |  |  |

| CRCJDK             | Joshi-Dubey-Kaplan Algorithm                 |  |  |

- CRCR Reduced Table Look-up Algorithm

- CRCS4 Slicing-by-4 Algorithm

- CRCS8 Slicing-by-8 Algorithm

- CRCT Table Look-up Algorithm

- EDC error detection code

- FCS frame check sequence

- FEC forward error correction

- FF flip-flop

- FPGA field-programmable gate array

- HDL hardware description language

- IEEE Institute of Electrical and Electronics Engineers

- IP intellectual property

- LFSR linear feedback shift register

- LSB least significant bit

- LTI linear time-invariant

- LUT look-up table

- MSB most significant bit

- PC personal computer

- PCLKS processor clock ticks

- PS pipeline stage

- VLSI very-large-scale integration

- XOR logical exclusive-or

# Preface

T HIS thesis aims to provide the reader with an understanding of the principles of the Cyclic Redundancy Check (CRC) computation. We assume that the reader has minimal knowledge of CRCs and have made our best effort to present the material accordingly. Many different conventions for describing the CRC computation exist in the literature, and we have selected what we feel are the best set of notations. In our presentation, we separate the formulations from the deployments, either in hardware or software for this case. By taking this approach, we have found that the ideas are more clearly conveyed to the non-expert reader.

Our experience has taught us that examples are an excellent tool for expressing the various CRC computation approaches. However, providing completely worked in-text examples would distract the reader from the further reaching concepts of a given approach. To combat this problem, we have included two appendices which contain the implementation details for some useful hardware architectures and software algorithms.

The preliminaries and literature analysis contained in this thesis provide the reader with a solid foundation in CRCs, which allows them to understand our contributions and the open research questions in this area. From the contributions contained in this thesis, we have had two refereed conference papers accepted and are proceeding with our second revised submission of a full journal manuscript. The comments received from the reviewers of our first journal submission have helped us improve our experimental methodology and gave us thoughtful advice on ways to clarify the formulation.

Finally, we draw inspiration from Évariste Galois; the late French mathematician who laid the foundations for Galois theory, which is the branch of mathematics that CRCs are based on. Without his contributions, this work would not have been possible.

## Organization

The organization of the content contained in this thesis is as follows. In Chapter 1, we provide the introduction. In Chapter 2, the preliminaries required to understand the CRC computation are reviewed. In Chapter 3, our analysis of the literature is presented. In Chapter 4, the novel CRC formulations and their resultant realizations as hardware architectures and software algorithms are proposed. In Chapter 5, the simulation and implementation comparison of the studied architectures and algorithms is presented. In Chapter 6, the conclusions and future work are discussed. In Appendix A, hardware equations for some CRC-32 computation architectures are listed. In Appendix B, software look-up table entries for some CRC-32 computation algorithms are listed. In Appendix C, the z-Transform approach to obtain parallel hardware equations is reviewed. In Appendix D, the identified technical errors in the literature are corrected.

A portrait of Évariste Galois (1811 - 1832).

# Chapter 1

## Introduction

## 1.1 Preview

A N increasing number of designers are utilizing wireless communication technology in their systems. However, wireless networks are more susceptible to transmission errors; some causes are random channel noise, fading of signals, and atmospheric conditions. Due to the greater probability of transmission errors occurring in these systems, it is necessary to verify the integrity of a received message using an error detection code (EDC). Research for fast and flexible computation methods for dependable EDCs is ongoing.

One of the more popular EDCs is the Cyclic Redundancy Check (CRC) [1]. From a certain perspective, the CRC can be considered as an insecure hash function. In other words, the CRC function maps a large variable length message to a small fixed sized checksum. This checksum is appended to its message to form a codeword. The redundancy in the codeword is typically used to verify the integrity of a message after it has been transmitted or stored.

The two major research areas surrounding CRCs concern its error detection properties and computation approaches. This thesis is primarily focused on the study of the mathematics and performance of the various approaches that perform the CRC computation. The existing formulations and their resulting realizations as hardware architectures and software algorithms are extensively reviewed, and some novel computation approaches are proposed.

In this chapter, we briefly introduce CRCs to set the stage of our study. Afterward, the motivation, approach, and objectives of this thesis are outlined.

#### 1.1.1 Organization

The remainder of this chapter is organized as follows. In Section 1.2, the basic concepts of the CRC are introduced. In Section 1.3, the motivation for this thesis is presented. In Section 1.4, the approach taken in this thesis is explained. In Section 1.5, the objectives of our work are stated.

## 1.2 Cyclic Redundancy Check

In information theory, there are two major error control strategies: forward error correction (FEC) and automatic repeat request (ARQ) [2]. FEC must be used when the transmission channel is unidirectional and detected errors must be corrected by the receiver. ARQ may be used in bidirectional communication systems when it is more convenient to simply detect an error and request a retransmission. ARQ codes are typically more light-weight in terms of the number of redundant bits and computation times compared to FEC [2].

The CRC was proposed in 1961 by Peterson and Brown [1] as a separable EDC, that is now used in many digital transmission and storage systems. Before transmission, a message has its CRC appended as a frame check sequence (FCS) to form a codeword. On arrival, the FCS of the received message is computed and compared with the sent FCS; if they differ, an error is detected, else the transmission is assumed to be error free. When errors are detected, the transmission protocol dictates what action should be taken, i.e., discard the corrupted data and/or send a retransmission request.

Some examples of digital communication standards where the CRC is currently employed are, the Asynchronous Transfer Mode (ATM) [3], and the Institute of Electrical and Electronics Engineers (IEEE) communication standards, such as, IEEE 802.3 (Wired Ethernet) [4], IEEE 802.11 (WiFi) [5], and IEEE 802.16 (WiMAX) [6].

As aforementioned, the main research activities concerning CRCs consist of error detection properties and computation approaches. In [1], the authors propose using a linear feedback shift register (LFSR) to perform the CRC computation. This simple architecture operates serially, processing one message bit per clock cycle. After [1], a large amount research effort has been invested in developing parallel hardware architectures and software algorithms that perform the computation more quickly or efficiently, and this thesis continues along this path.

## 1.3 Motivation

In this section, we present the motivation for our study. With the current wireless telecommunications boom that is world is undergoing, ensuring data integrity will become more of an issue in the future. The CRC is an attractive option for use in communication systems, because it is easily described mathematically and the error detection properties are well understood. Moreover, there are many different approaches to perform the CRC computation, and any contributions that advance or improve upon these ideas could end up being deployed in real-world industrial systems.

In terms of the amount of research attention it receives, the CRC can be considered a hot topic. At the time of this writing, recent IEEE Transactions journal papers with contributions pertaining to the theory of CRCs include [7], [8], [9], [10], [11], and [12]. This demonstrates the large amount of current interest in this area. Furthermore, the most recent and only survey [13], was published in 1988, and many developments have happened since then. For these reasons, we feel that the time is right for a fresh investigation and discussion of this topic.

## 1.4 Approach

h.,

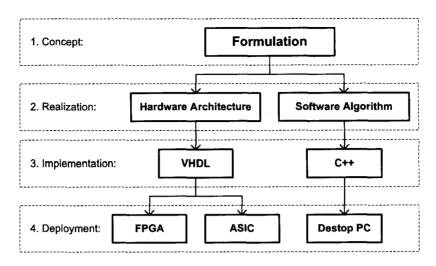

In this section, we present the approach of our study. Since this thesis is in the field of computer arithmetic, generally, all of the concepts discussed stem from a mathematical formulation. After one performs some manipulations and obtains a desired formulation, the next step is realizing that formulation as a hardware architecture or software algorithm. After realization, one proceeds to implement the architecture or algorithm, using a hardware description or programming language, respectively. Finally, the implementation is then deployed on a platform and its correctness can be verified. Figure 1.1 illustrates how we go through these steps in this study.

In this thesis, all of the formulations begin from the CRC equation, that is introduced in [1]. As shown later, many computation schemes have been deduced from the application of different techniques to manipulate that equation. Our approach begins by generalizing those existing methods found in the literature. By accomplishing this, we have more flexibility to describe and compare the different schemes which have been previously published. Afterward, we present some novel formulations and their resultant realizations as CRC computation approaches that yield new architectures and algorithms.

Figure 1.1: Different stages of the approach.

In terms of the experimental methodology, after an architecture or algorithm has been proposed, one can perform simulations to obtain the theoretical area/memory and time complexities. The majority of the simulation data in this thesis is obtained through custom C++ software, that has been written by the author over the course of this study. These theoretical evaluations serve to validate our experimental results gathered through deployment of our implementations on their respective platforms.

## 1.5 Objectives

The primary objective of this thesis is to propose novel CRC computation approaches which outperform the existing ones. In this study, the performance of an approach is measured in terms of both area/memory and time complexity. In order to achieve this primary objective, we first strive to provide the reader with a complete understanding of the fundamentals of the CRC computation. This involves using consistent notations to derive and generalize the previous computation approaches. We then perform simulations and experiments to demonstrate the high performance of our novel approaches, and we thoroughly explore the area/memory versus time complexity trade-off. Also, we aim to identify and propose some improvements to the existing computation approaches. Finally, we suggest open research questions that could be the focus of future work.

# Chapter 2

# Preliminaries

### 2.1 Preview

The Cyclic Redundancy Check (CRC) is a term that most of us have come across at one time or another reading computer literature in the Internet age. In this chapter, we present the preliminaries required to discuss the various aspects surrounding the CRC. This includes a review of the branch of mathematics that CRCs operate in, the first hardware architectures proposed to implement the computation, and the general error detection properties.

Like most topics in information technology, the presentation style and notations used to describe the mathematics of the CRC computation have evolved considerably since being first introduced by Peterson and Brown in 1961 [1]. Emphasis has shifted from discussing the basic serial computation case to more complex parallel computation cases, and exhaustive explorations of error detection properties have been undertaken. In light of these advancements, the goal of this chapter is to review the fundamental material using more modern notations and conventions, and lay the foundation for discussing the material in later chapters.

#### 2.1.1 Organization

The remainder of this chapter is organized as follows. In Section 2.2, the topic of binary polynomial arithmetic is reviewed. This includes a discussion of binary fields and binary polynomials, i.e., polynomials over GF(2). In Section 2.3, the CRC basics are introduced using modern conventions. This includes mathematics, generator polynomials, serial hardware architectures, and basic error detection properties. This chapter is concluded with a summary in Section 2.4. We note that, most of the material contained in this chapter can be found in [1], [2], and [13].

### 2.2 Binary Polynomial Arithmetic

This section quickly reviews the fundamentals of the branch of mathematics that is required for an understanding of CRC computation. This involves discussing the binary Galois field GF(2) and binary polynomials. This material forms the basis for the later binary polynomial formulation of the CRC computation. For a more formal and in-depth discussion of these topics, we refer the reader to [2] and [14].

#### 2.2.1 Binary Fields

To begin, we roughly define a field to be a set of elements for which one can perform addition, subtraction, multiplication, and division without leaving the set. Furthermore, the commutative, associative, and distributive laws must be satisfied by the addition (+) and multiplication  $(\cdot)$  operations [2], [14].

Next, an adaptation of the formal definition of a field contained in [2] is presented. Let F be a set of elements on which the addition and multiplication operations are defined. The set F together with the addition and multiplication operations, is a field if the following three conditions are satisfied:

- 1. The set F is a commutative group under addition. The identity element with respect to addition is called the zero element and denoted by 0.

- 2. The set of nonzero elements in F is a commutative group under multiplication. The identity element with respect to multiplication is called the unit element and denoted by 1.

- 3. Multiplication is distributive over addition; that is, for any three elements  $f_0$ ,  $f_1$ , and  $f_2$  in F,

$$f_0 \cdot (f_1 + f_2) = f_0 \cdot f_1 + f_0 \cdot f_2.$$

It follows from the above definition that a field must contain at least two elements, namely 0 and 1. In fact, it is the field that contains only these two elements, called the binary Galois field that we are most interested in. Before discussing this field, some basic properties are listed without proof, which can be easily derived from the previous definition of a field [2].

| +   | 0 | 1 |   | • | 0   | 1 |

|-----|---|---|---|---|-----|---|

| 0   | 0 | 1 |   | 0 | 0   | 0 |

| 1   | 1 | 0 |   | 1 | 0   | 1 |

| (a) |   |   | • |   | (b) |   |

Figure 2.1: Modulo-2 truth tables: (a) addition, (b) multiplication.

- 1. For every element  $f_0$  in a field,  $f_0 \cdot 0 = 0 \cdot f_0 = 0$ .

- 2. For any two nonzero elements  $f_0$  and  $f_1$  in a field,  $f_0 \cdot f_1 \neq 0$ .

- 3. For any two elements  $f_0$  and  $f_1$  in a field, for  $f_0 \cdot f_1 = 0$  and  $f_0 \neq 0$ , imply that  $f_1 = 0$ .

- 4. For any three elements  $f_0$ ,  $f_1$ , and  $f_2$  in a field, for  $f_0 \neq 0$ ,  $f_0 \cdot f_1 = f_0 \cdot f_2$ , implies that  $f_1 = f_2$ .

Now consider the binary Galois field denoted as  $GF(2) = \{0,1\}$  that has two elements, with modulo-2 addition and multiplication operations defined in Figures 2.1a and 2.1b, respectively. It is clear that the commutative, associative, and distributive laws hold for the addition and multiplications operations defined on the set GF(2). Thus,  $\{0,1\}$  is a field with two elements under modulo-2 addition and modulo-2 multiplication [2].

Note that binary addition and multiplication between two elements in  $GF(2) = \{0, 1\}$ , can be implemented in hardware using logical exclusive-or (XOR) and logical and (AND) gates, respectively. Throughout this thesis, unless otherwise noted, the addition sign, i.e., "+" is used to denote the XOR operation, and the dot sign, i.e., "." denotes the AND operation. Finally, note that for the set GF(2), addition and subtraction are defined to be the same operation, i.e.,  $1\pm 1 = 0$  and  $1\pm 0 = 0\pm 1 = 1$ .

#### 2.2.2 Binary Polynomials

From the definition of a binary field presented in the previous subsection, we are now ready to discuss binary polynomials. Consider a polynomial whose coefficients are from the binary field GF(2), with the variable x, i.e.,

$$F(x) = f_0 + f_1 x + \dots + f_n x^n,$$

where  $f_i \in \{0,1\}$  for  $0 \le i \le n$ . Polynomials of this form will be referred to as *polynomials over GF*(2) [2]. In this thesis, upper case letters are used to denote polynomials over *GF*(2) and the coefficients are lowercase letters.

The degree of a polynomial is defined as the largest power of x with a non-zero coefficient. Polynomials over GF(2) can be added (or subtracted), multiplied, and divided in the usual way. As an illustration of these operations let

$$G(x) = g_0 + g_1 x + \dots + g_m x^m,$$

be another polynomial over GF(2). Assuming  $m \leq n$ , then addition or subtraction is computed as,

$$F(x) \pm G(x) = (f_0 + g_0) + (f_1 + g_1)x + \dots + (f_m + g_m)x^m + f_{m+1}x^{m+1} + \dots + f_nx^n.$$

For multiplication one has the product

$$F(x) \cdot G(x) = C(x) = c_0 + c_1 x + \dots + c_{n+m} x^{n+m},$$

where

$$c_{0} = f_{0}g_{0}$$

$$= f_{0}g_{1} + f_{1}g_{0}$$

$$= f_{0}g_{2} + f_{1}g_{1} + f_{2}g_{0}$$

$$\vdots$$

$$c_{i} = f_{0}g_{i} + f_{1}g_{i-1} + f_{2}g_{i-2} + \dots + f_{i}g_{0}$$

$$\vdots$$

$$c_{n+m} = f_{n}g_{m}.$$

Note that for CRCs, binary polynomial division is the most important operation. From the Euclidean division algorithm, one knows that when F(x) is divided by G(x), a unique pair of polynomials over GF(2) is obtained: Q(x) called the quotient and R(x) called the remainder. Thus the relationship

$$F(x) = Q(x) \cdot G(x) + R(x)$$

(2.1)

is obtained, where the degree of R(x) is less than the degree of G(x). From (2.1) one can adopt the following notation for expressing the calculation of R(x) from F(x) and G(x) as

$$R(x) = F(x) \mod G(x).$$

The traditional elementary school long-division technique is often used when computing the division operation of two binary polynomials, and in the following section an example is provided in Figure 2.2.

#### **Data Representation**

It is convenient to represent binary strings as polynomials over GF(2) [2]. However, one source of confusion often arises with the Endianness associated to mapping bit positions of the binary strings to the coefficients of the polynomial [15]. In the CRC literature, two methods are readily used, the first being mapping the most significant bit (MSB) to the coefficient of the term with the highest power of x down to the least significant bit (LSB) being mapped to coefficient of the  $x^0$  term, i.e., 1011 1001  $\rightarrow$  $x^7 + x^5 + x^4 + x^3 + x^0$ . The second method is the reverse of the first, with the MSB being mapped to the coefficient of the  $x^0$  term up to the LSB being mapped to the coefficient of the largest power, i.e., 1011 1001  $\rightarrow x^0 + x^2 + x^3 + x^4 + x^7$ . These conventions will be referred to as the normal and reverse notation, for the first approach and second approach, respectively.

In this thesis, we have chosen to adopt the reverse notation, because software CRC computation algorithms are more efficiently implemented with this approach, and this is consistent the convention used in the latest software based CRC paper [7], as well as [13] and [16]. Also, in hardware it is more popular to illustrate the serial computation architecture using the reverse notation (e.g.: [1], [10], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26]), rather than using the normal notation.

#### 2.3 CRC Basics

After reviewing the related basics of binary polynomial arithmetic in the previous section, we are now prepared to discuss the fundamental aspects surrounding CRCs. In this section, the mathematics of the computation, generator polynomials, serial architectures, and error detection properties are all reviewed.

#### 2.3.1 Mathematics

Let us begin by introducing the following binary polynomials listed in Table 2.1, which are similar to the conventions found in [13]. The *m*-bit CRC polynomial, also called the *syndrome* and denoted by S(x) of a k-bit message, is defined as the

| Polynomial       | Name      | Max Degree |

|------------------|-----------|------------|

| A(x)             | Quotient  | k-1        |

| $E\left(x ight)$ | Error     | k+m-1      |

| $G\left(x ight)$ | Generator | m          |

| $R\left(x ight)$ | Received  | k+m-1      |

| S(x)             | Syndrome  | m-1        |

| $U\left(x ight)$ | Message   | k-1        |

| V(x)             | Codeword  | k+m-1      |

Table 2.1: CRC binary polynomials.

remainder of the division between the message polynomial U(x) multiplied by  $x^m$ , and the (m + 1)-bit generator polynomial G(x), i.e.,

$$S(x) = (x^m \cdot U(x)) \mod G(x).$$

(2.2)

The *n*-bit codeword polynomial, where n = k + m is defined as

$$V(x) = S(x) + x^m \cdot U(x), \qquad (2.3)$$

and consists of the syndrome polynomial concatenated with the message polynomial. The codeword polynomial corresponds to the bits transmitted by the sender. Define the *n*-bit received polynomial R(x) to consist of

$$R(x) = V(x) + E(x), \qquad (2.4)$$

where E(x) is an *n*-bit error polynomial. From (2.4) it is clear that if E(x) = 0, then R(x) = V(x). Define A(x) to the quotient of the division between  $x^m \cdot U(x)$  and G(x), then from the property of Euclidean division one can obtain

$$x^{m} \cdot U(x) = A(x) \cdot G(x) + S(x). \qquad (2.5)$$

Next, in order to discuss the error detection properties one needs to show that the codeword polynomial is a multiple of the generator polynomial. Substituting (2.5) into (2.3) and one obtains,

$$V(x) = S(x) + x^{m} \cdot U(x)$$

=  $S(x) + (A(x) \cdot G(x) + S(x))$

=  $A(x) \cdot G(x)$ . (2.6)

Thus, it is concluded that codeword is a multiple of the generator polynomial. At the receiver, the integrity of a frame is verified by performing one of the two following checks:

- 1. Compute and test to see if  $R(x) \mod G(x) = 0$ .

- 2. Separate R(x) into the received message  $x^m \cdot U'(x)$  and received syndrome S'(x), and then compute and test  $x^m \cdot U'(x) \mod G(x) = S'(x)$ .

If either equality does not hold, then it is known that  $R(x) \neq V(x)$ , and a transmission error is detected. Finally, from the above definitions, it can be shown that if

$$E(x) = F(x) \cdot G(x), \qquad (2.7)$$

then an error will go undetected. Beginning from (2.4) and substituting (2.6) and (2.7), one can obtain,

$$R(x) = V(x) + E(x)$$

=  $(A(x) \cdot G(x)) + (F(x) \cdot G(x))$

=  $(A(x) + F(x)) \cdot G(x)$ .

It is clear that in this case, that  $R(x) \mod G(x) = 0$ , and it is concluded that error patterns of this type are not detectable.

#### 2.3.2 Generator Polynomials

Next, we discuss CRC generator polynomials. Generator polynomials are always of the form,

$$G(x) = 1 + \sum_{i=1}^{m-1} g_i x^i + x^m, \ g_i \in \{0, 1\}$$

(2.8)

i.e., all generator polynomials have nonzero  $x^0$  and  $x^m$  terms [1]. Table 2.2 lists frequently referenced generator polynomials [10]. In this thesis, we denote the second greatest nonzero power of G(x) as  $\tau$ , i.e.,

$$G(x) = 1 + \sum_{i=1}^{\tau-1} g_i x^i + x^{\tau} + x^m.$$

| Name                  | Polynomial                                                     |

|-----------------------|----------------------------------------------------------------|

| CRC-12                | $1 + x + x^2 + x^3 + x^{11} + x^{12}$                          |

| CRC-16                | $1 + x^2 + x^{15} + x^{16}$                                    |

| CCITT-16              | $1 + x^5 + x^{12} + x^{16}$                                    |

| CRC-16†               | $1 + x + x^{14} + x^{16}$                                      |

| CCITT-16 <sup>†</sup> | $1 + x^4 + x^{11} + x^{16}$                                    |

| CRC-32                | $1 + x + x^2 + x^4 + x^5 + x^7 + x^8 + x^{10}$                 |

|                       | $x^{11} + x^{12} + x^{16} + x^{22} + x^{23} + x^{26} + x^{32}$ |

Table 2.2: Frequently referenced generator polynomials.

† denotes reversed polynomial coefficients.

From (2.8), we define the set  $\Gamma$ , as

$$\Gamma = \{\gamma_0, \gamma_1, \cdots, \gamma_{|\Gamma|-1}\} = \{i | g_i = 1, i \in [0, m-1]\},$$

(2.9)

and define the cardinality of the set Gamma to be the number of elements in  $\Gamma$ , denoted as  $|\Gamma|$ . It is noted that  $\gamma_0 = 0$ , since generator polynomials always have a nonzero  $x^0$  term, i.e.,  $g_0 = 1$ . Earlier we defined  $\tau$  to be the second greatest nonzero power in G(x), thus  $\gamma_{|\Gamma|-1} = \tau$ . In later chapters, it will be convenient to show generator polynomials as  $\sum_{i\in\Gamma} x^i + x^m$ , with  $\Gamma = \{\gamma_0 = 0, \gamma_1, \cdots, \gamma_{|\Gamma|-2}, \gamma_{|\Gamma|-1} = \tau\}$ . Table 2.3 lists the Gamma sets of the commonly used generator polynomials.

Observing (2.8), and note that CRC generator polynomials are never divisible by x. If one were to use a generator polynomial that had x as a factor, then the resultant syndrome would always have its zero-order coefficient equal to zero [1]. To illustrate this fact, the following derivation is provided. Consider computing a syndrome using a generator polynomial that has x as a factor, i.e.,  $G(x) = x \cdot G'(x)$ , then  $G'(x) = x^{m-1} + \sum_{i=1}^{m-2} g'_i x^i + 1$ . Using G'(x) in (2.5), one obtains,

$$x^{m-1} \cdot U(x) = A(x) \cdot G'(x) + S'(x),$$

Table 2.3: Gamma sets of frequently referenced generator polynomials.

| Name      | Γ                                                     | $ \Gamma $ |

|-----------|-------------------------------------------------------|------------|

| CRC-12    | $\{0, 1, 2, 3, 11\}$                                  | 5          |

| CRC-16    | $\{0, 2, 15\}$                                        | 3          |

| CCITT-16  | $\{0, 5, 12\}$                                        | 3          |

| CRC-16†   | $\{0, 1, 14\}$                                        | 3          |

| CCITT-16† | $\{0, 4, 11\}$                                        | 3          |

| CRC-32    | $\{0, 1, 2, 4, 5, 7, 8, 10, 11, 12, 16, 22, 23, 26\}$ | 14         |

where S'(x) is at most degree  $x^{m-2}$ . Multiplying both sides by x and one obtains,

$$x^{m} \cdot U(x) = A(x) \cdot G(x) + x \cdot S'(x).$$

Thus, it is shown that if  $G(x) = x \cdot G'(x)$ , then  $S(x) = x \cdot S'(x)$  and always has a zero as its zero-order coefficient.

#### 2.3.3 Sample Computation

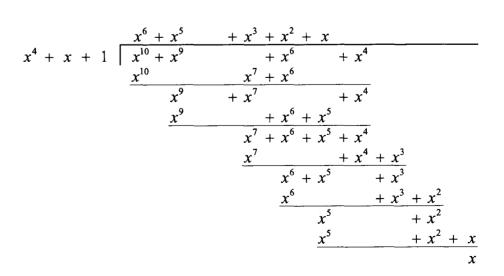

In this subsection, we present a sample CRC computation using the long-division technique. Consider the generator polynomial CCITT-4 ( $G(x) = 1 + x + x^4$  [27]), and the 7-bit message 101 0011. Using the reverse Endianness convention, the 7-bit binary sequence is mapped to the message polynomial as  $U(x) = 1 + x^2 + x^5 + x^6$ . Substituting this message polynomial into (2.2) and one obtains,

$$S(x) = (x^{m} \cdot U(x)) \mod G(x)$$

=  $(x^{4} \cdot (1 + x^{2} + x^{5} + x^{6})) \mod (1 + x + x^{4})$

=  $(x^{4} + x^{6} + x^{9} + x^{10}) \mod (1 + x + x^{4}).$  (2.10)

It is known that when using this generator polynomial the syndrome is 4-bits long, and corresponds to a binary polynomial of at most degree  $x^3$ , i.e.,  $S(x) = \sum_{i=0}^3 s_i x^i$ . One can proceed to perform the reduction in (2.10) and S(x) = x will be obtained. The long-division steps are shown in Figure 2.2, and we remind the reader that in this computation binary polynomials are being used, consequently, addition and

Figure 2.2: Example CCITT-4 binary polynomial long division computation.

subtraction are the same operation. The correctness of the result can be verified by recalling (2.5), and checking that,

$$x^{4} + x^{6} + x^{9} + x^{10} = (x + x^{2} + x^{3} + x^{5} + x^{6}) \cdot (1 + x + x^{4}) + x.$$

The codeword polynomial V(x) is formed by the concatenation of the syndrome polynomial and message polynomial (2.3), and for this example one obtains,

$$V(x) = S(x) + x^{m} \cdot U(x)$$

=  $x + x^{4} + x^{6} + x^{9} + x^{10}$

Using the long-division technique, one can verify that  $V(x) \mod G(x) = 0$ . Finally, the 11-bit codeword is transmitted or stored as 0100 1010 011.

#### 2.3.4 Serial Implementations

The historical serial implementation of the CRC computation (2.2) in hardware consists of a LFSR, which is constructed for a given generator polynomial [1]. The serial LFSR Architecture has a hardware cost

$$\Theta = m \cdot C_F + |\Gamma| \cdot C_X,$$

where  $C_F$  and  $C_X$  denote the cost of a flip-flop (FF) and a two-input XOR gate, respectively.

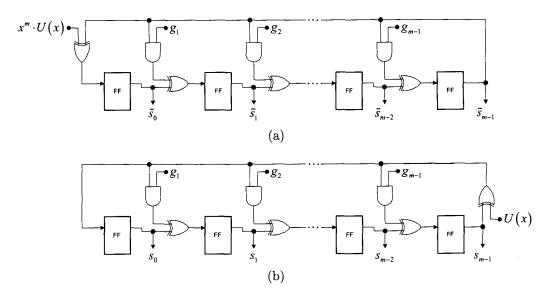

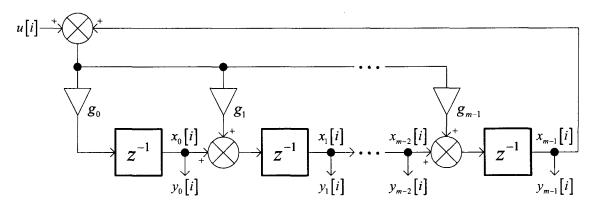

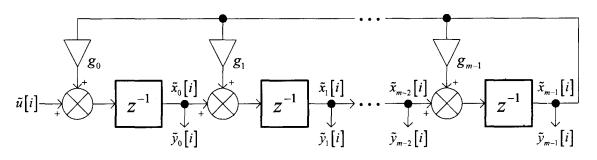

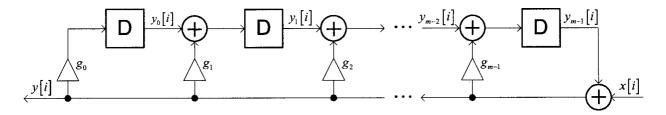

There are two different LFSR architectures presented in [1], named LFSR1 and LFSR2 in [26]. In terms of computation time, LFSR1 requires k + m clock cycles while LFSR2 requires k clock cycles, and the general form of each architecture is shown in Figure 2.3. In practice, all the AND gates are replaced by open or short circuits depending on the coefficients of the generator polynomial, and the XOR gates without present feedback connections are removed. Notice that the critical path delay (CPD), denoted by  $\Delta$ , of LFSR1 is  $1 \cdot T_X$  while LFSR2 has a CPD of  $2 \cdot T_X^{-1}$ , where  $T_X$  denotes the delay of a two-input XOR gate.

If the LFSR2 architecture is used, then the syndrome of a message is computed by feeding the k message bits in, beginning from the coefficient of the highest order term  $u_{k-1}$  down to  $u_0$ , afterward the syndrome of the message is stored in the FFs.

<sup>&</sup>lt;sup>1</sup>If  $G(x) = 1 + x^m$ , then the delay of the LFSR2 architecture is  $1 \cdot T_X$ . However, for the common generator polynomials in Table 2.2 this is never the case.

Figure 2.3: Generalized serial LFSR Architectures for  $G(x) = 1 + \sum_{i=1}^{m-1} g_i x^i + x^m$ : (a) LFSR1, (b) LFSR2.

Alternatively, if the LFSR1 structure is used, then m 0s must be fed in after  $u_0$  to obtain the syndrome [1]. More formally, the LFSR2 architecture performs the CRC computation as  $(x^m \cdot U(x)) \mod G(x)$ , whereas the LFSR1 architecture treats the computation as  $\tilde{U}(x) \mod G(x)$ , where  $\tilde{U}(x) = x^m \cdot U(x)$ . These two serial implementations serve as the starting points for all the parallel hardware architectures and software algorithms that are discussed in later chapters.

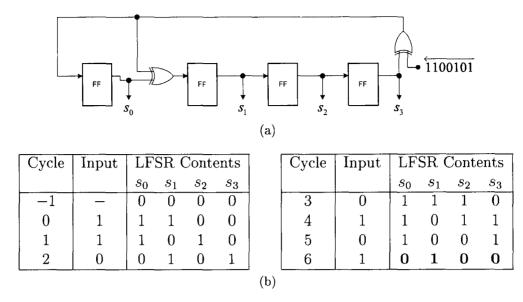

We close this subsection by tracing the previous example computation through the LFSR2 architecture. In Figure 2.4a we provide an illustration of the LFSR2 architecture for the generator polynomial CCITT-4 [27], and Figure 2.4b shows the contents of the FFs after each clock cycle when processing the message U(x) = $1 + x^2 + x^5 + x^6$ . Clock cycle -1 denotes the initial all zero state of the register, and as expected, the final result (marked in boldface) is 0100, which corresponds to  $S(x) = 0 \cdot x^0 + 1 \cdot x + 0 \cdot x^2 + 0 \cdot x^3 = x$ .

#### 2.3.5 Error Detection

A great amount of research effort has been invested in the study of the issues surrounding the error detection performance of CRCs. A complete discussion of this area is beyond the scope of this thesis, but for the sake of completeness, we review the basic concepts, terminology, and results. We refer the reader to the following sets of references for discussions concerning: general error detection properties [1], [13], [28], generator polynomials [8], [27], [29], [30], [31], [32], [33], [34], [35], and different CRC schemes [28], [36], [37], [38].

Figure 2.4: Example CCITT-4 serial hardware computation: (a) LFSR2 Architecture, (b) trace.

Generally, one can say that the error detection performance of a typical CRC scheme depends on three factors:

- the degree of the generator polynomial;

- the generator polynomial coefficients; and

- the length of the message (the number of message bits k).

We say that a CRC scheme is typical, if a codeword is formed by computing and appending the *m*-bit syndrome to a *k*-bit message (2.3). Other situations are possible, such as using product generator polynomials, two-fold, and cascading; for a detailed discussion of the effectiveness of these approaches see [38]. For the remainder of this subsection, our discussion is restricted to the typical scheme.

Recall the earlier definition of the error polynomial in (2.4), and it was shown that it must be a multiple of the generator polynomial for the error pattern to go undetected. The length of a burst error is defined to distance between and including the furthest two corrupted bits in a received codeword, e.g.: the burst error described by the error polynomial  $E(x) = x^i + x^j$  has a length of j - i + 1, assuming  $0 \le i < j < n$ . It is noted that every nonzero coefficient in E(x) corresponds to an inversion in the codeword at that bit position. From these concepts, we are ready to discuss some results for simple error patterns. Consider the situations when the *i*-th codeword bit is inverted, then  $E(x) = x^i$ for  $0 \le i < n$ . Since G(x) always has present  $x^0$  and  $x^m$  terms (2.8),  $x^i$  cannot be expressed as a multiple of G(x) and this type of error will always be detected.

For the cases when there are only two codeword bit inversions, they are described by the error polynomial  $E(x) = x^i + x^j$  with  $0 \le i < j < n$ . This error polynomial can be factored as  $E(x) = x^i \cdot (1 + x^{i-j})$ , and it is concluded that two bit errors will go undetected if and only if G(x) evenly divides  $1 + x^{i-j}$ .

For all burst errors of length less than m, the error polynomial can be written as  $E(x) = x^i \cdot P(x)$ , where the degree of P(x) is less than the degree of the generator polynomial. Then, one has  $P(x) \mod G(x) = P(x)$  and this error is always detected.

Here, some useful error detection theorems for CRCs are given without proof, and they can be found in [28].

- All single-bit errors will be detected because the generator polynomial always has more than one term. The simplest generator polynomial is G(x) = 1 + x (2.8).

- All cases where an odd number of bit errors have occurred will be detected if a generator polynomial has  $x^a + 1$  for a > 0, as a factor.

- All single- and double-bit errors will detected if the degree of the codeword polynomial is no greater than the period<sup>2</sup> of the polynomial.

- All single-, double-, and triple-bit errors will be detected if the generator polynomial has  $x^a + 1$  for a > 0 as a factor, and the degree of the codeword polynomial is no greater than the period of the generator polynomial.

- All burst errors of length less than or equal to m are detected.

- The misdetection probability  $P_{md}$ , is defined to be the ratio of the total number of error patterns to the number of possible error patterns that go undetected,

$$P_{md} \approx \frac{2^k - 1}{2^n - 1} < 2^{-m}.$$

and it can be estimated by the degree of the generator polynomial.

For proofs of these theorems and further discussion, the reader is encouraged to consult [1] and [13].

<sup>&</sup>lt;sup>2</sup>Period refers to the smallest degree polynomial that G(x) evenly divides.

#### **Error Correction**