#### **Western University**

#### Scholarship@Western

**Digitized Theses**

**Digitized Special Collections**

2008

# Development of a Hardware-in-the-loop Simulation Platform for Safety Critical Control System Evaluation

Drew James Rankin Western University

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### **Recommended Citation**

Rankin, Drew James, "Development of a Hardware-in-the-loop Simulation Platform for Safety Critical Control System Evaluation" (2008). *Digitized Theses*. 4114. https://ir.lib.uwo.ca/digitizedtheses/4114

This Thesis is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# Development of a Hardware-in-the-loop Simulation Platform for Safety Critical Control System Evaluation

(Spine title: Hardware-in-the-loop Simulation of Safety Control Systems)

(Thesis format: Monograph)

by

Drew James Rankin

Graduate Program

in

Engineering Science

Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering Science

The School of Graduate and Postdoctoral Studies

The University of Western Ontario

London, Ontario, Canada

© Drew J. Rankin 2008

# Abstract

During the lifetime of a nuclear power plant (NPP) safety electronic control system components become obsolete [7]. It is difficult to find replacement components qualified for nuclear applications [50]. Due to strict regulations, replacement components undergo extensive verification and operational analysis [70]. Therefore, the need for a platform to evaluate replacement safety control systems in a non-intrusive manner is evident. Verifying the operation or functionality of potential replacement electronic control systems is often performed through simulation [71].

To enable simulation, a physical interface between potential control systems and computer based simulators is developed. System connectivity is establish using Ethernet and standard industrial electrical signals. The interface includes a National Instruments (NI) virtual instrument (VI) and data acquisition system (DAQ) hardware. The interface supports simulator controlled transmission and receipt of variables. The transmission of simulated process variables to and from an external control system is enabled. This is known as hardware-in-the-loop (HIL) simulation [49]. Next, HIL interface performance is verified and the following are identified; a measure of availability; the effect of varied configurations; and limitations.

Further, an HIL simulation platform is created by connecting a NPP simulator and a programmable logic controller (PLC) to the interface, Canadian Deuterium Uranium (CANDU) reactor training simulator and Invensys Tricon version nine (v9) safety PLC respectively. The PLC is programmed to operate as shutdown system no. 1 (SDS1) of a CANDU reactor. Platform availability is verified and the response of the PLC as SDS1 and is monitored during reactor shutdown. Proper execution of the steam generator level low (SGLL) logic on the PLC and variable transmission are observed. Thus, a platform and procedure for the evaluation of replacements for obsolete electronic control system components is demonstrated.

**Keywords:** hardware-in-the-loop, simulation, National Instruments, interface, programmable logic controller, Tricon v9, shutdown system, SDS1, steam generator level low, obsolete, CANDU, nuclear power plant

# **Table of Contents**

| C  | ertifi | cate of Examination                                 | .1 |

|----|--------|-----------------------------------------------------|----|

| A  | bstra  | ct                                                  | i  |

| D  | edica  | tion                                                | V  |

| A  | ckno   | wledgements                                         | V  |

| Li | ist of | tables                                              | X  |

| Li | ist of | figures                                             | X  |

| A  | bbre   | viations and Nomenclaturexii                        | į  |

| 1  | Intr   | oduction                                            | 1  |

| _  | 1.1    |                                                     | 1  |

|    | 1.2    | Motivations                                         | 5  |

|    |        |                                                     | 6  |

|    |        | <b>V</b>                                            | 6  |

|    |        | 4                                                   | 7  |

|    | 1.3    |                                                     |    |

|    | 1.0    | 1.3.1 Hardware-in-the-loop interface development    |    |

|    |        | * · · · · · · · · · · · · · · · · · · ·             | 9  |

|    | 1.4    | Objectives                                          |    |

|    | 1.5    | Organization                                        |    |

|    | 2.0    | 0.586                                               |    |

| 2  | Nuc    | clear Power Plant Control Systems and Simulation 13 | 3  |

|    | 2.1    | NPP Fundamentals                                    | 3  |

|    | 2.2    | CANDU Fundamentals                                  | 6  |

|    | 2.3    | Safety Systems                                      | 0  |

|    |        | 2.3.1 Safety system concepts                        | 1  |

|    |        | 2.3.2 Shutdown system no. 1                         | 3  |

# Table of Contents

| 3           | Har   | dware- | -in-the-loop Interface Development                               | 9          |

|-------------|-------|--------|------------------------------------------------------------------|------------|

|             | 3.1   | Hardw  | vare-in-the-loop Interface Development Procedure                 | 29         |

|             | 3.2   | Hardw  | vare-in-the-loop Interface Development                           | 33         |

|             |       | 3.2.1  | Mock simulator                                                   | 34         |

|             |       | 3.2.2  |                                                                  | 35         |

|             |       | 3.2.3  | Hardware-in-the-loop interface device                            | 12         |

|             |       | 3.2.4  | Hardware-in-the-loop analog loop simulation platform             | 14         |

| 4           | Har   | dware- | -in-the-loop Interface Analysis                                  | <b>.</b> 5 |

|             | 4.1   | Hardw  | vare-in-the-loop Interface Timing Analysis                       | 15         |

|             |       | 4.1.1  | Method                                                           | 15         |

|             |       | 4.1.2  | Assumptions                                                      | 18         |

|             |       | 4.1.3  | Analysis of results                                              | 19         |

|             | 4.2   | Hardw  | vare-in-the-loop Interface Scalability Analysis 6                | 31         |

|             |       | 4.2.1  | Method                                                           | 31         |

|             |       | 4.2.2  | Assumptions                                                      | 35         |

|             |       | 4.2.3  | Analysis of results                                              | 35         |

|             |       | 4.2.4  | Transmission delay study                                         | 76         |

|             |       | 4.2.5  | Maximum system under test input/output study                     | 79         |

| 5           | Har   | dware- | -in-the-loop Shutdown System Simulation 8                        | 80         |

|             | 5.1   | NPP F  | Hardware-in-the-loop Simulation Platform Development Procedure 8 | 30         |

|             | 5.2   | NPP I  | Hardware-in-the-loop Simulation Platform Development 8           | 34         |

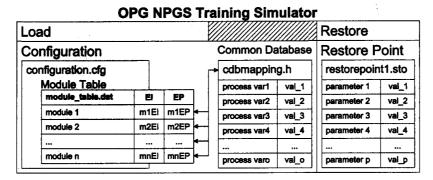

|             |       | 5.2.1  | Darlington NPP training simulator                                | 35         |

|             |       | 5.2.2  |                                                                  | 37         |

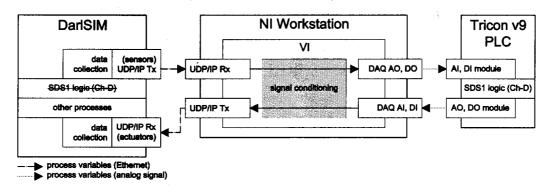

|             |       | 5.2.3  | Hardware-in-the-loop interface                                   | 39         |

|             |       | 5.2.4  | System under test: Tricon v9 PLC                                 | 90         |

|             |       | 5.2.5  | System under test: trip detection logic                          | 90         |

|             | 5.3   | Hardw  | vare-in-the-loop Simulation Platform Timing Verification 9       | 93         |

|             |       | 5.3.1  | Method                                                           | 93         |

|             |       | 5.3.2  | Assumptions                                                      | 95         |

|             |       | 5.3.3  | Analysis of results                                              | 95         |

|             | 5.4   | NPP S  | Shutdown System Hardware-in-the-loop Simulation 10               | )()        |

|             |       | 5.4.1  | Method                                                           | )()        |

|             |       | 5.4.2  | Assumptions                                                      | )3         |

|             |       | 5.4.3  | Bench-mark SDS1 SGLL simulation                                  | )3         |

|             |       | 5.4.4  | Hardware-in-the-loop SDS1 SGLL simulation                        | )7         |

| 6           | Con   | clusio | ns                                                               | 4          |

|             | 6.1   |        | ary of contributions                                             |            |

|             | 6.2   |        | stions for future work                                           |            |

| $R\epsilon$ | efere | nces . |                                                                  | 9          |

# Table of Contents

| A            | Darlington Nuclear Power Plant Design Specifications                              | 126 |

|--------------|-----------------------------------------------------------------------------------|-----|

| В            | Coverage of Process Failures by Shutdown Systems no. 1 and ${\bf 2}$ .            | 129 |

| $\mathbf{C}$ | C Program Modules for Simulation and Development Analysis                         | 134 |

| D            | Invensys Tricon v9 Safety Programmable Logic Controller and Shutdown System no. 1 |     |

| $\mathbf{E}$ | Invensys Tricon v9 PLC Function Block Diagrams                                    | 181 |

| $\mathbf{F}$ | National Intruments LabVIEW HIL Interface Virtual Instrument                      | 183 |

| Cı           | urriculum Vitae                                                                   | 187 |

# List of Tables

| 2.1               | Methods used to ensure NPP safety requirements [13]                                                                                           | 17                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.1<br>3.2<br>3.3 | Generic (SUT input) UDP/IP packet structure                                                                                                   | 39<br>39<br>40    |

| 3.4               | Controlled variable ranges by decimal position for 16 mA analog signals at a 12bit resolution.                                                | 42                |

| 4.1<br>4.2        | Percentage of successful transfers                                                                                                            | 55<br>79          |

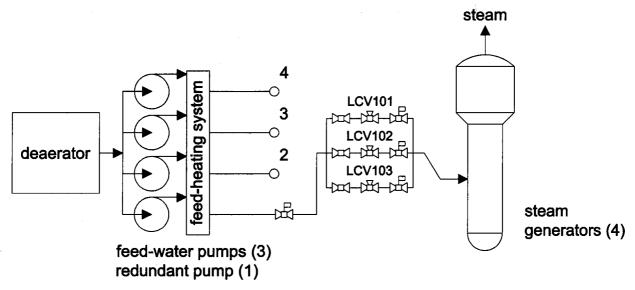

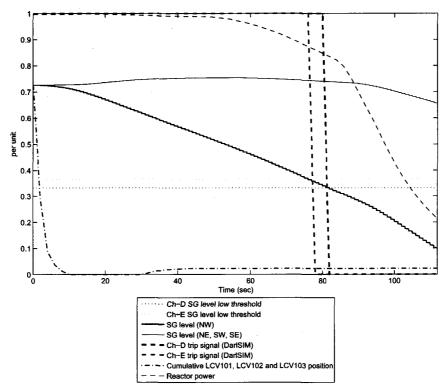

| 5.1<br>5.2        | Channelized steam generator level biases and low level trip thresholds. Controlled variable values                                            | 102<br>106        |

|                   | Darlington NPP general and reactor core design specifications Darlington NPP reactivity control and shutdown system specifications, continued | 127<br>128        |

| D.2               | General characteristic of Tricon v9 controller                                                                                                | 171<br>177<br>178 |

# List of Figures

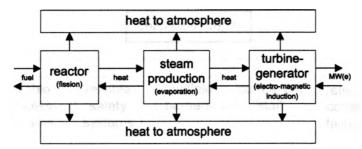

| 2.1  | Basic nuclear power plant energy cycle                                                                                                                    | 14 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

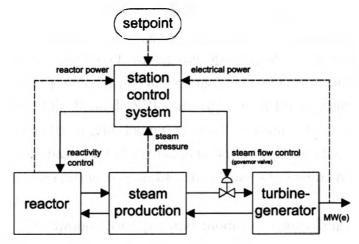

| 2.2  | Simplified nuclear power plant control system                                                                                                             | 14 |

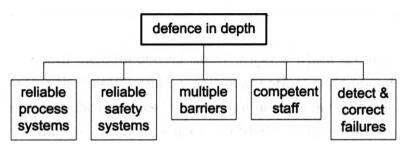

| 2.3  | Model of 'Defence in Depth' concept                                                                                                                       | 15 |

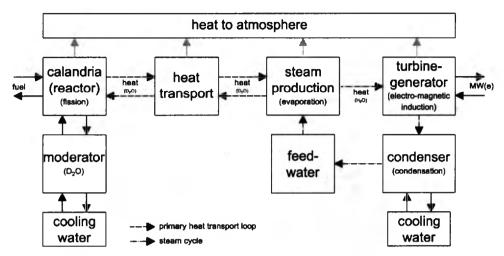

| 2.4  | Energy cycle and main CANDU NPP systems                                                                                                                   | 18 |

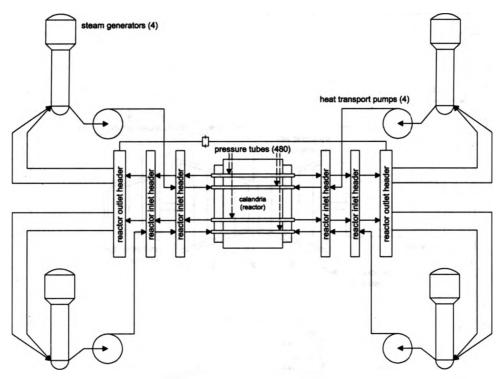

| 2.5  | Simplified CANDU NPP primary heat transport system (PHTS) [26].                                                                                           | 19 |

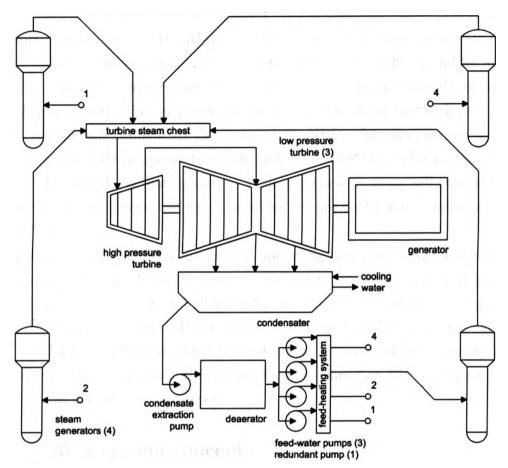

| 2.6  | Simplified CANDU NPP steam cycle [30]                                                                                                                     | 20 |

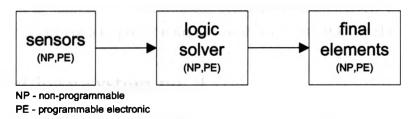

| 2.7  | Safety instrumented system (SIS) open action path                                                                                                         | 22 |

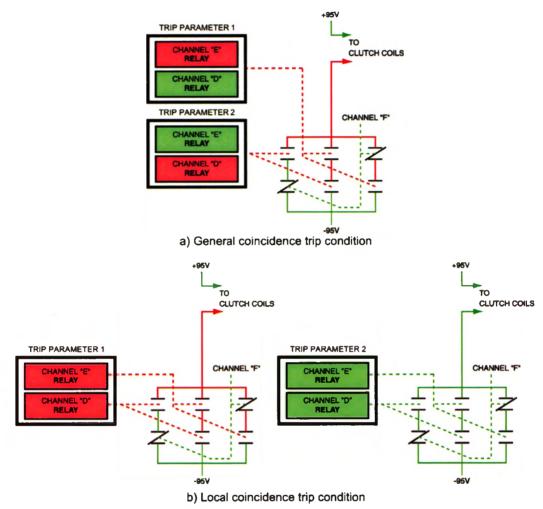

| 2.8  | a) General (SDS1) and b) local (SDS2) coincident two-out-of-three                                                                                         |    |

|      | (2003) trip mechanisms                                                                                                                                    | 25 |

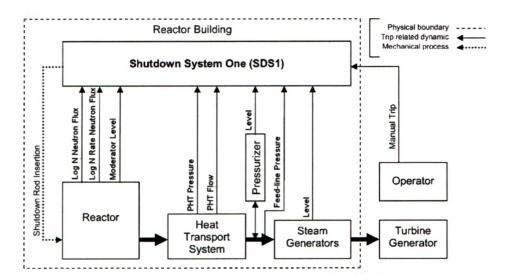

| 2.9  | CANDU SDS1 trip parameters and originating systems                                                                                                        | 26 |

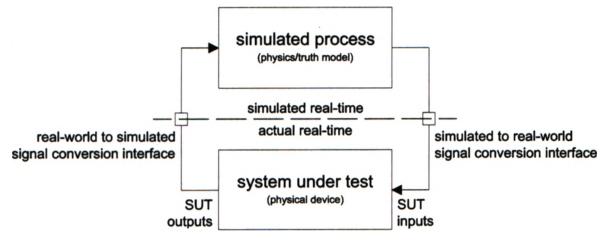

| 3.1  | HIL simulation platform concept                                                                                                                           | 30 |

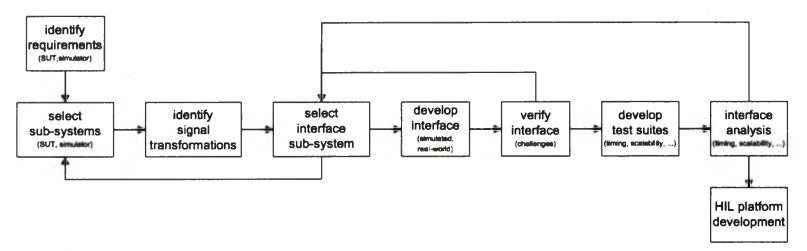

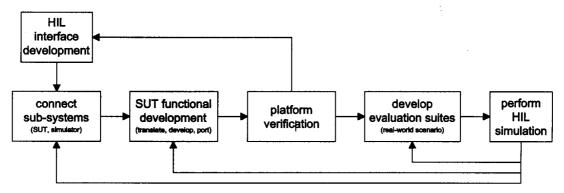

| 3.2  | interface developmental procedure                                                                                                                         | 30 |

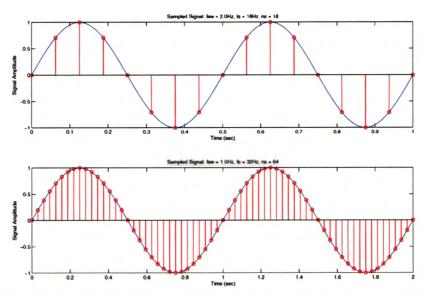

| 3.3  | Sample sine wave generation with parameters: top - waveform fre-                                                                                          |    |

| 5-   | quency = 2.0Hz, sampling frequency = 16Hz, number of samples = 17; bottom - waveform frequency = 1.0Hz, sampling frequency = 32Hz, number of samples = 65 | 36 |

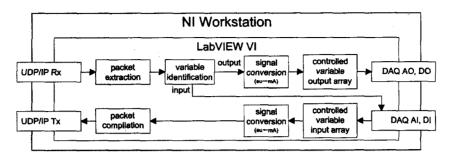

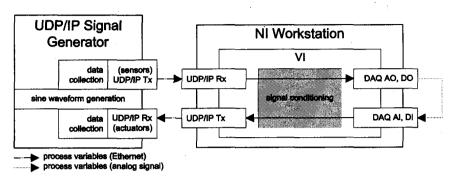

| 3.4  | LabVIEW virtual instrument process flow                                                                                                                   | 43 |

| 3.5  | HIL simulation evaluation platform                                                                                                                        | 44 |

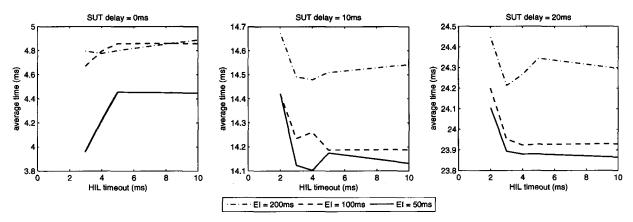

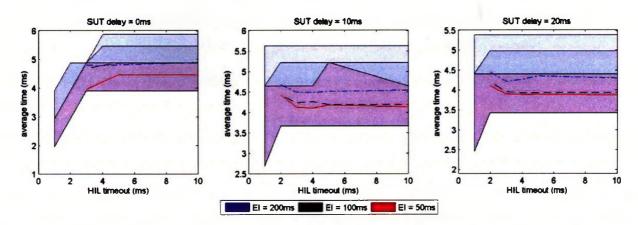

| 4.1  | Average signal transmission time vs. HIL timeout per SUT delay                                                                                            | 50 |

| 4.2  | Average time with 95th percentile vs. HIL timeout per SUT delay                                                                                           | 52 |

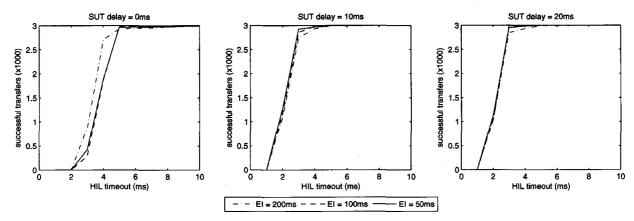

| 4.3  | Successful transfers vs. HIL timeout per SUT delay                                                                                                        | 54 |

| 4.4  | Cumulative successful transfers vs. poll time per SUT delay                                                                                               | 56 |

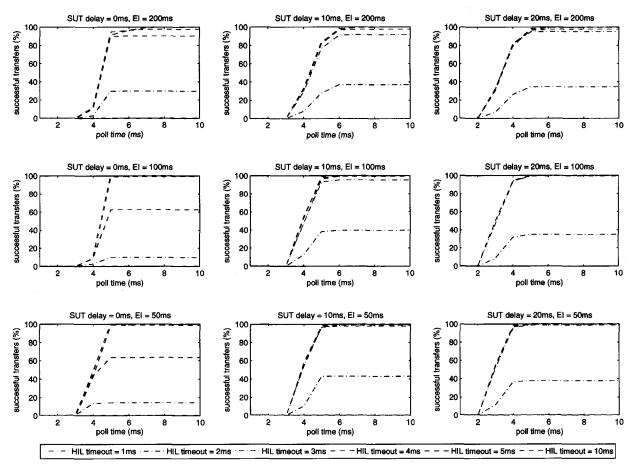

| 4.5  | interface availability vs. HIL timeout per execution interval                                                                                             | 58 |

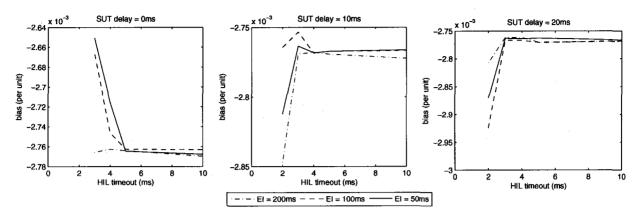

| 4.6  | Average signal bias vs. HIL timeout per SUT delay                                                                                                         | 60 |

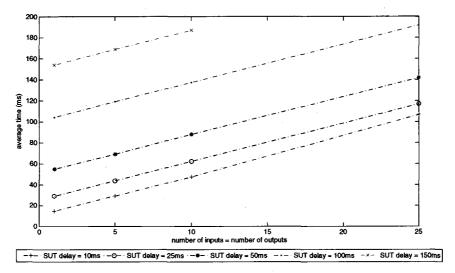

| 4.7  | Average total elapsed time vs. I/O configuration                                                                                                          | 67 |

| 4.8  | Average total elapsed time with 95th percentile vs. I/O configuration.                                                                                    | 69 |

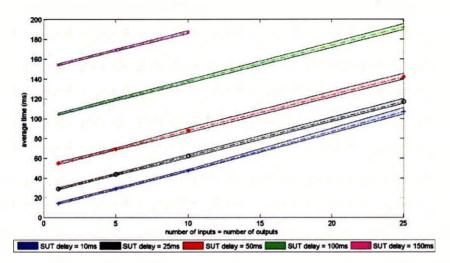

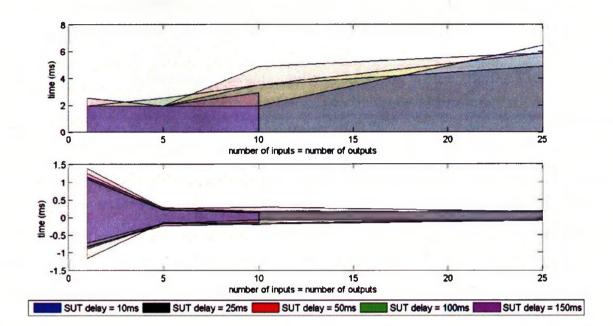

| 4.9  | Average total elapsed time with 95th percentile vs. I/O configuration.                                                                                    | 70 |

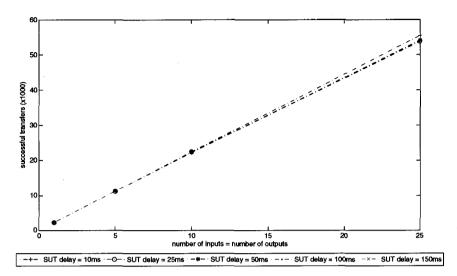

| 4.10 | Successful transfers vs. I/O configuration                                                                                                                | 72 |

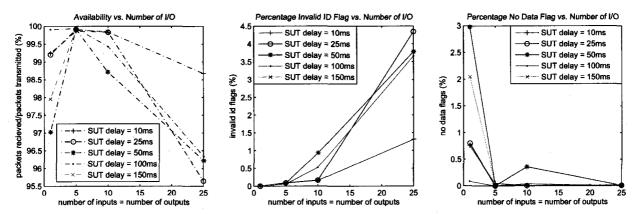

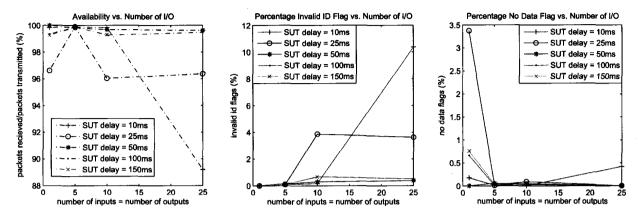

| 4.11 | interface availability with errors vs. I/O configuration (Dataset 1)                                                                                      | 73 |

| 4.12 | interface availability with errors vs. I/O configuration (Dataset 2)                                                                                      | 74 |

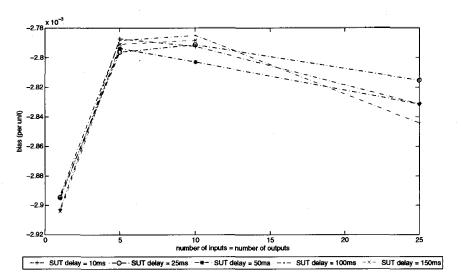

| 4.13 | Average signal bias vs. I/O configuration                                                                                                                 | 76 |

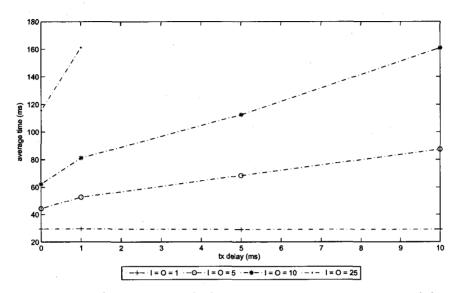

| 4.14 | Average total elapsed time vs.transmission delay                                                                                                          | 77 |

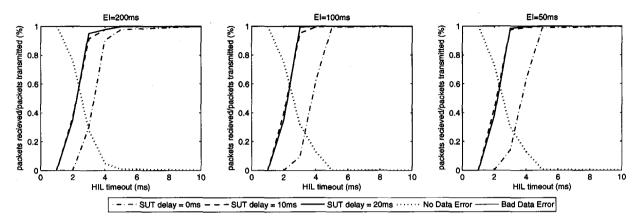

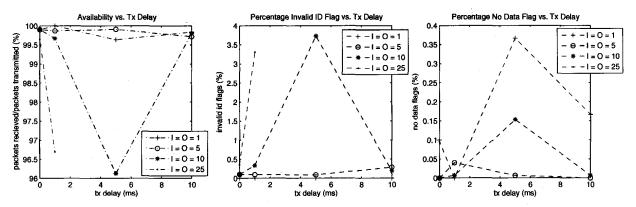

| 4.15 | interface availability and error flags vs. tranmission delay                                                                                              | 78 |

# List of Figures

| 5.1         | Application specific HIL simulation procedure                          | 81  |

|-------------|------------------------------------------------------------------------|-----|

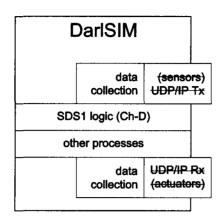

| 5.2         | DarlSIM component interconnections                                     | 85  |

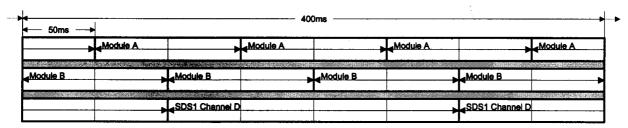

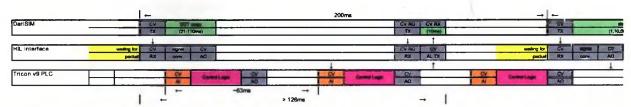

| 5.3         | Module execution interval and execution phase                          | 86  |

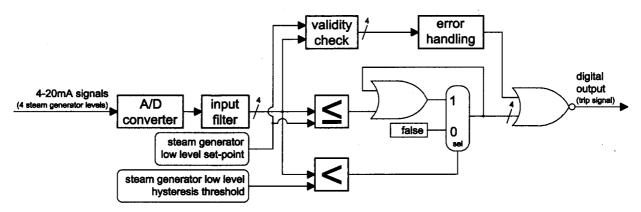

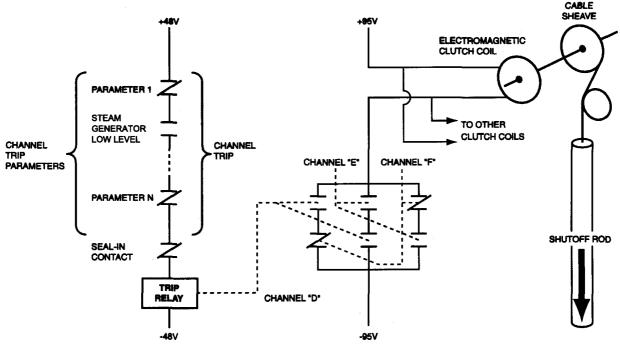

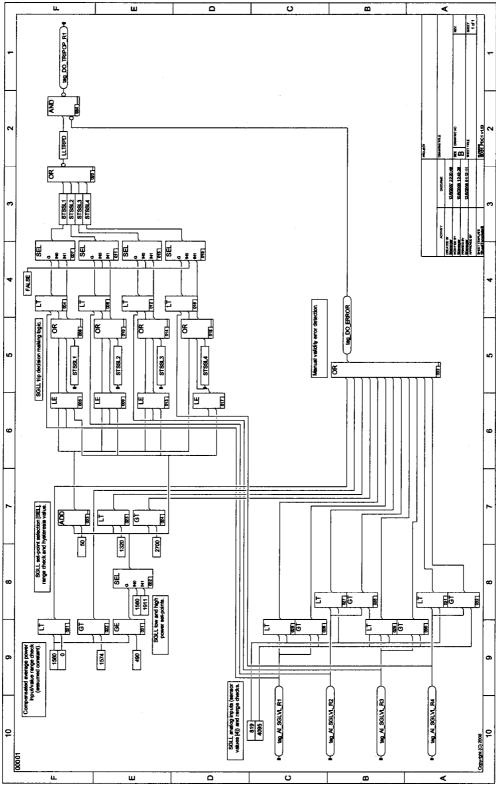

| 5.4         | SGLL trip logic                                                        | 92  |

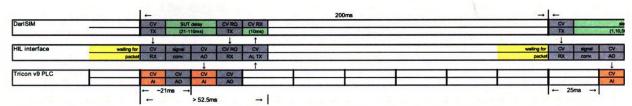

| 5.5         | Expected sequence of events during HIL simulation platform verifica-   |     |

|             | tion for a 21 ms SUT execution interval                                | 94  |

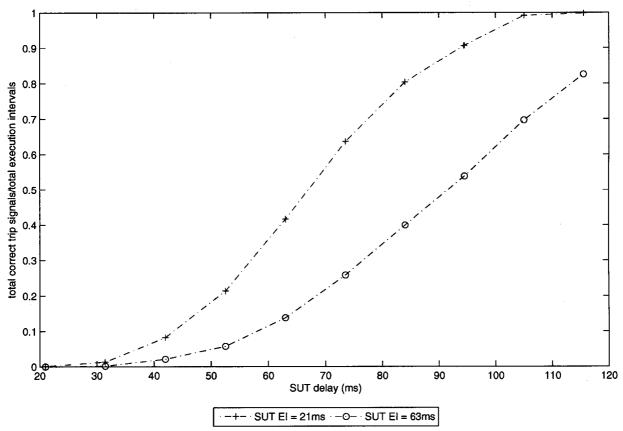

| 5.6         | NPP HIL simulation platform availability vs. SUT delay with Tricon     |     |

|             | v9 PLC installed                                                       | 96  |

| 5.7         | Sequence of events during HIL simulation platform verification for a   |     |

|             | 21 ms SUT execution interval                                           | 98  |

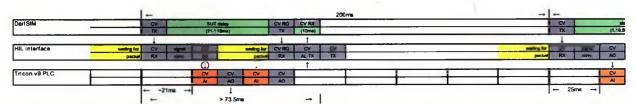

| 5.8         | Sequence of events during HIL simulation platform verification for a   |     |

|             | 63 ms SUT execution interval                                           | 99  |

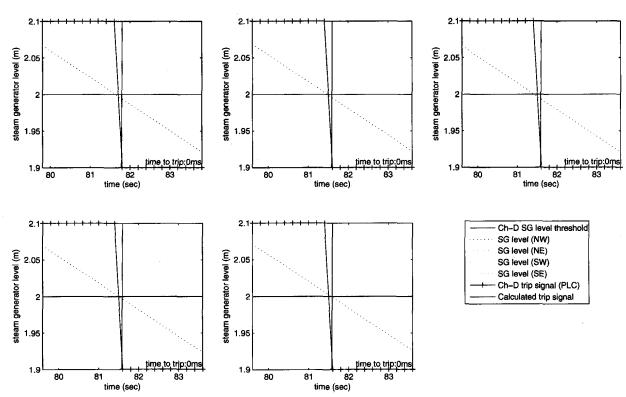

| 5.9         | Steam generator feed-water system                                      | 102 |

| 5.10        | Simulation platform for bench-mark SDS1 evaluation                     | 104 |

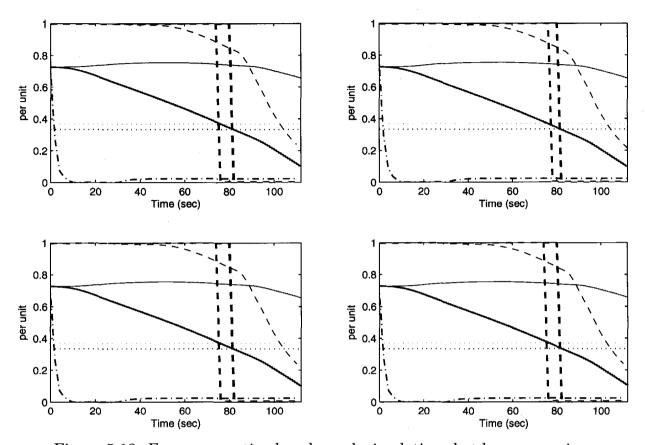

| 5.11        | Bench-mark SGLL trip detection, simulation of Darlington NPP re-       |     |

|             | sponse to loss of secondary side heat removal design base event        | 105 |

| 5.12        | General co-incidence trip logic satisfied by channel D and E SGLL trip |     |

|             | parameters                                                             | 107 |

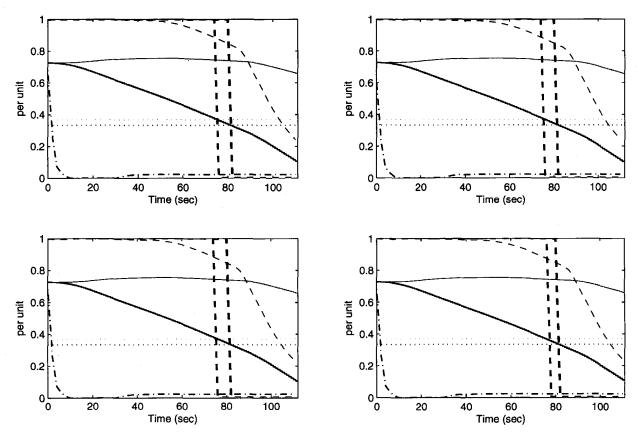

|             | Four consecutive bench-mark simulation shutdown scenarios              | 108 |

|             | HIL simulation platform for SDS1 evaluation using the Tricon v9 PLC.   | 109 |

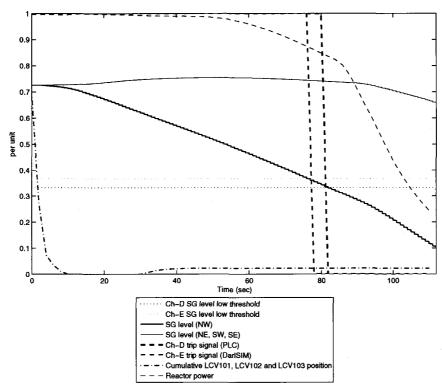

| 5.15        | Hardware-in-the-loop SGLL trip detection, Tricon v9 PLC induced        |     |

| <b>-</b> 10 | response to loss of secondary side heat removal design base event      | 111 |

|             | Four consecutive hardware-in-the-loop simulation shutdown scenarios.   | 112 |

| 5.17        | Hardware-in-the-loop SGLL trip detection, detailed analysis of Tricon  |     |

|             | v9 PLC induced response to loss of secondary side heat removal design  | 110 |

|             | base event                                                             | 113 |

| B.1         | Coverage of process failures by shutdown system no. 1 and indepen-     |     |

|             | dently by shutdown system no. 2                                        | 130 |

| B.2         | Coverage of process failures by shutdown system no. 1 and indepen-     |     |

|             | dently by shutdown system no. 2, continued                             | 131 |

| B.3         | Coverage of process failures by shutdown system no. 1 and indepen-     |     |

|             | dently by shutdown system no. 2, continued                             | 132 |

| B.4         | Coverage of process failures by shutdown system no. 1 and indepen-     |     |

|             | dently by shutdown system no. 2, continued                             | 133 |

| D 1         | This are and triple moduler redundant (TMP) controller                 | 170 |

| D.1         | Tricon v9 triple modular redundant (TMR) controller                    | 170 |

| E.1         | Invensys Tricon v9 safety PLC steam generator level low function block |     |

|             | diagram logic (Tristation 1131 Developer's Workbench)                  | 182 |

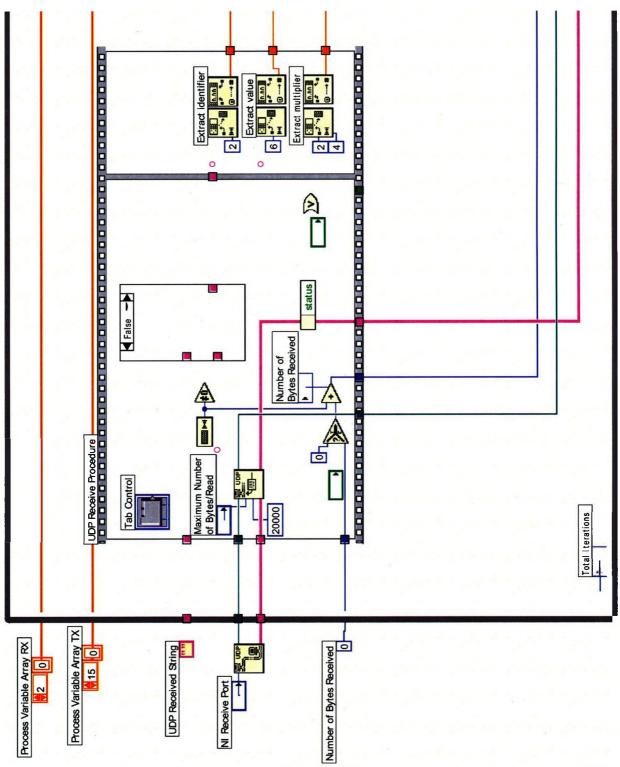

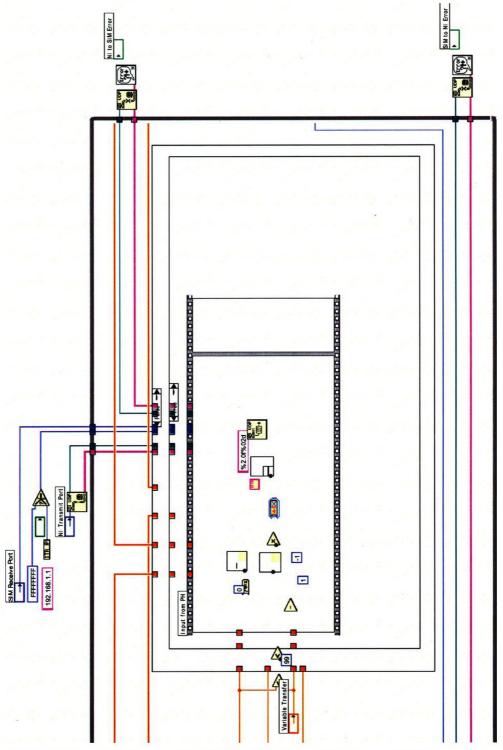

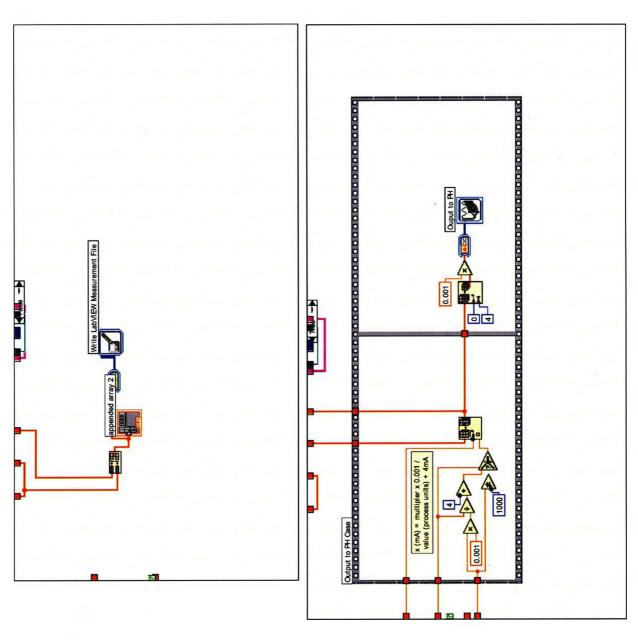

| F.1         | National Intruments LabVIEW HIL interface virtual instrument (G        |     |

|             | programming language)                                                  | 184 |

# List of Figures

| F.2 | National Intruments LabVIEW HIL interface virtual instrument (G |     |

|-----|-----------------------------------------------------------------|-----|

|     | programming language), continued                                | 185 |

| F.3 | National Intruments LabVIEW HIL interface virtual instrument (G |     |

|     | programming language), continued                                | 186 |

#### Abbreviations and Nomenclature

#### **Abbreviations**

2003 Two-out-of-three voting

AECL Atomic Energy of Canada Limited

BWR Boiling Water Reactor

CANDU CANadian Deuterium Uranium

Ch-X Channel (identified by X)

CNSC Canadian Nuclear Safety Commission

CPU Central Processing Unit

CSV Comma Separated Values

D<sub>2</sub>O Deuterium Oxide, Heavy Water

DAQ Data Acquisition System

DarlSIM Darlington Nuclear Power Plant Simulator

ECCS Emergency Core Cooling System

EI Execution Interval

eu engineering units (kg/s, m, °Celsius)

FBD Function Block Diagram

H<sub>2</sub>O Hydrogen Oxide, Water

HIL Hardware-in-the-Loop

I&C Instrumentation and Control

IAEA International Atomic Energy Agency

LCV Level Control Valve

LOCA Lost Of Coolant Accident

mA milli-ampere ms milli-second

#### Abbreviations and Nomenclature

MW megawatt

MW(e) Megawatt Electric Power

NI National Instruments

NPP Nuclear Power Plant

NW North-West

**OPG** Ontario Power Generation

OS Operation System

PCI Peripheral Component Interconnect

PHTS Primary Heat Transport System

PHWR Pressurized Heavy Water Reactor

PLC Programmable Logic Controller

PWR Pressurized Water Reactor

SCFW Spurious Closure of Feed-water valve

SDS Shutdown System

SDS1 Shutdown System no. 1

SDS2 Shutdown System no. 2

SG Steam Generator

SGLL Steam Generator Level Low

SIS Safety Instrumented System

SUT System Under Test

TCP/IP Transmission Control /Internet Protocol

TNT Trinitrotoluene

UDP/IP User Datagram Protocol/Internet Protocol

USNRC United States Nuclear Regulatory Commission

v9 version nine

VDC Voltage (Direct Current)

VI Virtual Instrument

#### Nomenclature

$av_{HIL}$  interface availability

$cv_{eu}$  controlled variable represented in engineering units  $cv_{eu_{tx}}$  transmitted variable represented in engineering units  $cv_{eu_{rx}}$  received variable represented in engineering units

$cv_i$  instantaneous controlled variable value

$cv_{max}$  maximum expected controlled variable value  $cv_{min}$  minimum expected controlled variable value  $cv_{range}$  range of expected controlled variable values

$f_{sw}$  frequency of the sine wave to generate

$f_s$  frequency of the samples

$n_{bit}$  resolution in bits for analog to digital conversion

$n_{bit}$  total number of identified erroneous transfers

$n_{I/O}$  number of configured inputs and outputs  $n_s$  number of sinusoidal samples to generate

$n_{total}$  total number of attempted transfers through the interface

$res_{analog}$  analog signal resolution

$res_{cv}$  expected controlled variable resolution

$res_{UDP/IP}$  resolution of the UDP/IP packet structure

$t_{EI}$  period of execution for modules on the simulator

$t_{HIL}$  maximum time expected for the majority of SUT outputs

to return after being requested to do so

$t_{s_{HIL}}$  interface signal settling time

$t_{s_{SIIT}}$  system under test signal settling time

$t_{SUT_{EI}}$  system under test control logic execution period  $t_{SUT}$  system under test control logic execution wait time

$t_{te}$  total elapsed time for all process variables to be transmitted

through the interface

$t_{te_{max}}$  maximum total elapsed time for process variable transmis-

sion over entire simulation

# Chapter 1 Introduction

The success of integrating nuclear power plants (NPPs) into a society with increasing population density and environmental concern relies heavily on safety system design [14]. Confidence in safety systems to mitigate environmental, economical and public health consequences must be demonstrated [14]. Many NPP safety analysis codes, simulation tools and methods of evaluation exist [6]. However, significant challenges remain in the verification process of electronic control systems for safety critical nuclear control applications [6].

A flexible simulation platform for the operational verification of safety electronic control systems is developed. In doing so, existing tools are interfaced with modern simulation practises and control system technologies. This platform is not intended to replace existing tools. However, it is intended to strengthen the set of currently available tools [6]. The following sections underscore the background, motivations, problems and objectives of the research undertaken in this thesis.

#### 1.1 Background

NPPs are required to abide by increasingly strict safety standards and regulations [70]. Safety critical control and shutdown systems within NPPs are essential in satisfying these regulations, assuring public health and safety, minimal environmental impact and stable plant economics [3]. Therefore, safety related electronic control systems must be evaluated to verify, validate, qualify or certify proper operation and design.

Evaluations are performed by regulatory bodies, manufacturers and systems engineers [6]. Depending on the intended application for the electronic control system, specific qualifications and certifications are required [11]. These requirements are specified by regional, national and international regulatory bodies whom develop NPP instrumentation and control (I&C) standards [8]. However, as mentioned, standards and regulations are becoming increasingly strict, and are also sometimes vague [31].

Therefore, the submission of an electronic control system for evaluation may require the commitment of extensive resources over a long period of time [43]. For many manufacturers, justifying certification procedures for nuclear applications is difficult due to the relatively small nuclear I&C market [50].

Though a small market for certified electronic control systems for nuclear applications currently exists, it is widely believed that the nuclear energy industry is entering a renaissance [21] [20]. The apparent renaissance is the result of an increase in energy demand, public awareness and an acceptance that nuclear power generation is necessary for base load electrical supply [21] [19]. However, as mentioned, manufacturers cannot justify performing extensive and costly industry certifications. The result is a small number of certified electronic control systems,. This places limitations on NPP utilities and systems engineers when developing new or replacement I&C system components. Engineers either; a) choose from few certified electronic control systems; b) design and qualify in-house electronic control systems; or c) attempt to integrate and qualify commercial electronic control systems which lack certification [4].

It is not clear whether manufacturers will respond to the expected increase in commercial nuclear activity and tightening regulations. However, the requirement for a range of electronic control systems covering a variety of applications is evident. Increasingly, the task of verifying, validating and qualifying electronic control systems to satisfy the requirements outlined by regulatory bodies is being placed on NPP systems engineers [18]. To prove system functionality electronic control systems are often evaluated through various simulation and emulation techniques [71]. Thus, the application and development of the platform within this thesis is performed to streamline the evaluation of electronic control systems applied in specific NPP applications.

The International Atomic Energy Agency (IAEA) estimates that total world-wide electrical generating capacity will grow in the range of 37 to 84 per cent between 2006 and 2030. Over the same period, nuclear generating capacity is expected to grow in the range of 21 to 87 per cent [16]. These projections are difficult to foresee given the average age of operational NPPs is over 24 years. In fact, today nearly 85 per cent of operational NPPs are within 25 years of their life expectancies [21] [20] [19]. Therefore, simply to sustain current nuclear power generating capacity there is a great need for major refurbishment and life extension initiatives in parallel with new nuclear build.

Public concern over nuclear proliferation and security causes significant roadblocks when addressing safety system development for nuclear applications [88]. Historically, nuclear power generation has a great safety record [88]. This record has been maintained through regulations, standards and thorough engineering practices which have ultimately resulted in an industry which is poised to respond to the ever growing demand for energy.

The fundamental basis for power generation by nuclear fission both enables and disables its application. Nuclear fission reactions release an immense amount of energy, 20 million times the amount of energy released by Trinitrotoluene (TNT) [2]. However, the fuel used to generate heat in a nuclear fission reaction is naturally radioactive. Further, fuel which has been depleted of its useful radioactive material, or spent fuel, has a higher radioactivity than the original natural or enriched uranium [2]. Therefore, spent nuclear fuel requires extensive monitoring, management, and storage facilities [88].

Currently, 18 nuclear reactors generate 14.6 per cent of Canada's total electrical supply [22]. However, a reactor has not commissioned in Canada for over 15 years. The most recently constructed reactor is Darlington Unit 4, an Atomic Energy of Canada Limited (AECL) design, which went into service in June 1993 [23]. Of the 18 operating Canadian reactors, two units, Pickering 1 and 4, are recently refurbished having been brought back into service within the last five years [37]. Also, in March 2008, New Brunswick Power began an 18-month refurbishment of the Point Lepreau NPP [78].

The estimated life expectancy for Canadian Deuterium Uranium (CANDU) NPPs operating in Canada is 40 years [23]. By 2030, 16 of the 18 operating Canadian reactors will have surpassed their life expectancies [23]. Therefore, it is immediately necessary to plan engineering methods for plant life extension, refurbishment, retrofit and new build projects. Failure to act will result in a reduced nuclear capacity of only 1870 megawatt (MW), Darlington 3 and 4 combined capacity, and a shortage in total Canadian electrical supply [23].

The accelerated development and expansion of NPP sites will require definite assurances that public health, public safety and the environment are not placed at risk [21] [20]. These assurances rely on engineering practices during NPP safety system design. Within the nuclear industry, for example, design basis events are well defined postulated events identified to establish the acceptable performance requirements for

structures, systems, and components [44]. To mitigate the consequences of design basis events, safety critical control and shutdown systems are installed.

In a NPP many systems are classified as safety critical. There are different standards and levels of classification. However, the safety critical and shutdown systems which are most critical to safety in all NPPs are those which prevent the release of radioactive material from a contained volume [29]. In order to maintain containment; pressures, temperatures, flow rates, and other plant processes as well as neutronic stability are monitored and controlled [29]. By controlling the physical plant, limitations of the mechanical components which contain radioactive materials are never reached and accidents are mitigated [29]. Further, conservative safety margins are maintained to assure safe operation [10]. Safety margins are the margins allocated between the limitations of physical operation in any given process and the specified safe limit of the components within the process during anticipated operational occurrences [61]. The reduced performance of ageing and obsolete components nullifies engineering efforts and can result in a reduction of the safety margin [87].

Aside from obsolete systems, many electronic control systems in NPPs are composed of ageing analog circuitry [10]. Concerns often arise when analog controllers are to be replaced by digital controller platforms [67]. The reliability of software based systems, common cause faults and fault tolerance of digital systems come into question [60]. Simple replacement of these systems can lead to minor variances in plant performance, or instability in plant operation [60]. However, through proper simulation methods it is believed that the performance of the digital systems can be measured and either observed variances can be minimized or process performance or safety margins can be improved [56].

The process of engineering replacement systems includes extensive testing and verification [53]. This is especially true for safety critical systems [53]. However, due to hazardous environments, it is not always possible to perform testing on replacements for obsolete systems as they exist in the plant [9]. In these cases, the use of simulation techniques not only assists with verifying proper electronic control system operation prior to installation within the NPP, but is the only means of testing the physical system prior to plant start-up [9].

Traditionally simulations are performed entirely by software [42]. In the Canadian nuclear industry there are many extensively developed nuclear power generation software simulation platforms [15]. These simulators are capable of performing com-

plex and extensive simulations [15]. With the increasing problems of obsolescence and replacement, expansion of software simulators to include connection to external hardware is becoming more common [89]. Process variables from within the software simulator are converted to compatible electrical input signals for input to the electronic control system under test (SUT). Also, SUT output process variables are converted from electrical signals to software variables and received by the software simulator. Connection of the two systems, simulator and SUT forms a loop. Therefore, this method of simulation is known as hardware-in-the-loop (HIL) simulation [79].

This thesis covers two major topics; i) the role of HIL simulation in the development and testing of electronic control systems; and ii) the simulation of a specific CANDU NPP shutdown system application. Throughout, focus is placed on the Canadian nuclear power generation industry where these topics have extensive application as well as motivation for research and development. Both the HIL interface and the simulation platform developed within this thesis are designed to be flexible and modular, enabling installation between various software simulators and electronic SUTs.

#### 1.2 Motivations

There are three distinct motivations behind the research performed in this thesis. All motivations are the result of strict industry regulations and limited availability of replacement electronic control systems discussed previously. The primary motive is the need for both a process and a platform for the qualification of shutdown system hardware and software based on relevant standards through HIL simulation. This is a long term motivation which extends beyond the scope of this thesis. The secondary motive is to better enable the replacement of obsolete digital and analog shutdown system hardware and software. The final motivation is to provide support for the integration of enhanced functionalities and advanced control techniques digital safety control systems.

## 1.2.1 Qualification

During replacement, a potential electronic control system must demonstrate equivalent functional performance to the system being replaced. Further, plant safety margins must be maintained and safety standards satisfied [87]. Within the nuclear industry, interest in qualifying electronic control systems has grown due to the lack of certifications, discussed earlier. Therefore, a method to qualify electronic control systems through evaluation is necessary.

Application specific qualification routines provide engineers with the ability to prove that potential replacement systems meet the criteria outlined in standards and regulations and do not negatively impact plant performance when installed in a specified application [50]. It is expected that related standards can be identified, reviewed and that system requirements can be quantified for a specific application. The quantified requirements are evaluated against the potential electronic control system and the system is either accepted for installation or removed from contention.

Qualification of a electronic control systems requires functional evaluation. However, installation into a NPP is not an option due to the continuous and expensive nature of NPP operations [68]. Therefore, performance evaluation of a potential electronic control system within an HIL simulation platform is performed to provide full functional evaluation and verification. Along with quantified standard requirements, an integrated platform for streamlined system qualification could be constructed.

## 1.2.2 Obsolescence and replacement

It is essential to better enable the replacement of obsolete shutdown system components in NPPs [67]. This is true as the rate of obsolescence rises with the age of operating reactors [7]. Also, it is expected that obsolescence will continue despite the predicted nuclear renaissance [33]. In fact, the opposite is true with an increase in anticipated refurbishment, retrofit, and plant life extension projects.

Currently, many projects address obsolete systems within NPPs [7]. However, due to financial, scheduling and regulatory restrictions the replacement of all systems and components is not realistic [7]. Therefore, proper functionality must be established between refurbished and existing systems. Additionally, continued obsolescence issues are inevitable. It is difficult to predict technological trends or support for currently installed systems [65].

Components once commonly available are now either manufactured on a per request basis, or are simply no longer manufactured [50]. Further, many suitable modern electronic control systems are not qualified for nuclear applications [50]. Therefore, reverse engineering techniques have become common practise in maintenance and refurbishment routines [1]. Through reverse engineering, physical, functional and operational replicas are developed to satisfy NPP design standards and regulations [25]. These replicas avoid or reduce the extensive requirements experienced when installing modern replacements [25]. Thus, functionality between old and new is maintained. However, at the system level, complexity proves to be a limiting factor in the process of reverse engineering [25]. Systems are comprised of intricate networks of non-serviceable components and can be very difficult to replicate. If the original manufacturer of the system is no longer willing to manufacture these devices, entire system replacement must be adopted.

For every system replacement, potential replacement systems must be extensively verified to assure confidence in mitigating design basis accidents and maintaining safety margins [79]. Though many methods of evaluation exist, the development of a HIL simulation platform which enables I&C component and electronic control system verification in a standardized, flexible and scalable manner would be a valuable addition to an already strong set of tools [35]. By this method, exhaustive reverse engineering practices would become obsolete. Further, the ability to prove the performance of modern replacement systems would be enabled.

This thesis encompasses the preliminary development of a flexible, scalable and modular interface. The interface is designed with focus on common, standardized simulator and electronic control system connectivity. It is expected that the proposed procedure can be utilized within the nuclear industry to facilitate streamlined integration of existing software simulator platforms and potential replacement systems. The platform developed is not intended to be used for qualifying or validating components. However, the platform enables evaluation of industrial processes and the functional verification of electronic control system logic.

#### 1.2.3 Enhanced capabilities

Obsolescence is the primary reason raised when replacing control systems or components [77]. However, replacement systems often emulate the performance of the

obsolete system [77]. There is a fundamental flaw in this practise. Obsolete systems are no longer manufactured because either modern, more capable products are available, or because problems are identified and the system did not perform as expected for some applications. This being said, when modern technologies are installed to replicate obsolete systems safe operation of the plant may be in jeopardy.

The enhancement of control routines is limited due to strict regulations within the nuclear industry, as previously mentioned [83]. Also, a reduction in nuclear power generating projects over the past decades has resulted in NPP control systems falling behind modern technology and practices [32]. With advancing technology, new algorithms and control techniques are constantly being developed [90]. These techniques have been extensively employed and proven through use in other industries [90]. However, the benefits of these techniques have been ignored by the nuclear industry [90].

Similar to the troubles surrounding the replacement of obsolete systems, the integration of enhanced capabilities requires extensive evaluation. In a NPP, simple control logic is preferred, especially for safety systems [34]. However, modifying safety system control logic through the implementation of built-in electronic control system functions, alarms and other routines can improve performance while maintaining or improving safety margins [34]. Performance metrics include among other parameters, reliability, visibility availability, accuracy and reduced execution time. HIL simulation is an extremely valuable tool for validating correct functionality and identifying the benefits that these enhanced capabilities provide prior to installation. Further, the work required to replace any given component is effectively reduced.

## 1.3 Problem Statement

There are two primary problems which are addressed within this thesis. The first is the development of an interface for connecting a software simulator to an electronic control system. The second is the application of the interface, of the first problem, to a specific safety critical process within a NPP. These two problems are essential in identifying the role of HIL simulation in electronic control system development and testing and applying modern simulation techniques to a specific NPP application.

#### 1.3.1 Hardware-in-the-loop interface development

Everyday, significant financial and human resources are directed at developing truth and physics models [24]. These software simulators are developed using many different computer platforms and operating systems [59]. Recently, increasing problems associated with obsolescence of electronic and electro-mechanical components have produced a common extension for the application of the simulators [77]. Refurbishment, upgrade and replacement of obsolete components is performed through functional verification and evaluation against real-time bench-mark simulated plant models. HIL simulation platforms provides this capability [41]. In fact, HIL simulation platforms are now developed specifically for the purpose of extending existing simulator functionality [41].

Within the Canadian nuclear industry, as discussed previously, there are concerns regarding the obsolescence of components. Consequently, the extension of well developed and tested simulators into HIL simulation platforms has become a priority of the Canadian nuclear research community [58].

A software, Unix based NPP training simulator, supplied by Ontario Power Generation (OPG) is used to provide extensive training and replication of operational scenarios [12]. However, the computer architecture and operating system on which the simulator was developed, though real-time, is very limited and is no longer supported by the manufacturer [38]. This becomes a problem as evaluating potential replacements for obsolete electronic control systems by HIL simulation requires interface between the actual control system hardware and the training simulator. Upon further investigation, development and analysis; a simple, flexible and inexpensive solution is established.

#### 1.3.2 Hardware-in-the-loop shutdown system simulation

Advances in digital safety control system platforms and algorithms are being constantly developed [90]. These advanced systems are installed in an array of applications and industries throughout the world [5]. Although the installation of digital systems into nuclear control systems, including safety critical systems has been limited, there are many recent ambitious initiatives for increased implementation [57]. Therefore, a renewed necessity is apparent to evaluate modern alternatives to analog

and legacy digital systems in safety critical control applications. In fact, three advanced electronic control systems are now certified for nuclear safety application by the United States Nuclear Regulatory Commission (USNRC) [69] [17].

The Canadian nuclear industry led the world in digital control system implementation in the 1980s [39]. However, reduced public support of nuclear power generation did not exclude Canada. Though AECL has taken minor design steps, limited electronic control system development has resulted [40]. Yet, the resurgence of nuclear interest has sparked refurbishment initiatives throughout the country. The NPP at Point Lepreau refurbishment involves specifically the installation of one of the three USNRC approved electronic control systems. Therefore, the refurbishment directly relates to the research within this thesis. The Tricon version nine (v9) programmable logic controller (PLC) is the electronic control system selected for replacement of shutdown system no. 1 (SDS1) at Point Lepreau [52]. It is also the electronic control system of focus within this thesis. Though the Tricon v9 PLC is considered a commercial-off-the-shelf system, it is a complicated system and requires extensive training and programming experience to implement all available enhancements [86] [84] [85]. Further, the logic solving unit of SDS1 does not rely on complex operations, functions and algorithms. The simplicity of the safety critical algorithms is apparent when studying the emulated station code of the training simulator and SDS1 fundamentals [39].

In conjunction with the previous problem, the implementation of SDS1 logic as it exists in the training simulator is ported to the Tricon v9 PLC. Further, combining the development of an advanced electronic control system platform for SDS1 and an HIL interface for a software simulator, results in the Tricon v9 PLC being implemented with the developed HIL interface to form a HIL simulation platform. Functional and operational evaluation of the Tricon V9 PLC and verification of the installed control logic and the capabilities of the simulation platform are performed.

# 1.4 Objectives

The objectives for the research performed within this thesis are outlined, in no particular order, in the following list. The two major objectives listed below stem from the problems and motivations stated in Sections 1.3 and 1.2 respectively. Extended objectives are nested below the two major problems.

- extend the functionality of a NPP training simulator to include hardwarein-the-loop simulation

- identify a method for simulator and electronic control system connectivity

- develop a software module for the acquisition of NPP training simulator process variables

- develop an interface which supports connectivity between the Tricon v9

PLC and the NPP training simulator

- \* propose a procedure for developing an hardware-in-the-loop interface

- \* evaluate the performance of the interface prior to simulation

- \* identify limitations of the interface

- \* develop a method for assuring hardware-in-the-loop simulation results

- \* propose a procedure for connecting and verifying the operation of the interface within a hardware-in-the-loop simulation platform

- demonstrate the functionality of CANDU shutdown system no. 1 control logic on a Tricon v9 PLC through hardware-in-the-loop simulation

- replicate shutdown system no. 1 control logic within the Tricon v9 PLC

- connect the Tricon v9 PLC to the HIL interface

- establish process scenarios for Tricon v9 PLC operational verification

- verify signal transmission through the hardware-in-the-loop simulation platform

- evaluate the performance of the Tricon v9 PLC against bench-mark NPP process simulations

#### 1.5 Organization

The thesis is organized as follows. Chapter 2 includes a review of NPP fundamentals, where the concept of nuclear power generation and related control systems are presented. Chapter 3 proposes a procedure for developing an HIL interface. The proposed procedure is performed and an interface is established. In Chapter 4, analysis of the interface is performed through the execution of two studies. Various timing

requirements and limitations of the interface are observed and discussed. Chapter 5 presents the installation of the interface developed in Chapter 3 within a HIL simulation platform. The simulation platform is designed to enable simulation of a specific CANDU NPP process. Compatible control logic is developed, and an electronic control system is programmed. After installing the electronic control system within the platform, variable transmission and platform timing routines are verified. A benchmark process is then observed and hardware-in-the-loop simulation is performed. During simulation, a software simulator executes CANDU specific NPP processes. The connected electronic control system is responsible for controlling a segment of the NPP shutdown system. The performance of the electronic control system as a replacement system for shutdown, and the developed interface as a tool for verifying proper electronic control system operation are discussed. Finally, Chapter 6 presents the conclusions related to the thesis work, contributions, and an outline of potential future research.

# Chapter 2

# Nuclear Power Plant Control Systems and Simulation

### 2.1 NPP Fundamentals

The basic energy cycle for a NPP is shown in Figure 2.1. Fuel for a nuclear fission reaction contains fissile material (uranium, plutonium). This fuel is fed into the reactor core where the fission reaction occurs. The energy produced from the chain fission reactions is released in the form of heat and is used to boil water. The steam produced from the boiling water drives a set of turbines and in turn an electrical generator. The electricity produced is supplied to the commercial electric power grid [27]. In conjunction with feeding fuel into the reactor, spent nuclear fuel is periodically removed from the reactor. Further, a small percentage of the generated electrical energy is utilized for electrical energy consumption requirements of the NPP [27].

There are many NPP designs in world-wide operation today, all of which follow this simplified NPP energy cycle. NPPs are classified by the properties of their moderator. The moderator is a material is contained within the reactor core [63]. Three typical moderator materials are ordinary water, heavy water, and graphite [28]. Most NPP in operation today use water as a moderator. Three main types of water reactors exist including heavy, or light water and heavy water reactors. In brief, light water is composed mostly of hydrogen oxide(H<sub>2</sub>O) molecules, whereas heavy water is composed of an increased amount of deuterium oxide (D<sub>2</sub>O) molecules [75]. D<sub>2</sub>O shares many chemical properties with H<sub>2</sub>O but allows for non-enriched uranium, or natural uranium to be used as reactor fuel [66]. This eliminates the requirement for uranium enrichment facilities. Two of the three main types of water moderated reactors are moderated by light water. Namely, pressurized water reactors (PWRs) and boiling water reactors (BWRs). The other is a heavy water moderated

Figure 2.1: Basic nuclear power plant energy cycle.

Figure 2.2: Simplified nuclear power plant control system.

reactor or pressurized heavy water reactors (PHWRs) [62]. These basic details of nuclear physics are sufficient in understanding the thesis as a whole.

NPPs are designed to operate for extended periods at constant electrical power output. Thus, they often provide base-load electricity supply to the commercial electrical power grid. A steady state balance must be maintained between the rate of energy released from the fuel in the reactor core and the electrical output of the generator. Many factors affect this balance, including disturbances in energy conversion processes, changes in the load requirements of the electrical power systems and in energy exchanges between the station and the environment [45]. Therefore, a control system must be implemented to compensate for the identified system imbalance [45]. A simplified plant control system is illustrated in Figure 2.2.

Primary inputs to the control system are reactor power, steam pressure and generator output (MW). Two common operating modes exist for NPPs. NPPs can operate in either mode. However, the most common mode is for the control system to operate in 'reactor-leading-turbine,' also referred to as 'turbine-following-reactor'

Figure 2.3: Model of 'Defence in Depth' concept.

mode. In this mode, steam pressure is maintained constant while the nuclear fission energy output is corrected to the desired set-point. The control system adjusts the steam flow to the turbine by changing the opening of the governor valve, thereby altering the electrical power output according to the current reactor core power generating capabilities [45]. Though NPPs are capable of fluctuating with the demands of the commercial electrical grid, known as 'load following,' it is not common practise. NPPs usually supply base-load electrical generation, and for this reason, other forms of electrical power generation respond to the changes in commercial electrical power demand [54] [55].

The above description, concepts and modes of controlling a NPP are significantly generalized. However, as indicated in Chapter 1, it is essential to minimize potential threats to the public and environment from the radioactive materials involved in the nuclear power generating process. Specific principles for achieving safe reactor operation are well defined [80]. Reactor safety is maintained if the reactor power is controlled, the fuel is cooled and the radioactivity is contained. For simplicity these principles are shortened to 'Control, Cool, and Contain,' [80].

Reactor safety is further incorporated through a concept known as 'Defence in Depth,' illustrated in Figure 2.3. The concept covers the entire process of designing, constructing, commissioning and operating a NPP. Further, the concept assumes that a) the NPP design will have some flaws, b) equipment will occasionally fail, and c) operating personnel will occasionally make mistakes. It is essential that the employed depth of defence covers both expected and unexpected flaws, failures and mistakes [80].

It is apparent that safety holds significant importance in all aspects of a NPP. At the top level control, cooling and containing are of greatest importance. This is primarily achieved through practising defence in depth as illustrated in Figure 2.3.

To assist in defence in depth practise, the methods documented in Table 2.1 are used [13].

Defence in depth includes special safety systems which are initiated as a last resort for preventing the unsafe consequences of abnormal plant operation during accident conditions. Specifically, these systems are used to mitigate the consequences of serious process failures requiring reactor shutdown, decay heat removal or retention of released radioactivity. Therefore, the systems perform no active function during normal NPP operation. In fact, all safety systems must be actively poised to allow operation of the NPP. For this reason safety system designs often require minimal system unavailability, an aspect which requires efficiently scheduled testing and maintenance procedures [13]. This is considered when developing an interface for satisfying electronic control system verification and the methods discussed in Table 2.1 are practised extensively during special safety system design. Safety systems are the primary focus within the work of this thesis.

## 2.2 CANDU Fundamentals

CANDU or Canadian Deuterium Uranium refers to a Canadian NPP design. CANDU NPPs are PHWR plants and are designed and maintained by AECL [47] [82]. A heavy water moderator and coolant are applied. This allows for natural as opposed to enriched uranium to be used as fuel. Canada has vast natural uranium reserves. Therefore, no uranium enrichment facilities are required [64]. CANDU NPPs include various additional characteristics which are unique in the nuclear industry. CANDU NPPs have the ability to refuel while the reactor is generating electrical power and connected to the commercial power grid. Other reactor designs replace fuel supplies regularly during extended scheduled shutdown periods. Many PWRs and BWRs are designed with high pressure reactor core and require bulk re-fuelling routines. The AECL NPP has a low pressure reactor core (calandria) which contains the moderator. High pressure tubes accessible from either end of the calandria enable fuel loading via fuel bundles. Primary coolant flows around the fuel bundles and heat energy produced by the fission reaction is transfered to the coolant [64]. These characteristics are known only to be implemented in AECL and CANDU-based reactor designs.

Similar to Figure 2.1, Figure 2.4 illustrates the energy cycle of a CANDU NPP. In addition, main CANDU process systems are included. The calandria contains

| Method          | Description [13]                                                 |

|-----------------|------------------------------------------------------------------|

| Redundancy      | Provision of alternative structures, systems and compo-          |

|                 | nents, so that any one can perform the required function         |

| Α.              | regardless of the state of operation or failure of any other.    |

| Diversity       | The presence of two or more redundant systems or compo-          |

|                 | nents to perform an identified function, where the different     |

|                 | systems or components have different attributes so as to         |

|                 | reduce the possibility of common cause, or mode, failure.        |

| Reliability     | The probability that a system or component will meet its         |

|                 | minimum performance requirements when called upon.               |

| Availability    | The fraction of time for which a system is capable of fulfilling |

| (Testability)   | its intended purpose.                                            |

| Separation      | Separation by geometry, by appropriate barriers, or by a         |

|                 | combination thereof.                                             |

| Environmental   | Generation and maintenance of evidence to ensure that            |

| Qualification   | equipment will operate on demand, under specified service        |

|                 | conditions, to meet system performance requirements.             |

| Quality Assur-  |                                                                  |

| ance            | • The function of a management system that provides con-         |

|                 | fidence that specified requirements will be fulfilled.           |

|                 | • A systematic programme of controls and inspections ap-         |

|                 | plied by any organization or body involved in the trans-         |

|                 | port of radioactive material which is aimed at providing         |

|                 | adequate confidence that the standard of safety prescribed       |

|                 | in regulations is achieved in practise.                          |

|                 | • All those planned and systematic actions necessary to          |

|                 | provide confidence that a structure, system or component         |

| 000             | will perform satisfactorily in service.                          |

|                 | <u> </u>                                                         |

| Codes and Stan- | In addition to the above methods, all system should comply       |

| dards           | with mandatory regional, national and international codes        |

|                 | and standards.                                                   |

Table 2.1: Methods used to ensure NPP safety requirements [13].

Figure 2.4: Energy cycle and main CANDU NPP systems.

heavy water moderator surrounded by a shield tank. The shield tank is filled with light water, a neutron absorber. Reactivity control is performed by vertical and horizontal reactivity control units installed between pressure tubes from the top and side of the calandria respectively [46].

Description of a simplified primary heat transfer loop begins with the reactor core. This closed loop is the primary heat transport system (PHTS), a system with a figure eight bi-directional coolant flow pattern. The PHTS is responsible for removing the coolant from the calandria and transferring it to light water boilers. An illustration of the PHTS is provided in Figure 2.5. Uranium is loaded into hundreds of pressure tube channels. Heavy water coolant circulates through pressurized tubes, where heat is transferred to the coolant. The heated (300°C) coolant enters the boilers, or steam generators. The coolant is then divided into hundreds of tubes where heat is transferred by conduction to light water. Following energy transfer, the cooler (260°C) heavy water exits the steam generator and is routed to heat transport pumps. The coolant then returns to the pressurized fuel channels. This completes the primary heat transport loop. Approximately 95 per cent of the heat energy generated during the fission reaction is transferred to the steam generator light feed-water with the other five per cent being lost to the moderator. A moderator cooling circuit is also included in the NPP but not discussed here. The heat energy is eventually lost to the atmosphere [26].

A steam cycle begins in the middle of the PHTS. An illustration of the steam cycle is provided in Figure 2.6. Light water in the steam generator is heated by

Figure 2.5: Simplified CANDU NPP primary heat transport system (PHTS) [26].

conduction from the heavy water of the PHTS. The light water boils and evaporates into steam. With a lower density than water, the steam rises to the top of the steam generator. A reduction in energy transfer efficiency results. The steam departs the steam generator and flows to the turbine set, both high pressure and low pressure, where it exerts force on the turbine blades. The force on the turbine causes the turbine shaft to rotate. The turbine shaft rotates the coupled rotor shaft of an electrical generator. Heat energy from the steam that does not contribute to driving the turbine blades is lost to cooling water in the condenser. Finally, the condensed steam, or water, is returned to the steam generator feed-water inlet through feed-heating and deaerator systems to complete the steam cycle [30]. Approximately 30 per cent of the total heat energy produced by the chain fission reaction is transferred to the mechanical energy in the turbine shaft [30].

In summary, kinetic energy from nuclear fission heats the heavy water coolant. Heat from the heavy water is conducted to the light water secondary coolant in the steam generator. The light water heat energy is then converted to mechanical energy (turbine) and mechanical energy converted to electrical energy (generator).

The Darlington NPP, located in the Municipality of Clarington near Bow-

Figure 2.6: Simplified CANDU NPP steam cycle [30].

manville, Ontario, Canada, is the subject of all further NPP descriptions. The NPP is used to illustrate NPP design, operation and safety characteristics. The design and practises of the Darlington NPP provide a basis for control system simulation and development. Darlington NPP is the newest CANDU NPP operating in Canada and is owned by OPG. Darlington NPP is a four-unit station with a total electrical output of 3,524MW(e) [39]. Design and operating specifications of the Darlington NPP are provided in Appendix A.

#### 2.3 Safety Systems

The objective of this research is to enhance safety critical control system practises. With this in mind, the following systems do not conform to classical closed loop control problems. In fact, the algorithms within these systems are relatively simple

[76]. It is common practise for special safety critical control systems to perform open-loop control functions [76]. By definition, open-loop control is any process in a system whereby one or more variables as input variables influence other variables as output variables. Characteristic for open-loop control is the open action path or in case of a closed action path, the output variables being influenced by the input variables are not continuously influencing themselves [76]. NPP safety systems are responsible for actuating fail-safe components which conform to the 'Control, Cool and Contain' principle. Though the actuating output signals of these systems will eventually affect input to the safety system, the input variables are not continuously influenced by the outputs [76].

In this section, the basic design and operating practises of AECL special safety systems are discussed. There are four special safety systems: shutdown system no. 1 (SDS1), shutdown system no. 2 (SDS2), emergency core cooling system (ECCS) and the containment system. These systems are responsible for ensuring safe operation of the NPP, and prevent the release of unsafe amounts of radioactivity into the environment [29]. Throughout this thesis, focus is placed on SDS1. Therefore, other safety systems are discussed in brief.

#### 2.3.1 Safety system concepts

Within CANDU NPPs, safety related systems are grouped to protect against common cause failures which may result from localized damage to the plant. There are two groups of safety systems. Group one encompasses the systems required for normal operation of the NPP as well as SDS1 and containment safety systems. Group two includes SDS2 and the ECCS safety systems [29].

Systems within each group are capable of independently performing reactor shutdown, decay heat removal, control, and monitoring. Physical separation and functional diversity separate the groups. Further, interconnection between groups is practically minimized. However, safety support services (electrical, power, cooling water and feed-water systems) are capable of providing backup support services to each group [29].

Control and monitoring of station events is performed from the main control room of group one. However, if the main control room becomes inoperable or inhabitable, a secondary control room belonging to group two remains functional [29].

Figure 2.7: Safety instrumented system (SIS) open action path.

The previously described NPP control routines provide some degree of safety protection as they maintain plant balance. However, special safety systems are by definition safety instrumented systems (SIS). An SIS is defined as an instrumented system used to implement one or more safety instrumented functions and is composed of any combination of sensors, logic solvers, and final elements [29]. This is similar to the open action path illustrated in Figure 2.7. There are two primary SISs in CANDU NPPs. One system, SDS1, consists of mechanical shut-off rods while the other, SDS2, injects a neutron absorbing solution into the moderator via liquid poison injection nozzles. The two shutdown systems respond automatically to both neutronic and process signals. Further, either system acting on its own is capable of shutting down the reactor and maintaining shut down for all design basis events [29].

The redundant SDS2 quickly terminates reactor operation when specific neutronic and process parameters enter an unacceptable range. The method of terminating reactor operation is the rapid injection of concentrated gadolinium nitrate solution into the moderator through a horizontal nozzle located on the side of the calandria [29].

The ECCS replenishes reactor coolant in the event of a loss-of-coolant accident (LOCA). This safety function is necessary to assure cooling of the reactor fuel. In the initial ECCS phase, pressurized light water is delivered to PHTS headers. Pressure is provided by ECCS gas tanks. Over the long term, the ECCS re-circulates the light water through the pressure tubes and dedicated ECCS heat exchangers for decay heat removal [29].

Containment is provided by containment envelope and containment isolation. The containment envelope is the reactor building. The envelope provides a pressure-retaining boundary and includes airlocks, piping and electrical penetrations, with isolation valves included as necessary. It is designed to withstand the maximum pressure of any design basis accident. Isolation is achieved automatically by closing

specific valves if an increase in containment pressure or radioactivity level is detected. In the long term, air coolers provide an atmospheric heat sink for the envelope [29].

#### 2.3.2 Shutdown system no. 1

The two NPP shutdown systems, SDS1 and SDS2, are designed in compliance with Canadian Nuclear Safety Commission (CNSC) regulations [29]. Though SDS1 is the focus of this section and the thesis work, general and performance requirements for both shutdown systems include [29]:

- A CANDU NPP must be equipped with two independent and diverse shutdown systems.

- Compliance with regulatory requirements must be approved by the governing body (CNSC, formerly the Atomic Energy Control Board) prior to issuance of construction approval or operating license.

- Designed such that, acting alone, it can ensure that:

- the reactor is rendered sub-critical and is maintained sub-critical;

- the reference dose limits are not exceeded; and

- a loss of primary heat transport system integrity shall not result from any fuel failure mechanism, in the event prompt shutdown is required.

- Ensure fuel in the reactor, with no defects prior to the event, does not fail as a consequence of the event for relevant events listed in Tables B.1, B.2, B.3, B.4 of Appendix B.

- Have the ability to operate when exposed to the most severe environmental conditions that accompany the events listed in Tables B.1, B.2, B.3, B.4 of Appendix B. This capability should be demonstrated and effects analyzed.

- Demonstrate the target unavailability of less than  $10^{-3}$  years per year including availability, testing and maintenance.

- Incorporate redundancy such that the failure of any single component will result in below allowable performance under accident conditions.

- Provide shutdown capabilities regardless of electrical power supply condition.

- Be designed to have consistent safety capabilities in all operating and failure modes. Failed components must fail at a safe state.

- Prevent disabling of manual operator shutdown capabilities, and to respond to redundant and remote location manual shutdown.

- Incorporate diverse, physical and operational independence.

- Be effective and independent of normal process, safety or special safety systems.

SDS1 is the primary method for terminating reactor operation when a specified set of NPP parameters enter an unacceptable range. SDS1 reduces the capability of nuclear fission reactions within the core through the release of spring-assisted gravity-drop shut-off rods [29]. The shut-off rods are composed of the neutron absorbing material cadmium.

SDS1 has three independent channels, designated D, E and F. Each channel detects the requirement for a reactor trip and de-energizes a set of relays which control direct current clutches for the release the shut-off rods. The triplicated design and measurement of safety critical NPP parameters will function even when a single loop component or power supply fails. Therefore, a failure will not incapacitate or spuriously invoke the operation of the safety system [29].

The logic for SDS1 operates using general coincidence. General coincidence operation requires that two of the three (2003) channels of SDS1 trip. The parameter on which SDS1 trips does not affect the dropping of the shut-off rods. Therefore, if any two parameters are beyond specified safe limitation set-points, SDS1 initiates shutdown routines [29].

SDS1 and SDS2 operation differ when more than one trip parameter is beyond normal operating range. Both SDS1 and SDS2 use a 2003 voting mechanism. SDS1 will trip on any two parameters, illustrated in Figure 2.9, which are beyond an acceptable range, known as general coincidence. On the other hand, SDS2 requires that the two parameters that are not satisfying proper NPP operation are produced by the same parameter on both channels. This is known as local coincidence [29]. Both coincidence voting techniques are illustrated in Figure 2.8.

The parameters which can initiate a general coincident reactor trip through SDS1 are listed below. Further, the parameters and the systems that the measured variables are captured from are illustrated in Figure 2.9. There are nine measured variables which must remain within specified ranges in order for the reactor to remain

Figure 2.8: a) General (SDS1) and b) local (SDS2) coincident two-out-of-three (2003) trip mechanisms.

in an operating state. The selection of variables is performed so that all categories of process failures identified in Appendix B are protected against. Also, the manual initiation of SDS1 is supported. This is performed by an operator from the main control room or secondary control area [36].

- neutron power Inconel in-core flux detectors. A linear amplifier converts detector current readings to a voltage signal. The set-point for neutron over power is altered depending whether abnormal reactor operating conditions are observed. Shutdown system design ensures protection coverage during normal fuel manoeuvring or single device failure.

- 2. rate log neutron Ion chamber detectors. Current signal proportional to the

Figure 2.9: CANDU SDS1 trip parameters and originating systems.

thermal neutron flux and amplified to linear and logarithmic neutron power and rate logarithmic signals. The rate logarithmic signal is used as a direct trip parameter. Set-point conditioning for rate log neutron trip is provided by neutron power levels.