# Secure Outsourcing of Circuit Manufacturing

Giuseppe Ateniese\*, Aggelos Kiayias†, Bernardo Magri‡, Yiannis Tselekounis†, and Daniele Venturi§

\*Stevens Institute of Technology

†University of Edinburgh

‡Aarhus University

§Sapienza University of Rome

January 29, 2019

#### Abstract

The fabrication process of integrated circuits (ICs) is complex and requires the use of off-shore foundries to lower the costs and to have access to leading-edge manufacturing facilities. Such an outsourcing trend leaves the possibility of inserting malicious circuitry (a.k.a. hardware Trojans) during the fabrication process, causing serious security concerns. Hardware Trojans are very hard and expensive to detect and can disrupt the entire circuit or covertly leak sensitive information via a subliminal channel.

In this paper, we propose a formal model for assessing the security of ICs whose fabrication has been outsourced to an untrusted off-shore manufacturer. Our model captures that the IC specification and design are trusted but the fabrication facility(ies) may be malicious. Our objective is to investigate security in an *ideal sense* and follows a simulation based approach that ensures that Trojans cannot release any sensitive information to the outside. It follows that the Trojans' impact in the overall IC operation, in case they exist, will be negligible up to simulation.

We then establish that such level of security is in fact achievable for the case of a single and of multiple outsourcing facilities. We present two compilers for ICs for the single outsourcing facility case relying on verifiable computation (VC) schemes, and another two compilers for the multiple outsourcing facilities case, one relying on multi-server VC schemes, and the other relying on secure multiparty computation (MPC) protocols with certain suitable properties that are attainable by existing schemes.

**Keywords:** Security models, hardware Trojans, circuit compilers, fabless manufacturing, verifiable computation.

## Contents

| 1   | 1 Introduction                      |          |   | 4.2 Compiler based on Input-     |           |

|-----|-------------------------------------|----------|---|----------------------------------|-----------|

|     | 1.1 Background                      | 1        |   | Private VC                       | 13        |

|     | 1.2 Previous Work                   | 2        |   | 4.3 Compiler based on VC without |           |

|     | 1.3 Our Contributions               | 3        |   | Input Privacy                    | 18        |

|     | 1.4 Related Work                    | 6        |   |                                  |           |

| f 2 | Preliminaries                       |          | 5 |                                  |           |

| _   | 2.1 Notation                        | <b>7</b> |   | turers                           | <b>22</b> |

|     |                                     |          |   | 5.1 Compilers based on VC with   |           |

|     | 2.2 Circuits                        | 8        |   | Multiple Servers                 | 22        |

| 3   | Secure Circuit Fabrication          | 8        |   | 5.2 Compiler based on MPC        | 26        |

|     | 3.1 Security                        |          | 6 | Concrete Instantiations          | 30        |

|     | 3.2 Undetectability                 | 11       |   |                                  |           |

|     |                                     |          |   | 6.1 Case Study I                 |           |

| 4   | Case Study I: Single Manufac-       |          |   | 6.2 Case Study II                | 30        |

|     | turer                               | 11       |   |                                  |           |

|     | 4.1 Prelude: Verifiable Computation | 12       | 7 | Conclusion and Open Problems     | <b>32</b> |

## 1 Introduction

## 1.1 Background

The fabrication process adopted by the semiconductor industry is fundamentally global, involving several parties that may not be trusted. As a result, integrated circuits (ICs) are vulnerable to so-called hardware Trojans that can compromise or disable critical systems, or covertly leak sensitive information [58, 24, 9]. Analogously to a software Trojan, a hardware Trojan is a back-door deliberately added to the circuit to disrupt its operation or disable it when certain events occur. A Trojan can be added to the circuit during the design phase, by some malicious designer, or more often during the manufacturing phase, by some malicious off-shore fabrication facility. A hardware Trojan's objectives may be to modify the functionality of the circuit (e.g., in order to compromise or disable critical systems), modify its specification (e.g., by changing its energy consumption), covertly leak sensitive information (e.g., from a secret memory), or simply disable the entire circuit when instructed to do so [7]. Once the Trojan is inserted into the circuit it can stay active the entire time, or it can be "triggered" by some event such as a special input to the circuit.

Reliably detecting compromised circuit components through testing and reverse engineering appears to be an impossible task given our current technology [15]. Indeed, all non-destructive testing techniques can easily be circumvented by properly obfuscating embedded Trojans. The U.S. military recognized this threat and started two programs, Trust and IRIS, with the intent of developing techniques and metrics to certify ICs going into weapon systems. The main concern is that advanced weapons may appear to work properly but then switch off in combat or when triggered by some special events. Another stated concern is information leakage, where a malicious component is programmed to leak sensitive information [75].

The U.S. military however currently obtains trusted chips through the DOD Trusted Foundry program which is currently managed by the NSA's Trusted Access Program Office (TAPO). Within this program, a trusted design center and foundry are established through an exclusive partnership with IBM for secure semiconductor fabrication and ASIC services, along with the involvement of several Trusted Suppliers which are accredited by an accreditation authority

(DMEA). The intent of the Trusted Foundry program is to provide national security and defense programs with access to ICs from trusted sources. However, a report by the U.S. Government Accountability Office (GAO) [60], released in April 2015, found that even though the Trusted Foundry program started in 2004, IBM remained the sole-source supplier for leading-edge technologies meeting the criteria put forth by DOD. GAO's report highlights two main issues: First, it notices that IBM sold its microelectronics fabrication business to a foreign-owned entity (GlobalFoundries). Second, relying on a single source supplier for defense microelectronics hinders competition and thus innovation in this critical area.

#### 1.2 Previous Work

Inspired by the above considerations, in this work we put forward a formal security model for the problem of utilizing off-shore fabrication facilities for IC manufacturing. Our main motivation is that the setting of secure circuit fabrication, while being an extremely important practical problem, almost completely lacks theoretical foundations. We discuss a few remarkable exceptions below.

- Seifert and Bayer [74] introduced a very strong security model for the fabrication of Trojanresilient circuits, where the produced circuit is required to always have the same output as the original circuit; unfortunately, they show how to achieve their definition only for very limited classes of Trojans (i.e., the adversary is allowed to "corrupt" only a small fraction of the gates in each layer of the IC, and a small fraction of the wires connecting different layers).

- Recently, Wahby et al. [76] introduced a new approach to the problem of defeating hardware Trojans in fabless circuit manufacturing. Their model reflects the fact that IC specification and design are trusted but the fabrication facility is not. Rather than testing or reverse engineering the IC hardware received, which only provides limited security, they consider a class of solutions where the IC's operations are continuously verified. Such an approach makes sense as long as the verification circuitry can be: (i) constructed cheaply, and (ii) run efficiently. These properties are achieved by leveraging a verifiable computation (VC) scheme for the function implemented by the original circuit. Verifiable computation (see, e.g., [41]) is a recent paradigm by which resource-constrained clients can delegate the computation of some function  $\mathcal{F}$ , on (possibly private) input X, to an untrusted (and computationally powerful) server, without the server being able to cheat about the outcome of the computation, and with the property that verifying the server's answer is much more efficient than computing the function from scratch.

- In a nutshell, the goal of [76] is to make sure that the produced circuit maintains correctness of the computation, meaning that the output of the circuit is either invalid, or equal to the output of the original circuit. The main drawback is that invalid outputs might be arbitrarily correlated with the secret state of the circuit, which could expose key material in case the produced circuit is a cryptographic circuit. (We will formalize this fact later in the paper.)

- In [35], the authors show how to protect against hardware Trojans using testing-based mechanisms. Their work is based on two existing techniques for Trojan detection, called "input scrambling" and "split manufacturing" [50], for which the authors provide formal models. Hence, they present a generic compiler that transforms any circuit into a new (equivalent) circuit with the following guarantee: Assuming the attacker invokes the circuit q times, and that the device is being tested t times, for t > q uniform on a specific range which is not known to the attacker, the compiled circuit is secure with probability at

least  $1 - (q/t)^{\ell/2}$ , were  $\ell$  is the number of copies of the sub-circuits whose production is outsourced.

The main limitation is that [35] assumes an a-priori known bound on the number q of interactions between the user and the device; in fact, without such a bound, their construction would require a super-polynomial number of tests. Unfortunately, in many important applications, it is not realistic to assume an upper bound on the value q, and thus it is an important open problem to design a methodology that provides security for an arbitrary polynomial number of interactions between the user/attacker and the device.

• The approach of applying secure distributed computing to defeat hardware Trojans has also been recently explored in [61]. However, this work is more focused on the implementation aspects of this idea, and moreover it assumes that a software developer builds and signs the applications to be run on the possibly malicious circuit components.

### 1.3 Our Contributions

We put forward a formal framework for assessing security of a circuit whose production has been, in part, outsourced to a set of manufacturers that are not trusted. Our security definition implies that using the produced circuit in the wild leaks no information on its secrets. Additionally, the adversarial model we consider does not assume any a-priori bound on the number of executions, and allows the manufacturer(s) to make arbitrary modifications to the outsourced components. In essence, our security model captures any attack in which the backdoored circuit communicates with the user/attacker through the input/output gates of the produced circuit. (This includes digital and analog Trojans, but not hidden antennas as considered in [35].)

With such a framework in hand, we give several design methodologies that achieve our definition with different tradeoffs in terms of security, efficiency, and underlying assumptions. Thus, our work establishes the theoretical feasibility of utilizing off-shore fabrication facilities for IC manufacturing. A more detailed explanation of our main contributions follows below.

Secure circuit fabrication. Let  $\Gamma$  be the original circuit to be produced. Instead of producing  $\Gamma$  directly, we first "compile" it into a different circuit  $\widehat{\Gamma}$  using an efficient, possibly randomized, procedure  $\Phi$  that we call an *outsourcing compiler*. The compiler  $\Phi$  takes as input a description of  $\Gamma$  and returns a description of  $\widehat{\Gamma}$ , together with some auxiliary information specifying how  $\widehat{\Gamma}$  can be divided into sub-components, and which of these components can be produced off-shore; the remaining components will be instead built in-house. After all components have been produced, the circuit designer re-assembles the circuit  $\widehat{\Gamma}$  (by combining the outsourced components and the components built in-house), which is then initialized with some initial secret memory  $M_1$ , and used in the wild.

In order to make sense, the above approach needs to satisfy a few important requirements. The first requirement is that  $\Phi$  needs to be functionality preserving, meaning that the compiled circuit  $\widehat{\Gamma}$  should compute the same functionality as the original circuit  $\Gamma$  (for all possible initial memories  $M_1$ , and for all possible inputs). The second requirement is that the effort needed to manufacture the trusted sub-components should be (much) less compared to the effort required to manufacture the original circuit  $\Gamma$ . The third requirement is that  $\Phi$  should be secure, meaning that, under an acceptable assumption about the manufacturers who construct the outsourced components, the produced circuit  $\widehat{\Gamma}$  can be safely used in real-life applications.

Our security definition follows the simulation paradigm, and is inspired by similar definitions in the setting of tamper-proof circuit compilers [52, 38]. We refer the reader to Section 1.4 for a more detailed comparison between the two approaches. In a nutshell, security of  $\Phi$  is defined by requiring that whatever an adversary can learn by interacting with the fabricated circuit  $\hat{\Gamma}$

(produced following the steps outlined above), can be simulated given only black-box access to the original circuit  $\Gamma$ . This essentially means that, no matter how the outsourced components are maliciously modified (e.g., by inserting a hardware Trojan), using circuit  $\widehat{\Gamma}$  is as secure as using the original circuit  $\Gamma$ , and thus, in particular, does not leak sensitive information on the secret memory. See Section 3 for a precise definition.

We also consider a weakening of the above definition, in which the simulator is allowed to receive a short advice (or leakage) on the secret memory  $M_1$ . This models a setting where the adversary might be able to learn a short amount of information on the secret memory, but still yields a meaningful security guarantee provided that the original circuit is resilient to such a short leakage. An appealing advantage of this weaker definition is that it might allow for significantly more efficient circuit compilers.

Case study I: Single manufacturer. In Section 4, we show how to construct secure outsourcing compilers that work for arbitrary circuits  $\Gamma$  in the setting where all outsourcing manufacturers are corrupted. Similarly to [76], our compilers generically leverage a VC scheme for the function  $\mathcal{F}$  implemented by  $\Gamma$ . Recent breakthrough research on verifiable computation led to nearly practical schemes that work for any function [67, 26]; some schemes additionally preserve the privacy of the inputs on which the function is being computed on [39]. VC schemes satisfying the latter property are called *input-private*.

The main idea of how to use verifiable computation in order to build secure outsourcing compilers is simple enough to describe it here. The fabrication of the chips that perform the entire bulk of computation will be outsourced to the untrusted fabrication facility, whereas the only circuit components that need to be built in-house are: (i) the component corresponding to the algorithm for encoding the inputs (in case of input-private VC), (ii) the component corresponding to the algorithm run by the client in order to verify correctness of the server's computation, and (iii) the component used to generate fresh random coins as needed for computing the function (in case of randomized functions). Thanks to the nature of VC, the size of the components in (i) and (ii) is independent of the size of the original circuit computing the function. As for the component in (iii), we can use any existing (and trusted) circuitry for generating true random numbers (RNG). A good example is the Intel on-chip hardware random number generator which can be accessed through the RDRAND instruction available on all modern processors [54, 49].<sup>1</sup>

We implement the above idea in two ways, depending on the properties satisfied by the underlying VC scheme, as explained below.

- Our first compiler relies on VC schemes with input-privacy, and achieves our strongest security notion (i.e., no leakage required for the simulation).

- Our second compiler relies on VC schemes without input-privacy, and achieves security provided the original primitive (implemented by the circuit  $\Gamma$ ) is resilient against a logarithmic amount of leakage on the private memory.

- Remarkably, any public-key encryption or signature scheme is resilient to such an amount of leakage at the price of a polynomial loss in the concrete security, and recently many leakage-resilient schemes [36, 69, 56, 34, 64, 19, 65, 37] have been constructed, where the concrete security does not degrade with the total amount of tolerated leakage.

The second compiler additionally relies on a special "self-destruct" feature (which is imple-

<sup>&</sup>lt;sup>1</sup>Intel's generator relies on unpredictable thermal noise to generate bits that are fed to a cryptographic "conditioner" (AES in CBC-MAC mode) which produces a 256-bit seed that is then passed through a NIST SP800-90A-based pseudorandom generator.

mented<sup>2</sup> in one of the components built in-house), meaning that after the first invalid output is ever processed, the entire memory is overwritten. As we show, this is an inherent requirement for this compiler, in that, without such a property, there exist generic attacks that allow to recover the entire private memory. Moreover, such attacks are undetectable by all polynomial-time (black-box) tests.

Our definition of undetectability (see Section 3.2) is similar in spirit to analogous definitions in the context of subversion-resilient cryptography [12, 11].

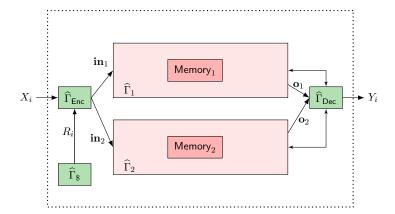

Case study II: Multiple manufacturers. In Section 5, we show how to construct secure outsourcing compilers for arbitrary circuits  $\Gamma$  in the setting where  $m \geq 2$  outsourcing manufacturers are available, and a certain unknown subset of them is malicious. This is a strictly stronger assumption compared to the setting of a single manufacturer, nevertheless, as we show, it opens the possibility for more efficient constructions and stronger availability guarantees. We present two different approaches.

- The first approach yields an outsourcing compiler utilizing a general client-server secure multiparty computation (MPC) protocol, i.e., a protocol that, for any function, enables a set of clients to privately communicate their inputs to a set of servers that will perform a computation and return the output to a single designated recipient. We stress that many MPC protocols follow this paradigm (e.g., [30]), while others, as we comment later, can be easily adapted to it.

- Given such a protocol, the compiler operates in the following way (see also Section 5.2). For a given circuit  $\Gamma$  it produces the MPC protocol implementing it, isolates the client and recipient computation for manufacturing in-house, and outsources each of the other components (representing a server in the MPC protocol) to the untrusted manufacturers. The key points of this compiler construction are as follows: (i) The client and recipient computation are typically quite lightweight; the client, in many protocols, simply performs an encryption or a secret-sharing operation, and the recipient a secret-reconstruction protocol; in either case, the computation is independent of the circuit that is outsourced. (ii) There are MPC protocols that can tolerate up to m-1 malicious servers, something we can leverage to argue that if at least one of the outsourcing manufacturer is honest the compiled circuit would be safe for use.

- Additional properties of the underlying MPC protocol can also be very valuable by our compiler: for instance, if the underlying MPC protocol supports guaranteed output delivery, we can use this guarantee to argue that the final circuit will be resilient to a certain faulty outsourced sub-component. Moreover, if the underlying protocol satisfies the identifiable abort property, cf. [51], we can enable our compiled circuit to switch-off an outsourced sub-component that is discovered to be faulty (or malicious), thus reducing energy consumption.

- The second approach yields outsourcing compilers based on so-called multi-server VC [21, 1]; these are VC schemes where the client outsources the computation of the function to multiple servers. In particular, one of our construction leverages a special type of multi-server VC scheme called Refereed Delegation of Computation (RDoC) [21, 22, 23]. This yields a very simple outsourcing compiler achieving the very strong guarantee that the compiled circuit outputs the same as the (untampered) original circuit with overwhelming probability. Furthermore, in this construction it is also possible to identify the malicious

<sup>&</sup>lt;sup>2</sup>The self-destruct feature can be realized in several ways. One option is to have the decoder overwrite the memory with all zeroes after an invalid output is produced. Alternatively, one could let the decoder keep a single bit of state, which is written to 1 as soon as the first invalid output is produced.

components, which can then be switched-off providing additional advantages in terms of efficiency and energy consumption.

The main technical ideas behind the compilers based on multi-server VC are similar in spirit to the ones underlying our first compiler based on single-server VC. We refer the reader directly to Section 5.1 for a high-level description of these compilers and their security analysis.

On efficiency. In Section 6, we describe several instantiations of our compilers, based on state-of-the-art construction in the settings of VC and MPC. This yields several concrete constructions with different tradeoffs in terms of security, efficiency, and underlying hardness assumptions. We do stress, however, that the main contributions of this paper are the security models and precise definitions put forward for the problem of fabless ICs manufacturing. The constructions presented in Section 6 are described mainly to evidence the feasibility of our proposed model.

An important remark is that all our approaches require a partitioning and assembly procedure which must be performed in-house. To lower the cost, trusted and untrusted sub-circuits will likely be diced in their own wafers and packaged independently. We note that recent advanced designs and emerging technologies in the electronics assembly and packaging industry make interconnecting different components a reasonably cost-efficient operation.

#### 1.4 Related Work

Hardware Trojans. Prevention of hardware Trojans in ICs is a common practice that might take place during the design, manufacturing, and post-manufacturing stage [70, 59]. However, since it is not always possible to efficiently prevent Trojans insertion, Trojans detection has also been vastly explored [15]; once a Trojan is detected, the circuit can be disposed and not used. Common methodologies used to perform Trojans detection vary from invasive ones (that destroy the IC to examine it inside), to non-invasive ones (where the circuit is executed and compared against a trusted copy of the circuit, or against some expected output values). Trojan detection is typically a very expensive and unreliable process, therefore the best practice is usually not to rely on any kind of testing to protect against Trojans. Explicit countermeasures against Trojans also exist, where the objective is to guarantee the functionality or security of the circuit even in the presence of some unknown Trojan. For instance, the so-called "data guards" are designed to prevent a Trojan from being activated and/or to access sensitive data [77]. Another approach is the duplication of logic elements and the division of the sensitive data to independent parts of the circuit [62, 77].

**Tamper-proof hardware.** The existence of tamper-proof hardware is a physical assumption that found several applications in cryptography, for instance in the setting of secure computation [55]. Here, parties in a protocol can exchange (and rely on) tamper-proof hardware tokens, executing (possibly stateful) programs in a black-box manner, upon inputs of the parties' choice.

In this vein, our work is related to the challenging scenario where the parties rely on tamperproof tokens that might have been produced by one (or more), possibly malicious, outsourcing facility. Such a question was studied in [40] for the special case of secure protocols for set intersection, and very recently in [25] for the more general case of arbitrary multi-party functionalities.

**Tamper-proof circuits.** Our main security definition shares similarities with analogous definitions in the context of protecting circuit implementations against tampering attacks. This line of research received considerable attention in the past few years [52, 38, 27, 57, 28]. The

main difference between this setting and the one considered in our paper is that tamper-proof circuit compilers are typically used to protect against fault injection [66] and tampering attacks at run-time; such attacks are usually carried out in an adaptive manner, depending on the outcome of previous attempts. Outsourcing compilers, instead, only protect against (non-adaptive) tampering taking place during the circuit fabrication process. Importantly, the latter restriction allows to obtain security against arbitrary modifications, whereas in circuit tampering one has to consider very restricted attacks (e.g., wire tampering [52] or gate tampering [57]).

**Subversion.** The above type of non-adaptive tampering is, in fact, reminiscent of the setting of subversion attacks against cryptographic primitives and algorithms. Inspired by the recent revelations of Edward Snowden [68, 5, 47], this line of research recently led to constructing several concrete primitives resisting large classes of subversion attacks [12, 32, 33, 3, 71, 72, 73]. In this light, our work could be interpreted as formalizing the security of circuits that might have been subject to subversion during fabrication.

Conference version. An extended abstract of this paper appeared in the proceedings of the 12th International Conference on Provable Security (ProvSec 2018). This is the full version of that paper, with revised proofs and new material, including, e.g., the constructions based on VC without input privacy (cf. Section 4.2) and on VC with multiple servers (cf. Section 5.1), as well as the notion of undetectability (cf. Section 3.2) and the negative result showing necessity of the self-destruct capability for the compiler of Section 4.3.

## 2 Preliminaries

#### 2.1 Notation

For a string x, we denote its length by |x|; if S is a set, |S| represents the number of elements in S; for a natural number n, [n] denotes the set  $\{1,\ldots,n\}$ . When x is chosen randomly in S, we write  $x \leftarrow S$ . When A is an algorithm, we write  $y \leftarrow A(x)$  to denote a run of A on input x and output y; if A is randomized, then y is a random variable and A(x;r) denotes a run of A on input x and randomness x. An algorithm A is probabilistic polynomial-time (PPT) if A is randomized and for any input  $x, x \in \{0, 1\}^*$  the computation of A(x; x) terminates in at most poly(|x|) steps. We denote with  $A \in \mathbb{N}$  the security parameter. A function  $x \in \mathbb{N}$  is negligible in the security parameter (or simply negligible) if it vanishes faster than the inverse of any polynomial in  $x \in \mathbb{N}$ , i.e.  $x \in \mathbb{N}$

The statistical distance between two random variables  $\mathbf{Z}$  and  $\mathbf{Z}'$  defined over some common set Z is defined as  $\Delta(\mathbf{Z}; \mathbf{Z}') = \frac{1}{2} \sum_{z \in Z} |\mathbb{P}[\mathbf{Z} = z] - \mathbb{P}[\mathbf{Z}' = z]|$ . For two ensembles  $\mathbf{Z} := \{Z_{\lambda}\}_{{\lambda} \in \mathbb{N}}$  and  $\mathbf{Z}' := \{Z'_{\lambda}\}_{{\lambda} \in \mathbb{N}}$ , we write  $\mathbf{Z} \equiv \mathbf{Z}'$  to denote that the two ensembles are identically distributed. We also write  $\mathbf{Z} \approx_c \mathbf{Z}'$  to denote that the ensembles are computationally indistinguishable, i.e. for all PPT distinguishers  $\mathcal{D}$  there exists a negligible function  $\nu : \mathbb{N} \to [0, 1]$  such that

$$\Delta^{\mathcal{D}}(\mathbf{Z};\mathbf{Z}') := \left| \mathbb{P}\left[ \mathcal{D}(z) = 1: \ z \leftarrow \$ \ \mathbf{Z} \right] - \mathbb{P}\left[ \mathcal{D}(z) = 1 \right]: \ z \leftarrow \$ \ \mathbf{Z}' \right| \leq \nu(\lambda).$$

We rely on the following lemma (which follows directly from the definition of statistical distance):

**Lemma 1.** Let  $\mathbf{Z}$  and  $\mathbf{Z}'$  be a pair of random variables, and W be an event defined over the probability space of  $\mathbf{Z}$  and  $\mathbf{Z}'$ . Then,

$$\Delta(\mathbf{Z}; \mathbf{Z}') \le \Delta(\mathbf{Z}; \mathbf{Z}' | \neg W) + \mathbb{P}[W].$$

### 2.2 Circuits

A (Boolean) circuit  $\Gamma = (V, E)$  is a directed graph. The vertices V are logical gates, and the edges E are wires connecting the gates. For the case of deterministic circuits, the gates can be of type AND, XOR and copy, where AND (resp. XOR) have fan-in two and fan-out one, and output the AND (resp. XOR) operation on the input bits; a copy gate, denoted copy, simply forwards the input bit into two output wires. The depth of a circuit is defined as the longest path from an input to an output; the size of a circuit is defined as its total number of gates. Sometimes we explicitly write  $\langle \Gamma \rangle$  for the description of the circuit  $\Gamma$ . A circuit is clocked if it evolves in clock cycles (or rounds). The input and output values of the circuit  $\Gamma$  in clock cycle i are denoted by  $X_i$  and  $Y_i$ , respectively. A circuit is *probabilistic* if it uses internal randomness as part of its logic. We call such probabilistic logic randomness gates and denote them with \$. In each clock cycle \$ outputs a fresh random bit. Additionally, a circuit may contain memory gates. Memory gates, which have a single incoming edge and any number of outgoing edges, maintain state: at any clock cycle, a memory gate sends its current state down its outgoing edges and updates it according to the value of its incoming edge. Any cycle in the circuit graph must contain at least one memory gate. The state of all memory gates at clock cycle i is denoted by  $M_i$ , with  $M_1$  denoting the initial state. When a circuit is run in state  $M_i$  on input  $X_i$ , the circuit will output  $Y_i$  and the memory gates will be in a new state  $M_{i+1}$ . We will denote this by  $(Y_i, M_{i+1}) \leftarrow \Gamma[M_i](X_i)$ .

## 3 Secure Circuit Fabrication

In this section we put forward a formal model for assessing security of a (cryptographic) circuit whose production is outsourced to one or more untrusted facilities. We start by recalling the standard notion of connected component of a circuit or graph.

**Definition 1** (Component). A circuit  $\Gamma' = (V', E')$  is a (connected) component of circuit  $\Gamma = (V, E)$  if  $V' \subseteq V$ ,  $E' \subseteq E$  and for all  $g_1, g_2 \in V'$  we have that  $(g_1, g_2) \in E'$  iff  $(g_1, g_2) \in E$ .

Next, we introduce the notion of an outsourcing circuit compiler (or simply compiler). In a nutshell, a circuit compiler is an efficient algorithm  $\Phi$  that takes as input (the description of) a circuit  $\Gamma$ , and outputs (the description of) a compiled circuit  $\widehat{\Gamma}$ . Additionally,  $\Phi$  returns a list of sub-components  $\widehat{\Gamma}_i$  of  $\widehat{\Gamma}$  whose production can be outsourced to one or more external manufacturers, together with the relevant information on how to connect those sub-components with the remaining ones (that need to be built in-house) in order to re-assemble the compiled circuit  $\widehat{\Gamma}$ .

**Definition 2** (Outsourcing circuit compiler). Let  $\Gamma$  be an arbitrary circuit. A  $(\rho, m)$ -outsourcing compiler  $\Phi$  is a PPT algorithm  $(\widehat{\Gamma}, \mathsf{aux}) \leftarrow \Phi(\Gamma)$ , such that the following holds:

- aux :=  $((\widehat{\Gamma}_1, \dots, \widehat{\Gamma}_n), \mathcal{M}, (I_1, \dots, I_m))$ , with  $n \in \mathbb{N}$  and  $I_j \subseteq [n]$ , for  $j \in [m]$ , mutually disjoint subsets.

- $(\widehat{\Gamma}_1, \dots, \widehat{\Gamma}_n)$  are disjoint (connected) components of  $\widehat{\Gamma}$  such that  $V = \bigcup_{i \in [n]} V_i$ , where  $\Gamma_i = (V_i, E_i)$ .

- $\mathcal{M}: V \times V \to \{0,1\}$  is a function such that  $\mathcal{M}(v,v') = 1$  iff  $v,v' \in V_i, V_j$  for some  $i \neq j$  and  $(v,v') \in E$ .

We call  $\rho := \frac{\sum_{i \in [n] \setminus I_1 \cup ... \cup I_m} |\widehat{\Gamma}_i|}{|\Gamma|}$  the outsourcing ratio of the compiler.

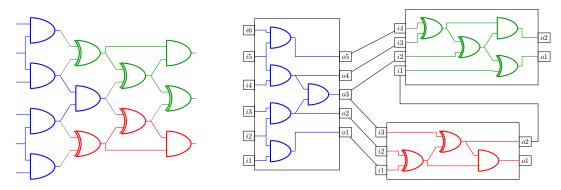

Figure 1: On the left side we present the description of a (compiled) circuit. On the right side the same circuit is represented as three different components. The mapping function  $\mathcal{M}$  establishes the connections between the blue component and the green and red components.

Intuitively, in the above definition, the outsourcing ratio  $\rho$  represents the fraction of the compiled circuit (w.r.t. the original circuit) that should be built in-house. Note that the sub-components  $(\widehat{\Gamma}_i)_{i\in[n]}$  "cover" the entire compiled circuit  $\widehat{\Gamma}$  (without overlap), and the mapping function  $\mathcal{M}$  specifies how to connect the different components in order to reconstruct  $\widehat{\Gamma}$ . The sets of indexes  $I_j \subseteq [n]$  represents the sub-components whose production will be outsourced to manufacturer  $j \in [m]$ . See Fig. 1 for a pictorial representation in a simple toy example.

Correctness of an outsourcing compiler demands that the compiled circuit maintains the same functionality of the original circuit.

**Definition 3** (Correctness). We say that an outsourcing compiler  $\Phi$  is functionality preserving if for all circuits  $\Gamma$ , for all values of the initial memory  $M_1$ , and for any set of public inputs  $X_1, \ldots, X_q$ , the sequence of outputs  $Y_1, \ldots, Y_q$  produced by running the original circuit  $\Gamma$  starting with state  $M_1$  is identical to the sequence of outputs produced by running the transformed circuit  $\widehat{\Gamma}$  starting with state  $M_1$  (with all but negligible probability over the randomness of the compiler and the randomness of the original and compiled circuit).

For randomized functionalities we require the output distributions of the original and the compiled circuits, to be statistically close.

#### 3.1 Security

We define security using the simulation paradigm. Our approach is similar in spirit to previous work on tamper-resilient circuit compilers (see, e.g., [52, 38]). In a nutshell, security is defined by comparing two experiments. In the first experiment, also called the real experiment, the circuit designer compiles the circuit and outsources the production of some of the components in the compiled circuit to a set of m untrusted manufacturers. A subset of size t of the manufacturers are malicious, and controlled by a monolithic adversary  $\mathcal{A}$ ; of course the circuit designer does not know which manufacturers are malicious and which ones are honest. During production,  $\mathcal{A}$  is allowed to completely change the outsourced circuit components under its control, whether by adding, removing or changing gates and/or wires. Later, the designer assembles the circuit by re-combining all the components (the outsourced ones and the ones built in-house). Finally,  $\mathcal{A}$  can access the assembled circuit in a black-box way, that is, it can observe inputs/outputs produced by running the assembled circuit (with some initial memory  $M_1$ ). In the second experiment, also called the ideal experiment, a simulator is given black-box access to the original circuit (initialized with initial memory  $M_1$ ). The goal of the simulator is to produce an output distribution which is indistinguishable from the one in the real experiment. In its most general

form, our definition allows the simulator to obtain a short leakage on the initial memory. This captures the (reasonable) scenario where the adversary, in the real experiment, could learn at most a short amount of information on the private memory.

**Real experiment.** The distribution  $\mathbf{Real}_{\mathcal{A},\Phi,\mathcal{C},\Gamma,M_1}(\lambda)$  is parameterized by the adversary  $\mathcal{A} = (\mathcal{A}_0,\mathcal{A}_1)$ , the set of corrupt manufacturers  $\mathcal{C}$ , the compiler  $\Phi$ , and the original circuit  $\Gamma$  with initial memory  $M_1$ .

- 1.  $(\widehat{\Gamma}, \mathsf{aux}) \leftarrow \Phi(\Gamma)$ : In the first step, the description of the original circuit  $\Gamma$  is given as input to the compiler  $\Phi$ ; the compiler outputs the description of the compiled circuit  $\widehat{\Gamma}$  plus the auxiliary information  $\mathsf{aux} := ((\widehat{\Gamma}_1, \dots, \widehat{\Gamma}_n), \mathcal{M}, (I_1, \dots, I_m))$  which is used to specify how the compiled circuit is split into sub-components, how the different sub-components are connected (via the mapping function  $\mathcal{M}$ ), and the subset of sub-components whose production is outsourced to each manufacturer (in the index sets  $I_j$ , for  $j \in [m]$ ).

- 2.  $(\{\widehat{\Gamma}'_i\}_{i\in I}, \tau) \leftarrow \mathcal{A}_0(1^{\lambda}, \{\langle \widehat{\Gamma}_i \rangle\}_{i\in I}, \langle \Gamma \rangle, \langle \widehat{\Gamma} \rangle)$ : The adversary is given as input the description of the components from the index set  $I = \bigcup_{j\in\mathcal{C}} I_j$ , the description of the original circuit  $\Gamma$ , the description of the compiled circuit  $\widehat{\Gamma}$ , and returns the modified components along with some value  $\tau$  that may contain some auxiliary state information.

- 3.  $\widehat{\Gamma}' := (\widehat{V}', \widehat{E}')$ : The compiled circuit  $\widehat{\Gamma}'$  is rebuilt by replacing the components  $(\widehat{\Gamma}_i)_{i \in I}$  with the modified components  $(\widehat{\Gamma}'_i)_{i \in I}$ , and by connecting the different components as specified by the mapping function  $\mathcal{M}$ .

- 4.  $\mathcal{A}_1^{\widehat{\Gamma}'[M_1](\cdot)}(1^{\lambda}, \tau)$ : Adversary  $\mathcal{A}_1$ , with auxiliary information  $\tau$ , is given oracle access to the rebuilt circuit  $\widehat{\Gamma}'$  with compiled private memory  $M_1$ .

**Simulation.** The distribution  $\mathbf{Ideal}_{\mathcal{S},\mathcal{A},\Phi,\mathcal{C},\Gamma,M_1,\ell}(\lambda)$  is parameterized by the simulator  $\mathcal{S}$ , the adversary  $\mathcal{A} = (\mathcal{A}_0,\mathcal{A}_1)$ , the compiler  $\Phi$ , the set of corrupt manufacturers  $\mathcal{C}$ , the original circuit  $\Gamma$  with initial memory  $M_1$ , and some value  $\ell \in \mathbb{N}$ .

- 1.  $f \leftarrow \mathcal{S}(1^{\lambda}, \langle \Gamma \rangle, \Phi, \mathcal{A}, \mathcal{C}, \ell)$ : Given as input a description of the original circuit, of the compiler and of the adversary, the subset of corrupt manufacturers, and the parameter  $\ell \in \mathbb{N}$ , the simulator specifies an arbitrary polynomial-time computable function  $f: \{0,1\}^* \to \{0,1\}^{\ell}$ .

- 2.  $\mathcal{S}^{\mathcal{A},\Gamma[M_1](\cdot)}(1^{\lambda},L)$ : The simulator takes as input leakage  $L=f(M_1)$ , and is given oracle access to adversary  $\mathcal{A}=(\mathcal{A}_0,\mathcal{A}_1)$  and to the original circuit  $\Gamma$  with private memory  $M_1$ . We remark that the simulator is restricted to be fully black-box. In particular,  $\mathcal{S}$  only accesses the modified sub-components returned by  $\mathcal{A}_0$  in a black-box way (i.e., without knowing their description).

**Definition 4** (Security). We say that a  $(\rho, m)$ -outsourcing circuit compiler  $\Phi$  is  $(\ell, t)$ -secure if the following conditions are met.

- (i) Non-triviality:  $\rho < 1$ , for sufficiently large values of  $\lambda \in \mathbb{N}$ .

- (ii) Simulatability: For all  $C \subseteq [m]$  of size at most t and for all PPT adversaries A, for all circuits  $\Gamma$ , there exists a simulator S with running time  $poly(|A|, |\Gamma|)$ , such that for all initial values of the memory  $M_1 \in \{0, 1\}^*$ ,

$$\left\{\mathbf{Real}_{\mathcal{A},\Phi,\mathcal{C},\Gamma,M_1}(\lambda)\right\}_{\lambda\in\mathbb{N}}\approx_c \left\{\mathbf{Ideal}_{\mathcal{S},\mathcal{A},\Phi,\mathcal{C},\Gamma,M_1,\ell}(\lambda)\right\}_{\lambda\in\mathbb{N}}.$$

In the above definitions the adversary is allowed to modify each  $\widehat{\Gamma}_i$  arbitrarily, i.e., there is no restriction on the edges and nodes of  $\widehat{\Gamma}'_i$ , as long as the input and output gates enable

connectivity with the remaining components. We also allow arbitrary modifications of the circuit memory (cf. Remark 1). Observe that, the above definition is only interesting for small values of  $\ell$  (as, e.g., it becomes trivial in case  $\ell = |M_1|$ ). The non-triviality condition demands that the ratio between the size of the sub-components of the compiled circuit built in-house, and the size of the original circuit, should be less than one. This is necessary, as otherwise a manufacturer could simply produce the entire circuit by itself, without the help of any off-shore facility. Clearly, the smaller  $\rho$  is, the better, as this means that a large fraction of the original circuit production can be outsourced.

#### Undetectability 3.2

We formally define what it means for an adversarial strategy to be undetectable by all black-box polynomial-time tests. Informally, this means that it is hard to distinguish the output of the original circuit from the output of the compiled circuit (after the outsourced sub-components have been maliciously modified). Importantly, the latter has to hold even if the testing strategy knows the initial content of the private memory and the description of all sub-components in the compiled circuit.

For simplicity, we give the definition in the case of a single manufacturer (i.e., m=1); a generalization to the case  $m \geq 2$  is immediate. The formalization borrows ideas from similar definitions in the setting of subversion and algorithm-substitution attacks [12, 11].

**Definition 5.** Let  $\Phi$  be an outsourcing circuit compiler, and  $\Gamma$  be a circuit. We say that an adversary A is undetectable for  $\Gamma$  w.r.t.  $\Phi$  if for all PPT algorithms Test there exists a negligible function  $\nu: \mathbb{N} \to [0,1]$  such that, for all initial values of the memory  $M_1$ , we have that  $\mathbb{P}[\text{Test }wins] \leq 1/2 + \nu(\lambda)$  in the following game:

- 1. The challenger samples  $b \leftarrow \$ \{0,1\}$ , runs  $(\widehat{\Gamma}, (\widehat{\Gamma}_1, \dots, \widehat{\Gamma}_n), \mathcal{M}, I) \leftarrow \Phi(\Gamma)$ , and returns  $(M_1, \dots, \widehat{\Gamma}_n)$  $\langle \Gamma \rangle, \langle \widehat{\Gamma} \rangle, (\langle \widehat{\Gamma}_1 \rangle, \dots, \langle \widehat{\Gamma}_n \rangle), \mathcal{M}, I)$  to Test. 2. Let  $\widehat{\Gamma}'$  be the circuit implicitly defined by the sub-components  $\{\widehat{\Gamma}_i\}_{i \in [n] \setminus I} \cup \{\widehat{\Gamma}_i'\}_{i \in I}$  together

- with the mapping function  $\mathcal{M}$ , where  $\{\widehat{\Gamma}'_i\}_{i\in I} \leftarrow \mathcal{A}(1^{\lambda}, \{\langle \widehat{\Gamma}_i \rangle\}_{i\in I}, \langle \Gamma \rangle, \langle \widehat{\Gamma} \rangle).$

- 3. Algorithm Test can ask polynomially many queries of the type  $X_i$ ; upon input such query, the answer from the challenger depends on the value of the bit b:

- In case b = 0, the output is  $(Y_i, M_{i+1}) \leftarrow \Gamma[M_i](X_i)$ .

- In case b=1, the output is  $(Y_i, M_{i+1}) \leftarrow \widehat{\Gamma}'[M_i](X_i)$ .

- 4. Algorithm Test outputs a bit b', and wins iff b' = b.

As we mention above, we allow the adversary to completely modify the circuit memory, thus in the above definition,  $\widehat{\Gamma}'$  can just omit  $M_i$  and compute over an adversarially chosen  $\widehat{M}_i$ . In this setting, the manufacturer can execute  $\widehat{\Gamma}'[M_i](X_i)$  (i.e., for memory value  $M_i$ ), however the circuit may perform computation over an arbitrary memory value  $M_i$ , that the manufacturer has no access to.

#### 4 Case Study I: Single Manufacturer

In this section we build secure outsourcing compilers that work for any circuit, in the presence of a single malicious manufacturer. The compilers are based on any verifiable computation (VC) scheme (satisfying certain properties) for the function computed by the underlying circuit. We start by recalling the basic definitions for VC schemes in Section 4.1. In Section 4.2, we describe our first compiler, which requires a VC scheme satisfying input privacy. In Section 4.3, we describe our second compiler, which can be instantiated with non-input-private VC schemes;

our second compiler requires that once the first invalid output is produced, the compiled circuit overwrites its entire memory with the all-zero string and "self-destructs." As we will show, this restriction is necessary. We refer the reader to Section 6 for concrete instantiations of our compilers based on state-of-the-art research on verifiable computation.

## 4.1 Prelude: Verifiable Computation

A verifiable computation scheme allows for a client to outsource the computation of a function to a (untrusted) server; the server produces a proof of correctness along with the output of the function. The client checks the correctness proof to decide whether the output provided by the server is accepted or not.

**Definition 6** (Verifiable Computation). Let  $\mathcal{F}$  be a function. A VC scheme  $\mathcal{VC} = (KeyGen, ProbGen, Compute, Verify) for function <math>\mathcal{F}$  consists of the algorithms described below.

- $(SK, PK) \leftarrow \text{KeyGen}(\mathcal{F}, \lambda)$ : The (randomized) key generation algorithm takes as input the function  $\mathcal{F}$  and the security parameter  $\lambda$ , and outputs a public key PK and a secret key SK.

- $(\Sigma_X, VK_X) \leftarrow \mathsf{ProbGen}_{SK}(X)$ : The (randomized) problem generation algorithm takes as input the value X and uses the secret key SK to compute an encoding  $\Sigma_X$  of X and a secret verification key  $VK_X$ .

- $\Sigma_Y \leftarrow \mathsf{Compute}_{PK}(\Sigma_X)$ : The (deterministic) compute algorithm takes as input the encoded value  $\Sigma_X$  and uses the public key PK to compute an encoding of  $Y = \mathcal{F}(X)$ .

- $Y \leftarrow \mathsf{Verify}_{SK}(VK_X, \Sigma_Y)$ : The (deterministic) verify algorithm takes as input the verification key  $VK_X$  and the value  $\Sigma_Y$ ; it uses the secret key SK and  $VK_X$  to compute a value  $Y \in \{0,1\}^* \cup \{\bot\}$ , where symbol  $\bot$  denotes that the algorithm rejects the value  $\Sigma_Y$ .

A typical VC scheme needs to satisfy some properties that we formalize below.

Correctness. A VC scheme is correct if the ProbGen algorithm produces problem instances that allow for a honest server to successfully compute values  $\Sigma_Y$  such that  $Y = \mathcal{F}(X)$ .

**Definition 7** (Correctness for VC schemes). Let VC be a VC scheme for some function F. We say that VC is correct if for all values X, the following holds:

$$\mathbb{P} \left[ Y = \mathcal{F}(X) : \begin{array}{c} (SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda); (\Sigma_X, VK_X) \leftarrow \mathsf{ProbGen}_{PK}(X) \\ \Sigma_Y \leftarrow \mathsf{Compute}_{PK}(\Sigma_X); Y \leftarrow \mathsf{Verify}_{SK}(VK_X, \Sigma_Y) \end{array} \right] = 1.$$

**Soundness.** A VC scheme is sound if no malicious server can "trick" a client into accepting an incorrect output, i.e, some value Y such that  $Y \neq \mathcal{F}(X)$ . We require this to hold even in the presence of so-called verification queries [39].

**Definition 8** (Soundness for VC schemes). Let  $\mathcal{VC}$  be a VC scheme for some function  $\mathcal{F}$ . We say that  $\mathcal{VC}$  is sound if for all PPT adversaries  $\mathcal{A}$  there exists some negligible function  $\nu: \mathbb{N} \to [0,1]$  such that  $\mathbb{P}[\mathcal{A} \text{ wins}] \leq \nu(\lambda)$  in the following game.

- 1. The challenger runs  $(SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda)$  to obtain the secret key SK and the public key PK, and sends PK to A.

- 2. Adversary A can make the following two types of queries to the challenger, that can be carried out polinomially many times in any order and in an adaptive way.

- (i) Adversary  $\mathcal{A}$  can specify an input  $X_i$ ; the challenger computes  $(VK_i, \Sigma_i) \leftarrow \mathsf{ProbGen}_{SK}(X_i)$  and sends  $\Sigma_i$  to  $\mathcal{A}$ .

- (ii) Adversary A can specify verification queries  $(i, \hat{\Sigma})$ ; the challenger computes  $Y = \mathsf{Verify}_{SK}(VK_i, \hat{\Sigma})$  and returns 1 if  $Y \neq \bot$ , otherwise returns 0.

- 3. Eventually, adversary  $\mathcal{A}$  will output a pair  $(i^*, \Sigma^*)$ ; we say that  $\mathcal{A}$  wins iff  $Y^* \neq \mathcal{F}(X_{i^*})$  and  $Y^* \neq \bot$ , such that  $Y^* = \mathsf{Verify}_{SK}(VK_{i^*}, \Sigma^*)$ .

**Input privacy.** A VC scheme is input-private if no server can learn the input value X that the function is being computed on.

**Definition 9** (Input-privacy for VC schemes). Let  $\mathcal{VC}$  be a VC scheme for some function  $\mathcal{F}$ . We say that  $\mathcal{VC}$  is input private if for all PPT adversaries  $\mathcal{A}$  there exists some negligible function  $\nu: \mathbb{N} \to [0,1]$  such that  $\mathbb{P}[\mathcal{A} \text{ wins}] - \frac{1}{2} \leq \nu(\lambda)$  in the following game.

- 1. The challenger runs  $(SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda)$  to obtain the secret key SK and the public key PK, and sends PK to A.

- 2. Adversary A can make the following two types of queries to the challenger, that can be carried out polinomially many times in any order and in an adaptive way.

- (i) Adversary A can specify an input  $X_i$ ; the challenger computes  $(VK_i, \Sigma_i) \leftarrow \operatorname{\mathsf{ProbGen}}_{SK}(X_i)$  and sends  $\Sigma_i$  to A.

- (ii) Adversary  $\mathcal{A}$  can specify verification queries  $(i,\hat{\Sigma})$ ; the challenger computes  $Y = \mathsf{Verify}_{SK}(VK_i,\hat{\Sigma})$  and returns 1 if  $Y \neq \bot$ , otherwise returns 0.

- 3. Adversary A chooses two values  $X_0$  and  $X_1$  and sends them to the challenger.

- 4. The challenger samples a random bit  $b \leftarrow \$\{0,1\}$  and computes  $(VK^*, \Sigma^*) \leftarrow \mathsf{ProbGen}_{SK}(X_b)$  forwarding  $\Sigma^*$  to  $\mathcal{A}$ .

- 5. Adversary A can still specify to the challenger the queries described above, including special verification queries for the verification key  $VK^*$ .

- 6. Finally, A outputs a bit b'; we say that A wins if and only if b = b'.

Outsourceability. A VC scheme is outsourceable if the time to encode the input plus the time to run a verification is smaller than the time to compute the function itself.

**Definition 10** (Outsourceability for VC schemes). A VC scheme can be outsourced if it allows efficient generation and efficient verification. This means that for any X and any  $\Sigma_Y$  the time (or circuit size) required for  $\mathsf{ProbGen}_{SK}(X)$  plus the time (or circuit size) required for  $\mathsf{Verify}_{SK}(VK,\Sigma_Y)$  is o(T), where T is the time (or circuit size) required to compute  $\mathcal{F}(X)$ .

VC without input-privacy. The above definitions can be adapted to cast VC schemes without input-privacy, i.e schemes where the server is allowed to learn the input value X used by the client. For such VC schemes, algorithm ProbGen returns the value X in the clear along with the secret verification key  $VK_X$ ; the correctness, soundness and outsourceability definitions can easily be adapted to this setting.

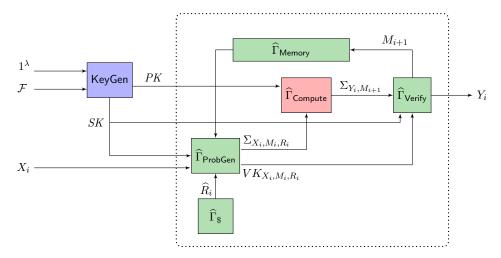

#### 4.2 Compiler based on Input-Private VC

In this section we construct an outsourcing circuit compiler by using a VC scheme that satisfies the properties of correctness, soundness, input-privacy and outsourceability. Let  $\Gamma$  be a circuit; the idea is to invoke a VC scheme for the function  $\mathcal{F}$  corresponding to the functionality computed by  $\Gamma$ . The compiled circuit will consist of four main components  $\widehat{\Gamma}_{\mathsf{ProbGen}}$ ,  $\widehat{\Gamma}_{\mathsf{Compute}}$ ,  $\widehat{\Gamma}_{\mathsf{Verify}}$ , and  $\widehat{\Gamma}_{\$}$ . The first three components are the circuit representations of the algorithms ProbGen, Compute and Verify corresponding to the underlying VC scheme; such components hard-wire

keys (SK, PK) generated using algorithm KeyGen. The fourth component samples the random coins  $R_i$  to be used during each invocation of the circuit. The production of component  $\widehat{\Gamma}_{\mathsf{Compute}}$  will then be outsourced to a single untrusted facility, whereas all other components are built in-house (as their implementation needs to be trusted). Notice that the implementation of algorithm KeyGen can be thought of as a pre-processing stage that runs only once (and could be carried out in software).

An important observation is that the size of circuit  $\widehat{\Gamma}_{\text{Verify}}$  and  $\widehat{\Gamma}_{\text{ProbGen}}$  is independent, and much smaller, than the size of circuit  $\widehat{\Gamma}_{\text{Compute}}$ . As discussed in the introduction, the size of  $\widehat{\Gamma}_{\$}$  can also be considered to be constant (consisting only of a few gates). We describe our first compiler below in more details.

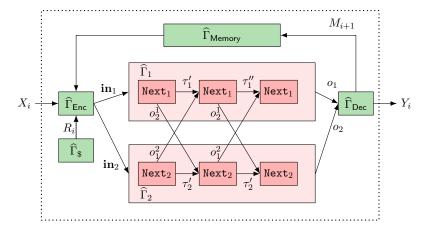

The compiler  $\Phi^1_{\mathcal{VC}}$ . Let  $\Gamma$  be a circuit, and  $\mathcal{VC} = (\text{KeyGen}, \text{ProbGen}, \text{Compute}, \text{Verify})$  be a VC scheme for the function  $\mathcal{F}$  implemented by  $\Gamma$ . Our first compiler is depicted in Fig. 2, and can be described as follows.

- 1. First run  $(SK, PK) \leftarrow \text{KeyGen}(\mathcal{F}, \lambda)$  once, obtaining the pair of keys (SK, PK).

- 2. Let  $\widehat{\Gamma}_{\mathsf{Memory}}$  be a circuit component consisting only of memory gates, as needed by the original circuit  $\Gamma$ , storing the initial value of the private memory  $M_1$ .

- 3. Let  $\widehat{\Gamma}_{\$}$  be a circuit outputting random coins  $\widehat{R}_i$  (as needed in each invocation of the compiled circuit).

- 4. Define a component for each function ProbGen, Compute and Verify of the VC scheme as explained below.

- $\widehat{\Gamma}_{\mathsf{ProbGen}}$ : This component embeds the secret key SK, and it takes three inputs; the input  $X_i$ , the (current) private memory  $M_i$ , and random coins  $\widehat{R}_i := R_i || R_i'$ . It implements function  $\mathsf{ProbGen}_{SK}(X_i || M_i || R_i; R_i')$ , that produces two outputs: an encoding  $\Sigma_{X_i, M_i, R_i}$ , and a verification key  $VK_{X_i, M_i, R_i}$ .

- $\widehat{\Gamma}_{\mathsf{Compute}}$ : This component embeds the public key PK, and it takes as input an encoding. It implements the function  $\mathsf{Compute}_{PK}(\Sigma_{X_i,M_i,R_i})$ , that produces the encoding  $\Sigma_{Y_i,M_{i+1}}$  of  $(Y_i,M_{i+1}) = \mathcal{F}(X_i,M_i;R_i)$  as output.

- $\widehat{\Gamma}_{\mathsf{Verify}}$ : This component embeds the secret key SK, and it takes two inputs; the encoding  $\Sigma_{Y_i,M_{i+1}}$  and the verification key  $VK_{X_i,M_i,R_i}$ . It implements function  $\mathsf{Verify}_{SK}(VK_{X_i,M_i,R_i},\Sigma_{Y_i,M_{i+1}})$ , to produce the output  $Y_i \in \{0,1\}^* \cup \{\bot\}$ , and eventually update the circuit private memory to  $M_{i+1}$ .

- 5. The output of  $\Phi^1_{\mathcal{VC}}$  is defined as follows. The first output is a (description of the) compiled circuit  $\widehat{\Gamma}$  as depicted in Fig. 2. The auxiliary information aux consists of the components  $\widehat{\Gamma}_{\mathsf{ProbGen}}, \widehat{\Gamma}_{\mathsf{Compute}}, \widehat{\Gamma}_{\mathsf{Verify}}, \widehat{\Gamma}_{\mathsf{Memory}}, \text{ and } \widehat{\Gamma}_{\$}$ , the mapping function  $\mathcal{M}$  that describes the physical connections between such components (i.e., the arrows in Fig. 2), and the index set  $I = \{2\}$  specifying the component  $\widehat{\Gamma}_{\mathsf{Compute}}$  as a candidate for outsourcing.

Remark 1 (On outsourcing memory gates.). In the compiler depicted in Fig. 2,  $\widehat{\Gamma}_{\mathsf{Memory}}$  is being built in-house. In order to outsource private memory to a potentially malicious manufacturer we can modify the above compiler as follows: instead of storing in  $\widehat{\Gamma}_{\mathsf{Memory}}$  the value  $M_i$  in plaintext, we store  $C \leftarrow \mathsf{AE}_{SK'}(M_i)$ , where C is the encryption of  $M_i$  using a symmetric, semantically secure authenticated encryption scheme, with secret key SK'. Moreover,  $\widehat{\Gamma}_{\mathsf{ProbGen}}$  is modified such that when receiving the private memory value C, it first decrypts it using  $\mathsf{SK'}$  and then executes the original circuit  $\widehat{\Gamma}_{\mathsf{ProbGen}}$  on the resulting plaintext. We also substitute  $\widehat{\Gamma}_{\mathsf{Verify}}$  so that it outputs the encryption of  $M_{i+1}$ , under  $\mathsf{SK'}$ . This modification enables the simulator to execute the circuit using the all-zeros bit-string as the initial memory value, and security follows

Figure 2: The description of compilers  $\Phi^1_{\mathcal{VC}}$ . The green components (i.e.,  $\widehat{\Gamma}_{\mathsf{ProbGen}}$ ,  $\widehat{\Gamma}_{\mathsf{Verify}}$ , and  $\widehat{\Gamma}_{\$}$ ) need to be built in-house, while the production of the red component (i.e.,  $\widehat{\Gamma}_{\mathsf{Compute}}$ ) can be outsourced; the blue component (i.e., KeyGen) is built only once (not necessarily in hardware). The dotted line depicts the circuit boundaries.

by the semantic security of the encryption scheme. Finally, whenever the decryption of C gives  $\bot$  the circuit output is  $\bot$ .

The theorem below, states that the compiler from Fig. 2 satisfies our strongest security notion (i.e., Definition 4 with  $\ell=0$ ), provided that the underlying VC scheme is correct, sound, input-private, and outsourceable.

**Theorem 1.** Let  $\Gamma$  be an arbitrary circuit and let  $\mathcal{VC}$  be a verifiable computation scheme for the function  $\mathcal{F}$  computed by  $\Gamma$ , satisfying the properties of correctness, soundness, input-privacy and outsourceability. Then the compiler  $\Phi^1_{\mathcal{VC}}$  is a correct, (0,1)-secure (o(1),1)-outsourcing circuit compiler.

*Proof.* We start by showing that the outsourcing ratio parameter  $\rho$  of the compiler  $\Phi^1_{\mathcal{VC}}$  is always smaller than 1, for sufficiently large values of the security parameter  $\lambda$ , thus meeting the non-triviality condition.

**Claim 1.**  $\rho = o(1)$ .

*Proof.* The non-triviality requirement from Definition 4 states that

$$\rho = \frac{|\widehat{\Gamma}_{\mathsf{ProbGen}}| + |\widehat{\Gamma}_{\mathsf{Verify}}| + |\widehat{\Gamma}_{\$}| + |\widehat{\Gamma}_{\mathsf{Memory}}|}{|\Gamma|} < 1.$$

The claim is that  $\rho = o(1)$ . By the outsourceability property of the  $\mathcal{VC}$  scheme we know that  $|\widehat{\Gamma}_{\mathsf{ProbGen}}| + |\widehat{\Gamma}_{\mathsf{Verify}}| = o(|\Gamma|)$ , i.e.,  $\lim_{\lambda \to \infty} \frac{|\widehat{\Gamma}_{\mathsf{ProbGen}}| + |\widehat{\Gamma}_{\mathsf{Verify}}|}{|\Gamma|} = 0$ . By substituting the expression for  $\rho$ , and by using the fact that the size of  $\widehat{\Gamma}_{\$}$  can assumed to be constant and that the original and the compiled circuit contain the same number of memory gates, we obtain:

$$\lim_{\lambda \to \infty} \frac{(|\widehat{\Gamma}_{\mathsf{Prob}\mathsf{Gen}}| + |\widehat{\Gamma}_{\mathsf{Verify}}| + |\widehat{\Gamma}_{\$}| + |\widehat{\Gamma}_{\mathsf{Memory}}|)/|\Gamma|}{1} = 0.$$

This shows that function  $\rho$  converges to 0. As the size of each component is monotonously increasing with the security parameter, for sufficiently large  $\lambda$ , the outsourcing ratio  $\rho$  will always be smaller than 1, as desired.

## Claim 2. The compiler $\Phi^1_{\mathcal{VC}}$ satisfies correctness.

*Proof.* The correctness of the compiler  $\Phi^1_{\mathcal{VC}}$  follows immediately from the correctness property of the underlying VC scheme.

We proceed to prove security of  $\Phi^1_{\mathcal{VC}}$ . We need to build a simulator  $\mathcal{S}$  that is able to "fake" experiment **Real** for all adversaries  $\mathcal{A}$ , for all circuits  $\Gamma$ , and for all initial memory values  $M_1$ . A description of the simulator follows.

- Run the compiler  $\Phi^1_{\mathcal{VC}}(\Gamma)$  supplying (a description of) the original circuit  $\Gamma$ ; the output is (a description of) the compiled circuit  $\widehat{\Gamma}$ , and the auxiliary information aux :=  $((\widehat{\Gamma}_{\mathsf{ProbGen}}, \widehat{\Gamma}_{\mathsf{Compute}}, \widehat{\Gamma}_{\mathsf{Verify}}, \widehat{\Gamma}_{\mathsf{Memory}}, \widehat{\Gamma}_{\$}), \mathcal{M}, \{2\}).$

- The description of component  $\widehat{\Gamma}_{\mathsf{Compute}}$  is sent to adversary  $\mathcal{A}$  together with the descriptions of  $\Gamma$  and  $\widehat{\Gamma}$ .

- Adversary  $\mathcal{A}$  produces the component  $\widehat{\Gamma}'_{\mathsf{Compute}}$  (that may be malicious) and sends it to the simulator; the circuit  $\widehat{\Gamma}'$  is assembled using the components  $(\widehat{\Gamma}_{\mathsf{ProbGen}}, \widehat{\Gamma}'_{\mathsf{Compute}}, \widehat{\Gamma}_{\mathsf{Verify}}, \widehat{\Gamma}_{\mathsf{Memory}}, \widehat{\Gamma}_{\$})$ , via the mapping function  $\mathcal{M}$ .

- Upon input  $X_i$  from  $\mathcal{A}$ , run  $(Y_i, \widetilde{M}_{i+1}) \leftarrow \widehat{\Gamma}'[0^{\mu}](X_i)$ , where  $\mu := |M_1|$ ; if  $Y_i = \bot$  then forward  $\bot$  to  $\mathcal{A}$ , otherwise query  $X_i$  to oracle  $\Gamma[M_1](\cdot)$  and forward the output to  $\mathcal{A}$ .

Let us write **R** and **S** for the distribution of the random variables in experiment **Real** and **Ideal** of Definition 4. Recall that these variables are parametrized by adversary  $\mathcal{A}$ , simulator  $\mathcal{S}$ , initial memory  $M_1$ , compiler  $\Phi^1_{\mathcal{VC}}$ , and circuit  $\Gamma$ , but we omit explicitly writing all these parameters to simplify the exposition. We consider a new experiment  $\mathbf{R}'$  that is exactly the same as  $\mathbf{R}$ , except that for all queries  $X_i$  such that  $(Y_i', M_{i+1}) \leftarrow \widehat{\Gamma}'[M_i](X_i)$  with  $Y_i' \neq \bot$ , the experiment computes  $(Y_i, M_{i+1}) \leftarrow \mathcal{F}(X_i, M_i)$  and outputs  $Y_i$ .

The claim below shows that experiment  $\mathbf{R}$  and  $\mathbf{R}'$  are computationally indistinguishable.

Claim 3. For all PPT adversaries  $\mathcal{A}$ , and for all PPT distinguishers  $\mathcal{D}$ , there exists a negligible function  $\nu : \mathbb{N} \to [0,1]$  such that  $\Delta^{\mathcal{D}}(\mathbf{R}; \mathbf{R}') \leq \nu(\lambda)$ .

Proof. Let  $q \in \text{poly}(\lambda)$  be the number of input queries asked by  $\mathcal{A}$  to its oracle, and let us define an event W that becomes true whenever there is some index  $i^* \in [q]$  such that in experiment  $\mathbf{R}'$  we have  $Y_{i^*} \neq Y'_{i^*}$ . Then, by Lemma 1, we have that  $\Delta^{\mathcal{D}}(\mathbf{R}; \mathbf{R}') \leq \Delta(\mathbf{R}; \mathbf{R}' | \neg W) + \mathbb{P}[W]$ . Note that the distributions  $\mathbf{R}$  and  $\mathbf{R}'$ , conditioned on event W not happening are exactly the same. We proceed to show that the probability of event W is negligible.

Let us assume that there exists some circuit  $\Gamma$ , some initial memory  $M_1$  and a PPT adversary  $\mathcal{A}$  provoking event W with non-negligible probability. We build a PPT adversary  $\mathcal{A}'$  that uses  $\mathcal{A}$  in order to break the soundness property of the underlying VC scheme (cf. Definition 8).

## Adversary $\mathcal{A}'(M_1, \mathcal{F}, \Gamma, \Phi)$ :

- 1. Receive PK from the challenger, where  $(SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda)$ .

- 2. Run  $(\widehat{\Gamma}, M_1, \mathsf{aux}) \leftarrow \Phi(\Gamma, M_1)$ , and send (the description of) circuit components  $(\widehat{\Gamma}_{\mathsf{Compute}}, \Gamma, \widehat{\Gamma})$  to  $\mathcal{A}$ . Adversary  $\mathcal{A}$  produces the modified component  $\widehat{\Gamma}'_{\mathsf{Compute}}$  and sends it to  $\mathcal{A}'$ .

- 3. For all  $i \in [q]$ , upon input query  $X_i$  from  $\mathcal{A}$ , do the following.

$<sup>^{3}</sup>$ We also omit to mention the set of corrupt manufacturers C, as in this case there is a single malicious manufacturer.

- Sample random coins  $R_i$ , create the string  $Z_i := X_i ||M_i||R_i$  and send it to the challenger as an encoding query. In response, the challenger computes  $(VK_{Z_i}, \Sigma_{Z_i}) \leftarrow \mathsf{ProbGen}_{SK}(Z_i)$  and sends back the encoding  $\Sigma_{Z_i}$  to  $\mathcal{A}'$ .

- Run  $\Sigma_{Y'_i,M_{i+1}} = \widehat{\Gamma}'_{\mathsf{Compute}}(PK,\Sigma_{Z_i})$  and send a query  $(i,\Sigma_{Y'_i,M_{i+1}})$  to the challenger; the answer from the challenger is a verification bit d. If d=0, then reply with  $\bot$ , otherwise compute  $(Y_i,M_{i+1}) = \mathcal{F}(M_i,X_i;R_i)$  and reply with  $Y_i$ .

- 4. Finally, pick a random  $i^* \in [q]$  and output the pair  $(i^*, \Sigma_{Y'_{:*}})$ .

For the analysis, we note that the above simulation is perfect. In particular the outputs seen by  $\mathcal{A}$  retain exactly the same distribution as in experiment  $\mathbf{R}'$ . Now  $\mathcal{A}$  provokes event W with non-negligible probability, so there exists some index  $i^* \in [q]$  such that  $Y_{i^*}$  is different from  $Y'_{i^*}$  where  $(Y'_{i^*}, M_{i^*+1}) \leftarrow \widehat{\Gamma}'[M_{i^*}](X_{i^*})$ . Since  $\mathcal{A}'$  guesses the right index  $i^*$  with probability 1/q, we obtain that  $\mathcal{A}'$  wins the soundness game with non-negligible probability  $\frac{1}{q} \cdot \mathbb{P}[W]$ . This contradicts the soundness property of the underlying VC scheme, and thus concludes the proof of the claim.

Claim 4. For all PPT adversaries  $\mathcal{A}$ , and for all PPT distinguishers  $\mathcal{D}$ , there exists a negligible function  $\nu' : \mathbb{N} \to [0,1]$  such that  $\Delta^{\mathcal{D}}(\mathbf{R}';\mathbf{S}) \leq \nu'(\lambda)$ .

*Proof.* Let  $q \in \text{poly}(\lambda)$  be the number of input queries asked by  $\mathcal{A}$  to its oracle. For an index  $i \in [q]$  consider the hybrid experiment  $\mathbf{H}_i$  that answers the first i queries as in  $\mathbf{R}'$  and all the subsequent queries as in  $\mathbf{S}$ . We note that experiments  $\mathbf{H}_{i-1}$  and  $\mathbf{H}_i$  only differ in how the output is computed in position i, and that  $\mathbf{H}_0 \equiv \mathbf{S}$  and  $\mathbf{H}_q \equiv \mathbf{R}'$ .

We now show that for all circuits  $\Gamma$ , all initial memories  $M_1$ , and all PPT adversaries  $\mathcal{A}$ , each pair of adjacent hybrids  $\mathbf{H}_{i-1}$  and  $\mathbf{H}_i$  are computationally indistinguishable. Fix some  $i \in [0, q]$ , and assume that there exists some circuit  $\Gamma$ , some initial memory  $M_1$ , a PPT adversary  $\mathcal{A}$ , and a PPT distinguisher  $\mathcal{D}$  that distinguishes between the pair of hybrids  $\mathbf{H}_{i-1}$  and  $\mathbf{H}_i$ . We build an adversary  $\mathcal{A}'$  that uses  $(\mathcal{A}, \mathcal{D})$  in order to break the input-privacy property of the underlying VC scheme (cf. Definition 9).

## Adversary $\mathcal{A}'(M_1, \mathcal{F}, \Gamma, \Phi, i)$ :

- 1. Receive PK from the challenger, where  $(SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda)$ .

- Run (Γ̂, aux) ← Φ(Γ), and send (the description of) circuit components (Γ̂<sub>Compute</sub>, Γ, Γ̂) to A. Adversary A produces the modified component Γ̂'<sub>Compute</sub> and sends it to A'.

- 3. Upon input query  $X_j$  from  $\mathcal{D}$ , such that  $j \neq i$ , answer as follows:

- Sample random coins  $R_j$ . If j < i create the string  $Z_j := X_j ||M_j||R_j$ , else create the string  $Z_j := X_j ||0^{\mu}||R_j$ .

- Send  $Z_j$  to the challenger as an encoding query. In response the challenger computes  $(VK_{Z_j}, \Sigma_{Z_j}) \leftarrow \mathsf{ProbGen}_{SK}(Z_j)$  and sends  $\Sigma_{Z_j}$  to  $\mathcal{A}'$ .

- Run  $\Sigma_{Y_j,M_{j+1}} = \widehat{\Gamma}'_{\mathsf{Compute}}(PK,\Sigma_{Z_j})$ , and send a verification query  $(j,\Sigma_{Y_j,M_{j+1}})$  to the challenger.

- The challenger replies with a decision bit d; if d = 0 then return  $\perp$ , otherwise compute  $(Y_j, M_{j+1}) = \mathcal{F}(M_j, X_j; R_j)$  and return  $Y_j$ .

- 4. Upon input query  $X_i$  from  $\mathcal{A}$ , answer as follows:

- Sample random coins  $R_i$ , and create two strings  $Z_0^* := X_i ||M_i|| R_i$  and  $Z_1^* := X_i ||0^{\mu}|| R_i$ .

- Send  $Z_0^*$  and  $Z_1^*$  to the challenger as challenge inputs for the input-privacy game; the challenger replies with  $\Sigma_{Z^*}$  (which corresponds to the encoding of either  $Z_0^*$  or  $Z_1^*$ ).

- Run  $\Sigma_{Y^*} = \widehat{\Gamma}'_{\mathsf{Compute}}(PK, \Sigma_{Z^*})$  and send a verification query  $(i, \Sigma_{Y^*})$  to the challenger; the challenger replies with a decision bit d. If d = 0 then return  $\bot$ , otherwise compute  $(Y_i, M_{i+1}) = \mathcal{F}(M_i, X_i; R_i)$  and return  $Y_i$ .

- 5. Finally, output whatever  $\mathcal{D}$  outputs.

For the analysis, we note that the above simulation is perfect. In particular, depending on  $Z^*$  being either an encoding of  $Z_0^*$  or  $Z_1^*$  the view of  $(\mathcal{A}, \mathcal{D})$  is identical to the view in either experiment  $\mathbf{H}_{i-1}$  or  $\mathbf{H}_i$ . Hence,  $\mathcal{A}'$  retains the same advantage as  $(\mathcal{A}, \mathcal{D})$  which contradicts input-privacy of the underlying VC scheme. We conclude that there exist negligible functions  $\nu', \nu'' : \mathbb{N} \to [0, 1]$  such that

$$\Delta^{\mathcal{D}}(\mathbf{R}'; \mathbf{S}) \leq \sum_{i=1}^{q} \Delta^{\mathcal{D}}(\mathbf{H}_{i-1}; \mathbf{H}_i) \leq q \cdot \nu'(\lambda) \leq \nu''(\lambda),$$

as desired.  $\Box$

The statement now follows by Claim 3 and Claim 4, and by the triangle inequality, as

$$\Delta^{\mathcal{D}}(\mathbf{R}; \mathbf{S}) \le \Delta^{\mathcal{D}}(\mathbf{R}; \mathbf{R}') + \Delta^{\mathcal{D}}(\mathbf{R}'; \mathbf{S}) \le \nu(\lambda) + \nu'(\lambda).$$

This finishes the proof.

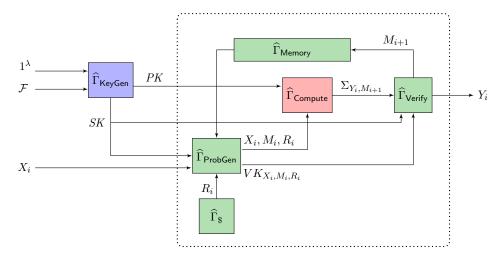

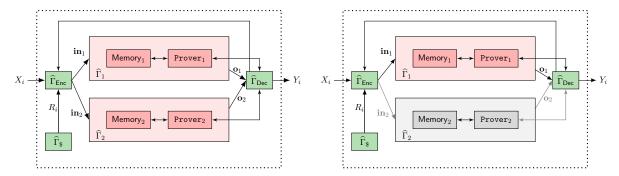

## 4.3 Compiler based on VC without Input Privacy

In this section, we construct an outsourcing circuit compiler by using any VC scheme that satisfies the properties of correctness, soundness and outsourceability. The construction follows the same ideas of compiler  $\Phi^1_{\mathcal{VC}}$  (cf. Section 4.2), with two main differences. First, as we rely on a VC scheme without input-privacy, the component  $\widehat{\Gamma}_{\mathsf{ProbGen}}$  now outputs the values  $X_i$ ,  $M_i$ ,  $R_i$  in the clear. Second, the component  $\widehat{\Gamma}_{\mathsf{Verify}}$  needs to implement a special "self-destruct" feature: The first time the component returns the special symbol  $\bot$ , the private memory is overwritten with the all-zero string.

As we argue later in this section, the self-destruct feature is *necessary*, in that, without such a feature, generic attacks against our compiler are possible, possibly exposing the entire private memory in an undetectable manner.

The compiler  $\Phi^2_{\mathcal{VC}}$ . Let  $\Gamma$  be a circuit, and  $\mathcal{VC} = (\text{KeyGen}, \text{ProbGen}, \text{Compute}, \text{Verify})$  be a VC scheme for the function  $\mathcal{F}$  implemented by  $\Gamma$ . The description of the compiler  $\Phi^2_{\mathcal{VC}}(\Gamma)$  can be found in Fig. 3. The case of memory outsourcing is identical to that of the first compiler and we refer the reader to Remark 1. The theorem below establishes that such a compiler is secure, provided that the original circuit to be produced is resilient to a logarithmic (in the security parameter) amount of leakage on its private memory.

**Theorem 2.** Let  $\Gamma$  be an arbitrary circuit and let  $\mathcal{VC}$  be a verifiable computation scheme for the function  $\mathcal{F}$  computed by  $\Gamma$ , satisfying the properties of correctness, soundness and outsourceability. Then the compiler  $\Phi^2_{\mathcal{VC}}$  is a correct  $(\log(q) + 1, 1)$ -secure (o(1), 1)-outsourcing circuit compiler, where q is the number of oracle queries asked by adversary  $\mathcal{A}$  in Definition 4.

Figure 3: The description of compiler  $\Phi_{\mathcal{VC}}^2$ . Notice that component  $\widehat{\Gamma}_{\mathsf{ProbGen}}$  does not need to hide its input, and that component  $\widehat{\Gamma}_{\mathsf{Verify}}$  implements the self-destruct feature. The dotted line depicts the circuit boundaries.

*Proof.* The proof of the non-triviality and the correctness condition are similar to the proofs of Claim 1 and Claim 2 respectively, and are therefore omitted.

We proceed to prove the security of  $\Phi_{\mathcal{VC}}^2$ . We need to build a simulator  $\mathcal{S}$  that is able to "fake" experiment **Real** for all adversaries  $\mathcal{A}$ , for all circuits  $\Gamma$ , and for all initial memory values  $M_1$ . The simulator  $\mathcal{S}$  is allowed to define an arbitrary polynomial-time computable function  $f: \{0,1\}^* \to \{0,1\}^{\log(q)+1}$  that leaks a logarithmic amount of information regarding the initial private memory  $M_1$ . The function f is defined as follows.

- Sample all random coins for experiment **Real**, including the random coins  $\rho_{\mathcal{A}}$  of adversary  $\mathcal{A}$ , and the random coins  $\rho_{\Phi}$  of the compiler  $\Phi$ .

- Function f takes as input the memory  $M_1$  and the sampled random coins  $\rho = (\rho_A, \rho_{\Phi})$ ; note that f can completely simulate experiment **Real** using the memory  $M_1$  and the sampled randomness  $\rho$ .

- For all  $i \in [q]$  function f runs simultaneously the circuits  $\widehat{\Gamma}'[M_i](X_i)$  and  $\Gamma[M_i](X_i)$  using the initial memory  $M_1$  and adversary  $\mathcal{A}$ 's randomness to sample the inputs  $X_i$ 's.

- Define the event W which becomes true in case there exists some index  $i^* \in [q]$  such that  $\widehat{\Gamma}'[M_{i^*}](X_{i^*}) \neq \Gamma[M_{i^*}](X_{i^*})$ .

- $\bullet$  The outputs of function f are

- abort  $\in \{0, 1\}$ : a predicate that is 1 if event W happens;

- $-q^* \in [q]$ : the index corresponding to the round in which a self-destruct is triggered (if any).

The claim below shows that the probability of event W happening is negligible.

**Claim 5.** For all PPT adversaries A, the probability that f returns abort = 1 is negligible.

*Proof.* Let us assume that there exists some circuit  $\Gamma$ , some memory  $M_1$ , and a PPT adversary  $\mathcal{A}$  that provokes an abort = 1 with non-negligible probability. We build a PPT adversary  $\mathcal{A}'$  that uses  $\mathcal{A}$  to break the soundness property of the underlying VC scheme (cf. Definition 8). The description of  $\mathcal{A}'$  follows.

## Adversary $\mathcal{A}'(M_1, \mathcal{F}, \Gamma, \Phi)$ :

- 1. Receive PK from the challenger, where  $(SK, PK) \leftarrow \mathsf{KeyGen}(\mathcal{F}, \lambda)$ .

- 2. Run  $(\widehat{\Gamma}, \mathsf{aux}) \leftarrow \Phi(\Gamma)$  and send (the description of) circuit components  $\widehat{\Gamma}_{\mathsf{Compute}}$ ,  $\Gamma$  and  $\widehat{\Gamma}$  to  $\mathcal{A}$ . Adversary  $\mathcal{A}$  produces the modified component  $\widehat{\Gamma}'_{\mathsf{Compute}}$  and sends it to  $\mathcal{A}'$ .

- 3. For all  $i \in [q]$ , upon input query  $X_i$  answer as follows.

- Sample random coins  $R_i$ , define the string  $Z_i := X_i ||M_i||R_i$ , and run  $\Sigma_{Y_i,M_{i+1}} = \widehat{\Gamma}'_{\mathsf{Compute}}(PK,Z_i)$ .

- Send a verification query  $(i, \Sigma_{Y_i, M_{i+1}})$  to the challenger, receiving back a verification bit d. If d = 0 then return  $\bot$ , and set  $M_{i+1} := 0^{\mu}$ ; otherwise, compute  $(Y_i, M_{i+1}) = \mathcal{F}(M_i, X_i; R_i)$  and return  $Y_i$ .

- 4. Finally, pick a random  $i^* \in [q]$  and output the pair  $(i^*, \Sigma_{Y_{i^*}, M_{i^*+1}})$ .

For the analysis, note that the above simulation is perfect. In particular, the first time a verification query is rejected, the reduction returns  $\bot$  and overwrites the private memory with the all-zero string. By definition of the event W, we know that there exists an index  $i^* \in [q]$  such that the value  $Y_{i^*}$  corresponding to the encoding  $\Sigma_{Y_{i^*},M_{i^*+1}}$  is different from the value  $Y_{i^*}$  computed via  $\mathcal{F}(M_{i^*},X_{i^*})$ .