# Analysis of Secure Caches using a Three-Step Model for Timing-Based Attacks

Shuwen Deng, Wenjie Xiong and Jakub Szefer

Yale University, New Haven, CT, USA {shuwen.deng,wenjie.xiong,jakub.szefer}@yale.edu

#### Abstract.

Many secure cache designs have been proposed in literature with the aim of mitigating different types of cache timing-based attacks. However, there has so far been no systematic analysis of how these secure cache designs can, or cannot, protect against different types of the timing-based attacks. To provide a means of analyzing the caches, this paper presents a novel three-step modeling approach that is used to exhaustively enumerate all the possible cache timing-based vulnerabilities. The model covers not only attacks that leverage cache accesses or flushes from the local processor core, but also attacks that leverage changes in the cache state due to the cache coherence protocol actions from remote cores. Moreover, both conventional attacks and speculative execution attacks are considered. With the list of all possible cache timing vulnerabilities derived from the three-step model, this work further manually analyzes each of the existing secure cache designs to show which types of timing-based side-channel vulnerabilities each secure cache can mitigate. Based on the security analysis of the existing secure cache designs using the new three-step model, this paper further summarizes different techniques gleaned from the secure cache designs and their ability help mitigate different types of cache timing-based vulnerabilities.

Keywords: Secure Caches · Timing-based Attacks · Security Analysis · Side Channels · Covert Channels

## 1 Introduction

Research on timing-based attacks in computer processor caches has a long history, e.g., [1, 2, 3, 4, 5], predating their recent use in Spectre [6] attacks. These past attacks have shown the possibility to extract sensitive information via the timing-based channels, and often the focus is on extracting cryptographic keys. In addition, due to the recent Spectre [6] attacks, there is now renewed interested in timing-channels. Especially, the Spectre attacks consist of two parts: first, speculative execution is used to access some sensitive information; second, a timing-based channel is used to actually transfer the information to the attacker. Whether by itself, or combined with speculative execution, the timing-based channels in processors pose a threat to a system's security, and should be mitigated.

We have recently proposed a three-step model [7] in order to analyze cache timingbased side-channel attacks. The previous model considers cache timing-based side-channel vulnerabilities as a set of three "steps" or actions performed by either the attacker or the victim, which can affect the states of the cache. In this work, our methodology from [7] is improved to better represent actions of the attacker and the victim: For each step, all possible states for a cache block are enumerated in terms of whether the operation is driven by the attacker or the victim, what memory range the data being operated on belongs to, and whether the state is changed because of a memory access or data invalidation operation (due to a cache coherence operation or a flush instruction, for example). To understand which possible three-step actions can lead to an attack, we further propose and develop a cache three-step simulator, and apply a set of reduction rules to derive a complete list of vulnerabilities by eliminating three-step combinations that do not map to an attack. Furthermore, we consider both normal and speculative execution for the memory operations and modeling of the cache attacks. Speculative execution has gotten increased attention due to recent Spectre [6] attacks, many of which depend on timing channels to actually extract information – speculation alone is not enough for most of these attacks. Our model considers timing channels in general, independent of whether it is a side or a covert channel.

In the process of development of the improved three-step model, we have uncovered 43 types of timing-based vulnerabilities which have not been previously exploited (in addition, there are 29 types that map to attacks already known in literature). We cannot directly compare the types of vulnerabilities found in this work and in our prior work [7] due to the improved and different categorizations of the states of the cache block.

To address the threat of the prior cache timing-based attacks, to date 18 different secure cache designs have been presented in academic literature [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25]. The secure processor caches are designed with different assumptions and often address only specific types of timing-based side-channel or covert-channel attacks. To help analyze the security of these designs, this work uses our three-step modeling approach to reason about all the possible timing-based vulnerabilities. Especially, since our work demonstrates a number of new timing-based attacks, the existing secure caches have never been analyzed with respect to these new attacks before. For this work, we manually reviewed and analyzed the 18 existing secure cache designs [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25] in terms of the security features and implementations. Most of these designs do not have publicly available hardware implementation source code, so automatic analysis of the caches is not possible.

Based on the analysis, we summarize cache features that help improve security. Especially, we propose that an "ideal" secure caches and processor architectures should provide new features to let software explicitly label memory loads or stores of sensitive data, and differentiate them from normal loads and stores, so sensitive data can be efficiently identified and protected by the hardware. The caches can use partitioning to isolate the attacker and the victim and prevent the attacker from being able to set the victim's cache blocks into a known state, which is needed by many attacks. To mitigate attacks based on internal interference, the caches can use randomization to de-correlate the data that is accessed and the data that is placed in the cache. More details of the possible defenses are discussed in Section 5 and Section 6.

## 1.1 Contributions

The new contributions of this work over [7] are as follows:

- A new formulation of the three-step model with new cache states and derivation of a new set of types for covering all the cache timing-based vulnerabilities (Section 3).

- Inclusion of cache coherence issues into the three-step mode.

- Expansion of the three-step model to consider both cases of normal and speculative execution attacks.

- Design of reduction rules and cache three-step simulator to automatically derive the exhaustive list of all the three steps which map to effective vulnerabilities; and elimination of three-step patterns which do not map to a potential attack.

- Overview of the 18 secure cache designs that have been presented in academic literature (Section 4).

- Manual evaluation of 18 secure processor cache designs to determine how they can help prevent timing-based attacks and analysis of security features secure caches used (Section 5 and Section 6).

- Discussion of "ideal" secure caches and the features they would need (Section 6).

- Attack strategies description and comparison among different attack strategies (Appendix A).

- Analysis of the soundness of the three-step model and why three-steps are able to describe all timing-based vulnerabilities (Appendix B).

## 2 Cache Timing-Based Attacks and the Threat Model

Modern processor caches are known to be vulnerable to timing-based attacks. The timing of the memory accesses varies due to caches' operation. For example, a cache hit is fast while a cache miss is slow. The cache coherence protocol can also change the cache states and affect the timing of the memory operations. The cache coherence may invalidate a cache block from a remote core, resulting in a cache miss in the local core, for example. Also, the timing of cache flush operations varies depending on whether the data to be flushed is in the cache or not. Flushing an address using *clflush* with valid data in the cache is slow, while flushing an address not in the cache is fast, for example. From these timing differences of memory-related operations, the attacker can infer a data's specific memory address or corresponding cache index value, and thus learn some information about the victim's secrets.

### 2.1 Threat Model

This work focuses only on timing-based attacks in processor caches. Numerous other types of side and covert channels that do not use timing or caches exist, e.g., power-based [26], EM-based [27] (including RF), thermal-based [28], and in processor channels based on features such as power state of the AVX unit [29], for example. This work aims to explore main cache attacks only, but similar approach can be done for the other buffers or cache-like structures, which may be target of attack once main processor caches are secured.

In our threat model, an attacker's objective is to retrieve victim's secret information using timing-based channels in the processor cache. Specifically, we consider the situation where the victim accesses an address u and the address depends on some secret information. The address u is within some set of physical memory locations x, which are known to the attacker. The goal of the attacker is to obtain the address u or at least partial bits of it which relate to the cache index of the address.

We assume the attacker knows some of the source code of the victim. Especially, the attacker can only learn some information <sup>1</sup> about the address u from the timing channels, but with knowledge of the source code he or she can further infer the likely specific value of u, and thus infer the secret he or she is trying to learn.

The attacker cannot directly access any data in the state machine of the cache logic, nor directly read the data of the victim, if the two are not sharing the same address space. The attacker can, however, observe its own timing or the timing of the victim process. And the attacker knows how the timing of the memory-related operations depends on the cache states.

The attacker further is able to force the victim to execute a specific function. For example, the attacker can request victim to decrypt a specific piece of data, thus triggering the victim to execute a function that makes use of a secret key he or she wants to learn.

<sup>&</sup>lt;sup>1</sup>For a hit-based vulnerabilities, the attacker is able to learn the full address of the victim's sensitive data, while for the miss-based vulnerabilities, the attacker usually can learn the cache index of the victim's sensitive data. For more details of these vulnerabilities' categorizations, please refer to Section 3.3.3.

The victim in the cache attacks can be user software, code in an enclave, operating system, or another virtual machine.

The processor microarchitecture and the operating system are assumed to be able to differentiate between the victim and the attacker in different processes by assigning different process IDs. If the victim and the attacker are in the same process, e.g., attacker is a malicious library, they will have the same process ID. The system software (e.g., operating system or hypervisor) is responsible for properly setting up virtual memory (page tables) and assigning IDs, which may be used by the hardware to identify different threads, processes or virtual machines. When analyzing secure cache designs, the system software is considered trusted and bug-free. The attacker is also assumed not to be able to undermine the physical implementation or change the hardware, e.g., he or she cannot influence randomness generated by any random number generators in hardware. Physical or invasive attacks are not in scope of this work. For secure cache designs which add new instructions for security related operations, the victim process or management software is assumed to correctly use these instructions. During speculative execution, the cache state can be modified by the instructions executed speculatively, unless a processor cache architecture explicitly prevents or forbids certain speculative accesses.

### 2.2 Side and Covert Channels

This work focuses on both side and covert channels. Covert channels use the same methods as side channels, but the attacker controls both the sender and the receiver side of the channel. All types of side-channel attacks are equally applicable to covert channels. For brevity, we just use the term "victim" in the text to represent both the victim (for side channels) and the sender (for covert channels).

## 2.3 Hyperthreading Versus Timing-Slice Sharing

When the hyperthreading is supported in a system, the attacker and the victim are able to run on different threads in parallel instead of runing once every time slice (when no hyperthreading is used). Our model can be applied to both of the scenarios since our model abstracts away how the sharing happens.

## 3 Modeling of the Cache Timing-Based Side-Channel Vulnerabilities

This section explains how we developed the three-step modeling approach and used it to model the behavior of the cache logic and to enumerate all the possible cache timing-based vulnerabilities.

### 3.1 Introduction of the Three-Step Model

We have observed that all of the existing cache timing-based attacks can be modeled with three steps of memory-related operations. Here, "memory-related operation" refers to loads, stores, or different flushes that can be done by the victim or the attacker on the same core or different cores. When the victim and the attacker are on different cores, cache coherence will also be triggered when one of the memory-related operations is performed.

The three-step model has three steps, as the name implies. In *Step* 1, a memory operation is performed, placing the cache in an initial state known to the attacker (e.g., a new piece of data at some address is put into the cache or the cache block is invalidated). Then, in *Step* 2, a second memory operation alters the state of the cache from the initial state. Finally, in *Step* 3, a final memory operation is performed, and the timing of the

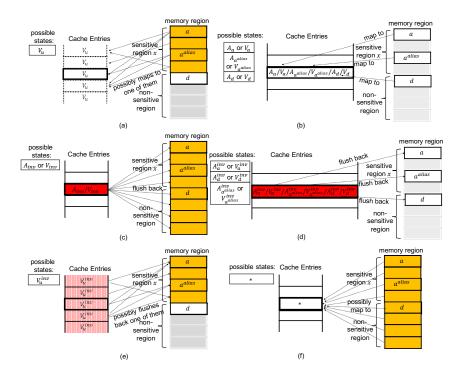

Figure 1: The 17 possible states for a single cache block in our three-step model: (a)  $V_u$ ; (b)  $A_a/V_a/A_{a^{alias}}/V_{a^{alias}}/A_d/V_d$ ; (c)  $A^{inv}/V^{inv}$ ; (d)  $A_a^{inv}/V_a^{inv}/A_{a^{alias}}^{inv}/V_a^{inv}/A_d^{inv}/V_d^{inv}$ ; (e)  $V_u^{inv}$ ; (f)  $\star$ ).

final operation reveals some information about the relationship among the addresses from Step 1, Step 2 and Step 3.

For example, in Flush + Reload [30] attack, in Step 1, a cache block is flushed by the attacker. In Step 2, security critical data is accessed by, for example, victim's AES encryption operation. In Step 3, the same cache block as the one flushed in Step 1 will be accessed and the time of the access will be measured by the attacker. If the victim's secret-dependent operation in Step 2 accesses the cache block, in Step 3 there will be a cache hit and fast timing of the memory operation will be observed, and the attacker learns the victim's secret address.

To model all the timing-based attacks, we write the three steps as:  $Step 1 \rightsquigarrow Step 2 \rightsquigarrow Step 3$ , which represents a sequence of steps taken by the attacker or the victim. To simplify the model, we focus on memory-related operation affecting one single cache block (also called cache slot, cache entry, or cache line). Cache block is the smallest unit of the cache. Since all the cache blocks are updated following the same cache state machine logic, it is sufficient to consider only one cache block.

### 3.2 States of the Three-Step Model

When modeling the attacks, we propose that there are 17 possible states for a cache block. Table 1 lists all the 17 possible states of the cache block for each step in our three-step model and their formal definitions. Figure 1 graphically shows for each possible state how the memory location maps to the cache block.

In each sub-figure of Figure 1, left-most part shows the possible state being described in the sub-figure. Middle part shows the possible situation of the cache state affected by

Table 1: The 17 possible states for a single cache block in our three-step model.

| State                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vu                                                                                        | A memory location $u$ belonging to the victim is accessed and is placed in the cache<br>block by the victim (V). Attacker does not know $u$ , but $u$ is from a set $x$ of memory<br>locations, a set which is known to the attacker. It may have the same index as $a$<br>or $a^{alias}$ , and thus conflict with them in the cache block. The goal of the attacker<br>is to learn the index of the address $u$ . The attacker does not know the address $u$ ,<br>hence there is no $A_u$ in the model.        |

| $A_a \text{ or } V_a$                                                                     | The cache block contains a specific memory location $a$ . The memory location is<br>placed in the cache block due to a memory access by the attacker, $A_a$ , or the victim,<br>$V_a$ . The attacker knows the address $a$ , independent of whether the access was by<br>the victim or the attacker themselves. The address $a$ is within the range of sensitive<br>locations $x$ . The address $a$ is known to the attacker.                                                                                   |

| $\begin{array}{c} A_{aalias} \\ \text{or} \\ V_{aalias} \end{array}$                      | The cache block contains a memory address $a^{alias}$ . The memory location is placed<br>in the cache block due to a memory access by the attacker, $A_{aalias}$ , or the victim,<br>$V_{aalias}$ . The address $a^{alias}$ is within the range x and not the same as a, but it has<br>the same address index and maps to the same cache block, i.e. it "aliases" to the<br>same block. The address $a^{alias}$ is known to the attacker.                                                                       |

| $A_d$ or $V_d$                                                                            | The cache block contains a memory address $d$ . The memory address is placed in the cache block due to a memory access by the attacker, $A_d$ , or the victim, $V_d$ . The address $d$ is not within the range $x$ . The address $d$ is known to the attacker.                                                                                                                                                                                                                                                  |

| $A^{inv}$ or $V^{inv}$                                                                    | The cache block is now invalid. The data and its address are "removed" from the cache block by the attacker, $A^{inv}$ , or the victim, $V^{inv}$ , as a result of cache block being invalidated, e.g., this is a cache flush of the whole cache.                                                                                                                                                                                                                                                               |

| $\begin{array}{c} A_a^{inv} \\ \text{or} \\ V_a^{inv} \end{array}$                        | The cache block state can be anything except $a$ in this cache block now. The data<br>and its address are "removed" from the cache block by the attacker, $A_a^{inv}$ , or the<br>victim, $V_a^{inv}$ . E.g., by using a flush instruction such as $clflush$ that can flush<br>specific address, or by causing certain cache coherence protocol events that force $a$<br>to be removed from the cache block. The address $a$ is known to the attacker.                                                          |

| $\begin{smallmatrix} A_{aalias}^{inv} \\ \text{or} \\ V_{aalias}^{inv} \end{smallmatrix}$ | The cache block state can be anything except $a^{alias}$ in this cache block now. The data and its address are "removed" from the cache block by the attacker, $A_{aalias}^{inv}$ , or the victim, $V_{aalias}^{inv}$ . E.g., by using a flush instruction such as $clflush$ that can flush specific address, or by causing certain cache coherence protocol events that force $a^{alias}$ to be removed from the cache block. The address $a^{alias}$ is known to the attacker.                                |

| $egin{array}{c} A_d^{inv} \ { m or} \ V_d^{inv} \end{array}$                              | The cache block state can be anything except $d$ in this cache block now. The data and its address are "removed" from the cache block by the attacker $A_d^{inv}$ or the victim $V_d^{inv}$ . E.g., by using a flush instruction such as $clflush$ that can flush specific address, or by causing certain cache coherence protocol events that force $d$ to be removed from the cache block. The address $d$ is known to the attacker.                                                                          |

| $V_u^{inv}$                                                                               | The cache block state can be anything except $u$ in the cache block. The data and its address are "removed" from the cache block by the victim $V_u^{inv}$ as a result of cache block being invalidated, e.g., by using a flush instruction such as $clflush$ , or by certain cache coherence protocol events that force $u$ to be removed from the cache block. The attacker does not know $u$ . Therefore, the attacker is not able to trigger this invalidation and $A_u^{inv}$ does not exist in the model. |

| *                                                                                         | Any data, or no data, can be in the cache block. The attacker has no knowledge of<br>the memory address in this cache block.                                                                                                                                                                                                                                                                                                                                                                                    |

each. For all sub-figures, the middle cache block (shown in bold) is the targeted cache block. Right-most part shows the memory region in relation to the cache block. Recall, the addresses a and  $a^{alias}$  are within the sensitive set of addresses x, while d is outside the set of sensitive addresses (for simplicity the set is shown as a contiguous region, but it can be any set). Also recall, A represents the operations performed by the attacker and V represents the victim's operations.

Figure 1a shows the description of the possible state  $V_u$ , where address u is within sensitive set and unknown to the attacker. Therefore, it can possibly map to any cache block including the target cache block shown in the middle. Since its position in the cache and specific address is unknown, we show  $V_u$  in dashed lines. Meanwhile, Figure 1e shows the description of the possible state  $V_u^{inv}$ , which is result of the victim invalidating data at the sensitive address u and possibly invalidating some address within sensitive region.

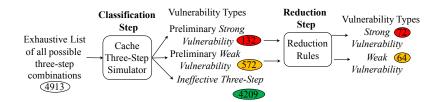

Figure 2: Procedure to derive the effective types of three-step timing-based vulnerabilities. Ovals refer to the number of vulnerabilities in each category.

Further, Figure 1f shows the description of the possible state \*, which represents null knowledge of the address for the attacker to this corresponding cache block. Therefore, it can possibly refers to any address in the memory, or no valid address at all.

Figure 1b shows the description of the possible state  $A_a/V_a/A_{a^{alias}}/V_{a^{alias}}/A_d/V_d$ . Their addresses are all known to the attacker and map to the same targeted cache block. Both a and  $a^{alias}$  are within the sensitive set of addresses x and  $a^{alias}$ , as its name indicates, is a different address than a but still within set x and maps to the same cache block as a. Address d is outside of the set x. Meanwhile, Figure 1d shows the description of the possible state  $A_a^{inv}/V_a^{inv}/A_{a^{alias}}^{inv}/V_d^{inv}}$ , which correspond to invalidation of the address shown in the subscript of the state. Some additional possible invalidation states,  $A^{inv}/V^{inv}$ , are shown in Figure 1c. These states indicate no valid address is in the cache block. Therefore, all the possible addresses that mapped to this cache block, e.g., a,  $a^{alias}$ , d and u (if it mapped to this block), before the invalidation step  $A^{inv}/V^{inv}$  will be flushed back to the memory.

### 3.3 Derivation of All Cache Timing-Based Vulnerabilities

With the 17 candidate states shown in Table 1 for each step, there are in total 17\*17\*17 = 4913 combinations of three steps. We developed a cache three-step simulator and a set of reduction rules to process all the three-step combinations and decide which ones can indicate a real attack. As is shown in Figure 2, the exhaustive list of the 4913 combinations will first be input to the cache three-step simulator, where the preliminary classification of vulnerabilities is derived. The effective vulnerabilities will then be sent as the input to the reduction rules to remove the redundant three steps and obtain final list of vulnerabilities.

#### 3.3.1 Cache Three-Step Simulator

We developed a cache three-step simulator that simulates the state of one cache block and derives the attacker's observations in the last step of the three-step patterns that it analyzes, for different possible u. Since u is in secure range x, the possible candidates of u for a cache block are a,  $a^{alias}$  and NIB (Not-In-Block). Here, NIB indicates the case that u does not have same index as a or  $a^{alias}$  and thus does not map to this cache block.

The cache three-step simulator is implemented in Python script and it's pesudo implementation is shown in Algorithm 2. Simulator's inputs are 17 possible states for each of the step. Outputs are all the vulnerabilities that belong to the *Strong* or the *Weak* type or the *Ineffective* type. The simulator uses a nested **for** loop to check all possible combinations (4913) of the three step pattern. For each step of each pattern, if it is  $V_u$ , this step will be extended to be one of three candidates:  $V_a$ ,  $V_{a^{alias}}$  and  $V_{NIB}$ . If it is  $V_u^{inv}$ , this step will be extended to be one of three candidates:  $V_a^{inv}$ ,  $V_{a^{alias}}^{inv}$  and  $V_{NIB}^{inv}$ . We wrote a function *output\_timing* that takes three known memory access steps as input and output whether fast or slow timing will be observed for the last step. In this case, for each of the *u*-related step's candidate, we can derive a timing observation. Using

Figure 3: Examples of relations between victim's behavior (u) and attacker's observation for each vulnerability type: (a),(b) *Strong Vulnerability*; (c),(d) *Weak Vulnerability*; (e),(f) *Ineffective Three-Step*).

these timing observation, function  $judge\_type$  decides whether a three-step pattern is a potential vulnerability by analyzing whether the attacker is able to observe different and unambiguous timing for different values of u.

The simulator categorizes all the three-step patterns into three categories, as listed below. Figure 3 shows two examples for the *Strong Vulnerability* (a, b), *Weak Vulnerability* (c, d) and *Ineffective Three-Step* (e, f), categories respectively.

- 1. Strong Vulnerability: When a fast or slow timing is observed by the attacker, he or she is able to uniquely distinguish the value of u (either it maps to some known address or has the same index with some known address). In this case, the vulnerability has strong information leakage (i.e. attacker can directly obtain the value of u based on the observed timing). We categorize these vulnerabilities to be strong. E.g., for  $V_d \rightsquigarrow V_u \rightsquigarrow A_a$  vulnerability shown in Figure 3a, if u maps to a, the attacker will always derive fast timing. If u is  $a^{alias}$  or NIB, slow timing will be observed. This indicates that the attacker is able to unambiguously infer the victim's behavior (u) from the timing observation.

- 2. Weak Vulnerability: When fast or slow timing is observed by the attacker, he or she knows it corresponds to more than one possible value of u (e.g., a or  $a^{alias}$ ). For these vulnerabilities, timing variation can still be observed due to different victim's behavior. However, the attacker cannot learn the value of the index of the address u unambiguously. E.g., for type  $\star \rightsquigarrow V_u \rightsquigarrow A_a^{inv}$  shown in Figure 3c, when fast timing is observed, u possibly maps to  $a^{alias}$  or NIB (the reason for the possibility of u mapping to NIB to derive fast timing is that due to the  $\star$  in Step 1, the cache could have a hit and then  $A_a$  would result in a cache hit). On the other hand, when slow timing is observed, u possibly maps to a or NIB. This pattern leads to uncertain u guess about value of u based on timing observation.

- 3. Ineffective Three-Step: The remaining types are treated to be ineffective. E.g., for

Algorithm 1 *simulate\_cache\_three\_step* (*state*[])

| Inj        | <b>put:</b> state[]: a list containing 17 possible states for each of the step                               |

|------------|--------------------------------------------------------------------------------------------------------------|

|            | tput: strong[]: a list containing all the vulnerabilities that belong to the Strong type                     |

|            | weak[]: a list containing all the vulnerabilities that belong to the Weak type                               |

|            | <i>ineffective</i> []: a list containing all the ineffective typs                                            |

| 1:         | for $step1 \in len(state[])$ do                                                                              |

| 2:         | for $step2 \in len(state[])$ do                                                                              |

| 3:         | for $step3 \in len(state[])$ do                                                                              |

| 4:         | steps = [state[step1], state[step2], state[step3]]                                                           |

| 5:         | candidates = [] // array to store all possible candidate combinations of this three-step                     |

|            | pattern                                                                                                      |

| 6:         | res = [] // array to store all possible timing observation regading different candidate                      |

|            | combinations for this three-step pattern                                                                     |

| 7:         | if $(u\_related(steps[0]) \text{ or } u\_related(steps[1]) \text{ or } u\_related(steps[2]))$ then           |

| 8:         | for $possi\_candidate \in 3 // V_u$ 's candidates are $V_a$ , $V_{a^{alias}}$ and $V_{NIB}$ ; $V_u^{inv}$ 's |

|            | candidates are $V_a^{inv}$ , $V_{a^{alias}}^{inv}$ and $V_{NIB}^{inv}$ . Both candidate's number is 3. do    |

| 9:         | $candidates.append[[change\_u(steps[0], possi\_candidate), ]$                                                |

|            | $change\_u(steps[1], possi\_candidate), change\_u(steps[2], possi\_candidate)]]$                             |

| 10:        | end for                                                                                                      |

| 11:        | for $i \in 3$ do                                                                                             |

| 12:        | $res.append(output\_timing(candidates[i]))$                                                                  |

| 13:        | end for                                                                                                      |

| 14:        | if $judge\_type(res) == Strong$ then                                                                         |

| 15:        | strong.append(steps)                                                                                         |

| 16:        |                                                                                                              |

| 17:        | if $judge_type(res) == Weak$ then                                                                            |

| 18:        | weak.append(steps)                                                                                           |

| 19:        |                                                                                                              |

| 20:        | ineffective.append(steps)<br>end if                                                                          |

| 21:        | end if                                                                                                       |

| 22:<br>23: | ella li                                                                                                      |

| 23: 24:    | ineffective.append(steps)                                                                                    |

| 24: 25:    | continue                                                                                                     |

| 20.<br>26: | end if                                                                                                       |

| 20:<br>27: | end for                                                                                                      |

| 27: 28:    | end for                                                                                                      |

|            | end for                                                                                                      |

| 49.        |                                                                                                              |

type  $A_a \rightsquigarrow V_u \rightsquigarrow A_d$  shown in Figure 3f, no matter what the value of u is, attacker's observation is always slow timing.

After computing the type of all the three-step patterns, the cache three-step simulator will output effective (*Strong Vulnerability* or *Weak Vulnerability*) three-step patterns. Due to the space limit, we only list and analyze the *Strong* vulnerabilities in this paper. *Weak* vulnerabilities are left for future work when channels with smaller channel capacities are desired to be analyzed.

### 3.3.2 Reduction Rules

We also have developed rules that can further reduce the output list of all the effective three steps from the cache three-step simulator. Figure 2 shows how the output of the simulator is filtered through the reduction rules to get the final list of vulnerabilities. Reduction's goal is to remove vulnerabilities of repeating or redundant types from the lists to form effective *Strong Vulnerability* or *Weak Vulnerability* output. A script was developed that automatically applies below reduction rules to the output of the simulator to get the final list of vulnerabilities. A three-step combination will be eliminated if it satisfies one of the below rules:

- 1. Three-step patterns with two adjacent steps which are repeating, or which are both known to the attacker, can be eliminated, e.g.,  $A_d \rightsquigarrow A_a \rightsquigarrow V_u$  can be reduced to  $A_a \rightsquigarrow V_u$ , which is equivalent to  $\star \rightsquigarrow A_a \rightsquigarrow V_u$ . Therefore,  $A_d \rightsquigarrow A_a \rightsquigarrow V_u$  is a repeat type of  $\star \rightsquigarrow A_a \rightsquigarrow V_u$  and can be eliminated.

- 2. Three-step patterns with a step involving a known address a and an alias to that address  $a^{alias}$  gives the same information. Thus three step combinations which only differ in use of a or  $a^{alias}$  cannot represent different attacks, and only one combination needs to be considered. For example,  $V_u \rightsquigarrow A_{a^{alias}} \rightsquigarrow V_u$  is a repeat type of  $V_u \rightsquigarrow A_a \rightsquigarrow V_u$ , and we will eliminate the first pattern.

- 3. Three-step patterns with steps  $V_u$  and  $V_{u^{inv}}$  in adjacent consecutive steps with each other will only keep the latter step and eliminate the first step. For example,  $A_a \rightsquigarrow V_u \rightsquigarrow V_{u^{inv}}$  can be reduced to  $A_a \rightsquigarrow V_{u^{inv}}$  and further equivalent to  $\star \rightsquigarrow A_a \rightsquigarrow V_{u^{inv}}$ . So  $A_a \rightsquigarrow V_u \rightsquigarrow V_{u^{inv}}$  can be eliminated.

#### 3.3.3 Categorization of *Strong*Vulnerabilities

As is shown in Figure 2, after applying the reduction rules, there are remaining 72 types of *Strong* vulnerabilities. In Appendix B, we analyze the soundness of the three-step model to demonstrate that the three-step model can cover all possible cache timing-based side-channel vulnerabilities. And if there is a vulnerability, it can always be reduced to a model that requires only three steps. Table 2 lists all the vulnerability types of which the last step is a memory access and Table 3 shows all the vulnerability types of which the last step is an invalidation-related operation. To ease the understanding of all the vulnerability types, we group the vulnerabilities based on attack strategies (left most column in Table 2 and Table 3), these strategies correspond to well-known names for the attacks, if such exist, otherwise we provide a new name. In Appendix A we provide description for each attack strategies where such existed before, even if similar attacks, e.g., attacks differing in only one step, have been given different names before. We use these established names to avoid confusion, but detail some of the similarities in Appendix A as a clarification.

The list of vulnerability types can be further collected into four simple macro types which cover one or more vulnerability types: internal interference miss-based (IM), internal interference hit-based (IH), external interference miss-based (EM), external interference hit-based (EH), as labeled in the Macro Type column of Table 2 and Table 3. All the types of vulnerabilities that only involve the victim's behavior, V, in the states in *Step 2* and *Step 3* are called internal interference vulnerabilities (I). The remaining ones are called external interference (E). Some vulnerabilities allow the attacker to learn that the address of the victim accesses map to the set the attacker is attacking by observing *slow* timing due to a cache miss or *fast* timing due to invalidation of data not in the cache<sup>2</sup>. We call these miss-based vulnerabilities (M). The remaining ones leverage observation of *fast* timing due to a cache hit or *slow* timing due to an invalidation of an address that is currently valid in the cache, and are called hit-based vulnerabilities (H).

Many vulnerability types have been explored before. E.g., the Cache Collision attack [4] is effectively based on the Internal Collision, and it maps to types labeled (2) in the Attack column in Table 2 and Table 3. The types labeled **new** correspond to new attack not previously discussed in literature. We believe these 43 are new attacks not previously analyzed nor known.

$<sup>^{2}</sup>$ Invalidation is fast when the corresponding address which is to be invalidated does not exist in the cache since no operation is needed for the invalidation.

Table 2: The table shows all the cache timing-based cache vulnerabilities where the last step is a memory access related operation. The *Attack Strategy* column gives a common name for each set of one or more specific vulnerabilities that would be exploited in an attack in a similar manner. The *Vulnerability Type* column gives the three steps that define each vulnerability. For *Step 3*, *fast* indicates a cache hit must be observed to derive sensitive address information, while *slow* indicates a cache miss must be observed. The *Macro Type* column proposes the categorization the vulnerability belongs to. "E" is for external interference vulnerabilities. "I" is for internal interference vulnerabilities. "I" is for hit-based vulnerabilities. The *Attack* column shows if a type of vulnerability has been previously presented in literature.

| Attack      |                     | Vulnerabili       | ty Type      | Macro |        |

|-------------|---------------------|-------------------|--------------|-------|--------|

| Strategy    | Step 1              | Step 2            | Step 3       | Type  | Attack |

|             | $A^{inv}$           | $V_u$             | $V_a$ (fast) | IH    | (2)    |

|             | $V^{inv}$           | $V_u$             | $V_a$ (fast) | IH    | (2)    |

| Cache       | $A_d$               | $V_u$             | $V_a$ (fast) | IH    | (2)    |

| Internal    | $V_d$               | $V_u$             | $V_a$ (fast) | IH    | (2)    |

| Collision   | A <sub>aalias</sub> | $V_u$             | $V_a$ (fast) | IH    | (2)    |

|             | Valias              | $V_u$             | $V_a$ (fast) | IH    | (2)    |

|             | $A_{c}^{inv}$       | $V_u$             | $V_a$ (fast) | IH    | (2)    |

|             | $V_{-}^{inv}$       | $V_u$             | $V_a$ (fast) | IH    | (2)    |

|             | $A_a^{inv}$         | $V_u$             | $A_a$ (fast) | EH    | (5)    |

|             | $V_a^{unv}$         | $V_u$             | $A_a$ (fast) | EH    | (5)    |

|             | A <sup>inv</sup>    | $V_u$             | $A_a$ (fast) | EH    | (5)    |

| Flush       | $V^{inv}$           | $V_u$             | $A_a$ (fast) | EH    | (5)    |

| + Reload    | $A_d$               | $V_u$             | $A_a$ (fast) | EH    | (5)    |

|             | $V_d$               | $V_u$             | $A_a$ (fast) | EH    | (5)    |

|             | A <sub>aalias</sub> | $V_u$             | $A_a$ (fast) | EH    | (5)    |

|             | Valias              | $V_u$             | $A_a$ (fast) | EH    | (5)    |

| Reload      | $V_u^{inv}$         | $A_a$             | $V_u$ (fast) | EH    | new    |

| + Time      | $V_u^{inv}$         | $V_a$             | $V_u$ (fast) | IH    | new    |

|             | $\tilde{A}_a$       | $V_u^{inv}$       | $A_a$ (slow) | EM    | (6)    |

| Flush       | $A_a$               | $V_u^{\bar{i}nv}$ | $V_a$ (slow) | IM    | new    |

| + Probe     | $V_a$               | $V_u^{inv}$       | $A_a$ (slow) | EM    | new    |

|             | $V_a$               | $V_u^{inv}$       | $V_a$ (slow) | IM    | new    |

| Evict       | $V_{u}$             | Ad Ad             | $V_u$ (slow) | EM    | (1)    |

| + Time      | $V_u$               | Aa                | $V_u$ (slow) | EM    | (1)    |

| Prime       | $A_d$               | $V_u$             | $A_d$ (slow) | EM    | (4)    |

| + Probe     | $A_a$               | $V_u$             | $A_a$ (slow) | EM    | (4)    |

|             | $V_u$               | Va                | $V_u$ (slow) | IM    | (3)    |

| Bernstein's | $V_u$               | $V_d$             | $V_u$ (slow) | IM    | (3)    |

| Attack      | $V_d$               | $V_u$             | $V_d$ (slow) | IM    | (3)    |

|             | $V_a$               | $V_u$             | $V_a$ (slow) | IM    | (3)    |

| Evict       | $V_d$               | $V_u$             | $A_d$ (slow) | EM    | new    |

| + Probe     | $V_a$               | $V_u$             | $A_a$ (slow) | EM    | new    |

| Prime       | $A_d$               | $V_u$             | $V_d$ (slow) | IM    | new    |

| + Time      | $A_a$               | Vu                | $V_a$ (slow) | IM    | new    |

| Flush       | $V_u$               | $A_a^{inv}$       | $V_u$ (slow) | EM    | new    |

| + Time      | $V_u$               | $V_a^{inv}$       | $V_u$ (slow) | IM    | new    |

(1) Evict + Time attack [31].

(2) Cache Internal Collision attack [4].

(3) Bernstein's attack [3].

(4) Prime + Probe attack [31, 2], Alias-driven attack [32].

(5) Flush + Reload attack [30, 33], Evict + Reload attack [34].

(6) SpectrePrime, MeltdownPrime attack [35].

## 4 Secure Caches

Having explained the three-step model, we now explore the various secure caches which have been presented in literature to date [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25]. Later, in Section 5 we will apply the three-step model to check if the secure caches can defend some or all of the vulnerabilities in our model.

This section gives brief overview of the 18 secure cache designs that have been presented in academic literature in the last 15 years. To the best of our knowledge, these cover all the secure cache designs proposed to date. Most of the designs have been realized in functional

| Attack                      |                      | Vulnerabilit     | у Туре                                                          | Macro |        |

|-----------------------------|----------------------|------------------|-----------------------------------------------------------------|-------|--------|

| Strategy                    | Step 1               | Step 2           | Step 3                                                          | Type  | Attacl |

|                             | Ainv                 | $V_u$            | $V_{a}^{inv}$ (slow)                                            | IH    | new    |

| ~                           | Vinv                 | $V_u$            | $V_a^{(\text{slow})}$<br>$V_a^{inv}$ (slow)                     | IH    | new    |

| Cache Internal<br>Collision | Ad                   | Vu               | $V_a^{(\text{blow})}$ (slow)                                    | IH    | new    |

| Invalidation                | Vd                   | Vu               | $V^{inv}$ (slow)                                                | IH    | new    |

| mundation                   | A <sub>a</sub> alias | Vu               | <u> </u>                                                        | IH    | new    |

|                             | $V_{a^{alias}}$      | V <sub>u</sub>   | $\frac{V_a^{inv} \text{ (slow)}}{V_a^{inv} \text{ (slow)}}$     | IH    | new    |

|                             | Ainv                 | Vu               | $V_a^{inv}$ (slow)                                              | IH    | (1)    |

| Flush + Flush               | $V_{a}^{unv}$        | $V_u$            | $V^{inv}$ (slow)                                                | IH    | (1)    |

| r lusn + r lusn             | Ainv                 | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | (1)    |

|                             | $V_a^{inv}$          | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | (1)    |

|                             | A <sup>inv</sup>     | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | new    |

|                             | $V^{inv}$            | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | new    |

| Flush + Reload              | $A_d$                | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | new    |

| Invalidation                | $V_d$                | $V_u$            | $A_a^{inv}$ (slow)                                              | EH    | new    |

|                             | A <sub>a</sub> alias | $V_{u}$          | $A_a^{inv}$ (slow)                                              | EH    | new    |

|                             | Valias               | $V_{u}$          | $A_a^{inv}$ (slow)                                              | EH    | new    |

| Reload + Time               | $V_{u}^{inv}$        | $A_a$            | $V_u^{inv}$ (slow)                                              | EH    | new    |

| Invalidation                | $V_u^{inv}$          | $V_a$            | $V_u^{inv}$ (slow)                                              | IH    | new    |

|                             | A <sub>a</sub>       | $V_{u}^{inv}$    | $A_a^{inv}$ (fast)                                              | EM    | new    |

| Flush + Probe               | $A_a$                | $V_{u}^{inv}$    | $V_a^{inv}$ (fast)                                              | IM    | new    |

| Invalidation                | $V_a$                | $V_u^{inv}$      | $A_{a}^{inv}$ (fast)                                            | EM    | new    |

|                             | $V_a$                | $V_{u}^{inv}$    | $V_{a}^{inv}$ (fast)                                            | IM    | new    |

| Evict + Time                | $V_u$                | $\overline{A}_d$ | $\frac{V_{u}^{inv} \text{ (fast)}}{V_{u}^{inv} \text{ (fast)}}$ | EM    | new    |

| Invalidation                | $V_u$                | $A_a$            | $V_u^{inv}$ (fast)                                              | EM    | new    |

| Prime + Probe               | $A_d$                | $V_u$            | $A_d^{inv}$ (fast)                                              | EM    | new    |

| Invalidation                | $A_a$                | $V_u$            | $A_a^{inv}$ (fast)                                              | EM    | new    |

| Bernstein's                 | $V_u$                | $V_a$            | $V_{u}^{inv}$ (fast)                                            | IM    | new    |

| Invalidation                | $V_u$                | $V_d$            | $V_u^{inv}$ (fast)                                              | IM    | new    |

| Attack                      | $V_d$                | $V_u$            | $V_d^{inv}$ (fast)                                              | IM    | new    |

|                             | $V_a$                | $V_{u}$          | $V_a^{inv}$ (fast)                                              | IM    | new    |

| Evict + Probe               | $V_d$                | $V_u$            | $A_d^{inv}$ (fast)                                              | EM    | new    |

| Invalidation                | Va                   | $V_u$            | $A_a^{inv}$ (fast)                                              | EM    | new    |

| Prime + Time                | Ad                   | Vu               | Vinv (fast)                                                     | IM    | new    |

| Invalidation                | A <sub>a</sub>       | Vu               | $V_{\underline{a}}^{(\mathrm{rast})}$ (fast)                    | IM    | new    |

| Flush + Time                | Vu                   | $\Delta inv$     | $V_u^{inv}$ (fast)                                              | EM    | new    |

| Invalidation                | $V_u$                | V <sup>inv</sup> | $V_{u}^{inv}$ (fast)                                            | IM    | new    |

Table 3: The table shows the second part of the timing-based cache side-channel vulnerabilities where the last step is an invalidation related operation. For *Step* 3, *fast* indicates no corresponding address of the data is invalidated, while *slow* indicates invalidation operation makes some data invalid, causing longer processing time.

(1) Flush + Flush attack [36].

simulation, e.g., [14, 19]. Some have been realized in FPGA, e.g., [23], and a few have been realized in real ASIC hardware, e.g., [37]. No specific secure caches have been implemented in commercial processors to the best of our knowledge, however, CATalyst [18] leverages Intel's CAT (Cache Allocation Technology) technology available today in Intel Xeon E5 2618L v3 processors, and could be deployed today.

When the secure cache description in the cited papers did not mention the issue of using flush or cache coherence, we assume the victim or the attacker cannot invalidate each other's cache blocks by using *clflush* instructions or through cache coherence protocol operations; but they can flush or use cache coherence to invalidate their own cache lines. The victim and the attacker also cannot invalidate protected or locked data. Further, if the authors specified any specific assumptions (mainly about the software), we list the assumption as part of the description of the cache. What's more, when the level of cache hierarchy was unspecified, we assume the secure caches' features can be applied to all levels of caches, including L1 cache, L2 cache and Last Level Cache (LLC). If the inclusivity of the caches was not specified, we assume they target inclusive caches. Following the below descriptions of each secure cache design, the analysis of the secure caches is given in Section 5.

$SP^*$  cache [15, 38]<sup>3</sup> uses partitioning techniques to statically partition the cache ways

<sup>&</sup>lt;sup>3</sup>Two existing papers give slightly different definitions for an "SP" cache, thus we selected to define a

into *High* and *Low* partition for the victim and the attacker according to their different process IDs. The victim typically belongs to *High* security and attacker belongs to *Low* security. Victim's memory accesses cannot modify *Low* partition (assigned to processes such as the attacker), while the attacker's memory accesses cannot modify *High* partition (assigned to the victim). However, the memory accesses of both the victim and the attacker can result in a hit in either *Low* or *High* partition if the data is in the cache.

SecVerilog cache [9, 8] statically partitions cache blocks between security levels L (Low) and H (High). Each instruction in the source code for programs using SecVerilog cache needs to include a *timing label* which effectively represents whether the data being accessed by that instruction is Low or High based on the code and this *timing label* can be similar to a process ID that differentiates attacker's (Low) instructions from victim's (High) instructions. The cache is designed such that operations in the High partition cannot affect timing of operations in the Low partition. For a cache miss due to Low instructions, when the data is in the High partition, it will behave as a cache miss, and the data will be moved from the High to the Low partition to preserve consistency. However, High instructions are able to result in a cache hit in both High and Low partitions, if the data is already in the cache.

**SecDCP cache** [14] builds on the SecVerilog cache and uses partitioning idea from the original SecVerilog cache, but the partitioning is dynamic. It can support at least two security classes H (*High*) and L (*Low*), and configurations with more security classes are possible. They use the percentage of cache misses for L instructions that was reduced (increased) when L's partition size was increased (reduced) by one cache way to adjust the number of ways of the cache assigned to the *Low* partition. When adjusting number of ways in the cache dedicated to each partition, if L's partition size decreases, the process ID is checked and L blocks are flushed before the way is reallocated to H. On the other hand, if L's partition size increases, H blocks in the adjusted cache way remain unmodified so as to not add more performance overhead, and they will eventually be evicted by L's memory accesses. However, the feature of not flushing *High* partition data during way adjustment may leak timing information to the attacker.

**NoMo cache** [17] dynamically partitions the cache ways among the currently "active" simultaneous multithreading (SMT) threads. Each thread is exclusively reserved Y blocks in each cache set, where Y is within the range of  $[0, \lfloor \frac{N}{M} \rfloor]$ , where N is the number of ways and M is the number of SMT threads. NoMo-0 equals to traditional set associative cache while NoMo- $\lfloor \frac{N}{M} \rfloor$  partitions cache evenly for the different threads and there are no non-reserved ways. The number of Y assigned to each thread is adjusted based on its activeness. When adjusting number of blocks assigned to a thread, Y blocks are invalidated for cache sets to protect timing leakage. Eviction is not allowed within each thread's own reserved ways, we assume NoMo- $\lfloor \frac{N}{M} \rfloor$  is used to fully partition the cache. When the attacker and the victim share the same library, there will be a cache hit if accessing the shared data, and the normal cache hit policy holds to guarantee the cache coherence.

**SHARP cache** [16] uses both partitioning and randomization techniques to prevent victim's data from being evicted or flushed by other malicious processes and it targets on the inclusive caches. Each cache block is augmented with the core valid bits (CVB) to indicate which private cache (process) it belongs to (similar to the Process ID), where CVB stores a bitmap and *i*-th bit in the bitmap is set if the line is present in *i*-th core's private cache. Cache hit is allowed among different processes' data. When there is cache miss and data needs to be evicted, data not belonging to any current processes will be evicted first. If there is no such data, data belonging to the same process, a random data in the

new cache, the  $SP^*$  cache, that combines secure cache features of the Secret-Protecting cache from [15] with secure cache features of the Static-Partitioned cache from [38].

cache set will be evicted. This random eviction will generate an interrupt to the OS to notify it of a suspicious activity. For pages that are read-only or executable, SHARP cache disallows flushing using *clflush* in user mode. However, invalidating victim's blocks by using cache coherence protocol is still possible.

**Sanctum cache** [13] focuses on isolation of enclaves (equivalent to Trusted Software Module in other designs) from each other and the operating system (OS). In terms of caches, they implements security features for L1 cache, TLB and LLC. Cache isolation of LLC is achieved by assigning each enclave or OS to different DRAM address regions. It uses page-coloring-based cache partitioning scheme [39, 40] and a software security monitor that ensures per-core isolation between OS and enclaves. For L1 cache and TLB, when there is a transition between enclave and non-enclave mode, the security monitor will flush the core-private caches to achieve isolation. Normal flushes triggered by the enclave or the OS can only be done within enclave or not within enclave code. Also, timing-based side-channel attacks exploiting cache coherence are explicitly not prevented, thus behavior on cache coherence operations is not defined. This cache listed extra software assumptions as follows:

Assumption 1. Software security monitor guarantees that victim and attacker process cannot share the same cache blocks. It uses page coloring [39, 40] to ensure that victim and attacker's memory is never mapped to the same cache blocks for the LLC.

Assumption 2. The software runs on a system with a single processor core where victim and attacker alternate execution, but can never run truly in parallel. Moreover, security critical data is always flushed by the security monitor when program execution switches away from the victim program for the L1 cache and the TLB.

MI6 cache [23] is part of the memory hierarchy of the MI6 processor, which combines Sanctum [13] cache's security feature with disabling speculation during the speculative execution of memory-related operations. During normal processor execution, for L1 caches and TLB, the corresponding states will be flushed across context switches between software threads. For the LLC, set partitioning is used to divide DRAM into contiguous regions. And cache sets are guaranteed to be strictly partitioned (two DRAM regions cannot map to the same cache set). Each enclave is only able to access its own partition. Speculation is simply disabled when enclave interacts with the outside world because of small performance influence based on the rare cases of speculation. This cache listed extra software assumptions as follows:

Assumption 1. Software security monitor guarantees that the victim and the attacker process cannot share the same cache blocks. It uses page coloring [39, 40] to ensure that victim's and attacker's memory are never mapped to the same cache blocks for the LLC.

Assumption 2. The software runs on a system with a single processor core where victim and attacker alternate execution, but can never run truly in parallel. Moreover, security critical data is always flushed by the security monitor when program execution switches away from the victim program for the L1 cache and the TLB.

Assumption 3. When an enclave is interacting with the outside environment, the corresponding speculation is disabled by the software.

**InvisiSpec cache** [22] is able to make speculation invisible in the data cache hierarchy. Before a visibility point shows up, when all of its prior control flow instructions resolve, unsafe speculative loads (USL) will be put into a speculative buffer (SB) without modifying any cache states. When reaching the visibility point, there are two cases. In one case, the USL and successive instructions will be possibly squashed because of mismatch of data in the SB and the up-to-date values in the cache. In another case, the core receives possible invalidation from the OS before checking of memory consistency model and no comparison is needed. When speculative execution happens, the hardware puts the data into SB, as to identify visibility point for dealing with final state transition of the speculative execution. InvisiSpec cache targets on Spectre-like attacks and futuristic attacks. However, InvisiSpec cache is vulnerable to all non-speculative side channels.

**CATalyst cache** [18] uses partitioning, especially Cache Allocation Technology (CAT) [41] available in the LLC of some Intel processors. CAT allocates up to 4 different Classes of Services (CoS) for separate cache ways so that replacement of cache blocks is only allowed within a certain CoS. CATalyst first uses CAT mechanism to partition caches into secure and non-secure parts (non-secure parts may map to 3 CoS while secure parts map to 1 CoS). Secure pages are assigned to virtual machines (VMs) at a granularity of a page, and not shared by more than one VM. Here, attacker and victim reside in different VMs. Combined with CAT technology and pseudo-locking mechanism which pins certain page frames managed by software, CATalyst guarantees that malicious code cannot evict secure pages. CATalyst implicitly performs preloading by remapping security-critical code or data to secure pages. Flushes can only be done within each VM. And cache coherence is achieved by assigning secure pages to only one processor and not sharing pages among VMs. This cache listed extra software assumptions as follows:

Assumption 1. Security critical data is always preloaded into the cache at the beginning of the whole program execution.

Assumption 2. Security critical data is always able to fit within the secure partition of the cache. I.e. all data in the range x can fit in the secure partition.

Assumption 3. The victim and the attacker process cannot share the same memory space.

Assumption 4. Use pseudo-locking mechanism by software to make sure that victim and attacker process cannot share the same cache blocks.

Assumption 5. Secure pages are reloaded immediately after the flush, which is done by the virtual machine monitor (VMM) to make sure all the secure pages are still pinned in the secure partition.

**DAWG cache** [21] (Dynamically Allocated Way Guard) partitions the cache by cache ways and provides full isolation for hits, misses and metadata updates across different protection domains (between the attacker and the victim). DAWG cache is partitioned for the attacker and the victim and each of them keep their own different *domain\_id* (which is similar to process ID used in general caches). Each *domain\_id* has its own bit fields, one is called *policy\_fillmap*, for masking fills and selecting the victim to replace, another is called *policy\_fillmap*, for masking hit ways. Only both the tag and the *domain\_id* are the same will a cache hit happen. Therefore, DAWG allows read-only cache lines to be replicated across ways for different protection domain. For a cache miss, the victim can only be chosen within the ways belonging to the same *domain\_id*, recorded by the *policy\_fillmap*. Consistently, the replacement policy is updated with the victim selection and the metadata derived from the *policy\_fillmap* for different domains is updated as well. The paper also proposes the idea to dynamically partitions the cache ways following the system's workload changes but does not actually implement it.

**RIC cache** [20] (Relaxed Inclusion Caches) proposes a low-complexity cache to defend against eviction-based timing-based side-channel attacks on the LLC. Normally for an inclusive cache, if the data R is in the LLC, it is also in the higher level cache, and eviction of the R in the LLC will cause the same data in the higher level cache, e.g., L1 cache to be invalidated, making eviction-based attacks in the higher level cache possible (e.g., attacker is able to evict victim's security critical cache line). For RIC, each cache line is extended with a single bit to set the relaxed inclusion. Once the relaxed inclusion is set for that cache line, the corresponding LLC line eviction will not cause the same line in the higher-level cache to be invalidated. Two kinds of data will be set relaxed inclusion bit: *read only data* and *thread private data* when they are loaded into the cache. These two kinds of data are claimed by the paper to cover all the critical data for ciphers. Therefore, RIC will not prevent writable in-private critical data, which is currently not found in any ciphers. Apart from that, RIC requires flushing for the corresponding cache lines in the cases that the RIC bits are modified or for thread migration events to avoid the timing leakage during transition time.

**PL cache** [10] provides isolation by partitioning the cache based on cache blocks. It extends each cache block with a process ID and a lock status bit. The process ID and the lock status bits are controlled by the extended load and store instructions (ld.lock/ld.unlock and st.lock/st.unlock) which allow the programmer and compiler to set or reset the lock bit through use of the right load or store instruction. In terms of cache replacement policy, for a cache hit, PL cache will perform the normal cache hit handling procedure and the instructions with locking or unlocking capability can update the process ID and the lock status bits while the hit is processed. When there is a cache miss, locked data cannot be evicted by data that is not locked and locked data among different processes cannot be evicted by each other. In this case, the new data will be either loaded or stored without caching. In other cases, data eviction is possible. This cache listed extra software assumption as follows:

Assumption 1. Security critical data is always preloaded into the cache at the beginning of the whole program execution.

**RP cache** [10] uses randomization to de-correlate the memory address accessing and timing of the cache. For each block of RP cache, there is a process ID and one protection bit P set to indicate if this cache block needs to be protected or not. A permutation table (PT) stores each cache set's pre-computed permuted set number and the number of tables depends on number of protected processes. For memory access operations, cache hits need both process ID and address to be the same. When a cache miss happens to data D of a cache set S, if the to-be-evicted data and to-be-brought-in data belong to the same process but have different protection bit, arbitrary data of a random cache set S' will be evicted and D will be accessed without caching. If they belong to different processes, D will be stored in an evicted cache block of S' and mapping of S and S' will be swapped as well. Otherwise, the normal replacement policy is executed.

Newcache cache [11, 37] dynamically randomizes memory-to-cache mapping. It introduced a ReMapping Table (RMT), and the mapping between memory addresses and this RMT is as in a direct mapped cache, while the mapping between the RMT and actual cache is fully associative. The index bits of memory address are used to look up entries in the RMT to find the cache block that should be accessed. It stores the most useful cache lines rather than hold a fixed set of cache lines. This index stored in RMT combined with the process ID is used to look up the actual cache where each cache line is associated with its real index and process ID. Each cache block is also associated with a protection bit (P) to indicate if it is security critical. For cache replacement policy, it is very similar to RP cache. Cache hit needs both process ID and address to be the same. When cache miss happens to data D, arbitrary data will be evicted and D will be accessed without caching if they belong to the same process but either one of their protection bit is set. If the evicted data and brought-in data have different process IDs, D will randomly replace a cache line since it is fully associative in the actual cache. Otherwise, the normal replacement policy for direct mapped cache is executed.

**Random Fill cache** [12] de-correlates cache fills with the memory access using random filling technique. New instructions used by applications in Random Fill cache can control if the requested data belongs to a normal request or a random fill request. Cache hits are processed as in normal cache. For the security critical data accesses of the victim, a *Nofill request* is executed and the requested data access will be performed without caching. Meanwhile, on a *Random Fill request*, arbitrary data, from the range of addresses, will be brought into the cache. In the paper [12], the authors show that random fill of spatially near data does not hurt performance. For other processes' memory accesses and normal victim's memory accesses, *Normal request* will be used to achieve normal replacement policy. Victim and attacker are able to remove victim's own security critical data including

using *clflush* instructions or cache coherence protocol since the flush will not influence timing-based side-channel attack prevention (the random filling technique is used for this).

**CEASER cache** [24] is able to mitigate conflict-based LLC timing-based side-channel attacks using address encryption and dynamic remapping. CEASER cache does not differentiate whom the address belongs to and whether the address is security critical. When memory access tries to modify the cache state, the address will first be encrypted using Low-Latency BlockCipher (LLBC) [42], which not only randomizes the cache set it maps, but also scatters the original, possibly ordered and location-intensive addresses to different cache sets, decreasing the probability of conflict misses. The encryption and decryption can be done within two cycles using LLBC. Furthermore, the encryption key will be periodically changed to avoid key reconstruction. The periodic re-keying will cause the address remapping to dynamically change.

**SCATTER cache** [25] uses cache set randomization to prevent timing-based attacks. It builds upon two ideas. First, a mapping function is used to translate memory address and process information to cache set indices, the mapping is different for each program or security domain. Second, the mapping function also calculates a different index for each cache way, in a similar way to the skewed associative caches [43]. The mapping function can be keyed hash or keyed permutation derivation function – a different key is used for different application or security domain resulting in a different mapping from address to cache sets for each. Software (e.g., the operating system) is responsible for managing the security domains and process IDs which are used to differentiate the different software and assign it different keys for the mapping. For the hardware extension, a cryptographic primitive such as hashing and an index decoder for each scattered cache way is added. SCATTER cache also stores the index bits of the physical address to efficiently perform lookups and writebacks. There is also one bit per page-table entry added to allow the kernel to communicate with the user space for security domain identification.

Non Deterministic cache [19] uses cache access delay to randomize the relation between cache block access and cache access timing. There is no differentiation of data caching between different process ID or whether the data is secure or not. A per-cache-block counter records the interval of its data activeness, and is increased on each global counter clock tick when the data is untouched. When the counter reaches a predefined value, the corresponding cache line will be invalidated. Non Deterministic Cache randomly sets the local counters' initial value that is less than the maximum value of the global counter. In this case, the cache delay is changed to be randomized. Cache delay interval controlled by this non-deterministic execution can lead to different cache hit and miss statistics because the invalidation is determined by the randomized counter of each cache line, and therefore de-correlates any cache access time from the address being accessed. However, the performance degradation is tremendous.

## 5 Analysis of the Secure Caches

In this section, we manually evaluate the effectiveness of the 18 secure caches [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25]. We analyze how well the different caches can protect against the 72 types of vulnerabilities defined in Table 2 and Table 3, which cover all the possible *Strong* (according to the definition in Seciton 3) cache timing-based vulnerabilities. Following the analysis, discuss what types of secure caches and features are best suited for defending different types of timing-based attacks.

## 5.1 Effectiveness of the Secure Caches Against Timing-Based Attacks

Table 4 and Table 5 list the result of our analysis of which caches can prevent which types of attacks. Some caches are able to prevent certain vulnerabilities, denoted by a checkmark,  $\checkmark$ , and green color in the table. For example, SP\* cache can defend against  $V_u \rightsquigarrow A_d \rightsquigarrow V_u$  (slow) (one type of Evict + Time [31]) vulnerability. For some other caches and vulnerabilities, the cache is not able to prevent the vulnerabilities and it is indicated by  $\times$  and red color. For example, SecDCP cache cannot defend against  $V_u \rightsquigarrow V_a \rightsquigarrow V_u$  (slow) (one type of Bernstein's Attack [3]) vulnerability.

Each cache is analyzed for each type of vulnerability listed in Table 2 and Table 3. A cache is judged to be able to prevent a type of cache timing-based vulnerability in three cases:

- 1. A cache can prevent a timing attack if the timing of the last step in a vulnerability is always constant and the attacker can never observe fast and slow timing difference for the given set of three steps. For instance, in a regular set-associative cache, the  $V_d \rightsquigarrow V_u \rightsquigarrow A_a$  (fast) (one type of Flush + Reload [30]) vulnerability will allow the attacker to know that address *a* maps to secret *u* when the attacker observes fast timing, compared with observing slow timing in the other cases. However, in case of the RP cache [10] will make the timing of the last step to be always slow because RP cache does not allow data of different processes to derive cache hit between each other.

- 2. A cache can prevent a timing attack if the timing of last step is randomized and cannot have original corresponding relation between victim's behavior and attacker's observation. For instance,  $A_d \rightsquigarrow V_u \rightsquigarrow A_d^{inv}$  (fast) (one type of Prime + Probe Invalidation) vulnerability when executed on a normal set-associative cache will allow the attacker to know that the address d has the same index with secret u when observing fast timing, compared with slow timing in the other cases. However, when executing this attacks on the Random Fill cache [12], for example a slow timing will not determine that u and d have the same index as the secret, since in Random Fill cache u would be accessed without caching and another random data would be cached instead.