## Imperial College London

#### Department of Electrical and Electronic Engineering

# Ultra-Low Power Mixed-Signal Frontend for Wearable EEGs

Mohammad Usaid Abbasi May 2021

Supervised by Prof. Esther Rodriguez-Villegas

A Thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College London.

**Declaration of Originality**

It is to certify that all the material in this thesis is my work, and I have appropriately

acknowledged the source of any work that is not my own. This thesis was not and will not be

submitted to any other university or institution for fulfilling the requirements of a degree.

**Copyright Declaration**

The copyright of this work rests with the author and is made available under a Creative

Commons Attribution - Non-Commercial 4.0 International License (CC BY-NC). Researchers

are allowed to copy, distribute or transmit the thesis in any medium or format, on the condition

that they attribute it appropriately, and that they do not use this work or any derivative of this

work for commercial purposes. For any reuse or redistribution, researchers must make clear to

others the license terms of this work.

Mohammad Usaid Abbasi

May 2021

2

# **Abstract**

Electronics circuits are ubiquitous in daily life, aided by advancements in the chip design industry, leading to miniaturised solutions for typical day to day problems. One of the critical healthcare areas helped by this advancement in technology is electroencephalography (EEG). EEG is a non-invasive method of tracking a person's brain waves, and a crucial tool in several healthcare contexts, including epilepsy and sleep disorders. Current ambulatory EEG systems still suffer from limitations that affect their usability. Furthermore, many patients admitted to emergency departments (ED) for a neurological disorder like altered mental status or seizures, would remain undiagnosed hours to days after admission, which leads to an elevated rate of death compared to other conditions. Conducting a thorough EEG monitoring in early-stage could prevent further damage to the brain and avoid high mortality. But lack of portability and ease of access results in a long wait time for the prescribed patients.

All real signals are analogue in nature, including brainwaves sensed by EEG systems. For converting the EEG signal into digital for further processing, a truly wearable EEG has to have an analogue mixed-signal front-end (AFE). This research aims to define the specifications for building a custom AFE for the EEG recording and use that to review the suitability of the architectures available in the literature. Another critical task is to provide new architectures that can meet the developed specifications for EEG monitoring and can be used in epilepsy diagnosis, sleep monitoring, drowsiness detection and depression study.

The thesis starts with a preview on EEG technology and available methods of brainwaves recording. It further expands to design requirements for the AFE, with a discussion about critical issues that need resolving. Three new continuous-time capacitive feedback chopped amplifier designs are proposed. A novel calibration loop for setting the accurate value for a pseudoresistor, which is a crucial block in the proposed topology, is also discussed. This pseudoresistor calibration loop achieved the resistor variation of under 8.25%.

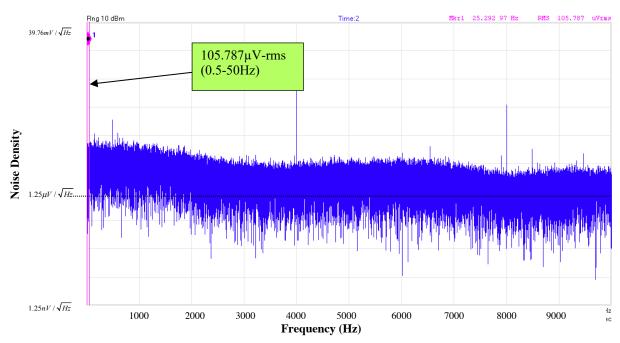

The thesis also presents a new design of a curvature corrected bandgap, as well as a novel DDA based fourth-order Sallen-Key filter. A modified sensor frontend architecture is then proposed, along with a detailed analysis of its implementation. Measurement results of the AFE are finally presented. The AFE consumed a total power of 3.2µA (including ADC, amplifier, filter, and current generation circuitry) with the overall integrated input-referred noise of

$0.87\mu V$ -rms in the frequency band of 0.5-50Hz. Measurement results confirmed that only the proposed AFE achieved all defined specifications for the wearable EEG system with the smallest power consumption than state-of-art architectures that meet few but not all specifications. The AFE also achieved a CMRR of 131.62dB, which is higher than any studied architectures.

-To my family-

# **ACKNOWLEDGEMENTS**

I could not have been able to finish this PhD without the help of a lot of people.

First, I would like to thank my parents for encouraging me to embark on this journey and frequently motivated me to carry on. I would like to mention my late grandfather, Dr Zahoor Ahmad for being a source of inspiration all those years. I want to thank my wife, Kamilia for enduring with me over the years when I had no time to commit to other activities. And especially grateful to my son, Yazan who have to bear with the absence of his father on many evenings and the weekends, and sometimes on bank holidays.

I would like to especially thank my supervisor Professor Esther Rodriguez-Villegas, for supporting me over the years and pushed me to achieve more in my work without overburdening.

I would also like to thank Dr Ruchir Saraswat for frequently providing me listening ears when I had to share some idea or a key finding and being there as a guide and a friend. I am also grateful to Dr Syed Anas Imtiaz for extending a helping hand and being there when I needed him.

Thanks, are also due to my colleagues and friends - Amit, Piyush, Saam, Zhou for taking time out and reviewing my work.

I must especially thank Mrs. Wiesia Hsissen, to help me with any admin issues.

Thanks, are also due to my managers - Robert Sneddon and Richard Goldman for providing me with the research funding and supporting my decision to pursue the PhD while working at Intel.

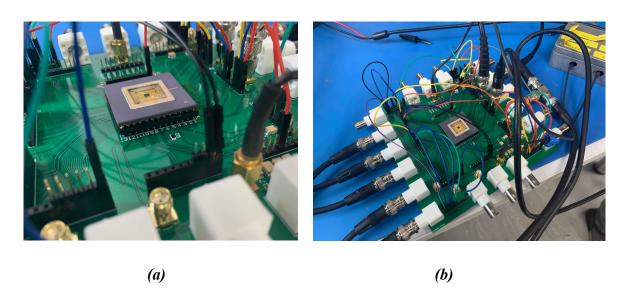

I must also thank my friends Nabil and Abdou for helping me with the chip testing and planning. I especially want to mention Nagaraju for guiding me in the PCB designing.

I would like to especially mention my mentor and friend, Dr Qadeer Ahmad Khan, who motivated me to pursue analogue mixed-signal circuit designing as a career.

Well, if I have forgotten any names then please forgive me as it was not intentional.

# **Table of Contents**

| Dec    | laration of Originality                                                       | 2  |

|--------|-------------------------------------------------------------------------------|----|

| Cop    | yright Declaration                                                            | 2  |

| Abs    | tract                                                                         | 3  |

| List   | of Figures                                                                    | 10 |

| List   | of Tables                                                                     | 16 |

| List   | of Acronyms                                                                   | 17 |

| Chapte | er 1 - Electroencephalography                                                 | 20 |

| 1.1    | Overview                                                                      | 20 |

| 1.2    | History and evolution of electroencephalography                               | 20 |

| 1.3    | Basics of bioelectrical signals and nature of EEG                             | 21 |

| 1.4    | EEG recording                                                                 | 24 |

| 1.5    | The Electrode-tissue Interface                                                | 26 |

| 1.6    | EEG application areas                                                         | 27 |

| 1.7    | Wearable electroencephalography                                               | 29 |

| Refe   | erences:                                                                      | 33 |

| Chapte | er 2 - Design Specifications and Literature Review                            | 38 |

| 2.1    | Overview                                                                      | 38 |

| 2.2    | Major challenges in designing an EEG recording system                         | 39 |

| 2.3    | Dynamic offset reduction techniques for a precision amplifier                 | 41 |

| 2.4    | Chopper modulation technique for reducing the DC offset and the flicker Noise | 42 |

| 2.5    | Specifications for the EEG analogue frontend                                  | 46 |

| 2.6    | Literature review of the EEG analogue frontend                                | 48 |

| 2.7    | EEG recording system designed for this research                               | 50 |

| 2.8    | Conclusion                                                                    | 50 |

| Refe   | erences                                                                       | 51 |

| Chapte | er 3 - Towards an ultra-low power amplifier for EEG recording system          | 54 |

| 3.1    | Background study on EEG amplifiers                                            | 54 |

| 3.2    | Capacitively coupled EEG amplifier                                            | 57 |

| 3.3    | Noise limit for a differential pair                                           | 59 |

| 3.4    | Fully differential folded-cascode amplifier                                   | 60 |

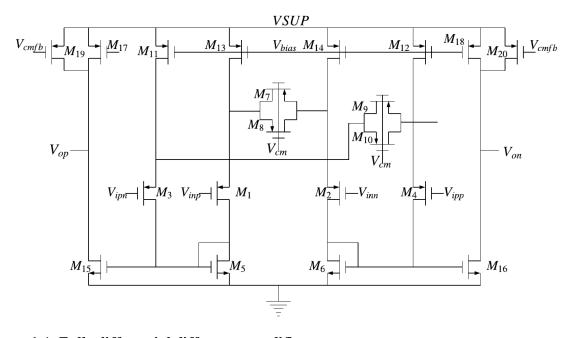

| 3.5         | Common-mode feedback circuit                                                        | 65     |

|-------------|-------------------------------------------------------------------------------------|--------|

| 3.6         | Two-stage fully differential amplifier with a chopping modulation scheme            | 67     |

| 3.7<br>(CCF | Chopper based capacitive feedback EEG amplifier using modified pseudo- resi         |        |

| 3.8<br>(CCF | Chopper based capacitive feedback EEG amplifier using duty-cycled resistors FEA-II) | 91     |

| 3.9         | Proposed calibration loop for setting an accurate value of a pseudo-resistor        | 101    |

| 3.10        | Conclusion                                                                          | 105    |

| Refe        | rences                                                                              | 106    |

| Chapter     | r 4 - Pseudo-Resistor Design                                                        | 110    |

| 4.1         | Introduction                                                                        | 110    |

| 4.2         | State-of-art implementations and novel pseudoresistors                              | 112    |

| 4.3         | Conclusion                                                                          | 124    |

| Refe        | rences                                                                              | 125    |

| Chapter     | r 5 - A high PSRR, ultra-low power curvature-corrected bandgap voltage reference    | ce 127 |

| 5.1         | Traditional low-voltage bandgap reference                                           | 127    |

| 5.2         | Proposed low-voltage curvature corrected current mode BGR                           | 130    |

| 5.3         | Conclusion                                                                          | 134    |

| Refe        | rences                                                                              | 135    |

| Chapte      | r 6 - Sallen-Key Low Pass Filter Design                                             | 137    |

| 6.1         | Introduction                                                                        | 137    |

| 6.2         | Sallen-Key low pass filter design                                                   | 138    |

| 6.3         | Design of a fully differential difference amplifier                                 | 139    |

| 6.4         | DDA based fully-differential Sallen-Key low pass filter                             | 142    |

| 6.5         | A duty-cycled resistor                                                              | 143    |

| 6.6         | Fourth order Sallen-Key low-pass filter                                             | 145    |

| 6.7         | Conclusion                                                                          | 147    |

| Refe        | rences                                                                              | 147    |

| Chapte      | r 7 - The complete analogue front-end for EEG applications                          | 149    |

| 7.1         | Introduction                                                                        | 149    |

| 7.2         | Non-overlapping clock generation circuit                                            | 149    |

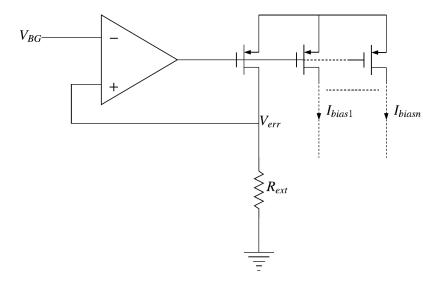

| 7.3         | Current generation block                                                            | 150    |

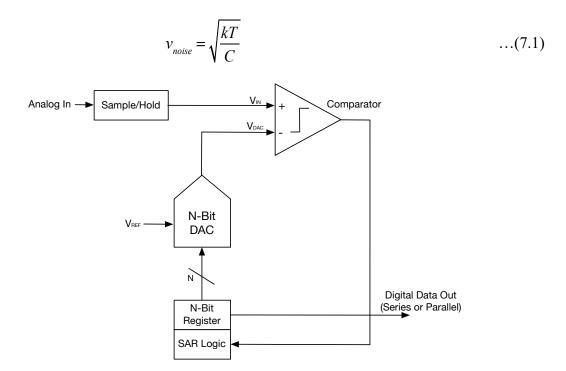

| 7.4     | 12-Bit fully differential SAR ADC                       | 151 |

|---------|---------------------------------------------------------|-----|

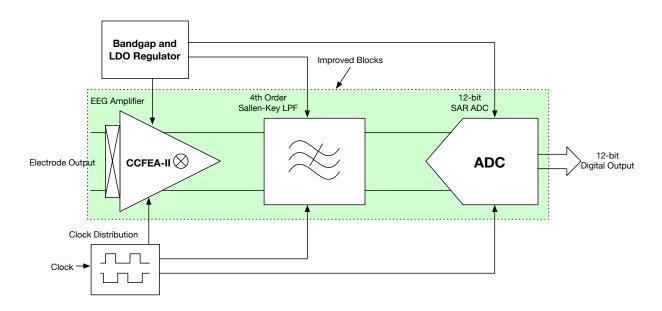

| 7.5     | Proposed AFE Design                                     | 160 |

| 7.7     | Conclusion                                              | 167 |

| Refe    | rences                                                  | 167 |

| Chapter | r 8 - Conclusion and Future Work                        | 169 |

| 8.1     | Conclusion                                              | 169 |

| 8.2     | Future Work                                             | 170 |

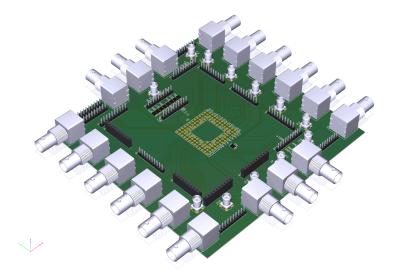

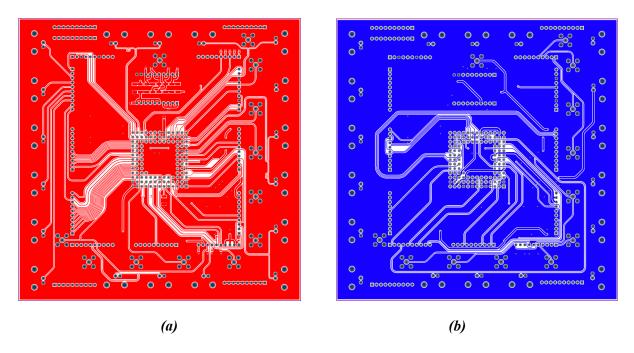

| Append  | lix A - Discussion on the PCB design and the test setup | 172 |

# **List of Figures**

| Figure 1.1 | Nerve cell (a neuron) structure                                                             |

|------------|---------------------------------------------------------------------------------------------|

| Figure 1.2 | EEG samples showing different frequency signals [redrawn from 9]                            |

| Figure 1.3 | Location and Nomenclature of 10% electrode positions standardized by the                    |

|            | American Electroencephalographic Society [Redrawn from 10]                                  |

| Figure 1.4 | International 10-20 system, seen from left and top of the head. $A = Ear\ lobe,\ C =$       |

|            | central, $Pg = nasopharyngeal$ , $P = parietal$ , $F = frontal$ , $Fp = frontal$ polar, $O$ |

|            | = occipital [Redrawn from 10].                                                              |

| Figure 1.5 | Bipolar and Unipolar measurement [Redrawn from 10]25                                        |

| Figure 1.6 | Approximate small signal model for skin-electrode interface                                 |

| Figure 1.7 | Biopotential signals and their frequency band [16]29                                        |

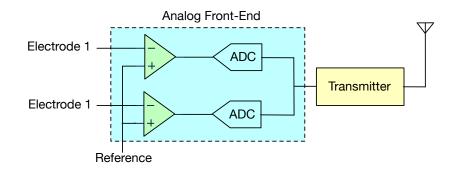

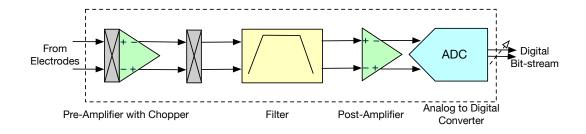

| Figure 2.1 | Placement of the instrumentation amplifier in an EEG recording system 38                    |

| Figure 2.2 | A simplified two-channel wireless EEG recording system [12]39                               |

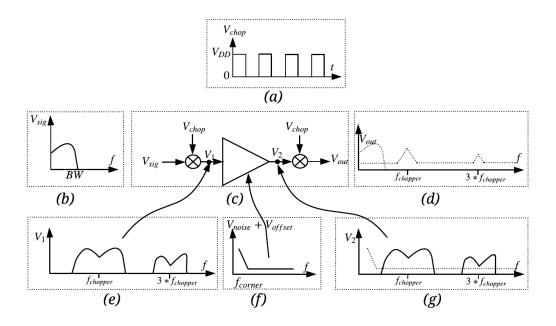

| Figure 2.3 | Chopper modulation technique to reduce 1/f noise and dc offset [5], (a) square              |

|            | modulating clock signal, (b) input signal, (c) input and output chopper connected           |

|            | to the amplifier, (d) frequency spectrum after the chopping, separating the noise           |

|            | and the input signal, (e) input signal modulated to $f_{chop}$ , (f) noise and the offset   |

|            | contributed by the amplifier, (g) amplifier noise and the offset added to the input         |

|            | signal                                                                                      |

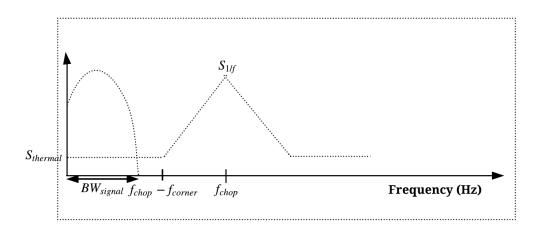

| Figure 2.4 | Power spectral density of the relevant signal and the noise after chopping [25].44          |

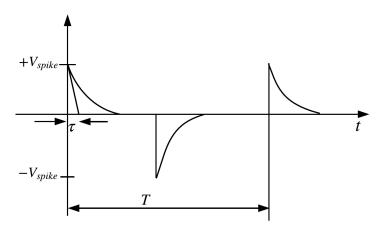

| Figure 2.5 | Spike at the output of the modulator, causing residual offset [12]                          |

| Figure 2.6 | A single channel analogue front-end for an EEG recording system [26] 47                     |

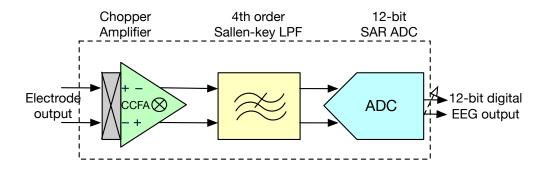

| Figure 2.7 | Top-level architecture of the proposed analogue front-end for EEG recording 50              |

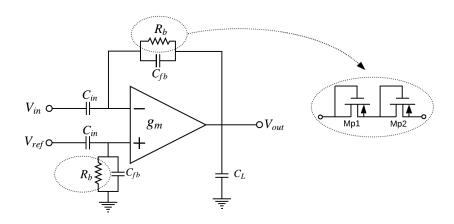

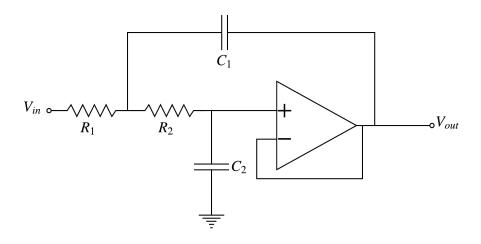

| Figure 3.1 | Capacitive feedback neural amplifier proposed by Reid [1]                                   |

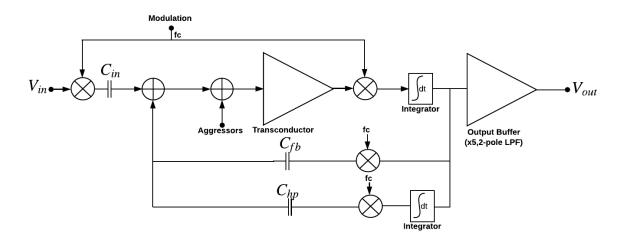

| Figure 3.2 | A chopper-capacitive feedback neural amplifier proposed presented in [6] 56                 |

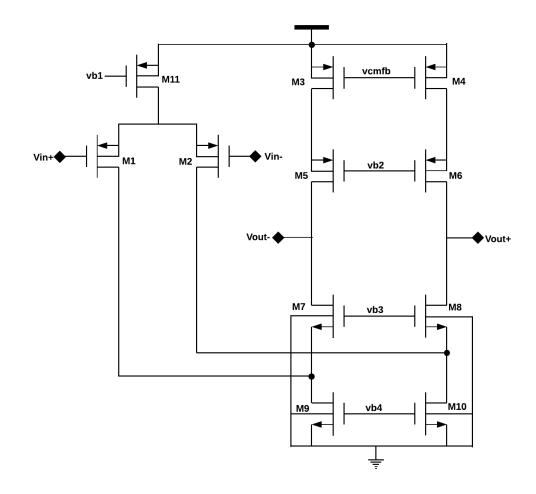

| Figure 3.3 | Conventional fully-differential folded cascode amplifier [14]61                             |

| Figure 3.4 | (a) A two-port model for an amplifier [16], (b) small-signal equivalent model for           |

|            | a MOS device61                                                                              |

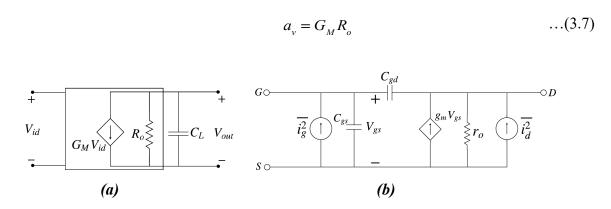

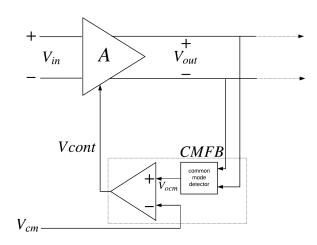

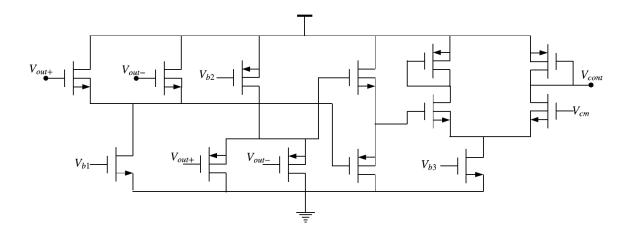

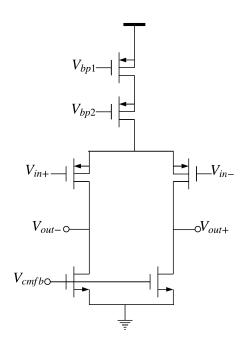

| Figure 3.5 | Concept of a common mode feedback circuit for a fully-differential circuit [23].            |

|            | 65                                                                                          |

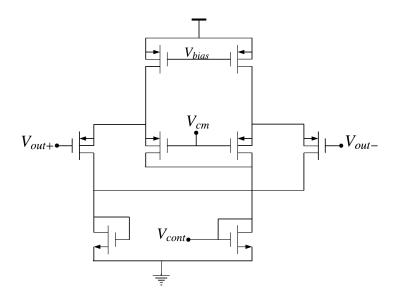

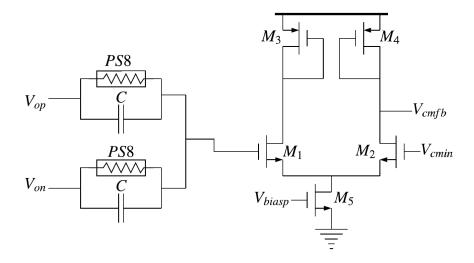

| Figure 3.6 | Improved frequency response continuous-time rail-to-rail CMFB circuit used in               |

|            | the first stage amplifier $(A_{vl})$ . 66                                                   |

| Figure 3.7 | DDA based CMFB circuit used in the second stage amplifier, $A_{v2}$ [27]                    |

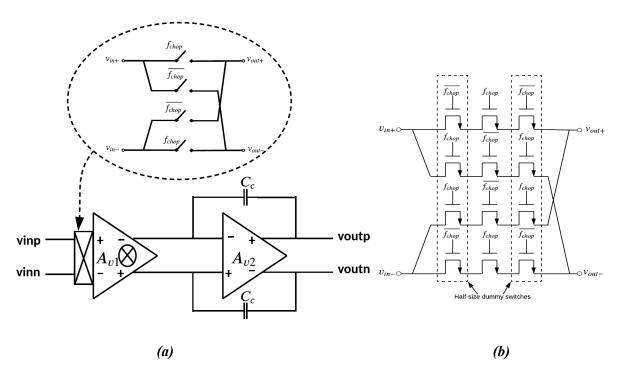

| Figure 3.8 (a) Architecture of the two-stage fully-differential chopped amplifier, $A_{amp}$ [6-7]    |

|-------------------------------------------------------------------------------------------------------|

| (b) switches used in the chopping modulator [52]                                                      |

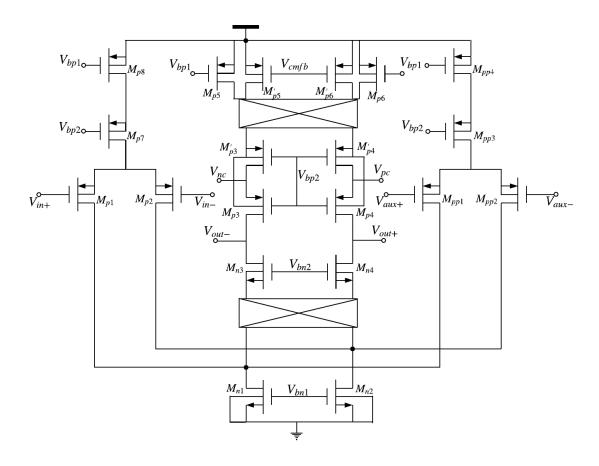

| Figure 3.9 Folded cascode amplifier $(A_{vl})$ implemented with indirect compensation and             |

| auxiliary path for ripple rejection68                                                                 |

| Figure 3.10 Common source amplifier used as the second stage $(A_{v2})$ for achieving large output    |

| swing                                                                                                 |

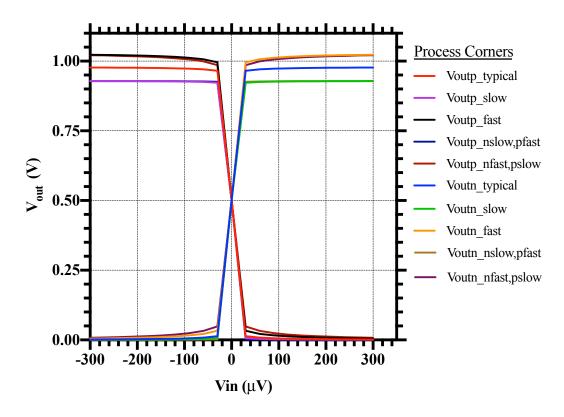

| Figure 3.11 Simulated process corner DC sweep result for the two-stage amplifier, $A_{amp}$           |

| Amplifier exhibited consistent gain up to the ground and the supply rail                              |

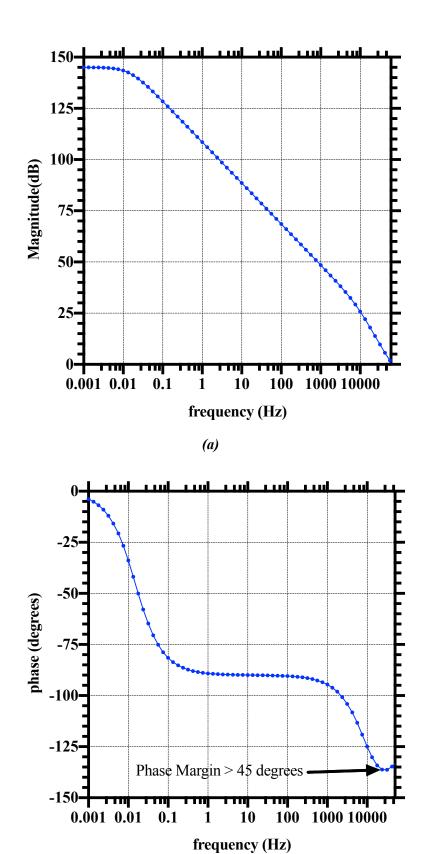

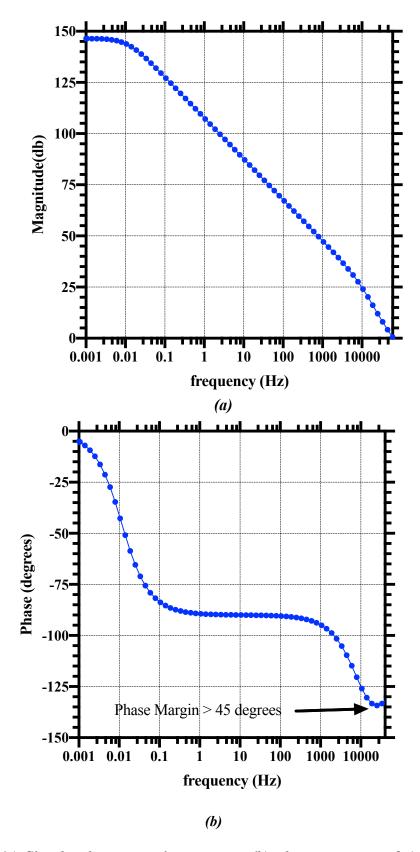

| Figure 3.12 (a) Simulated output gain response, (b) phase response of $A_{amp}$ at the typical        |

| corner. The response shows phase margin of over 45 degrees with no complex                            |

| poles. Left hand plane zero at unity gain frequency improved the phase margin.71                      |

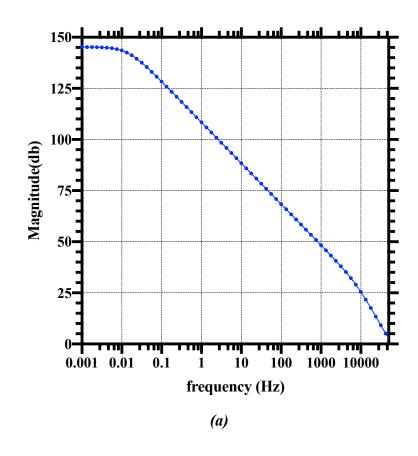

| Figure 3.13 (a) Simulated output gain response, (b) phase response of $A_{amp}$ at the fast corner    |

| The response shows phase margin of over 45 degrees with no complex poles 72                           |

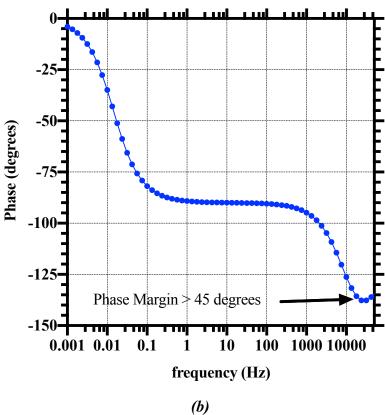

| Figure 3.14 (a) Simulated output gain response, (b) phase response of $A_{amp}$ at the slow corner    |

| The response shows phase margin of over 45 degrees with no complex poles 73                           |

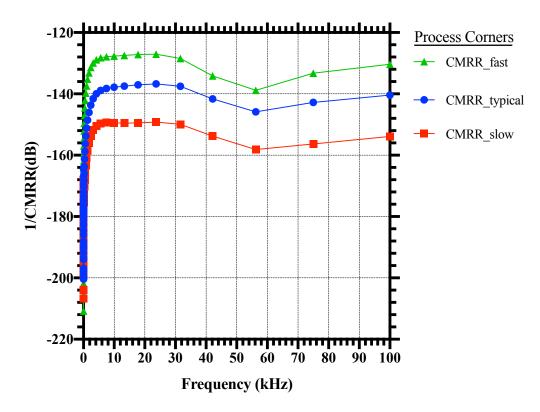

| Figure 3.15 Simulated process corner common mode rejection ratio for the two-stage core               |

| amplifier, $A_{amp.}$ . Worst case common mode gain achieved is larger than 120dB (less               |

| than -120dB for negative value)74                                                                     |

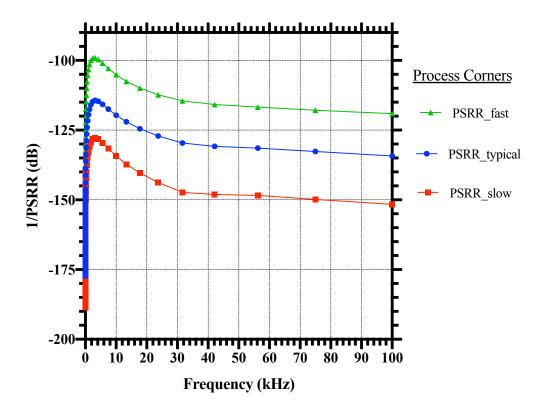

| Figure 3.16 Simulated process corner PSRR for the two-stage core amplifier, $A_{amp.}$ . Worst case   |

| power supply gain achieved is below -100dB                                                            |

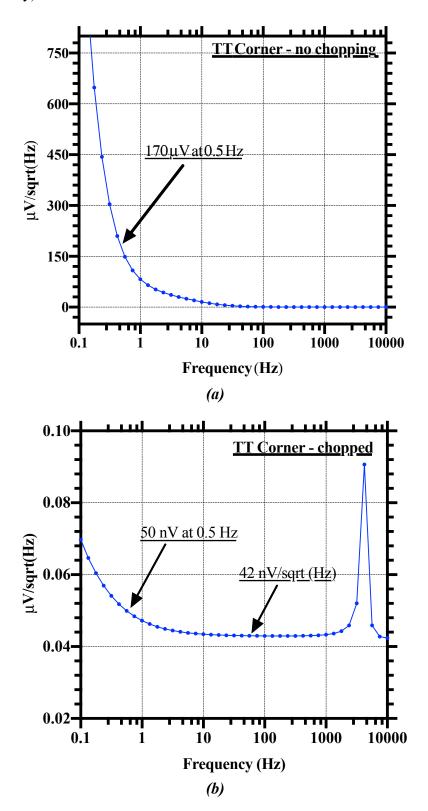

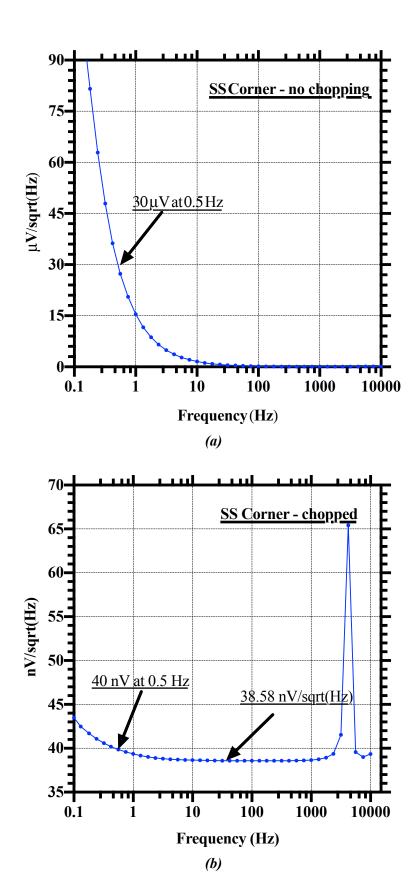

| Figure 3.17 Simulated input noise density of the core amplifier, $A_{amp}$ – (a) without the chopping |

| (b) with the chopping (typical corner)76                                                              |

| Figure 3.18 Simulated input noise density of the core amplifier, $A_{amp}-(a)$ without the chopping   |

| (b) with the chopping (slow corner)                                                                   |

| Figure 3.19 Simulated input noise density of the core amplifier, $A_{amp}-(a)$ without the chopping   |

| (b) with the chopping (fast corner)                                                                   |

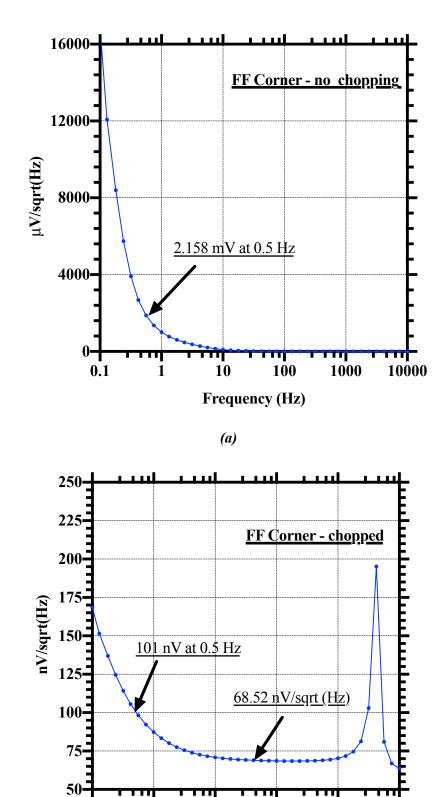

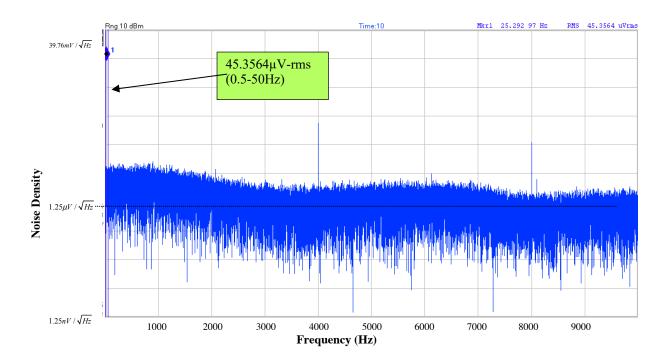

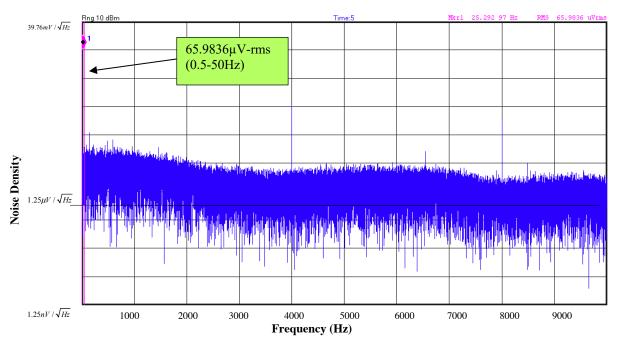

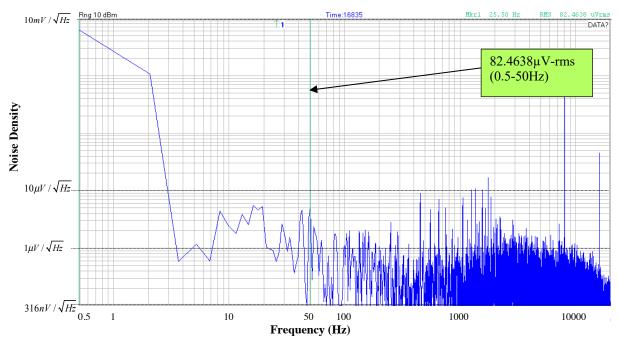

| Figure 3.20 Measured output noise for the two-stage core amplifier, $A_{amp}$ (in closed loop         |

| configuration). A closed loop gain of $100$ is used (50 $\Omega$ impedance is used for the            |

| measurement)79                                                                                        |

| Figure 3.21 Chopped capacitive feedback EEG amplifier (CCFEA-I) with PFB, DSL and RRI                 |

| loop                                                                                                  |

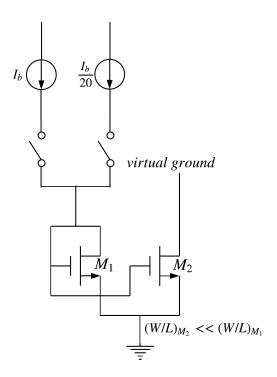

| Figure 3.22 Additional current source for speeding-up the transient settling in the simulation        |

| [6]81                                                                                                 |

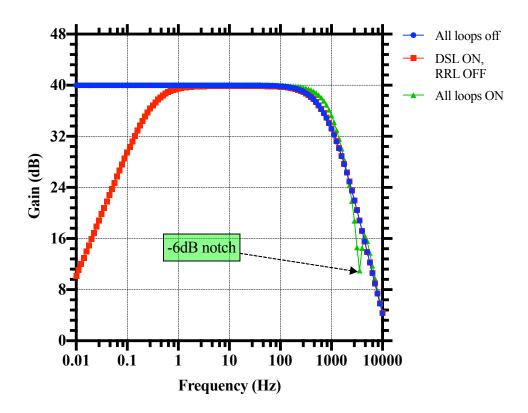

| Figure 3.23 Simulated gain transfer function of the CCFEA-I (using Cadence's pss/pa             | lC |

|-------------------------------------------------------------------------------------------------|----|

| analysis)8                                                                                      | 4  |

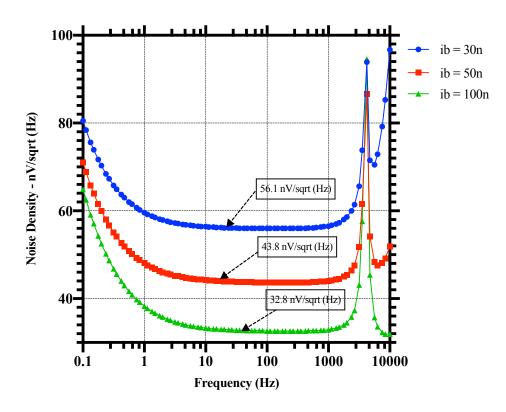

| Figure 3.24 Simulated input referred noise simulation, using Cadence's pss/pnoise analysis      | _  |

| DSL and RRL are disabled                                                                        | 5  |

| Figure 3.25 Simulated input referred noise simulation, using Cadence's pss/pnoise analysis      | _  |

| DSL is ON and RRL is off                                                                        | 5  |

| Figure 3.26 Measured output noise for the CCFEA-I when RRL is off (50 $\Omega$ impedance is use | d  |

| for the measurement)8                                                                           | 6  |

| Figure 3.27 Measured output noise of the CCFEA-I for the condition when both DSL and RR         | L  |

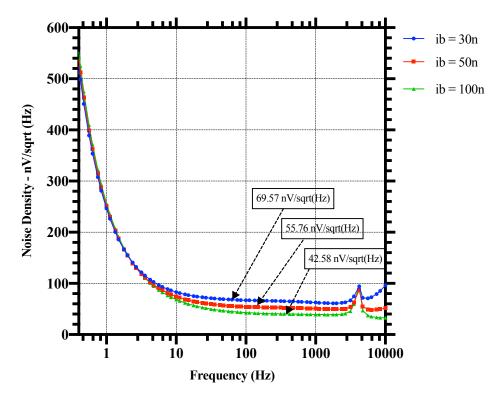

| are ON ( $f_{chop}=4kHz$ ) (50 $\Omega$ impedance is used for the measurement)                  | 6  |

| Figure 3.28 Simulated input referred noise simulation, using Cadence's pss/pnoise analysis      | _  |

| DSL and RRL both are ON8                                                                        | 7  |

| Figure 3.29 Measured output noise for the CCFEA-I when both loops are active, an                | d  |

| ibias=75n (50 $\Omega$ impedance is used for the measurement)                                   | 7  |

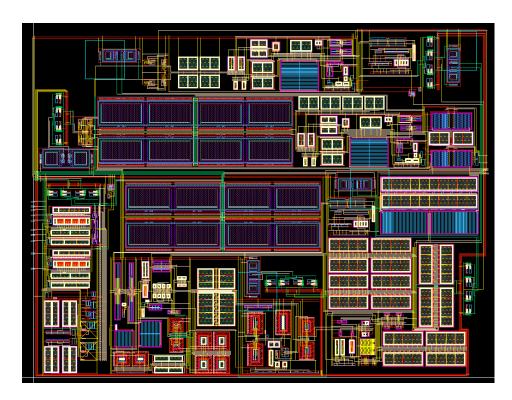

| Figure 3.30 Layout of the chopped capacitive feedback amplifier                                 | 8  |

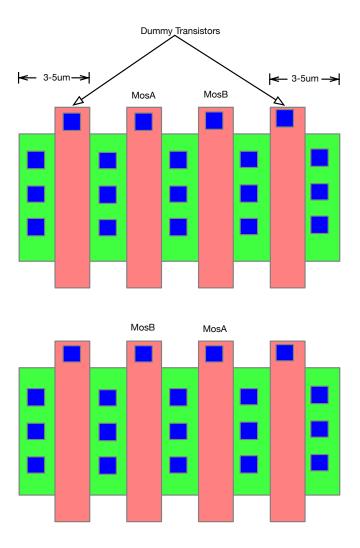

| Figure 3.31 Common-centroid layout matching pattern along with dummy transistors 8              | 9  |

| Figure 3.32 Interdigitated layout matching pattern along with dummy transistors9                | 0  |

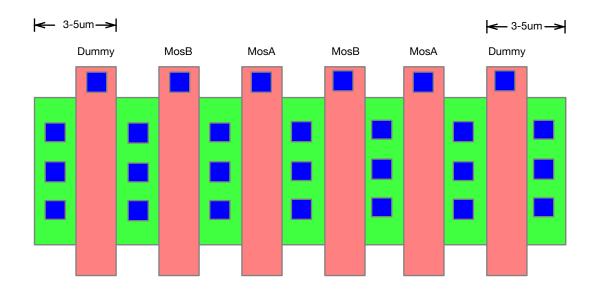

| Figure 3.33 Measured stimulus response for the CCFEA-I with a 2mV peak to peak sine way         | 'e |

| and a 50mV DC offset9                                                                           | 0  |

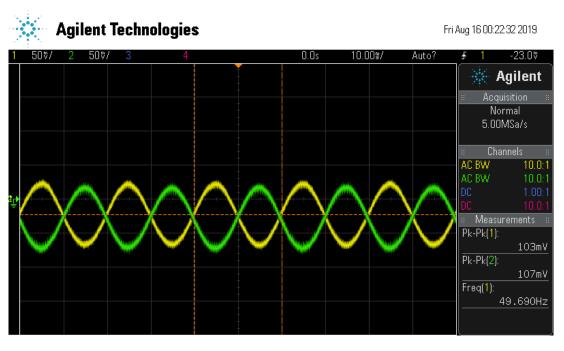

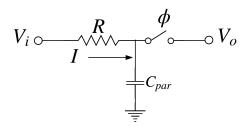

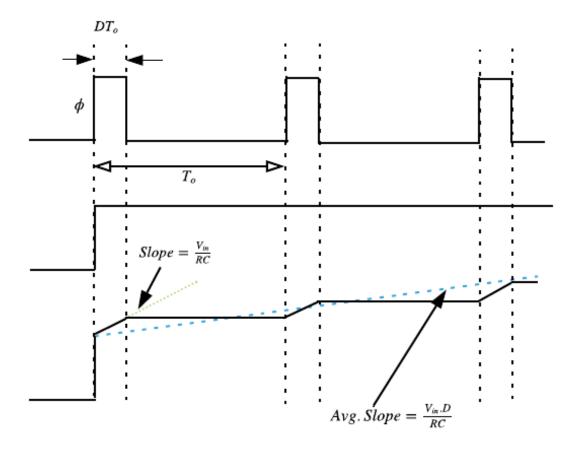

| Figure 3.34 (a) Timing signal for the duty cycled resistor, (b) A duty-cycled resistor (DCF     | ?) |

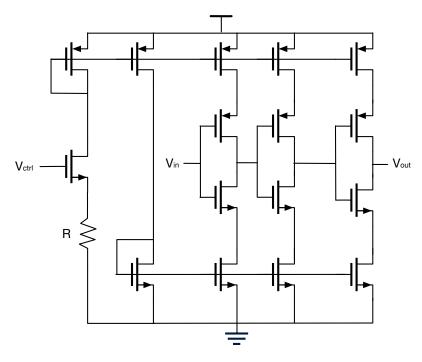

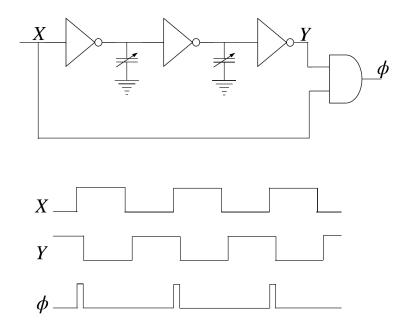

| [8], (c) Pulse generator circuit with current starved inverters voltage control dela            | !y |

| line (CSI-VCDL) [40]9                                                                           | 1  |

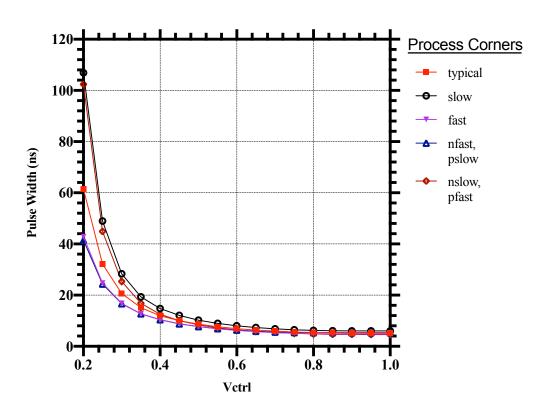

| Figure 3.35 A current starved cascaded inverters voltage controlled delay line (CSI-VCDI        | (ر |

| used to control the pulse-width [40]9                                                           | 3  |

| Figure 3.36 Simulated process corners result for the pulse width variation9                     | 3  |

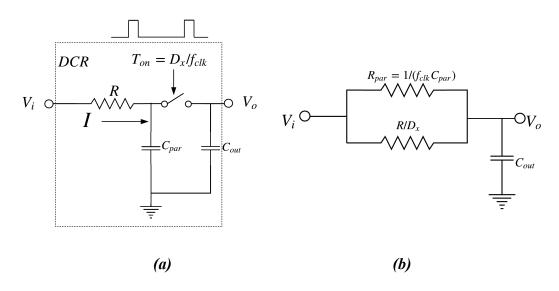

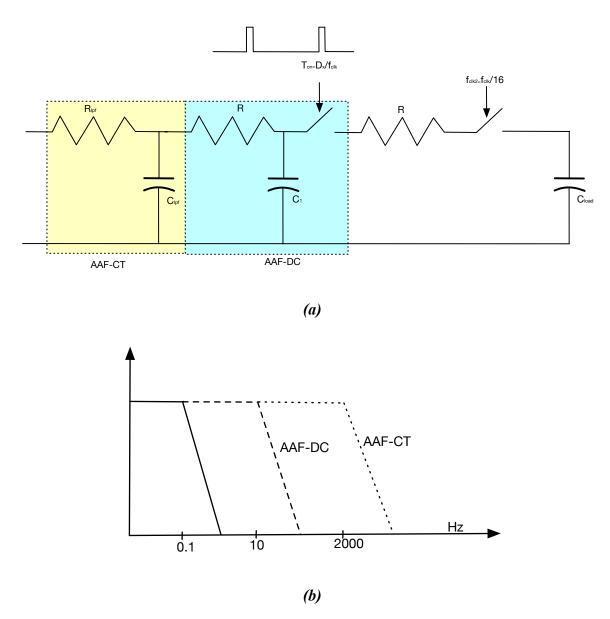

| Figure 3.37 (a) Parasitic capacitor in the low pass filter build by a duty cycled resistor, (b) | )  |

| Equivalent circuit of the LPF9                                                                  | 4  |

| Figure 3.38 (a) Multi-rate duty cycle resistor used in the CCFEA-II, (b) Frequency respons      | e  |

| of the MDCR [38]9                                                                               | 5  |

| Figure 3.39 Chopper based capacitive feedback EEG amplifier (CCFEA-II) with PFB, DS             | L  |

| and RRL loop. A switched-resistor is used instead of a pseudoresistor9                          | 6  |

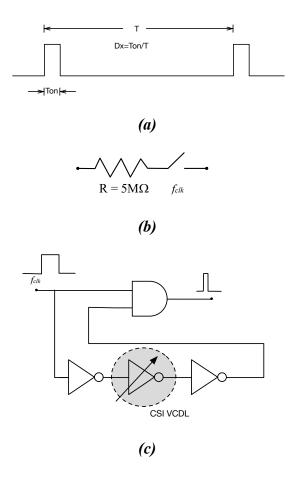

| Figure 3.40 Measured gain transfer function of the CCFEA-II, when all feedback loops ar         | ·e |

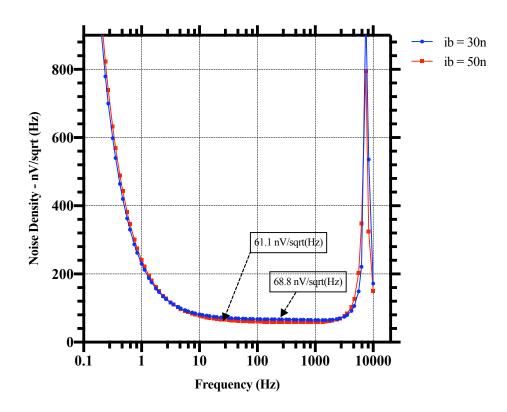

| active9                                                                                         | 7  |

| Figure 3.41   | Simulated input referred noise voltage of CCFEA-II, using Cadence's pss/pnoise      |

|---------------|-------------------------------------------------------------------------------------|

| а             | analysis – DSL and RRL both are active98                                            |

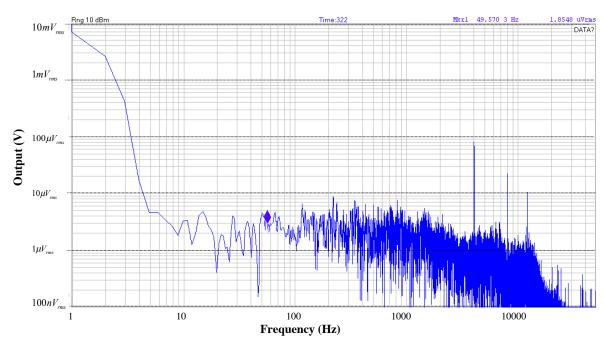

| Figure 3.42   | Measured output noise for the CCFEA-II when all loops are active, and ibias=50 $n$  |

| (             | $750\Omega$ impedance is used for the measurement)                                  |

| Figure 3.43   | Measured output noise for the CCFEA-II when the RRL loop was disabled (50 $\Omega$  |

| i             | mpedance is used for the measurement)99                                             |

| Figure 3.44   | Final layout implementation of the CCFEA-II99                                       |

| Figure 3.45   | Measured differential output gain with a 200mVp-p common-mode sine wave             |

| S             | ignal. Common mode gain is -91.6dB, and with a differential gain of 40db,           |

| (             | CMRR= -131.62dB (50 $\Omega$ impedance is used for the measurement)                 |

| Figure 3.46   | Measured differential output gain with a power supply noise of 200mVp-p sine        |

| ν             | wave. Power supply gain is -80.5dB, and with a differential gain of 40db, PSRR=     |

| -             | 120.5dB                                                                             |

| Figure 3.47   | Basic tunable pseudoresistor element [44]103                                        |

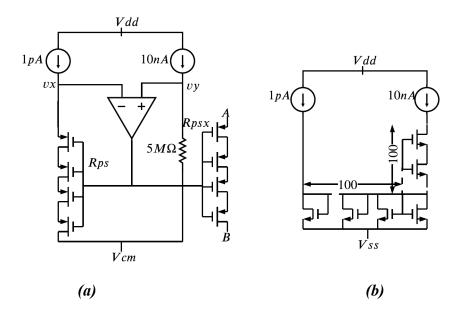

| Figure 3.48   | (a) Negative feedback calibration loop, (b) series-parallel current division 103    |

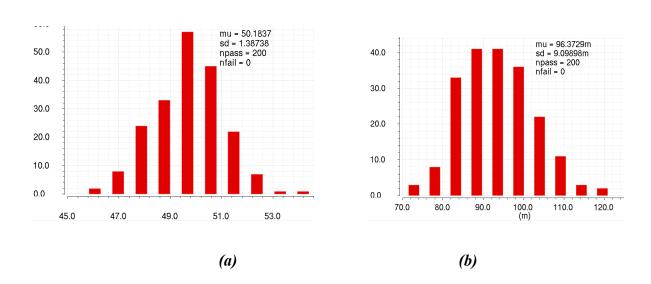

| Figure 3.49   | (a) Simulated Monte-Carlo variation for the pseudo-resistor value ( $N=200$ ), (b)  |

| S             | Simulated Monte-Carlo variation in the high-pass cut-off frequency for capacitive   |

| C             | coupled amplifier CCFEA-III                                                         |

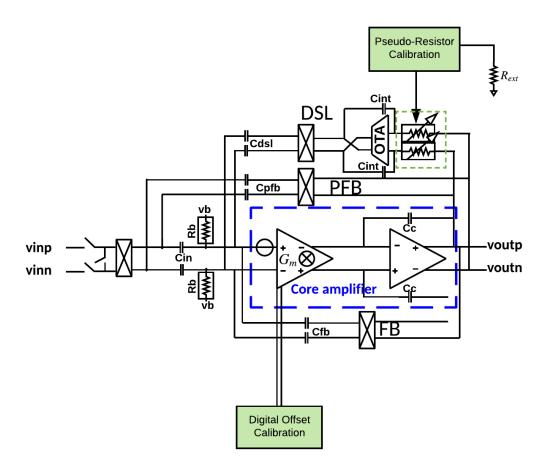

| Figure 3.50   | Chopped capacitive feedback EEG amplifier (CCFEA-III) with pseudo-resistor          |

| C             | calibration loop and digital offset correction104                                   |

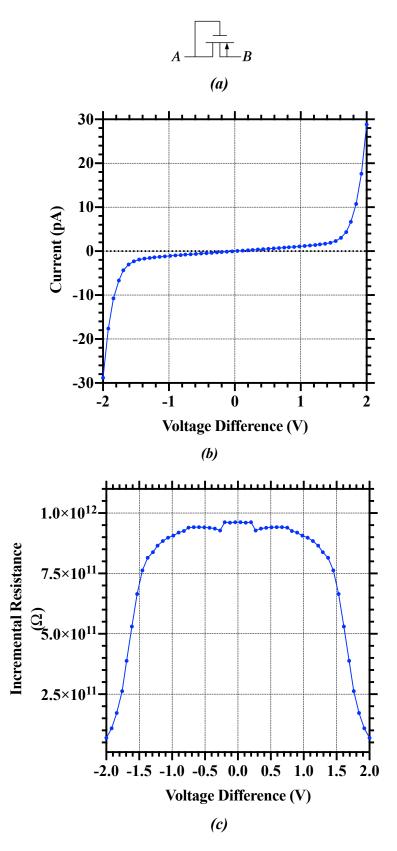

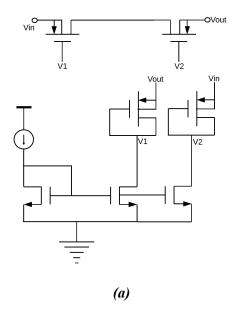

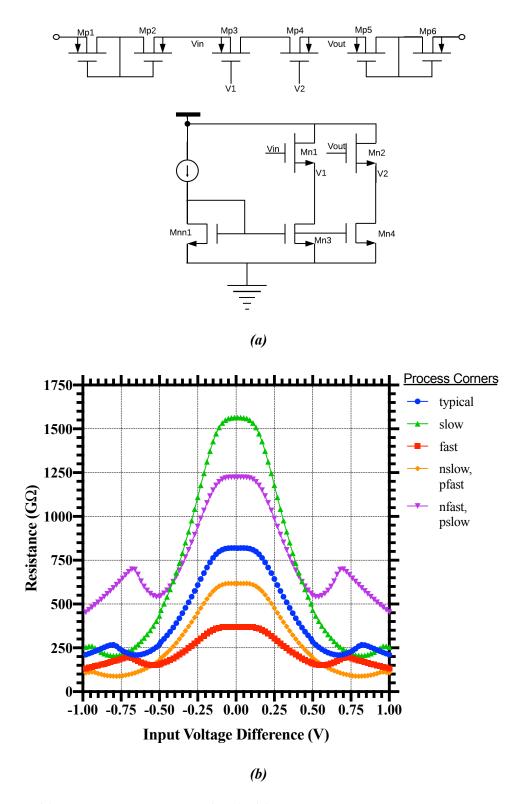

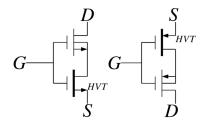

| Figure 4.1 (  | (a) MOS_bipolar element (b) Simulated Current-Voltage characteristics of MOS-       |

| b             | pipolar element [3] (c) Simulated incremental resistance of a single MOS-bipolar    |

| $\epsilon$    | element. For a low voltage difference, this incremental resistance can be very high |

| [             | 73]                                                                                 |

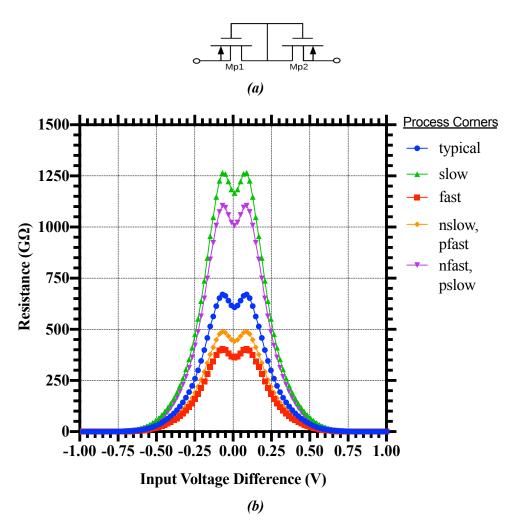

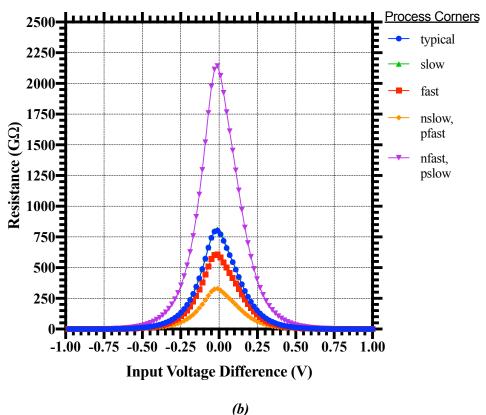

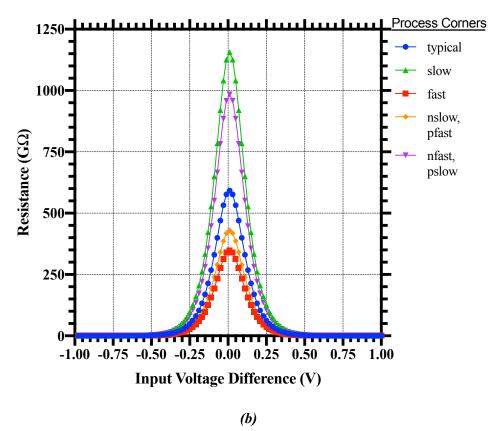

| Figure 4.2 (d | a) Pseudoresistor type 1(PS1) [5], (b) Simulated cross-corner resistance variation  |

| f             | for PS1                                                                             |

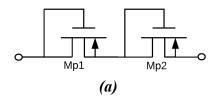

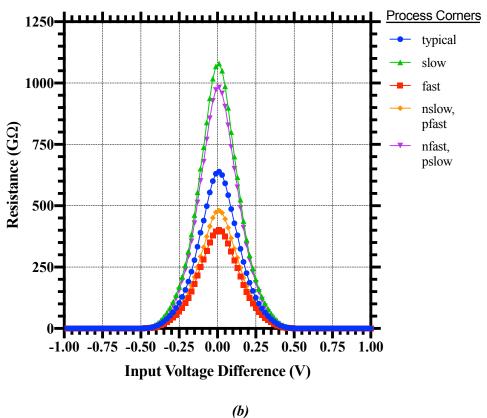

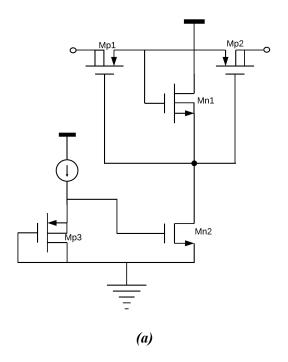

| Figure 4.3    | (a) Pseudoresistor type 2 (PS2) [3-4], (b) Simulated cross-corner resistance        |

| ν             | variation for PS2                                                                   |

| Figure 4.4 (d | a) Pseudoresistor type 3 (PS3) [7], (b) Simulated cross-corner resistance variation |

| f             | for PS3                                                                             |

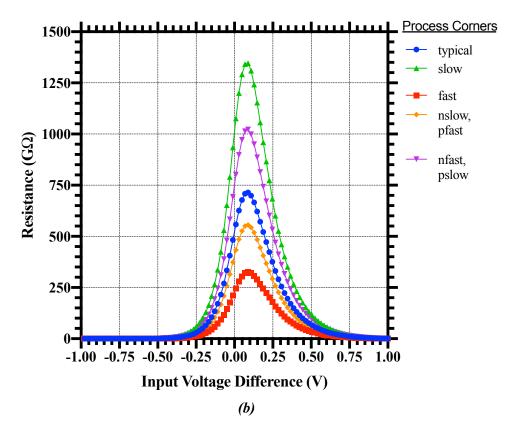

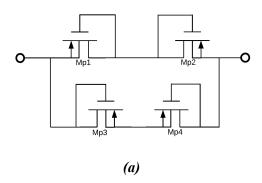

| Figure 4.5 (d | a) Pseudoresistor type 4 (PS4) [9], (b) Simulated cross-corner resistance variation |

| f             | for PS4                                                                             |

| Figure 4.6 (  | (a) Pseudoresistor type 5 (PS5) (based on [4],[10]), (b) Simulated cross-corner     |

| ν             | resistance variation for PS5                                                        |

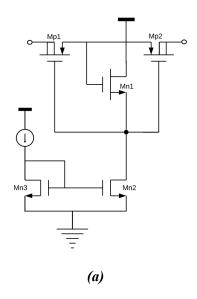

| Figure 4.7 (a) Pseudo-resistor type 6 (PS6) [11], (b) Simulated cross-corner resista       | nce  |

|--------------------------------------------------------------------------------------------|------|

| variation for PS6.                                                                         | 118  |

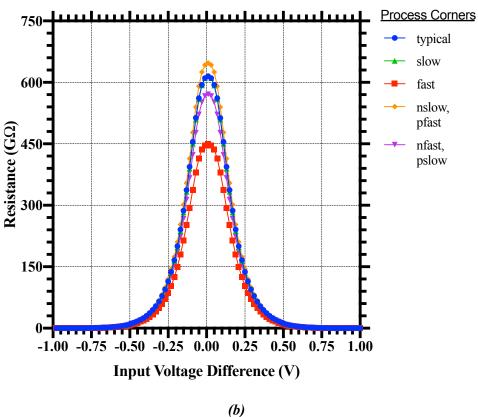

| Figure 4.8 (a) Pseudo resistor type 7 (PS7), (b) Simulated cross-corner resistance variate | tion |

| for PS7                                                                                    | 120  |

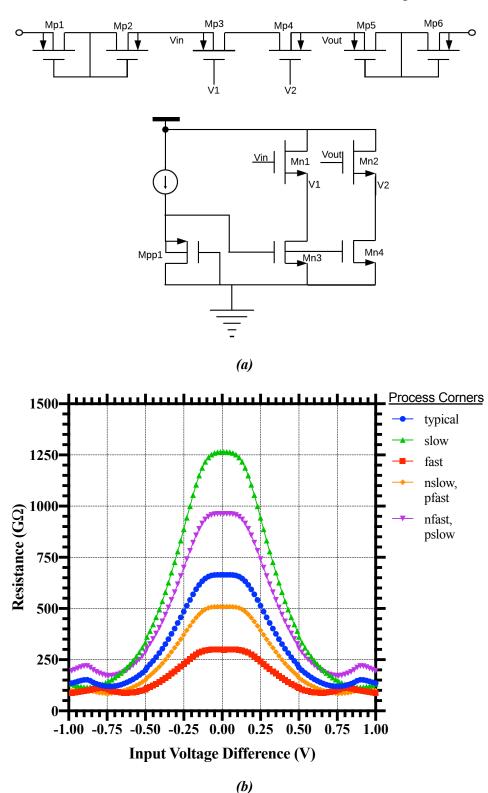

| Figure 4.9 (a) Pseudo-resistor type 8 (PS8), (b) Simulated cross-corner resistance variate | tion |

| for PS8.                                                                                   | 121  |

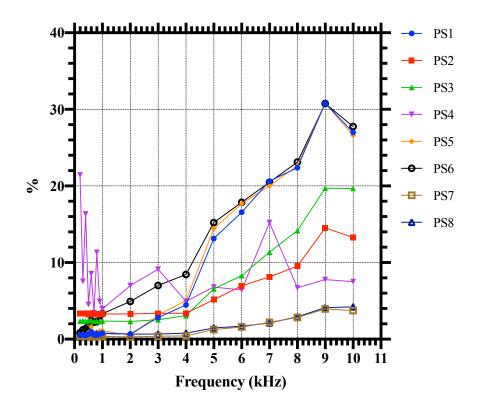

| Figure 4.10 Simulated percentage total harmonic distortion (THD) for all topologies (An in | put  |

| signal of amplitude $0.25V$ is swept through multiple frequencies)                         | 122  |

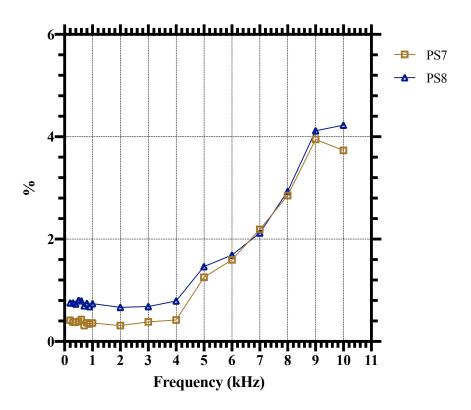

| Figure 4.11 Simulated total harmonic distortion for PS7 and PS8.                           | 123  |

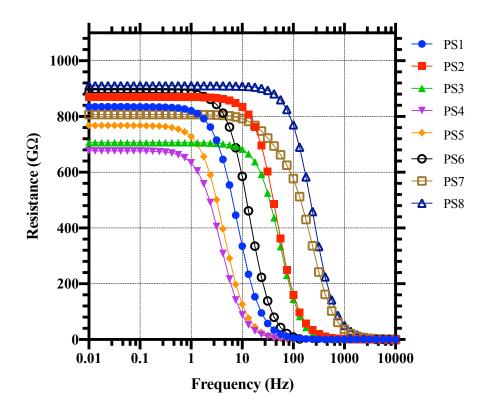

| Figure 4.12 Simulated small-signal resistance value for all topologies. PS7 and PS8        | are  |

| showing superior performance in the EEG frequency band (0.5 $-$ 50Hz)                      | 124  |

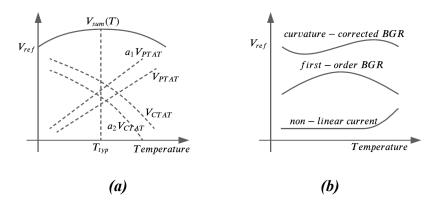

| Figure 5.1 Temperature independent voltage generation. (a) First order BGR, (b) curvat     | ure  |

| corrected BGR                                                                              | 128  |

| Figure 5.2 Temperature independent voltage generation, (a) PTAT generation, (b) combin     | ing  |

| a PTAT and a CTAT                                                                          | 129  |

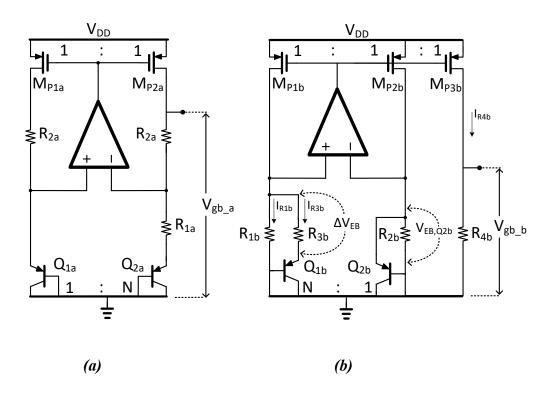

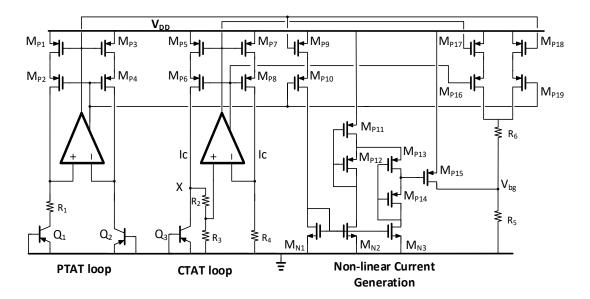

| Figure 5.3 Proposed curvature-compensated BGR.                                             | 130  |

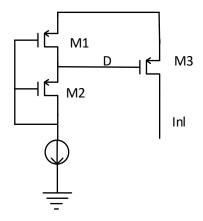

| Figure 5.4 Basics of a non-linear current generation circuit.                              | 131  |

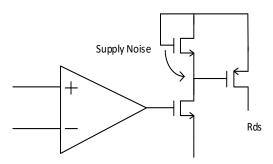

| Figure 5.5 Voltage subtractor circuit employed to enhance the PSRR                         | 132  |

| Figure 5.6 Simulation result for the first order BGR and the curvature compensated BGR us  | ing  |

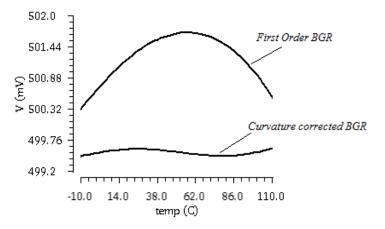

| the proposed technique.                                                                    | 133  |

| Figure 5.7 Simulated Monte-Carlo variation in the proposed curvature-corrected BGR (       | see  |

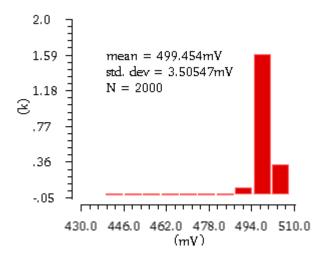

| Figure 5.3), $3\sigma$ variation simulated is 2.1% for 2000 samples (bin=10)               | 133  |

| Figure 5.8 Simulated Monte-Carlo variation in the PSRR of the proposed curvature-correct   | cted |

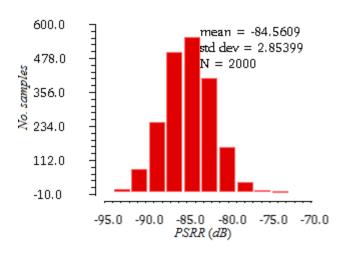

| BGR, $3\sigma$ variation simulated is $10.1\%$ for $2000$ samples (bin=10)                 | 134  |

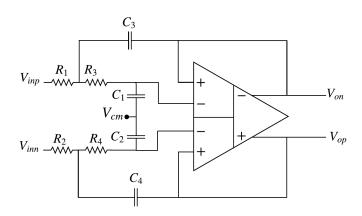

| Figure 6.1 A single-ended Sallen-Key low pass filter.                                      | 138  |

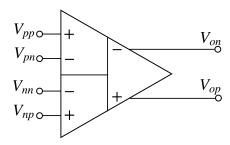

| Figure 6.2 Symbol for the DDA [4]                                                          | 139  |

| Figure 6.3 Signal flow diagram representation for the DDA [4].                             | 140  |

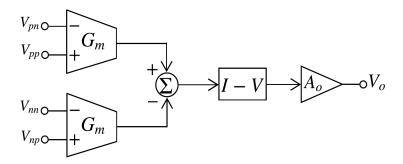

| Figure 6.4 Fully differential difference amplifier.                                        | 140  |

| Figure 6.5 Composite stacked transistors.                                                  | 141  |

| Figure 6.6 Common-mode feedback circuit used in the DDA                                    | 141  |

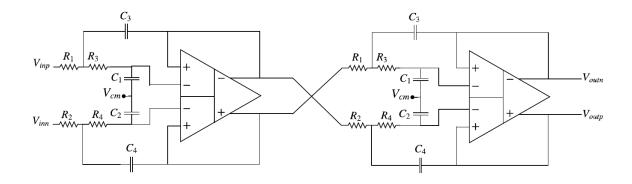

| Figure 6.7 Fully-differential Sallen-Key low pass filter.                                  | 142  |

| Figure 6.8 A duty-cycled resistor (DCR).                                                   | 143  |

| Figure 6.9 Simulated transient response of the LPF to a step response                      | 144  |

| Figure 6.10 Duty-cycled clock generation circuit and the timing diagram [8]                | 145  |

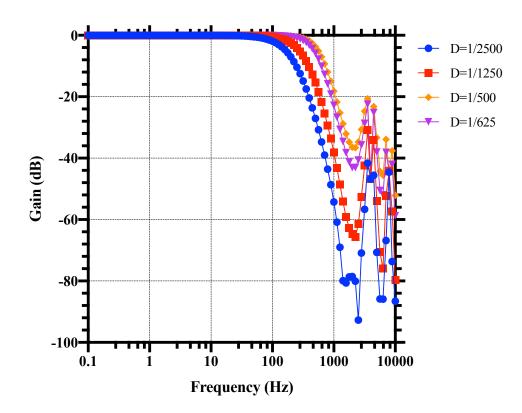

| Figure 6.11 Fourth order fully differential Sallen-Key low pass filter                          | 146          |

|-------------------------------------------------------------------------------------------------|--------------|

| Figure 6.12 Simulated frequency response for the fourth order Sallen-Key low pass               | s filter for |

| different duty cycles of the DCR                                                                | 146          |

| Figure 6.13 Layout of the final implemented fourth order Sallen-Key Low pass filter             | r 147        |

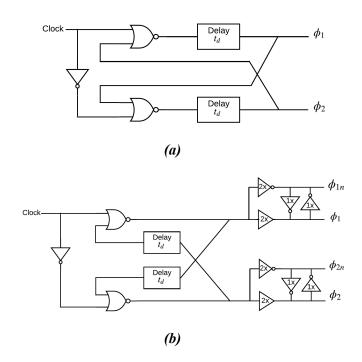

| Figure 7.1 (a) Non-overlapping clock generator. (b) Non-overlapping clock generator.            | ator with    |

| the output latch (for aligning the edges).                                                      | 149          |

| Figure 7.2 Block diagram of the chip current generation circuitry                               | 150          |

| Figure 7.3 Simplified N-bit SAR ADC architecture [6].                                           | 151          |

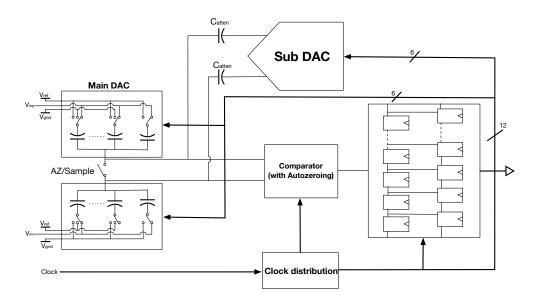

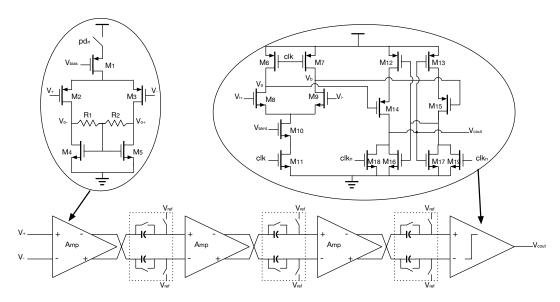

| Figure 7.4 Block diagram of the fully differential 12-bit SAR ADC implementation.               | 152          |

| Figure 7.5 Timing of the SAR ADC.                                                               | 153          |

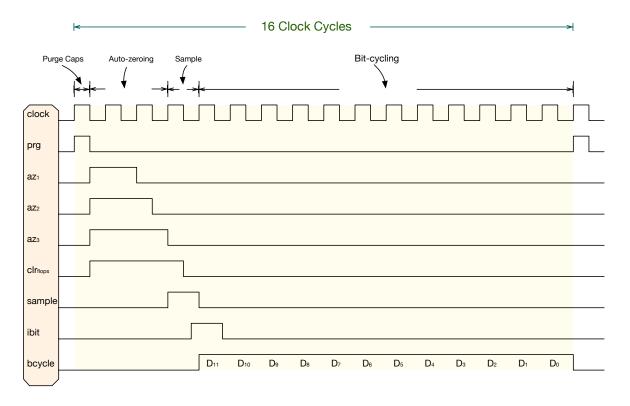

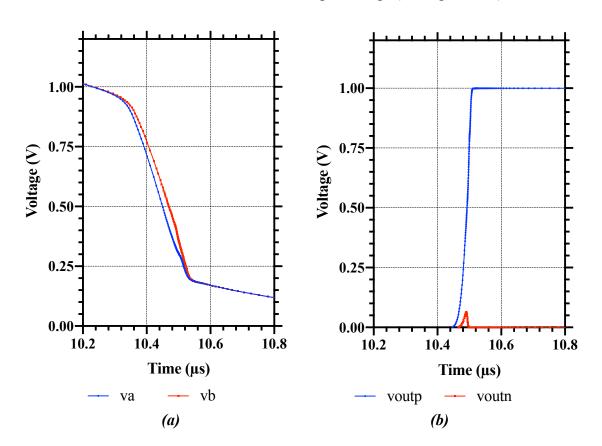

| Figure 7.6 (a) Input sine wave with an amplitude of 0.35V, 1.46484Hz frequency. (b)             | Simulated    |

| output of the SAR ADC                                                                           | 154          |

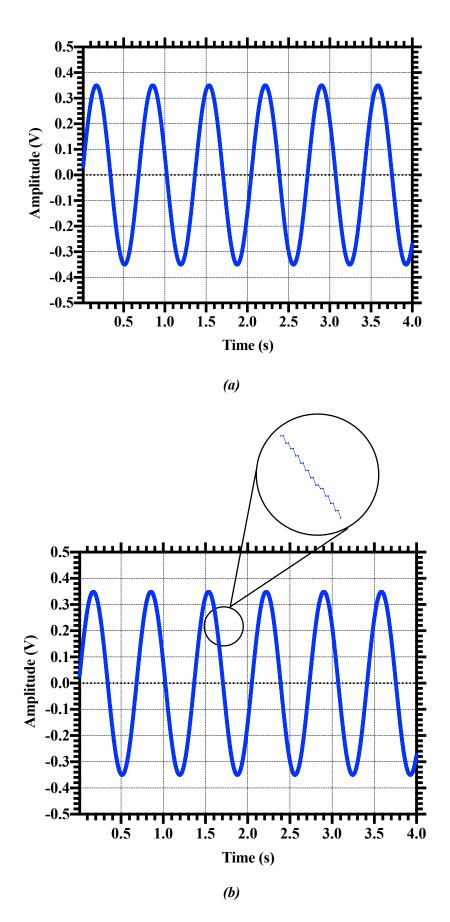

| Figure 7.7 Simulated FFT of the ADC output when a sine wave is applied at the inp               | ut 155       |

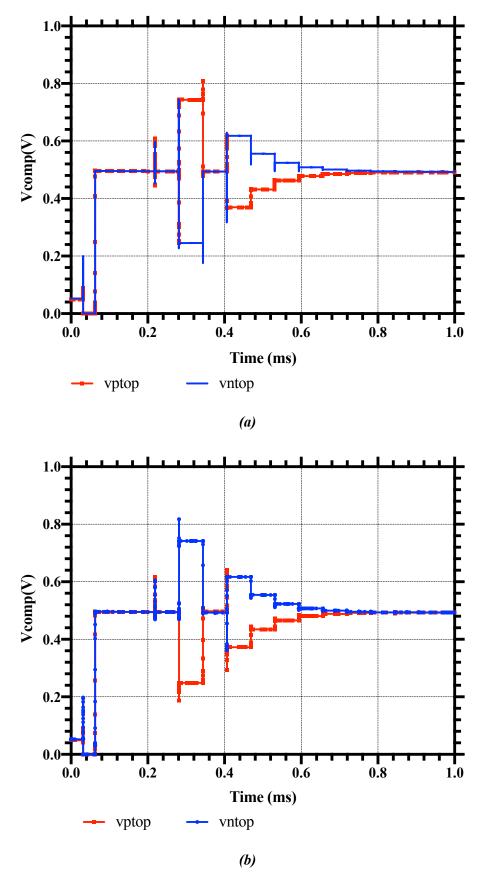

| Figure 7.8 (a) Simulated input signals for the comparator, when $V_{in} = -500 \text{mV}$ ; (b) | simulated    |

| input signals for the comparator, when $V_{in} = 500 \text{mV}$                                 | 156          |

| Figure 7.9 Architecture of the proposed comparator used in the SAR ADC                          | 157          |

| Figure 7.10 (a) Delay at the output of the first stage, while outputs are pulled down           | wn by the    |

| transistor M11. (b) Output of the latch stage once the M18 and M19 a                            | re turned    |

| OFF                                                                                             | 158          |

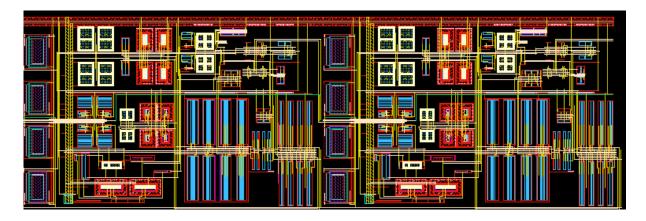

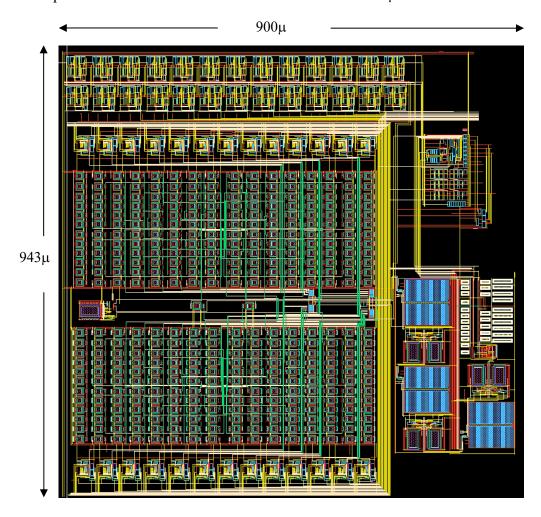

| Figure 7.11 Layout of the 12-bit SAR ADC.                                                       | 159          |

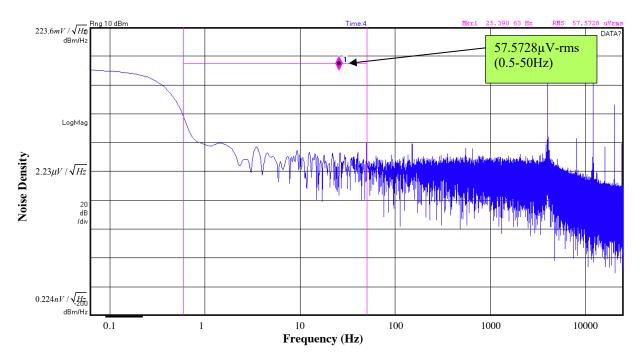

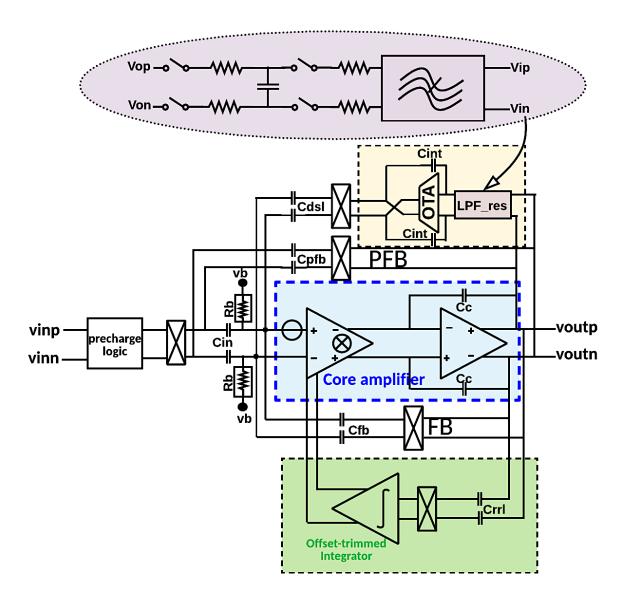

| Figure 7.12 Proposed analogue sensor front-end for the EEG recording system                     | 161          |

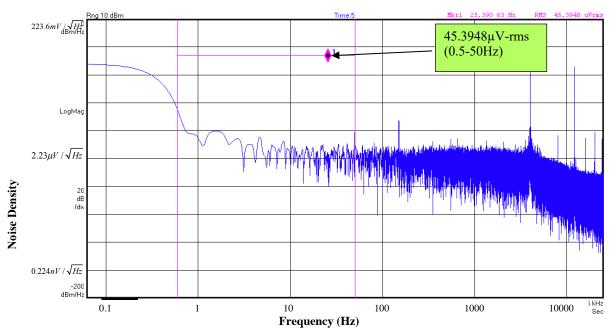

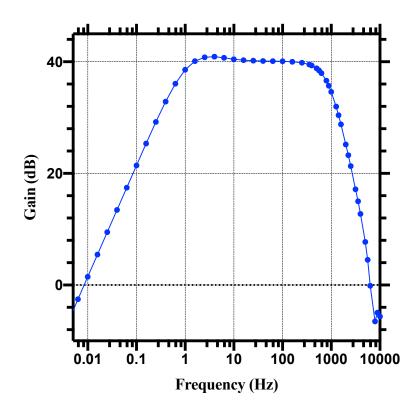

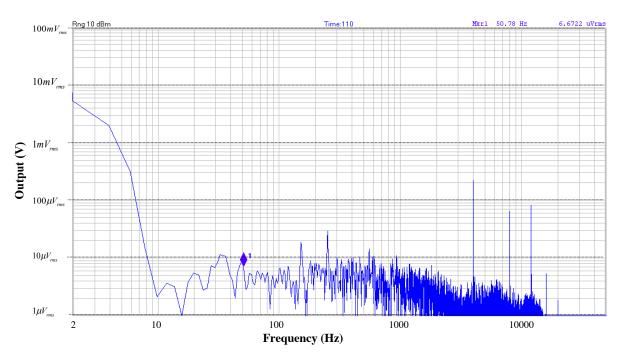

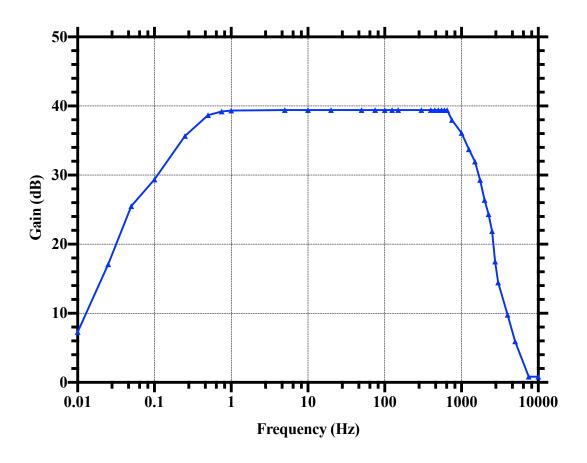

| Figure 7.13 Measured frequency response for the final AFE (mainly decided by the                | response     |

| of CCFEA-II).                                                                                   | 161          |

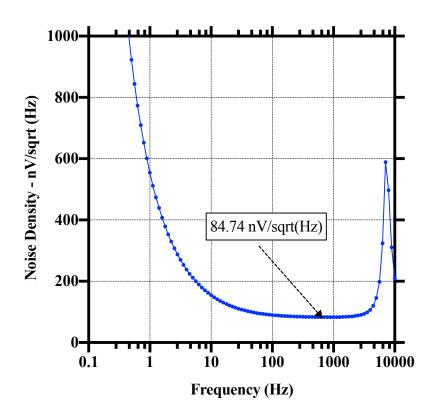

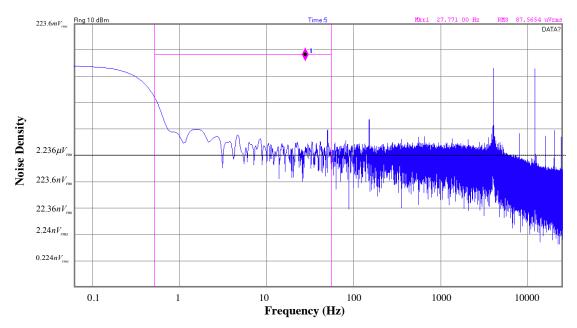

| Figure 7.14 Measured noise performance of the AFE (dominated by the CCFEA-II are                | ıd the SK-   |

| filter). 50 $\Omega$ impedance is used for the measurement                                      | 162          |

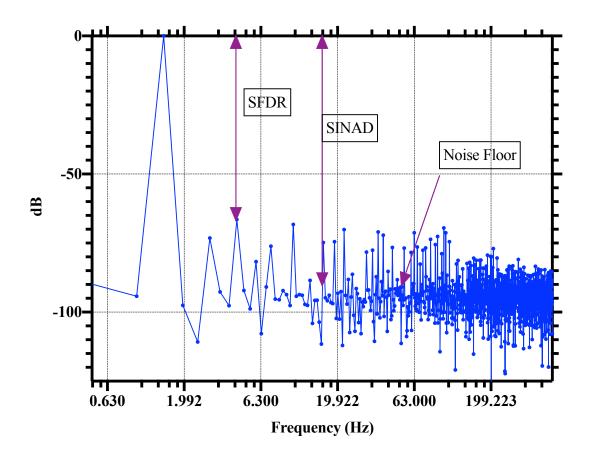

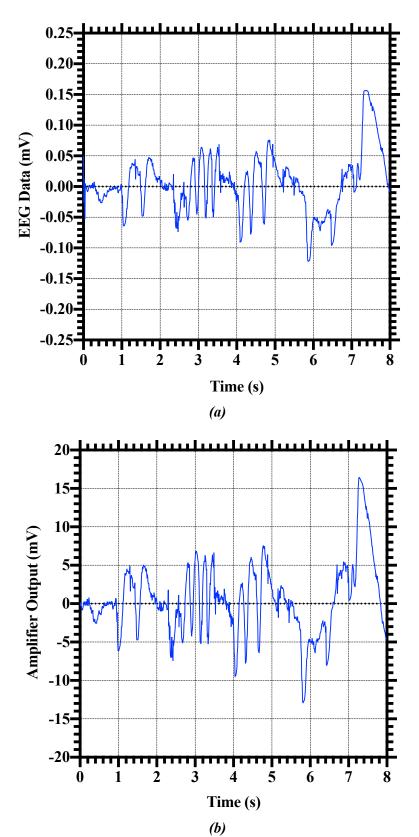

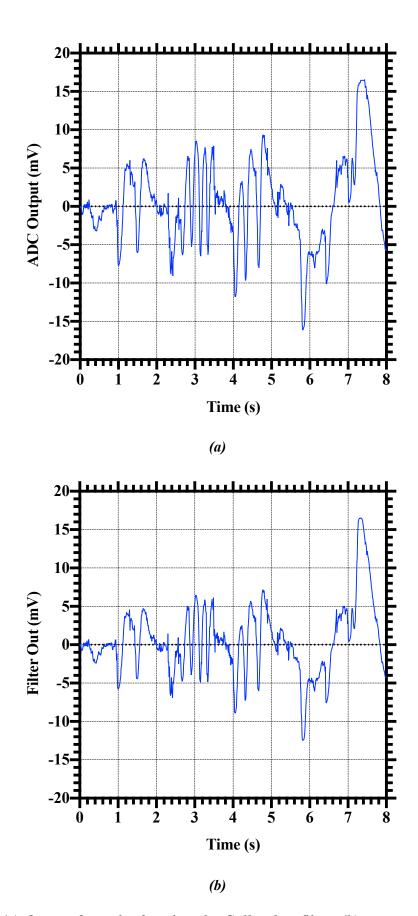

| Figure 7.15 (a) Input EEG data , (b) amplified EEG data at the output of the CCFE               | 4-II 163     |

| Figure 7.16 (a) Output from the fourth order Sallen-key filter, (b) converted outp              | out of the   |

| SARADC.                                                                                         | 164          |

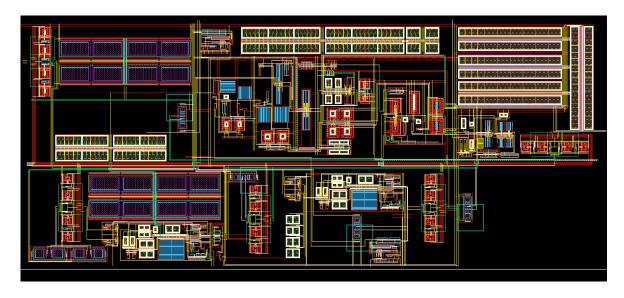

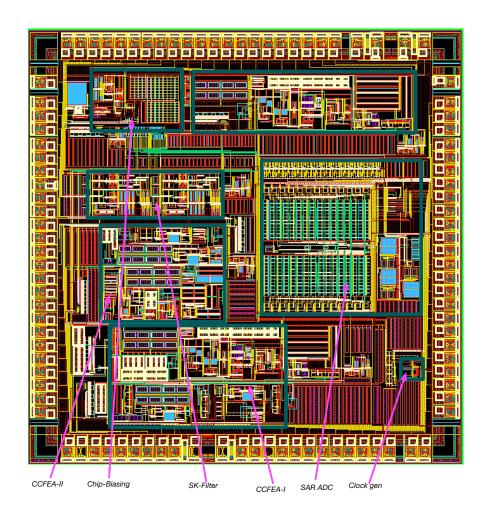

| Figure 7.17 Top-level layout of the fabricated chip.                                            | 165          |

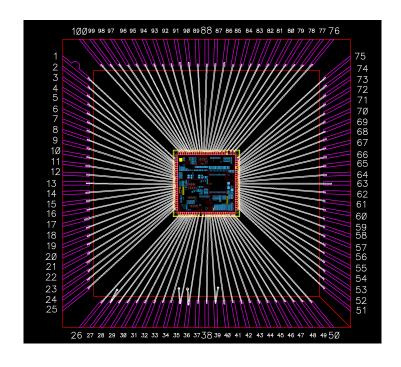

| Figure 7.18 Wire bonding arrangement for the full-chip                                          | 165          |

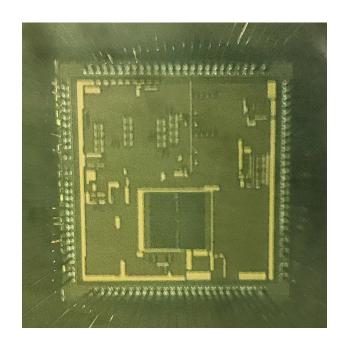

| Figure 7.19 Microphotograph of the final wire-bonded chip                                       | 166          |

# **List of Tables**

| Table 1.1 Electrode positioning systems for EEG recording [10]                            | 4  |

|-------------------------------------------------------------------------------------------|----|

| Table 2.1 Summarised standards for Digital EEG recording [14-15]                          | 0! |

| Table 2.2 Comparison of target specifications with state-of-art AFE implementation 4      | !8 |

| Table 3.1 Performance comparison of proposed EEG amplifiers with state of art designs. 10 | 15 |

| Table 5.1 Comparison with other published results                                         | 4  |

| Table 7.1 Performance comparison of the proposed AFE with state-of-art designs            | 66 |

# **List of Acronyms**

AAF anti-aliasing filter

ADC analogue-to-digital converter

AFE analogue front-end

ASIC application specific integrated circuit

AZ auto-zeroing

BGA ball grid array package

BPF band-pass filter

CCFEA-I Chopper based capacitive feedback EEG amplifier using modified pseudo-

resistors (CCFEA-I)

CCFEA-II Chopper based capacitive feedback EEG amplifier using duty-cycled resistors

CCFEA-III Chopped capacitive feedback EEG amplifier with pseudo-resistor calibration

loop and digital offset correction

CDS correlated double sampling

CMFB common-mode feedback

CMRR common-mode rejection ratio

CTAT complementary to absolute temperature

DAC digital-to-analogue converter

DCR duty cycled resistor

DDA differential-difference amplifier

DSL dc servo loop

EEG electroencephalography

EM electromagnetic

ENOB effective number of bits

ESD electrostatic discharge

FFT fast fourier transform

FOM figure of merit

HPF high-pass filter

IC integrated circuit

IOS input offset storage

LPF low-pass filter

MDCR multi-rate duty cycled resistor

NEF noise efficiency factor

OOS output offset storage

OTA operational transconductance amplifier

PCB printed circuit board

PEF power efficiency factor

PFB positive feedback loop

PR pseudoresistor

PSD power spectral density

PSRR power supply rejection ratio

PTAT proportional to absolute temperature

RMS root mean square

RRL ripple rejection loop

SAR successive approximation register

SC switched capacitor

SFDR spurious free dynamic range

S/H sample-and-hold

SINAD signal to noise and distortion ratio

SNR signal-to-noise ratio

SOI silicon on insulator

THD total harmonic distortion

VDS drain-to-source voltage

VGS gate-to-source voltage

VLSI very-large-scale integration

# **Chapter 1 - Electroencephalography**

#### 1.1 Overview

Electroencephalography, or EEG, refers to a method for recording the electrical activity of a person's brain through the scalp over a period of time [1-7]. This is done both for research purposes and the evaluation of various neurological disorders. EEG imposes a more significant challenge than other bioelectrical recording methods due to their high complexity, non-linearity and low signal to noise ratio [1],[7]. EEG offers three distinct advantages over other methods of brain processes sensing: 1) It is a non-invasive procedure, so measurements can be conducted on human subjects without the need for surgery; 2) It has a very high time resolution, in several milliseconds, which make it easier to track temporal dynamics of the brain processes; 3) It is relatively inexpensive. Advantages associated with EEG provided the use of EEG in a wide range of applications ranging from sleep monitoring, epilepsy monitoring to alertness detection or Brain-Computer Interfaces (BCI).

This chapter briefly discusses the history of EEG, physiology, recording methods, application areas, and a brief summary of the evolution of EEG recording systems. An analysis of the motivation for utilising ambulatory techniques, rather than traditional clinical recordings and the need for wearable EEG systems, is also presented.

## 1.2 History and evolution of electroencephalography

In 1875, Richard Caton discovered the existence of the electrical signals in the brain by examining the exposed brains of rabbits and monkeys [2],[7]. Later on, Hans Berger became the first researcher to record the electrical activity from the human scalp. In 1924, he amplified the brain signals recorded from scalp using double coil galvanometer and non-polarizable pad electrodes. He later published his finding in 1929 journal article titled "Über das Elektroenkephalogramm des Menschen". In the study, he reported a brain oscillation of 10Hz, which he called the alpha wave, observed in subjects in a relaxed state and closed eyes. During this time, a group in the institute of brain research in Berlin-Bush led by A. E. Kornmuller collaborated with J. F. Toennies. This group provided a more precise recording of the EEG signals. J. F. Toennies is attributed to the development of the first ink-writing biological

amplifier for recording brain potentials. While as a fellow of the Rockefeller Foundation in 1932, he designed a differential amplifier for EEG recording.

It was Kornmuller who first recognized the significance of recording from a large number of electrodes. He worked together with M. H. Fischer and H. Lowenbach to record EEG from the cortex of animals after poisoning with convulsive substances. It was the first EEG work focussed on epileptic manifestations and the first demonstration of epileptic spikes.

Later in 1934, Lord Edgar Adrian (1889-1977) at Cambridge confirmed the findings of Berger. From thereon, EEG triggered a revolution in the study of brain functioning and dynamics [1-7].

#### 1.3 Basics of bioelectrical signals and nature of EEG

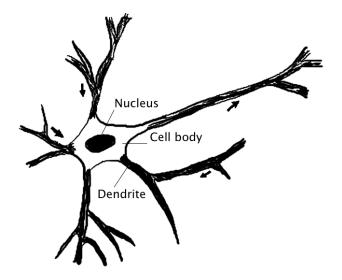

Nerve cells, or neurones, have visible contrast in the detailed structure but are typically constituted of a cell body, containing a nucleus, a long nerve fibre called axon which carries electrical nerve impulses away from the cell body, and many short branches called dendrites which bring the impulses towards the cell body (see Figure 1.1)[1].

Figure 1.1 Nerve cell (a neuron) structure.

There is a higher concentration of potassium (K+) within a neurone and a lower concentration of sodium (Na+), and the reverse is true for extracellular fluid. The cell membrane is much more permeable to potassium ions than to sodium ions. When these ions diffuse down their concentration gradients, an electric potential is set up across the cell membrane. The membrane

is polarized when negative potential inside the membrane with respect to the outside becomes large enough to prevent potassium ions from escaping. This occurs at a resting potential of around -70mV. Under certain circumstances, the membrane potential is reduced, reaching a certain threshold when ionic permeabilities change, and the cell membrane becomes impermeable to potassium but allows sodium to move in freely. When the inside of the cell membrane becomes 30mV positive with respect to the outside, the selective permeabilities restores its original state, producing an overshoot that lasts about 1ms, called action potential. The action potential then transmits the signal through the axon to other nerve cells. The points of contact from axon to dendrites and cell bodies of other neurons are called synapses. When an action potential reaches a synapse, a chemical substance called a 'neurotransmitter' is released, which diffuses in the membrane of the adjacent post-synaptic neuron and brings electrical changes called post-synaptic potentials. They are about 5-10mV in amplitude and last about 10ms [1].

The effects of the various synapses across the cell body is averaged out. Based on the threshold they reach, they might result in depolarising or excitatory postsynaptic potentials (ESPs), triggering off action potentials with some synapses producing polarising effects or inhibitory postsynaptic potentials (IPSPs).

An electrode connected to the scalp detects the electrical signal caused by the synchronous activity of thousands of neurons. The synchronization between PSPs is essential for detection of EEG; otherwise, the signal will appear as a low amplitude random noise [1].

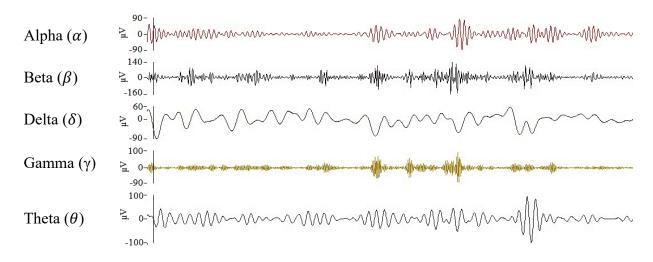

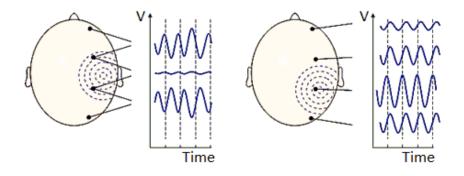

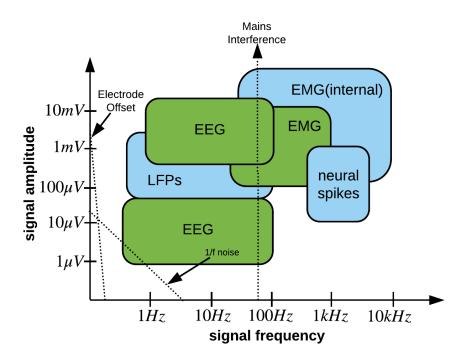

The EEG signals recorded through scalps are of very low amplitude, around  $10\text{-}100\mu\text{V}$  within a frequency range of 0.5-50Hz [20]. The EEG signals are classified into five frequency bands: alpha ( $\alpha$ ), beta ( $\beta$ ), theta ( $\theta$ ), delta ( $\delta$ ) and gamma ( $\gamma$ ) (see Figure 1.2). In 1929, Berger introduced the alpha and beta waves. Jasper and Andrews (1938) used the term 'gamma' for the waves above 30Hz. Walter in 1936 used the term 'delta' to classify all frequencies below the alpha rhythm. Walter and Dovey then introduced theta waves in 1944 [7]. As a summary:

- Delta  $(\delta)$  These waves can be detected within the range of 0.5–4 Hz and are mainly associated with the deep sleep condition and may be present in the awake state [7-8].

- Theta (θ) These correspond to the frequency band of 4 to 8Hz (further classified into theta1 which is between 4 to 6Hz and theta2 from 6 to 8Hz) [7-8]. Theta waves start to appear as consciousness slowly moves towards drowsiness. Theta waves often exist with

the other frequencies and are considered to be related to arousal. Theta waves are dominant during infancy and childhood, and considerable theta activity in waking adults is deemed to be abnormal and is caused by pathological problems [7-8].

- Alpha (α) These waves are visible between 8 to 13 Hz (13 inclusive) and appear as a round or sinusoidal shaped signal. However, in some cases, it may appear as sharp waves. Alpha waves are considered to be associated with a mentally relaxed state without any attention or concentration. Alpha waves can be sub-classified into alpha1 (8-8.9Hz), alpha2 (9-10.9Hz) and alpha3 (11-12.9Hz) [8]. They are considered as waiting or scanning pattern produced by the visual regions of the brain. These waves are reduced or eliminated by opening the eyes, by anxiety, or mental concentration or attention [7].

- Beta (β) These waves correspond to a frequency range of 14–26 Hz (beta1 from 13 to 18Hz, beta2 from 18 to 22Hz and beta3 from 22 to 30Hz) [8]. A beta wave is considered to be normal in the waking state of the brain. It is associated with active thinking, active attention, focus on the outside world, or solving difficult problems, and is found in healthy adults [7].

- Gamma (γ) These are the frequencies above 30 Hz. The amplitudes of these rhythms are very low, and their occurrence is rare. These rhythms are used for the confirmation of certain brain diseases [7-8].

Figure 1.2 EEG samples showing different frequency signals [redrawn from 9].

#### 1.4 EEG recording

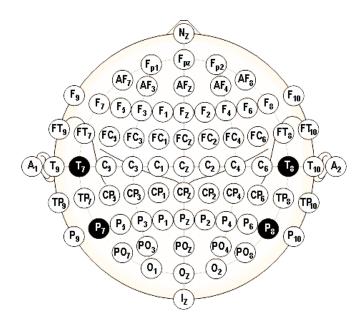

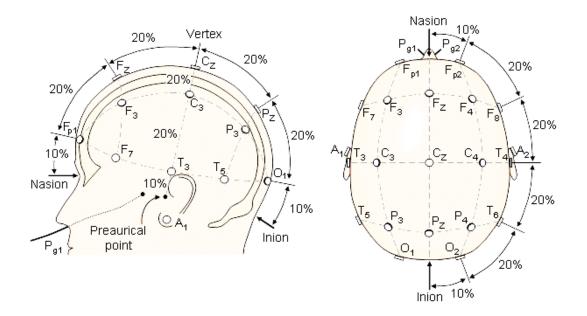

Current EEG recording generally employ the internationally standardized 10-20 electrode system for electrodes positioning. Based on this system, a set of 21 electrodes is spread out on the surface of the scalp. Reference points are nasion, which is at the top of the nose at the same level as eyes, and inion, which is at the bottom of the skull, along with the centre line (see Figure 1.3). Besides 21 electrodes, intermediate 10% electrode positions may also be used following the standard of American Electroencephalographic Society. The nomenclature and position of the electrodes are given in Figure 1.4.

Table 1.1 Electrode positioning systems for EEG recording [10].

| S. No. | System name            | Description                                                         |

|--------|------------------------|---------------------------------------------------------------------|

| 1.     | 10-20 electrode system | The first electrode from the nasion, inion or preauricular point is |

|        |                        | at the interval of 10%. The remaining electrodes are equidistant    |

|        |                        | at a spacing of 20%.                                                |

| 2.     | Intermediate 10%       | The Skull perimeter between nasion and inion is marked into         |

|        | electrode system       | equal intervals of 10%, and electrodes are placed over them.        |

| 3.     | Queen square system    | Five electrodes are positioned at 5 cm above the inion and 5 cm     |

|        |                        | apart. This arrangement placed two electrodes at either side of a   |

|        |                        | midline electrode.                                                  |

Figure 1.3 Location and Nomenclature of 10% electrode positions standardized by the American Electroencephalographic Society [Redrawn from 10].

Figure 1.4 International 10-20 system, seen from left and top of the head. A = Ear lobe, C = central, Pg = nasopharyngeal, P = parietal, F = frontal, Fp = frontal polar, O = occipital [Redrawn from 10].

Figure 1.5 Bipolar and Unipolar measurement [Redrawn from 10].

Two methods of recording can be used, unipolar recording, which compares the potential of the electrode with a neutral reference electrode or the average of all electrodes; and bipolar recording which compare the potential between two electrodes (see Figure 1.5).

Wet or dry electrodes can be used for sensing EEG signal [1]. Wet electrodes (Ag/AgCl based) require extensive skin preparation like abrasion, application of electrolyte or gel. The skin resistance is very high, of the order of  $10\text{-}100\text{k}\Omega/cm^2$  so electrolyte paste is required to reduce this resistance [11]. The disadvantage associated with the application of gel is that there are more chances of impedance variation among various sites due to gel drying out. Also, the gel might create shorts between adjacent recording sites. Moreover, the skin preparation causes

discomfort and may cause allergic reactions or infections. To alleviate some of these disadvantages dry or insulating electrodes are being developed [12].

Even with the inconvenience associated with wet electrodes, they found widespread usage in medical recording as wet electrodes are cheaper, simple, lightweight and initial contact impedances are low enough for a good recording [12]. Dry electrodes may have a significant advantage for wearable or ambulatory EEG application, as they allow recording signals without the need for skin preparation, enabling the subject to be able to undertake daily routine tasks without being isolated from his/her surrounding [13-14].

One of the common shortcomings in both types of the electrode is the problem of the electrode DC offset (EDO), which is caused by the difference in the potential of the electrodes [1]. This electrochemical potential is uncontrollable to a certain extent and depends on the electrode-electrolyte (wet electrode) interface or the electrode-skin (dry electrode) interface [1].

The significant advantage of the wet electrodes is a lower dc offset, 50mV as compared to around 200 mV or more for the dry electrodes [15]. Smaller dc offset is the principal argument to use the wet electrodes in the design of a low-voltage system, where the amplifier can be developed with a reduced voltage supply.

#### 1.5 The Electrode-tissue Interface

All neural recording systems need a physical interface between the electronic circuit and the biological tissue. In a majority of EEG recording systems, Ag/AgCl electrodes are held close to the head with a snug-fitting cap or headset. Preparation of the skin is done by applying an electrolyte gel injected between each electrode and the scalp for providing a stable and conductive path through the hair. It is also possible to record biopotential signals from the scalp using dry stainless-steel electrodes, but these are more susceptible to movement artefacts.

Figure 1.6 Approximate small signal model for skin-electrode interface.

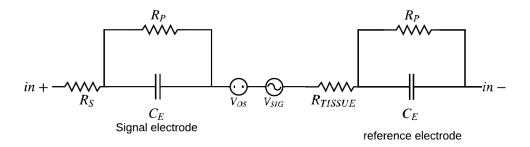

An electrical double layer is formed once the equilibrium is reached across the electrodetissue interface. This interface acts as a capacitance for small current and voltages. Many textbook models add a resistance parallel to the electrode capacitance as well as series resistance (see Figure 1.6). Charge accumulation due to the chemical interaction between the metallic electrode and electrolytic solution (gel) generates a DC offset ( $V_{OS}$  in Figure 1.6). The magnitude and sign of this offset are very difficult to predict as it is a function of material properties, tissue condition, and temperature. This offset could be up to  $\pm 50$ mV for the wet electrodes ( $\pm 15$ mV for diagnostic applications), and between 100mV to 300mV for the dry electrodes. The biopotential can be modelled as an AC voltage source  $V_{sig}$  in series with resistance  $R_{TISSUE}$ , which represents the conductive tissue between the reference electrodes and the signal.

The equivalent model for the electrode-tissue interface is shown in Figure 1.6 [16], is a very useful first-order approximation for the low-voltage applications, but it is important to remember that the actual model is a complex, non-linear, time-varying system which is very hard to model in a precise way. The capacitance and the resistance values, given in Figure 1.6, vary with the frequency and the signal amplitude.

In EEG systems, differential recording from two nearby points is used to avoid 50/60-Hz power line interference pickup, employing identical electrodes. The two terminals in+ and inpresented in Figure 1.6, can be connected to the input of the differential amplifier. An additional electrode is used to tie the circuit ground to the body for guaranteeing a reasonable DC potential at the amplifier input [16]. The resistance  $R_S$ , which is due to the conduction through the electrolyte, may be on the order of  $2k\Omega$ , while  $R_P$  and  $C_E$ , which originates from the skin, can be on the order of  $2M\Omega$  and 50nF, respectively [15]. For avoiding a severe signal attenuation, the input impedance of the instrumentation amplifier must have much a larger resistive component and a much smaller capacitive component than this.

## 1.6 EEG application areas

Since Hans Berger (1924) recorded the electrical activity of the brain through the scalp, EEG has become a vital research tool in studies of brain activity. Thus, many different application areas have been explored utilizing the EEG recording [13-29].

EEG signal contains important physiological information, making it useful in epileptic seizure detection and epilepsy diagnosis. Epilepsy is one of the most common neurological disorders, affecting approximately 1% of the world's population, and up to 5% of people may have at least one seizure during their lifetime [21],[36]. An epileptic seizure occurs at random to impair the everyday functioning of the brain. Several patients also suffer from numerous other side effects, such as loss of memory, depression and other psychological disorders [21]. Hence, it is imperative that the epilepsy is detected at an early stage, helping the patient take appropriate actions in advance to avoid damaging consequences. Because of this reason, automated seizure detection and epilepsy diagnosis system from electroencephalogram (EEG) signals has become an active research topic in past decades [21].

Patients who are suffering from Amyotrophic Lateral Sclerosis (ALS) or the late stages of Alzheimer's disease are unable to use facial expression to express their emotions. Still, their brain EEG signals do contain information about their emotional state [22]. A wearable EEG-based emotion detection hardware feasibility is presented in [22], which can help such patients to communicate in real-time under normal social settings.

EEG is also finding use in the field of sleep monitoring to diagnose for any sleep disorders. Sleep disorders can raise the risk of hypertension, sleep apnoea syndrome, obesity, cardiovascular disease, Alzheimer's disease, Parkinson's disease, and lowering the efficiency of the immune system [23],[27]. Sleep disorders are typically investigated in a clinic by a medically trained person. The patient needs to be admitted overnight, which may be an inconvenient, time-consuming, and expensive method [24]. [24] proposed an automated sleep monitoring system using single in-ear EEG sensor. This sensor achieved an accuracy of 74.1% over five sleep stage classification with respect to hypnogram based on the full polysomnography (PSG) recording.

EEG has also found usage in studying the response of antidepressant treatment. The link between the prefrontal EEG dynamics and the antidepressant response has gathered significant interest [25]. Depressed patients who respond to antidepressant treatment, found to have significantly higher alpha power than average. Also, several studies associated increase or decrease in theta power with the treatment response [25].

Due to a non-invasive recording, EEG along with the eye movement data have found usage in the depression detection. Depression is a common mental disorder that affects approximately

350 million people around the world [27]. [28] used the feature extracted from the EEG data for the diagnosis of depression. Alpha, alpha1, alpha2, beta, delta and theta power and theta asymmetry were used as features.

A drowsiness detection wearable headband using EEG signal is proposed in [29], achieving a detection accuracy of 92% using selected features and a linear support vector machine classifier. [17] proposed an alertness detection scheme using the EEG spectrum. [18] recorded EEG signals for drowsiness estimation, which could be used in the context of driving and for attention critical jobs like an air traffic controller. In [30], EEG data was explored for person authentication system. And it has also received a lot of attention in the design of brain-computer interface (BCI) systems [31-33]. EEG data is also being considered for covid-19 diagnosis [34].

Figure 1.7 Biopotential signals and their frequency band [16].

## 1.7 Wearable electroencephalography

Due to the non-invasive nature, the electroencephalogram (EEG) is ubiquitous in brain monitoring systems. The most common way of recording EEG is by placing conductive electrodes on the scalp, that can detect microvolt magnitude electrical signals arising from neuronal action within the brain. The primary benefit of EEG is its very high time resolution—helping it to catch events within the brain with millisecond accuracy—and that aides in the

portability of application allowing real-world neuroimaging to be executed outside of clinical and laboratory settings [35].

Current EEG monitoring is either inpatient: where the person attends a tertiary care centre with time-locked video monitored by a trained medical professional and is restricted to a bed by wires connecting the electrodes and recording unit; or ambulatory: where the recorder is portable, and the recording can be done whilst the subject can move around with the recorder and potentially go on with their normal daily routine [13-14],[35],[53].

Though ambulatory EEGs provides advantages over in-clinic EEG, they still suffer from several shortcomings, such as:

- Wires coming from electrodes have to be connected to the device all the time, which restrict the normal movement.

- AEEG systems can weigh up to 1kg; carrying such a system is itself a problem [13-14].

Portability is the main reason why a person undergoing EEG monitoring prefers to stay at home, rather than being seen carrying over a bulky device in public [13-14].

Furthermore, a lot of patients admitted to emergency departments (ED) for a neurological disorder like altered mental status or status or seizures, would remain undiagnosed hours to days after admission, which leads to an elevated rate of death compared to other conditions [39]. By conducting a thorough EEG monitoring in early-stage could prevent further damage to the brain and can avoid high mortality. But lack of portability and ease of access results in a long wait time for the prescribed patients [39].

The above shortcomings can be eliminated from the EEG recording by the use of a wearable EEG. The wearable EEG is the evolution of the bulky AEEG, which can be worn on the body. The wearable EEG is benefited by the advancement in VLSI techniques which aided in the miniaturization and portability of EEG systems. A complete system can now be implemented in a single chip with a mix of analogue and digital devices. The most important benefit of a wearable solution is that it enables recording to be carried out over an extended time by appropriate use of data manipulation, storage and transfer algorithms [13-14],[35]. A wearable solution could be a component of an epilepsy prediction system, which continuously monitors the patient's EEG signals and can alert nurses or health care professionals of impending seizures.

Furthermore, wearable EEG is aiding in the development of new EEG systems like drowsiness detection, alertness detection, wellness, meditation, BCI, etc.

Also, in the current situation of Covid-19 outbreak, social distancing has been put in place, and a lot of scheduled appointments are either pushed or reduced in number. An alternative to ambulatory in-clinic recording would be a wearable EEG recording system, that can help the patient receive appropriate diagnosis and care while maintaining the physical distancing and lockdown protocols.

There are multiple issues that need to be considered for a wearable EEG device [41].

- The device should have good ergonomics, so easier to set up and remove.

- The device should be portable, comfortable, lightweight, and easier to store.

- The device should be hypoallergenic and non-toxic to the body.

- The device should have good accuracy and not very costly to manufacture.

Several commercially ready wearable EEG devices are now available to buy [42-47]. Emotiv Insight is a five-channel EEG device with a battery life of 8hours using USB receiver [42]. The MindWave Mobile 2 by NeuroSky can record the EEG spectrum in the frequency band of 3-100Hz, providing a battery life of 8hours with a single AAA battery [43]. Muse 2 and Brainlink pro are developed for meditation and neurofeedback [44-45]. MyndBand can record the EEG spectrum between 3-100Hz [46]. Also, SenzeBand from Neeuro can record all major EEG signal bands [47]. Besides the commercial products, there are multiple wearable solutions proposed in literature [40],[48-52].

Commercially available devices mentioned above can be used only for a continuous run time of eight hours or less, before the need to replace the battery [42-47]. This short battery life will make their use limited in ambulatory epilepsy diagnosis, where the test may need to be carried out for days and sometimes weeks [53]. Also, for sleep monitoring, their battery life is at the borderline. The target for this research will be to power the system using a coin cell battery, and the power budget considered is  $7\mu W$  per AFE channel (explained in chapter 2). Also, to enhance the portability and storage, the size of the PCB for the wireless system is restricted to  $1 \text{cm}^3$  [54].

This research aims to define the specifications for building a custom analogue mixed-signal front-end for the EEG recording (mainly in the context of epilepsy diagnosis) and use that to review the suitability of the architectures available in the literature. Also, another critical task is to provide new architectures that can meet the developed specifications for EEG monitoring and can be used in epilepsy diagnosis, sleep monitoring, drowsiness detection and depression study. The research is only aimed to optimise the performance of the analogue frontend while assuming that a data reduction circuit is available [54] and a Bluetooth low energy transmitter like TI's CC2640R2F is available [55].

This research work and the thesis made following key contributions:

- 1. A novel fully-differential two-stage amplifier design was proposed with an improved frequency response continuous-time common-mode feedback circuit. This amplifier is discussed in detail in Chapter 3.

- 2. A novel EEG amplifier was proposed using the high-pass frequency set through duty-cycled resistor technique similar to the one presented in [8]. Detailed discussion is given in Chapter 3.

- 3. A novel EEG amplifier was proposed employing the novel low-distortion pseudoresistor design for setting the high-pass frequency for the amplifier. This design is presented in Chapter 3.

- 4. A novel EEG amplifier was proposed, where the high-pass frequency was set through a novel pseudo-resistor calibration loop. This design is discussed in Chapter 3.

- 5. A novel pseudoresistor calibration scheme was proposed to set the value of pseudoresistors accurately, that reduced the variation in the resistor value from 10-20x to just 8.25%. This calibration technique is discussed in Chapter 3.

- 6. Two novel pseudoresistor designs are proposed. These pseudoresistors achieved a bandwidth of 160Hz and 236Hz respectively, compared to the highest of 54Hz achieved for state-art-implementations designed for EEG application. Also, they attained a total harmonic distortion of 3.73% and 4.2% respectively, compared to 7.5% of the nearest state-of-the-art implementation for EEG amplifier. These designs are presented in Chapter 4.

- 7. A novel ultra-low-power, high PSRR bandgap reference design was proposed (also published at IEEE conference). This is discussed in detail in Chapter 5.

- 8. A novel fully-differential fourth-order Sallen-Key filter low pass filter was proposed using duty-cycled resistors and modified differential difference amplifier. This filter is described in detail in Chapter 6.

- 9. A novel auto-zeroing based dynamic comparator is designed to use in the 12-bit SAR ADC. The design is presented in Chapter 7.

- 10. Finally, a novel fully-differential analogue front-end was proposed for the EEG recording. The design is presented in Chapter 7.

Following research papers are written during this PhD:

- M. U. Abbasi, G. Raikos, R. Saraswat and E. Rodriguez-Villegas, "A high PSRR, ultralow power 1.2V curvature corrected Bandgap reference for wearable EEG application," 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, 2015, pp. 1-4.

- R. Saraswat, M. U. Abbasi and E. Rodriguez-Villegas, "Ultra-low power, low noise MAC protocol compliant non-PLL based wearable transmitter for dynamic open spectrum sharing," 2015 7th International IEEE/EMBS Conference on Neural Engineering (NER), Montpellier, 2015, pp. 553-556.

- 3. Mohammad Usaid Abbasi, "A Wearable EEG Amplifier Using a Novel Teraohm low-Distortion Tunable Hybrid pseudo-Resistor", 2021 IEEE International Symposium on Circuits & Systems.

- 4. Mohammad Usaid Abbasi, "An Ultra Low Power, Low Noise EEG Amplifier with Chopper Stabilisation and pseudo-Resistor Calibration", 2021 IEEE International Symposium on Circuits & Systems.

#### **References:**

[1] C. D. Binnie, A. J. Rowan and T. Gutter, A manual of electroencephalographic technology. Cambridge: Cambridge University Press, 1982.

- [2] T. F. Collura, 'History and Evolution of Computerized Electroencephalography', Journal of Clinical Neurophysiology, pp. 214–229, 1995.

- [3] M. Teplan, 'Fundamentals of EEG Measurement', Measurement Science Review, vol. 2, pp. 1–11, 2002.

- [4] W. J. Freeman and R. Q. Quiroga, 'Imaging Brain Function With EEG: Advanced Temporal and Spatial Analysis of Electroencephalographic Signals', Springer Link, pp. 1–19, 2013.

- [5] B. Rosenblatt and J. Gotman, 'Computerized EEG Monitoring', Seminars in Pediatric Neurology, vol. 6, no. 2, pp. 120–127, 1999.

- [6] David E. Blum, 'Computer-based electroencephalography: technical basics, basis for new applications, and potential pitfalls', Electroencephalography and clinical Neurophysiology, vol. 106, no. 2, pp. 118-126, 1998.

- [7] Saeid Sanei, J. A. Chambers; EEG Signal Processing, John Wiley & Sons Ltd, 2007.

- [8] C. Kaur and P. Singh, 'EEG Derived Neuronal Dynamics during Meditation: Progress and Challenges', Advances in Preventive Medicine, vol. 2015, pp. 1-10, 2015.

- [9] http://glneurotech.com/bioradio/wireless-eeg.php

- [10] Jaakko Malmivuo, Robert Plonsey; Bioelectromagnetism: Principles and Applications of Bioelectric and Biomagnetic Fields, 1995, http://www.bem.fi/book/index.htm.

- [11] S. Nishimura, Y. Tomita and T. Horiuchi, 'Clinical application of an active electrode using an operational amplifier', in IEEE Transactions on Biomedical Engineering, vol. 39, no. 10, pp. 1096-1099, 1992.

- [12] Searle and L Kirkup, 'A direct comparison of wet, dry and insulating bioelectric recording electrodes', IOP Science, vol. 21, no. 2, pp 271-283, 2000.

- [13] A. J. Casson, S. Smith, J. S. Duncan and E. Rodriguez-Villegas, 'Wearable EEG: what is it, why is it needed and what does it entail?', 2008 30th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Vancouver, BC, Canada, pp. 5867-5870, 2008.

- [14] A. J. Casson, D. C. Yates, S. J. M. Smith, J. S. Duncan and E. Rodriguez-Villegas, 'Wearable Electroencephalography', in IEEE Engineering in Medicine and Biology Magazine, vol. 29, no. 3, pp. 44-56, 2010.

- [15] N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag and A. P. Chandrakasan, 'A Micro-Power EEG Acquisition SoC With Integrated Feature Extraction Processor for a Chronic Seizure Detection System', in IEEE Journal of Solid-State Circuits, vol. 45, no. 4, pp. 804-816, 2010.

- [16] R. R. Harrison, 'A Versatile Integrated Circuit for the Acquisition of Biopotentials', 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, pp. 115-122, 2007.

- [17] Tzyy-Ping Jung, S. Makeig, M. Stensmo and T. J. Sejnowski, 'Estimating alertness from the EEG power spectrum', in IEEE Transactions on Biomedical Engineering, vol. 44, no. 1, pp. 60-69, 1997.

- [18] Chin-Teng Lin, Ruei-Cheng Wu, Sheng-Fu Liang, Wen-Hung Chao, Yu-Jie Chen and Tzyy-Ping Jung, 'EEG-based drowsiness estimation for safety driving using independent component analysis', in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 12, pp. 2726-2738, 2005.

- [19] C. D. Binnie and H. Stefan, 'Modern electroencephalography: its role in epilepsy management', Clinical Neurophysiology, vol. 110, no. 10, pp. 1671–1697, 1999.

- [20] S. M. Lee, J. H. Kim, H. J. Byeon, Y. Y. Choi, K. S. Park and S. H. Lee, 'A capacitive, biocompatible and adhesive electrode for long-term and cap-free monitoring of EEG signals', Journal of Neural Engineering, vol. 10, no. 3, 2013.

- [21] Z. Chen, G. Lu, Z. Xie and W. Shang, 'A Unified Framework and Method for EEG-Based Early Epileptic Seizure Detection and Epilepsy Diagnosis', in IEEE Access, vol. 8, pp. 20080-20092, 2020.

- [22] H. A. Gonzalez, S. Muzaffar, J. Yoo and I. M. Elfadel, 'BioCNN: A Hardware Inference Engine for EEG-Based Emotion Detection', in IEEE Access, vol. 8, pp. 140896-140914, 2020.

- [23] H. Liu and S. A. Imtiaz, 'Studying the Effects of Compression in EEG-Based Wearable Sleep Monitoring Systems', in IEEE Access, vol. 8, pp. 168486-168501, 2020.

- [24] T. Nakamura, Y. D. Alqurashi, M. J. Morrell and D. P. Mandic, 'Hearables: Automatic Overnight Sleep Monitoring With Standardized In-Ear EEG Sensor', in IEEE Transactions on Biomedical Engineering, vol. 67, no. 1, pp. 203-212, 2020.

- [25] Z. Cao, C. -T. Lin, W. Ding, M. -H. Chen, C. -T. Li and T. -P. Su, 'Identifying Ketamine Responses in Treatment-Resistant Depression Using a Wearable Forehead EEG', in IEEE Transactions on Biomedical Engineering, vol. 66, no. 6, pp. 1668-1679, 2019.

- [26] J. Zhou et al., 'Automatic Sleep Stage Classification With Single Channel EEG Signal Based on Two-Layer Stacked Ensemble Model', in IEEE Access, vol. 8, pp. 57283-57297, 2020

- [27] J. Zhu et al., 'An Improved Classification Model for Depression Detection Using EEG and Eye Tracking Data', in IEEE Transactions on NanoBioscience, vol. 19, no. 3, pp. 527-537, 2020.

- [28] S. Mahato and S. Paul, 'Classification of depression patients and normal subjects based on electroencephalogram (EEG) signal using alpha power and theta asymmetry', J. Med. Syst., vol. 44, no. 1, 2020.

- [29] A. Mehreen, S. M. Anwar, M. Haseeb, M. Majid and M. O. Ullah, 'A Hybrid Scheme for Drowsiness Detection Using Wearable Sensors', in IEEE Sensors Journal, vol. 19, no. 13, pp. 5119-5126, 2019.

- [30] P. Campisi, D. La Rocca, G. Scarano, 'EEG for Automatic Person Recognition', IEEE computer transaction, vol. 45, no. 7, pp. 87-89, 2012.

- [31] Luzheng Bi, Xin-An Fan and Yili Liu, 'EEG-Based Brain-Controlled Mobile Robots: A Survey', IEEE Transactions on Human-Machine Systems, vol. 43, no. 2, pp. 161-176, 2013.

- [32] M. Chiesi, M. Guermandi, S. Placati, E. F. Scarselli and R. Guerrieri, 'Creamino: A Cost-Effective, Open-Source EEG-Based BCI System', in IEEE Transactions on Biomedical Engineering, vol. 66, no. 4, pp. 900-909, 2019.

- [33] P. Arico, G. Borghini, G. D. Flumeri, N. Sciarafa and F. Babiloni, 'Passive BCI beyond the lab: current trends and future directions', Physiological Measurement, vol. 39, no. 8, pp. 1-19, 2018.

- [34] Ana-Maria Petrescu, Delphine Taussig and Viviane Bouilleret, 'Electroencephalogram (EEG) in COVID-19: A systematic retrospective study', Neurophysiologie Clinique, vol. 50, no. 3, pp. 155-165, 2020.

- [35] Alexander J. Casson, 'Wearable EEG and beyond', Biomedical Engineering Letters, vol. 9, pp. 53-71, 2019.

- [36] WHO, 'Epilepsy: A Public Health Imperative', World Health Organization: Geneva, Switzerland, 2019.

- [37] A. F. Setiawan, A. D. Wibawa, M. H. Purnomo and W. R. Islamiyah, "Monitoring Stroke Rehabilitation Re-Learning Program using EEG Parameter: A preliminary study for developing self-monitoring system for stroke rehabilitation during new normal," 2020 International Seminar on Application for Technology of Information and Communication (iSemantic), Semarang, Indonesia, 2020, pp. 620-624.

- [38] J. Yang, J. Zhou, G. Tao, M. Alrashoud, K. N. A. Mutib and M. Al-Hammadi, 'Wearable 3.0: From Smart Clothing to Wearable Affective Robot', in IEEE Network, vol. 33, no. 6, pp. 8-14, 2019.

- [39] A. Dabbaghian, T. Yousefi, S. Z. Fatmi, P. Shafia and H. Kassiri, 'A 9.2-g Fully-Flexible Wireless Ambulatory EEG Monitoring and Diagnostics Headband With Analog Motion Artifact Detection and Compensation', in IEEE Transactions on Biomedical Circuits and Systems, vol. 13, no. 6, pp. 1141-1151, 2019.

- [40] G. Li, B. Lee and W. Chung, 'Smartwatch-Based Wearable EEG System for Driver Drowsiness Detection', in IEEE Sensors Journal, vol. 15, no. 12, pp. 7169-7180, 2015.

- [41] C. Chen et al., 'Novel Flexible Material-Based Unobtrusive and Wearable Body Sensor Networks for Vital Sign Monitoring', in IEEE Sensors Journal, vol. 19, pp. 8502-8513, 2019.

- [42] Insight headset, https://www.emotiv.com/insight.

- [43] Mindwave mobile 2 brainwave sensing headset, https://store.neurosky.com/pages/mindwave.

- [44] Muse 2 meditation device, https://choosemuse.com/muse-2.

- [45] BrainLink Pro smart headset, http://o.macrotellect.com/default.html.

- [46] MyndBand brainwave headset, https://store.myndplay.com/products.php?prod=48.

- [47] Senzeband EEG headband, https://www.neeuro.com/senzeband/

- [48] J. Xu et al., 'A 665 μW Silicon Photomultiplier-Based NIRS/EEG/EIT Monitoring ASIC for Wearable Functional Brain Imaging', in IEEE Transactions on Biomedical Circuits and Systems, vol. 12, no. 6, pp. 1267-1277, 2018.

- [49] Siddharth, A. N. Patel, T. -P. Jung and T. J. Sejnowski, 'A Wearable Multi-Modal Bio-Sensing System Towards Real-World Applications', in IEEE Transactions on Biomedical Engineering, vol. 66, no. 4, pp. 1137-1147, 2019.

- [50] T. Zhan, S. Z. Fatmi, S. Guraya and H. Kassiri, 'A Resource-Optimized VLSI Implementation of a Patient-Specific Seizure Detection Algorithm on a Custom-Made 2.2 cm2 Wireless Device for Ambulatory Epilepsy Diagnostics', in IEEE Transactions on Biomedical Circuits and Systems, vol. 13, no. 6, pp. 1175-1185, 2019.

- [51] G. Li and W. Chung, 'Combined EEG-Gyroscope-tDCS Brain Machine Interface System for Early Management of Driver Drowsiness', in IEEE Transactions on Human-Machine Systems, vol. 48, no. 1, pp. 50-62, 2018.

- [52] S. -Y. Yang and Y. -P. Lin, 'Validating a LEGO-Like EEG Headset for a Simultaneous Recording of Wetand Dry-Electrode Systems During Treadmill Walking', 2020 42nd Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Montreal, QC, Canada, 2020.

- [53] EEG tests and epilepsy, https://www.epilepsy.org.uk/info/diagnosis/eeg-electroencephalogram

- [54] S. Iranmanesh and E. Rodriguez-Villegas, 'A 950 nW Analog-Based Data Reduction Chip for Wearable EEG Systems in Epilepsy', in IEEE Journal of Solid-State Circuits, vol. 52, no. 9, pp. 2362-2373, 2017.

- [55] CC2640R2F SimpleLink Bluetooth low energy wireless MCU, https://www.ti.com/lit/ds/symlink/cc2640r2f.pdf

# **Chapter 2 - Design Specifications and Literature Review**

#### 2.1 Overview

Current advancements in very-large-scale integration technology motivate engineers to look for low-cost system-on-chip alternatives to most large multi-chip systems. One area gaining a lot of attention is physiological signal acquisition devices. Such devices have stringent implementation requirements, like long-term operation, without replacing the energy source, small size with lack of wires to reduce the probability of infection and, in some cases, wireless transmission.

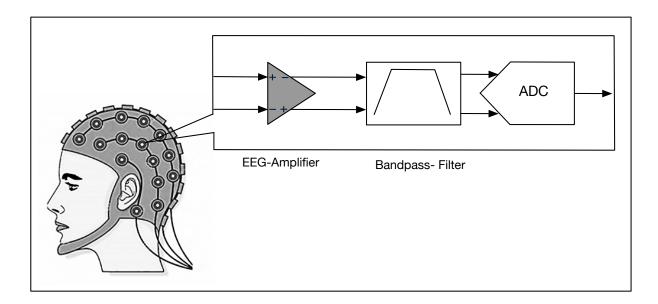

Figure 2.1 Placement of the instrumentation amplifier in an EEG recording system.