Technische Universität Dresden

# Implementation of bioinspired algorithms on the neuromorphic VLSI system SpiNNaker 2

Dipl.-Ing.

### Yexin Yan

## der Fakultät Elektrotechnik und Informationstechnik der Technische Universität Dresden

zur Erlangung des akademischen Grades

### Doktoringenieur

(Dr.-Ing.)

### genehmigte Dissertation

Vorsitzender:Prof. Dr. rer. nat. Stefan MannsfeldTag der Einreichung24.03.2022Gutachter:Prof. Dr.-Ing. habil. Christian Georg MayrTag der Verteidigung15.12.2022Gutachter:Prof. Dr. Emre NeftciTag der Verteidigung15.12.2022

ii

### Acknowledgements

First and foremost I would like to thank my supervisor Prof. Christian Mayr who provided me the opportunity to work on SpiNNaker 2 and guided me throughout the journey of my PhD. His expertise and insightful feedback were invaluable and pushed me to sharpen my thinking and brought my work to a higher level.

This work wouldn't have been possible without my collaborators from the chair of highly parallel VLSI systems and neuromorphic circuits at Technische Universität Dresden, the University of Manchester, Technische Universität Graz, the University of Waterloo and Applied Brain Research. In particular, I would like to thank Dr. Andrew Rowley and Andreas Dixius for explanations of the software of SpiNNaker 1 and the hardware of the first SpiNNaker 2 prototype when I was getting started, and Dr. Sebastian Höppner and Bernhard Vogginger for the collaboration on the implementation of the software demonstrating DVFS with spiking neural networks. In addition, I would like to thank Dr. David Kappel, Prof. Robert Legenstein and Prof. Wolfgang Maass for showing me the world of Bayesian reinforcement learning and for the collaboration on the implementation of reward-based synaptic sampling on the SpiNNaker 2 prototype. Also, I would like to thank Dr. Terrence Stewart, Dr. Xuan Choo and Prof. Chris Eliasmith for introducing me to control theory and for the collaboration on the implementation of keyword spotting and adaptive control and comparison with Loihi. Furthermore, I would like to thank Felix Neumärker, Dr. Johannes Partzsch and Florian Kelber for designing the random number generator, the exponential accelerator and the MAC array which my work was based on.

Last but not the least, I would like to thank my family for their unconditional support throughout the years.

ii

### Abstract

It is believed that neuromorphic hardware will accelerate neuroscience research and enable the next generation edge AI. On the other hand, brain-inspired algorithms are supposed to work efficiently on neuromorphic hardware. But both processes don't happen automatically. To efficiently bring together hardware and algorithm, optimizations are necessary based on the understanding of both sides. In this work, software frameworks and optimizations for efficient implementation of neural network-based algorithms on SpiNNaker 2 are proposed, resulting in optimized power consumption, memory footprint and computation time. In particular, first, a software framework including power management strategies is proposed to apply dynamic voltage and frequency scaling (DVFS) to the simulation of spiking neural networks, which is also the first-ever software framework running a neural network on SpiNNaker 2. The result shows the power consumption is reduced by 60.7% in the synfire chain benchmark. Second, numerical optimizations and data structure optimizations lead to an efficient implementation of reward-based synaptic sampling, which is one of the most complex plasticity algorithms ever implemented on neuromorphic hardware. The results show a reduction of computation time by a factor of 2 and energy consumption by 62%. Third, software optimizations are proposed which effectively exploit the efficiency of the multiply-accumulate array and the flexibility of the ARM core, which results in, when compared with Loihi, 3 times faster inference speed and 5 times lower energy consumption in a keyword spotting benchmark, and faster inference speed and lower energy consumption for adaptive control benchmark in high dimensional cases. The results of this work demonstrate the potential of SpiNNaker 2, explore its range of applications and also provide feedback for the design of the next generation neuromorphic hardware.

iv

## Kurzfassung

Neuromorphe Hardware trägt die Hoffnung, Neurowissenschaft voranzutreiben und die nächste Generation von Edge KI zu ermöglichen. Zudem wird erwartet, dass sich vom Gehirn inspirierte Algorithmen effizient auf neuromorpher Hardware umsetzen lassen. Aber das Zusammenspiel geschieht nicht automatisch. Um Hardware und Algorithmus effizient zusammenzubringen, sind Optimierungen notwendig, die auf dem Verständnis beider Seiten basieren. In dieser Arbeit werden Software-Frameworks und Optimierungen für die effiziente Implementierung von Algorithmen auf Basis von neuronalen Netzen auf dem neuromorphen System SpiNNaker 2 vorgeschlagen, die Leistungsaufnahme, Speicherbedarf und Rechenzeit optimieren. Insbesondere wird erstens ein Software-Framework inklusive Power Management Strategien vorgeschlagen für die Anwendung von Dynamic Voltage and Frequency Scaling für die Simulation von gepulsten neuronalen Netzen. Dies stellt das erste Software-Framework dar, womit ein neuronales Netzwerk auf SpiNNaker 2 realisiert wurde. Das Ergebnis zeigt eine Reduzierung der Leistungsaufnahme um 60.7%. Zweitens führen numerische- und Datenstruktur-Optimierungen zu einer effizienten Implementierung von Reward-basiertem Synaptic Sampling: einer der kompliziertesten Plastizitäts-Algorithmen, der jeweils auf neuromorpher Hardware implementiert wurde. Die Ergebnisse zeigen eine Reduktion der Rechenzeit um den Faktor 2 und des Energieverbrauchs um 62%. Drittens werden Software-Optimierungen vorgeschlagen, die die Effizienz vom Multiply-Accumulate Array und die Flexibilität vom ARM core von SpiNNaker 2 effektiv ausnutzen können, was im Vergleich zu Intels neuromorphen Chip Loihi zu 3-mal schnellerer Inferenzgeschwindigkeit und 5-mal niedrigerem Energieverbrauch in der Keyword-Spotting Benchmark führt. Ergebnisse dieser Arbeit zeigen das Potenzial von SpiNNaker 2, explorieren dessen Umfang von Anwendungen und stellen Feedback für den Entwurf von der nächsten Generation neuromorpher Hardware zur Verfügung.

vi

## Contents

| Li       | List of Figures xi |         |                                                       |           |  |

|----------|--------------------|---------|-------------------------------------------------------|-----------|--|

| Li       | st of              | Table   | 5                                                     | xix       |  |

| G        | lossa              | ry      |                                                       | xxi       |  |

| 1        | Intr               | oducti  | ion                                                   | 1         |  |

|          | 1.1                | Motiva  | ation and Background                                  | 1         |  |

|          | 1.2                | SpiNN   | Vaker 2 and Contribution of This Work                 | 4         |  |

|          | 1.3                | Public  | eations                                               | 6         |  |

| <b>2</b> | Fun                | damer   | Itals                                                 | 9         |  |

|          | 2.1                | The S   | piNNaker 2 System                                     | 9         |  |

|          | 2.2                | Neuro   | n and Synapse                                         | 11        |  |

|          | 2.3                | Neura   | l Network                                             | 17        |  |

| 3        | Effic              | cient S | piking Neural Network Simulation using Dynamic Voltag | ge        |  |

|          | and                | Frequ   | ency Scaling                                          | <b>21</b> |  |

|          | 3.1                | Introd  | uction                                                | 21        |  |

|          | 3.2                | Power   | Management Hardware                                   | 23        |  |

|          | 3.3                | Spikin  | g Neural Network Model                                | 24        |  |

|          |                    | 3.3.1   | Locally Connected Network                             | 24        |  |

|          |                    | 3.3.2   | Synfire Chain Network                                 | 25        |  |

|          | 3.4                | Softwa  | are Flow                                              | 26        |  |

|          |                    | 3.4.1   | Basic Software Flow                                   | 26        |  |

|          |                    | 3.4.2   | DVFS Software Flow                                    | 29        |  |

|          | 3.5                | Power   | Management Strategies                                 | 31        |  |

|   |     | 3.5.1  | Performance Level Selection                                                                                                                                                                            | 31 |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.5.2  | Energy Model                                                                                                                                                                                           | 33 |

|   |     | 3.5.3  | Power Measurement Strategy                                                                                                                                                                             | 35 |

|   | 3.6 | Measu  | rement Results on Test Chip                                                                                                                                                                            | 35 |

|   |     | 3.6.1  | Locally Connected Network                                                                                                                                                                              | 36 |

|   |     | 3.6.2  | Synfire Chain                                                                                                                                                                                          | 38 |

|   | 3.7 | Conclu | usion                                                                                                                                                                                                  | 42 |

| 4 | Rev | vard-B | ased Synaptic Sampling Enables Learning in Edge Devices                                                                                                                                                | 43 |

|   | 4.1 | Introd | uction                                                                                                                                                                                                 | 43 |

|   | 4.2 | Hardw  | vare Accelerators for RNG and EXP                                                                                                                                                                      | 46 |

|   |     | 4.2.1  | Random Number Generator                                                                                                                                                                                | 46 |

|   |     | 4.2.2  | Exponential Function Accelerator                                                                                                                                                                       | 47 |

|   | 4.3 | Rewar  | d-based Synaptic Sampling                                                                                                                                                                              | 48 |

|   |     | 4.3.1  | Neuron Model                                                                                                                                                                                           | 48 |

|   |     | 4.3.2  | Synapse Model                                                                                                                                                                                          | 49 |

|   |     | 4.3.3  | Reward-based Synaptic Sampling                                                                                                                                                                         | 50 |

|   |     | 4.3.4  | Random Reallocation of Synapse Memory                                                                                                                                                                  | 52 |

|   | 4.4 | Softwa | are Implementation and Optimizations                                                                                                                                                                   | 54 |

|   |     | 4.4.1  | Reducing computation time with hardware generated uniform                                                                                                                                              |    |

|   |     |        | random numbers                                                                                                                                                                                         | 54 |

|   |     | 4.4.2  | Reducing computation time with exponential function accelerator $% \left( {{{\bf{x}}_{i}}} \right)$                                                                                                    | 55 |

|   |     | 4.4.3  | Reducing memory footprint with 16-bit floating point data type $% \left( {{{\left[ {{{\left[ {{\left[ {{\left[ {{\left[ {{{c}}} \right]}} \right]_{i}} \right.} \right]_{i}}}}} \right]_{i}}} \right)$ | 56 |

|   |     | 4.4.4  | Local Computation                                                                                                                                                                                      | 56 |

|   |     | 4.4.5  | Memory Model                                                                                                                                                                                           | 57 |

|   |     | 4.4.6  | $\operatorname{Program}$ Flow and SpiNNaker Software Framework Integration $% \operatorname{Program}$ .                                                                                                | 59 |

|   | 4.5 | Measu  | rement Results on Test Chip                                                                                                                                                                            | 60 |

|   |     | 4.5.1  | Computation Time of Plasticity Update                                                                                                                                                                  | 61 |

|   |     | 4.5.2  | Network Description                                                                                                                                                                                    | 61 |

|   |     | 4.5.3  | Implementation Results                                                                                                                                                                                 | 63 |

|   |     | 4.5.4  | Power and Energy Measurement Results                                                                                                                                                                   | 66 |

|   | 4.6 | Discus | sion                                                                                                                                                                                                   | 67 |

|   |     | 4.6.1  | Scalability                                                                                                                                                                                            | 67 |

### CONTENTS

|          |       | 4.6.2   | Comparison with SpiNNaker 1                                                                                                            | 68        |

|----------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          |       | 4.6.3   | Comparison with other neuromorphic platforms                                                                                           | 68        |

|          | 4.7   | Conclu  | usion                                                                                                                                  | 69        |

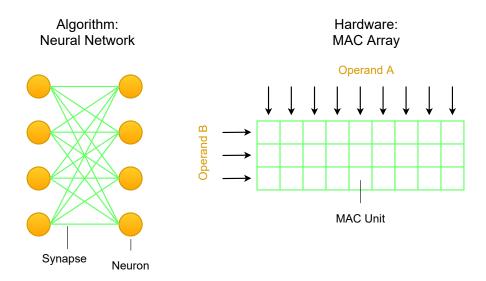

| <b>5</b> | Hył   | orid SI | NN DNN operation                                                                                                                       | <b>71</b> |

|          | 5.1   | Introd  | $uction \ldots \ldots$ | 71        |

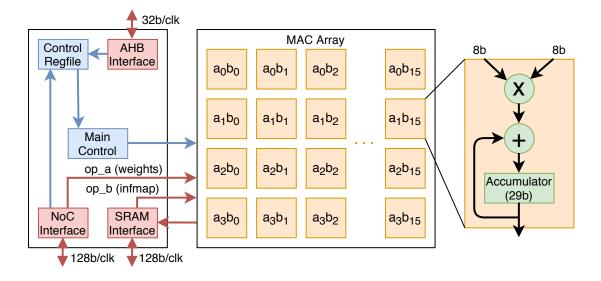

|          | 5.2   | MAC     | Array                                                                                                                                  | 73        |

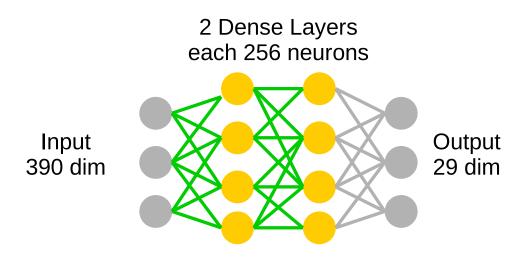

|          | 5.3   | Keywo   | ord Spotting Model and Implementation                                                                                                  | 75        |

|          |       | 5.3.1   | Model Description                                                                                                                      | 75        |

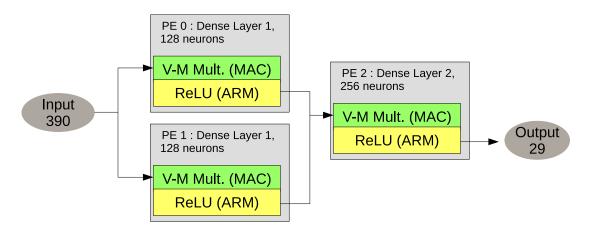

|          |       | 5.3.2   | Mapping Strategy and Software Implementation                                                                                           | 76        |

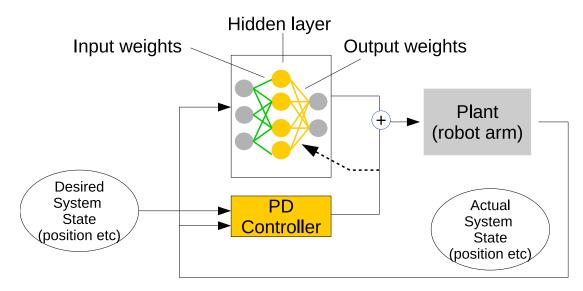

|          | 5.4   | Adapt   | vive Control Model and Implementation                                                                                                  | 77        |

|          |       | 5.4.1   | Model Description                                                                                                                      | 77        |

|          |       | 5.4.2   | Mapping Strategy and Software Implementation                                                                                           | 78        |

|          | 5.5   | Measu   | rement Results and Comparison with Loihi                                                                                               | 80        |

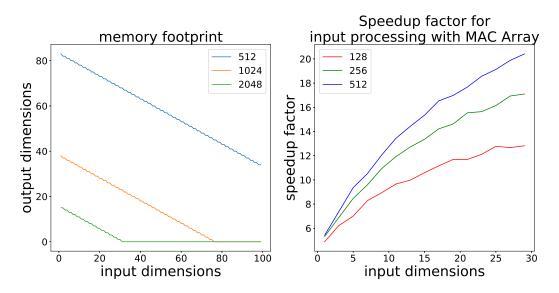

|          |       | 5.5.1   | Keyword Spotting: Memory Footprint                                                                                                     | 81        |

|          |       | 5.5.2   | Keyword Spotting: Computation Time and Comparison with Loihi                                                                           | 81        |

|          |       | 5.5.3   | Keyword Spotting: Energy Measurement and Comparison with                                                                               |           |

|          |       |         | Loihi                                                                                                                                  | 83        |

|          |       | 5.5.4   | Adaptive Control: Memory Footprint                                                                                                     | 83        |

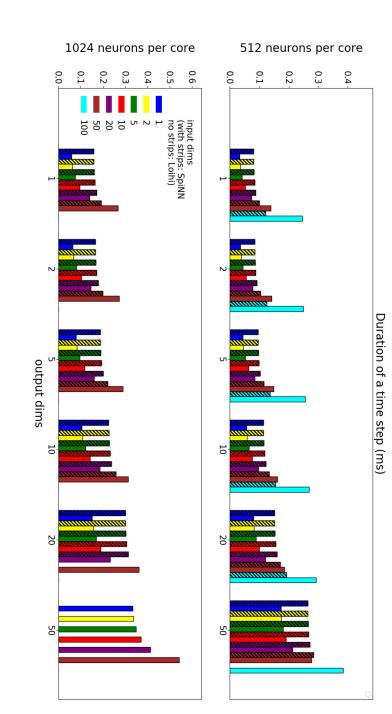

|          |       | 5.5.5   | Adaptive Control: Computation Time and Comparison with Loihi                                                                           | 84        |

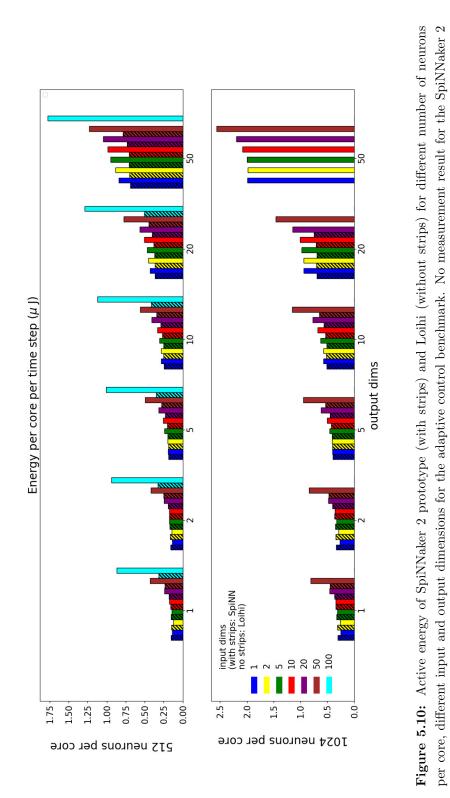

|          |       | 5.5.6   | Adaptive Control: Energy Measurement and Comparison with                                                                               |           |

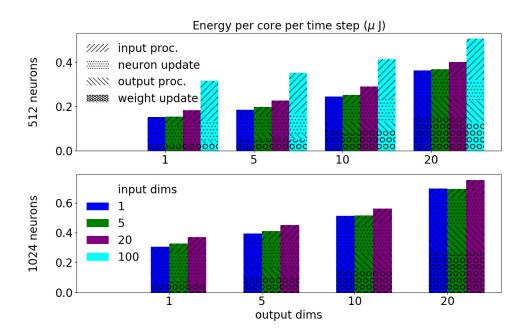

|          |       |         | Loihi                                                                                                                                  | 87        |

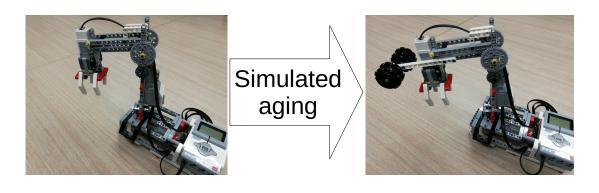

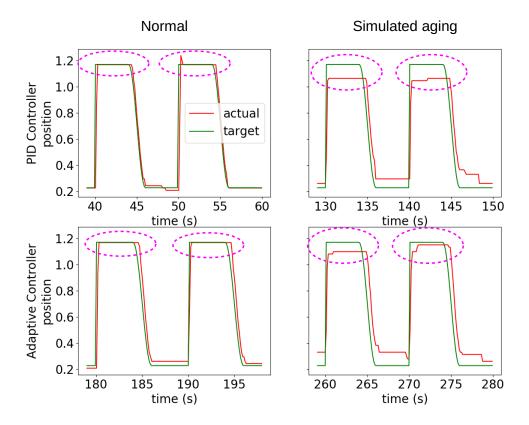

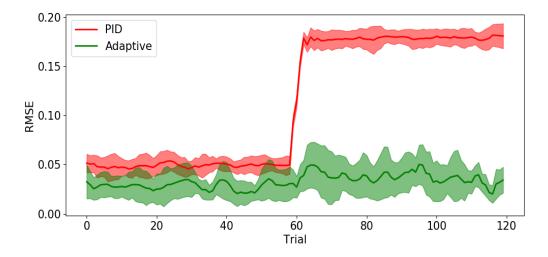

|          |       | 5.5.7   | Adaptive Control: Robotic Demo                                                                                                         | 91        |

|          | 5.6   | Discus  | ssion                                                                                                                                  | 92        |

|          |       | 5.6.1   | Comparison with SpiNNaker 1                                                                                                            | 92        |

|          |       | 5.6.2   | Comparison with other neuromorphic platforms                                                                                           | 93        |

|          | 5.7   | Conclu  | usion                                                                                                                                  | 94        |

| 6        | Sun   | nmary   | and Outlook                                                                                                                            | 97        |

|          | 6.1   | Summ    | ary                                                                                                                                    | 97        |

|          | 6.2   | Outlo   | ok                                                                                                                                     | 98        |

| R        | efere | nces    | 1                                                                                                                                      | 101       |

### List of Figures

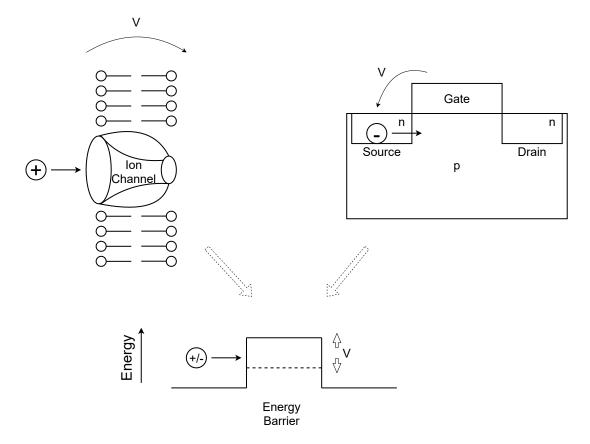

- 1.1 Upper left: the ion channels in the neuron membrane control the ions flowing into the neuron, which effectively forms an energy barrier for the ions. This energy barrier is found to depend on various factors including the difference of electrical potential between the extracellular and interior fluid of the neuron cell. Upper right: in a metal–oxide–semiconductor field-effect transistor (MOSFET) (in this case an N-type MOSFET), the gate voltage controls the energy barrier between the source and drain, thus controlling the charge carriers (in this case the electrons) flowing from source to drain. This similarity was first discovered by Carver Mead, who started to build circuits to mimic the biological neural network, which then developed into the field of neuromorphic engineering.

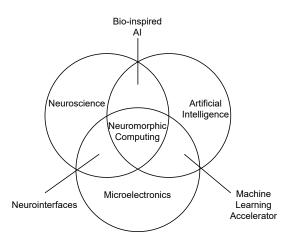

- 1.2 Relation between neuromorphic engineering, neuroscience, artificial intelligence and microelectronics. Neuromorphic engineering is an interdisciplinary research area at the intersection between neuroscience, AI and microelectronics.

3

4

9

2.1 Rendering of the final SpiNNaker 2 system consisting of 16 racks. Each rack contains 90 SpiNNaker 2 boards. Each board contains 48 SpiN-Naker 2 chips. Each SpiNNaker 2 chip contains 152 cores (Processing Elements). The final SpiNNaker 2 system has 16 racks, 1440 SpiNNaker 2 boards, 69,120 SpiNNaker 2 chips and 10,506,240 cores.

### LIST OF FIGURES

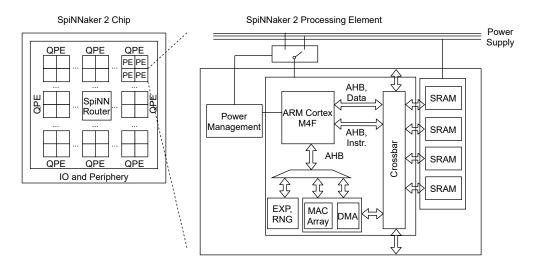

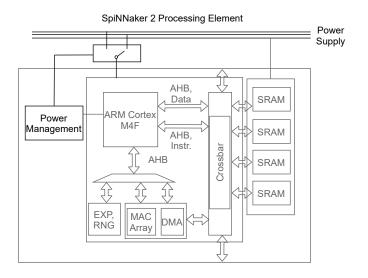

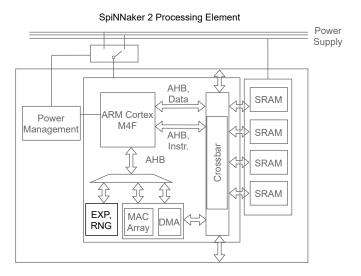

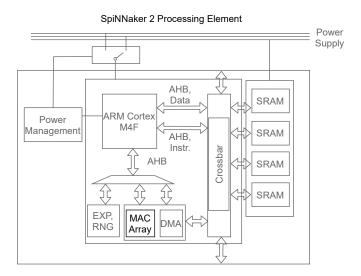

| 2.2 | Simplified schematic of SpiNNaker 2 chip and SpiNNaker 2 Processing                  |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | Element. The final SpiNNaker 2 chip contains 38 QPEs where each                      |    |

|     | QPE contains 4 PEs, a SpiNNaker Router and IO and periphery. The                     |    |

|     | PE contains an ARM Cortex M4F core, SRAM, power management                           |    |

|     | module, numerical accelerators like the exponential function accelerator             |    |

|     | and random number generator, and MAC array. $\ldots$                                 | 10 |

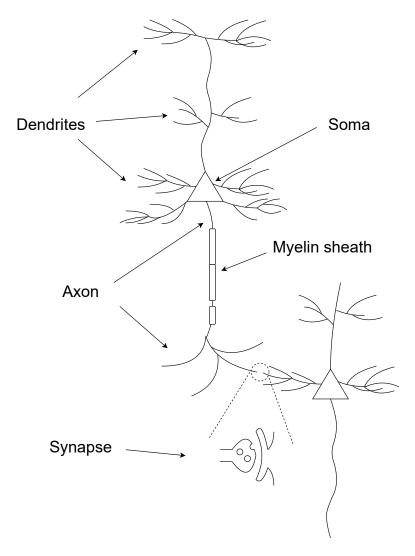

| 2.3 | Schematic drawing of a pyramidal neuron with dendrites, soma, axon                   |    |

|     | and synapse.                                                                         | 12 |

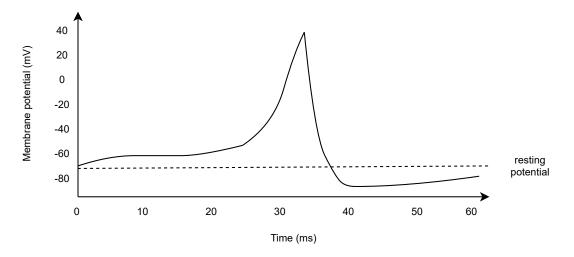

| 2.4 | Schematic drawing of a spike                                                         | 13 |

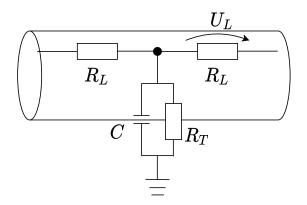

| 2.5 | Illustration of cable theory.                                                        | 15 |

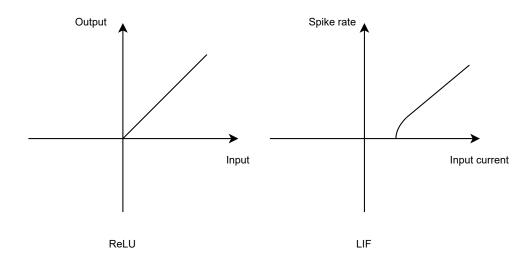

| 2.6 | Similar input-output relation of ReLU and LIF                                        | 16 |

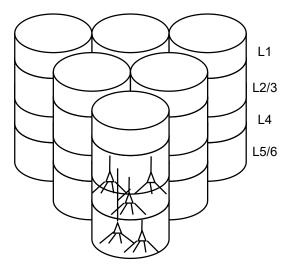

| 2.7 | The hypothesized columnar structure of the neocortex with six layers in              |    |

|     | the vertical direction and similar columnar arrangement in the horizontal            |    |

|     | direction                                                                            | 17 |

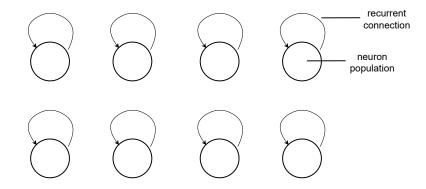

| 2.8 | A winner-take-all network with three excitatory populations and one                  |    |

|     | inhibitory population.                                                               | 18 |

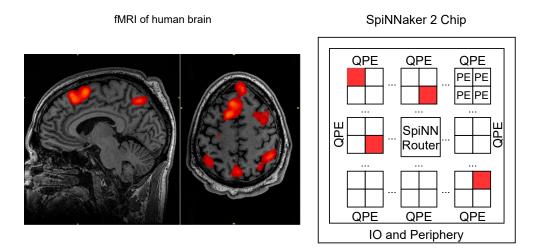

| 3.1 | Left: Functional magnetic resonance imaging (fMRI) of a human brain                  |    |

|     | undertaking a working memory task. The red color indicates the change                |    |

|     | in activity level in certain regions during the time when the task is per-           |    |

|     | formed [1]. Right: The SpiNNaker 2 chip with DVFS enabling each PE                   |    |

|     | to adjust its Performance Level (PL) individually according to its work              |    |

|     | load. The red color indicates increased PL of certain PEs at a certain               |    |

|     | time point                                                                           | 21 |

| 3.2 | Power management in the SpiNNaker 2 PE architecture                                  | 23 |

| 3.3 | The locally connected network for the measurement of the energy per                  |    |

|     | neuron update and energy per synaptic operation. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 24 |

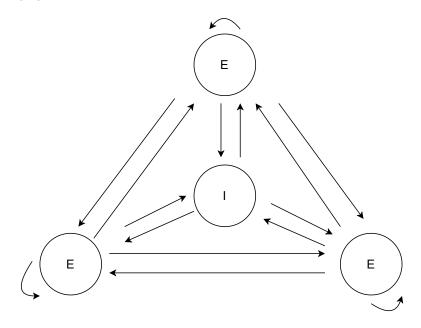

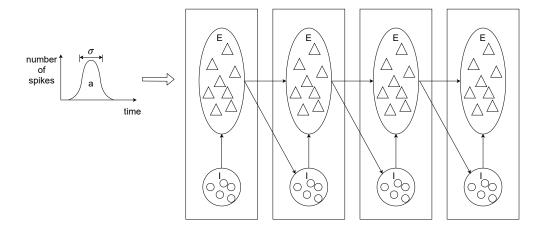

| 3.4 | Network structure of synfire chain. 'E' stands for excitatory and 'I'                |    |

|     | stands for inhibitory. A pulse packet is usually used to kick-off the                |    |

|     | network activity in a simulation                                                     | 25 |

28

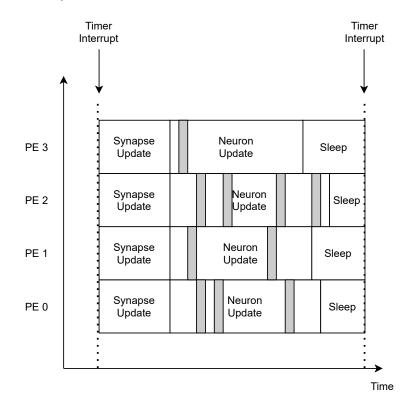

| 3.5 | Illustration of SpiNNaker 1 software flow. The software runs on the ARM $$ |

|-----|----------------------------------------------------------------------------|

|     | cores independently. In each time step, there are two processing steps:    |

|     | synapse update and neuron update. After these two steps are finished,      |

|     | the ARM core goes to sleep. Note that the processing is interrupted by     |

|     | incoming spike events which need to be processed immediately (shown        |

|     | in grey)                                                                   |

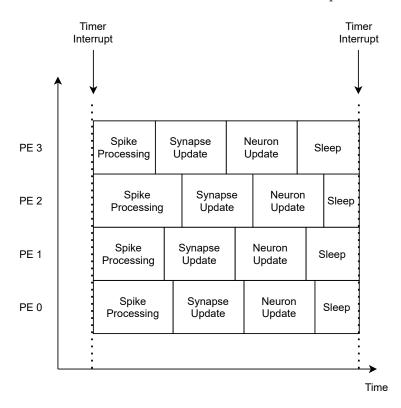

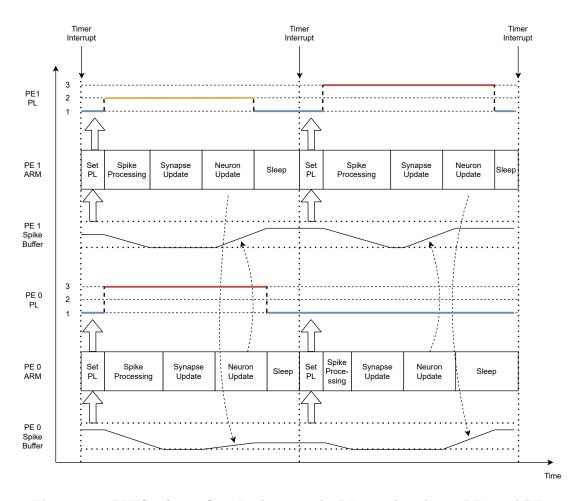

- 3.6 The basic software flow running on SpiNNaker 2. In each time step, there are three processing steps: spike processing, synapse update and neuron update. The difference to the SpiNNaker 1 software flow is that the spike processing is not done immediately after receiving the spike. Instead, the spikes are buffered and processed in the next time step, which is the basis for DVFS software flow.

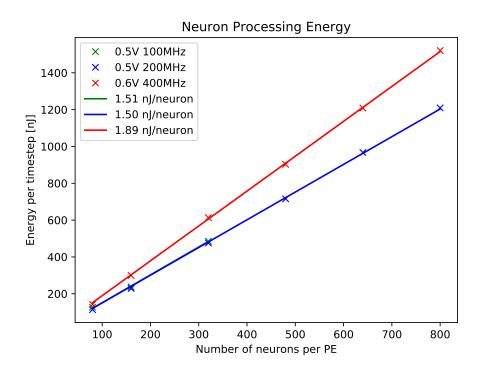

- 3.9 Energy per timestep for different number of synaptic events per PE ~ . ~ 37 ~

### LIST OF FIGURES

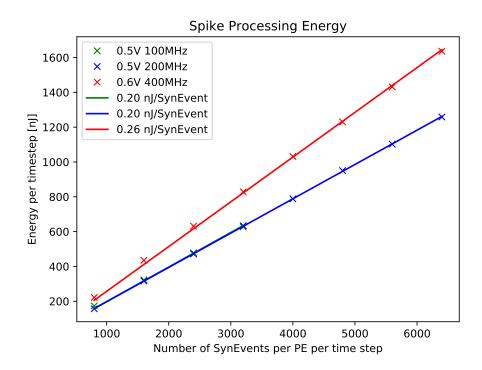

| 3.10 | Simulation of synfire chain. The X-axis shows time in milliseconds. In                                                                                                   |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the label of the Y-axis, c0 denotes PE 0, c1 denotes PE 1 and so on. For                                                                                                 |    |

|      | each PE, two panels are shown, one for the spike train (blue), and one                                                                                                   |    |

|      | for the number of received spikes (green) and the PL chosen (red). At                                                                                                    |    |

|      | the start of the simulation, a stimulus pulse packet is used to kick start                                                                                               |    |

|      | the network activity. These spikes are sent from PE 3 (top panel) to PE $$                                                                                               |    |

|      | 0 (bottom panel), as can be seen from the rise of the number of incoming $% \left( $ |    |

|      | spikes in PE 0. The rise of the incoming spikes causes PE 0 to raise its                                                                                                 |    |

|      | PL from PL 1 over PL 2 to PL3. After a short delay, the neurons in PE $$                                                                                                 |    |

|      | $0\ {\rm start}$ to fire, sending spikes to PE 1, and so on. The spike pulse packet                                                                                      |    |

|      | from one layer to the next layer becomes more and more synchronous                                                                                                       |    |

|      | over time                                                                                                                                                                | 40 |

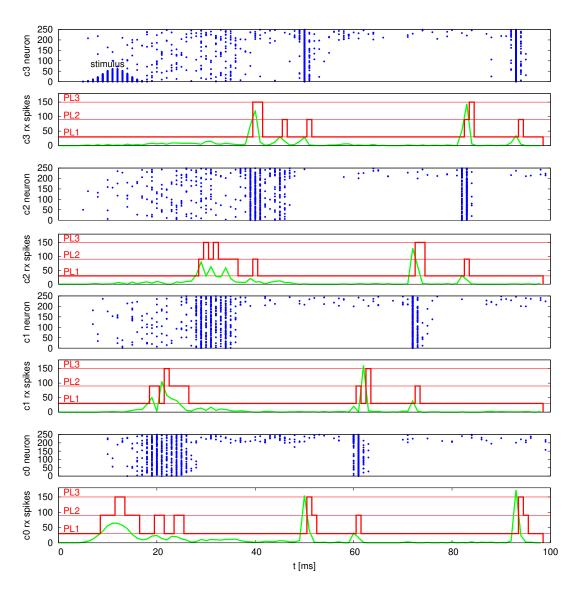

| 3.11 | DVFS model vs. measurement                                                                                                                                               | 41 |

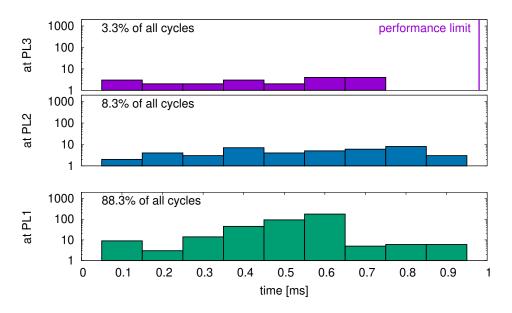

| 3.12 | Histogram of simulation cycles $(1 \text{ ms})$ processed at different PLs versus                                                                                        |    |

|      | time                                                                                                                                                                     | 42 |

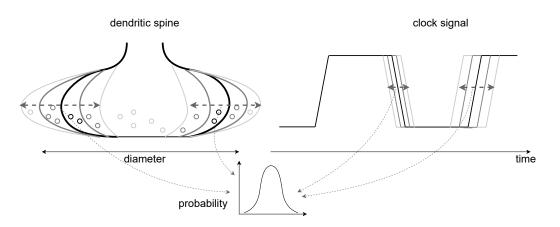

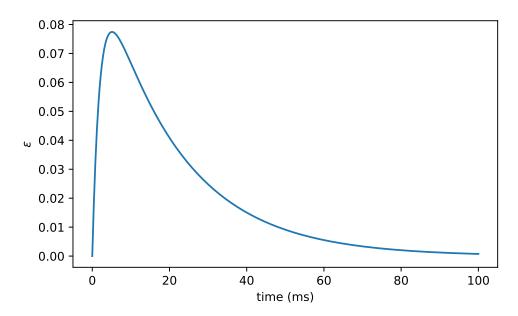

4.1 Left: as observed in biophysiological experiments, the size of a synapse changes randomly over time, causing random synaptic weight fluctuations. This randomness is believed to be involved in the stochastic computation employed by biology. The different darkness of the lines indicates the probability of the size of a synapse. Right: the rising and falling edges of a clock signal in a digital circuit. The clock signal is generated by the clock-generator. The deviation of the generated clock period from the ideal clock period is the jitter, which could change randomly over time. The different darkness of the lines indicates the probability of the rising and falling edges. 434.2Hardware accelerators in the SpiNNaker 2 PE architecture. . . . . . 46Illustration of the shape of  $\epsilon(t)$  in equation 4.3. 494.3. . . . . . . . . . . . .

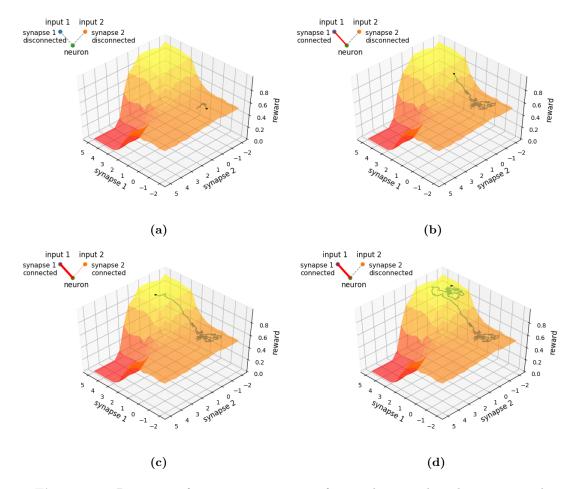

| 4.4        | Dynamics of synaptic parameters of a simple network with 2 inputs and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | a single neuron (upper left). The strength of the synaptic connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|            | is illustrated with the width of the red line. When the synapse is dis-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|            | connected, it is shown as a dashed line. The two horizontal axes are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|            | the synaptic parameters for synapse 1 and synapse 2. The vertical axis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|            | is the reward. The synaptic parameters explore the parameter space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|            | stochastically guided by the reward signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

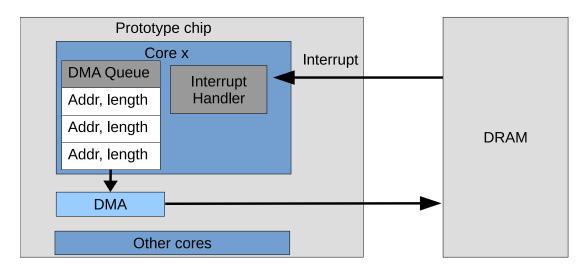

| 4.5        | The time and energy-consuming interaction between the SpiNNaker 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|            | prototype chip and the DRAM chip, which could be saved by storing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|            | data locally in SRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56 |

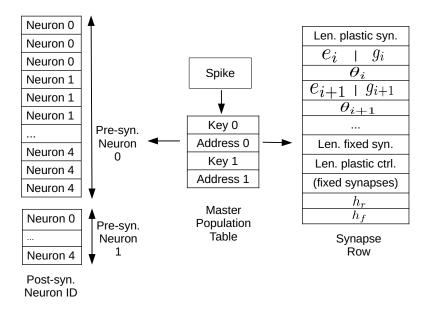

| 4.6        | Memory model with master population table, synapse rows and postsy-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|            | naptic neuron ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58 |

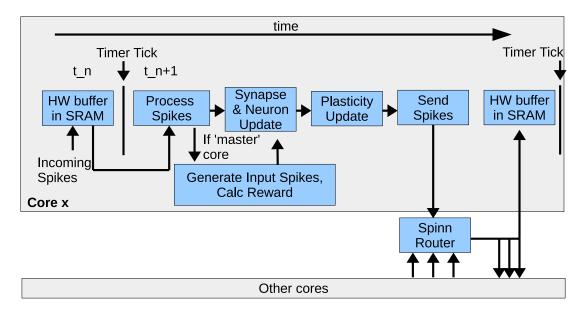

| 4.7        | SpiNNaker software framework. Each simulation time step $t_n$ is triggered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|            | by the timer tick interrupt. At the end of the time step, the spikes are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|            | sent to the SpiNNaker router which then multicasts the spikes to other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|            | cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59 |

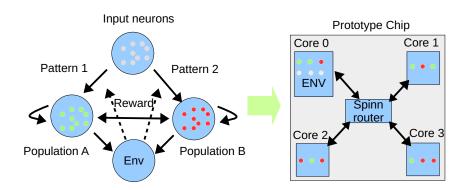

| 4.8        | Illustration of the network topology (left) and its mapping to the proto-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|            | type chip (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62 |

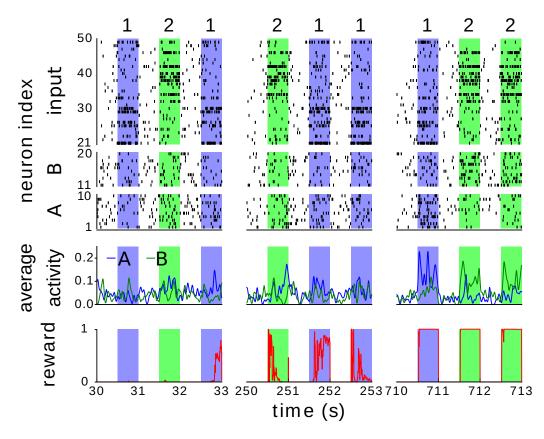

| 4.9        | Network activity and reward throughout learning. Shaded areas indicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|            | the presented patterns. Spike trains (top) of the two populations and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|            | input spikes. 30 neurons were randomly chosen from the 200 inputs. $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64 |

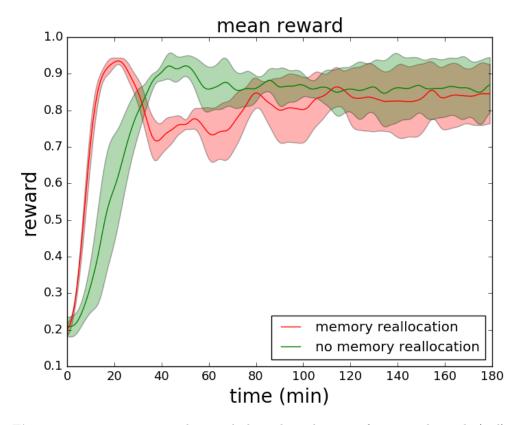

| 4.10       | Time-averaged reward throughout learning for networks with (red) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|            | without (green) random reallocation of synapse memory. $\hfill \hfill \$ | 65 |