Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-1997

# A Framework for an Automated Compilation System for Reconfigurable Architectures

George R. Roelke IV

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Computer and Systems Architecture Commons

#### **Recommended Citation**

Roelke, George R. IV, "A Framework for an Automated Compilation System for Reconfigurable Architectures" (1997). *Theses and Dissertations*. 5936. https://scholar.afit.edu/etd/5936

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

A FRAMEWORK FOR AN AUTOMATED COMPILATION SYSTEM FOR RECONFIGURABLE ARCHITECTURES

THESIS

George R. Roelke IV 2nd Lieutenant, USAF

AFIT/GE/ENG/97M-01

DISTRIBUTION STATEMENT J

Approved for public releases Distribution Unlimited

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

#### AFIT/GE/ENG/97M-01

# A FRAMEWORK FOR AN AUTOMATED COMPILATION SYSTEM FOR RECONFIGURABLE ARCHITECTURES

## THESIS

George R. Roelke IV 2nd Lieutenant, USAF

#### AFIT/GE/ENG/97M-01

19970402 078

Approved for public release; distribution unlimited.

#### AFIT/GE/ENG/97M-01

# A FRAMEWORK FOR AN AUTOMATED COMPILATION SYSTEM FOR RECONFIGURABLE ARCHITECTURES

.

## THESIS

Presented to the Faculty of the Graduate School of Engineering

of the Air Force Institute of Technology

**Air University**

In Partial Fulfillment of the

**Requirements for the Degree of**

**Master of Science in Computer Engineering**

George R. Roelke IV

2nd Lieutenant, USAF

## **March 1997**

Approved for public release; distribution unlimited.

#### Preface

The purpose of this thesis was to investigate the problem of automating the development of applications for reconfigurable computers. This was accomplished by creating a framework for a high-level language based development system, determining the key tasks involved, and creating a test implementation of part of the system.

I would like to thank all of the people who have given me advice, support, and encouragement throughout the thesis process. I would like to thank my thesis advisor, Dr. Henry Potoczny, for providing guidance and encouragement, and for helping me see the obvious. I also owe a great deal of thanks to my (other) advisor, Lt.Col. Dave Gallagher. Although I was not technically his thesis student, he spent countless hours with me discussing the problems, processes, and solutions contained in this document. And along the way, he even managed to give a few Air Force insights to this brand new Second Lieutenant.

I would also like to thank the other member of my committee, Lt.Col. Tom Wailes, for providing several much needed comments, and pointing out one or two areas of additional research. In addition, I must thank the sponsor of this research, Keith Anthony of the National Air Intelligence Center, for providing a fascinating topic, and for allowing me the flexibility to choose my own path into this wide-open area of research.

Finally, I owe thanks to everyone who has helped me stay sane throughout my 18 months at AFIT. I'd like to thank James Savage, Javier Marti, Bruce Hunt, and everyone

else in the VLSI lab, whose humor lightened up more than one dark and stressful day. And most of all, I'd like to thank my parents and my brothers, for providing the continued love, understanding, and support that have helped carry me to where I am today.

George Roelke

# Table of Contents

| Pre | efaceii                                                                                                                                                                             |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tal | ole of Contentsiv                                                                                                                                                                   |  |  |

| Lis | List of Figuresix                                                                                                                                                                   |  |  |

| Lis | List of Tablesxi                                                                                                                                                                    |  |  |

| Ab  | Abstractxii                                                                                                                                                                         |  |  |

|     | ntroduction         1           1.1 Background         1           1.2 Problem         4                                                                                            |  |  |

|     | 1.3 Assumptions                                                                                                                                                                     |  |  |

|     | 1.4 Objectives                                                                                                                                                                      |  |  |

|     | 1.5 Approach/Methodology9                                                                                                                                                           |  |  |

|     |                                                                                                                                                                                     |  |  |

| II. | Background11                                                                                                                                                                        |  |  |

|     | <b>Background11</b><br>2.1 Introduction                                                                                                                                             |  |  |

|     | -                                                                                                                                                                                   |  |  |

|     | 2.1 Introduction                                                                                                                                                                    |  |  |

|     | 2.1 Introduction       11         2.2 Programmable Logic Devices       11                                                                                                           |  |  |

|     | 2.1 Introduction       11         2.2 Programmable Logic Devices       11         2.2.1 Overview       11                                                                           |  |  |

|     | 2.1 Introduction       11         2.2 Programmable Logic Devices       11         2.2.1 Overview       11         2.2.2 FPGA Configuration       13                                 |  |  |

|     | 2.1 Introduction112.2 Programmable Logic Devices112.2.1 Overview112.2.2 FPGA Configuration132.2.3 FPGA Advantages14                                                                 |  |  |

|     | 2.1 Introduction112.2 Programmable Logic Devices112.2.1 Overview112.2.2 FPGA Configuration132.2.3 FPGA Advantages142.2.4 FPGA Limitations14                                         |  |  |

|     | 2.1 Introduction112.2 Programmable Logic Devices112.2.1 Overview112.2.2 FPGA Configuration132.2.3 FPGA Advantages142.2.4 FPGA Limitations142.2.5 Estimates of Future Capabilities15 |  |  |

|      | 2.3.2.1 Description                         | 21 |

|------|---------------------------------------------|----|

|      | 2.3.2.2 The CHAMP I System                  | 22 |

|      | 2.3.3 The Dynamic Instruction Set Model     | 24 |

|      | 2.3.4 Summary                               | 29 |

|      | 2.4 Tools for Application Development       | 29 |

|      | 2.4.1 Design Process                        | 31 |

|      | 2.4.1.1 Partitioning                        | 31 |

|      | 2.4.1.2 Synthesis                           | 33 |

|      | 2.4.1.3 Simulation                          | 34 |

|      | 2.4.1.4 Hardware/Software Codesign          | 36 |

|      | 2.4.2 Schematic Entry                       | 38 |

|      | 2.4.3 Hardware Description Languages        | 38 |

|      | 2.4.4 Custom Hardware Description Languages | 40 |

|      | 2.4.5 Automated Extraction and Synthesis    | 41 |

|      | 2.4.5.1 Overview                            | 41 |

|      | 2.4.5.2 Manual Partitioning                 | 42 |

|      | 2.4.5.3 Automated Partitioning              | 47 |

|      | 2.4.5.4 Writable Microcode                  | 54 |

|      | 2.5 Summary                                 | 55 |

| III. | Framework for a Reconfigurable Compiler     | 57 |

|      | 3.1 Introduction                            | 57 |

|      | 3.2 Overview of the Development System      | 58 |

|      | 3.2.1 Choice of Input Language              | 58 |

|      | 3.2.2 Hardware Model                        | 58 |

|      | 3.2.3 An Example                            | 59 |

v

| 3.2.4 Stages in the Development System         |  |

|------------------------------------------------|--|

| 3.3 Partitioning                               |  |

| 3.3.1 Overview                                 |  |

| 3.3.2 Computation of Runtime and Hardware Cost |  |

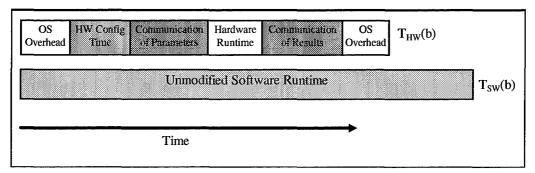

| 3.3.2.1 Execution Model                        |  |

| 3.3.2.2 Runtime Derivation                     |  |

| 3.3.2.3 Hardware Cost Derivation76             |  |

| 3.3.3 Other Factors Affecting Partitioning77   |  |

| 3.3.3.1 Hardware Feasibility77                 |  |

| 3.3.3.2 Interdependence of Estimates           |  |

| 3.3.3.3 Runtime Reconfiguration                |  |

| 3.3.4 Partitioning Algorithms                  |  |

| 3.3.4.1 The Partitioning Decision              |  |

| 3.3.4.2 Search Space Reduction                 |  |

| 3.3.4.3 Search Algorithms                      |  |

| 3.4 Block Selection                            |  |

| 3.4.1 Block Growth                             |  |

| 3.4.1.1 The Ideal Case                         |  |

| 3.4.1.2 A Compromise Solution                  |  |

| 3.4.2 Hardware Feasibility 101                 |  |

| 3.5 Estimation 105                             |  |

| 3.5.1 Software Runtime105                      |  |

| 3.5.2 Hardware Runtime 107                     |  |

| 3.5.2.1 FPGA Timing Estimation108              |  |

| 3.5.2.2 Hardware Requirements Estimation112    |  |

| 3.5.2.3 Operation and Loop Level Parallelism | 118 |

|----------------------------------------------|-----|

| 3.5.3 Hardware Cost                          |     |

| 3.5.4 Communication Time                     | 126 |

| 3.5.5 Configuration Time                     | 132 |

| 3.5.5.1 Total Configuration                  |     |

| 3.5.5.2 Partial Configuration                | 139 |

| 3.6 Synthesis                                | 142 |

| 3.6.1 Software Code Generation               | 142 |

| 3.6.2 Hardware Generation                    | 144 |

| 3.6.2.1 Overview                             | 144 |

| 3.6.2.2 Hardware Optimization                | 145 |

| 3.7 Back Annotation                          | 147 |

| 3.7.1 Estimate Verification                  | 147 |

| 3.7.2 Incremental Routing                    | 151 |

| 3.8 Conclusion                               | 152 |

| IV. Implementation Results                   | 153 |

| 4.1 Introduction                             |     |

| 4.2 The IMPACT C Compiler                    | 154 |

| 4.3 Implementation Overview                  |     |

| 4.4 Estimation                               |     |

| 4.4.1 Software Runtime                       |     |

| 4.4.2 Hardware Feasibility                   |     |

| 4.4.3 Hardware Cost                          |     |

| 4.4.4 Hardware Runtime                       |     |

| 4.4.5 Hardware Communication Time            |     |

| 4.4.6 Hardware Configuration Time                                                                      | 170               |

|--------------------------------------------------------------------------------------------------------|-------------------|

| 4.5 Extraction and Synthesis                                                                           |                   |

| 4.6 An Additional Example                                                                              |                   |

| 4.7 Lessons Learned                                                                                    |                   |

| 4.7.1 Choice of Compilation Stage                                                                      |                   |

| 4.7.2 Dataflow Analysis                                                                                |                   |

|                                                                                                        |                   |

| V. Conclusions and Recommendations                                                                     | 185               |

| <ul><li>V. Conclusions and Recommendations</li><li>5.1 Research Goals and Contributions</li></ul>      |                   |

|                                                                                                        |                   |

| 5.1 Research Goals and Contributions                                                                   |                   |

| <ul><li>5.1 Research Goals and Contributions</li><li>5.2 Recommendations for Future Research</li></ul> | 185<br>187<br>189 |

.

# List of Figures

| Figure 1: Typical FPGA Structure [52]                                                                           |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 2: The Static Logic Model 19                                                                             |

| Figure 3: Coprocessor Model                                                                                     |

| Figure 4: CHAMP I Architecture                                                                                  |

| Figure 5: Typical Reconfigurable Processor Pipeline Architecture                                                |

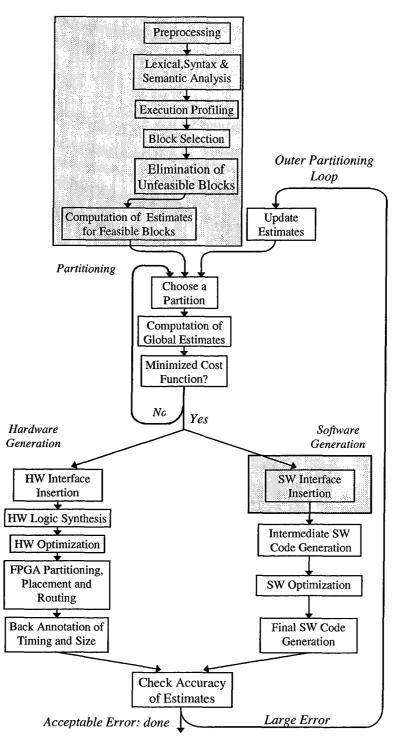

| Figure 6: COSYMA Design Process                                                                                 |

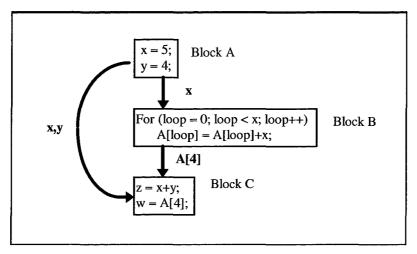

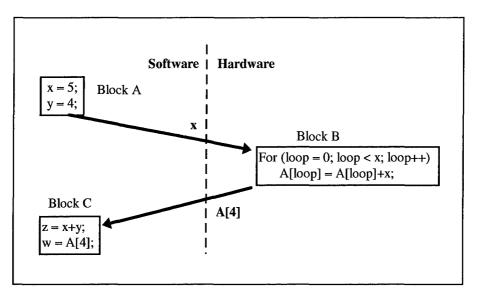

| Figure 7: C Source for a Simple Bit Reversal Program60                                                          |

| Figure 8: Optimized Assembly Code for Bit Reversal Loop                                                         |

| Figure 9: C Source for a Simple Bit Reversal Program After Partitioning                                         |

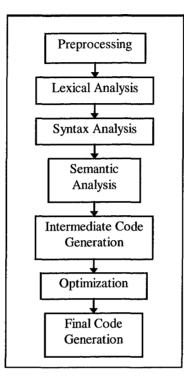

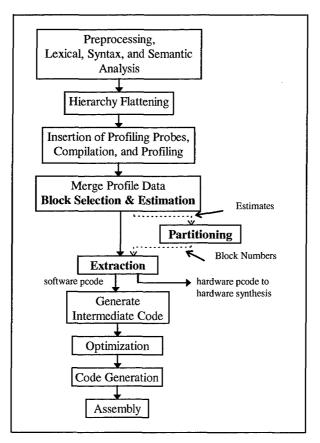

| Figure 10: Stages of a Typical Compiler                                                                         |

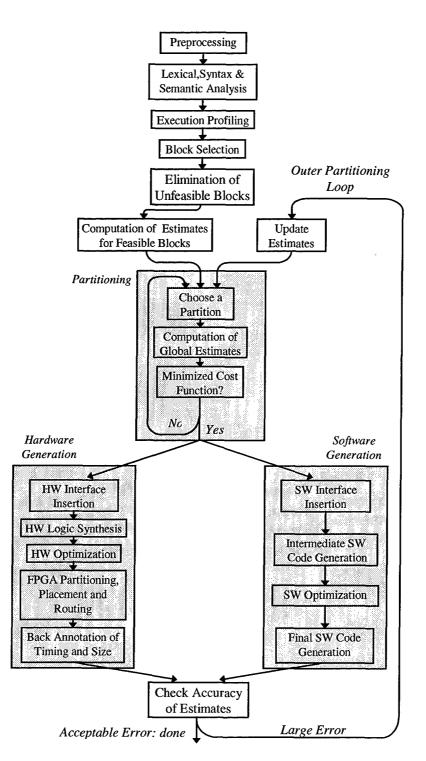

| Figure 11: Stages of a Reconfigurable Compiler                                                                  |

| Figure 12: Source Code for a Software Function Identified for Hardware Implementation73                         |

| Figure 13: Comparison of $t_{SW}$ and $t_{HW}$ for a block b                                                    |

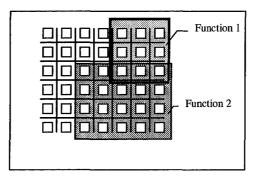

| Figure 14: Two Overlapping Hardware Functions                                                                   |

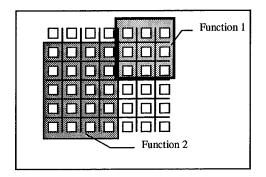

| Figure 15: Non Overlapping Placement of the Two Hardware Functions                                              |

| Figure 16: Code Fragment Showing How Intervening Code Can Result in Inefficient<br>Grouping of Code into Blocks |

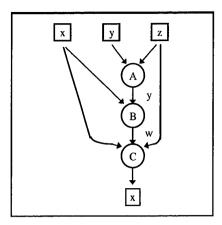

| Figure 17: Example Sequence of Statements, Showing Data Dependencies Between<br>Statements                      |

| Figure 18: Pointer versus Array Indexing Memory Access 103                                                      |

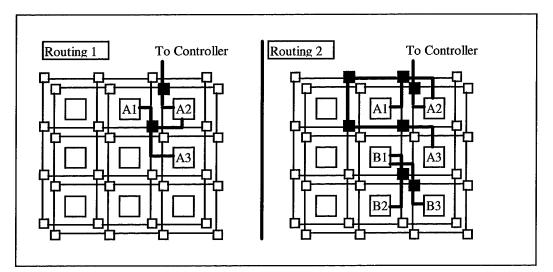

| Figure 19:Two Possible Routing Paths Connecting Logic Blocks A and B 110                                        |

| Figure 20: Source Code for Hardware Runtime Example112                                                          |

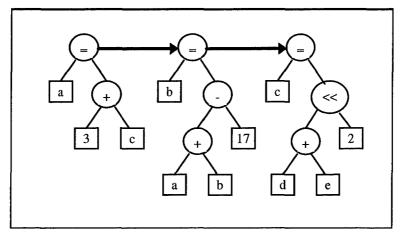

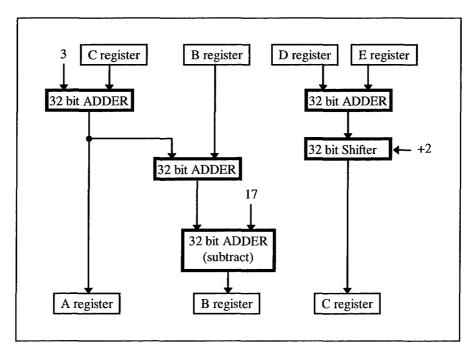

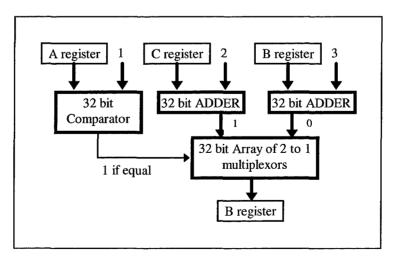

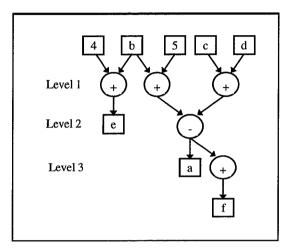

| Figure 21: Parse Tree Representation of the Code Block 113                                                      |

|                                                                                                                 |

| Figure 23: Example Conditional Statement                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 24: Hardware Implementation of the Conditional Statement                                                                                        |

| Figure 25: Structure of a For Loop                                                                                                                     |

| Figure 26: Hardware Implementation of the Bit Reversal Loop (Unoptimized)                                                                              |

| Figure 27: Code Fragment With Opportunities for Parallel Operation Scheduling 119                                                                      |

| Figure 28: Operations of the Code Block When Parallel Scheduling is Used 120                                                                           |

| Figure 29: Code for Live In and Live Out Set Example                                                                                                   |

| Figure 30: Dependence of t <sub>comm</sub> on Adjoining code Blocks                                                                                    |

| Figure 31: One Possible Partitioning of the Blocks, Showing Communication<br>Requirements                                                              |

| Figure 32: A Second Partition of the Code, Reducing the Communication Requirements130                                                                  |

| Figure 33: Inefficient Grouping of Functions into Bitfiles, Resulting in Unnecessary<br>Reconfiguration                                                |

| Figure 34: Reduced Reconfiguration Needed Due to Redundant Bitfiles                                                                                    |

| Figure 35: Serial Connection of Configuration Registers in an Atmel FPGA 139                                                                           |

| Figure 36: Typical Bitfile for a Partially Configurable FPGA                                                                                           |

| Figure 37: Changes to Timing of Function A Due to Routing of Function B 150                                                                            |

| Figure 38: Implemented Tasks of the Reconfigurable Compiler                                                                                            |

| Figure 39: Sequence of Events in the Implementation                                                                                                    |

| Figure 40: Generated C Code for the Partitioned Bit Reversal Program, Showing the<br>Main Software Function and the Interface to the Hardware Function |

| Figure 41: Generated C Code for the Bit Reversal Program, Showing the Extracted<br>Hardware Function                                                   |

| Figure 42: Source Code for the Dilation Filter in the IRMW Application                                                                                 |

| Figure 43: Source Code for the Morphological Filter                                                                                                    |

# List of Tables

| Table 1: Performance and Cost Estimates for Partitioning Example                                                        |

|-------------------------------------------------------------------------------------------------------------------------|

| Table 2: Partitioning Estimates of Total Runtime                                                                        |

| Table 3:Computational Density Estimates for Block Selection Example                                                     |

| Table 4: Typical CLB and IOB Timing Parameters for Xilinx XC4025 FPGA [52] 109                                          |

| Table 5: Equivalent CLB Levels for Operations Used In Example,                                                          |

| Table 6: Configuration Times for Typical FPGAs                                                                          |

| Table 7: Configuration Information for the First Load of Bitfile Containing E                                           |

| Table 8: Configuration Information for the Second Call to Function E                                                    |

| Table 9: Software Runtime Estimates for Bit Reversal Program                                                            |

| Table 10: Hardware Cost Calculation for Bit Reversal Loop       164                                                     |

| Table 11: Hardware Runtime Computation for Bit Reversal Loop       169                                                  |

| Table 12: Execution, Communication, and Configuration Time Estimates for Feasible         Loops in the IRMW Application |

| Table 13: Speedup Calculation for the Candidate Loops in the IRMW Application 180                                       |

-----

#### Abstract

The advent of the Field Programmable Gate Array has allowed the implementation of runtime reconfigurable computer systems. These systems are capable of configuring their hardware to provide custom hardware support for software applications. Since these architectures can be reconfigured during operation, they are able to provide hardware support for a variety of applications, without removal from the system. The Air Force is currently investigating reconfigurable architectures for avionics and signal processing applications.

This thesis investigates the problem of automating the application development process for reconfigurable architectures. The lack of automated development support is a major limiting factor in the use of these systems. This thesis creates a framework for a reconfigurable compiler, which automatically implements a single high level language specification as a reconfigurable hardware/software application. The major tasks in the process are examined, and possible methods for implementation are investigated. A prototype reconfigurable compiler has been developed to demonstrate the feasibility of important concepts, and to uncover additional areas of difficulty.

xii

# A FRAMEWORK FOR AN AUTOMATED COMPILATION SYSTEM FOR RECONFIGURABLE ARCHITECTURES

#### I. Introduction

#### 1.1 Background

Historically, several approaches have been available to designers of electronic applications. The primary differences between these approaches are specialization and flexibility. By specializing the design, very good performance for a particular application can be achieved. Unfortunately, a more specialized circuit is much more difficult to adapt to perform other applications. Designers often must make a decision between performance and flexibility.

Approaches to circuit design range across a wide spectrum. At one extreme, Application Specific Integrated Circuits (ASICs) are designed to implement a single application with the best performance possible. These circuits usually cannot be used for other tasks. At the other extreme, general purpose processors (GPPs) are designed to implement a range of applications by providing a flexible instruction set. Complicated functions can be constructed from these instructions. Unfortunately, the instruction set is by necessity very broad, and many functions which have very simple hardware implementations cannot be included. For example, the bit-reversal operation, in which the order of the bits in a register is reversed, is very useful in many digital signal processing (DSP) applications. This operation is not implemented in most general purpose processors, and must be implemented with some sequence of other instructions.

The result is a much slower implementation of the bit-reversal operation than could be achieved by custom hardware. As a result, the performance of a GPP is typically much less than that of an ASIC with custom hardware support for any particular application.

A third method, the Application Specific Instruction Processor (ASIP), is an attempt to provide a compromise between the performance of an ASIC and the flexibility of a general purpose architecture. ASIPs add specialized instructions to a GPP to improve its performance for a specific type of application. For example, Digital Signal Processors (DSPs) provide most of the flexibility of a GPP, while providing additional hardware support for common DSP operations, such as the multiply-accumulate and bitreversal instructions.

In the last several years, a fourth alternative has drawn increasing attention from researchers. Reconfigurable computer architectures provide a means of achieving performance close to that of ASICs on certain applications, while maintaining the flexibility of more general purpose hardware. Sometimes called Custom Computing Machines, reconfigurable architectures can be configured to provide custom hardware support for one application, and then reconfigured to support additional applications. The Air Force is currently investigating this technology as a means of providing high performance signal processing hardware to combat aircraft. Current approaches utilize expensive ASICs which must be replaced whenever the DSP algorithms are upgraded. Reconfigurable architectures can be reprogrammed to implement these new algorithms with only a software upgrade, without removal from the aircraft or the purchase of new

hardware. This results in a tremendous savings in both hardware cost and in aircraft down-time, since the upgrade does not require the aircraft to be removed from service.

Reconfigurable computer architectures are based upon programmable logic devices (PLDs). These circuits can be programmed by the user to implement both combinational and sequential logic. PLDs can be used to implement the same digital logic as an ASIC, and they can be modified after fabrication. Several families of programmable devices exist. Some of these devices are programmable only once (such as fuse-based PROMs), while others can be modified many times. Until the development of SRAM-based Field Programmable Gate Array (FPGA) technology in the mid 1980s, all of these devices required the removal of the chip from the system during programming. FPGAs can be reprogrammed in-system, without the use of ultra-violet light or higherthan-normal voltages. These devices form the basis for a growing class of systems which can modify their hardware to suit changing applications.

Reconfigurable devices allow for hardware implementation of functions which would otherwise be done in software using a general purpose processor. If the application is subsequently changed, the devices can be reconfigured to meet the needs of the new application. One model for such a system is a reconfigurable coprocessor attached to a general purpose processor. Examples of these systems include Wright Laboratory's CHAMP (Configurable Hardware Algorithm Mappable Processor) system [11] and Brown University's PRISM system [14]. Research with similar systems has

shown speedups ranging from 20 to 1000 times over GPP implementations for a variety of applications, from genetic algorithms to digital signal processing [5:17].

Two major limiting factors to reconfigurable systems are device density and development tools. Because of the overhead required to implement logic reconfiguration, FPGAs provide only a fraction of the number of gates an ASIC can provide on a single chip. Currently, the largest FPGAs have a gate capacity in the 50-100K gate range. FPGAs have been increasing in density rapidly, however, and it is predicted that gate densities will approach one million by the turn of the century.

A more significant problem is the lack of software tools to support the development and use of reconfigurable systems. With current tools, hardware description languages (such as VHDL or Verilog) or gate-level schematic entry tools must be used to develop the logic for reconfigurable applications. In the coprocessor model, the code for the GPP must be developed separately and manually interfaced with the reconfigurable system. Applications developers must have detailed knowledge of the hardware and the ability to design digital hardware. For reconfigurable systems to be adopted on a larger scale, automated tools must be developed which enable those without engineering knowledge to use them.

#### 1.2 Problem

The current method of application development for reconfigurable systems typically requires the use of a hardware description language. While these languages describe digital logic quite well, they lack the general purpose functionality of a high level programming language such as C or Ada. In addition, the number of engineers who can use VHDL or Verilog is very small compared to the number of software developers who use high level languages. There are many applications written in high level languages for general purpose computers which could benefit from implementation on reconfigurable systems. Unfortunately, the tasks of identifying which parts of a HLL application can be done better with hardware support and creating the mixed hardware/software specification is not automated, and requires a great deal of time and effort from skilled engineers.

High level language compilers remove the requirement for detailed knowledge of the underlying computer hardware and assembly language in conventional systems. Researchers are now beginning to develop similar compilers for reconfigurable machines. A compiler for a reconfigurable computer would take an application written in a single specification and identify those parts of the program which would benefit most from hardware support. The compiler would create the hardware and software automatically, removing the need for the developer to understand digital logic design or the underlying hardware. Such compilers would greatly reduce development time and costs for reconfigurable applications.

Unfortunately, the problem of compiling high level language code to execute on a reconfigurable system is more complicated than for a conventional system. Conventional processors have fixed instruction sets. Compilers for these systems must fabricate the

more complex operations required in an application from these building blocks. Reconfigurable systems, however, can be modified to implement portions of the application in hardware, leaving the rest as conventional code for a GPP. The goal is to move those portions of code which can be done faster in hardware away from the GPP. Unfortunately, identifying those portions can be very difficult. Since HLLs provide constructs and operations based upon general purpose architectures, they do not provide concise ways of describing operations which do not exist on typical GPPs. Many operations which have direct hardware implementations must be described by long sequences of simple instructions. Recognizing that a sequence of instructions can be replaced by a single hardware structure is difficult.

Once those operations which can be implemented in hardware have been identified, the compiler must select the most suitable candidates. This process depends heavily on the characteristics of the target hardware. Since FPGAs are limited in the amount of logic that can be implemented, only a fraction of these candidates can be mapped to hardware at any given time. In addition to the raw computation time, overhead due to communication, memory accesses, and configuration time can sometimes result in a hardware execution time that is longer than the original software version. Only those blocks which will execute faster in hardware should be moved. Proper estimation of these factors is critical to the correct partitioning of an application.

The problem of concurrently designing combined hardware/software applications is often referred to as Hardware/Software Codesign. The hardware and software

specifications are developed simultaneously, carefully considering the tradeoffs associated with implementing different portions of the application in hardware or software. The primary focus of codesign research has been for embedded control applications, augmenting microcontrollers with custom hardware to meet real-time operating constraints that could not be satisfied with a software-only system. The hardware portion is typically implemented with ASICs, although FPGAs are coming into increasing use. However, the FPGAs are programmed only once, and are not modified during operation. Most of these methods use HDLs or other specialized languages (e.g. object-oriented specification languages, UNITY, etc.) to allow the developer to manually describe the partitioning between hardware and software. A great deal of effort is still needed to create a combined hardware/software application.

Some research has been done to develop techniques to automate the partitioning of a single specification between hardware and software. However, the focus of this research has been on static logic (whether it is implemented with ASICs or FPGAs) and does not consider benefits and limitations unique to dynamically reconfigurable hardware. For example, with static systems, configuration time is not a factor in the partitioning estimation process. In addition, hardware cost estimation changes significantly when dynamically reconfigurable systems are used. Reconfigurable systems usually have tighter limits on the amount of logic that can be implemented at any instant, but system can be reprogrammed any number of times during the application (effectively providing infinite hardware). It is also more difficult to predict whether a design with a certain gate count can be placed onto a FPGA, due to the difficulties in routing on

FPGAs. This difference in focus between conventional hardware/software codesign and reconfigurable codesign can be quite significant.

This thesis proposes a framework for an automated application development system for reconfigurable architectures. This system, called a reconfigurable compiler, uses a single high level language specification to create a mixed software/hardware application that takes full advantage of the runtime reconfiguration capabilities of the target architecture. The major tasks of the reconfigurable compiler are identified and examined. The key factors used in deciding which portions of the code to implement with hardware are discussed, and methods for their estimation are proposed.

#### 1.3 Assumptions

The primary goal of this thesis is to investigate the problem of creating a compiler for reconfigurable computer systems. Since there are many different architectures under investigation, the results should be independent of the hardware model as much as possible. A general loosely-coupled coprocessor model is used as the basis for later assumptions, however, since this architecture is the most similar to modern computers. Coprocessor systems provide the most obvious target for mixed hardware/software applications, and would benefit most from compiler support. Since estimates must be made for communication times, gate capacities, and other characteristics of reconfigurable systems, some attempt has been made to specify typical characteristics of current systems.

#### 1.4 Objectives

There are two primary objectives for this research. The first objective is to identify the unique problems which must be overcome to create a compiler for reconfigurable computers. The major tasks facing a reconfigurable compiler are detailed, and methods for accomplishing each of these tasks are suggested. The second objective looks in greater detail at two of these tasks, the identification and selection of hardware mappable portions of conventional C code. Some blocks of code cannot be implemented in hardware for a variety of reasons, while others would simply be unprofitable, due to the amount of hardware required, the communication time, or other factor. Methods for estimating the important characteristics necessary for the proper partitioning of code between hardware and software are suggested.

#### 1.5 Approach/Methodology

To provide a basis for this work, a literature search was conducted in the areas of reconfigurable computer architectures, compilers, hardware synthesis, FPGA technology forecasts, hardware/software codesign, and VHDL. An analysis of current reconfigurable systems was performed to select an architectural model to upon which to base later design decisions. Predictions of gate density and speed increases in FPGAs are used to predict hardware limitations.

Methods of hardware synthesis were examined to determine how hardware mappable portions of C code could be identified. While there has been a significant amount of work in the area of behavioral VHDL synthesis, some adaptation is necessary to use these methods for C. The area of hardware/software codesign was examined to determine how applications are partitioned for embedded system design, and how that knowledge could be applied to reconfigurable systems. Most of the criteria used in the partitioning of codesign applications have counterparts in the reconfigurable area, but additional criteria must be introduced to reflect several unique differences. Methods for estimating all of these criteria are suggested.

To demonstrate the concepts introduced in this work and to gain problem insights which only become apparent when one actually attempts to implement a solution, an optimizing C compiler was modified to implement the estimation and extraction stages of the reconfigurable compiler. The implementation examines the source code for feasible code blocks, makes the required performance and cost estimates for each block, and outputs the estimates for use by a partitioning program. After the partitioner selects which block should be extracted for hardware implementation, the reconfigurable compiler removes the marked code blocks, inserts interface code, and outputs the software and hardware specifications as standard C code. The software portion is compiled normally, while the hardware code can be used to create a behavioral HDL description which would ultimately be synthesized. The software system was evaluated using specially created code and the code from an Infrared Missile Warning System developed for the CHAMP board at Wright Laboratory.

#### II. Background

#### 2.1 Introduction

This chapter provides an overview of reconfigurable computer architectures and the tools available for application development. Programmable logic devices, the basis for reconfigurable architectures, will be examined, providing an overview of their current capabilities and limitations. The three major architectural models are discussed, and several example systems are introduced. The remainder of the chapter focuses on the application design process for reconfigurable systems. An overview of the design process is given, followed by examinations of the four major approaches to development: schematic entry, conventional hardware description languages, custom hardware description languages, and high level language extraction. The latter method, high level language extraction, is the most relevant to this thesis, and past and current work in the area is examined in some detail.

#### 2.2 Programmable Logic Devices

#### 2.2.1 Overview

The term programmable logic device is used to describe electronic devices which can be configured by the user to implement arbitrary digital logic. Programming can be accomplished either at the foundry or in the field (by the user). The latter family of devices is typically referred to as Field Programmable Logic Devices (FPLDs). These devices can be programmed by the user, with little or no special equipment. Depending on the type of device, an FPLD can be programmed only once or many times. An important type of FPLD is the Field Programmable Gate Array (FPGA). The FPGA provides the basis for current research in reconfigurable computers. Xilinx marketed the first FPGA in 1985 [52:1]. FPGAs are based upon static random access memory (SRAM) look-up tables and programmable interconnect. A typical FPGA provides a large number of configurable logic blocks (CLBs), which are derived from SRAM look-up tables. A 16 entry look-up table containing one output bit can implement any combinational logic function containing up to four inputs. Different manufacturers provide FPGAs with different granularity.

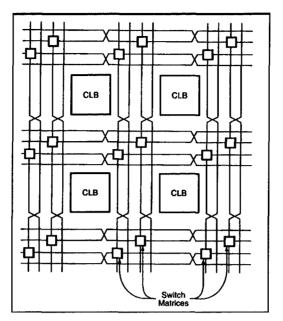

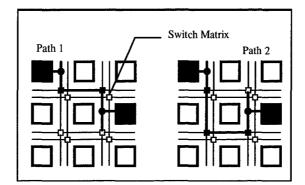

The CLB structure is typically augmented with one or more flip-flops, and sometimes with other common digital structures which would otherwise have to be implemented using a number of CLBs (typically one or more small multiplexors and fast carry generation logic for use in adders, etc.)[52:2-9]. Increasingly, some amount of onchip RAM is provided as well. Typical FPGAs include several hundred to several thousand CLBs arranged in a two-dimensional mesh. A fragmented network of wires fills the space between the CLBs, as shown in Figure 1. Connections between two CLBs can be made by connecting the output of one CLB to one of the wires of the interconnect, through the interconnect, and finally to the input of the second CLB. Most of the lines in the interconnect are very short, so routing between two distant CLBs often requires the connection of several lines. Connections are made by transmission gates, whose switch inputs are determined from SRAM configuration registers.

Figure 1: Typical FPGA Structure [52]

## 2.2.2 FPGA Configuration

The configuration information of an FPGA is called a bitfile. The bitfile contains the configuration information of each of the CLBs and interconnect devices on the FPGA, and is essentially an image of all of the SRAM configuration elements on the chip. Most FPGAs are configured serially, although newer devices allow a limited parallel input (either 8,16, or 32 bits) for faster configuration [20][36]. Configuration of an FPGA can be accomplished in several microseconds to several milliseconds, depending on the size of the FPGA and the fraction of the FPGA being reprogrammed. Some FPGAs can be partially reconfigured, allowing a portion of the FPGA to be configured while the remainder of the FPGA is still functional. Most FPGAs, however, require that the entire FPGA be reconfigured at once. An excellent example is the Xilinx XC4025 FPGA. The XC4025 contains 1,024 CLBs, providing roughly 25,000 gates of usable logic [52:2.26]. Roughly 350 bits of configuration information are required for each CLB and its neighboring interconnect. With error detection bits and other additional overhead, a total of 422,168 bits are required for configuration data. The XC4025 can be configured either serially, or in parallel using an 8 bit bus. The configuration clock speed of the device is roughly 10MHz, so the configuration time of the entire chip is roughly 5.3ms.

#### 2.2.3 FPGA Advantages

FPGAs possess several characteristics which make them useful for reconfigurable computing. The largest advantage is reconfigurability. Since FPGAs do not require special programming voltages or hardware, so they can be reconfigured in the system. This allows hardware reconfiguration under the control of the application itself. Complete configuration of even the largest FPGAs can be accomplished in milliseconds. Since FPGAs are based upon SRAM, they can be reconfigured an unlimited number of times. This results in tremendous flexibility. FPGAs can implement any digital logic circuit, limited only by the size of the device. When applied to reconfigurable computing, application developers can implement arbitrary hardware circuits at runtime and change those circuits as often as desired.

#### 2.2.4 FPGA Limitations

There are several difficulties associated with the use of FPGAs. The SRAM structure which gives FPGAs their unique capabilities creates some special limitations.

The most important limitations of FPGAs are density and speed. A great deal of die area is needed by the interconnect lines, the configuration registers, and the CLBs. This overhead severely reduces the amount of logic an FPGA can implement. While a conventional ASIC can provide well over a million logical gates, the largest FPGAs provide only 100,000 gates. In addition, the long interconnect lines can create large delays, and result in circuits that are slower than ASIC implementations. The fastest FPGA circuits operate at 50MHz or less. These limitations may be critical to developers who must choose between an ASIC implementation and an FPGA implementation of static logic. In the area of reconfigurable computing, however, the performance offered by a FPGA may provide a substantial improvement over a software implementation of an algorithm.

#### 2.2.5 Estimates of Future Capabilities

FPGA designs continue to evolve to better serve reconfigurable system developers. Many of the limitations of current FPGA designs will be reduced in future FPGAs. The most obvious limitations, density and performance, will be reduced as CMOS technology improves. FPGAs will always provide fewer gates and lower performance than ASICs, but as density increases, larger and larger applications will be achievable. Fawcett estimated in 1995 that FPGAs would provide over 100,000 gates (which has already been reached in 1996) and operate at 200MHz by the end of the century [20:160]. The capacity of FPGAs will continue to increase in direct relation to the increases in VLSI device density. Just as important as density increases, however, are architectural changes. One of the current limitations of many FPGAs is configuration time. While the time to configure an entire FPGA is very small (<10ms) for many uses, it is an extremely long period of time to a computer system with a clock period measured in single nanoseconds. Some current FPGA architectures allow partial reconfiguration, while others will provide that capability in the near future. Many FPGAs are moving away from the serial configuration used in the past, allowing 8, 16, or 32 bit parallel input. This is ideal for configuration over a microprocessor bus.

Another suggested FPGA architecture is the Dynamic Programmable Gate Array (DPGA) [17]. The DPGA is based upon a standard FPGA, augmented with additional configuration registers to allow fast switching between two or more configurations. Once the configurations are loaded, switching between configurations requires only a single clock cycle. Internal state can even be saved. This will allow easier task switching and thus multi-tasking of hardware. This architecture would make FPGA hardware more useful to applications in a multi-tasking environment.

Recognizing that many FPGAs are being interfaced with standard computer systems, Xilinx is developing an architecture specially adapted for use in these systems [20:164-165]. Most FPGA designers must create the bus interface hardware manually, utilizing the limited number of CLBs. The XC6200 series devices have dedicated interface circuitry for this task, offering better performance with less die area. The CLB structures have been made less complex and more numerous, providing a more regular

structure that is easier to route. The XC6200 also supports partial reconfiguration, requiring only 3 bytes of information per logic cell. As a result, programming of the chip is much faster than in previous devices, allowing configuration in only 200µs. As proposed by the DPGA architecture, the XC6200 will support multiple configurations and rapid swapping. The state of internal logic will be saved and can be restored very quickly. It is likely that many of these characteristics will be incorporated into future reconfigurable computers.

#### 2.3 Reconfigurable Computer Architectures

A reconfigurable computer is a computer system which can modify the characteristics of its hardware to provide increased performance for a specific application. These systems are typically based upon Field Programmable Gate Arrays (FPGA), which can be configured by the user to implement a variety of digital logic functions. In a conventional system, the hardware configuration remains constant, providing a fixed set of capabilities to the user. Reconfigurable architectures allow a developer to optimize the hardware for a particular application, while maintaining the flexibility to quickly adapt the system to other applications. In effect, reconfigurable architectures allow a developer to achieve some of the performance gains of special purpose hardware, but retain the benefits of a general purpose machine.

There has been a limited amount of research into this field. Until ten years ago, programmable logic devices were too limited in density and performance to allow the creation of useful reconfigurable systems. The older programmable devices, such as the

Programmable Logic Array (PLA) and the Programmable Read-Only Memory (PROM), could provide only a small amount of logic. In addition, these devices could not be modified after programming without removing them from the system. In 1985, Xilinx introduced the Field Programmable Gate Array. While initially limited in speed and density, FPGAs have shown a 35%-per-year improvement in speed, and a better than 55%-per-year improvement in density [52:1]. FPGAs capable of implementing the equivalent of 100,000 gates of logic are currently in production.

A range of reconfigurable systems have been built in recent years, by researchers and commercial developers. Most of these systems fall into three major categories. The primary difference between the categories is the method in which the reconfigurable hardware is used. Other differences include the method in which the reconfigurable hardware communicates with attached general purpose or custom processors, and in the level of reconfigurability. The following sections provide an overview of the three families of reconfigurable architectures, and give several examples of each type.

#### 2.3.1 The Static Logic Model

The first systems developed using reconfigurable logic were based upon the static logic model. In this model, the FPGAs are programmed upon system or application startup and are not reconfigured during operation. The reconfigurable hardware can be viewed as any other fixed hardware device, whose specific functionality is determined before operation begins. As a result, the amount of logic a system can implement is limited to the size of the FPGAs. Typically, only a few thousand gates are implemented

on these systems. Since the FPGAs are not reprogrammed during operation, the overhead incurred by configuration is paid only once and does not slow operation. The reconfigurable hardware can be either standalone or a part of a larger system.

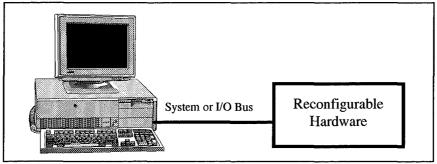

The reconfigurable hardware in a static system is typically less tightly integrated into the overall system than in the other families. When it is connected to a conventional computer system, the reconfigurable hardware is typically not closely linked to the system. Most static logic systems communicate to the host processor via the host's I/O interface or system bus. The reconfigurable hardware is used to perform a single function. Information is sent to the reconfigurable hardware, the function is performed, and the result is copied back. The reconfigurable system may or may not be allowed to access system memory for this purpose. Figure 2 shows a typical configuration for the static logic model.

Figure 2: The Static Logic Model

An example of a static logic system is the PeRLe system, developed by DEC Paris [10]. The PeRLe system was based upon a 5x5 array of Xilinx 3090 FPGAs, providing roughly 150,000 gates to the user. Applications developed for the system include RSA cryptography, LaPlace transforms, long multiplication, and a stereoscopic vision system.

In 1990, PeRLe set a speed record for RSA cryptography using 512-bit keys, delivering roughly ten times the performance of a custom VLSI implementation [20:157]. This performance was achieved largely as a result of the ability to easily customize the algorithm on the reconfigurable hardware.

Other examples of static logic systems include the SPLASH processor and the ACE-12 system. SPLASH was developed at the Supercomputing Research Center [22]. SPLASH-1 was constructed of 32 FPGAs linked in a linear array, connected via a VME bus to a Sun workstation. SPLASH was designed to implement systolic algorithms for one-dimensional pattern matching in DNA research. It outperformed a Cray-2 by a factor of 325, and a custom built ASIC device by a factor of 45 [20:158]. An example of a commercial system is the ACE-12 system, developed by Metalithic Systems. The ACE-12 contains up to 12 FPGAs, using a SIMD architecture for processing. A swap/sort algorithm implemented on the ACE-12 system executes more than 360 times faster than on an Intel 486/33 processor.

The static logic model is the most similar to current ASIC-based systems, and thus most of the first reconfigurable systems were based upon it. While many static logic machines have been able to show great performance gains over GPP and sometimes ASIC implementations, they fail to take advantage of many of the key features of programmable logic. The primary advantage of these systems over ASIC implementations is a faster development time, and the ability to rapidly "tweak" the algorithm to incorporate changes made as a result of execution profiling.

#### 2.3.2 The Coprocessor Logic Model

#### 2.3.2.1 Description

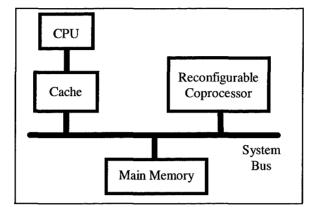

A more flexible model of reconfigurable systems is the coprocessor model. In these systems, the reconfigurable logic supplements a conventional processor. This model is sometimes referred to as the *loosely-coupled model*, since the reconfigurable coprocessor is more closely integrated with the main processor than in static systems (which may not be attached to one at all), but not as closely as in the dynamic instruction set model (discussed in the next section). Portions of an application which can be implemented quickly and efficiently in hardware are partitioned to the FPGAs, while the remaining portions are executed on a general purpose processor. The processor can reconfigure the FPGAs either before execution of an application begins or during execution.

Many examples of this type of architecture exist, including the CHAMP system [11], the PRISM system [5][1], the Transmogrifier system [21], and Virtual Computer Corporation's EVC-1 [16]. These systems are comprised of one or more FPGAs connected to a host processor. They typically provide between 4,000 and 400,000 logic gates to the user. The system is configured either directly by the application or through operating system calls. For those systems which allow the application to reconfigure the FPGAs during execution, reconfiguration time becomes very important to the overall speed of the application. As discussed in Section 2.2.2, configuration time is typically on

the order of several milliseconds, a very long time for modern CPUs running with clock periods of less than 10 ns. Figure 3 shows a typical coprocessor architecture.

Figure 3: Coprocessor Model

Communication between the processor and the reconfigurable coprocessor is done over the system bus, and is therefore limited by bus speed. The bus can also adversely affect reconfiguration time, in the cases where the bus cannot provide the configuration bits to the FPGAs as fast the device can accept them. In this case, bus speed becomes a limiting factor. Bus speed becomes very important during execution, as it determines how fast the processor and the reconfigurable system can communicate. The bus width limits the amount of data that can be transferred between the two devices in parallel.

# 2.3.2.2 The CHAMP I System

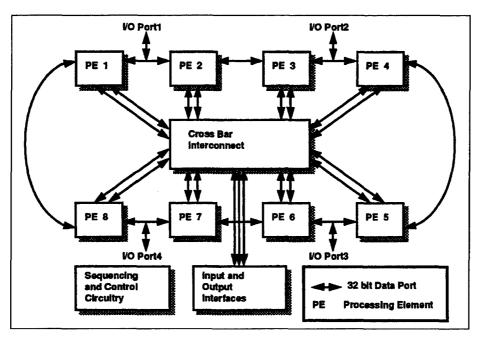

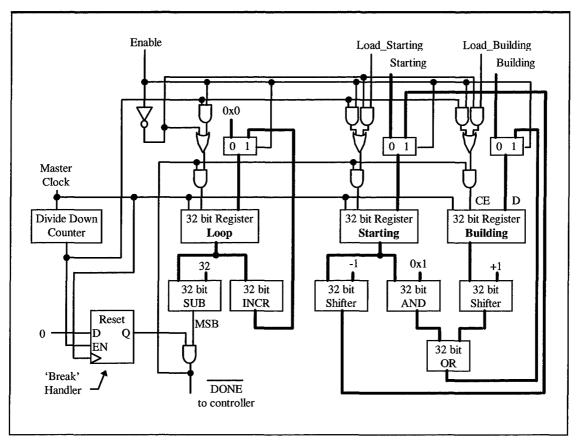

An example of a loosely-couple coprocessor system is the Configurable Hardware Array Mappable Processor (CHAMP I), developed by Lockheed Sanders for the Air Force's Wright Laboratory [11]. Wright Laboratory has been working to determine whether reconfigurable architectures can provide performance near the level of ASIC hardware, while maintaining the flexibility of software-based approaches. As an example application, they chose to implement an Infrared Missile Warning System (IRMW). The CHAMP system was developed to investigate the advantages of such a system. Based upon a coprocessor model, the reconfigurable logic is connected to a conventional workstation by the VME Bus. The CHAMP I system is constructed from 8 Processing Elements (PEs), each of which contains 2 Xilinx XC4013 FPGAs. The PEs are connected in a ring and supplemented by a crossbar connection network. In addition, a 16K by 32 bit dual port RAM is provided on board. All told, the system can implement roughly 350,000 gates of digital logic [11:8]. The CHAMP I system architecture is shown in the following figure.

Figure 4: CHAMP I Architecture

The IRMW algorithm was originally implemented in the C programming language. Engineers at Wright Laboratory manually identified and removed those portions of the code which could be effectively implemented on the CHAMP board, From this partition, they created a hardware schematic and software code for the host processor. The process of placing the application on the hardware required several months. The hardware implementation proved to be faster than the original implementation, in the range of 4 to 25 times faster, depending on the portion of the algorithm examined. [11:15].

Communication speed proved to be a problem with the CHAMP system, as all communication takes place over a very slow VME bus [11]. Information had to be transferred in serial (one byte per bus cycle), and could not provide the high speed communication necessary to do real-time processing of data in applications in which the host system provides the data. CHAMP was capable of real-time operation when the data was provided by a custom hardware interface to an external camera. Other limitations of the system shortage of on-board RAM (since CHAMP could not access the workstation's main memory) and a limited number of CLBs [12:43].

# 2.3.3 The Dynamic Instruction Set Model

The final model of a reconfigurable system incorporates reconfigurable logic into the processor itself. The processor is either wholly or partially reconfigurable. This model is often referred to as the tightly-coupled model, since the reconfigurable hardware is closely integrated into the processor itself. This is the most complex of the three families of reconfigurable architecture, and was the last to be investigated. Most of the

examples of this type of architecture exist only as proposals or FPGA prototypes. No full-fledged systems exist.

Dynamic instruction set systems get their name from the fact that the instruction set is not fixed, and can be modified to provide custom instructions to the application. Whereas the coprocessor model can be seen as providing custom functions to an application that can be called by the software application, the dynamic instruction set computer can provide custom *instructions*. A certain number of the system's assembly language opcodes are assigned as dynamic instructions, whose exact functionality depends on the configuration of the FPGAs. The intent of dynamic instruction set computers is to eliminate the costly communications overhead incurred by coprocessor systems by pulling the reconfigurable logic into the processor itself.

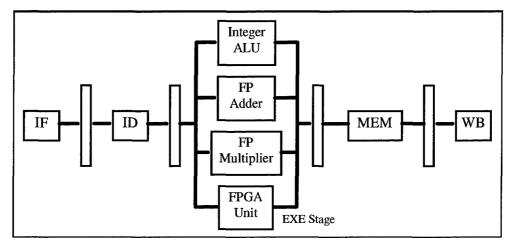

Two subclasses of dynamic instruction set computer have been proposed. In the first, a conventional fixed processor is augmented with one or more FPGA execution units. For example, in addition to hardware fixed-point and floating-point adders, multipliers, and dividers, several FPGA units would be included in the execution stage of a pipelined processor. An FPGA block could be configured to perform the bit-reversal operation (which is very common in many DSP applications) in a single cycle. It could then be reconfigured at a later time to perform a different function. The other subclass is the completely reconfigurable processor, in which all logic is implemented on the FPGA. In this case, the entire pipeline structure of the processor could be adapted to the application.

The Dynamic Instruction Set Computer (DISC) is a completely reconfigurable processor [49]. DISC is based upon a single National Semiconductor CLAy31 FPGA, coupled to an external memory and a configuration controller FPGA. The CLAy31 is one of the few FPGAs that can be partially reconfigured. The DISC system uses this capability to implement what is called *cache logic*. Cache logic allows functional blocks to be placed onto the FPGA, where they can be used to provide custom instructions for the processor. After use, the blocks remain on the FPGA until the space is needed by other functions. If a functional block is still in this cache when a later instruction needs the same operation, there is no need to program the FPGA. The communications overhead between the conventional functional blocks and the reconfigurable (custom) blocks is very small, since they are all implemented in the same FPGA. The disadvantage to this system is that it requires a great deal of FPGA space, and is very slow. Current FPGAs cannot implement the large amounts of logic required of floating point adders, instruction and data caches, etc., on a single device. The DISC system provided only limited functionality for this reason. Full systems would require several FPGAs. Most importantly, an FPGA requires more die area and operates at a slower frequency than a fixed VLSI implementation of a given execution unit. If a functional unit is frequently used (such as a fixed-point adder), it is much more effective to implement it in fixed hardware.

It is for this reason that the other subclass of dynamic instruction set systems has been proposed. The more commonly used functional units are implemented in fixed logic, while a certain amount of reconfigurable logic is provided for the more uncommon,

application-specific functions. A proposed architecture for such a system is shown in Figure 5.

Figure 5: Typical Reconfigurable Processor Pipeline Architecture

An interesting example of this type of architecture is the OneChip [50]. This system is based upon the widely-known MIPS architecture, augmenting the standard pipeline with two Programmable Function Units (PFUs) in the execute stage. The system is currently implemented in prototype form on the Transmogrifier-1 field programmable system, but a custom VLSI implementation is planned. The specified uses for the system are for application specific hardware accelerators, and for glue logic for use in embedded controller applications. The PFUs are configured upon system (or program) startup, and are not reconfigured during operation. The OneChip has been tested on several applications, and shows promise. For a discrete cosine transform application, the system achieved a speedup of 40 times over the same program running on a MIPS R4400 processor. The major weaknesses of this system are the inability to reconfigure the functional units during execution, and a lack of application development tools.

Three other examples of dynamic instruction set processors are known. Harvard's PRISC system is a fixed-core reconfigurable processor which creates reconfigurable execution unit blocks that can implement combinational logic [41]. Only those functions which can be executed in one clock cycle can be implemented. It has been clearly defined and is implemented in simulation, unlike the DPGA-coupled microprocessor from MIT [17]. This architecture exists as a proposal only, discussing the use of the DPGA-type of programmable logic devices (as discussed in Section 2.2.5). The third example is the NanoProcessor, developed at Brigham Young [48]. This architecture is similar to the PRISC, but it allows functions with latencies of more than one cycle to be implemented. However, the static control module which forms the core of the processor is implemented in the FPGA as well. No mention is made of a custom VLSI implementation of this static logic.

Of the three families of reconfigurable architecture, the dynamic instruction set computer offers the greatest potential, but at the same time the greatest challenges. Since the reconfigurable logic is incorporated into the processor itself, the communication bottleneck which causes problems for the other two families is significantly reduced. The reconfigurable logic can be used to greatest advantage. Unfortunately, this model is the most different from present architectures. The problems involved in creating such a system have never been fully investigated. In addition, non-trivial dynamic instruction set computers require custom VLSI implementations. Static logic and coprocessor systems can be built by adding FPGAs to conventional processors, at a much lower cost. Because of these difficulties, dynamic instruction set systems are only beginning to be

investigated. The exact architecture of such systems are still unclear, as are the many difficulties involved in their implementation in a larger system and their integration with software. Perhaps most important is the complete lack of software development tools. The design of a compiler for a dynamic instruction set system will undoubtedly prove a challenging task.

#### 2.3.4 Summary

While many examples of reconfigurable systems were given in this section, many others were left out. The architectures discussed provide a broad overview of the architectures being investigated and a frame of reference for the remainder of this thesis. While the closely-couple dynamic instruction set model appears to offer the best performance and may be the model most used in the long term, the coprocessor approach is immediately realizable. It offers many of the benefits of the closely-coupled model, although it has a higher communication cost. The coprocessor model has the advantage, however, of being very similar to many embedded controller architectures, and as such can benefit from hardware/software codesign research.

### 2.4 Tools for Application Development

Perhaps the biggest difficulty to overcome in reconfigurable computing is the lack of integrated development tools. The task of simultaneously developing an application in both hardware and software is very difficult. There are very good compilers, debuggers, and other tools for the development of software-only applications. Likewise, there are tools to synthesize, simulate, and debug digital hardware. Unfortunately, reconfigurable applications consist of both software and hardware components, which must be designed and simulated in a cooperative manner. Software compilers use a fixed hardware model, in which the assembly language (and thus the capabilities of the hardware) are set. But in reconfigurable systems, the hardware capabilities can easily be changed to better suit the application being developed. Software compilers for systems in which the hardware capabilities are not specified are the subject of research.

The two major issues in the design of combined hardware/software systems are *partitioning* and *simulation*. An application can be divided into parts, each of which must be implemented either with software or hardware. The determination of the optimal partitioning (one optimizing speed, cost, memory, or other factors) is very difficult, and often requires an iterative process in which many partitions are created and simulated. The simulation of developmental hardware and software at the same time can be quite complicated and time consuming. In most modern designs, the partitioning process is done by hand.

This section describes the most common approaches to the codesign of applications for reconfigurable systems. First, several design issues for reconfigurable applications are introduced. A few of these issues are similar to those in another area of research, hardware/software codesign. The remaining sections focus on four approaches to reconfigurable application development: schematic entry, hardware description languages, custom hardware description languages, and automated extraction and synthesis.

### 2.4.1 Design Process

The design of an application for a reconfigurable system involves the codesign of hardware and software. Any application can be broken into blocks, at the task, functional, basic block, statement, or operational level. The designers decide whether to implement the functionality of each block using either specialized hardware or as software code. From this partitioning, the actual hardware can be designed and the software code generated. At this point, the prototype design can be evaluated to determine whether it meets the design requirements for correctness, throughput, memory size, etc. The design process is thus broken into three distinct phases: partitioning, synthesis, and simulation.

# 2.4.1.1 Partitioning

An important part of the application design process is a requirements specification. Certain applications must satisfy real-time operating constraints. For other applications, minimizing the system cost is the most important factor. Other constraints include software memory requirements, throughput, and hardware area. The choice of partitions will ultimately determine whether a design meets these requirements. The proper choice of partition depends heavily on the specific requirements for the application. A particular partition may be adequate for one set of requirements, and totally inappropriate for others.

Determining the best partition for a particular application is an involved process. Since each block can be implemented in either hardware or software, an application composed of N blocks has 2<sup>N</sup> possible partitions. While a certain block may be implemented better in hardware when viewed in isolation, a software implementation may result in a better overall system. The problem is very similar to the classical knapsack problem (multidimensional optimization). A non-optimal local decision may be needed to find the optimal global solution. As a result, a greedy partitioner will not necessarily find the optimal partition. The partitioning algorithm must search the solution space to find the best solution. This process is made slightly easier with the knowledge that not every type of operation can be implemented efficiently or easily in hardware (such as some recursive functions, etc.) or software (A/D conversion). The sample space can thus be reduced, but there is still a large set of possible solutions that must be tested to find the best one.

To determine the value of a particular partition, estimates are made of the important characteristics of the partition. Estimates are made of software, hardware, and overall run-times, and of hardware cost, memory size, etc. Partitions which do not meet the specified requirements are discarded. Ultimately, a partition is found which meets the requirements. A non-optimal partition that meets the requirements is often chosen to shorten search time. This is an important point to consider since most of this estimation and partitioning is currently done by hand. Research into automating the partitioning process for embedded and reconfigurable systems is discussed in more detail in Section 2.4.5.

### 2.4.1.2 Synthesis

Once a partitioning of the algorithm has been achieved, the design must be created. The synthesis phase involves the actual design of the hardware and software. From the specifications developed in the partitioning phase, hardware can be designed. In the same manner, the software code can be written. In the conventional design process, the two design teams can proceed independently of each other. The hardware designers know what capabilities the hardware must provide, while the software developers know what the hardware platform looks like and what is left to implement in software.

There are many choices of design tools for both hardware and software. Hardware developers can use schematic entry tools such as Synopsys, Cadence, Mentor, etc. (See Section 2.4.2) They may also choose to synthesize the design from a hardware description language such as VHDL or Verilog (See Section 2.4.3) It is also possible to develop the hardware from a custom hardware description language more closely resembling conventional high level languages (See Section 2.4.4). The problem is more difficult for software developers. Current compilers create code for processors with fixed capabilities. Since they attempt to optimize code for a fixed architecture, these compilers are ill-suited to take advantage of a system which can modify itself to better suit the software. For this reason, software development usually proceeds after the hardware architecture is completely specified, often resulting in a poor partitioning of the algorithm.

# 2.4.1.3 Simulation

Once the design is created, it must be tested to verify that it meets specified requirements. There are two alternatives for the testing of a design: prototyping and cosimulation. For small designs, it may be possible to construct actual prototypes to test the application. For larger designs, however, cost is prohibitive, and computer simulation of the hardware and software is used. This is particularly important when multiple iterations of the design process will be used to find an optimal design. The estimates of performance made in the partitioning stage can be verified or refined by simulation. If the design is unsatisfactory, the simulation information can be used to re-partition the algorithm and produce a partitioning with better performance.

Tools exist to simulate both digital and analog hardware. Digital logic simulators typically simulate VHDL or Verilog designs. Analog simulators include packages such as SPICE. While these simulators typically do a good job in simulating the functional and timing characteristics of the hardware, they run very slowly. Hardware simulators run at a small fraction of the speed of the real system. This has a serious impact on the simulation of the software system.

The major challenge of simulation of reconfigurable applications is the simulation of the combined system. This simulation involves testing software on a hardware platform that exists only as a simulation. Since hardware simulation is slow even for small test programs, simulation of a non-trivial software program can be extremely time consuming. In many reconfigurable systems, most of the software runs on a conventional

processor, and can be easily simulated at high speeds. The interfaces to the hardware can be replaced with stubs which simulate the operation of the hardware components. This provides a method of simulating part of the software, but the interface between hardware and software remains untested.

An example of a cosimulator was developed at Carnegie-Mellon [44]. The cosimulator was part of a larger codesign system, targeted toward a system architecture in which a general purpose processor is augmented by application specific hardware. A Verilog logic simulator is used to simulate the behavioral description of the hardware partition. The software portion of the system is compiled and executed on the actual processor. The major difficulty in simulation is simulating the interface between them. Carnegie-Mellon's system allows the Verilog simulator and the HLL program to communicate directly, through UNIX sockets. The intent is to allow the Verilog simulation to act as a drop-in replacement for the actual hardware. While compromises had to be made, it illustrated what would be required of a cosimulator for codesign (and also reconfigurable) systems.

The goal for cosimulation is an environment which can simulate both the software and hardware components of a system together, with a minimum of modification to the code. In addition, designers would like this simulation to execute as quickly as possible, both to speed the verification of a model, and to acquire partition profiling information for use in later partitioning steps. There are good software tools to simulate both software and hardware independently. Researchers in this area do not seek to create new tools so much as to create better interfaces between them.

# 2.4.1.4 Hardware/Software Codesign

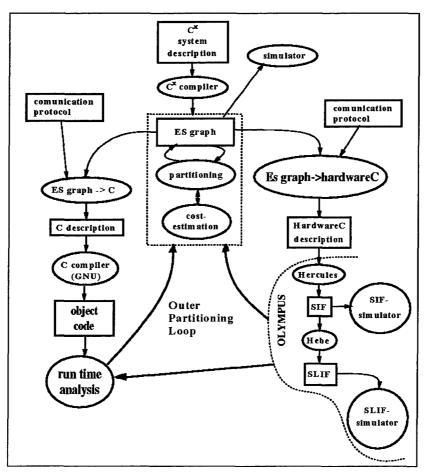

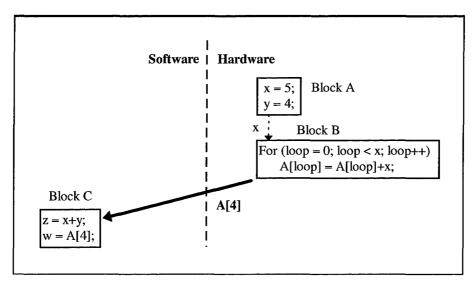

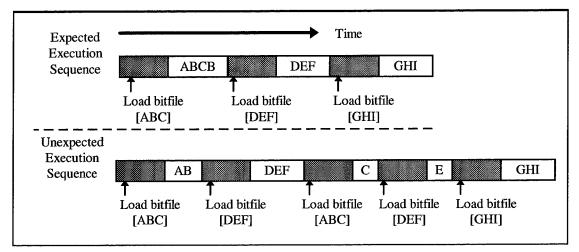

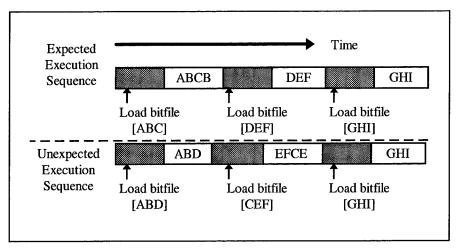

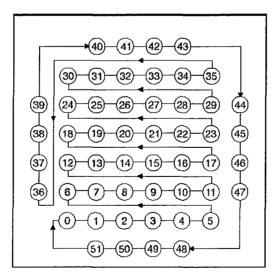

Hardware/software codesign is a design philosophy espousing communication and cooperation throughout the design process. It finds its roots in the development of embedded systems, although many of its techniques can be applied to other areas, including reconfigurable systems. Codesign aims to overcome some of the disadvantages of the conventional approach to system design through better communication between the software and hardware development paths. In this manner, any problems can be found and overcome much earlier in the process, at a substantial savings in time and cost.