#### Air Force Institute of Technology

#### **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

12-1996

### **Evaluation of Design Tools for Rapid Prototyping of Parallel Signal Processing Algorithms**

James C. Savage

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Signal Processing Commons

#### **Recommended Citation**

Savage, James C., "Evaluation of Design Tools for Rapid Prototyping of Parallel Signal Processing Algorithms" (1996). Theses and Dissertations. 5931.

https://scholar.afit.edu/etd/5931

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

EVALUATION OF DESIGN TOOLS FOR

RAPID PROTOTYPING OF

PARALLEL SIGNAL PROCESSING ALGORITHMS

**THESIS**

James C. Savage, Captain, USAF AFIT/GE/ENG/96D-18

Approved for public releases

Distribution Unlimited

AIR UNIVERSITY

AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

TYPE OTTAL THE THEPROPED 1

# EVALUATION OF DESIGN TOOLS FOR RAPID PROTOTYPING OF PARALLEL SIGNAL PROCESSING ALGORITHMS

#### **THESIS**

James C. Savage, Captain, USAF

AFIT/GE/ENG/96D-18

Approved for public release; distribution unlimited

## EVALUATION OF DESIGN TOOLS FOR RAPID PROTOTYPING OF PARALLEL SIGNAL PROCESSING ALGORITHMS

#### **THESIS**

Presented to the Faculty of the Graduate School of Engineering

of the Air Force Institute of Technology

Air University

In Partial Fulfillment of the

Requirements for the Degree of

Master of Science in Electrical Engineering

James C. Savage, B.S.E.E.

Captain, USAF

December 1996

Approved for public release; distribution unlimited

#### **Acknowledgments**

I would like to thank those who have helped me in this research. I thank my thesis advisor, Dr. Gary Lamont, for his effort to find an area of research which not only aligned with my experience, but also provided me the opportunity to investigate other areas previously unfamiliar to me. Dr. Lamont provided the right amount of suggestion, encouragement, and freedom for me to make the most out of the research experience. I thank my sponsor, Dr. Robert Ewing, for his insight into current Wright Laboratory signal processing needs and the accompanying motivation. I also would like to thank the members of my thesis committee. My topic has taken many twists and turns over the past year, and while I may have lost some along the way, each was helpful at different stages of the journey. The weary travelers of my thesis committee are Dr. Andrew Terzuoli, Lt. Col. Tom Wailes, Dr. Ken Stevens, Dr. Bruce Suter, and Lt. Col. David Gallagher. Thanks also go to Greg Richardson for his last minute software installation efforts.

Many thanks go to the other VLSI lab rats. With the help and camaraderie of Captain Javier Marti, Captain Jeff Butler, Captain George Dalton, and Lieutenant George Rohlke, the VLSI sequence and the endless hours spent staring at a computer screen in the laboratory were almost bearable.

Finally, I must thank my roommates, Lieutenant Ron Schwing and Captain

Dwight Smith, for leaving me alone when I needed to get some work done.

## **Table of Contents**

| ACKNOWLEDGMENTS                                                                          | iii  |

|------------------------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                                          | vi   |

| LIST OF TABLES                                                                           | vii  |

| ABSTRACT                                                                                 | viii |

| I. INTRODUCTION                                                                          | 1    |

| BACKGROUND                                                                               | 2    |

| PROBLEM STATEMENT                                                                        | 5    |

| RATIONALE                                                                                | 6    |

| SCOPE                                                                                    | 7    |

| STANDARDS                                                                                | 7    |

| METHODOLOGY                                                                              | 7    |

| Literature Review                                                                        |      |

| Algorithm Selection and Design                                                           |      |

| Design Implementation                                                                    |      |

| MATERIALS AND EQUIPMENT                                                                  |      |

| Summary                                                                                  |      |

| II. LITERATURE REVIEW                                                                    | 11   |

| HIGH-SPEED AVIONICS SIGNAL PROCESSING                                                    | 11   |

| DIGITAL SIGNAL PROCESSING                                                                |      |

| PARALLEL/DISTRIBUTED DSP DESIGNS                                                         |      |

| Georgia Institute of Technology Digital Signal Multiprocessors                           |      |

| DSP Multiprocessor Architectures                                                         | 22   |

| RAPID PROTOTYPING AND DSP DEVELOPMENT TOOLS                                              |      |

| SOFTWARE EVALUATION FACTORS                                                              |      |

| SUMMARY                                                                                  |      |

| III. ALGORITHM SELECTION AND DESIGN                                                      |      |

| ALGORITHM SELECTION                                                                      | 22   |

| INTRODUCTION TO THE FAST FOURIER TRANSFORM                                               |      |

| Fourier Transform                                                                        |      |

| Discrete Fourier Transform                                                               |      |

| Fast Fourier TransformFast Fourier Transform                                             |      |

| Hast Fourier Transform                                                                   |      |

| PARALLEL TWO-DIMENSIONAL FAST FOURIER TRANSFORM                                          |      |

| Parallel Row-Column Decomposition Fast Fourier Transform                                 |      |

|                                                                                          |      |

| Parallel Vector-Radix Fast Fourier Transform                                             |      |

| Tensor Product Programming Language TWO-DIMENSIONAL FAST FOURIER TRANSFORM DESIGN IN SPW |      |

|                                                                                          |      |

| Algorithm Selection                                                                      |      |

| Block Diagram Design Example                                                             |      |

| Adding Levels of Hierarchy                                                               |      |

| Parallel Partitioning in SPW                                                             |      |

| SUMMARY                                                                                  | 00   |

| IV DETAILED DESIGN AND IMPLEMENTATION                                                    | 67   |

| CODE GENERATION USING CGS                                           | 67        |

|---------------------------------------------------------------------|-----------|

| Standard C Code Generation System                                   | 67        |

| Code Generation System for DSP Microprocessors                      | 73        |

| VHDL GENERATION THROUGH HDS                                         | 75        |

| HDS Main Library                                                    | <i>77</i> |

| HDS Micro Library                                                   | <i>78</i> |

| Floating to Fixed-Point Conversion Utility                          | <i>78</i> |

| Fixed-Point Optimizer                                               | <i>78</i> |

| HDL Link                                                            | <i>79</i> |

| 2D FFT VHDL Generation                                              | 80        |

| Summary                                                             |           |

| V. CONCLUSIONS AND RECOMMENDATIONS                                  | 83        |

| SPW Review                                                          | 83        |

| Ease of Learning                                                    |           |

| Ease of Use                                                         |           |

| Functionality                                                       |           |

| Summary                                                             |           |

| RECOMMENDATIONS                                                     |           |

| Summary                                                             | 93        |

| APPENDIX A - GUIDE TO DSP PROCESSORS AND CORES                      |           |

| APPENDIX B - MULTIDIMENSIONAL FFT VECTOR NOTATION                   | 96        |

| APPENDIX C - VECTOR-RADIX FFT                                       | 97        |

| APPENDIX D- SPW/CGS GENERATED C CODE STRUCTURE                      | 100       |

| APPENDIX E - SPW/HDS GENERATED VHDL CODE FOR THE (2X2)-POINT 2D FFT | 102       |

| VITA                                                                | 107       |

| BIBLIOGRAPHY                                                        | 108       |

## **List of Figures**

| Figure 1 - SPW Components [2:III]                                                                | 3  |

|--------------------------------------------------------------------------------------------------|----|

| Figure 2 - SPW MultiProx [2]                                                                     | 4  |

| FIGURE 3 - RELATIVE SAMPLING RATES AND ALGORITHM COMPLEXITIES OF SIGNAL PROCESSING               |    |

| APPLICATIONS [8]                                                                                 | 12 |

| FIGURE 4 - HARVARD ARCHITECTURE [16:41]                                                          | 16 |

| FIGURE 5 - OSCAR I [16:293]                                                                      |    |

| FIGURE 6 - OSCAR-32 [16:301]                                                                     |    |

| FIGURE 7 - BIER AND LEE ARCHITECTURE [17:300]                                                    | 22 |

| FIGURE 8 - N-CLUSTERS ARCHITECTURE [18:94]                                                       | 23 |

| FIGURE 9 - ADEPAR DUAL PORT RAM [19:150]                                                         |    |

| FIGURE 10 - SPW DEVELOPMENT PROCESS                                                              |    |

| FIGURE 11 - SAMPLE BLOCK DIAGRAM OF THE NOTCH FILTER [2]                                         | 27 |

| FIGURE 12 - RECTANGULAR SAMPLING GRID [28:36]                                                    | 39 |

| FIGURE 13 - HEXAGONAL SAMPLING GRID [28:44]                                                      |    |

| FIGURE 14 - GRAPHICAL DEVELOPMENT OF THE 2D FFT WITH ROW-COLUMN DECOMPOSITION [25:242]           |    |

| FIGURE 15 - 2D FFT REORGANIZATION FOR CONVENTIONAL VIEWING [25:245]                              | 43 |

| FIGURE 16 - ISOLATED RADIX-(2 x 2) BUTTERFLY [28:78]                                             |    |

| FIGURE 17 - RADIX-(4 x 4) FFT BUILT UPON RADIX-(2 x 2) FFTS (ONLY ONE OF THE FOUR BUTTERFLIES IS |    |

| SHOWN IN THE SECOND COLUMN)                                                                      |    |

| FIGURE 18 - 16-POINT FFT ON FOUR PROCESSORS WHERE EVERY FOUR ROWS IS ON A SEPARATE PROCESSO      |    |

| [7:384]                                                                                          |    |

| FIGURE 19 - COMBINATION OF ELEMENTS IN A (4x4)-POINT 2D FFT [7:394]                              |    |

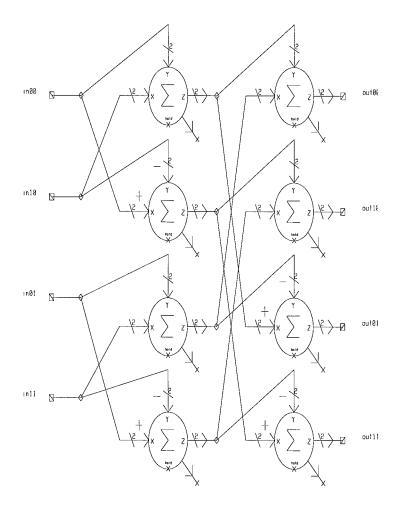

| FIGURE 20 - BLOCK DIAGRAM DETAIL MODEL OF THE (2x2)-POINT BUTTERFLY                              |    |

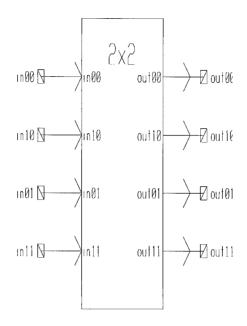

| FIGURE 21 - BDE CREATED SYMBOL FOR THE (2x2)-POINT BUTTERFLY                                     |    |

| FIGURE 22 - CUSTOM SYMBOL FOR THE (2X2)-POINT BUTTERFLY                                          |    |

| FIGURE 23 - TEST SYSTEM FOR THE (2x2)-POINT BUTTERFLY                                            |    |

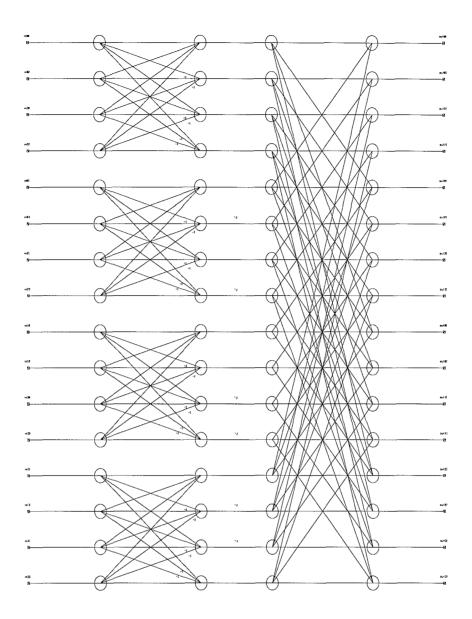

| FIGURE 24 - BLOCK DIAGRAM DETAIL MODEL FOR THE (4X4)-POINT FFT                                   |    |

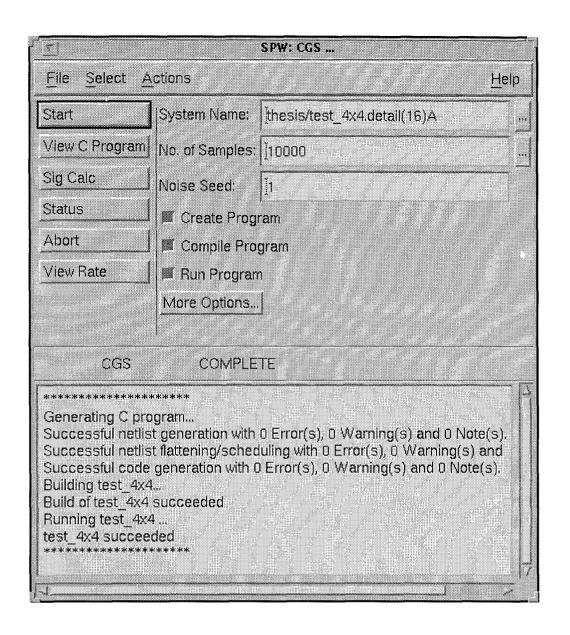

| FIGURE 25 - STANDARD C CGS ON LOCAL PLATFORM [:1-3.]                                             |    |

| FIGURE 26 - PLATFORM SELECTION [2]                                                               |    |

| FIGURE 27 - CGS CONTROL WINDOW [2]                                                               |    |

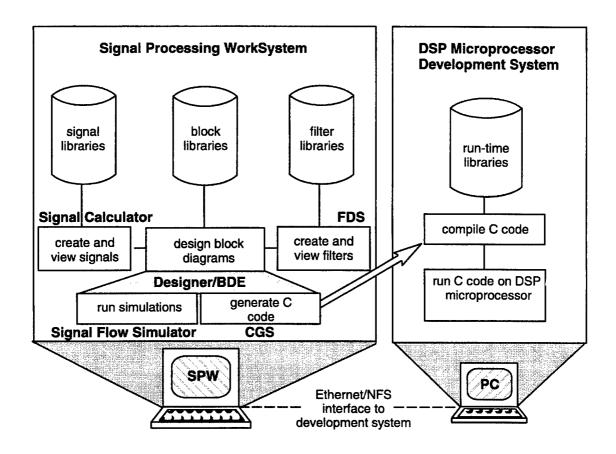

| FIGURE 28 - CGS USING PC DEVELOPMENT BOARD [33:1-4]                                              |    |

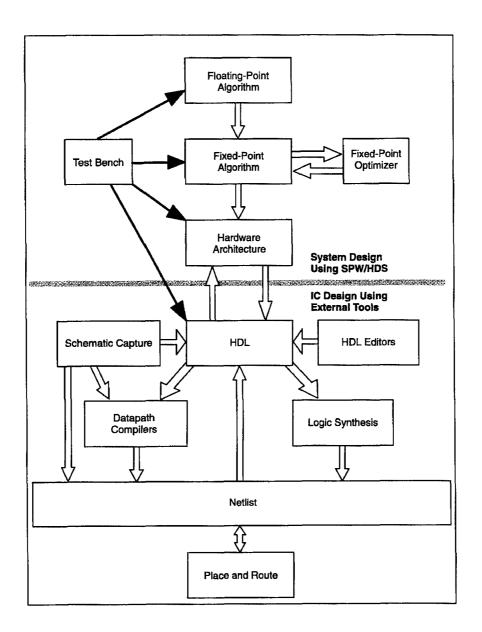

| FIGURE 29 - HARDWARE DESIGN FLOW [35:1-11]                                                       |    |

| FIGURE 30 - ISOLATED RADIX-(2X2) BUTTERFLY[28:78]                                                | 99 |

## **List of Tables**

| TABLE 1 - URLS OF PUBLISHERS OF BLOCK DIAGRAM BASED SIGNAL PROCESSING TOOLS                 | .29 |

|---------------------------------------------------------------------------------------------|-----|

| TABLE 2 - RATIO OF EFFICIENCY OF AN M-DIMENSIONAL CUBIC LATTICE TO A HYPERSPHERICAL LATTICE |     |

| [28:47]                                                                                     | .40 |

| TABLE 3 - COMPARISON OF NUMBER OF COMPLEX MULTIPLICATIONS REQUIRED FOR M-DIMENSIONAL FFT    |     |

| ALGORITHMS [28:82]                                                                          | .47 |

| Tarle 4- How SPW satisfies criteria of well designed software                               |     |

#### **Abstract**

Digital signal processing (DSP) has become a popular method for handling not only signal processing, but communications, and control system applications. A DSP application of interest to the Air Force is high-speed avionics processing. The real-time computing requirements of avionics processing exceed the capabilities of current singlechip DSP processors, and parallelization of multiple DSP processors is a solution to handle such requirements. Designing and implementing a parallel DSP algorithm has been a lengthy process often requiring different design tools and extensive programming experience. Through the use of integrated software development tools, rapid prototyping becomes possible by simulating algorithms, generating code for workstations or DSP microprocessors, and generating hardware description language code for hardware synthesis. This research examines the use of one such tool, the Signal Processing WorkSystem (SPW) by the Alta Group of Cadence Design Systems, Inc., and how SPW supports the rapid prototyping process from an avionics algorithm design through simulation and hardware implementation. Throughout this process, SPW is evaluated as an aid to the avionics designer to meet design objectives and evaluate trade-offs to find the best blend of efficiency and effectiveness. By designing a two-dimensional fast Fourier transform algorithm as a specific avionics algorithm and exploring implementation options, SPW is shown to be a viable rapid prototyping solution allowing an avionics designer to focus on design trade-offs instead of implementation details while using parallelization to meet real-time application requirements.

## EVALUATION OF DESIGN TOOLS FOR RAPID PROTOTYPING OF PARALLEL SIGNAL PROCESSING ALGORITHMS

#### I. Introduction

Digital signal processing (DSP) processors are in wide use in communications, signal processing, and control system applications. These high-speed, single-chip microcomputers are specifically designed for handling computationally intensive tasks in lieu of using conventional microprocessors [1:482]. A DSP application of interest to the Air Force is high-speed avionics. As computing demands of existing and emerging DSP applications continue to increase, the current single-chip DSP processor technology can no longer keep pace. While parallelization of multiple DSP processors is a solution to increase throughput and speed beyond the capabilities of a single processor for the demanding requirements of avionics signal processing, designing and implementing parallel DSP processor systems can be a lengthy process. Rapid prototyping of parallel architectures is possible through the use of software tools such as the Signal Processing WorkSystem (SPW) [2]. The purpose of this thesis effort is to evaluate the rapid prototyping process to design and implement parallel DSP algorithms using SPW and SPW's applicability for high-speed avionics applications.

#### Background

Real-world DSP is the filtering of signals in real-time [1:3]. Analog to digital conversion takes place either on-chip or off-chip after which manipulation of the digital signal simplifies to computational operations. The digitized results can then be converted back to analog signals via digital to analog converters. To process real-time data, both the converters and the DSP processors must possess the speed and throughput necessary for continuous processing. However, computing requirements are surpassing the capabilities of single-chip DSP processors. For example, algorithms that integrate speech coding/decoding into a multi-media environment require 1-30 million instructions per second (MIPS) which is well within the 30-50 MIPS capability of today's computer workstation [3:269]. Emerging applications, such as video coding/decoding and medical imaging algorithms, require 0.1-10 billion instructions per second [3:269]. Current DSP processors are not capable of handling these requirements. Thus, parallel architectures such as those used for shipboard radar systems may contain as many as 1000 processors to handle the tremendous processing and throughput requirements [4]. Design of such systems can now take advantage of emerging DSP development tools to exploit the capabilities of a DSP processor in parallel architectures.

Of the DSP development tools available today, AFIT and Wright Laboratory

(WL) have access to Signal Processing WorkSystem (SPW). SPW is an integrated

software environment for developing, simulating, and implementing DSP systems. SPW

consists of a number of components to accomplish these tasks as designed and

Analog to digital conversion is converting an analog input consisting of a voltage or current to digital output binary word.

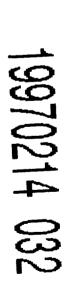

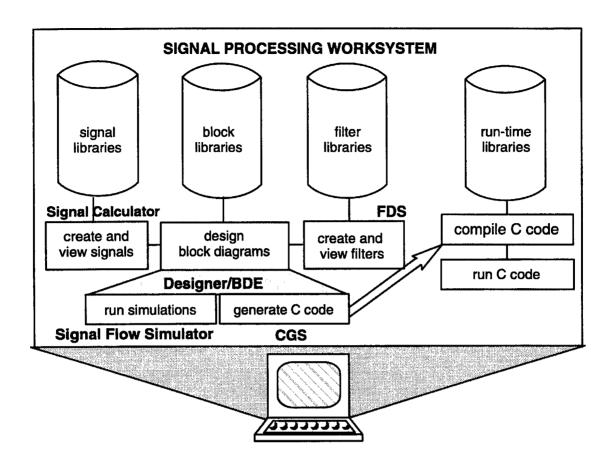

implemented by the Alta Group of Cadence Design Systems [2]. Figure 1 illustrates these components.

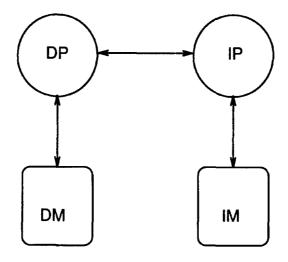

Figure 1 - SPW Components [2:iii]

DSP systems are interactively designed using blocks from the SPW libraries or blocks created using the Filter Design System (FDS) or Finite State Machine (FSM) Editor. System block diagrams are designed in the Block Diagram Editor (BDE) with interconnections to represent data flow. Simulation is performed through the Signal Flow Simulator with signal analysis using the Signal Calculator. The Code Generation System (CGS) option of SPW adds the capability to automatically generate C code for execution on workstations or DSP processors [2]. The addition of the MultiProx (MPX) option gives SPW the capability to partition a design among multiple processors for

multiprocessing simulations or downloading to a development board containing multiple processors [2].

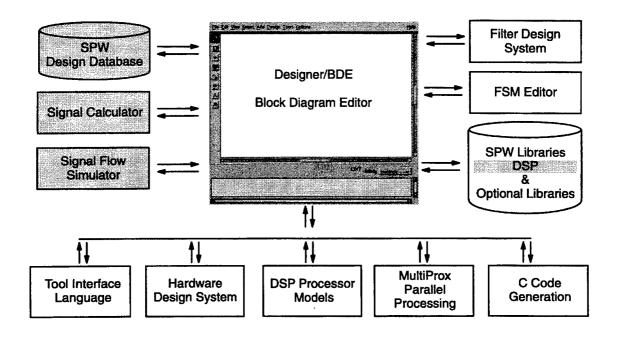

Figure 2 - SPW MultiProx [2]

Another component of SPW, the Hardware Design System (HDS), generates VHDL<sup>2</sup> descriptions with when used with VLSI synthesis tools, can result in a layout for fabrication of an application specific integrated circuit (ASIC) [2,5]. The combination of the tools available within the SPW environment supports rapid prototyping as well as parallel implementations for signal processing.

<sup>&</sup>lt;sup>2</sup> VHDL is the VHSIC Hardware Description Language where VHSIC is Very High Speed Integrated Circuit. VHDL is a standard language for the specification of hardware behavior and structure for very-large scale integration design [5].

#### Problem Statement

Real-time processing of data is a requirement for avionics signal processing applications. However, the speed and throughput requirements for real-time signal processing currently exceed the capabilities of single-chip DSP processor implementations. Moreover, the current development time from DSP algorithm selection to design simulation to testable hardware implementation often prohibits efforts to make design changes and evaluate trade-offs.

The objective of this thesis investigation is to evaluate the rapid prototyping process from algorithm selection through design, simulation, and hardware test of parallel DSP architectures for avionics signal processing using the SPW environment. This is accomplished by first choosing a general algorithm representative of those used in high-speed avionics applications. The algorithm is then designed at a high-level using functional blocks and interconnections using the SPW environment for simulation and analysis. Simulation and analysis of the simulation results are performed to determine whether or not the algorithm functions and performs as required based upon acceptance criteria. With the use of the code generation capabilities of SPW, porting to a workstation and a development board (Texas Instruments) for hardware/software testing is investigated. Finally the capability of the HDS component of SPW to generate VHDL is evaluated. Throughout the rapid prototyping process, the SPW environment is evaluated for ease of learning, ease of use, and functionality and to what extent SPW allows a designer to evaluate design and implementation trade-offs.

#### Rationale

Why is it important that signal processing system designers take advantages of emerging software development tools? The primary reason is the time savings involved in rapid prototyping. Instead of spending time writing code<sup>3</sup> which is in most cases an exercise of translating the functions of an abstract system design, a designer can spend more time analyzing the design by making trade-offs in cost and performance to improve efficiency and effectiveness [6]. Through rapid prototyping, the process of design, simulation, and hardware test can be completed efficiently so that more time may be spent refining the algorithm and addressing design issues such as numeric formats and sampling rates rather than being bogged down with low-level implementation details. If necessary, extra performance may be gained by fine tuning the automatically generated code by hand once the design of the algorithm has been decided. Another benefit of rapid prototyping is the ability to test a system in real time on actual hardware which not only speeds up the testing process, but also reflects a better representation of the final product. The time savings achieved through rapid-prototyping allows a designer to spend more time examining and evaluating design trade-offs. These design trade-offs include parallel partitioning strategies and data handling strategies to include input, output, and storage. Other design issues include power consumption, in-circuit testing capability, and redundancy. Rapid prototyping time savings provides more time to be spent examining these design issues.

<sup>&</sup>lt;sup>3</sup> Code or more appropriately, source code is the form in which a computer program is written by the designer in a formal programming language which is subsequently compiled automatically into a machine-recognizable code [6]

#### Scope

This research focuses on the capability of SPW to design, simulate, and implement a parallel system of DSP processors using a rapid prototyping methodology. Synthesis is attempted on unmodified VHDL code or portions of the VHDL code which are synthesizable. A selected avionics algorithm is used throughout the process. Design trade-offs of this algorithm are evaluated through the use of parallel processing metrics [7].

#### Standards

Evaluating computing performance is critical to analyzing different architectural approaches. Performance metrics include run time, speedup, efficiency (time and space), cost and the isoefficiency metric of scalability [7:117-141]. Each of these metrics is defined in Kumar's Introduction to Parallel Computing [7].

#### Methodology

The following subsections identify and describe the tasks that comprise this research effort:

#### **Literature Review**

The literature review, Chapter II, is a continuing process to examine the areas of high-speed avionics signal processing, parallel DSP architectures, and DSP software development tools. The goal of a literature review of high-speed avionics signal processing is an understanding of the classification of avionics applications and the

requisite computing requirements for a particular classification. The literature review of current efforts to parallelize DSP applications enables selection of an architecture to support a particular avionics signal processing applications. A survey of DSP software development tools serves both to identify the most promising environments in use today for rapid prototyping and to allow comparisons with the SPW environment. In an effort to locate information in these areas, the World Wide Web (WWW) and associated WWW search engines are used extensively. The growth of the DSP industry has been accompanied by a proliferation of sites on the internet relating signal processing. Finally, factors to consider while evaluating DSP software development tools such as SPW are described.

#### **Algorithm Selection and Design**

In order to demonstrate the process of taking an algorithm through the rapid prototyping process, an algorithm representative of those used in high-speed avionics signal processing is chosen. In addition to avionics signal processing applicability, selection is based upon algorithm complexity so design and test may be completed within the time allotted for this research. Chapter III, Algorithm Selection and Design, provides background on the chosen algorithm, the two-dimensional fast Fourier transform, and describes the design and simulation of the algorithm in SPW. SPW is evaluated for whether or not it provides adequate functionality to allow a designer to make design trade-offs while providing a proper interface.

#### **Design Implementation**

Chapter 4, Design Implementation, investigates the three different implementation options available in SPW. From the block diagram design of the algorithm, C code can be generated for execution on workstation. Also, C code may be generated for porting to DSP processors for testing on development boards. The potential of Wright Laboratory's (WL) Texas Instruments Quad C40 DSP320 Development Board is assessed. Finally, hardware synthesis support exists through VHDL code generation. Each of these options is analyzed with appropriate metrics applied.

#### Materials and Equipment

The following materials and equipment are required:

- Sun Workstation (AFIT VLSI Laboratory)

- Signal Processing WorkSystem (SPW) Version 3.0 (AFIT)

- SPW Hardware Design System (HDS) option

- SPW Code Generation System (CGS) MultiProx option

- Synopsys VHDL Tools

- Texas Instruments Quad C40 DSP320 Development Board/PC-OS/2 (WL Avionics Laboratory)

#### Summary

To evaluate the utility of the Signal Processing WorkSystem, an algorithm representative of high-speed avionics applications is implemented using a rapid prototyping methodology. With the parallel processing support, code generation, and hardware synthesis support of SPW, significant time may be saved in the development process while at the same time, an algorithm can be parallelized to improve upon the capabilities of a single-chip DSP processor.

This chapter describes the problem and describes the potential advantages of using software development tools for rapid prototyping. The reader is assumed to have a basic understanding of computer science and electrical engineering concepts. Chapter II discusses the areas of high-speed avionics signal processing, DSP in general, parallel/distributed DSP design, rapid prototyping through DSP software development tools and software evaluation principles. Chapter III describes the algorithm selection and its design in SPW. Chapter IV covers implementation of the design to include C code generation, and HDL generation for hardware synthesis. Finally, Chapter V draws conclusions and presents recommendations on the use of SPW to support a rapid prototyping methodology for high-speed avionics applications.

#### **II. Literature Review**

This chapter provides background information on examples of high-speed avionics signal processing and computational requirements, along with engineering to meet these requirements. This is followed by a discussion of DSP processors. Then, an explanation of how parallelism may be used along with descriptions of several current parallel DSP designs is provided. The rapid prototyping methodology is explained and emergence of software development tools which support this methodology is examined. Finally, factors to consider while evaluating hardware/software development platforms are described.

#### High-Speed Avionics Signal Processing

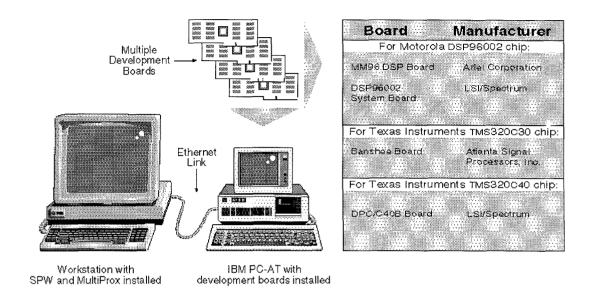

DSP applications may be classified based upon relative algorithm complexity, required sample rates, clock rates, and numeric formats [8]. Algorithms specify the arithmetic operations but not how the operations are to be implemented at lower levels of detail. Implementation details, for example, include the sample rate or the rate at which samples are consumed, processed, or produced [8]. The ratio of clock rate to sample rate partially determines the hardware required to implement an algorithm with a given complexity [8]. Numeric formats are also a design issue to evaluate the trade-offs between algorithm simplicity and numerical accuracy. The following graph shows the range of the signal processing applications when considering relative algorithm complexity and sample rates:

Figure 3 - Relative Sampling Rates and Algorithm Complexities of Signal Processing Applications [8]

High-speed avionics signal processing typically falls in the area of high sample rates with less complex algorithms.

Military avionics signal processing applications include secure communications, sonar processing, image processing, navigation, missile guidance, and radar/sensor processing [1:474]. A DSP application of vital interest to the Air Force in the area of radar/sensor processing is accurate, real-time target recognition through the use of radar cross-section (RCS) images. *Xpatch* [9] is currently used for this purpose, but the real-time computing requirements far exceed the capabilities today. *Xpatchf*, the frequency domain program of *Xpatch*, requires 35 minutes on an Intel i860 computer to calculate the

RCS image of an F-15 aircraft from a single perspective, and a complete image requires 16,800 hours or 700 days of computer time [10:1-2]. While the ultimate goal of real-time RCS prediction some time away, parallelization can offer significant speed-ups in the near term.

The first AFIT research on parallelizing electromagnetic prediction code was conducted by Captain Scott Suhr [11], who demonstrated the speedup possibilities by parallelizing a previously designed serial code. A precursor to *Xpatch*, NECBSC, was modified for execution on an Intel iPSC Hypercube. The results were a speedup of 3.59 on an eight node Intel iPSC/2 over the serial benchmark on the same machine. Speedup on an Intel iPSC/860 was 2.51 due to a faster benchmark, but overall time was reduced by 23 percent [11:xi]. Research continued by Lieutenant Paul Work to parallelize serial ray-tracing code considered factors such as load balancing and decomposition [12:xi], which demonstrated the speedup possibilities using parallel processing with electromagnetic code.

Later research conducted by Captain B. A. Kadrovach focused on the *Xpatch* algorithms by profiling *Xpatchf*, the frequency domain portion of *Xpatch*, to reveal any repetitive functionality and periodicity [10]. This profiling identified the ray-tracing portion of the multi-bounce feature of *Xpatchf* as a candidate for a hardware implementation [10:3-11]. Aspects of the ray-tracing algorithm are computationally independent, enabling many rays to be processed simultaneously. Captain Kadrovach designed a hardware model, called a Voxel Unit (VU), to handle the multi-bounce RCS processing. He envisioned that multiple VUs under the control of a single

microprocessor would be used in parallel to achieve speedups greater than two orders of magnitude when using a network of eight cards each with a four-by-four array of VUs [10: vii,4-2]

The research of Captains Suhr and Kadrovach and Lieutenant Work has shown the advantages parallelism can offer for radar processing. While Captain Suhr demonstrated the speedup possibilities inherent in a serially designed electromagnetic code, Captain Kadrovach focused on a portion of a code and the description of hardware, the VU, to accomplish this portion in parallel. DSP development tools with parallel design support offer the designer the ability to make these design decisions at a high level and automate the implementation.

The fast Fourier transform (FFT) and more specifically, the two-dimensional FFT is another useful algorithm in radar processing applications. Like the ray-tracing algorithm, the 2-D FFT algorithm may benefit from parallelism. Tools such as SPW allow a designer to experiment with different parallel partitioning approaches, data rates, and numeric formats at a block diagram level to determine the best solution for given requirements.

#### Digital Signal Processing

Real world DSP is the real-time processing of converted analog signals [1:3].

Analog to digital conversion takes place either on-chip or off-chip after which manipulation of the digital signal as bits and bytes simplifies to mathematical operations in a digital computer. The results can then be converted back to analog signals via digital

to analog converters. To process real-time data, DSP processors must possess the speed and throughput necessary for continuous processing to handle incoming data as it becomes available. However, computing requirements now surpass the capabilities of single-chip DSP processors. For example, algorithms that integrate speech coding/decoding into a multi-media environment require 1 to 30 million instructions per second (MIPS) which is well within the 30 to 50 MIPS capability of today's computer workstation [3:269]. Emerging applications, such as video coding/decoding and medical imaging algorithms, will require 0.1 to 10 billion instructions per second [3:269]. Current DSP processors with processing rates from 1 to 30 MIPS are not capable of handling these emerging applications.

Since DSP processors are designed with signal processing in mind, they have capabilities not found in conventional microprocessors. To handle large amounts of data in real time, DSP processors' internal architectures differ from those of conventional microprocessors. For example, the TMS 320 series manufactured by Texas Instruments uses a Harvard-type architecture [16] as illustrated in Figure 4.

Figure 4 - Harvard Architecture [16:41]

The Harvard architecture has separate address spaces for instructions (IM) and data (DM) to allow for concurrent instruction and data fetching [1:482]. The TMS 320 architecture is different from a conventional microprocessor which must sequentially access instructions and data from a single address space. Another characteristic unique to the DSP processor is the existence of the single-instruction multiply-and-accumulate (MAC) operation [1:482]. DSP algorithms often require a sum-of-products arithmetic operation which is handled by a MAC operation. The use of a MAC operation is illustrated by examining the difference equation of a nonrecursive digital filter of order M:

$$y[n] = \sum_{m} B_m * x[n-m] \tag{1}$$

where  $B_m$  are filter coefficients [13:614]. This difference equation is an example of the need for a MAC operation. Other features of DSP processors vary depending on the particular manufacturer, but the different internal architecture and presence of the MAC

operation are two characteristics which distinguish the DSP processor from conventional microprocessors.

DSP systems may be classified into different families. These are the Bit-Slice. Word-Slice® (registered trademark of Analog Devices, Inc.), single-chip DSP microcomputers, and DSP microprocessor families. Bit-slice systems were early attempts at DSP parallelism using small but fast subunits to build a required word-length [3:250]. The Bit-Slice approach, which used medium scale integration technology, has since been surpassed by the Word-Slice® approach due to the improvements in very large scale integration (VLSI) technology [3:252]. Word-Slice® systems benefit from fewer components with similar performance. Single-chip DSP microcomputers and microprocessors are designed primarily for individual use, with the single-chip DSP processor the most self-contained [3:252]. An abundance of single-chip DSP applications has led to a very competitive market, and therefore the price-performance ratio for this family of processors is relatively low. Of the four families, the single-chip DSP microcomputer is the best building block for a parallel architecture since it offers the best price-performance ratio using the latest in VLSI technology. Appendix A provides the Pocket Guide to DSP Processors and Cores [14] which provides a sampling of DSP processors and their characteristics to include architectural details, RAM and ROM sizes, and unit prices.

Another characteristic of DSP processors which may be required of a particular application, is low power operation. Portable consumer electronics such as pagers, cellular telephones, personal audio equipment, and laptop computers demand low power

consumption to extend battery life [15]. DSP processors employ several techniques for power reduction. Reducing the supply voltage is one technique since power consumption is proportional to the square of supply voltage [7]. This reduction is possible through the tighter integration of transistors on a chip. Power management features such as sleep/idle modes, clock frequency control, and control over unused peripherals and outputs are also used to reduce power consumption [7]. System and programming techniques to avoid external memory access and unnecessary logic state transitions also help to reduce overall power consumption [7]. The competitive DSP market is forcing manufacturers to use these methods to achieve the longest battery life. While ASICs can be designed to minimize the number of transistors necessary for an application, the existence of power reduction measures on DSP processors makes them attractive for low power applications.

#### Parallel/Distributed DSP Designs

With parallel processing, speed and throughput of single-chip DSP processors can be surpassed. Simply put, parallel processing techniques may be used to take advantage of the parallelism inherent in many DSP algorithms. That is, the calculations involved in signal processing required are often independent so that the work can be partitioned among two or more separate processors. Parallel processing has long been used to connect multiple microprocessors, and the associated architectures and algorithms developed for microprocessors are applicable to parallel DSP.

#### **Georgia Institute of Technology Digital Signal Multiprocessors**

The concepts used in parallel microprocessor architectures may be applied to DSP processors. Continuing research at Georgia Institute of Technology on Digital Signal Multiprocessors (DSMP) systems. At Georgia Tech, two experimental laboratory DSMP systems have been built. The two laboratory systems are known as OSCAR (Optimal Synchronous Cyclo-static Array) and OSCAR-32 [16:293]. These systems represent the first of multiprocessor systems designed for DSP.

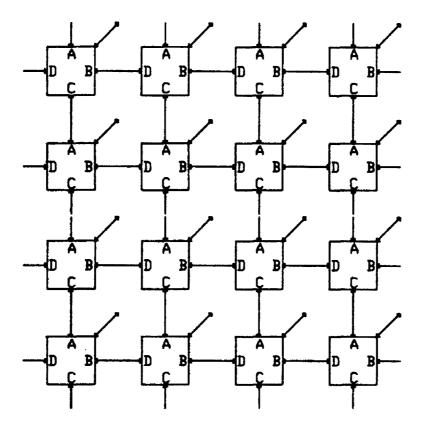

The first DSMP prototype at Georgia Tech, OSCAR, was completed in 1986. The OSCAR project was divided into two phases. The first phase, OSCAR I, was a small-scale supercomputer model which consisted of sixteen commercially available processors in a 4x4 rectangular array.

Figure 5 - OSCAR I [16:293]

OSCAR II was to be built using 128 processors, but funding cuts prevented its realization. The OSCAR I was a complex system where each processor contained five fully parallel communication ports, a 32-bit floating-point arithmetic unit, local memory, address generation unit, micro-controller, and a debugger/monitor processor [16:294].

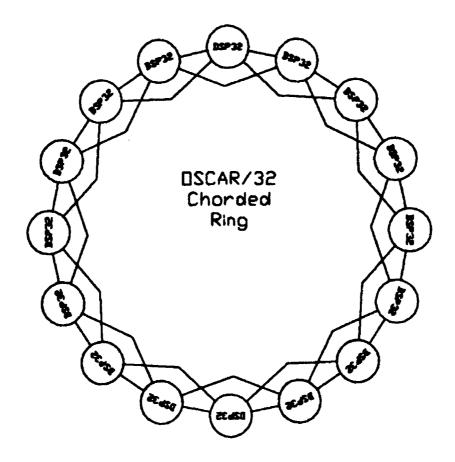

The second DSMP prototype, OSCAR-32, was built at Georgia Tech in 1987. OSCAR-32 is a reconfigurable ring structure of 32-bit processors with each processor resident on a constituent processor boards (CPB). Up to sixteen of the CPBs can be connected to form a ring of processors.

Figure 6 - OSCAR-32 [16:301]

The OSCAR-32 uses the AT&T WE-DSP32 floating-point signal processing microcomputer which provides high-speed processing at the expense of heavy timing penalties for inter-processor communication [16:297].

The experimental DSMPs at Georgia Tech are examples of the use of parallel processing concepts of architecture and algorithm design for signal processing applications. These machines had general purpose signal processing in mind. However,

even within the scope of signal processing, there exists a variety of applications which could benefit from different architectures.

#### **DSP Multiprocessor Architectures**

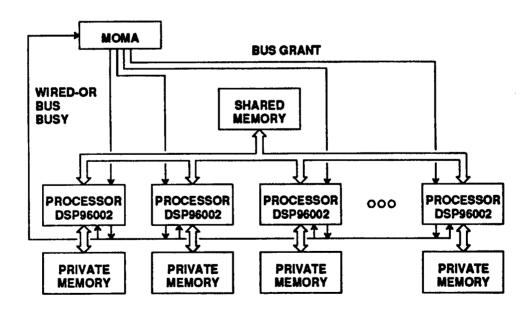

A paper by Bier and Lee [17] describes several abstract multiprocessor architectures for real-time DSP. Each of the architectures contain a memory shared by the individual processors along with a controller processor which grant access to a bus connecting the processors to the shared memory. The Gated-Shared-Memory Architecture uses a gate keeper as a hardware implementation of the semaphore concept [17:299]. To avoid the use of a gate keeper and its complexity, a central controller, called the MOMA (Maintains Ordered Memory Accesses), is used in an Ordered Shared-Memory Architecture.

Figure 7 - Bier and Lee Architecture [17:300]

The MOMA takes advantage of a-priori knowledge of shared memory accesses by the processors. The MOMA grants access to the bus and the shared memory in a prespecified order. The main advantage of this scheme is that no explicit hardware or software is required to resolve memory access issues [17:299-300].

Another multiprocessor architecture for DSP is described by Baraniecki and Baraniecki. The architecture is composed of 'N-Clusters' each consisting of 1 to M processor elements. The processors within a cluster share a common main memory for application programs and a common database memory. Memory accesses are handled by two interconnection chips.

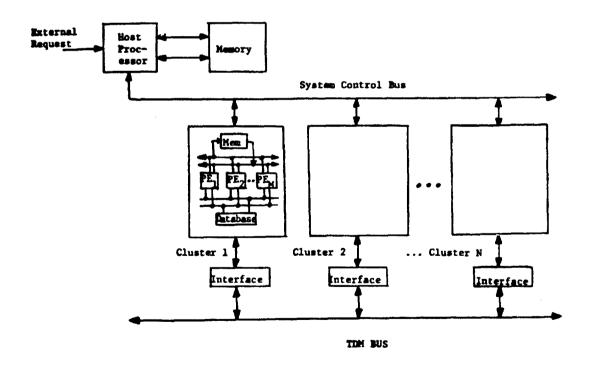

Figure 8 - N-Clusters Architecture [18:94]

The entire system is controlled by a single processor known as the host with a control and data bus interconnecting the different clusters [18:90]. While this architecture has the flexibility to handle a wide range of applications through various partitioning schemes among the different clusters, the repeatability and limited communication requirements of ray-tracing does not require such a complex architecture.

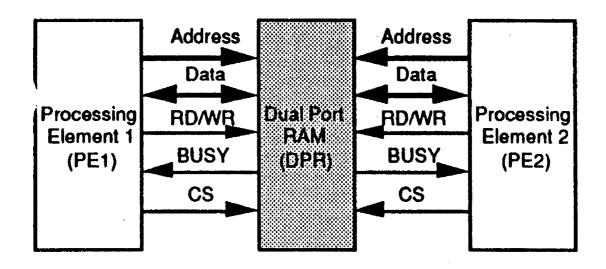

Two hardware examples of parallel DSP systems use dual port memories to handle inter-processor communication.

Figure 9 - AdEPAR Dual Port RAM [19:150]

The Advanced Educational Parallel (AdEPAR) DSP system uses boards containing TMS320C25 DSP processors hosted by an IBM PC. The PC host handles communication between processors or from the processors to the host by dual port memory for simplicity, speed, modularity, and configurability [19:149]. A system used for image processing described in [20:494] also makes use of a dual port memory

configuration for message passing and intermediate storage. While both examples use this configuration for higher performance/cost ratios, the number of processors and the amount of communication could hinder performance as processors not adjacent pass messages through intermediate processors. This approach does offer a simple solution for interconnection of multiple processors.

#### Rapid Prototyping and DSP Development Tools

The rapid growth in the DSP industry over past decade has seen equal growth in the number of software tools and what these tools offer the signal processing system designer. The most sophisticated of these environments allow a designer to realize an algorithm in a hardware prototype or even a VLSI layout in a fraction of the time once required. Benefits of using these tools include version control and automatic design rule checking along with simulation, test data generation, software generation, and hardware synthesis.

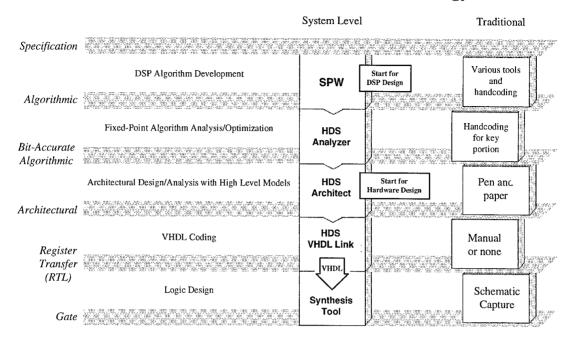

A simple methodology for the development of a DSP system can be defined by the design, simulation, and implementation stages. In design, a system based upon a specification is designed at a high level usually graphically. Simulation includes test generation to determine if the design is functioning as intended. Implementation can consist of software generation for a workstation, a network of workstations, or a DSP chip. Implementation can also include generation of hardware description language code like VHDL to be used with synthesis tools for the fabrication of a custom chip. Sophisticated tools provide the means to accomplish each of these stages.

Figure 10 - SPW Development Process

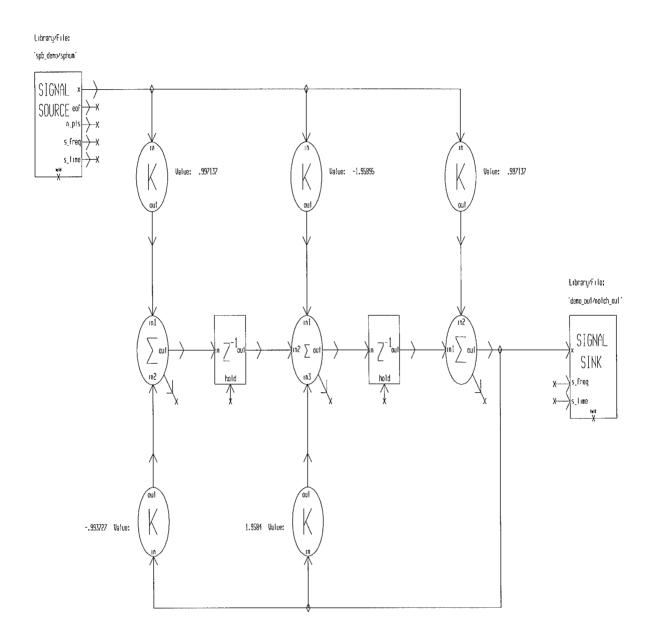

Block diagrams are the most common way to represent a signal processing system. Block diagrams have long been used for documentation and the use of these diagrams in software tools provides a way to describe, document, and analyze a signal processing system. A system block diagram is represented as a network of transfer functions, data sources and sinks, and control functions. The following block diagram, included as part of the SPW tutorials, represents a notch filter<sup>4</sup>.

26

<sup>&</sup>lt;sup>4</sup> A notch filter is used to attenuate frequencies within a specified band.

Second order 60 Hz notch filter

Figure 11 - Sample Block Diagram of the Notch Filter [2]

These blocks are interconnected with lines or arrows to represent data movement. The block diagram can also be referred to as a dataflow graph. Each block in the system has an underlying computational model to define the block's behavior [21].

Simulation of a system is performed using either a synchronous dataflow (SDF) or dynamic dataflow(DDF) model. In SDF, each block consumes or produces a fixed number of samples prior to execution, whereas a DDF block can consume and produce varying numbers of samples on its inputs and outputs [21]. The DDF simulation model is supported by Mentor Graphics' DSP Station and COSSAP. SPW uses the SDF model for simulation. For the purposes of analyzing the data produced in a simulation, the capability data plotting and parameter changing during simulation is advantageous. SPW includes the Signal Calculator for analysis purposes.

While most block diagram based software tools offer simulation capabilities, few have the capability to generate software code and even fewer support hardware synthesis. Tools with hardware synthesis support are the most expensive with costs in excess of \$30K compared with PC software tools without synthesis support costing from \$500 to \$5K [21]. In addition to SPW's HDS tool, DSP Station and COSSAP also support hardware synthesis. Synthesis support can be in the form of either a register-transfer-level (RTL) design or a behavioral level design. All three tools support RTL designs, but only DSP Station and COSSAP produce behavioral descriptions. RTL designs are expressed in terms of RTL elements such as registers, multipliers, and shifters while a behavioral level design dictates nothing about implementation and allows the synthesis tool to handle details [21].

A few software tools support simulation and software generation for parallel systems. These include SPW's MultiProx, Pegasus from Jovian Systems, and RIPPEN from ORINCON Technologies. MultiProx allows a designer to partition a design for

multiple processors. Individual code can then be generated for each processor in the system along with the communication required among the processors in the system.

Real-time testing on a development board containing multiple DSPs can be monitored to analyze load balancing. Table 1 contains the uniform resource locators (URLs) for block diagram based signal processing development tools where additional information regarding these products may be obtained.

Table 1 - URLs of publishers of block diagram based signal processing tools

| Publisher            | Software Package                               | Publisher URL                      |

|----------------------|------------------------------------------------|------------------------------------|

| Cadence/Alta Group   | Signal Processing WorkSystem                   | http://www.altagroup.com/          |

| Hyperception         | Hypersignal-Windows Block Diagram              | http://www.hyperception.com/       |

| Jovian               | Pegasus Parallel Processing Design Environment | http://www.jovian.com/jovian/      |

| Mentor Graphics      | DSP Station                                    | http://www.mentorg.com/            |

| Orincon              | Rippen                                         | http://www.ppgsoft.com/rippen.html |

| Signalogic           | DSPower                                        | http://www.signalogic.com/         |

| Synopsys/CADIS GmbH. | COSSAP                                         | http://www.synopsys.com/           |

| U.C. Berkeley        | Ptolemy                                        | http://www.ptolemy.berkeley.edu/   |

Of the tools available for signal processing application development, SPW offers the most promise for rapid prototyping. Algorithm design begins using intuitive, graphical block diagrams as a system specification. Next, the algorithm's block diagram can be simulated for proper operation. Implementation can take the form of either code generation for workstations and off-the-shelf DSP processors or VHDL code for synthesis and the fabrication of a custom VLSI chip.

#### Software Evaluation Factors

A well designed software package is one which strikes a balance between ease of learning, ease of use, and functionality [22:13]. To evaluate a software package, each of these factors must be kept in mind while learning to use and eventually using a software package to perform tasks it was designed to perform. Ease of learning is the extent to which a new user can become proficient with the software with minimal training and practice [22:13]. What is the quality of the introductory tutorials? How long does it take to gain proficiency with the software? Ease of use is the extent to which the software allows an experienced user to perform tasks with minimal effort [22:13]. Are there shortcuts which allows an experienced user to perform tasks more quickly? Functionality is the extent of different capabilities the software provides [22:13]. Does the software provide all the necessary functions and sufficient options to tailor those functions? Is the user protected from complexity while at the same time given sufficient capabilities to keep from outgrowing the system? While evaluating software, these factors and the techniques to optimize them must be kept in mind.

In his book on computer interface design guidelines, Brown describes four techniques for optimizing the ease of learning, ease of use, and functionality of a software package [22:14]. The first technique is to design for novices, experts, and intermittent users alike. Menus should be available for the novices and intermittent users, but shortcuts such as keystroke combinations should be available for experienced users. The second technique is to avoid excess functionality. Functions should be prioritized by estimated frequency of use so that the more used are easiest to perform while seldom used functions are accessible through secondary paths or eliminated entirely. The third

technique is to provide multiple paths through the use of menu bypass, stacking or type-ahead techniques, and user-defined macros to handle the same task. The fourth technique is to design for progressive disclosure and graceful evolution by making basic functions simple to learn and frequent tasks quick to perform, encouraging experimentation by minimize consequences through reversible actions, and using defaults to minimize the user choices to produce the most likely outcome [22:15-17].

There are various other design details to consider when evaluating a software package. For example, the appropriate use of color allows a user to locate or identify classes of information with greater speed and reliability [22:66]. Icons, when used correctly, can simply task selection. Error messages should allow a user to learn what was done incorrectly and how to go about correcting the error [23:ix]. On-line documentation should not just be an electronic version of what is available from the printed manuals, but it should supplement the manuals by being content-sensitive. A well designed software package uses all of these elements to contribute to the ease of learning, ease of use, and functionality of a system.

# Summary

This literature review provides background information on high-speed avionics signal processing applications. Research has shown the advantages of parallelism and the parallelization possibilities existing in the avionics application, *Xpatch*. Algorithms such as the FFT can also exploit the advantages of parallelism. The unique characteristics of the single-chip DSP microcomputer make it an ideal candidate to serve as a building block for a parallel architecture. Careful analysis of the architectures described herein is

required to determine their applicability to a particular algorithm. An overview of different DSP development environments was provided along with methods to evaluate them. Environments such as SPW allow a designer to design, simulate, and implement a DSP algorithm. After an explanation of the algorithm selected, the next chapter describes an algorithm design using SPW.

# III. Algorithm Selection and Design

This chapter begins with an explanation of the algorithm selection which is representative of algorithms encountered in high-speed avionics applications. The selected algorithm serves as a basis from which to evaluate SPW as a tool to support rapid prototyping or parallel signal processing algorithms. The explanation of the algorithm selection is followed by an introduction to the selected algorithm, the 2D fast Fourier transform (FFT), beginning with the fundamentals of continuous Fourier transform and ending with the parallel multidimensional FFT. A description of the SPW 2D FFT design follows.

# Algorithm Selection

To adequately evaluate whether or not SPW properly blends ease of learning, ease of use, and functionality, the software must be sufficiently exercised. That is, an algorithm must be chosen which represents a class of problem which might be used in an avionics application. Moreover, the chosen algorithm must have a level of complexity to sufficiently test the simulation and code generation capabilities of SPW. Toward these aims, the 2D FFT has been selected as the algorithm to implement with SPW.

The 2D FFT has found use in a variety of applications. Applications include tomography, data compression and picture processing [24:216]. Also, the 2D FFT is used for two-dimensional waveforms encountered in geophysical arrays, gravity and magnetic data, and antenna analysis [25:232]. Radar applications include cross-section measurement, moving target indicators, synthetic aperture, Doppler processing, pulse

compression and clutter rejection [25:2-3]. Any of the aforementioned applications can benefit from possible speed and accuracy improvements. However, in real-time applications where data post-processing is not an option, speed becomes a hard requirement.

Xpatch algorithms were not chosen to design and implement in SPW for several reasons. When this research was initiated, the offices responsible for xpatch maintenance were in the midst of reorganization. This reorganization hindered efforts to receive foresight into the future of xpatch. The restricted nature of the xpatch code itself also limited accessibility. Interest expressed by both the sponsor, Wright Laboratory, and Rome Laboratories as well as the universal applicability of the 2D FFT to applications other than radar led to the ultimate selection.

## Introduction to the Fast Fourier Transform

#### **Fourier Transform**

Essentially, the Fourier transform of a waveform is the decomposition of that waveform into sinusoids of varying frequencies which must sum to the original waveform [25:4]. Mathematically stated, the Fourier integral is defined as

$$H(f) = \int_{0}^{\infty} h(t)e^{-j2\pi ft} dt$$

(2)

where h(t) is the time domain waveform decomposed into a sum of sinusoids of varying frequencies, and H(t), the frequency domain, is the Fourier transform of h(t) if the integral exists for every value of f [25:9]. Traditionally, lowercase letters represent functions of

time while uppercase letter represent functions of frequency. The Fourier transform is a continuous function. For computer calculations the Fourier transform must be discretized resulting in the discrete Fourier transform (DFT).

#### **Discrete Fourier Transform**

The DFT approximates the continuous Fourier transform by representing the waveform to be decomposed as a set of regularly sampled points rather than a continuous waveform. Thus, the DFT is a linear transformation which maps a set of regularly sampled points from a cycle of a periodic signal onto an equal number of points to represent a signal's frequency spectrum [7:377]. The DFT approximation can unambiguously determine frequencies within a range as defined by the Shannon's sampling theorem [26]. This is also known as the Nyquist rate where the frequencies contained in the signal are all less than half the rate at which the points are sampled [27:9]. However, when accounting for real-world restrictions such as finite word lengths and associated quantization error, rates as high as 10-to-1 are suggested. Mathematically, the DFT is stated as [27:10]

$$A(k) = \sum_{n=0}^{N-1} a(n) * e^{-j2\pi nk/N}$$

(3)

where

$$e^{-j2\pi nk/N} = \cos(2\pi nk/N) - j\sin(2\pi nk/N)$$

N: number of complex data points

n: input point index

k: output point index

a(n): discretized input signal

While this discretized approximation of the Fourier transform can be handled by digital computer, the number of operations can be reduced as found by Cooley and Tukey in 1965 to form the FFT.

#### **Fast Fourier Transform**

The algorithm Cooley and Tukey devised in 1965 and its subsequent variations which compute the DFT of an n-point series in O(nlogn) operations are collectively referred to as the FFT [7:377]. The FFT allows Fourier analysis of signals through the use of digital hardware and computers instead of analog filter banks and spectrum analyzers [28:60]. The FFT is essentially a recursive algorithm for computing the DFT [29:231]. An excellent explanation of the development of the FFT is provided in [25:132]. Here, an example shows how the matrix factorization process introduces zeros into the factored matrix thus eliminating the need for some multiplication operations. Essentially, the efficiency of the FFT is based on the capitalizing on the symmetry and periodicity attributes of the complex phase portion of the DFT calculations [24:217].

The FFT offers an improvement over the DFT with reduced computational load. The computational load is reduced from  $4N^2$  additions and  $4N^2$  multiplications for the DFT to 2N additions and  $Nlog_2(N)$  multiplications for the FFT [27:28]. Reduced quantization noise is an indirect benefit from the fewer number of calculations required. Quantization noise is reduced since fewer multiplications are performed and therefore there are fewer times where the multiplication result must be rounded off [27:28].

The FFT has two disadvantages. The reorganization of data and the computation reduction necessitates computation of all of the output frequencies even if only a few are required [27:28]. While the DFT outputs one output frequency at a time, often all frequencies are needed and the computational savings compensate for this weakness [27:28]. Another disadvantage to FFT algorithms are their inability to handle inputs varying numbers of points. That is, the number of input points is fixed. To overcome this, zero padding is can be used for signal with fewer samples than the FFT algorithm [27:14]. While adding zeros to a signal allows for variable data collection lengths for a given FFT algorithm, the real and imaginary responses are affected [27:15]. The affects of this can be minimized through the use of weighting (or window) functions [27:35].

#### **Multidimensional Fast Fourier Transform**

The multidimensional FFT extends the single dimensional FFT to two or more dimensions. A 2D signal is a function h(x,y) of two variables x and y to describe 2D waveforms such as images [25:232]. Video, for example, offers a third dimension of time. Assuming the 2D signal is periodic in all dimensions, in the continuous space, the 2D Fourier transform is given by

$$H(u,v) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} h(x,y) e^{-j2\pi(ux+vy)} dxdy$$

(4)

where h(x,y) is the 2D function and H(u,v) is the 2D transform of h(x,y) [25:232-233]. Similar to the 1D transform, the 2D  $(N_1 \times N_2)$  discrete Fourier transform is given by [27:74]

$$A(k_1, k_2) = \sum_{n_{1=0}}^{N_1-1} \sum_{n_2=1}^{N_2-1} a(n_1, n_2) e^{-j2\pi \left[n_1 k_1 / N_1 + n_2 k_2 / N_2\right]}$$

(5)

where

$$e^{-j2\pi[n_1k_1/N_1+n_2k_2/N_2]} = \cos(2\pi(n_1k_1/N_1+n_2k_2/N_2)) - j\sin(2\pi(n_1k_1/N_1+n_2k_2/N_2))$$

$N_1 \times N_2$ : size of discretized input signal

$n_1$ ,  $n_2$ : input point indices

$k_1$ ,  $k_2$ : output point indices

and  $a(n_1,n_2)$  and  $A(k_1,k_2)$  are the discretized input and output signals respectively. This separability of the summations in terms of  $n_1$  and  $n_2$  leads to the row-column decomposition of the 2D Fourier transform.

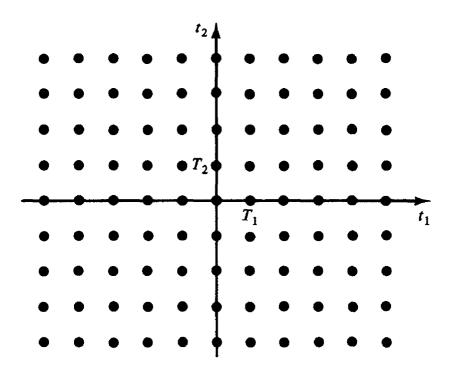

Multidimensional transform implementations can be hampered by the volume of sampling data required. To reduce the amount of sampling points required, different sampling geometries may be employed. The straightforward, uniform rectangular sampling pattern is most often used for simplicity of use and implementation. This consists of periodic sampling in rectangular coordinates as illustrated in Figure 12 [28:36].

Figure 12 - Rectangular sampling grid [28:36]

This is also known as the sampling matrix or lattice [28:266]. It can be shown that for higher and higher dimensions of transforms, the rectangular sampling scheme does not provide the most efficient sampling method in terms of the number of samples needed to represent a multidimensional signal. Figure 13 shows a hexagonal sampling grid:

Figure 13 - Hexagonal sampling grid [28:44]

The efficiency gains of a hexagonal sampling scheme (hyperspherical) over a rectangular sampling scheme (cubic) is quite substantial with increasing dimensions of transforms as shown in Table 2.

Table 2 - Ratio of efficiency of an M-dimensional cubic lattice to a hyperspherical lattice [28:47]

| M | Efficiency |

|---|------------|

| 1 | 1.000      |

| 2 | 0.866      |

| 3 | 0.705      |

| 4 | 0.499      |

| 5 | 0.353      |

| 6 | 0.217      |

| 7 | 0.125      |

| 8 | 0.062      |

Multidimensional DFTs are mathematically represented using matrices in order to represent the periodicities due to both the sampling lattice and the signal to Fourier transform [30:45]. Refer to Appendix B for more information.

#### **Row-Column Decomposition**

The most natural method of calculating the 2D Fourier transform is the row-column decomposition method due to the structure. This method uses the separability of the 2D Fourier transform to decompose the problem into two sets of 1D transforms. By factoring the exponential term

$$e^{-j2\pi[n_1k_1/N_1+n_2k_2/N_2]} = e^{-j2\pi(n_1k_1/N_1)} * e^{-j2\pi(n_2k_2/N_2)}$$

(6)

the two summations may be separated to give

$$\sum_{n_1=0}^{N_1-1} \left[ \sum_{n_2=0}^{N_2-1} a(n_1, n_2) * e^{-j2\pi(n_2 k_2/N_2)} \right] * e^{-j2\pi(n_1 k_1/N_1)}$$

(7)

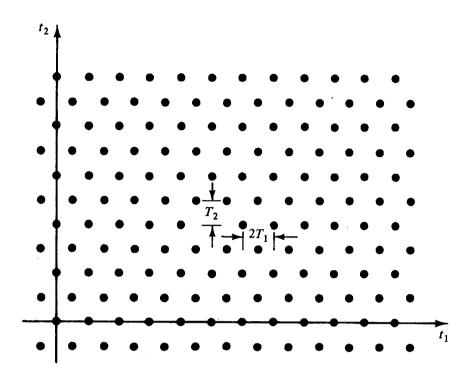

This results in taking a 1D Fourier transform in the  $n_2$  dimension followed by a 1D Fourier transform in the  $n_1$  dimension or a row-column decomposition. Of course, this can be accomplished in either order. An excellent graphical development of the 2D Fourier transform is given in Brigham [25:241]. The following figure illustrates the row-column decomposition FFT:

Figure 14 - Graphical development of the 2D FFT with row-column decomposition [25:242]

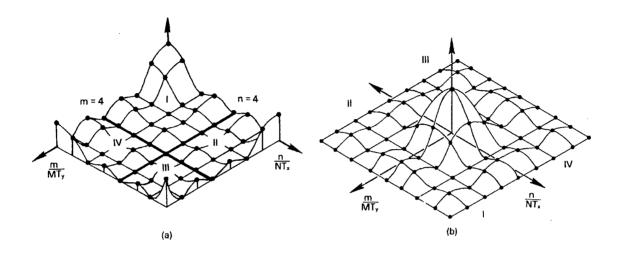

Figure 14 (c) gives the unordered 2D FFT result. Conventional viewing would require rearranging the FFT results. If the FFT results were divided into quadrants, rearranging would be accomplished by performing a right circular shift through two quadrants [25:244] as illustrated in Figure 15.

Figure 15 - 2D FFT reorganization for conventional viewing [25:245]

The row-column decomposition has an advantage in its simplicity. The decomposition is intuitive and easy to visualize. Also, a 2D transform algorithm can be constructed out of 1D transform algorithms that may already be provided. 1D algorithms are readily available and highly optimized for different computational machines. For example, the CLASSPACK Signal Processing Library contains optimized C routines to perform FFTs [31]. Thus, construction of a 2D algorithm can benefit from their computational efficiency.

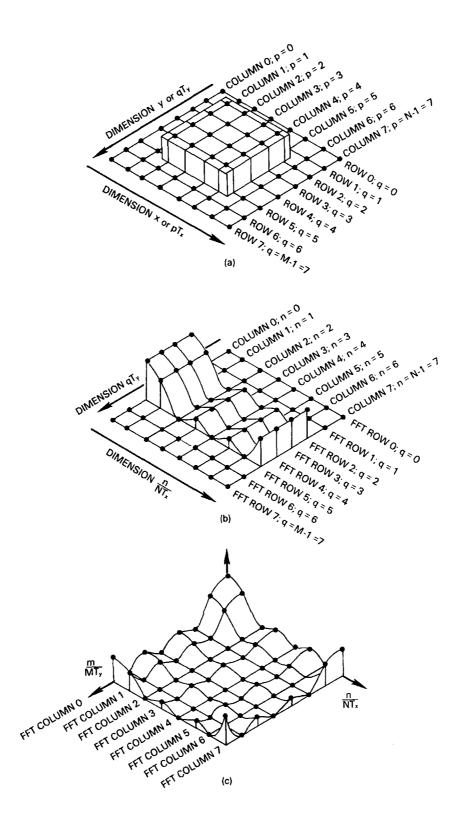

#### **Vector-Radix Algorithms**

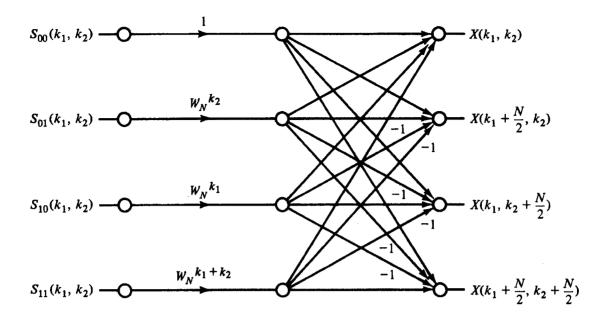

A 1D FFT achieves computational efficiency through the "divide and conquer" strategy where each transform length is recursively divided by a power of 2 into smaller transform lengths [28:76]. Like the 1D FFT, the 2D vector-radix FFT decomposes a 2D DFT into successively smaller 2D DFTs until only trivial 2D DFTs remain [28:76]. This basic structure of the algorithm is commonly called a butterfly. The decimation-in-time version of the vector-radix algorithm is accomplished by expressing a  $(N_1 \times N_2)$ -point DFT in terms of four  $N_1/2 \times N_2/2$  DFTs represented by four summations [28:77]:

$$S_{00}(k_1, k_2) = \sum_{m_1=0}^{N/2-1} \sum_{m_2=0}^{N/2-1} x(2m_1, 2m_2) W_N^{2m_1 k_1 + 2m_2 k_2}$$

(8)

$$S_{01}(k_1, k_2) = \sum_{m_1=0}^{N/2-1} \sum_{m_2=0}^{N/2-1} x(2m_1, 2m_2 + 1) W_N^{2m_1k_1 + 2m_2k_2}$$

(9)

$$S_{10}(k_1, k_2) = \sum_{m_1=0}^{N/2-1} \sum_{m_2=0}^{N/2-1} x(2m_1 + 1, 2m_2) W_N^{2m_1 k_1 + 2m_2 k_2}$$

(10)

$$S_{11}(k_1, k_2) = \sum_{m_1=0}^{N/2-1} \sum_{m_2=0}^{N/2-1} x(2m_1 + 1, 2m_2 + 1) W_N^{2m_1 k_1 + 2m_2 k_2}$$

(11)

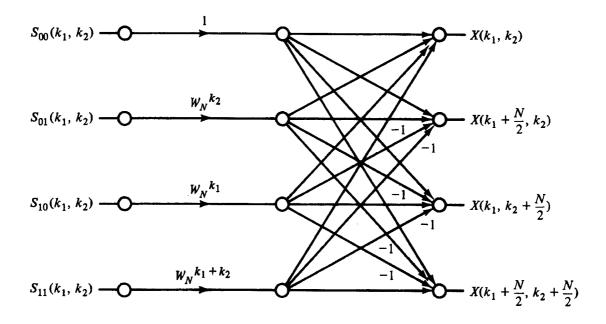

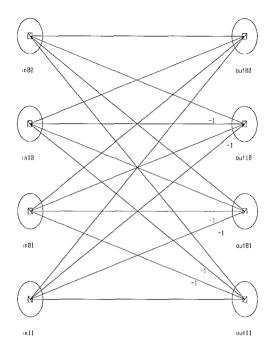

One summation handles data with both even indices, a second handles data with even and odd indices, a third handles data with odd and even indices, and a fourth handles data with two odd indices [28:77]. Figure 16 illustrates a single radix-(2 x 2) butterfly:

Figure 16 - Isolated Radix-(2 x 2) Butterfly [28:78]

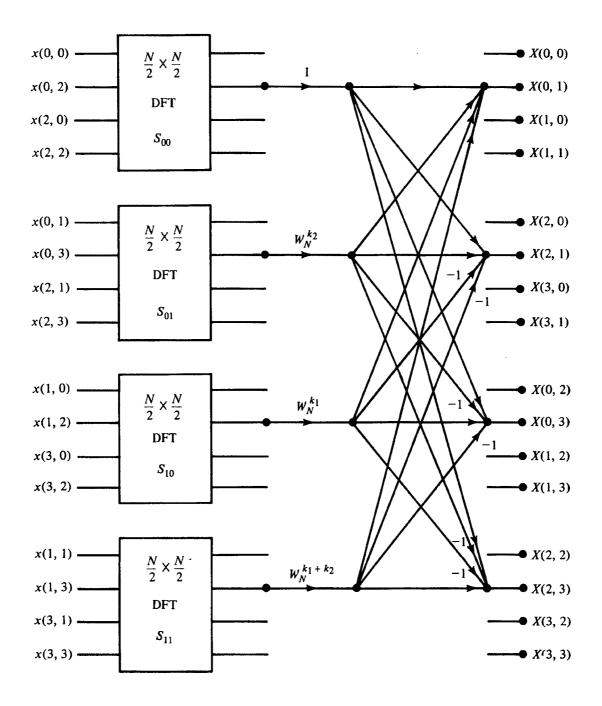

Figure 17 illustrates how a larger FFT is constructed from smaller FFTs:

Figure 17 - Radix-(4 x 4) FFT built upon radix-(2 x 2) FFTs (only one of the four butterflies is shown in the second column) [28:79]

Refer to Dudgeon [28] for a complete derivation of the vector-radix FFT.

Computational savings are the primary advantage of the vector-radix algorithm over the row-column decomposition. The number of complex multiplications for the row-column decomposition is

$$C_{r/cFFT} = \frac{M}{2} N^M \log_2 N \tag{12}$$

where

M = number of dimensions

N = number of complex points

and the number of complex multiplications for the vector-radix algorithms is given by

$$C_{vr(2x2)} = \frac{2^M - 1}{2^M} N^M \log_2 N \tag{13}$$

Table 3 shows the computational savings in terms of complex multiplications required for vector-radix ( $C_{vr}$ ) and row-column ( $C_{r/c}$ ) multidimensional FFTs:

Table 3 - Comparison of number of complex multiplications required for M-dimensional FFT algorithms [28:82]

| M | C <sub>vr(2x2)</sub> /C <sub>r/c FFT</sub> |

|---|--------------------------------------------|

| 2 | 0.75                                       |

| 3 | 0.58                                       |

| 4 | 0.47                                       |

| 5 | 0.39                                       |

The vector-radix algorithm requires fewer and fewer complex multiplications as compared to the row-column algorithm as the number of dimensions increases. The number of complex additions required is the same for both methods and is given as [28:82]

$$A_{r/cFFT} = A_{vr(2x2)} = MN^2 \log_2 N \tag{14}$$

Though each approach requires the same number of complex additions, the vector radix does offer savings in the number of complex multiplications required.

#### Parallel Two-Dimensional Fast Fourier Transform

#### Parallel Row-Column Decomposition Fast Fourier Transform

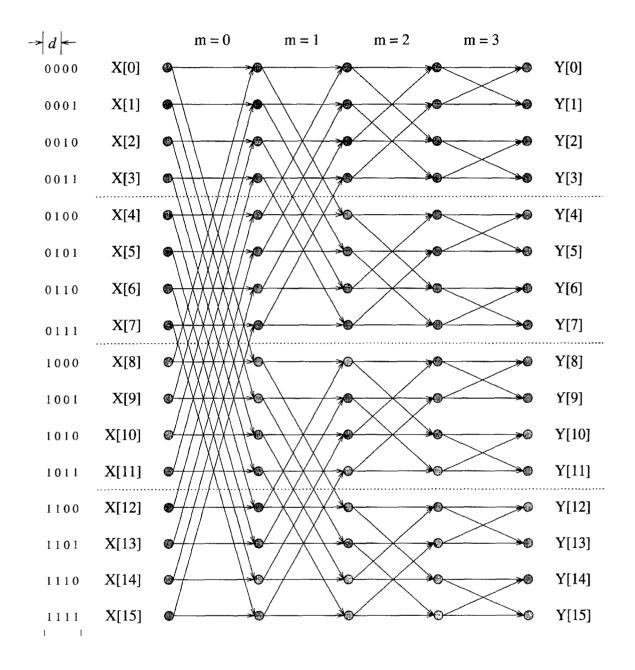

A 2D FFT with row-column decomposition can be accomplished in parallel by either performing parallel 1D FFTs serially, performing serial FFTs in parallel, or by a combination thereof. Choosing among the approaches depends largely on the resources available, for example, the number of processors and the availability of existing code. Two algorithms for performing parallel 1D FFTs are described in Kumar [7]. They are the binary-exchange algorithm and the transpose algorithm.

#### **Binary-Exchange Algorithm**

The binary-exchange algorithm is described in Kumar for a hypercube for one or multiple elements per processor and a mesh architecture. The FFT structure lends itself to the hypercube architecture since the required communications use the added connectivity of the hypercube topology efficiently. For the one element per processor approach, the FFT is cost-optimal with a processor-time product of  $\Theta(n \log n)$ , equal to the complexity of a serial n-point FFT [7:383]. Since, this approach is usually not

feasible for a large number of points, the multiple elements per processor approach must be taken as shown in Figure 18.

Figure 18 - 16-point FFT on four processors where every four rows is on a separate processor [7:384]

Kumar shows that for this approach the binary-exchange algorithm is reasonably scaleable if the problem size is increased at the rate of  $\Theta(p \log p)$  and the communication bandwidth and processing speed of the processors are balanced [7:388]. On the other hand, the binary-exchange algorithm is not very scaleable on a mesh since the problem size must be increased exponentially with the number of processors to maintain constant efficiency [7:390].

#### **Transpose Algorithm**

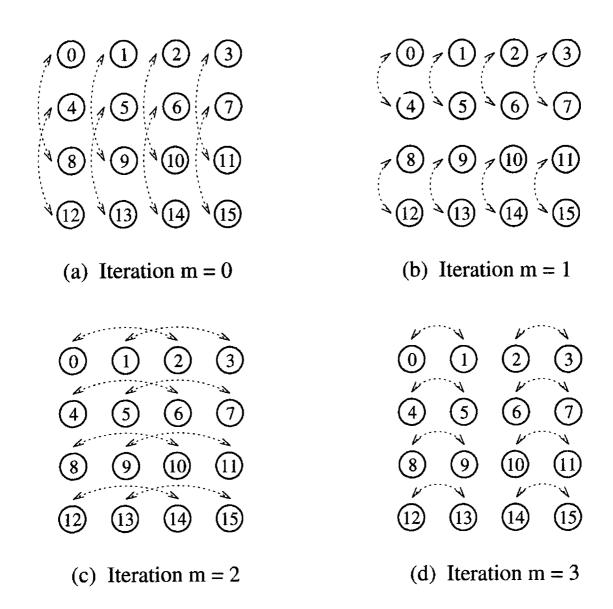

The transpose algorithm, which uses matrix transposition, is useful when the ratio of communication bandwidth to processor speed is low and high efficiencies are required [7:393]. In the transpose algorithm, a  $\sqrt{n}$ -point FFT is computed for each column of  $\sqrt{n} \times \sqrt{n}$  array of points. After the array is transposed (the only communication required),  $\sqrt{n}$ -point FFTs are computed for each of the columns for the transposed array [7:394]. Figure 19 shows the how the elements are combined to compute a 16 point 2D FFT using 4 x 4 square array.

Figure 19 - Combination of elements in a (4x4)-point 2D FFT [7:394]

The choice of whether to use the binary-exchange or the transpose algorithm depends on the relative values of the communication time parameters with SIMD and shared-memory computers leaning toward the transpose algorithm and MIMD computers with the binary-exchange algorithm [7:396].

#### **Parallel Vector-Radix Fast Fourier Transform**

Since the vector-radix approach to the FFT is similar to the 1D FFT in that both are decomposed into smaller FFTs, a similar decomposition among multiple processors is possible. Two approaches are possible. The first approach involves pipelining where one or more of the columns of the signal flow diagram are handled by each processor. This approach would be more suitable for performing a series of FFT computations for higher throughput at the expense of latency. For example, if a single processor were assigned to handle the computations of each stage,  $\log_2 N$  processors would be required for a N x N 2D FFT. This results in  $\Theta(N^2)$  computations assuming the same execution times for both complex additions and multiplications. On the other hand, partitioning the graph horizontally would reduce latency times subject to the increased communication required between processors. If the number of processors, p, were equal to N for an N x N FFT, the computations would be  $\Theta(N\log_2 N)$ . The overhead required for communication would be  $\Theta(N\log_2 N)$  and  $\Theta(N^2)$  for the vertical partitioning  $(p=N\log_2 N)$  and horizontal partitioning (p=N) respectively. The pipelining method can benefit from fewer messages with less processors since messages may be combined between stages for better efficiency whereas horizontal partitioning requires communication between all processors at each stage.

#### **Tensor Product Programming Language**

Another approach to designing FFT algorithms is through the use of tensor products. The tensor product notation is a concise method for characterizing complex signal processing algorithms with mechanisms for specifying operation for serial, vector,

or multiprocessor computers [32:41]. The tensor product is a binary matrix operator used to combine two matrices to form a single, larger matrix, and tensor product factorizations can reveal underlying symmetries which may be used to design efficient algorithms [32:41]. The reader is referred to [32] for an explanation of the tensor product approach and the applicability to FFT algorithms.

# Two-Dimensional Fast Fourier Transform Design in SPW Algorithm Selection

The vector-radix 2D FFT was chosen as the algorithm to implement in SPW for its applicability to avionics and more specifically, radar applications. While a row-column approach would have sufficed, the vector-radix algorithm is well suited in a hierarchical design environment whereby FFTs capable of a larger number of input points are built using FFTs of fewer points. Thus, larger and larger systems may be constructed while increasing system complexity and exercising the software's capability to handle this complexity. Also, the regular structure of the vector-radix 2D FFT is well suited for partitioning for multiple processors.

One assumption must be stated before block diagram design. First, input sampling points are assumed to be equally spaced in each dimension or rectangular. Algorithms capable of handling different geometries may be designed, but there is no specific need for that capability in this research. Furthermore, in radar applications of the 2D FFT, source data is collected in traditional rectangular form. While other geometries can use more efficient sampling geometries, such an approach would require more effort on the sampling side of the problem.

#### **Block Diagram Design Example**

The block diagram design process begins with the Block Diagram Editor (BDE) of SPW. In the BDE, a signal flow diagram of a particular algorithm is constructed by connecting functional blocks together. SPW provides a wide variety of functional blocks (approximately 350) for this purpose, and SPW has the facility to allow a designer to create custom blocks by linking in FORTRAN or C programs to a new block. At the block diagram design level, features such as self-test and redundancy may be designed in to address reliability. Reproducing sections of a block diagram design and adding decision-making logic is possible within the BDE.

For the purposes of the vector radix 2D FFT, all the required blocks are provided. Levels of hierarchy are used to hide detail at higher levels of abstraction. Every block, whether it be SPW-provided or user-designed, contains a detail model and a symbol. The following explanation of the block diagram design process centers on the design of the basic vector radix-(2x2) butterfly.

#### **Butterfly Detail Model**

The detail model is the level of design which determines how a particular block functions. It consists of other blocks and the associated interconnections. The vector radix butterfly consists solely of complex additions as shown by the following equations [28:73]:

$$X(0,0) = x(0,0) + x(1,0) + x(0,1) + x(1,1)$$

(15)