## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2018

# Gating Methods for High-Voltage Silicon Carbide Power MOSFETs

**Audrey Dearien** University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

### Citation

Dearien, A. (2018). Gating Methods for High-Voltage Silicon Carbide Power MOSFETs. Graduate Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/2794

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

## Gating Methods for High-Voltage Silicon Carbide Power MOSFETs

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Audrey Mae Dearien John Brown University Bachelor of Science in Engineering, 2016

> May 2018 University of Arkansas

| This thesis is approved for recommen    | dation to the Graduate Council.           |

|-----------------------------------------|-------------------------------------------|

| H. Alan Mantooth, Ph.D. Thesis Director |                                           |

| Simon Ang, Ph.D. Committee Member       | Juan Carlos Balda, Ph.D. Committee Member |

#### **ABSTRACT**

The objective of this thesis is to assess the challenges associated with driving Silicon Carbide (SiC) power devices, and to compare the potential gate drive methods for these devices which address those challenges. SiC power devices present many benefits that make them suitable for next generation automotive, power utility grid, and energy management applications. High efficiency, increased power density, and reliability at high-temperatures are some of the main benefits of SiC technology. However, the many challenges associated with these devices have prevented their adoption into industry applications. The argument is made in this thesis that the gate driver is a key component in providing proper control to enable the reliable and high performance of these devices. Thus, as the main control mechanism, the gate driver topology should be carefully considered in the design of SiC-based converters.

In this thesis, the main issues and challenges of operating SiC power devices will be explored, and the common mitigation techniques will be discussed. Next, the switching operation of the SiC power MOSFET and the loss analysis will be performed for the voltage-mode and current-mode drivers. Additionally, a solution incorporating a multi-level voltage-mode driver is proposed as an alternative to the other methods. The comparison of these techniques and their ability mitigate EMI and other negative consequences of fast-switching while minimizing switching energy losses will be analyzed. This is done through the comparison of the methods based on the analytical approach, through the use of simulations using device models, and through experimentation. The multi-level driver is found to be good alternative to the conventional voltage-mode driver, and is thus assessed in detail in the experiments. Finally, the considerations for the experimental setup using the double pulse test (DPT) is also discussed. Conclusions are made based on the performance of the device under multi-level turn-off, and future considerations for enabling the next generation high-voltage SiC MOSFETs are discussed.

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Dr. H. Alan Mantooth, for his guidance and for providing me with the means to gain deeper knowledge into this field of power electronics. It was a great honor to work in the Power MSCAD research group. I would also like to thank Dr. Juan Carlos Balda and Dr. Simon Ang for being on my advising committee, and for the knowledge they shared in the classroom. Additionally, I am grateful for Chris Farnell for his leadership and detailed supervision throughout my time as a graduate student.

My gratitude also goes to Andrea Wallace, Zeke Zumbro, and Daniel Schwartz for going through graduate school alongside me and for the memories that will last a lifetime. Additionally, I am grateful for my lab mates who have taught me so much and have guided me along the way: Shuang Zhao, Janviere Umuhoza, Yusi Liu, Yuzhi Zhang, Sayan Seal, Haider Mhiesan, Kenneth Mordi, and Dereje Woldegiorgis.

Finally, I'd like to thank the GRid-connected Advanced Power Electronics Systems (GRAPES) research center for the funding of the gate driver project.

## **DEDICATION**

I would like to dedicate this to my parents for their continuous support and encouragement and for making me the person I am today. Thank you for giving me courage to pursue my dreams.

## TABLE OF CONTENTS

| Table of Contents                                             | 5  |

|---------------------------------------------------------------|----|

| LIST OF FIGURES                                               | 1  |

| LIST OF TABLES                                                | 1  |

| Chapter 1                                                     | 1  |

| INTRODUCTION                                                  | 1  |

| 1.1 Motivation for this Research                              | 1  |

| 1.1.1 Power Semiconductor Devices                             | 3  |

| 1.1.2 Applications for Wide-Band-Gap Power Devices            | 6  |

| 1.1.3 Challenges of Implementing SiC MOSFETs                  | 8  |

| 1.1.4 Gating methods and considerations for SiC power devices | 10 |

| 1.2 Thesis Objectives                                         | 12 |

| 1.3 Thesis Organization                                       | 12 |

| 1.4 References                                                | 13 |

| Chapter 2                                                     | 16 |

| CHALLENGES OF IMPLEMENTING SIC MOSFETS                        | 16 |

| 2.1 Introduction                                              | 16 |

| 2.2 SiC Operating Challenges and Solutions                    | 16 |

| 2.2.1 Crosstalk and Self-turn-on                              | 16 |

| 2.2.2 Common-mode noise and isolation                         | 19 |

| 2.2.3 Parasitic Inductance                                    | 22 |

| 2.2.4 Protection                                              | 23 |

| 2.3 Conclusion                                                | 27 |

| 2.4 References                                                | 28 |

| Chapter 3                                                     | 30 |

| GATE DRIVE METHODS AND PERFORMANCE                            | 30 |

| 3.1 Introduction                                              | 30 |

| 3.2 Gate Driver Considerations                                | 30 |

| 3.3 Conventional Voltage-Mode Gate Driver                     | 32 |

| 3.4 Current-Mode Gate Driver                                  | 44 |

| 3.3 Multi-Level Gate Driver                                   | 50 |

| 3.3.1 Methodology of Multi-Level Gate Driver                  | 51 |

| 3.5 Conclusion                                                | 55 |

| 3.6 References                                                | 56 |

| Chapter 4                                          | 58  |

|----------------------------------------------------|-----|

| Comparison of the Drivers                          | 58  |

| 4.1 Introduction                                   | 58  |

| 4.2 Comparison                                     | 58  |

| 4.2.1 The Conventional Voltage-Mode Driver         | 58  |

| 4.2.2 The Current-Mode Driver                      | 61  |

| 4.2.3 The Multi-Level Voltage-Mode Driver          | 64  |

| 4.2.4 Comparison of the Drivers                    | 66  |

| 4.3 Simulated Results                              | 76  |

| 4.5 Conclusion                                     | 86  |

| 4.6 References                                     | 86  |

| Chapter 5                                          | 88  |

| Test Setup and Experimental Results                | 88  |

| 5.1 Introduction                                   | 88  |

| 5.2 Test Setup                                     | 89  |

| 5.2.1 Measurements                                 | 89  |

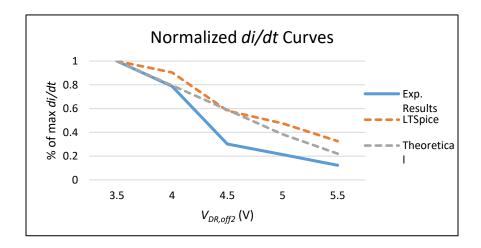

| 5.2.2 Board Layout                                 | 90  |

| 5.2 Experimental Results                           | 92  |

| 5.2.1 Test parameters                              | 92  |

| 5.2.2 Gate driver design                           | 94  |

| 5.3 Experimental Results                           | 96  |

| 5.4 Conclusion                                     | 104 |

| 5.5 References                                     | 105 |

| Chapter 6                                          | 106 |

| CONCLUSIONS AND RECOMMENDATION FOR FUTURE WORK     | 106 |

| 6.1 Summary and Conclusions                        | 106 |

| 6.2 Recommendations                                | 109 |

| 6.3 References                                     | 110 |

| Appendix A                                         | 112 |

| MATLAB™ Code for Gate Driver Analytical Comparison | 112 |

| Appendix B                                         | 119 |

| ANSYS Q3D Extraction tool                          | 119 |

## LIST OF FIGURES

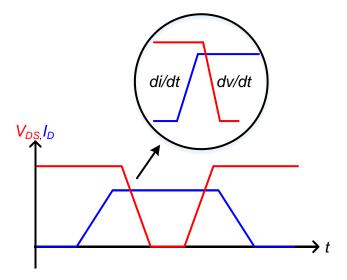

| Figure 1.1. $dv/dt$ and $di/dt$ of a semiconductor device.                              | 2  |

|-----------------------------------------------------------------------------------------|----|

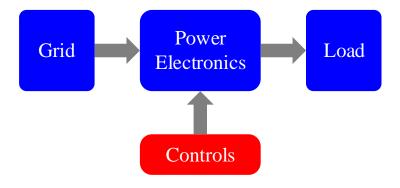

| Figure 1.2. Power electronics as interfaces.                                            | 3  |

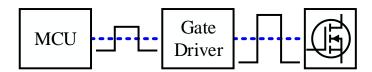

| Figure 1.3. Gate driver signaling.                                                      | 3  |

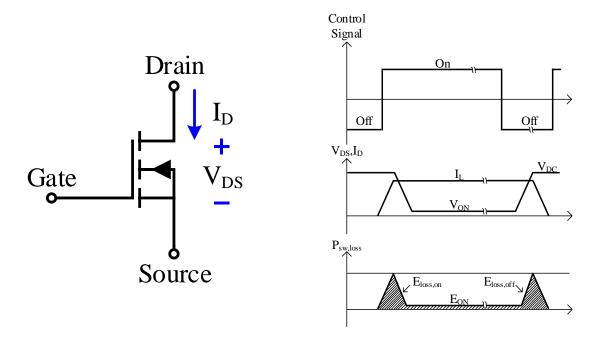

| Figure 1.4. MOSFET switching waveforms.                                                 | 4  |

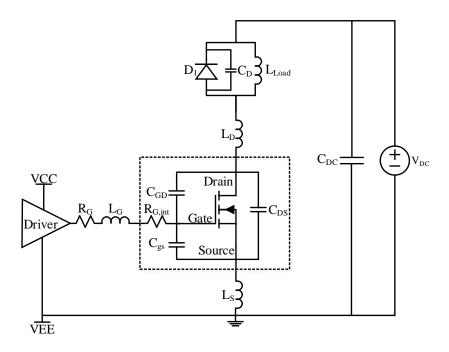

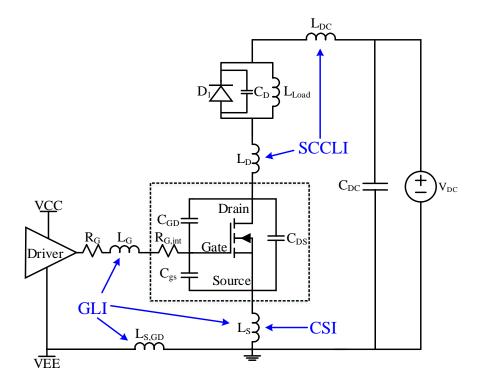

| Figure 1.5. Parasitic model of a MOSFET switching circuit with a clamped inductive load | 9  |

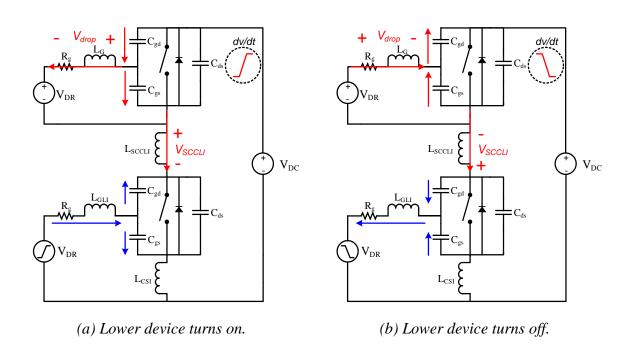

| Figure 2.1. Crosstalk of two devices in a phase leg.                                    | 18 |

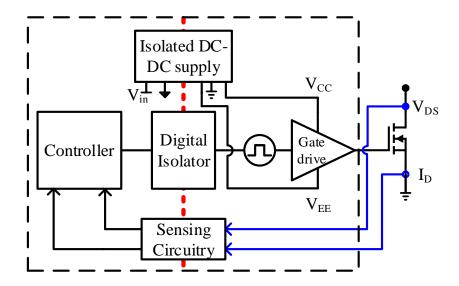

| Figure 2.2. Gate driver and isolation barriers.                                         | 20 |

| Figure 2.3. Common-mode current through isolation barriers.                             | 21 |

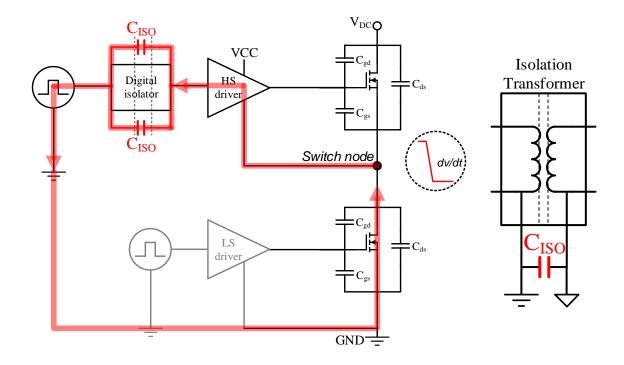

| Figure 2.4. Parasitic components surrounding the SiC MOSFET.                            | 23 |

| Figure 2.5. Failed SiC MOSFET due to short circuit.                                     | 24 |

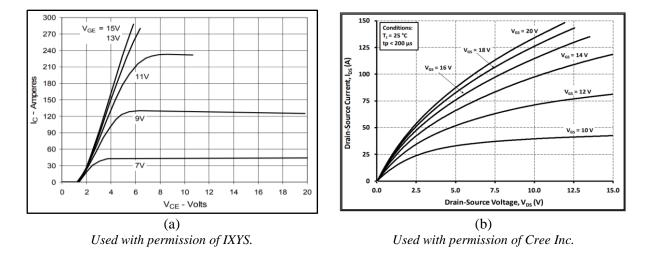

| Figure 2.6. (a) Si IGBT vs. (b) SiC MOSFET i-v characteristics [15, 16]                 | 25 |

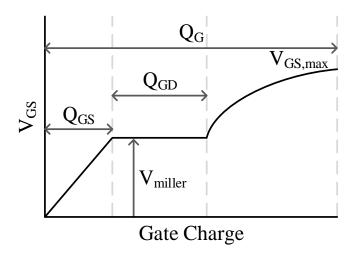

| Figure 3.1. Gate charge plot.                                                           | 31 |

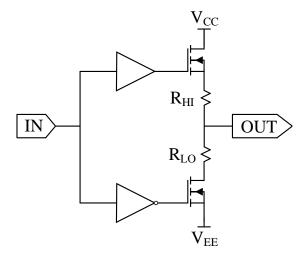

| Figure 3.2. NFET totem-pole buffer.                                                     | 33 |

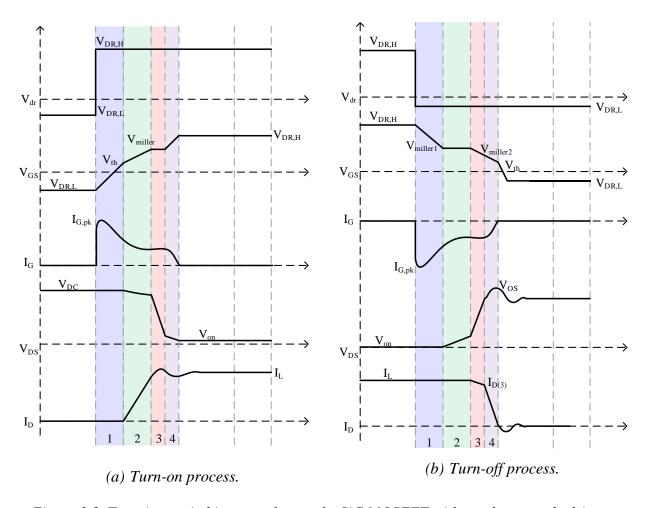

| Figure 3.3. Transient switching waveforms of a SiC MOSFET with a voltage-mode driver    | 34 |

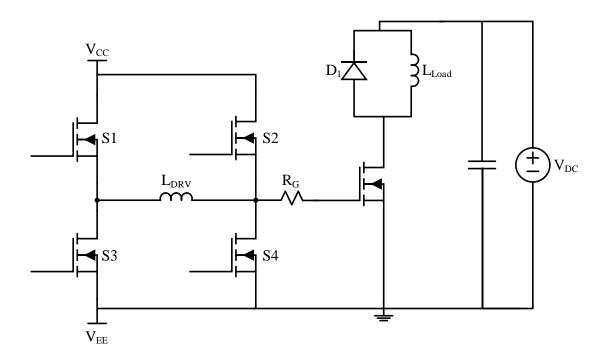

| Figure 3.4. Turn-on and turn-off current paths of voltage-mode driver.                  | 39 |

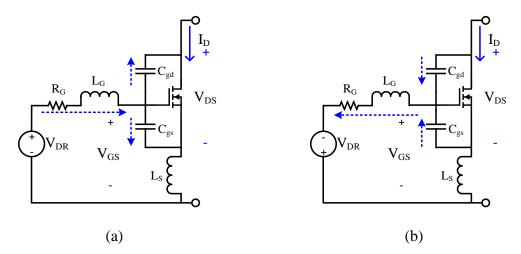

| Figure 3.5. Transient switching waveforms of a SiC MOSFET with a current-mode driver    | 44 |

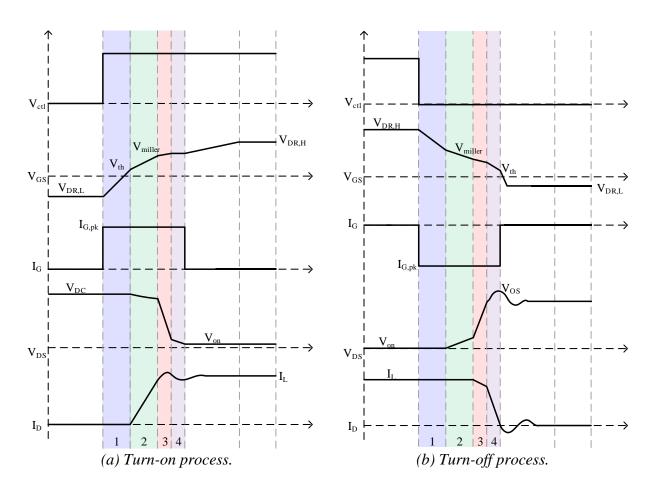

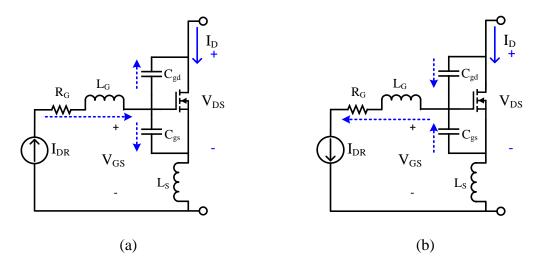

| Figure 3.6. Turn-on and turn-off current paths of current-mode driver                   | 48 |

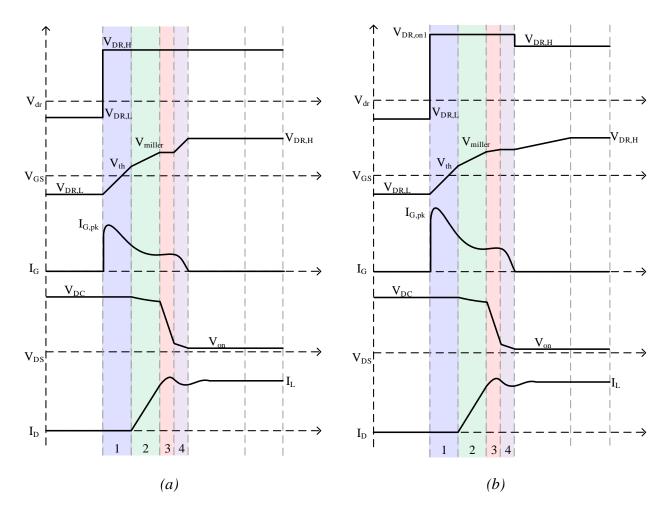

| Figure 3.7. Transient waveforms for (a) conventional turn-on versus (b) ML turn-on      | 52 |

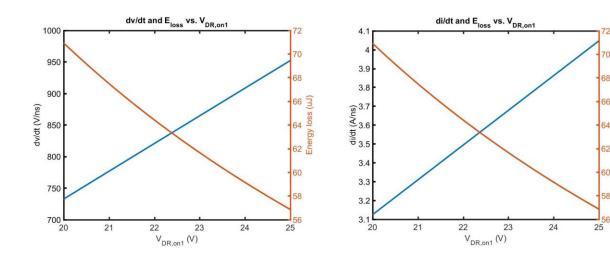

| Figure 3.8. $dv/dt$ and $E_{loss}$ versus $V_{DR,on1}$ .                                | 53 |

| Figure 3.9. $di/dt$ and $E_{loss}$ versus $V_{DR,on1}$ .                                | 53 |

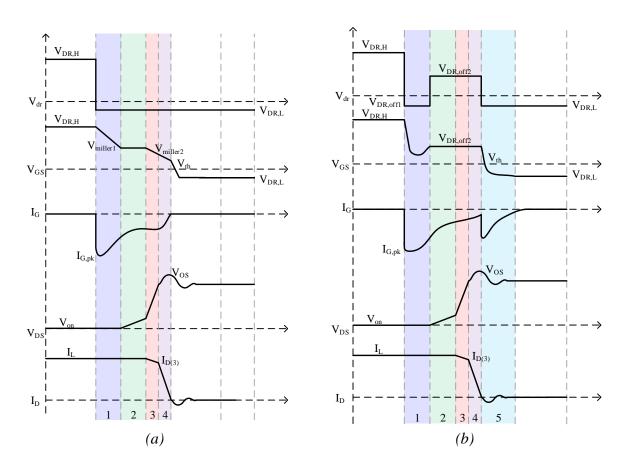

| Figure 3.10. Transient waveforms for (a) conventional turn-off versus (b) ML turn-off   | 54 |

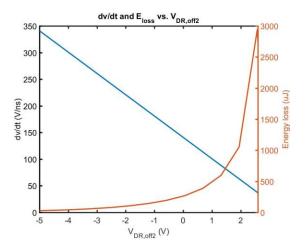

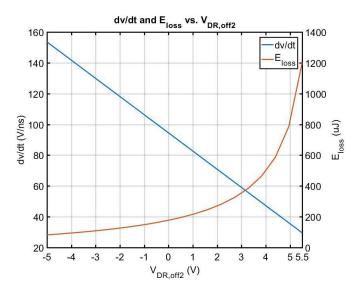

| Figure 3.11. $dv/dt$ and $E_{loss}$ versus $V_{DR,off2}$ .                              | 55 |

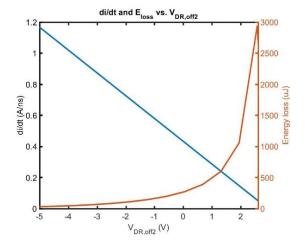

| Figure 3.12. $di/dt$ and $E_{loss}$ versus $V_{DR,off2}$ .                              | 55 |

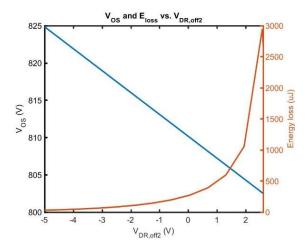

| Figure 3.13. $V_{OS}$ and $E_{loss}$ versus $V_{DR,off2}$ .                             | 55 |

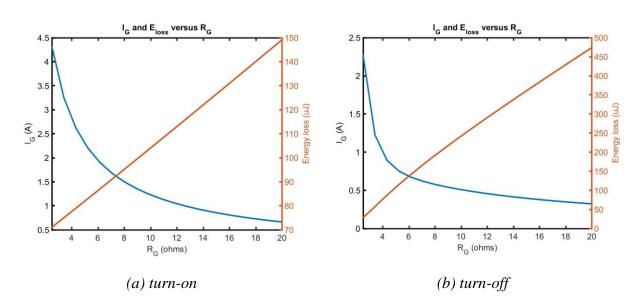

| Figure 4.1. $R_G$ influence on $I_G$ and $E_{loss}$ .                                   | 59 |

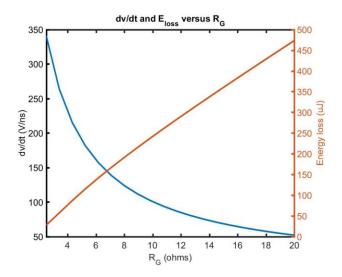

| Figure 4.2. $R_G$ influence on $dv/dt$ and $E_{loss}$ at turn-off.                      | 60 |

| Figure 4.3. Current-source driver based on inductor [1].                                | 61 |

| Figure 4.4. Current routes for current-mode driver [1]                                  | 62 |

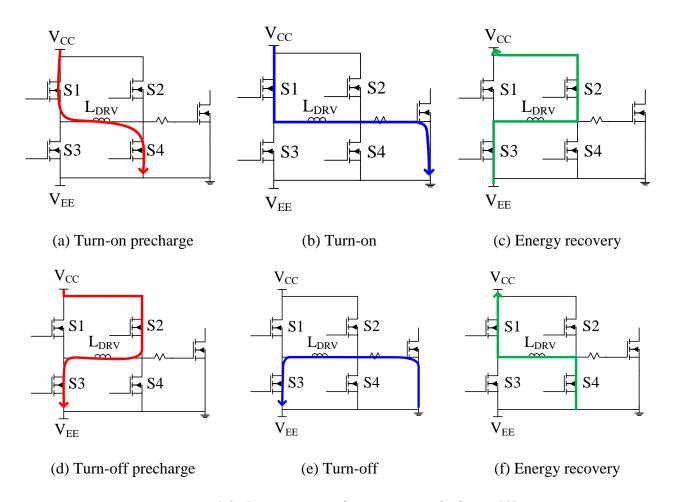

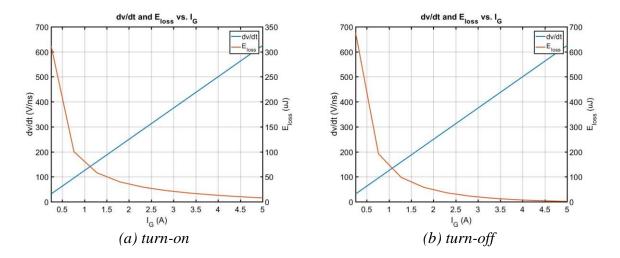

| Figure 4.5. $I_G$ influence on $dv/dt$ and $E_{loss}$ .                                 | 63 |

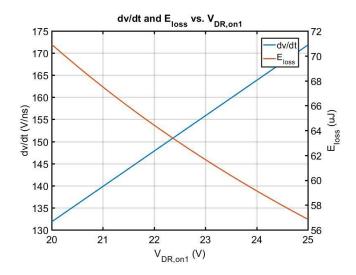

| Figure 4.6. $V_{DR,on1}$ influence on $dv/dt$ and $E_{loss}$ .                          | 65 |

| Figure 4.7. $V_{DR,off2}$ influence on $dv/dt$ and $E_{loss}$ during turn-off.          | 65 |

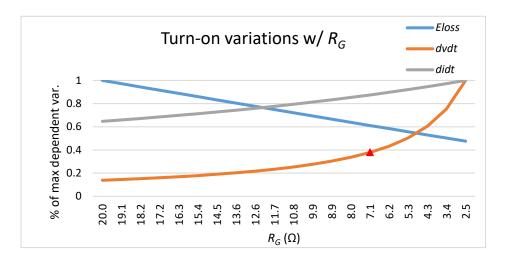

| Figure 4.8. Turn-on variations dependent on $R_G$ .                                     | 68 |

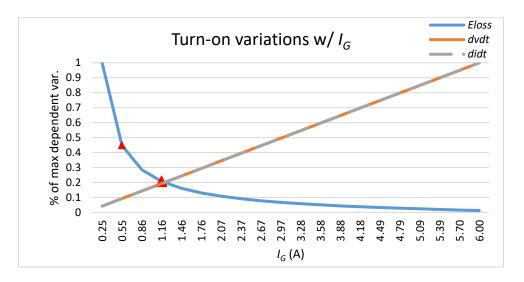

| Figure 4.9. Turn-on variations dependent on $I_C$                                       | 69 |

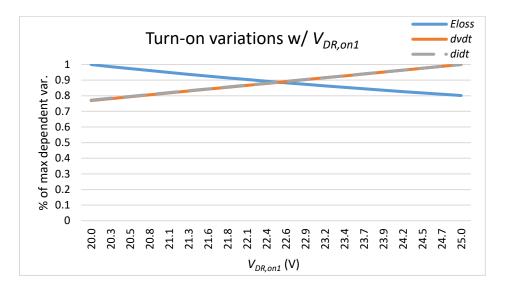

| Figure 4.10. Turn-on variations dependent on $V_{DR,on1}$ .                              | 70  |

|------------------------------------------------------------------------------------------|-----|

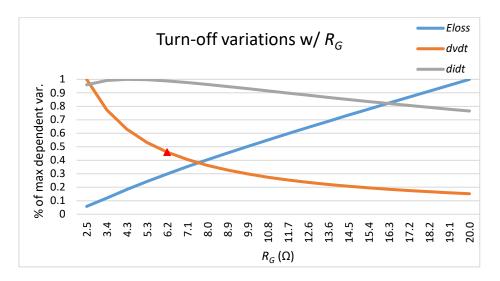

| Figure 4.11. Turn-off variations dependent on $R_G$ .                                    | 71  |

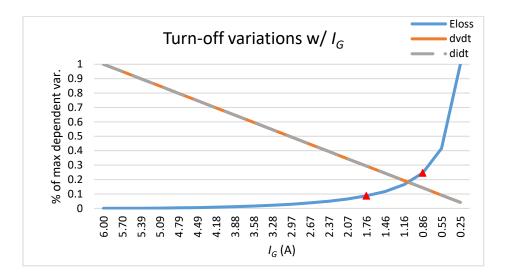

| Figure 4.12. Turn-off variations dependent on $I_G$ .                                    | 72  |

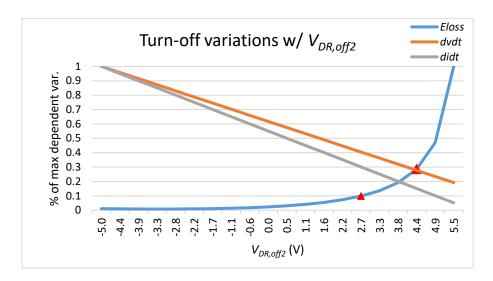

| Figure 4.13. Turn-off variations dependent on $V_{DR,off2}$ .                            | 73  |

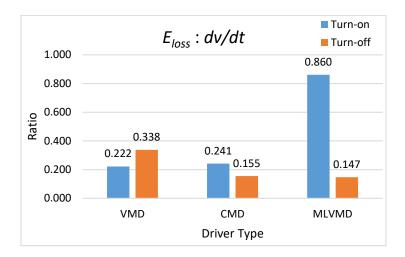

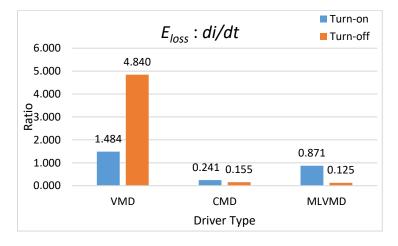

| Figure 4.14. <i>E<sub>loss</sub>:dv/dt</i> ratio comparison.                             | 74  |

| Figure 4.15. <i>E<sub>loss</sub>:di/dt</i> ratio comparison.                             | 74  |

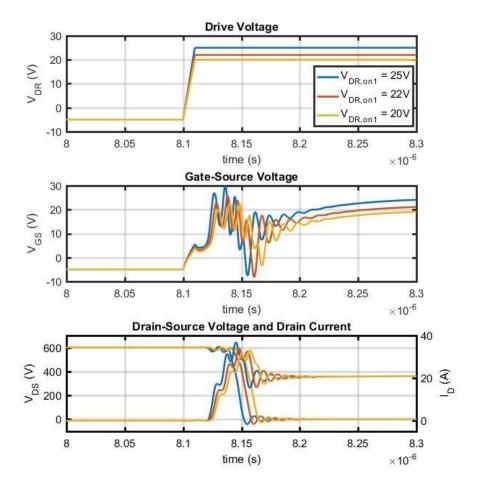

| Figure 4.16. $V_{DR}$ , $V_{GS}$ , $V_{DS}$ and $I_D$ using ML turn-on.                  | 78  |

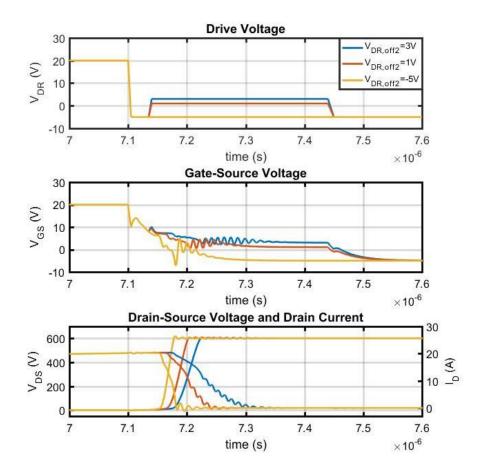

| Figure 4.17. $V_{DR}$ , $V_{GS}$ , $V_{DS}$ and $I_D$ for ML turn-off                    | 79  |

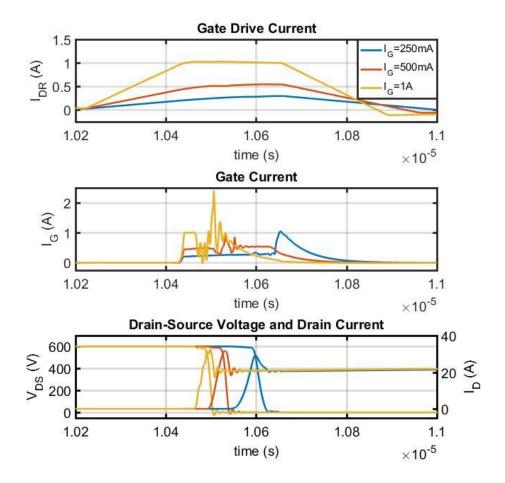

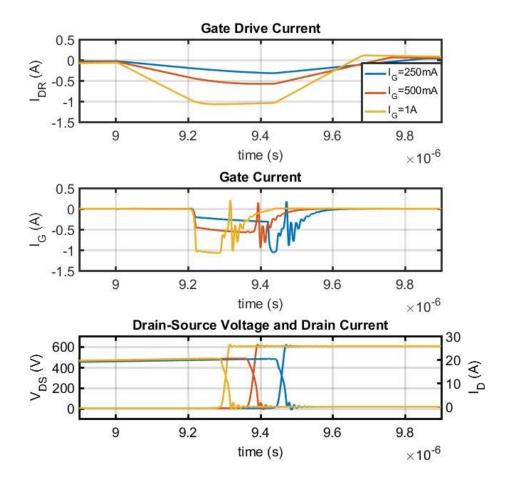

| Figure 4.18. Current-mode driver at turn-on.                                             | 80  |

| Figure 4.19. Current-mode driver at turn-off.                                            | 81  |

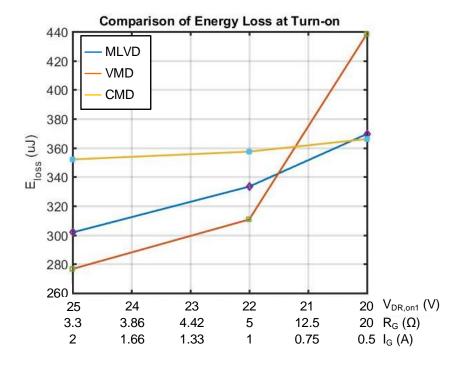

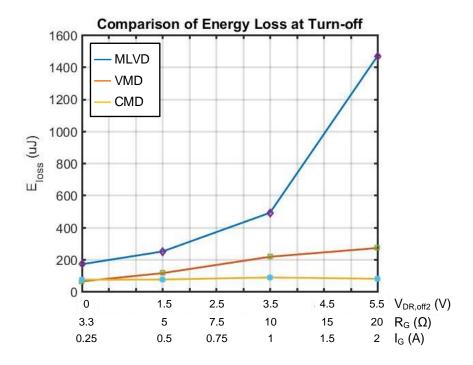

| Figure 4.20. Comparison of $E_{loss}$ at turn-on.                                        | 82  |

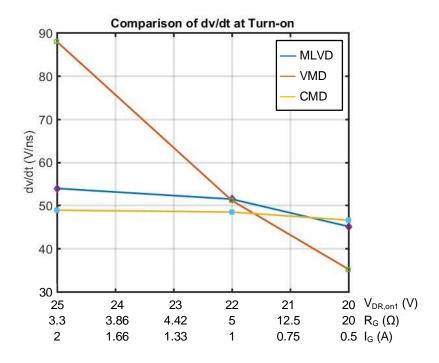

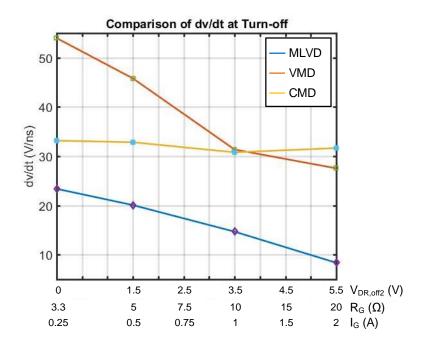

| Figure 4.21. Comparison of <i>dv/dt</i> at turn-on.                                      | 83  |

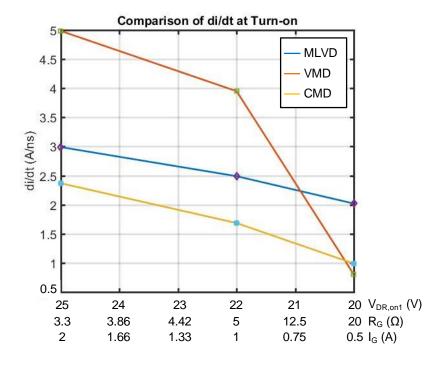

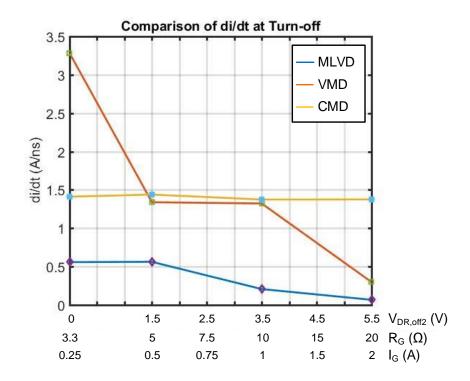

| Figure 4.22. Comparison of <i>di/dt</i> at turn-on.                                      | 83  |

| Figure 4.23. Comparison of $E_{loss}$ at turn-off.                                       | 84  |

| Figure 4.24. Comparison of <i>dv/dt</i> at turn-off.                                     | 84  |

| Figure 4.25. Comparison of <i>di/dt</i> at turn-off.                                     | 85  |

| Figure 5.1. Pearson current monitor and coaxial shunt current viewing resistor           | 90  |

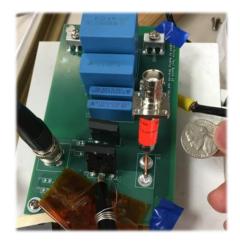

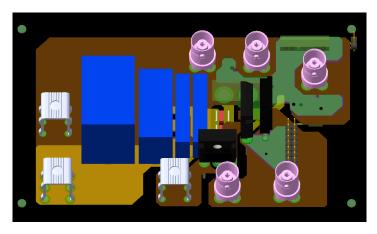

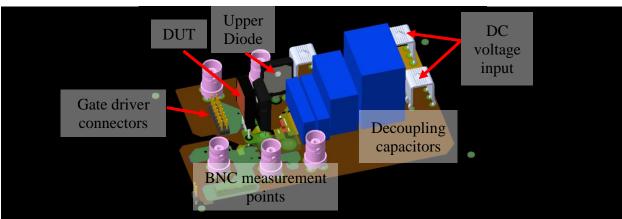

| Figure 5.2. DPT experiment boards.                                                       | 91  |

| Figure 5.3. 3D Rendering of optimized DPT board                                          | 92  |

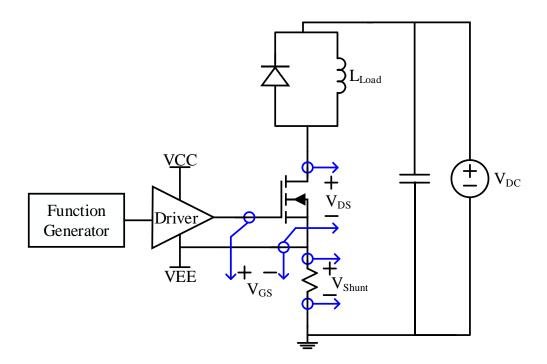

| Figure 5.4. Double Pulse Test (DPT) circuit and measurement points.                      | 93  |

| Figure 5.5. ML gate driver board.                                                        | 95  |

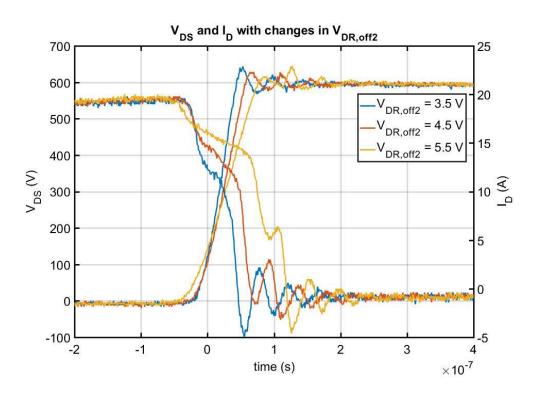

| Figure 5.6. Experimental results where $V_{DC}$ =600 V, $I_L$ =20A.                      | 96  |

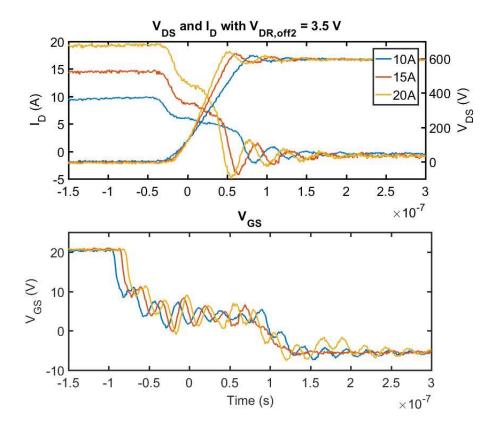

| Figure 5.7. $V_{DS}$ , $I_D$ and $V_{GS}$ vs. changes in $I_L$ when $V_{DR,off2}$ =3.5 V | 97  |

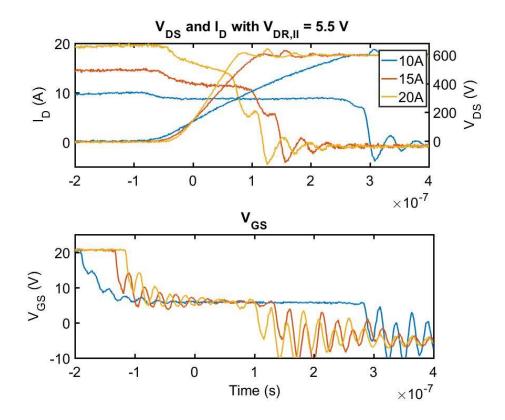

| Figure 5.8. $V_{DS}$ , $I_D$ and $V_{GS}$ vs. changes in $I_D$ when $V_{DR,off2}$ =5.5 V | 98  |

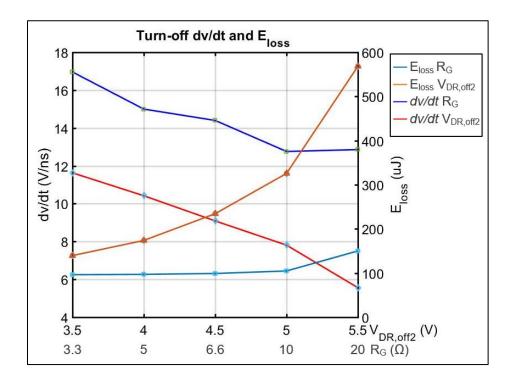

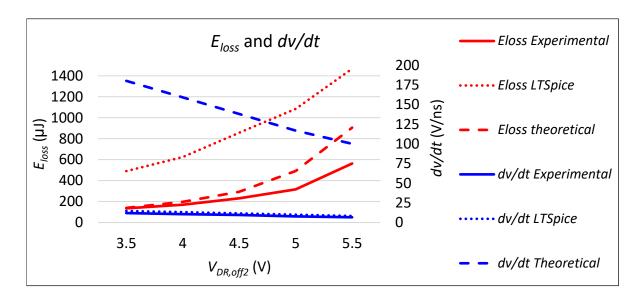

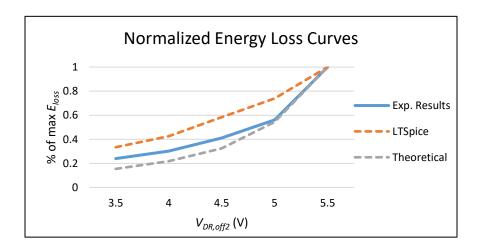

| Figure 5.9. $dv/dt$ and $E_{loss}$ vs. $V_{DR,off2}$ when $V_{DC}$ =600 V, $I_L$ =20 A.  | 99  |

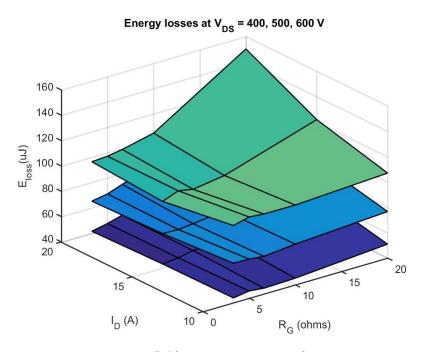

| Figure 5.10. $E_{loss}$ versus $I_D$ and $R_G$ .                                         | 100 |

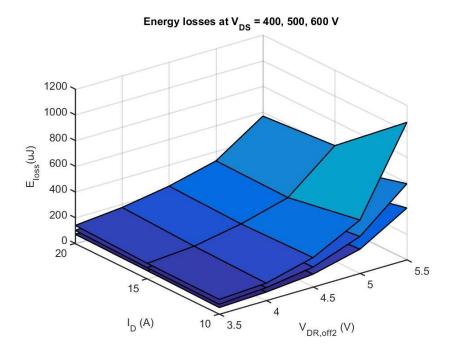

| Figure 5.11. $E_{loss}$ versus $I_D$ and $V_{DR,off2}$ .                                 | 100 |

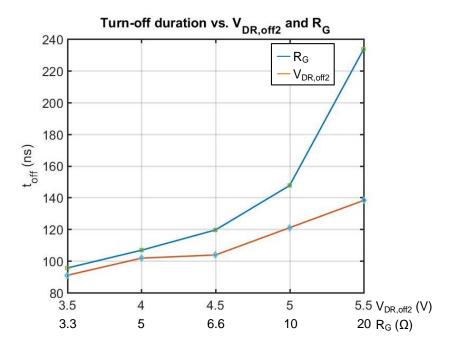

| Figure 5.12. Turn-off duration comparison.                                               | 101 |

| Figure 5.13. $E_{loss}$ and $dv/dt$ comparison of results.                               | 102 |

| Figure 5.14. Experimental, LTpice and theoretical results comparison of $E_{loss}$       | 102 |

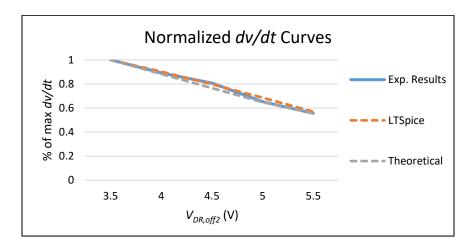

| Figure 5.16. Experimental, LTSpice and theoretical results comparison of <i>di/dt</i>    | 103 |

| Figure 5.15. Experimental, LTSpice and theoretical results comparison of $dv/dt$         | 103 |

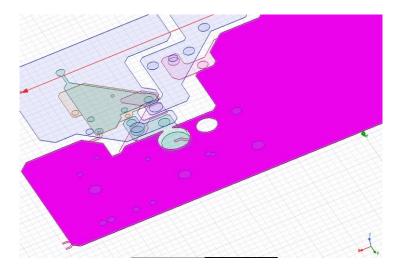

| Figure B.1. PCB Layout in Cadence Allegro                                                | 119 |

| Figure B.2. Export the .dxf file                                                         | 120 |

|                                                                                          |     |

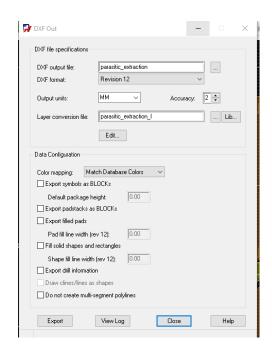

| Figure B.3. Setup of DXF export                                   | 120 |

|-------------------------------------------------------------------|-----|

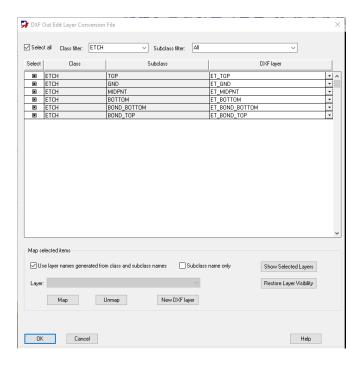

| Figure B.4. Output of DXF files by layer                          | 120 |

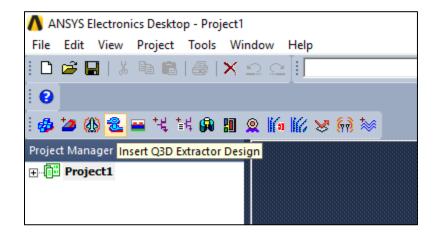

| Figure B.5. Insert a Q3D design                                   | 121 |

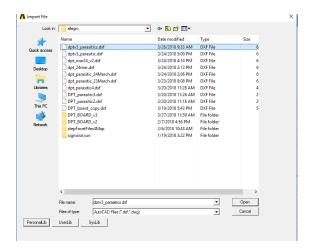

| Figure B.6. Selecting the .dxf file                               | 121 |

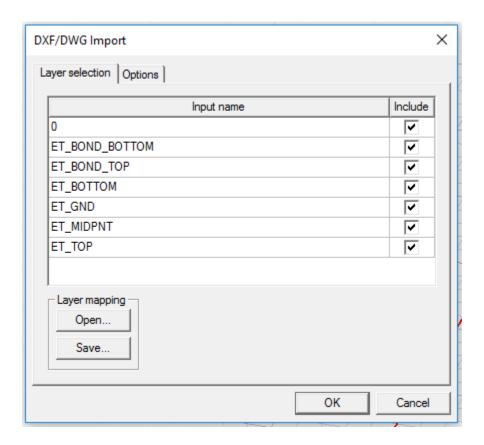

| Figure B.7. Selecting the PCB layers from the .dxf file           | 122 |

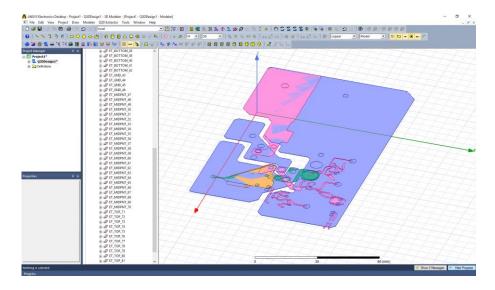

| Figure B.8. Selecting the PCB layers in ANSYS Q3D                 | 123 |

| Figure B.9. Cross section editor in Allegro PCB Editor            | 123 |

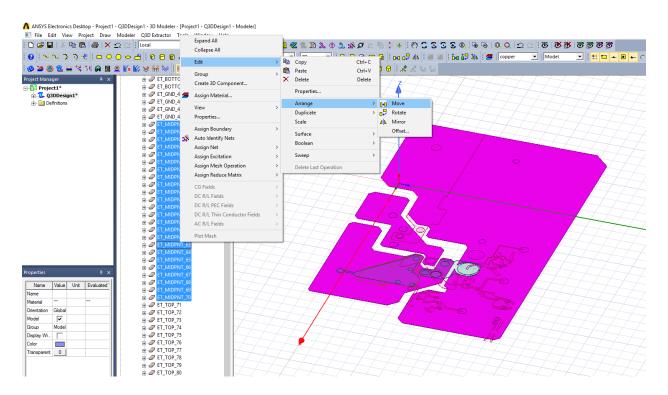

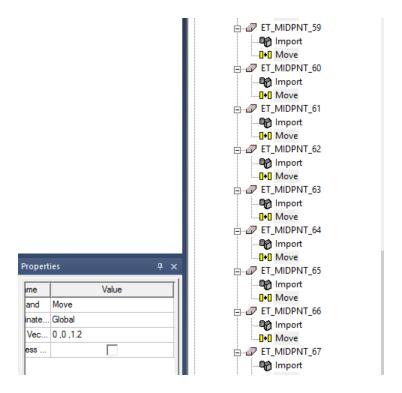

| Figure B.10. Moving layers in the z-direction                     | 124 |

| Figure B.11. Editing the move option                              | 125 |

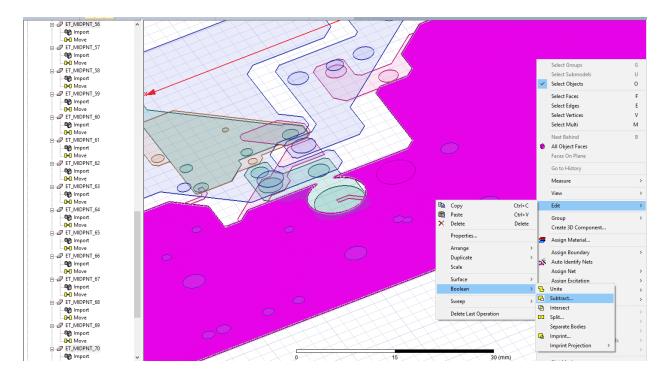

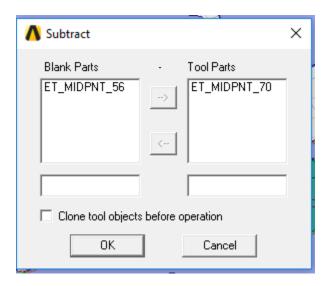

| Figure B.12. Using the Boolean function to generate holes/cutouts | 126 |

| Figure B.13. Using the Boolean subtract edit                      | 126 |

| Figure B.14. Hole generated from Boolean subtract edit            | 127 |

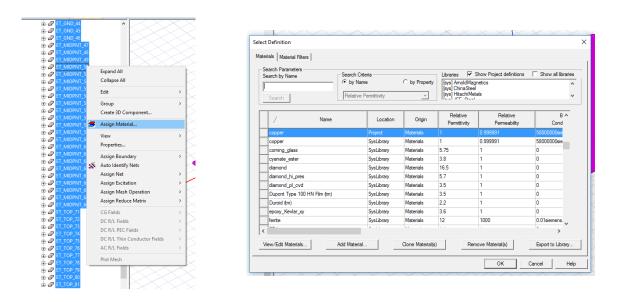

| Figure B. 15. Setting the material properties for the layers      | 127 |

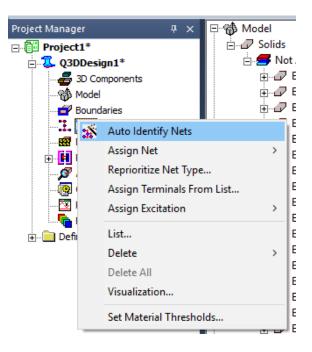

| Figure B.16. Auto identifying nets of the copper layers           | 128 |

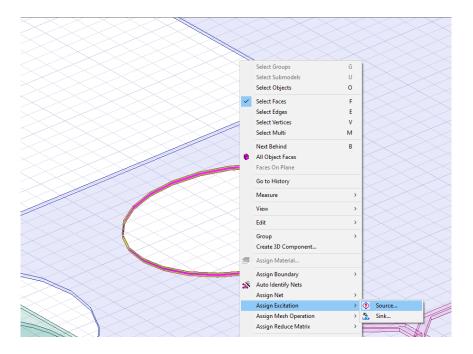

| Figure B.17. Setting a 'Source' at the surface of the hole        | 129 |

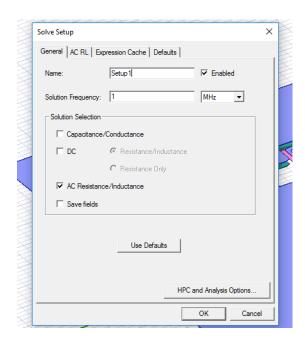

| Figure B.18. Solver setup window                                  | 130 |

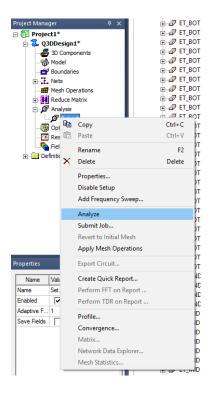

| Figure B.19. Performing the analysis                              | 131 |

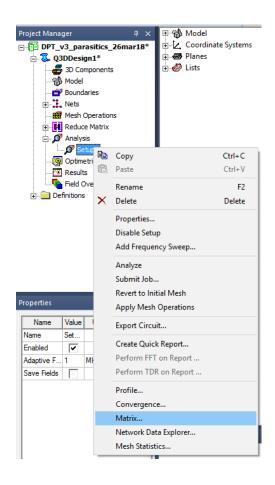

| Figure B.20. Viewing the solution matrix                          | 132 |

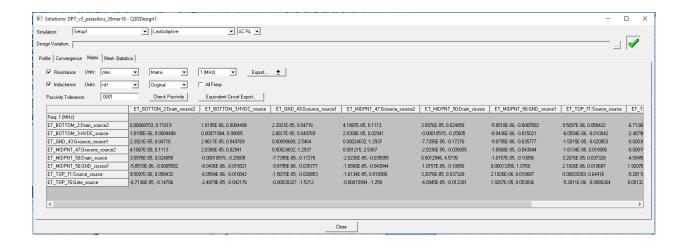

| Figure B.21. The solution matrix with R/L values                  | 132 |

|                                                                   |     |

## LIST OF TABLES

| Table 1.1. Comparison of SiC and Si power devices [1, 7]                | 5  |

|-------------------------------------------------------------------------|----|

| Table 3.1. ML gate driver terminology.                                  | 51 |

| Table 4.1. Effects of gating method on $E_{loss}$ , $dv/dt$ and $di/dt$ | 67 |

| Table 4.2. Turn-on dependence on $R_G$ .                                | 68 |

| Table 4.3. Turn-on dependence on $I_G$ .                                | 69 |

| Table 4.4. Turn-on dependence on $V_{DR,on1}$                           | 70 |

| Table 4.5. Turn-off dependence on $R_G$ .                               | 71 |

| Table 4.6. Turn-off dependence on $I_G$ .                               | 72 |

| Table 4.7. Turn-off dependence on $V_{DR,off2}$ .                       | 73 |

| Table 4.8. Comparison of optimal operating points for each driver       | 75 |

| Table 4.9. Simulation parameters.                                       | 77 |

| Table 4.10. Turn-on comparison of voltage-mode drivers.                 | 78 |

| Table 4.11. Turn-off comparison of voltage-mode drivers                 | 79 |

| Table 4.12. Current-mode driver simulated results.                      | 81 |

| Table 5.1. Test parameters.                                             | 93 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation for this Research

Silicon Carbide (SiC) power semiconductor devices are quickly gaining interest due to the many benefits they provide, enabling higher power density and efficiency. From a materials standpoint, SiC devices are set apart due to their properties as a wide bandgap semiconductor, referring to the distance between the valence and conduction bands. Using this material in a power device enables operation at high voltages, temperatures and frequency. SiC MOSFETs are available on the market in voltages ranging from 900 V to 1700 V [1, 2], and devices in the range of 10 kV to 15 kV have been fabricated and characterized in the literature [3, 4, 5]. Through the use of these devices, medium-voltage (MV) converters may become smaller because fewer devices are required. Additionally, the overall size of the converter can be further reduced by switching at higher frequencies resulting in smaller passive components.

SiC power devices provide many system-level benefits for a variety of applications. However, due to adverse side-effects, which were not previously a concern for power electronics designers, their implementation has to be carefully considered to mitigate those side-effects. For example, SiC devices can switch faster than any other device of its power class, defined by its dv/dt and di/dt, as shown in Figure 1.1, where dv/dt is the change in drain-source voltage and di/dt is the change in drain current. However, with voltage transitions up to, and exceeding, 80 V/ns, common-mode noise and failure of control circuitry can result [5]. The drain current transitions, or di/dt, are also very high, and result in voltage overshoot and resonant effects that can overstress the device or inhibit its performance.

Figure 1.1. dv/dt and di/dt of a semiconductor device.

As shown in Figure 1.1, the dv/dt of the device is proportional to the voltage level and rise or fall times. This means as higher voltage devices become available, the dv/dt problem will be even more excessive. The impact of the di/dt is dependent on the parasitic inductances of the circuit, which can be moderated, but are unavoidable. To reduce detrimental effects due to parasitics, alternate device packaging techniques and board layout optimization have been employed. These solutions require additional design time and resources to implement, and can unnecessarily increase the complexity of the system. Thus, it is the goal of this thesis to provide solutions from the perspective of the gate driver. The optimization of performance and mitigation techniques is a key factor in the determination of the best gate driver for a specific application. This introduction discusses the benefits of SiC power devices to provide an understanding of why these devices are desirable, and why the gate driver is of significant importance in the converter design.

Figure 1.2. Power electronics as interfaces.

## 1.1.1 Power Semiconductor Devices

Power electronics circuits enable the conversion of power from one form to another in a variety of applications, ranging from electric vehicles to energy storage for the home. The grid is used to distribute power to loads ranging from residential to commercial, requiring either ac or dc power with various specifications. Thus, one of the main purposes of power electronics is to serve as the interface between the grid power and the end equipment, as shown in Figure 1.2.

These power electronics systems come in a variety of forms with regards to circuit topology and controls. Switch mode power converters are used in many applications to provide maximum control over the conversion process through the use of power semiconductor devices. These devices are the controllable switches that allow the designer to optimize the performance of the converter based on the switching scheme. The gate driver serves as the main interface between the

Figure 1.3. Gate driver signaling.

Figure 1.4. MOSFET switching waveforms.

designer's control algorithm and the switching device itself. As shown in Figure 1.3, the gate driver receives a control signal from the microcontroller unit (MCU) and converts it into a signal powerful enough to drive the semiconductor device, a MOSFET in this case.

There are a variety of gate drivers available on the market, all with the single goal of driving the power device. These drivers vary in drive strengths, protection functions, and other features. The selection of the gate driver is dependent on the power device being driven, and must provide sufficient drive strength to reduce the switching losses of the device. Figure 1.4 describes the basic switching process of a MOSFET and the consequence of power and energy losses.

When the signal is high, the device begins to conduct, and the drain current,  $I_D$ , rises while the drain-source voltage,  $V_{DS}$ , falls. During the on-state,  $V_{DS}$  will be close to 0 V and  $I_D$  will be at the maximum load current value. When the control signal is low the device becomes an open-circuit, and  $V_{DS}$  rises to the maximum voltage and  $I_D$  falls to 0 A. The switching power losses,

$P_{sw,loss}$ , are an unavoidable consequence of switching a power device under hard-switching conditions. In an ideal case, the control signal has an infinite slope, resulting in the fast transition of the voltage across the device and current through the device. This is not physically realized due to various parasitic components affecting the speed of the driving signal, contributing more to the switching power losses shown in Figure 1.4. These losses translate into energy losses over time, which is the area under the waveform of  $P_{sw,loss}$ . The total switching losses of a particular converter are proportional to these energy losses,  $E_{sw,loss}$ , and the switching frequency. Fortunately, in recent years, WBG devices have been developed and provide switching performance as close to the ideal case than ever before. These devices switch at very fast rates, have lower conduction losses ( $E_{ON}$ ), and have high breakdown voltages. Additionally, these devices have large thermal conductivity, allowing them to operate at higher temperatures. Comparisons of some of the main WBG devices versus Si devices can be found in [6]. Table 1.1 shows a comparison of some key characteristics.

*Table 1.1. Comparison of SiC and Si power devices [1, 7].*

| Type                                                                                                            | SiC MOSFET |             |       | Si BiMOSFET |            |        |       |        |

|-----------------------------------------------------------------------------------------------------------------|------------|-------------|-------|-------------|------------|--------|-------|--------|

| Manufacturer                                                                                                    |            | CREE        |       |             | IXYS       |        |       |        |

| Part #                                                                                                          |            | C2M0045170D |       |             | IXBH42N170 |        |       |        |

| Voltage                                                                                                         | 1700 V     |             |       | 1700 V      |            |        |       |        |

| $Max T_j$                                                                                                       |            | 150 °C      |       |             | 150 °C     |        |       |        |

| Current (25 °C)                                                                                                 |            | 72 A        |       |             | 80 A       |        |       |        |

| V <sub>DS(on)</sub> or V <sub>CE(sat)</sub>                                                                     |            | ~2 V        |       |             | 2.7 V      |        |       |        |

| $V_{\mathrm{F}}$                                                                                                |            | 4.1 V       |       |             | 2.8 V      |        |       |        |

| Internal Gate Resistance (R <sub>G,int</sub> )                                                                  | 1.3 Ω      |             |       | N/A         |            |        |       |        |

| Total Gate Charge                                                                                               | 188 nC     |             |       | 188 nC      |            |        |       |        |

| $\begin{array}{ c c c c c c }\hline t_{rise} & t_{fall} & t_{delay(on)} & t_{delay(off)} \\ \hline \end{array}$ | 20 ns      | 18 ns       | 65 ns | 48 ns       | 188 ns     | 740 ns | 36 ns | 330 ns |

As shown in the table, one advantage that the SiC device has over the Si device is the switching speed, having a turn-off time 41 times smaller. This results in lower energy losses, i.e. total switching losses. Additionally, the conduction losses for the SiC MOSFET are smaller, as it has a smaller on-state voltage versus the Si device's saturation voltage.

## 1.1.2 Applications for Wide-Band-Gap Power Devices

There are many power electronics systems that can benefit from the performance provided by SiC MOSFETs. For example, in hybrid electric vehicles (HEVs), both the inverter and the dc/dc converter operate in elevated temperatures, so the switching devices must be effective at these temperatures and have low on-resistance to reduce losses [8]. In [9], a comparison of dc/dc converters using Si versus SiC devices showed that the converter with SiC devices operating at 150 kHz still achieved higher efficiency than the Si converter at 20 kHz. That is a substantial achievement because switching losses increase linearly with the switching frequency, thus this demonstrates the exceptional benefits of SiC devices. The increase of frequency resulted in smaller passive components, such as the dc capacitor and choke inductor, reducing the total system volume and weight. Another challenge associated with vehicular converters is thermal management, and its contribution to the system's size and weight. Thus, it was shown that a 55 kW traction inverter drive using SiC devices allowed for the use of air cooling to significantly reduce the price in comparison to a liquid cooling system, all while maintaining similar size to that of the Si converter [10].

The Modular Multilevel Converter (MMC) is also a prime candidate for the utilization of high-voltage SiC devices [11]. The size and control complexity can be reduced by using fewer devices to achieve the high-voltage connection to the grid. It is expected that the losses will be reduced by using these devices, as opposed to Si. Using the MMC, battery energy storage can be

connected to the grid to enable additional energy in the case of grid failure or misoperation and provides the interface to recharge the batteries. With devices such as SiC MOSFETs that can operate at high voltage and high switching frequencies, the bulky 60 Hz line transformer can be replaced with a high-frequency transformer for galvanic isolation, reducing the size of the overall system. However, there are challenges with this implementation to ensure reliable operation of the SiC devices due to the complexity of the circuit and control. As will be discussed later, these challenges are made even more problematic because of SiC's very low short-circuit withstand time (SCWT), as compared to Si IGBTs.

Devices of lower switching speeds have typically been used in medium-voltage (MV) applications. These devices, such as gate turn-off thyristors (GTOs) and integrated gate-commutated thyristors (IGCTs), have high breakdown voltages at which the Si IGBT cannot reach. However, there is potential for SiC in these grid and utility applications due to the development of devices with 10 kV and 15 kV blocking voltages and fast switching speeds. For example, a solid-state transformer (SST) and grid-tied converter design utilizing 10 kV SiC MOSFETs is presented in [12]. The development of these converters are primarily focused on reducing the size of the typical 60 Hz transformer and increasing the efficiency while maintaining the galvanic isolation between the grid and distribution voltages. This converter includes the front-end converter (FEC), the dual active bridge (DAB), and low-voltage side converters. The FEC is connected to the 3-phase, 13.8 kV distribution grid, providing a voltage of 22 kV to the input of the DAB, generating a voltage of 11 kV across each device with an efficiency of 98% [12].

Such research shows the remarkable benefits that make SiC devices suitable for these hightemperature and high-voltage systems, yet, they are still not utilized widely in industry. The challenges associated with SiC devices have prevented their immediate adoption into industry applications, but various solutions are being investigated throughout both industry and academia. Some of the main challenges are briefly described in the next section.

## 1.1.3 Challenges of Implementing SiC MOSFETs

Along with the many benefits associated with SiC power devices are some significant challenges that designers must anticipate. In an ideal case, SiC devices could be directly interchanged with their Si counterparts with the same control scheme and circuitry, with only the positive performance of SiC altering the system; however, this is not the case. This section serves as an introduction to some of the main challenges that come with using SiC MOSFETs.

There are many consequences due to the fast switching speeds of SiC, i.e. large dv/dt and di/dt. The parasitic circuit components, both inductive and capacitive, interact with these transitions and result in undesired voltages and currents derived from the following relationships:

$$V_{ind} = L * \frac{di}{dt} \tag{1}$$

and

$$I_{cap} = C * \frac{dv}{dt} \tag{2}$$

The parasitic inductances, as shown in Figure 1.5, include the internal device inductance from bond wires and the trace inductance of the circuit. These gate, source, and drain inductances  $(L_G, L_S, \text{ and } L_D)$  will cause reduced driver strength and voltage spikes across the device.

Figure 1.5. Parasitic model of a MOSFET switching circuit with a clamped inductive load.

The main capacitive elements of the circuit include the internal capacitors of the MOSFET,  $C_{GD}$ ,  $C_{GS}$ , and  $C_{DS}$ , which prevent the device from acting as an ideal switch. The gate-to-drain capacitor,  $C_{GD}$  (Miller capacitance) also acts as a path for current to flow through the gate, causing false turn-on or crosstalk between two devices in a phase-leg [13]. Additionally, various forms of capacitive coupling become sources for common-mode currents, such as the gate driver isolation or the coupling of a module's baseplate to its heatsink [14].

Another disadvantage of SiC devices is their ability to withstand a short-circuit event, defined as the short-circuit withstand time (SCWT). Thus, protection of SiC devices is an important aspect of the design, even more so than for Si IGBTs. As described in [15], a SiC device may only have half the SCWT time of a Si IGBT. This requires the protection circuitry to be as fast as possible in order to detect the short-circuit before a catastrophic failure. Subsequently, the device must be shut down after detection. However, if the device is turned off at its normal speed,

the *di/dt* will exceed even the normal operating speed, and will cause very large voltage overshoots, which will degrade the device.

All of these challenges are difficult to deal with at low-voltage levels, and will only escalate as the voltage-level increases. Power devices are being investigated at 10 kV and 15 kV in order to increase power density and increase efficiency and performance [3, 4, 5]. These devices cannot be integrated into the power electronics systems they are designed for unless they are properly controlled. This is why the gate driver is such an integral technology to enable industry acceptance of high-voltage SiC MOSFETs. The benefits of these devices must be balanced with their negative side-effects to make their implementation both time- and cost-effective. Thus, the main consideration of this paper is the comparison of gating methods to enable SiC device technology.

## 1.1.4 Gating methods and considerations for SiC power devices

Due to the operational differences between SiC and Si transistors, the gate driver for SiC should also be different to provide features that may not be applicable for a Si device. Relevant gate drive considerations such as rise and fall time, propagation delay, and drive power are still important for SiC gate drivers. However, other considerations must also be made for SiC with regards to the isolation of the gate drive power supply, *dv/dt* immunity, variable gate drive strength, and protection mechanisms. A variety of gate driving techniques have been proposed to address these issues. For example, the use of larger gate resistances or snubbers have been proposed to reduce high *dv/dt* transients. While this method may suffice for IGBTs, they do not provide many benefits for SiC devices. There are many ICs on the market designed to drive SiC devices, which may provide a combination of a negative drive voltage, high common-mode transient immunity (CMTI), high output current, fast desaturation protection, two-level turn-off and Miller clamping. Many of these control functions are constant, and do not change based on the device's operating

conditions. This is an essential consideration for SiC MOSFETs as parameters such as the threshold voltage, Miller plateau voltage and energy losses change with the load conditions. Thus, research of SiC gate drivers is still ongoing to evaluate these variations to achieve optimized performance.

Gate drivers for 1.2 kV, 1.7 kV, and 10 kV SiC MOSFETs were developed in [16, 17, 18] to provide sufficient isolation, high-drive strength, and fast and reliable protection. An intelligent gate driver for 10 kV and 15 kV SiC MOSFETs was developed, addressing the careful design of the isolated power supply, resulting in a coupling isolation capacitance smaller than 1 pF, and providing fast protection and constant health-monitoring of the device [19, 20, 21]. Other gate drivers have also been designed to vary the drive strength during transitions to utilize the full performance benefits of SiC and still mitigate the effects of high dv/dt. These drivers are addressing the issues related to operational variations as mentioned before, and are entitled "active" gate drivers. These drivers typically utilize feedback or a pre-determined set of controls to change the drive strength during the turn-on or turn-off process. For example, an auxiliary circuit is designed to reduce crosstalk between the upper and lower devices in a phase-leg configuration [22]. Other active gate drivers have been created to enhance the speed at certain instances, i.e. during the Miller plateau region, using a variable gate resistance to reduce switching losses [23]. Some methods control the voltage level during transition to control the slew rates and mitigate EMI [24]. A variety of other drive types have also been considered, including resonant drivers, current-mode drivers, and other methods focused on mitigating the aforementioned challenges [25].

These gate driver solutions provide methods in which to mitigate the large dv/dt, di/dt and provide protection, but there has yet to be an in-depth investigation and comparison of the drive methods for high-voltage SiC devices. Active gating is considered a crucial method for SiC due to

the many variations of parameters affected by temperature or operating conditions. This thesis investigates the effects of different types of gate driver schemes on the performance of high-voltage SiC MOSFETs with an in-depth investigation of an active gating method utilized to mitigate the effects of high dv/dt.

## 1.2 Thesis Objectives

The objective of this thesis is to provide an investigation of the main challenges associated with the implementation of SiC power devices, as well as the solutions presented from the standpoint of the gate driver. The main factors affecting gate driver design are described, and the performance based on different drive-types will be assessed. The ability of those gate drivers to mitigate the main challenges while still enabling the high-performance of SiC devices is investigated. The drivers will be compared based on the performance of the SiC MOSFET operating during hard-switching and the subsequent power consumption and complexity of the driver itself. Other considerations in the design will also be described, such as the test setup and board layout. The main objectives will be accomplished through the following analyses:

- Assessment of the system-level challenges associated with operating SiC devices

- Comparison of the operation of the gate driver-based solutions

- Analysis of the tradeoffs between dv/dt and di/dt reduction and switching loss increase

- Considerations of gate drivers for future high-voltage SiC devices

- Suggestions for the optimal drive technique for the demands of the system

### 1.3 Thesis Organization

This thesis is organized as follows: the assessment of challenges and issues associated with utilizing the SiC power devices is presented in Chapter 2. The gate driver considerations and

impact of the different types is shown in Chapter 3. Chapter 4 will show the evaluation of the methods and discuss the tradeoffs of each. Chapter 5 will describe the experimental setup and design of the proposed gate driver. Finally, Chapter 6 will present the conclusions of the work and future considerations.

### 1.4 References

- [1] CREE, "Silicon Carbide Power MOSFET C2M<sup>TM</sup> MOSFET Technology," C2M0045170D datasheet, June 2016.

- [2] CREE, "Silicon Carbide Power MOSFET C2M™ MOSFET Technology," C2M0080120D datasheet, Oct. 2015 [Rev. C].

- [3] J. Wang *et al.*, "Characterization, Modeling, and Application of 10-kV SiC MOSFET," *IEEE Trans. on Electron Devices*, vol. 55, no. 8, pp. 1798-1806, Aug. 2008.

- [4] A. Q. Huang, Q. Zhu, L. Wang and L. Zhang, "15 kV SiC MOSFET: An enabling technology for medium voltage solid state transformers," *CPSS Trans. on Power Electronics and Applications*, vol. 2, no. 2, pp. 118-130, 2017.

- [5] E. P. Eni, B. I. Incau, T. Kerekes, R. Teodorescu and S. Munk-Nielsen, "Characterisation of 10 kV 10 A SiC MOSFET," in *Proc. 2015 Intl Aegean Conference on Electrical Machines & Power Electronics (ACEMP)*, Side, TU, 2015, pp. 675-680.

- [6] P. Palmer, X. Zhang, E. Shelton, T. Zhang and J. Zhang, "An experimental comparison of GaN, SiC and Si switching power devices," in *Proc. IECON 2017 43rd Annual Conference of the IEEE Industrial Electronics Society*, Beijing, China, 2017, pp. 780-785.

- [7] IXYS, "High Voltage, High Gain BIMOSFET™ Monolithic Bipolar MOS Transistor," IXBH42N170 datasheet, Oct. 2008.

- [8] F. Shang, A. P. Arribas and M. Krishnamurthy, "A comprehensive evaluation of SiC devices in traction applications," in *Proc. 2014 IEEE Transportation Electrification Conference and Expo (ITEC)*, Dearborn, MI, 2014, pp. 1-5.

- [9] D. Han, J. Noppakunkajorn and B. Sarlioglu, "Comprehensive Efficiency, Weight, and Volume Comparison of SiC- and Si-Based Bidirectional DC–DC Converters for Hybrid Electric Vehicles," *IEEE Trans. on Vehicular Technology*, vol. 63, no. 7, pp. 3001-3010, Sept. 2014.

- [10] M. Chinthavali, J. A. Tawfik and R. V. Arimilli, "Design and analysis of a 55-kW air-cooled automotive traction drive inverter," in *Proc. 2011 IEEE Energy Conversion Congress and Exposition (ECCE)*, Phoenix, AZ, 2011, pp. 2345-2352.

- [11] J. Umuhoza, C. Farnell, H. A. Mantooth, et al., "A SiC-Based Power Electronics Interface for Integrating a Battery Energy Storage into the Medium (13.8 kV) Distribution System," in *Proc. 2018 IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antionio, TX, 2018, pp. 1023-1028.

- [12] S. Madhusoodhanan et al., "Solid-State Transformer and MV Grid Tie Applications Enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs Based Multilevel Converters," *IEEE Trans. on Industry Applications*, vol. 51, no. 4, pp. 3343-3360, July-Aug. 2015.

- [13] S. Yin *et al.*, "Gate driver optimization to mitigate shoot-through in high-speed switching SiC half bridge module," in *Proc. 2015 IEEE 11th International Conference on Power Electronics and Drive Systems*, Sydney, NSW, 2015, pp. 484-491.

- [14] N. Christensen et al., "Common mode current mitigation for medium voltage half bridge SiC modules," in *Proc. 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe)*, Warsaw, 2017, pp. P.1-P.8.

- [15] J. Rice and J. Mookken, "SiC MOSFET gate drive design considerations," in *Proc. 2015 IEEE International Workshop on Integrated Power Packaging (IWIPP)*, Chicago, IL, 2015, pp. 24-27.

- [16] C. DiMarino, W. Zhang, N. Haryani, Q. Wang, R. Burgos and D. Boroyevich, "A high-density, high-efficiency 1.2 kV SiC MOSFET module and gate drive circuit," in *Proc. 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA)*, Fayetteville, AR, 2016, pp. 47-52.

- [17] J. Wang, Z. Shen, C. DiMarino, R. Burgos and D. Boroyevich, "Gate driver design for 1.7kV SiC MOSFET module with Rogowski current sensor for shortcircuit protection," in *Proc.* 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 516-523.

- [18] C. DiMarino, J. Wang, R. Burgos and D. Boroyevich, "A high-power-density, high-speed gate driver for a 10 kV SiC MOSFET module," in *Proc. 2017 IEEE Electric Ship Technologies Symposium (ESTS)*, Arlington, VA, 2017, pp. 629-634.

- [19] K. Mainali, S. Madhusoodhanan, A. Tripathi, K. Vechalapu, A. De and S. Bhattacharya, "Design and evaluation of isolated gate driver power supply for medium voltage converter applications," in *Proc. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Long Beach, CA, 2016, pp. 1632-1639.

- [20] A. Tripathi, K. Mainali, S. Madhusoodhanan, A. Yadav, K. Vechalapu and S. Bhattacharya, "A MV intelligent gate driver for 15kV SiC IGBT and 10kV SiC MOSFET," in *Proc. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Long Beach, CA, 2016, pp. 2076-2082.

- [21] A. Kumar, A. Ravichandran, S. Singh, S. Shah and S. Bhattacharya, "An intelligent medium voltage gate driver with enhanced short circuit protection scheme for 10kV 4H-SiC

- MOSFETs," in *Proc. 2017 IEEE Energy Conversion Congress and Exposition (ECCE)*, Cincinnati, OH, 2017, pp. 2560-2566.

- [22] Z. Zhang, J. Dix, F. F. Wang, B. J. Blalock, D. Costinett and L. M. Tolbert, "Intelligent Gate Drive for Fast Switching and Crosstalk Suppression of SiC Devices," *IEEE Trans. on Power Electronics*, vol. 32, no. 12, pp. 9319-9332, Dec. 2017.

- [23] A. P. Camacho, V. Sala, H. Ghorbani and J. L. R. Martinez, "A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory," *IEEE Trans. on Industrial Electronics*, vol. 64, no. 11, pp. 9032-9042, Nov. 2017.

- [24] H. C. P. Dymond, D. Liu, J. Wang, J. J. O. Dalton and B. H. Stark, "Multi-level active gate driver for SiC MOSFETs," in *Proc. 2017 IEEE Energy Conversion Congress and Exposition (ECCE)*, Cincinnati, OH, 2017, pp. 5107-5112.

- [25] D. Peftitsis and J. Rabkowski, "Gate and Base Drivers for Silicon Carbide Power Transistors: An Overview," *IEEE Trans. on Power Electronics*, vol. 31, no. 10, pp. 7194-7213, Oct. 2016.

#### **CHAPTER 2**

#### CHALLENGES OF IMPLEMENTING SIC MOSFETS

### 2.1 Introduction

As discussed in the previous chapter, SiC MOSFETs present a variety of benefits that make them ideal for applications which operate at high voltages, temperatures, and switching frequencies. However, many challenges present themselves due to circuit and device parasitic elements, as well as variations in the operating characteristics of the device. The consequences due to interactions of *di/dt* or *dv/dt* with parasitics can be detrimental to the device, and ultimately the system. The result of these interactions are excessive stress on the device, failure of the device, increased losses, and affected control signal integrity. These issues are further divided into specific topics of research such as crosstalk, self-turn-on, common-mode currents, voltage overshoot, reduced drive strength, and protection. This chapter will investigate these challenges in detail, providing the context for the necessity of an effective gate driver for high-voltage SiC MOSFETs.

## 2.2 SiC Operating Challenges and Solutions

## 2.2.1 Crosstalk and Self-turn-on

Silicon carbide devices are known for their ability to switch at very fast speeds with high dv/dt and di/dt, resulting in smaller switching power losses and the ability to operate at higher frequencies. Unfortunately, there are unintentional effects that manifest themselves when these SiC devices switch at dv/dt rates as high as 30 kV/ $\mu$ s or higher [1]. One side-effect of high dv/dt is crosstalk, meaning the interaction between complementary devices in a phase-leg, when the switching transient of one device causes the unintentional turning-on of the opposite device. This

effect is referred to as false-turn-on, implying that the event occurred due to circuit parasitics and not as a result of a faulty control signal.

The main result of a false-turn-on is that both devices will be conducting at the same time, allowing high current to flow and a short-circuit to occur. Even if the short-circuit does not result in a catastrophic event, there are still reliability concerns due to high thermal losses and unnecessary electro-thermal stresses on the device's wire bonds and die [2]. Additionally, the likelihood of a false-turn-on is greater with higher temperature because the threshold voltage has a negative temperature coefficient, making it easier to turn on the device [3]. The shoot-through current also has a positive temperature coefficient, resulting in higher stress on the device at higher temperatures [3]. The potential for failure is greater for SiC devices compared to Si IGBTs because the SiC MOSFET has a lower short circuit withstand time (SCWT). In [6], it was reported to be 8  $\mu$ s for a SiC MOSFET compared to the Si IGBT's 33  $\mu$ s withstand time. This will affect the requirements for the protection circuitry and demonstrates the necessity to monitor the health of the device.

False-turn-on can be caused by the interaction with a complementary device or by a device's own high-speed transient and interaction with the common-source inductance, as demonstrated in [6]. In both cases, the Miller capacitance,  $C_{GD}$ , serves as the main pathway for current to flow to the gate. This is an uncontrolled variable, as it is inherent to the device. Some of the other variables affecting the likelihood of a false-turn-on are the threshold voltage,  $V_{th}$ , the internal gate resistance  $R_{G,int}$  and the packaging inductances at the gate and source,  $L_G$  and  $L_S$  respectively, in the path of the gate current.

Crosstalk between two devices can occur during either the turn-on or turn-off transition of either device in a half-bridge due to the rapidly changing voltage and current sharing at the midpoint. During the turn-on of the lower device, as shown in Figure 2.1 (a), a negative-slope dv/dt transition occurs across the  $C_{GD}$  of the upper device. The dv/dt across  $C_{GD}$  results in a current that flows through the gate of the upper device, causing a voltage drop across the gate resistance,  $R_G$  and  $R_{G,int}$ , as well as the gate inductance, which increases the voltage of  $V_{GS}$ . If this voltage exceeds the threshold, the device will turn-on [5, 7]. This effect is further amplified due to ringing of  $L_{SCCLI}$  due to the high di/dt, causing additional power loss.

In the event of the lower device turning-off, there is a positive-slope dv/dt that causes current through  $C_{GD}$  of the upper device in the opposite direction, as shown in Figure 2.1 (b). This current flows through the  $R_{G}$ ,  $L_{G}$ , and  $L_{SCCLI}$  causing a negative voltage that further pulls-down the device.

Figure 2.1. Crosstalk of two devices in a phase leg.

If the device is already held at -5 V, the voltage may be pulled to a value exceeding the maximum negative bias, causing degradation of the gate oxide over time [5].

Various solutions with the gate drive circuitry have been evaluated to mitigate this problem. One commonly adopted solution is the use of a negative bias, -5 V, to hold the device in the offstate and cancel any positive voltage spikes. However, the magnitude of the voltage spikes may be large enough to still reach the threshold voltage, especially at higher temperatures when the threshold voltage is lower. The magnitude of the voltage spikes will be affected by the impedance in the gate loop, including  $R_G$ ,  $L_G$ , and  $L_S$ . Thus, it is necessary to make the impedance as small as possible, which is achieved by changing the gate resistor. A higher  $R_G$  is typically used to reduce dv/dt, thus there is a tradeoff between the size of the resistor and the amount of impedance in the path. Another accepted solution is the use of an Active Miller Clamp (AMC) which provides a low-resistance path to ground for the current to flow. However, the physical location of the AMC determines the actual effectiveness of the method due to the presence of internal gate resistance and other interconnection inductances, which still may be large enough to cause false-turn-on [8]. Other methods of mitigating this problem include separate turn-on and turn-off gate paths or active gate drivers. A combination of the bipolar drive, with -5 V, separate turn-on and turn-off paths, and a snubber capacitor was recommended in [3].

### 2.2.2 Common-mode noise and isolation

When using SiC MOSFETs and other high-voltage power devices it is necessary to provide sufficient isolation. Aside from protecting the low-voltage control circuitry from high-voltage surges, it is also beneficial to isolate the grounds to prevent noise from reaching the controls. As shown in Figure 2.2, the main isolation barriers are created to protect the control signals via the

Figure 2.2. Gate driver and isolation barriers.

digital isolator and the isolated power supply for the gate driver. Additionally, the feedback signals through the sensing circuitry should also be isolated. Additional board layout techniques can be implemented to increase the isolation barrier, including the addition of slots or cutouts in the board to increase creepage, or the potting of the circuit in isolation material.

The upper device in the half-bridge must have an isolated signal, or level-shifted signal, due to its connection to the switch node of the phase-leg. This requires the use of an isolated gate driver or separate signal isolation using a digital isolator. This isolation barrier has a parasitic capacitance, as shown in Figure 2.3. Thus, due to the high dv/dt shown at the switch node, noisy currents will be allowed to flow through the control circuitry in the path shown in red [9]. Noise is then transferred to the ground on the primary side, and the control signal experiences a non-stable reference, which may affect the control signals. This results in serious problems, especially if the gate of a device is falsely triggered while a complementary device is on, resulting in shoot-through. Additionally, the isolation barrier of the gate driver's DC-DC converter must also be

Figure 2.3. Common-mode current through isolation barriers.

designed to reduce the capacitance between transformer windings. In the same way as shown in Figure 2.3, common-mode currents are allowed to flow through the ground to the controls side of the isolation barrier through this power supply. Thus, it is necessary to carefully consider the design of these isolation barriers. Small isolation capacitance of the digital isolator and proper PCB layout can help reduce these effects [9]. The lower device's gate drive signals and power supply may also isolated, but this increases the complexity and number of components in the gate driver design. Additionally, the design of the high-voltage isolation transformer for the DC-DC converter should also be considered, and is a challenging task as described in [1].

Another technique to prevent the malfunction of the control signals due to common-mode noise issues is to use differential signaling for the gate drive signals. In this case, the single-ended signal from the digital signal processor (DSP), or other control card, is translated into a differential signal before being received and then translated back into a single-ended signal to drive the gate

driver. Differential signals are commonly used in digital applications which require very accurate signals and immunity to noise. One downfall of differential signaling is the additional components necessary to transmit the data, as well as the need for two wires, instead of one, to transmit a signal. A tradeoff exists between mitigation of dv/dt and design of the circuitry around the device based on the application's requirements with regards to EMI, switching loss and cost. Other methods of reducing common-mode noise may be through filtering using common-mode chokes at the inputs and outputs of the power supplies and DSP signal connections. However, common-mode chokes also introduce a delay, and are designed only for certain frequency response, requiring detailed tuning to harmonics that may also vary depending on the circuit. If care is not taken in the design of the isolation barriers and/or signaling connections, then it is likely that noisy grounds will affect the operation of the SiC MOSFETs and cause false triggering.

### 2.2.3 Parasitic Inductance

Another critical challenge in the implementation of SiC devices are the parasitic inductances in the device and circuit. The package of the SiC device, whether discrete or in a power module, and the circuit board layout affect the amount of parasitic inductances present in certain regions of the circuit. Each of these inductances can be lumped into the critical areas of the circuit, as shown in Figure 2.4. The interactions of *di/dt* during the turn-on and turn-off transitions result in ringing, voltage overshoot, or reduced driving speed. As described in [10], the parasitic inductances can be split into three main categories: the common-source inductance (CSI), the gate loop inductance (GLI), and the switched current commutation loop inductance (SCCLI). The CSI includes the inductance at the source inside the package of the SiC MOSFET, the source interconnect inductance, and the PCB source trace inductance. The GLI is the area enclosed by the gate drive current path, including the gate path from the gate driver through the source return path

Figure 2.4. Parasitic components surrounding the SiC MOSFET.

back to the driver. Finally, the SCCLI includes the connections between the upper and lower devices in a phase-leg configuration, and results in the main voltage and current ringing of the power loop.

The drain inductance acts as a turn-on snubber for the MOSFET by limiting the di/dt of the drain current and reducing the drain-source voltage across the device (L\*di/dt), thus reducing turn-on losses. However, at turn-off, the voltage induced across the inductor is added to  $V_{DS}$ , producing an overshoot and increases the turn-off switching losses. When the device is subjected to these voltage overshoots at every switching cycle the stress over time may decrease the device's lifetime.

## 2.2.4 Protection

SiC MOSFETs can operate very efficiently at high-temperatures, and can actually switch faster as temperature increases. The speed at which they switch, however, also affects how fast

Figure 2.5. Failed SiC MOSFET due to short circuit.

they will reach a damaging level of current during a short circuit event. The ability to prevent, protect, or react to such an event is a critical part of the gate driver design. Short circuits will not only cause damage to the device over time, but can cause catastrophic failure of the device, see Figure 2.5. As discussed before, the SCWT of a SiC device can be almost half of the withstand time of a Si device [11, 12]. This means that the gate driver has to be able to detect a short-circuit event much faster than the gate driver for a Si device. Additionally, because SiC devices can switch so fast, the action of turning off the device when a short circuit is detected must be handled carefully so that a very large voltage spike is not caused due to the high di/dt. As mentioned in the previous section, excessive voltage overshoot can result in the fast degradation of the device. Thus, there are three main gate driver considerations for this problem, namely: 1) how the short-circuit is detected, 2) how fast the gate driver responds to the detection, and 3) what the gate driver does after detecting the short-circuit.

Typically, a short circuit is detected using the desaturation method, or DESAT, which is used to determine when the device moves from the saturation region to the active region. Unfortunately for SiC devices, the transition from saturation to active is not as clear as for a Si device, as shown in the characteristic curves in Figure 2.6. The DESAT method can still be utilized for a SiC MOSFET, but the design must be more precise than that of a Si device, or else false detections and unnecessary shut-down instances can occur. The DESAT method utilizes the onresistance and the maximum current rating of the device to determine a normal on-voltage across the device. Usually a high-voltage desaturation diode in series with a zener diode is used to block the current signal to the DESAT pin of a gate driver IC until the reference voltage is surpassed, and DESAT is triggered. This means  $V_{DS}$  is being monitored at all times. Other than the difficulty in detecting the transition, this method also has the downfall of having to connect sensing circuitry to the high-voltage  $V_{DS}$  of the MOSFET. The isolation barrier needs to be sufficient to protect the control circuitry and the delay between the sensed signal and the controller's response needs to be very short. Additionally, the actual reference voltage for the DESAT protection should be adjustable based on the operating condition, such that a short circuit is not falsely detected.

Figure 2.6. (a) Si IGBT vs. (b) SiC MOSFET i-v characteristics [15, 16].

The speed of the detection must be fast. As described in [10], the SiC MOSFET can fail in half the time that a similarly rated Si IGBT would. When utilizing an IC gate driver with DESAT detection, the propagation delays and detection times from the datasheet should be considered [13]. The propagation delay, which applies to both turn-on and turn-off, will indicate how fast the driver will respond to a control signal telling it to turn-off the device. This is added to the time it takes for the control circuitry to detect the fault, which may also be given in the IC's datasheet if it has DESAT protection as a functionality. Additionally, the physical location of the gate driver will affect the speed at which it detects the fault because parasitic inductance increases with length of traces, and thus increases the propagation delay between the device and the driver.

Another aspect of the DESAT design is what action the gate driver takes to shut down the device in a controlled manner. If the device is turned off as usual, the current will fall at a very fast di/dt transition, causing large voltage overshoot due to parasitic inductances. Thus, the device should be shut down slowly to avoid over-voltages. This can be achieved through the use of large gate resistors to decrease the gate current during the transition, or by adding an intermediate voltage level during turn-off, sometimes called soft turn-off or two-level turn-off (TLTO) [11]. An intermediate voltage is utilized at this time to bring the current down to an acceptable level before completely shutting it down using the lowest drive voltage available, typically -5 V. Utilizing the intermediate voltage level allows the current to transition slowly, and will increase the SCWT of the device. In [11], the 1.2 kV SiC MOSFET was able to handle a short-circuit for 13  $\mu$ s before failing when using an intermediate voltage of 15 V, versus surviving for 7  $\mu$ s when the gate-source voltage was held at 20 V. This may cause a designer to conclude that the device should be driven at 15 V in order to improve the reliability of the device in these types of scenarios, however, the designer will then suffer the consequences of higher conduction losses because of greater  $R_{ds(on)}$  at

lower  $V_{GS}$ . In [14], the Rowgowski coil is used to detect the current without measuring the voltage, providing complete isolation of the measurement, as well as avoiding the cost of false-triggering the fault signal if an incorrect voltage reference is used in DESAT. The di/dt information from the Rowgowski coil is processed through the use of an integrator sensing circuit and comparator to enable the fault signal. The coil must have a high bandwidth in order to measure all of the details of the waveform. Being a non-intrusive measurement, the impedance in the commutation loop is not affected. Alternatively, current shunt resistors, or current viewing resistors, are also utilized due to their very high bandwidth and high accuracy, but they must be inserted into the circuit itself. This may introduce additional inductance into the loop, but can be compensated with the measurement circuitry or precise design.

## 2.3 Conclusion

The challenges associated with using SiC MOSFETs may sound daunting, but the benefits are very appealing. Some common solutions to those challenges were discussed in this chapter. The role of the gate driver is to provide the necessary functions to enable the high performance of the device, while still maintaining the reliability and safety of the circuit around it. The gate driver for high-voltage SiC MOSFETs should include all the necessary functions to prevent failure of the device and system through careful design of the DC-DC converter isolation, other control signal isolation barriers, noise mitigation, and protection. Aside from these functions, the gate driver can actually be used to mitigate the challenges with regards to dv/dt and di/dt transients, and still achieve high performance. In the following chapters, the gate driver technology will be discussed, and the methodologies will be compared to determine the best driver for high-voltage SiC MOSFETs.

### 2.4 References

- [1] K. Mainali, S. Madhusoodhanan, A. Tripathi, K. Vechalapu, A. De and S. Bhattacharya, "Design and evaluation of isolated gate driver power supply for medium voltage converter applications," in *Proc. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Long Beach, CA, 2016, pp. 1632-1639.

- [2] T. Funaki, "A study on self turn-on phenomenon in fast switching operation of high voltage power MOSFET," in *Proc. 2013 3rd IEEE CPMT Symposium*, Japan, Kyoto, 2013, pp. 1-4.

- [3] S. Jahdi, O. Alatise, J. A. Ortiz Gonzalez, R. Bonyadi, L. Ran and P. Mawby, "Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules," *IEEE Trans. on Industrial Electronics*, vol. 63, no. 2, pp. 849-863, Feb. 2016.

- [4] W. Zhang, Z. Zhang, F. Wang, D. Costinett, L. Tolbert and B. Blalock, "Common source inductance introduced self-turn-on in MOSFET turn-off transient," in *Proc. 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Tampa, FL, 2017, pp. 837-842.

- [5] S. Yin *et al.*, "Gate driver optimization to mitigate shoot-through in high-speed switching SiC half bridge module," in *Proc. 2015 IEEE 11th International Conference on Power Electronics and Drive Systems*, Sydney, NSW, 2015, pp. 484-491.

- [6] J. Sun, H. Xu, X. Wu and K. Sheng, "Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT," in *Proc. 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS)*, Beijing, 2016, pp. 42-45.

- [7] H. Chen and D. Divan, "High speed switching issues of high power rated silicon-carbide devices and the mitigation methods," in *Proc. 2015 IEEE Energy Conversion Congress and Exposition (ECCE)*, Montreal, QC, 2015, pp. 2254-2260.

- [8] D. Martin, W. A. Curbow and T. McNutt, "Performance analysis of a SiC MOSFET half bridge power module with a Miller clamp," in *Proc. 2017 IEEE International Workshop On Integrated Power Packaging (IWIPP)*, Delft, 2017, pp. 1-5.

- [9] W. Zhang, X. Huang, F. C. Lee and Q. Li, "Gate drive design considerations for high voltage cascode GaN HEMT," in *Proc. 2014 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Fort Worth, TX, 2014, pp. 1484-1489.

- [10] E. Shelton, X. Zhang, T. Zhang, N. Hari and P. Palmer, "Low inductance switching for SiC MOSFET based power circuit," in *Proc. 2017 IEEE Energy Conversion Congress and Exposition (ECCE)*, Cincinnati, OH, 2017, pp. 5093-5100.

- [11] J. Rice and J. Mookken, "SiC MOSFET gate drive design considerations," in *Proc. 2015 IEEE International Workshop on Integrated Power Packaging (IWIPP)*, Chicago, IL, 2015, pp. 24-27.

- [12] J. Sun, H. Xu, X. Wu and K. Sheng, "Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT," in *Proc. 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS)*, Beijing, 2016, pp. 42-45.

- [13] J. Wang, Z. Shen, C. DiMarino, R. Burgos and D. Boroyevich, "Gate driver design for 1.7kV SiC MOSFET module with Rogowski current sensor for shortcircuit protection," in *Proc.* 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 516-523.

- [14] C. DiMarino, J. Wang, R. Burgos and D. Boroyevich, "A high-power-density, high-speed gate driver for a 10 kV SiC MOSFET module," in *Proc. 2017 IEEE Electric Ship Technologies Symposium (ESTS)*, Arlington, VA, 2017, pp. 629-634.

- [15] CREE, "Silicon Carbide Power MOSFET C2M<sup>TM</sup> MOSFET Technology," C2M0045170D datasheet, June 2016.

- [16] IXYS, "High Voltage, High Gain BIMOSFET<sup>TM</sup> Monolithic Bipolar MOS Transistor," IXBH42N170 datasheet, Oct. 2008.

### **CHAPTER 3**

### GATE DRIVE METHODS AND PERFORMANCE

## 3.1 Introduction

From Chapter 2, it was shown that poor gate driver design and ignorance of the challenges of driving SiC MOSFETs could result in an ineffective system. The main solution is to have a gate driver that enables the device to have low energy losses while still mitigating the *dv/dt* and *di/dt* to the levels required by the system. State-of-the-art gate driver technologies may not provide the control necessary to enable SiC MOSFETs. First, this chapter will introduce some of the main considerations for the gate driver. Secondly, two categories of gate driver circuits are discussed: the conventional voltage-mode driver and the current-mode driver. The theoretical operation of these drivers is outlined, and the main parameters of each are pointed out [1]. Finally, a multi-level voltage driver is proposed as a solution for mitigating the harmful effects of fast switching, and the theoretical analysis of this method is given.

### **3.2 Gate Driver Considerations**

This section will first introduce the main considerations of the gate drive circuitry to effectively drive a power MOSFET. Many of these parameters are included in the device datasheet, such as the gate charge, its capacitances, the threshold voltage, the on-resistance, and the internal gate resistance. Firstly, MOSFETs are driven through the charging and discharging of its input capacitance,  $C_{iss}$ , which is the sum of the  $C_{GS}$  and  $C_{GD}$  capacitors. The amount of charge needed to fully turn-on the device is given as the gate charge,  $Q_G$ . The gate charge is found by applying a constant current at the gate and observing the time it takes for the gate-source voltage to rise to its

maximum value. In other words, the gate charge can be measured by taking the integral of the gate current over time.

$$Q_G = \int I_G dt \tag{3}$$

This is an important parameter because it defines the drive strength,  $I_G$ , which can be found using:

$$I_G = \frac{Q_{G,total}}{t_{rise/fall}} \tag{4}$$

Where  $t_{rise/fall}$  is the desired rise and fall times of  $V_{GS}$ . The effects of the capacitors and their charge on the switching operation of the device can be further investigated by looking at the gate charge plot vs.  $V_{GS}$  located in the device datasheet. This plot is divided into three main regions during which the input capacitors,  $C_{GS}$  and  $C_{GD}$ , are being charged or discharged, as shown in Figure 3.1. The first portion of the gate charge figure represents  $Q_{GS}$ , during which  $C_{GS}$  is charged from the off-voltage to the Miller plateau. The flat region of the plot represents the so-called Miller plateau voltage, during which the current is redirected to charge  $C_{GD}$ . The Miller region is greatly

Figure 3.1. Gate charge plot.

dependent on the ratio of  $C_{GD}$  to  $C_{GS}$ . When the slope is non-zero, which is the case for SiC MOSFETs, some of the current flows through  $C_{GS}$  while  $C_{GD}$  is also being charged, making the voltage plateau non-flat. After the Miller plateau region ends,  $V_{GS}$  rises to the final turn-on voltage level, and all the current flows through  $C_{GS}$ .

It is also important to note that the Miller plateau voltage changes with the load, primarily due to the drain current. The duration of the plateau region, however, also tends to increase with larger  $V_{DS}$ . The equation below is commonly used to describe the Miller plateau voltage.

$$V_{miller} = V_{th} + \frac{I_D}{g_{fs}} \tag{5}$$

This value may not always be accurate due to variations of  $V_{th}$  and  $g_{fs}$ .  $V_{th}$  is the threshold voltage, or the minimum voltage required to enhance the device, and  $g_{fs}$  is the device's transconductance. The transconductance describes the change in the drain current,  $I_D$ , with a given change in  $V_{GS}$ .

This information will serve as a baseline for the minimum required drive strength. The gate current is controlled through various gate driver methods, each utilizing different ways of controlling it. These drivers will be discussed in the following section and the switching waveforms are given for each, with the equations given to describe each transition.

# 3.3 Conventional Voltage-Mode Gate Driver

The most common gate driver for power MOSFETs is the voltage-mode driver. This type of driver typically employs a type of totem-pole buffer, utilizing BJTs or MOSFETs, to pull the gate of the power device to a high or low voltage depending on the MOSFET's power rating. One

Figure 3.2. NFET totem-pole buffer.

such topology is shown in Figure 3.2, where  $R_{HI}$  and  $R_{LO}$  are the output resistances of the driver [2].

The switching processes for turn-on and turn-off are shown in Figure 3.3, where  $V_{dr}$  is the drive voltage from the gate driver,  $V_{GS}$  is the voltage at the gate of the device, and  $I_G$  is the gate current, which charges and discharges the MOSFET's capacitors [1]. On the  $V_{GS}$  waveform,  $V_{th}$  is the device's threshold voltage, and  $V_{miller}$  is the Miller plateau voltage.  $I_{G,pk}$  on the gate current waveform is the peak gate current. The drain-source voltage,  $V_{DS}$  is shown, as well as the drain current  $I_D$ , which are used to define the dv/dt, di/dt and energy losses.  $V_{on}$ , shown on the  $V_{DS}$  waveform, is the on-state voltage, which is dependent on the value of  $I_D$  and  $R_{DS(on)}$ . The high-level drive voltage,  $V_{DR,H}$ , is chosen based on the datasheet of the MOSFET, corresponding to the lowest on-resistance,  $R_{DS(on)}$ , during conduction. The low-level drive voltage,  $V_{DR,L}$ , is also the datasheet recommended value, typically a negative voltage for SiC MOSFETs. The negative voltage rail provides both a larger potential across the gate resistor to increase the discharge current, as well as increases the margin between the amplitude of gate ringing and the threshold voltage.

The turn-on process can be split into four main intervals: (1) the turn-on delay, (2) the current rise time, (3) the first voltage fall time, and (4) the second voltage fall time, as shown in Figure 3.3 (a). The relevant equations for these intervals are shown below.

During period (1) the gate voltage rises from  $V_{DR,L}$  to  $V_{th}$ .  $C_{GS}$  is charged during this interval, and there are no losses in this period because the current still flows through the Schottky diode in the upper switch position.

During period (2) the current begins to rise across the MOSFET and there is a slight voltage drop on  $V_{DS}$  due to the power loop inductance SCCLI interaction with di/dt. The gate voltage

Figure 3.3. Transient switching waveforms of a SiC MOSFET with a voltage-mode driver.

during this period rises from  $V_{th}$  to the Miller plateau voltage,  $V_{miller}$ . The drain current rise is dependent on the transconductance,  $g_{fs}$ , and the gate voltage, as described in (6).

$$I_d(t) = g_{fs} (V_{qs}(t) - V_{th})$$

(6)

The duration of period (2) is found by rearranging the equation for the relationship between the voltage change and current in a capacitor, I=C\*dv/dt, where the input capacitance is being charged:

$$t_{on(2)} = \frac{C_{iss}(V_{miller} - V_{th})}{I_q} \tag{7}$$

$C_{iss}$  is equal to  $C_{gd}+C_{gs}$ , where  $C_{gd}$  can be split into two values, one when  $V_{DS}>V_{gs}-V_{th}$  and the other when  $V_{DS}< V_{gs}-V_{th}$ . The Miller plateau voltage is found using:

$$V_{miller} = V_{th} + \frac{I_L}{g_{fs}} \tag{8}$$