# Study of Integration Technology with 3D-stacked Heterogeneous Dielets for Flexible Hybrid Devices

| 著者     | Susumago Yuki                        |  |

|--------|--------------------------------------|--|

| 学位授与機関 | Tohoku University                    |  |

| URL    | http://hdl.handle.net/10097/00137548 |  |

# 博士学位論文 Doctoral Thesis

## 論文題目

Thesis Title

| Study of Integration Technology       |

|---------------------------------------|

|                                       |

| with 3D-stacked Heterogeneous Dielets |

|                                       |

| for Flexible Hybrid Devices           |

|                                       |

|                                       |

# 東北大学大学院工学研究科

# Graduate School of Engineering, TOHOKU UNIVERSITY

専攻/Department: Department of Mechanical Systems Engineering

学籍番号/ ID No: COTD1008

氏名/Name: Yuki Susumago

# TOHOKU UNIVERSITY Graduate School of Engineering

Study of Integration Technology with 3D-stacked Heterogeneous Dielets for Flexible Hybrid Devices

(異種ダイレット積層を用いたフレキシブルハイブリッドデバイスの 集積技術に関する研究)

A dissertation submitted for the degree of Doctor of Philosophy (Engineering)

Department of Mechanical Systems Engineering

by

Yuki SUSUMAGO

January 10, 2023

# Study of Integration Technology with 3D-stacked Heterogeneous Dielets for Flexible Hybrid Devices

#### Yuki Susumago

#### **Abstract**

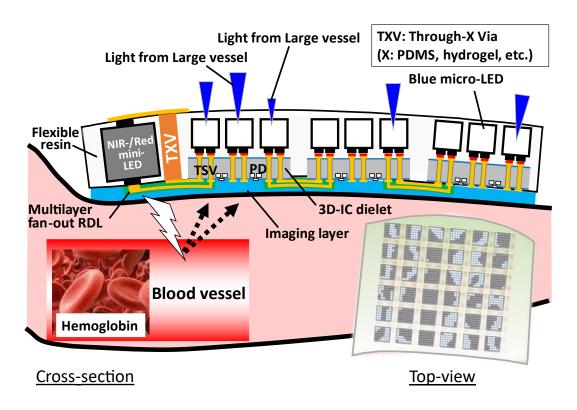

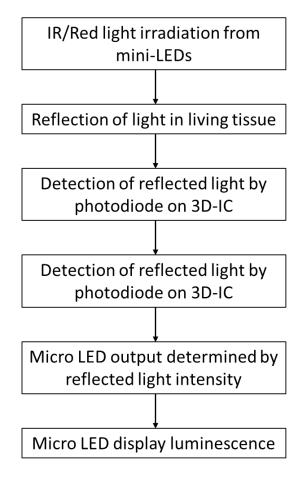

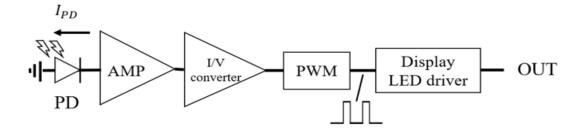

This thesis focuses on integration technology research and development for a healthcare monitoring and vain viewer device called Smart Skin Display as a Flexible Hybrid Electronics (FHE) that combines the performance of rigid single crystalline semiconductors with flexible organic substrates. So far, structurally new FHE is proposed with embedded heterogeneous chips using fan-out wafer-level packaging (FOWLP). Conventional flexible devices are limited to so-called flexible printed circuits (FPC), where only limited parts without any components surfacemounted on polyimide substrates are flexible. In contrast, highly flexible devices have been developed using organic semiconductors. However, the performance of the organic semiconductors is low compared to Si and III-VI semiconductors. On the other hand, ultrathin Si dies themselves used in conventional FHE are flexible. In previous studies, the ultrathin dies thinned to less than several tens of micrometers are surface-mounted on polymeric substrates and interconnected with printable wirings. However, the conventional FHE has a severe problem caused by mechanical stress to give characteristics fluctuation when bending. The FHE used in this research consists of several tiny chips called "dielet" and embeds them in an extremely flexible elastomer substrate PDMS at the wafer-level. Recently, "chiplet" has been attracting attention in the semiconductor field. A chiplet is a tiny chip designed to separate several functions previously combined into a monolithic system on a chip (SoC). The advantage of chiplet is that each chiplet can be manufactured using the appropriate technology nodes at a low cost. The concept of the dielets in this study encompasses a broader spectrum of initially tiny devices such as optical devices, MEMS, and passive devices, in addition to the chiplets mentioned above. Smart Skin Display, as a highly integrated FHE device, consists of mini-LEDs, micro-LEDs, and 3D-ICs with photodiodes and LED drivers. The micro-LEDs are stacked on the 3D-ICs having TSV (through-silicon via). The mini-LEDs emit red and IR light to human skin, and the 3D-ICs receive the reflected light from the blood vessel and drive the micro-LEDs used as micro-LED display components. This highly integrated wearable flexible hybrid device can diagnose conditions like arteriosclerosis obliterans more easily since it can simultaneously visualize blood vessels and acquire biological information. This thesis mainly describes five key integration technologies to fabricate Smart Skin Display. The first one is high-precision tiny dielet assembly. The second one is highly bendable multi-level wiring formation on an elastomer PDMS, the third one is room-temperature micro-LED bonding on a wafer, the fourth one is TSV barrier and seed layer deposition using standard PVD tool, and the last one is micro-LED stacking on thin 3D-ICs. I will develop these key technologies required to implement Smart Skin Display in each chapter.

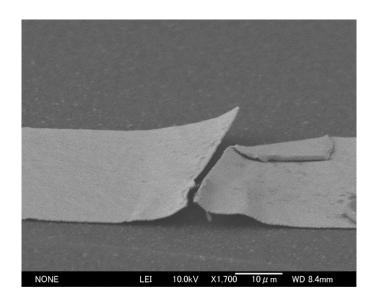

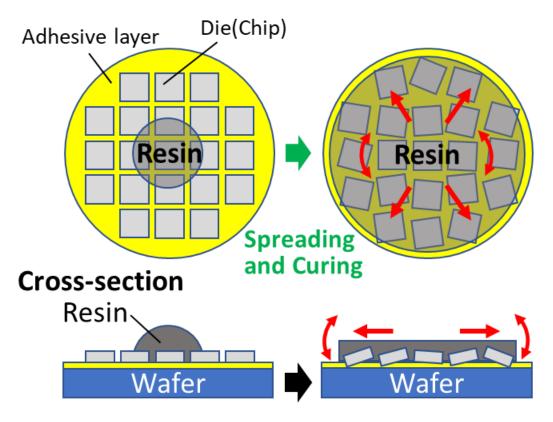

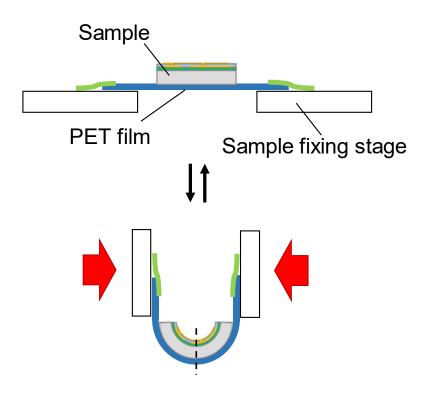

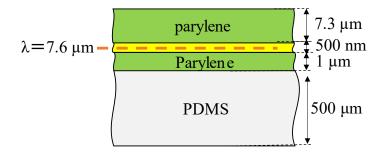

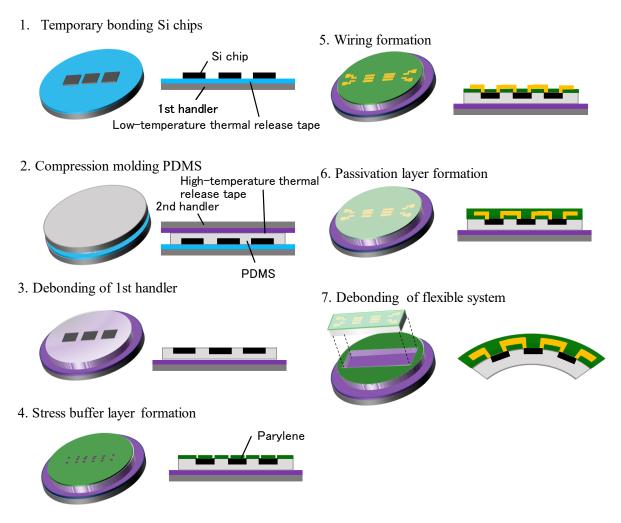

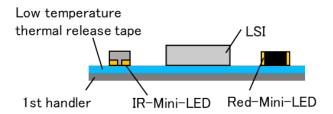

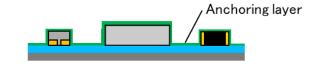

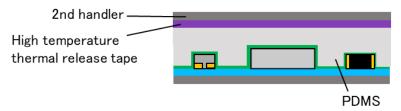

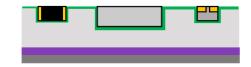

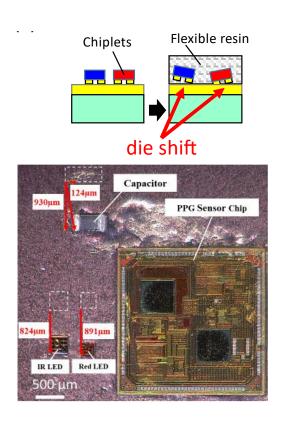

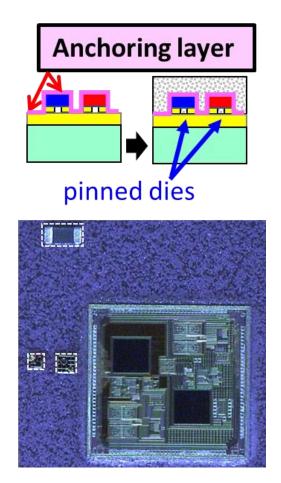

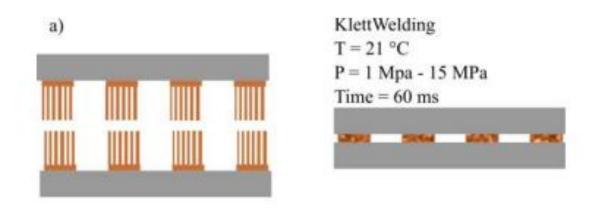

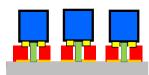

Process integration and flexible redistributed multi-wiring layer design/formation of Smart Skin Display are the main topics of Chapter 2. In the highly integrated Smart Skin Display, heterogeneous dielets are temporarily fixed on a thermal rerelease tape attached to a support substrate, followed by filling and molding with a biocompatible and flexible PDMS. A critical issue for tiny dielet positioning within  $\pm 10~\mu m$  in the integration process integration is die shift, which refers to the movement of the dielet caused by the fluidic force of the resin

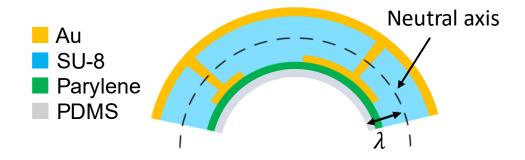

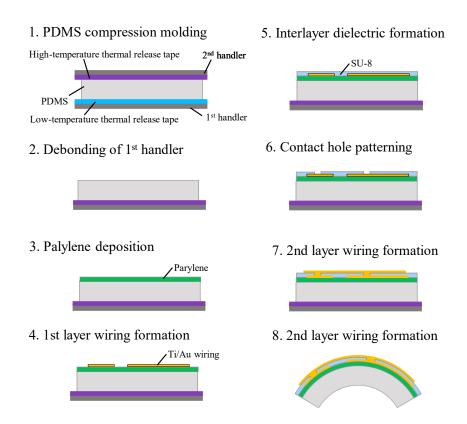

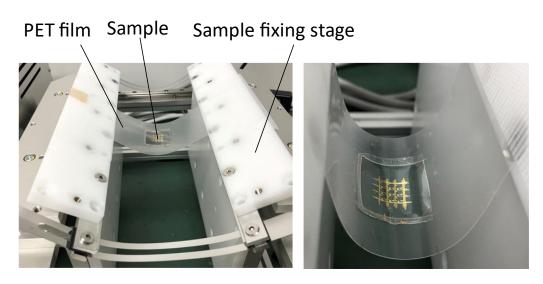

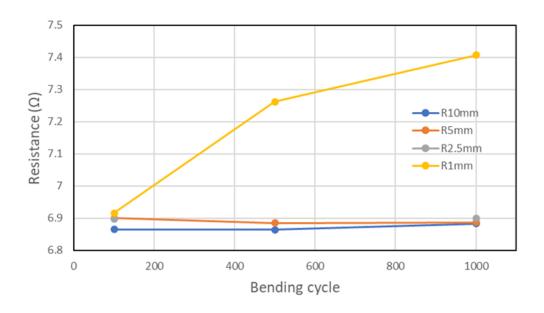

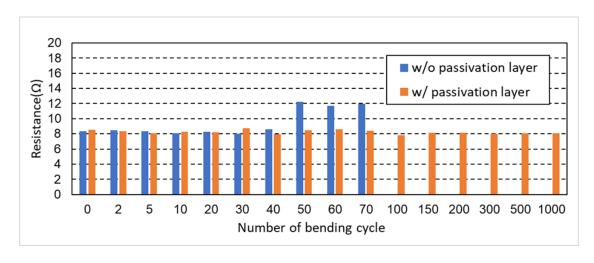

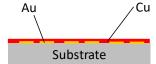

and thermomechanical stress. In this study, an anchor layer is proposed as a method to suppress die shift regardless of the size of the dielets. By introducing the anchor layer, suppressing the die shift of mini-LEDs with a side length of 300 µm down to several micrometer ranges is succeeded. To construct the mechanically robust Smart Skin Display, I then focus on the fabrication of flexible redistributed two-layer interconnects on an elastomer PDMS. The flexible multilayer wiring is structurally designed based on a stress neutral axis concept. When Smart Skin Display is bent, more significant stress is applied at the outermost wiring layer from the stress neutral axis. The stress neutral axis is, therefore, to be located in the middle of the two-layer wires in this study by designing the thickness and Young's moduli of the materials. Since conventional polyimide flexible substrates have high Young's moduli around 3-4 GPa, such a stress-neutral axis control is challenging, and low-Young's-modulus PDMS can achieve the structural design. I accomplish the flexible wiring formation with a width of 50 µm or smaller required for Smart Skin Display. Furthermore, the mechanical durability of the flexible multilayer wiring is evaluated by bending tests. The flexible multilayer wiring can survive the severe conditions of a 1-mm radius of curvature during the bending test. This result suggests that the flexible multilayer wiring can be endured by mechanical stress when folding Smart Skin Display.

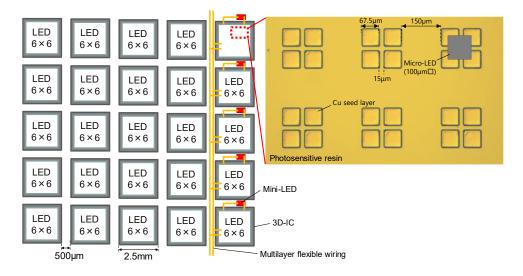

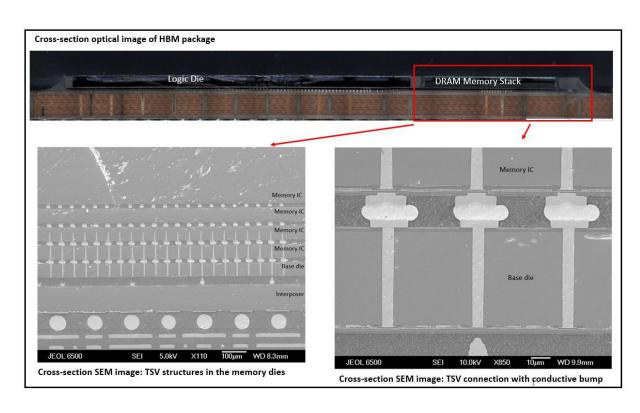

Low-thermomechanical-stress bonding and interconnect technologies for heterogeneous dielets on the wafer are discussed in Chapter 3. Conventional bonding used for 3D integration requires thermocompression bonding. However, the 3D-IC would be damaged when a high-temperature point load is applied, making it difficult to attach micro dielets to the 3D-IC. As a result, I create room-temperature electroplated Cu direct bonding and show that it could be done using sapphire wafers as a host substrate. Micro-LEDs, which are expected to be used in next-generation displays, are used as tiny dielets and successfully bonded. For Smart Skin Display, an electroluminescence yield of about 100% is required. A failure analysis is underwent to enhance the yield of electroplated Cu direct bonding. Finally, the prospect of achieving 100% luminescence yield is obtained. This bonding method can vertically stack and electrically interconnect dielets that are not suitable for thermocompression bonding in one batch. Furthermore, it is a fantastic bonding method that can attach multiple heterogeneous components at once.

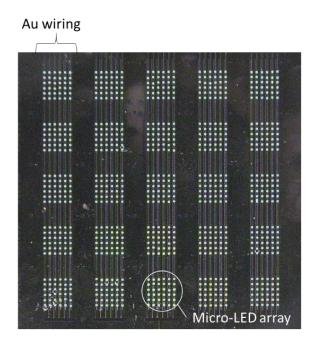

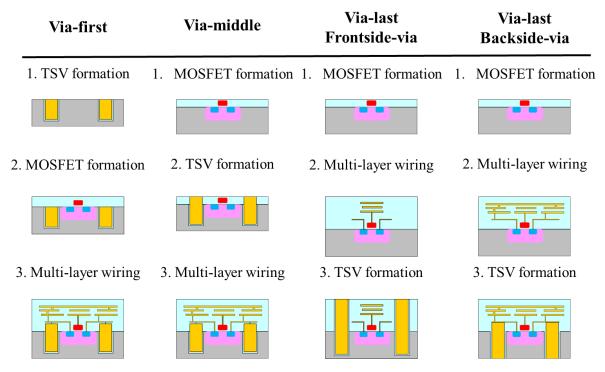

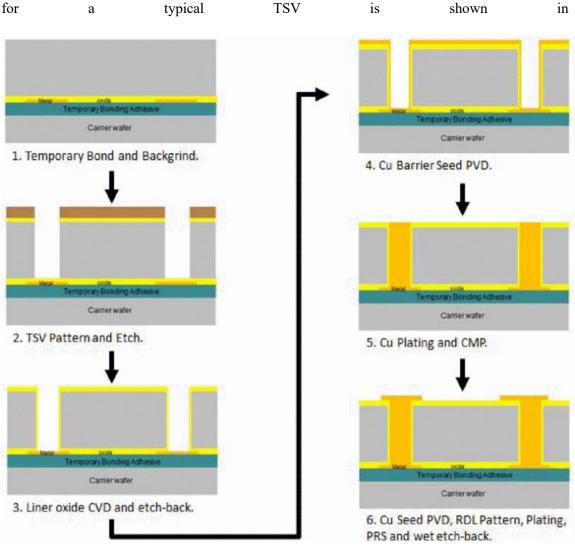

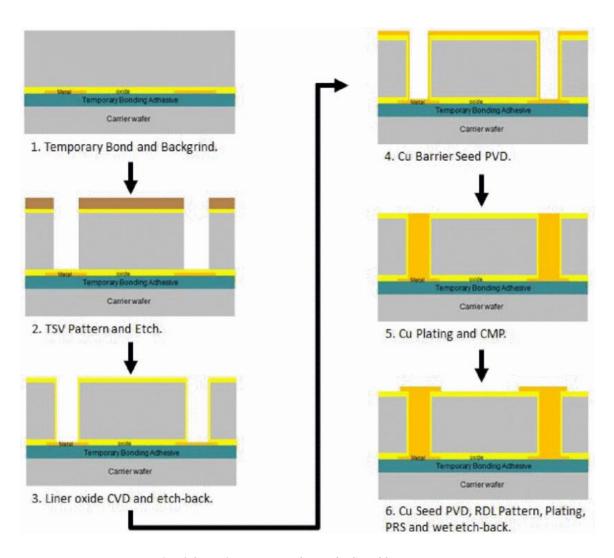

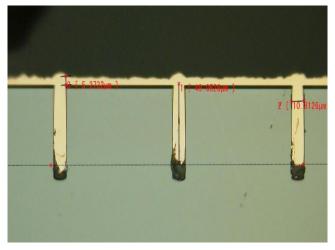

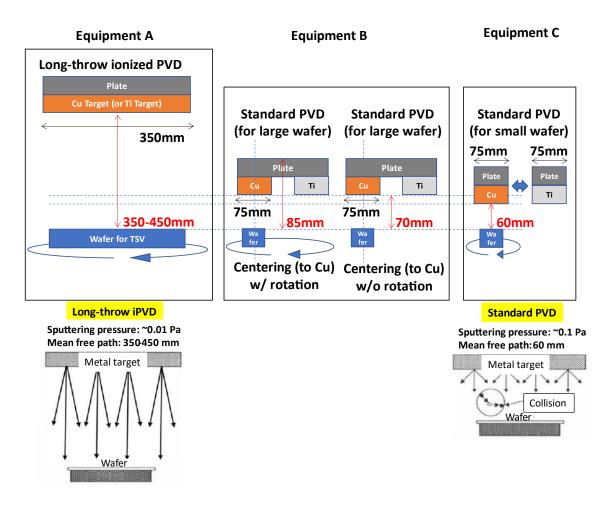

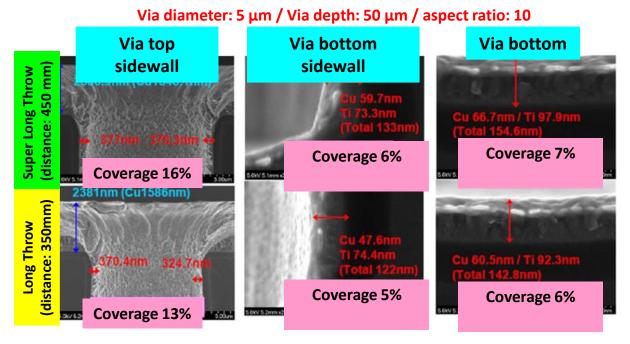

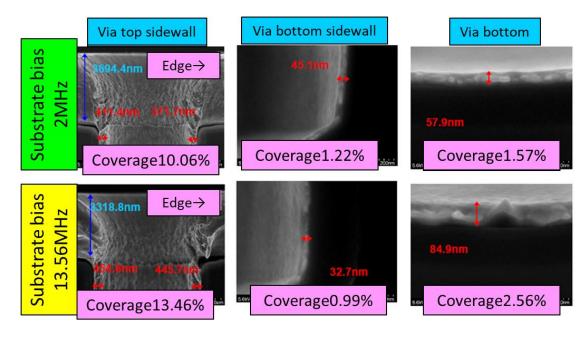

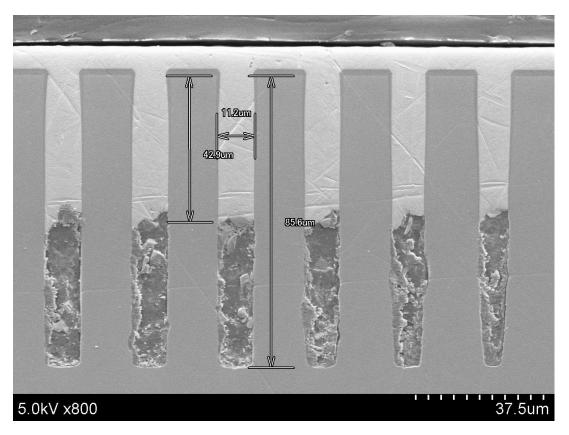

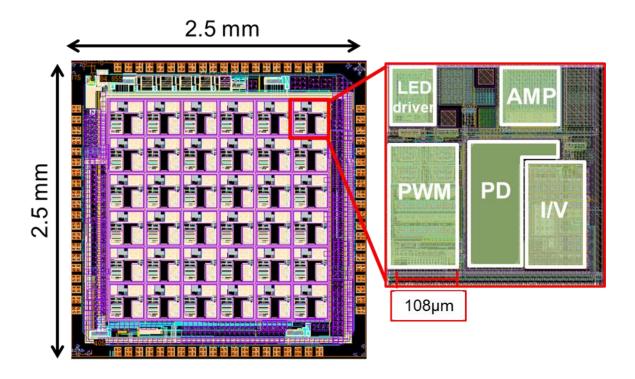

The processability of dielet-on-wafer 3D integration based on Via-last TSV formation is described in Chapter 4. The TSV barrier and seed layer sputtering is an important process that determines the success or failure of 3D-IC fabrication. In industry, a specialized sputtering apparatus such as ionized sputtering and long-throw sputtering is used for the deposition of TSV barrier/seed layers; however, their usefulness is constrained for TSV with large aspect ratios. In this investigation, I optimize the process utilizing standard sputtering by controlling rotation, tilting, and positioning conditions between target metals and wafer samples and challenge the maximum aspect ratio that can be fabricated. The results of this research are significant in that they expand the range of 3D-IC that can be fabricated using standard sputtering equipment. Based on this outcome, I design the TSV geometry and fabricate 3D-IC at the die-level. Micro-LEDs are successfully bonded onto the thinned 3D-IC by room-temperature electroplated Cu direct bonding without any cracks. Therefore, micro-LEDs are successfully operated. The 3D-IC dielets can be integrated by the highly integrated FHE techniques, which significantly enhance the performance of flexible devices. The FHE in this research gives a breakthrough against the constraints of traditional flexible devices and can greatly contribute to the development of the mechanical and electrical systems engineering and biomedical engineering fields.

Finally, Smart Skin Display integration technologies described in Chapters 2-4 are summarized in Chapter

5.

## **Contents**

| Chapter 1 Introduction                                                        | 1  |

|-------------------------------------------------------------------------------|----|

| 1.1 Background                                                                | 1  |

| 1.2 Heterogeneous integration                                                 | 2  |

| 1.3 Fan Out Wafer Level Packaging (FOWLP)                                     | 6  |

| 1.4 Flexible hybrid electronics.                                              | 7  |

| 1.4.1 Conventional FHE                                                        | 11 |

| 1.4.2 New FHE in this study                                                   | 14 |

| 1.5 Chiplet                                                                   | 16 |

| 1.6 Definition of dielet                                                      | 18 |

| 1.7 Blood vessel visualization device                                         | 19 |

| 1.8 Smart Skin Display                                                        | 22 |

| 1.9 Objectives and organization of the dissertation                           | 27 |

| References                                                                    | 29 |

| Chapter 2 Structure design and fabrication of new flexible hybrid electronics | 41 |

| 2.1 Introduction.                                                             | 41 |

| 2.1.1 Conventional flexible wiring                                            | 41 |

| 2.1.2 Flexible wiring in this work                                            | 44 |

| 2.1.3 Die shift issue                                                         | 45 |

| 2.2 Experimental                                                              | 49 |

| 2.2.1 Structural design of multilayer wiring FHE based on stress-neutral axis | 49 |

| 2.2.2 Fabrication of multilayer FHE                                           | 50 |

| 2.2.3 Bending test of the flexible multilayer wiring                          | 51 |

| 2.2.4 Passivation layer design                                                | 52 |

|                                                                               |    |

| 2.3 Evaluation of flexible multilayer wiring                                  | 55 |

| 2.5 Anchoring layer                                                                 | 62       |

|-------------------------------------------------------------------------------------|----------|

| 2.6 Conclusions                                                                     | 65       |

| References                                                                          | 67       |

| Chapter 3 Room-temperature electroplated direct bonding for 3D dielet-              | on-wafer |

| heterogeneous integration                                                           | 74       |

| 3.1 Introduction                                                                    | 74       |

| 3.1.1 Micro-LED                                                                     | 74       |

| 3.1.2 Manufacturing Technology of micro-LED display                                 | 78       |

| 3.1.3 Direct bonding                                                                | 83       |

| 3.1.4 Room-temperature bonding                                                      | 87       |

| 3.2 Experimental                                                                    | 90       |

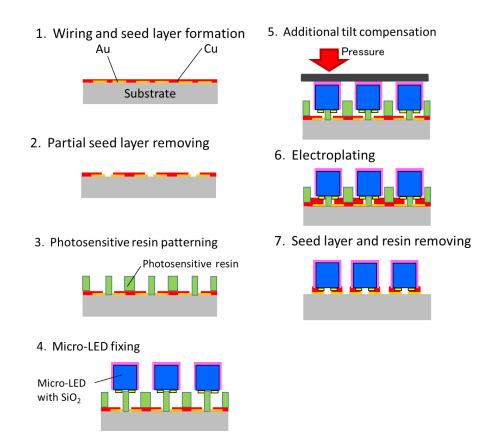

| 3.2.1 Electroplated Cu direct bonding                                               | 90       |

| 3.3 Yield evaluation of micro-LED bonded by electroplated Cu direct bonding         | 92       |

| 3.4 Failure analysis of electroplated Cu direct bonding                             | 96       |

| 3.4.1 Sidewall insulation.                                                          | 96       |

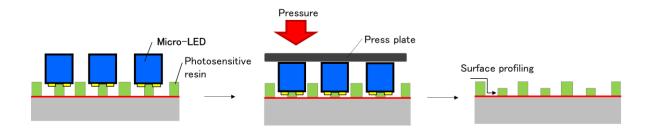

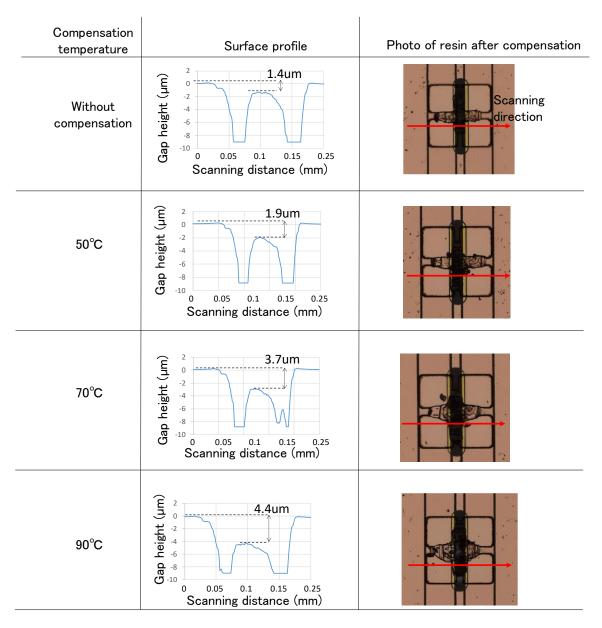

| 3.4.2 Additional tilt compensation                                                  | 99       |

| 3.4.3 Optimized process of electroplated Cu direct bonding                          | 100      |

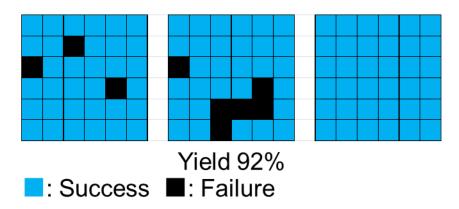

| 3.5 Yield evaluation of micro-LED bonded by optimized electroplated Cu direct bonds | ng 101   |

| 3.6 Conclusion                                                                      | 106      |

| References                                                                          | 107      |

| Chapter 4 Micro-LED stacking on 3D-IC using dielet-on-wafer bonding                 | 117      |

| 4.1 Introduction.                                                                   | 117      |

| 4.1.1 3D stacking method                                                            | 117      |

| 4.1.2 Thorough Silicon Via (TSV)                                                    | 118      |

| 4.1.3 Deposition of barrier/seed layer                                              | 124      |

| 4.2 Experimental                                                                    | 129      |

| Acknowledgments                                                           | 157               |

|---------------------------------------------------------------------------|-------------------|

| Chapter 5 Conclusion                                                      | 154               |

| References                                                                | 149               |

| 4.7 Conclusion                                                            | 147               |

| 4.6 Evaluation of micro-LED stacked on 3D-IC                              | 145               |

| 4.5 Process integration of via-last TSV formation and micro-LED stacking  | g141              |

| 4.4 3D-IC chip design and specification for Smart Skin Display            | 135               |

| 4.3 Comparison of barrier/seed layer deposition between standard and long | g-through PVD 130 |

# **List of Figures**

| Fig. | 1-1 LSI performance improvement approach                                                       |

|------|------------------------------------------------------------------------------------------------|

| Fig. | 1-2 Features of 3D-IC                                                                          |

| Fig. | 1-3 Comparison of conventional DRAM and HBM [14]                                               |

| Fig. | 1-4 Cross-section of HBM package [14]                                                          |

| Fig. | 1-5 Schematic of heterogeneous integration                                                     |

| Fig. | 1-6 Schematic of CoWoS [22]                                                                    |

| Fig. | 1-7 Process flow of two type FOWLP                                                             |

| Fig. | 1-8 Roll-to-roll process [59]                                                                  |

| Fig. | 1-9 Conceptual images of FHE [63]                                                              |

| Fig. | 1-10 Young's modulus variation versus wafer thickness                                          |

| Fig. | 1-11 Ultrathin Si wafer                                                                        |

| Fig. | 1-12 FHE using ultrathin Si                                                                    |

| Fig. | 1-13 Median retention time of DRAM cell array at 50% failure versus chip thickness 13          |

| Fig. | 1-14 FHE device with island structure [75]                                                     |

| Fig. | 1-15 Schematic illustrations of advanced FHE with embedded 3D-IC and heterogeneous             |

|      | dielets                                                                                        |

| Fig. | 1-16 Highly integrated FHE with 625 Si dielets                                                 |

| Fig. | 1-17 Schematic of chiplet [85]                                                                 |

| Fig. | 1-18 Chiplet-based processor [84]                                                              |

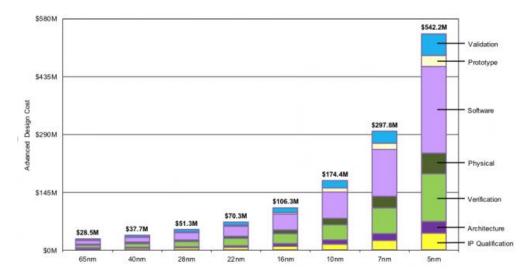

| Fig. | 1-19 Chip Design and Manufacturing Cost under Different Process Nodes [86]                     |

| Fig. | 1-20 Concept of dielet                                                                         |

| Fig. | 1-21 Abdominal CT with contrast enhancement. (A) Axial view, (B) an enlarged axial view,       |

|      | and (C) a three-dimensional image of the arteries. The site of occlusion was the left superior |

|      | gluteal artery (A and B, arrows; C, circle). The low-density area in the enlarged axial view   |

|      | was suspected to be a thrombus (B, arrowhead)[89]                                              |

| Fig. 1-22 Hand-held vascular visualization device. (Upper) Accu Vein[90]. (Lower) Vein Viewer |                                                                                       |    |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----|

|                                                                                               | Flex[91]                                                                              | 21 |

| Fig.                                                                                          | 1-23 Absorption spectra of the oxygenated and deoxygenated hemoglobin molecules[92]   | 22 |

| Fig.                                                                                          | 1-24 Conventional skin display[93]                                                    | 24 |

| Fig.                                                                                          | 1-25 Concept of Smart Skin Display                                                    | 25 |

| Fig.                                                                                          | 1-26 Operation flow of Smart Skin Display                                             | 26 |

| Fig.                                                                                          | 1-27 Key technology of Smart Skin Display                                             | 27 |

| Fig.                                                                                          | 2-1 Flexible printed circuit [10]                                                     | 42 |

| Fig.                                                                                          | 2-2 Horizontal wavy wiring [25]                                                       | 43 |

| Fig.                                                                                          | 2-3 Vertical wavy wiring [19]                                                         | 43 |

| Fig.                                                                                          | 2-4 Construction of the system on a gel substrate using LM paste [34].                | 44 |

| Fig.                                                                                          | 2-5 SEM image of broken Au wiring on PDMS                                             | 45 |

| Fig.                                                                                          | 2-6 Schematic diagram of die shift.                                                   | 46 |

| Fig.                                                                                          | 2-7 Image of a neutral axis                                                           | 50 |

| Fig.                                                                                          | 2-8 Process flow of flexible multilayer wiring                                        | 51 |

| Fig.                                                                                          | 2-9 Schematic diagram of repeated bending test                                        | 52 |

| Fig.                                                                                          | 2-10 Photo of repeated bending test                                                   | 52 |

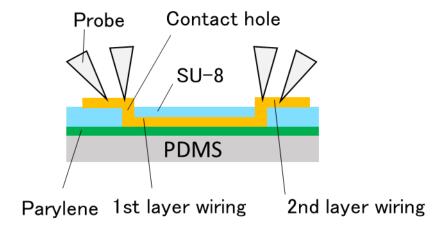

| Fig.                                                                                          | 2-11 Cross-section of flexible wiring with a passivation layer                        | 54 |

| Fig.                                                                                          | 2-12 Process flow of flexible wiring with a passivation layer                         | 54 |

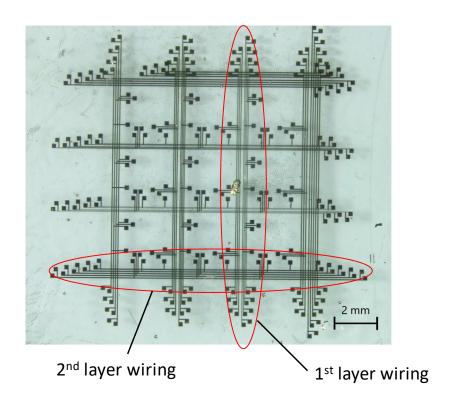

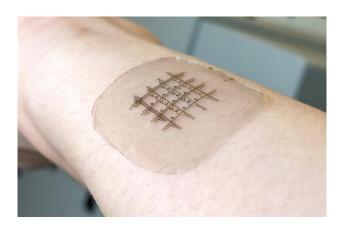

| Fig.                                                                                          | 2-13 A photo of the fabricated multilayer wirings on PDMS                             | 56 |

| Fig.                                                                                          | 2-14 Flexible multilayer wiring on a human arm                                        | 56 |

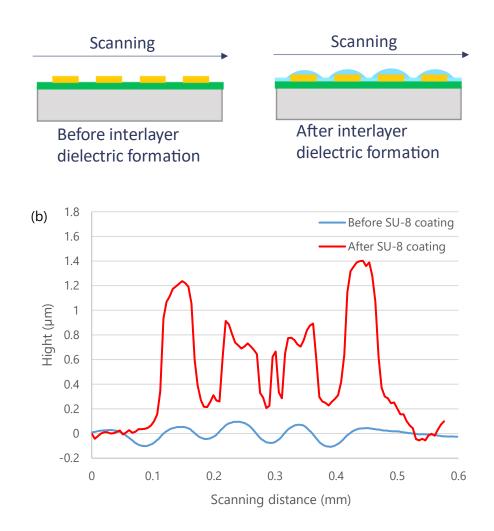

| Fig.                                                                                          | 2-15 Step height before and after SU-8 coating                                        | 57 |

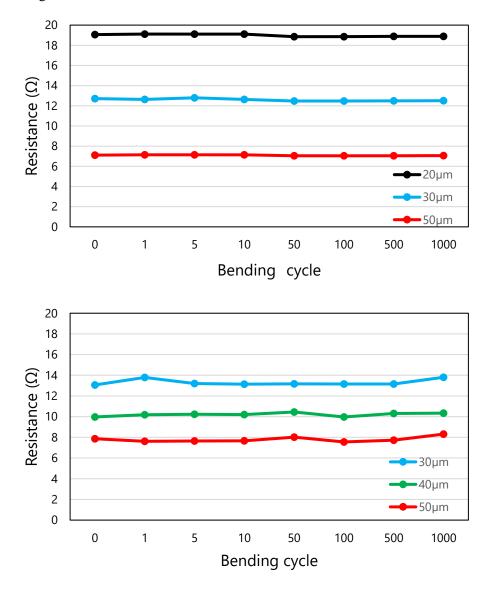

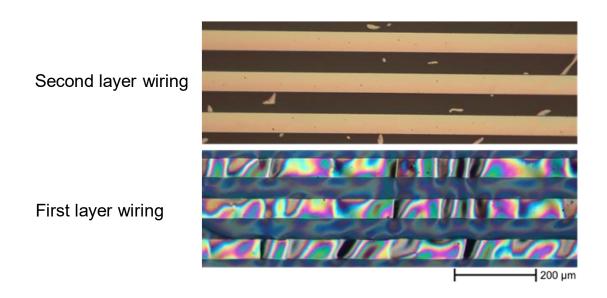

| Fig.                                                                                          | 2-16 Bending properties of first-layer wiring (upper) and second-layer wiring (lower) | 58 |

| Fig.                                                                                          | 2-17 Cross-sectional schematics of the first layer wiring                             | 59 |

| Fig.                                                                                          | 2-18 Photo of first and second layer wiring                                           | 59 |

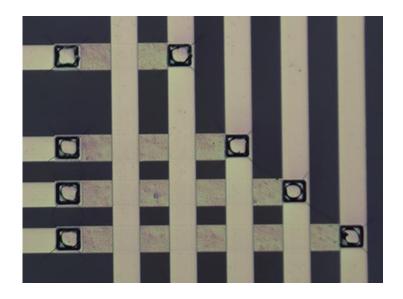

| Fig.                                                                                          | 2-19 Multilayer wiring with the contact hole                                          | 60 |

| Fig. 2-20 Cross-section of electrical characterization with a flexible multilayer wiring         | 60      |

|--------------------------------------------------------------------------------------------------|---------|

| Fig. 2-21 Bending property of flexible multilayer wiring                                         | 61      |

| Fig. 2-22 Fabricated sample of flexible wiring with a passivation layer                          | 62      |

| Fig. 2-23 Bending property of flexible wiring with a passivation layer                           | 62      |

| Fig. 2-24 Process flow of PDMS compression molding with anchoring layer                          | 63      |

| Fig. 2-25 Die shift without anchoring layer                                                      | 64      |

| Fig. 2-26 Die shift reduction by anchoring layer                                                 | 65      |

| Fig. 3-1 Commercially available micro-LED display by Sony (upper)[9] and Samsung (lower          | r) [10] |

|                                                                                                  | 77      |

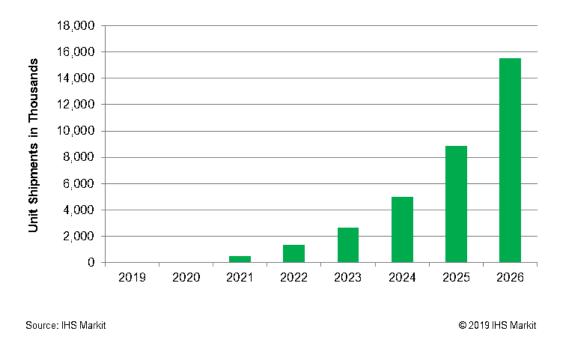

| Fig. 3-2 Global micro-LED market shipment forecast [11].                                         | 78      |

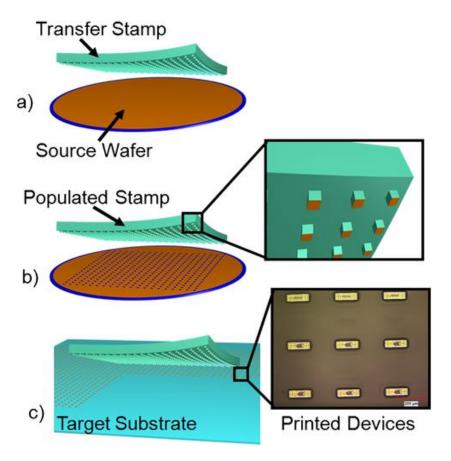

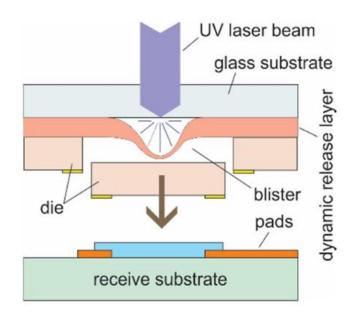

| Fig. 3-3 Transfer stamping process [20]                                                          | 79      |

| Fig. 3-4 Roll transfer process [23]                                                              | 80      |

| Fig. 3-5 Laser transfer process [24]                                                             | 80      |

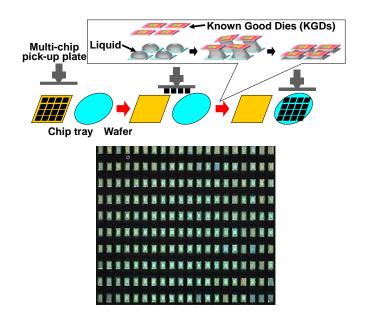

| Fig. 3-6 Blue micro-LED chips (75 $\mu m$ by 125 $\mu m$ ) self-assembled in batches by liquid s | urface  |

| tension.                                                                                         | 81      |

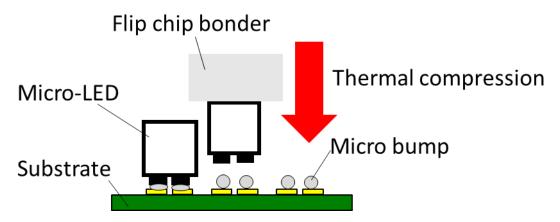

| Fig. 3-7 Schematic diagram of micro-LED bonding with a micro bump                                | 82      |

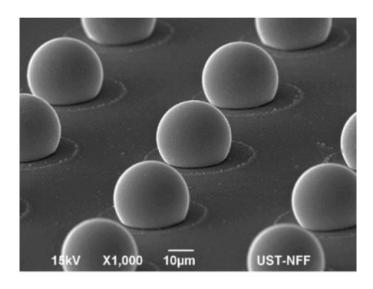

| Fig. 3-8 SEM image of micro bumps [32]                                                           | 82      |

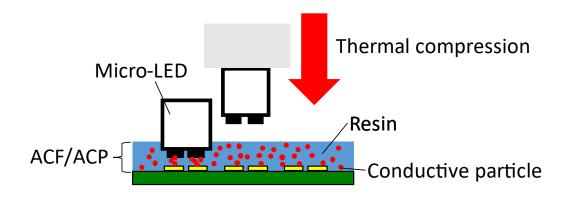

| Fig. 3-9 Schematic diagram of micro-LED bonding with ACF/ACP                                     | 82      |

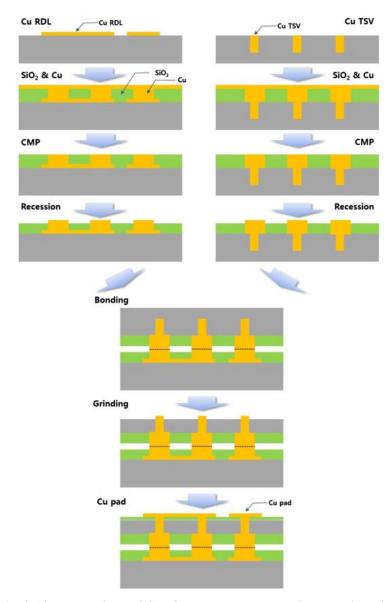

| Fig. 3-10 Process flow of Cu–Cu thermal compression bonding [45].                                | 85      |

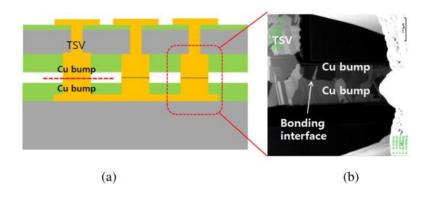

| Fig. 3-11 (a) schematic of wafer level stacking (b) FIB image of bonding interface [45]          | 85      |

| Fig. 3-12 Schematic of hybrid bonding [53]                                                       | 86      |

| Fig. 3-13 Typical failure modes of thin Si die [76]                                              | 88      |

| Fig. 3-14 Microtube for fine-pitch bonding at room temperature [87].                             | 89      |

| Fig. 3-15 Room-temperature bonding technology using nanowires.                                   | 89      |

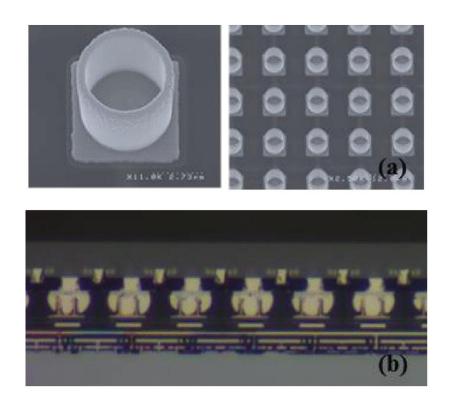

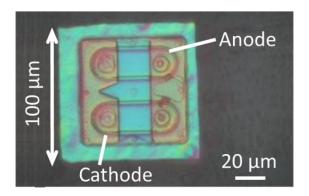

| Fig. 3-16 100µm cubic micro-LED.                                                                 | 91      |

| Fig. 3-17 Process flow of electroplated Cu direct bonding                                        | 91      |

| Fig. 3-18 Micro-LED arrangement and aperture pattern.                                           | 92     |

|-------------------------------------------------------------------------------------------------|--------|

| Fig. 3-19 Micro-LEDs temporarily fixed on photosensitive resin                                  | 93     |

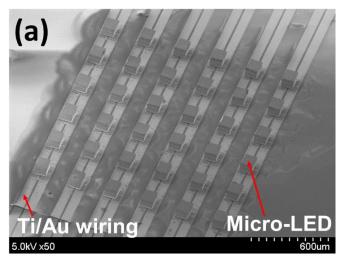

| Fig. 3-20 Micro LED array bonded by electroplated Cu direct bonding (a) and magnified n         | nicro- |

| LED (b)                                                                                         | 94     |

| Fig. 3-21 Cross-section of HBM[89]                                                              | 95     |

| Fig. 3-22 Micro-LED emitting light.                                                             | 95     |

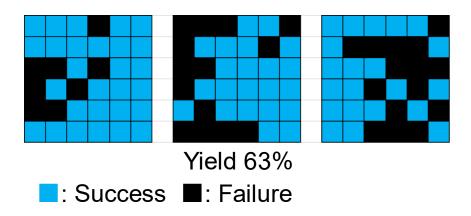

| Fig. 3-23 Yield mapping of electroplated Cu direct bonding                                      | 96     |

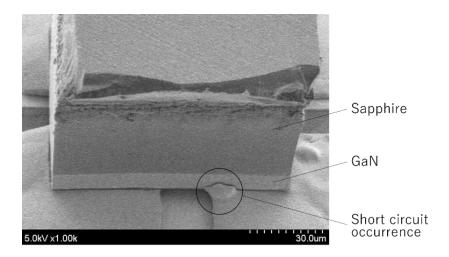

| Fig. 3-24 Sidewall plating with bonded LEDs                                                     | 97     |

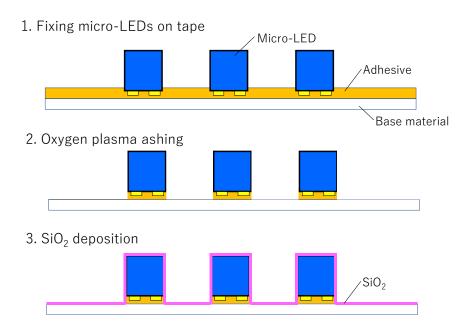

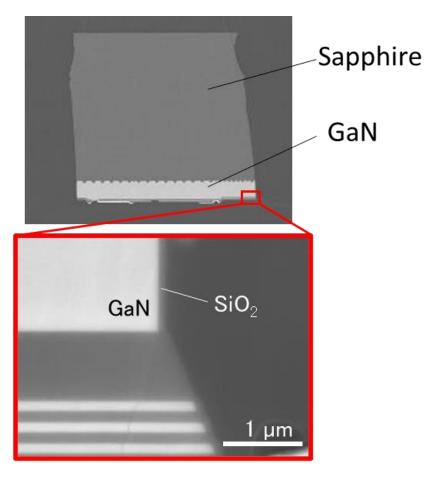

| Fig. 3-25 Process flow of OER-SiO2-CVD on the side wall of the micro-LEDs                       | 98     |

| Fig. 3-26 Cross-section of micro-LED sidewall with SiO2                                         | 98     |

| Fig. 3-27 Evaluation method of additional tilt compensation                                     | 99     |

| Fig. 3-28 Comparison of compensation temperature                                                | 100    |

| Fig. 3-29 Optimized process flow of electroplated Cu direct bonding                             | 101    |

| Fig. 3-30 Yield mapping of optimized electroplated Cu direct bonding                            | 102    |

| Fig. 3-31 the photo of a μLED array emitting light.                                             | 102    |

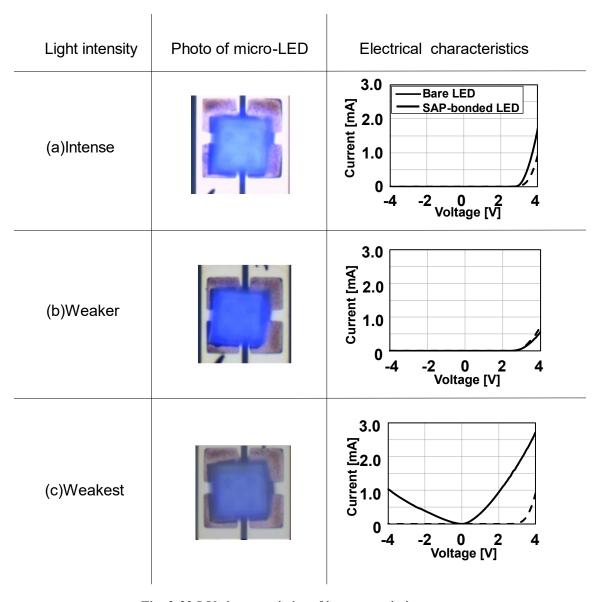

| Fig. 3-32 I-V characteristics of intense-emission.                                              | 104    |

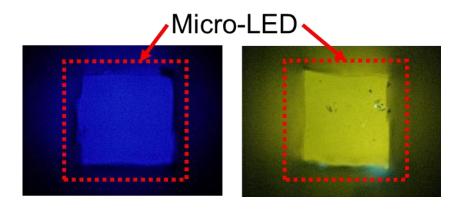

| Fig. 3-33 Fluorescence microscope of intense micro-LED(left) and weakest micro-LED (            | right) |

|                                                                                                 | 105    |

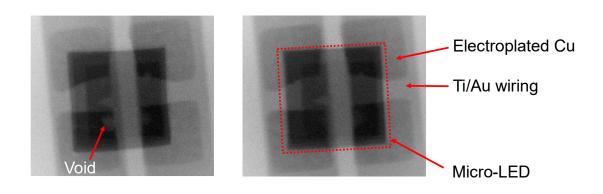

| Fig. 3-34. X-ray transmission image of the intense (left) and weakest (right) emission micro-I  | LEDs.  |

|                                                                                                 | 105    |

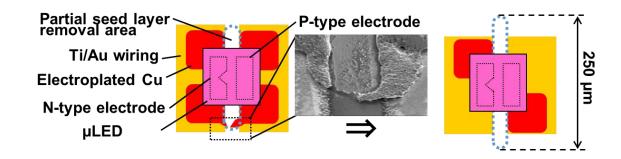

| Fig. 3-35 SEM image of an inter-pillar bridge formed at the interface between the photosen      | sitive |

| resin and a wafer, and current and proposed aperture/pre-etch seed designs                      | 105    |

| Fig. 4-1 Comparison of stacking methods for 3D integration.                                     | 118    |

| Fig. 4-2 Classification of the TSV formation process [18]                                       | 119    |

| Fig. 4-3 Typical process flow of TSV [32]                                                       | 123    |

| Fig. 4-4 Via fill failures owing to poor coverage of conventional sputtered barrier/seed layers | s. 124 |

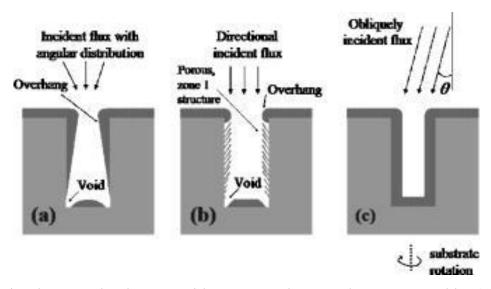

| Fig.  | 4-5 Films deposited in trenches/vias by conventional physical vapor deposition (PVD)       | _    |

|-------|--------------------------------------------------------------------------------------------|------|

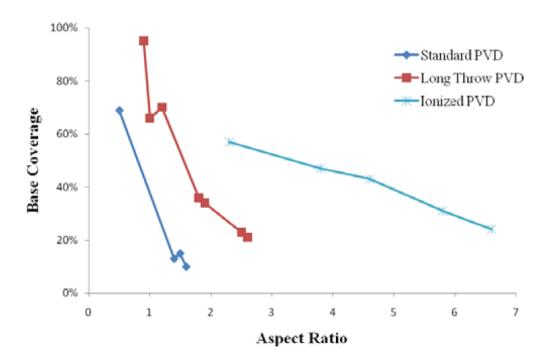

| Fig.  | 4-6 Comparison of the effect of different PVD techniques on base coverage at increasing as |      |

|       | ratio (TSV diameter: 15 μm) [33]                                                           | 125  |

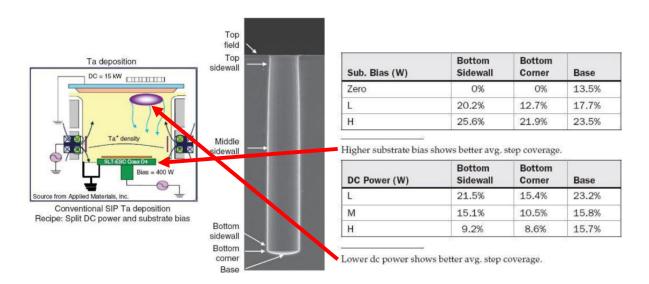

| Fig.  | 4-7 Step coverage of Ta barrier on TSV with different DC power setting and substrate bid   | ases |

|       | of iPVD [38]                                                                               | 127  |

| Fig.  | 4-8 Step coverage of Cu seed on TSV with different DC power setting and substrate biase    | s of |

|       | iPVD [38]                                                                                  | 128  |

| Fig.  | 4-9 TSV filling performance for iPVD [39]                                                  | 128  |

| Fig.  | 4-10 Structure of sputtering tool used in this study and distance between sample and m     | etal |

|       | targets (Ti and Cu)                                                                        | 130  |

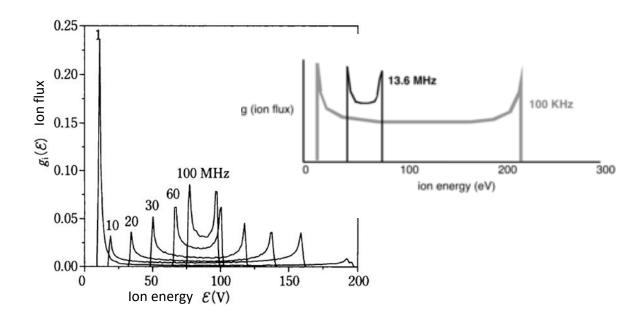

| Fig.  | 4-11 Calculated ion energy distribution function (number of ions vs. ion energy) for argo  | n at |

|       | "high" and "low" frequencies; data from Dry Etching for VLSI, van Roosmalen et. al         | 132  |

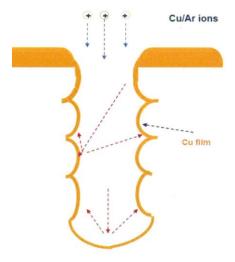

| Fig.  | 4-12 The re-sputtering effect to deposit Cu at the hidden part by large scallop            | 132  |

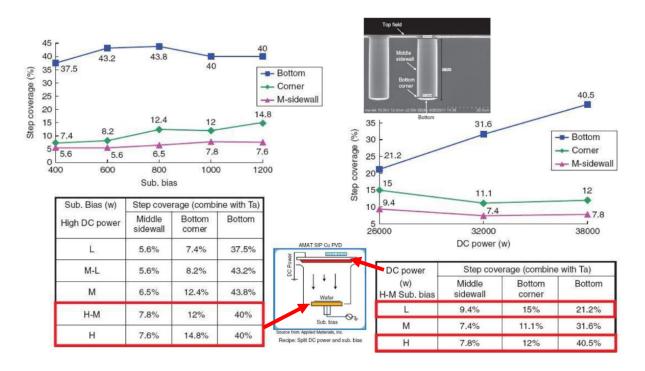

| Fig.  | 4-13 Step coverage of Ti/Cu deposited with long-throw iPVD with low-frequency subst        | rate |

|       | RF bias (via diameter: 5 $\mu$ m, via depth: 50 $\mu$ m, and aspect ratio: 5)              | 133  |

| Fig.  | 4-14 Dependence of step coverage of Cu/Ti on RF bias frequency (via diameter: 5 μm,        | via  |

|       | depth: 50 μm, and aspect ratio: 5)                                                         | 133  |

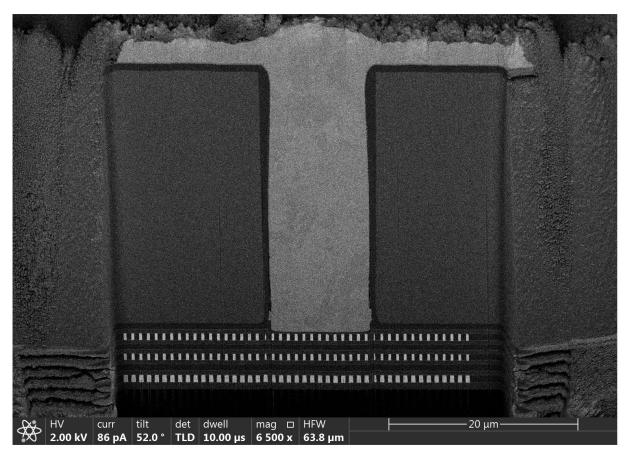

| ig. 4 | -15 SEM of high aspect ratio TSV                                                           | 135  |

| Fig.  | 4-16 Layout of LSI dielet                                                                  | 136  |

| Fig.  | 4-17 Block diagram of pixel circuit                                                        | 136  |

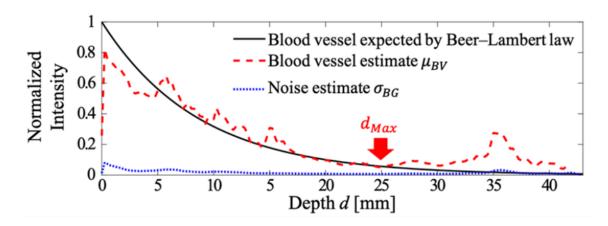

| Fig.  | 4-18 Relative light absorption and blood vessel depth[42]                                  | 138  |

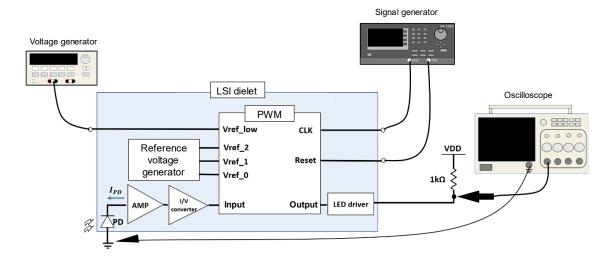

| Fig.  | 4-19 Measurement experiment of LSI dielet                                                  | 139  |

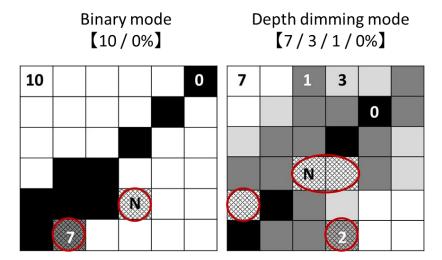

| Fig.  | 4-20 Imaging result of LSI dielet                                                          | 140  |

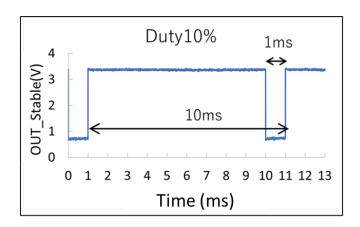

| Fig.  | 4-21 Output signal of binary mode.                                                         | 140  |

| Fig.  | 4-22 Output signal of depth dimming mode.                                                  | 141  |

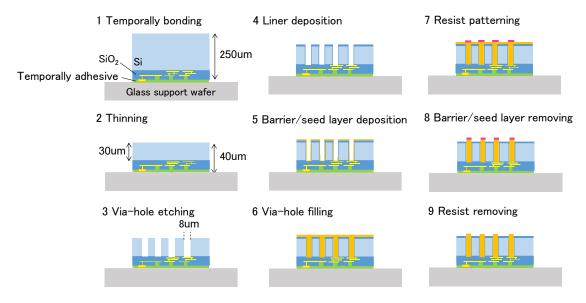

| Fig. 4-23 Process flow of 3D-IC dielet                                                        |

|-----------------------------------------------------------------------------------------------|

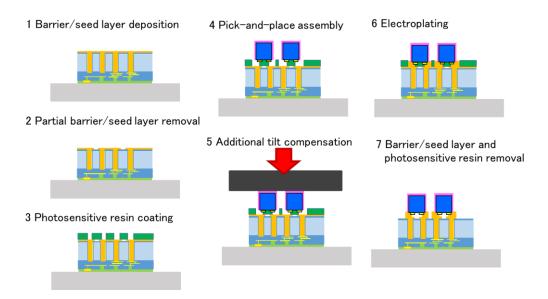

| Fig. 4-24 Process of 3D integration with micro-LED                                            |

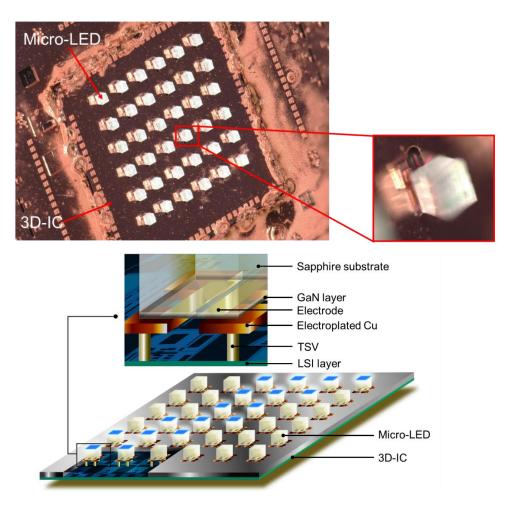

| Fig. 4-25 A photomicrograph and schematic of micro-LEDs stacked on a thin 3D-IC dielet 144    |

| Fig. 4-26 A cross-sectional SEM image of Cu-TSV formed with a standard PVD                    |

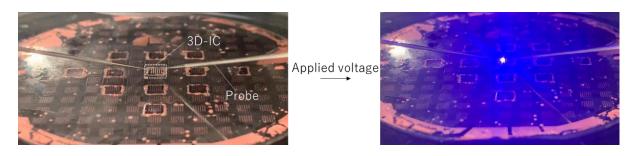

| Fig. 4-27 Luminescent micro-LEDs on the 3D-IC                                                 |

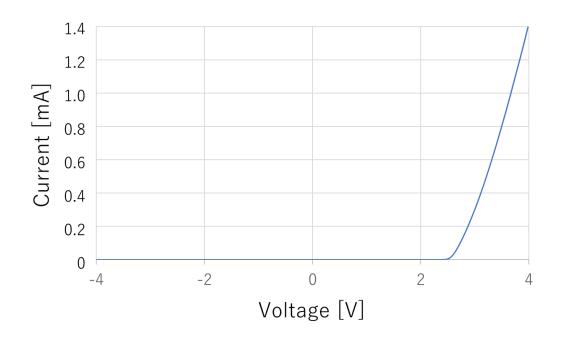

| Fig. 4-28 Electrical characteristics of a micro-LED on the 3D-IC                              |

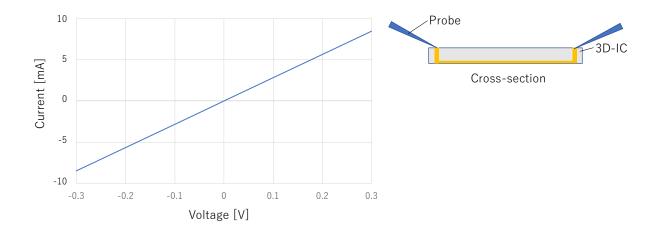

| Fig. 4-29 Electrical characteristic of a pair of TSV in 3D-IC                                 |

|                                                                                               |

| List of Tables                                                                                |

| Table 1-1 A comparison of the organic interposer and Si interposer [42]                       |

| Table 1-2 Comparison of flexible device fabrication technology                                |

| Table 1-3 Specification and requirements for Smart Skin Display                               |

| Table 2-1 Thermomechanical and fluidic force effects on die shift described in previous FOWLP |

| works with rigid epoxy mold compounds                                                         |

| Table 2-2 Young's modulus of each material in the multilayer wiring                           |

| Table 2-3 Young's modulus of each material in flexible wiring with the passivation layer 53   |

| Table 2-4 Comparison of die shift without and with anchoring layer                            |

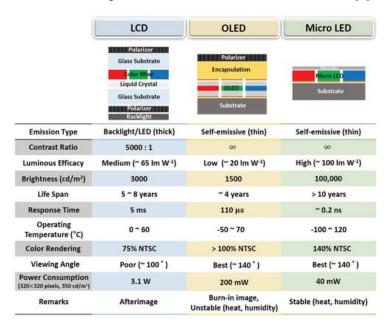

| Table 3-1 Comparison of LCD, OLED, and micro-LED [5]                                          |

| Table 3-2 Comparison of micro-LED application requirements [7]                                |

| Table 3-3 Comparison of thermal compression bonding (TCB) and room temperature hybrid         |

| bonding (HB) [53]87                                                                           |

# Chapter 1

# Introduction

## 1.1 Background

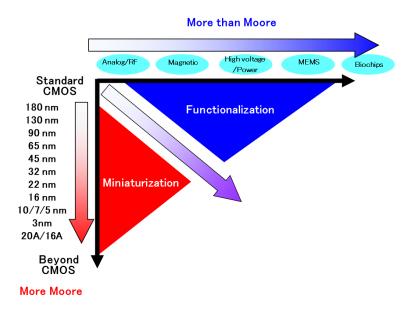

Over the years since the invention of the transistor, a large-scale integrated circuit (LSI) has continued to get smaller, according to Moore's Law [1]. Today, 3nm processes are in production [2]-[4], while 2 nm [5][6] and 16Å processes are also developing. Process node shrinking leads to improved LSI performance and lower power consumption. However, Moore's law has decreased since 2000, and the gap between Moore's law projection and actual chip performance has grown 15-fold by 2008. Spurring this slowdown is the declining cost-effectiveness associated with the shrinking of LSI manufacturing processes. The post-Moore era is anticipated to begin in the future [7], and a strategy is being taken to boost performance that combines miniaturization and functionalization, as shown in Fig. 1-1.

Fig. 1-1 LSI performance improvement approach.

## 1.2 Heterogeneous integration

Monolithic stacking of III-V device layers on Si or GaAs wafers for optoelectronic applications has kicked off investigations on heterogeneous integration [8]. At that time, multichip modules were the term used [9][10]. Until the late 1990s, conventional heterogeneous integration had been restricted to the fabrication of heterojunctions, such as., GaAs/GaAlAs, and heterostructures with multi-wavelength LEDs. Over the past two decades, flip-chip bonding technology for even small chips has been employed extensively in industry, and heterogeneous integration research has been extended to include additional areas, such as microelectromechanical systems (MEMS) [11] and sensors [12]. Meanwhile, heterogeneous integration works have been moving beyond 2D structures to 3D [1].

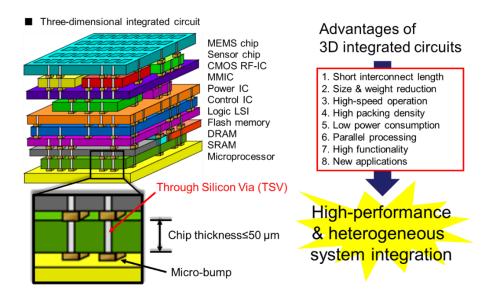

At first, fully 3D-integrated IC (3D-IC) attracted attention as a high-performance and multipurpose heterogeneous integration [2]-[6]. 3D-ICs require chips thinner than a few tens of m, because of their limited mechanical strength they are prone to warpage and residual stress problems and Joule heat [7]-[9].

Fig. 1-2 Features of 3D-IC

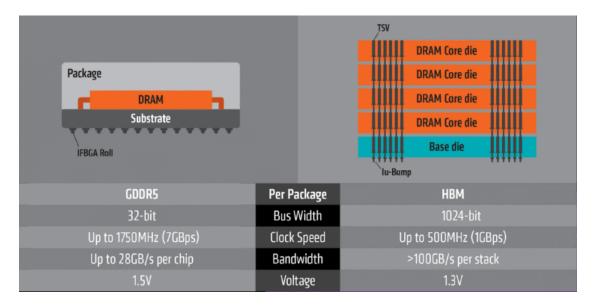

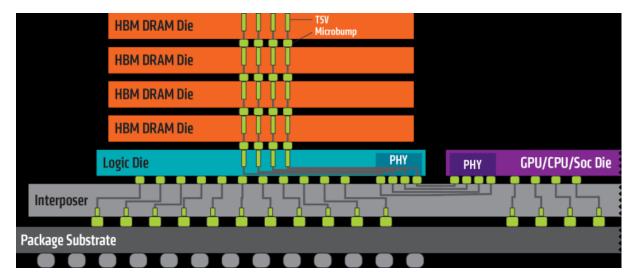

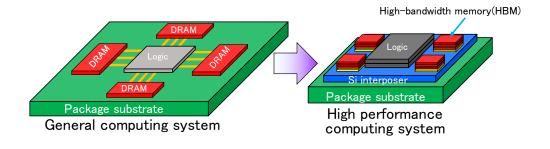

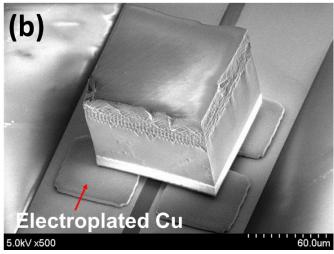

3D-IC is undoubtedly a very promising technology, but it also has many difficulties. Because of this, current research has focused heavily on heterogeneous integration, which is based on 3D-IC technology. More recently, 3D-DRAM [10][11] has been divided into several high-bandwidth memory (HBM) [12]-[15] and heterogeneously integrated with CPUs. A comparison of high-bandwidth memory (HBM) and conventional DRAM is given in Fig. 1-3; HBM uses 3D stacking To dramatically increase the number of inputs and outputs, resulting in a very wide overall bandwidth. The most recent standard, HBM3, has a bandwidth of 896 GB/s [16]. As seen in Fig. 1-4, silicon interposers connect the HBM and logic, as described below.

Fig. 1-3 Comparison of conventional DRAM and HBM [14]

Fig. 1-4 Cross-section of HBM package [14]

Such a heterogeneous integration architecture is also increasingly used to three-dimensionally stack logic chips manufactured at different technology nodes [17] as shown in Fig. 1-5.

Fig. 1-5 Schematic of heterogeneous integration

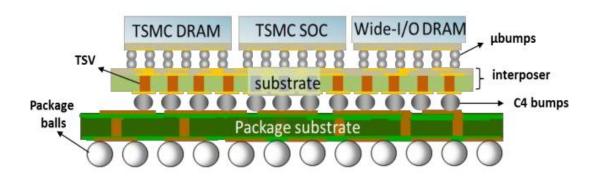

The 2.5D package, which incorporates the aforementioned Si interposer and interconnects the chips, is known as a 2.5D package. Chip on Wafer on Substrate (CoWoS) technology, created by TSMC, served as the foundation for 2.5D packages [18]-[22], CoWoS is displayed in Fig. 1-6. The Si interposer is the key component of CoWoS, which preserves the advantages of integrating numerous dies while avoiding the problems that 3D-ICs have, such as heat

difficulties [23]. Si interposer has the following benefit: (1) Smaller form factor (total circuitry size) in comparison to PCB-board integration, (2) much higher bandwidth between memory and logic dies, (3) lower power consumption because there are fewer large IOs among chips on a PCB board, and (4) quicker turn-around time to integrate multiple-node chips without implementing cutting-edge technology from scratch[24]. For these reasons, Si interposers attracted much attention [25][26].

Fig. 1-6 Schematic of CoWoS [22].

Furthermore, organic interposers have attracted attention in recent years [27]-[29]. The size of Si interposers that can be produced using the wafer process is limited by the size of the reticle used for lithography. This precludes the integration of big ASICs with high functionality that need lots of HBMs. Organic interposers, on the other hand, can be used in greater sizes because they are made at the panel level. Table 1-1 shows a comparison of the Si interposer and the organic interposer.

Table 1-1 A comparison of the organic interposer and Si interposer [30]

| Features                                               | Organic Interposer               | Silicon Interposer |

|--------------------------------------------------------|----------------------------------|--------------------|

| Cu Wiring<br>(Dielectric)                              | SAP Pattern Plating<br>(Organic) | Damascene (Oxide)  |

| Front Side UBM or<br>pad size / pitch<br>(min.)        | 30 / 55 μm                       | 25/55 μm           |

| Front Side wiring<br>line / space /<br>thickness (min) | 6/6/10 µm                        | 0.5 / 0.5 / 1.0 μm |

| Number of routing<br>layers (typical)                  | 10                               | 4                  |

| Wiring layer via<br>size                               | 20 μm                            | 1.0 µm             |

| PTH or TSV size /<br>pitch / depth                     | 57 / 150 / 200 μm                | 10 / 50 / 100 μm   |

| Back Side UBM or<br>pad size / pitch                   | 100 / 150 μm                     | 100 / 150 μm       |

| Back Side wiring<br>line / space /<br>thickness (min)  | 6/6/10 µm                        | 10 / 10 / 1.0 μm   |

#### 1.3 Fan Out Wafer Level Packaging (FOWLP)

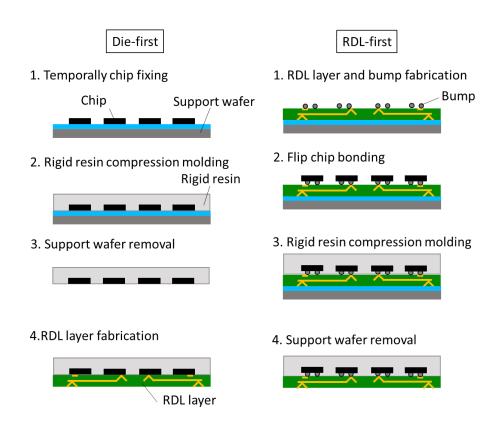

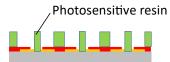

FOWLP: RDL-first, in which the chip is bonded after wiring is created, and die-first, in which the chip is enclosed in hard resin before wiring is created.

The corresponding process flows are shown in Fig. 1-7 [31]. Die-first method, in particular, does not necessitate bumps, thus allowing for a low-profile package and streamlining the procedure. Due to these characteristics, FOWLP, including integrated fan-out (inFO) [32]-[34], which is a derivative of die-first FOWLP, is employed in the production of mobile processors, where space-efficiency and cost-efficiency are crucial considerations.

However, it is now also being utilized for packaging for heterogeneous integration, due to its capacity to combine many types of chips [35]-[37]. FOWLP is applied to applications where performance is critical, such as the production of processors for Tesla's Dojo supercomputer [38],

which does machine learning for automatic driving. The technology is also being used in situations where performance is crucial.

Fig. 1-7 Process flow of two type FOWLP

## 1.4 Flexible hybrid electronics

In recent years, wearable devices, implantable devices, and the Internet of Things have become increasingly popular as devices have become smaller and lighter, and the development of wireless communications made it easier for device-to-device connections, thus diversifying the applications of electronic devices. However, conventional devices are limited by the shape of their internal printed circuit boards, making them impossible to bend. Because of this, flexible devices using flexible substrates instead of rigid printed circuit boards have recently been developed, and

many flexible devices based on organic semiconductors [42][43][44] and thin film transistors (TFT) [45][46]have been reported. However, there are several problems with conventional flexible devices using organic semiconductors: First, the electron mobility of organic semiconductors is lower than that of inorganic single-crystal semiconductors such as Si. The hole electron mobility of organic semiconductors has been increasing year by year, and some organic semiconductors with electron mobility exceeding 30 cm2V-1s-1 have been reported in hole-transporting semiconductor polymers [47]-[51], However, it falls short of the 450 cm²/Vs hole electron mobility of single-crystal silicon. Since electron mobility is an important factor in determining the processing speed and power consumption of a circuit, it is challenging to construct high-performance devices that perform high-speed operations in organic semiconductors as it is with inorganic single-crystal semiconductor devices. The switching frequency of organic transistors is several MHz [52][53], which is significantly slower than the GHz switching frequency of inorganic semiconductor transistors.

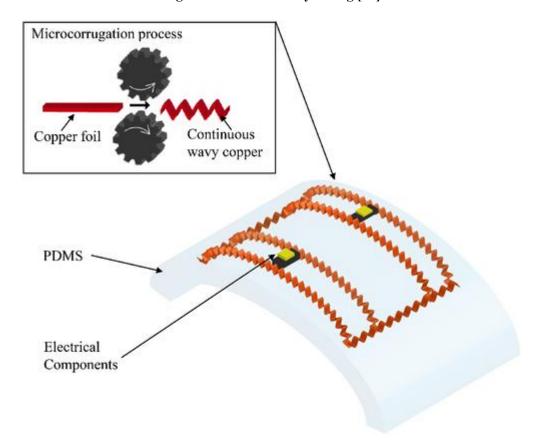

The second problem is that it is challenging to produce printed wiring. The wiring width of ordinary printed electronics is several millimeters to several tens of millimeters [54][55], making it challenging to achieve high circuit integration and construct compact, high-performance devices. Since conventional printing methods such as inkjet and gravure are difficult to miniaturize, methods such as self-assembling metallic nano ink by combining hydrophobic and hydrophilic patterns have been proposed 0. Although this method can construct finer wiring than current methods, it is not yet practical because the resistance increases rapidly below 1 m[57].

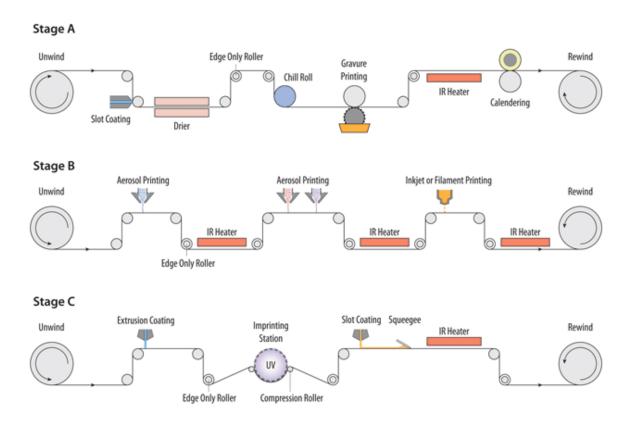

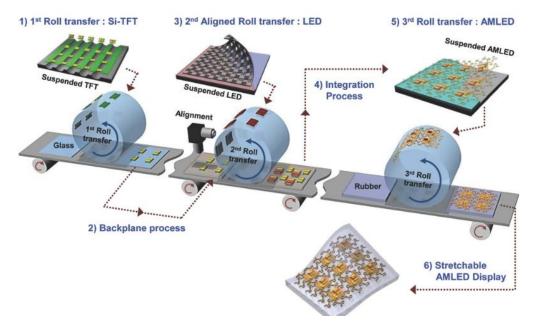

The third problem is involved in the roll-to-roll procedure [58]. It is a method of creating circuits wherein rolled flexible boards are fed from one side of the production line and processed as shown in Fig. 1-8. It is then rolled up again on the other side of the production line before moving on to the next process. It costs money to transport distinct substrates that have been

separated from the start of the operation in the traditionally manufacturing process that uses rigid substrates. The Roll-to-Roll method is expected to lower costs by connecting several manufacturing lines for continuous processing. However, it has been shown that during large-area sheet processing, the roll-to-roll operation results in sheet deformation [60]. This decreases yields and results in severe alignment errors. These problems issues have prevented, conventional flexible devices from performing as well as inorganic single-crystal semiconductor devices.

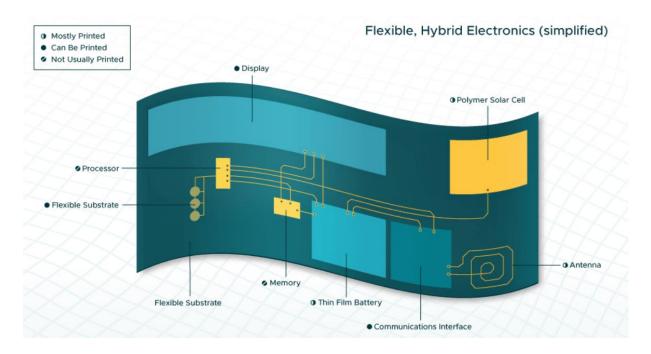

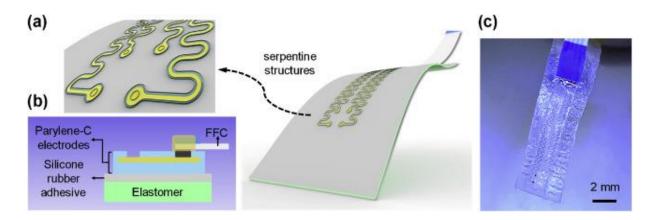

The field of flexible hybrid electronics (FHE) has been attracting attention [61][62]. FHE blends standard inorganic semiconductor device production with flexible electronics employing organic semiconductors. Devices with both high flexibility and high performance can be produced through FHE. A conceptual diagram of FHE is shown in Fig. 1-9. The FHE is a flexible substrate with a printed wiring system. Therefore, FHE can create flexible devices with the performance of traditional LSI chips. Flexible and biocompatible organic materials can be attached to or attached to the human body. Inorganic semiconductor chips with high-speed calculation capabilities are also suitable for processing complicated biological signals. For these reasons, FHE has attracted considerable interest in the medical and healthcare fields.

Fig. 1-8 Roll-to-roll process [59]

Fig. 1-9 Conceptual images of FHE [63]

#### 1.4.1 Conventional FHE

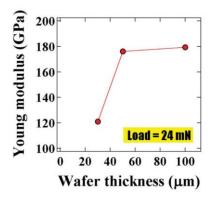

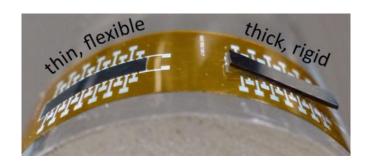

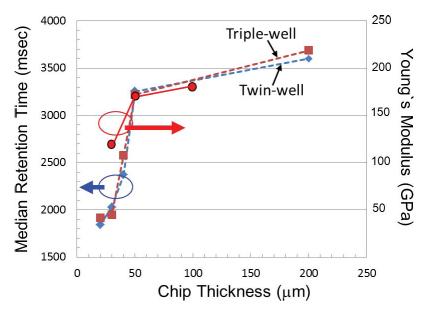

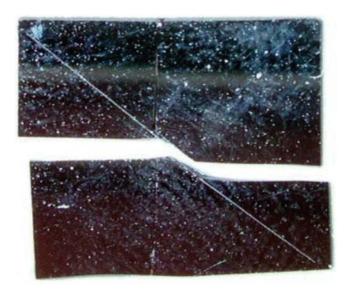

It has been discovered that single-crystalline Si exhibits flexibility when manufactured extremely thin (𝒯). As illustrated in Fig. 1-10, when Young's modulus of a Si wafer is assessed using a nano indenter, Young's modulus rapidly decreases at a thickness of 50 μm or less. As seen in Fig. 1-11, it becomes so flexible that it can be easily bent by a finger. For the typical FHE process ultrathin dies (20 μm or less in thickness) must be created by backside grinding so they can be bent and follow curved profiles 0-[66]. The ultrathin dies can be technologically fabricated down to 7 μm or less [67][68]. The manufacture of flexible electronics using this property has been suggested [69]. Fig. 1-12 shows the concept of FHE using an ultrathin Si wafer. By embedding an LSI chip with an ultrathin Si chip in a flexible resin, flexibility is given to the entire device. However, one of the issues with devices using ultrathin Si chips is reported to be the degradation of device properties due to the thinning of Si (𝒯). A Young's modulus falls as DRAM chips with planar capacitors get thinner, as seen in Fig. 1-13, However, retention time gets shorter. This is hypothesized to be caused by the lattice structure distortion when the Si wafer becomes ultrathin. In addition, the durability against repeated bending has not been adequately evaluated, and the reliability is low.

Another issue is that the mechanical strength of the ultrathin dies is determined by thinning processes (chemical mechanical polishing, plasma etching, dry polishing, kai-dry polishing, poly grinding, ultra-poly grinding, #2000, etc.) [70]. Simple saw dicing and cost-effective mechanical grinding with dry polishing are not enough to relieve the mechanical stress and remove microcracks at the chip edges. Other intriguing methods to create ultrathin dies without using mechanical thinning procedures include a spalling technology [71] and transfer technologies from SOI wafers [72]-[74].

Fig. 1-10 Young's modulus variation versus wafer thickness

Fig. 1-11 Ultrathin Si wafer

Fig. 1-12 FHE using ultrathin Si

Fig. 1-13 Median retention time of DRAM cell array at 50% failure versus chip thickness.

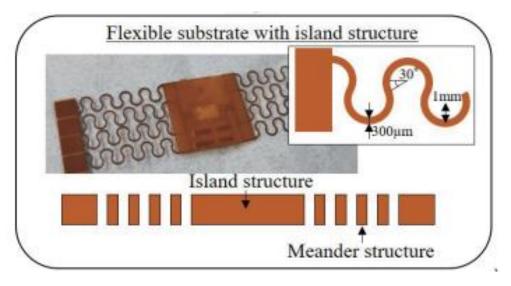

FHE uses flexible wiring to connect the mounting region of semiconductor chips known as an island [75]. The flexible wiring absorbs bending stress in this technique, so no stress is placed on the semiconductor chip. Therefore, stress-related fluctuations in chip properties can be reduced. However, because of the extensive flexible wiring in this device, performance improvement cannot be anticipated despite the high integration.

Fig. 1-14 FHE device with island structure [75]

#### 1.4.2 New FHE in this study

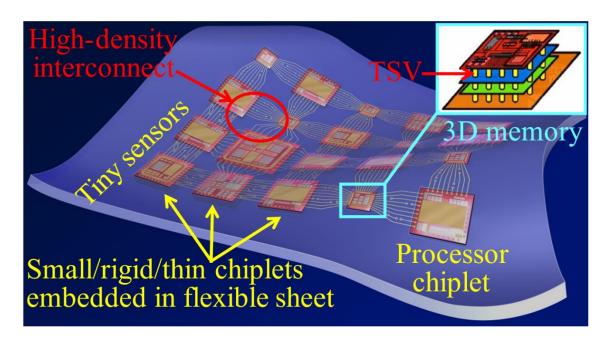

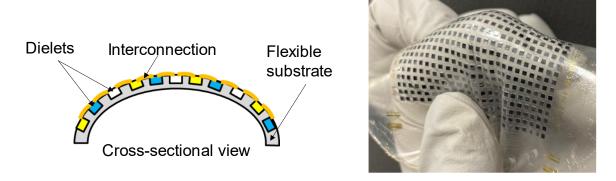

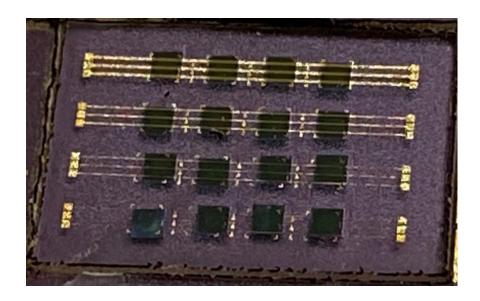

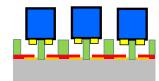

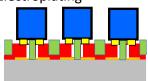

I have talked about the problems with traditional FHE. Our laboratory has suggested a new flexible device structure [75][77]. Table 1-2 compares traditional flexible device technologies. The FHE devices in this research aim to solve the with traditional technologies and create highperformance flexible devices. This device uses inorganic single-crystal semiconductors, especially Si, and does not use organic, amorphous, or polycrystalline semiconductors. Additionally, the system can be highly flexible without bending Si itself and can achieve high performance. This highly integrated FHE applies the fan-out wafer-level packaging (FOWLP) procedure [78], in which several small LSI chips are embedded in a flexible substrate and connected with fine wiring created by a wafer-level process. The suggested procedure is to achieve high integration of FHE by embedding several small LSI chips in a flexible substrate and connecting them with fine wiring created by a wafer-level process as illustrated in Fig. 1-15. several moderately thin, rigid, small LSI chips are embedded in a flexible organic substrate, and the organic substrate between the chips bends to create high flexibility in the entire system. Since the chips are not very thin, devices can be made without affecting the performance of traditional LSI chips. In addition, wiring formation at the wafer level, which is a comparable step to the traditional Si device fabrication process connects chips tightly. Fig. 1-16 shows an actual FHE with 625 Si chips implanted in a flexible substrate.

Fig. 1-15 Schematic illustrations of advanced FHE with embedded 3D-IC and heterogeneous dielets.

Fig. 1-16 Highly integrated FHE with 625 Si dielets

Table 1-2 Comparison of flexible device fabrication technology

|                  | Si Electronics                                    | Organic electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Conventional FHE                     | New FHE in this<br>work                           |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------|

|                  |                                                   | The same of the sa | Jacobse thick read                   |                                                   |

| Device materials | Inorganic single<br>crystalline<br>semiconductors | Organic<br>semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Inorganic and organic semiconductors | Inorganic single<br>crystalline<br>semiconductors |

| Interconnects    | Photolithography                                  | Printing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Printing                             | Photolithography                                  |

| Processing       | Sheet-level                                       | Sheet-level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sheet-level                          | Wafer-level                                       |

| Performance      | High                                              | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | High                                 | High                                              |

| Reliability      | High                                              | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Low                                  | High                                              |

| Flexibility      | Low                                               | Extremely high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Midium                               | High                                              |

## 1.5 Chiplet

Chiplets are system design techniques that integrate numerous module chips into a single package to create hetero-integrated systems [79]-[83]. According to Moore's law, the chiplet is expected to be a potential driver for advancing performance scaling as well as size scaling in the future. The figure illustrates a conceptual diagram of a chiplet. Chiplets are individually constructed functioning blocks. With the aforementioned 3D/2.5D packaging technologies, chiplets are joined by cutting-edge microelectronic packaging techniques such as redistribution layers (RDLs), solder micro bumps, and TSVs. Products incorporating the chiplet are already being sold as high-end processors as shown in Fig. 1-18 [84].

Fig. 1-17 Schematic of chiplet [85]

Fig. 1-18 Chiplet-based processor [84]

As shown in Fig. 1-19, development costs are increasing rapidly as technology nodes become smaller [86]. Therefore, it is getting more and more challenging to continue with traditional monolithic integration. Chiplet may reuse individually made chips, thus efficiently addressing issues such as development cost and time. Chiplets are Si's intellectual property subsystems and not s smaller SoC-partitioned chip (system on a chip). Therefore, standardization is required to integrate chiplets more successfully. The Common Heterogeneous Integration and IP Reuse Strategies (CHIPS) program of the Defense Advanced Research Projects Agency served as the first impetus for the chiplet ecosystem [87]. Standardization is currently being promoted by industry associations led by Intel [88]. Standardized chiplets helped to effectively accelerate the

speed of development but also reduce the development expenses and threshold while also speeding up development., Chip R&D will therefore concentrate on algorithms and basic technologies, greatly increasing the overall level of innovation and capability.

Fig. 1-19 Chip Design and Manufacturing Cost under Different Process Nodes [86]

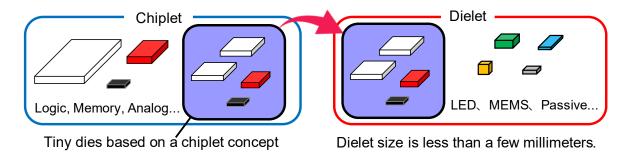

#### 1.6 Definition of dielet

The collection of little die that will be used in the FHE in this investigation is called "dielet." Chiplet is a system design methodology that interconnects chips manufactured in different technology nodes utilizing cutting-edge packaging techniques such as 2.5D packaging To produce a high-throughput, high-performance package. Chiplet is a function-focused idea that considers which technological node to build each functional block. On the other hand, dielet is a concept that emphasizes only geometry. A dielet is a die that is only a few millimeters in size that can be used to build a flexible system using the FHE technology in this research [39]-[41]. Fig. 1-20, a dielet's notion is depicted. In general, chips designed based on chiplets are functional blocks such as logic, memory, and analog circuits that are typically separated from conventional SoC. These chips along with other chips such as sensors, MEMS, passive devices, and optical devices like

VCSELs, LEDs, and mirrors are all included in dielets. This research aims to develop flexible systems with significantly higher integration than traditional flexible devices by incorporating dielets.

Fig. 1-20 Concept of dielet.

#### 1.7 Blood vessel visualization device

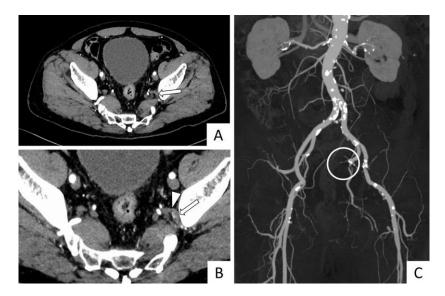

Arteriosclerosis causes stenosis or blockage of blood vessels in the arteries throughout the body. For instance, blocked arteries in the brain can result in cerebral infarction and blocked coronary arteries in the heart can result in angina pectoris or myocardial infarction. When arteries in the limbs get blocked and are unable to deliver nutrients and oxygen sufficiently, symptoms such as coldness at the tips of the limbs and aching muscles occur. This condition is called arteriosclerosis obliterans (ASO). It is crucial to take care of the foot every day because, in the worst-situation, ASO might result in the amputation of the foot. Echocardiography and Computed Tomography (CT) are used to diagnose ASO. The figure displays a CT scan image of an ASO-induced stenosis. These tests require a hospital visit.

Fig. 1-21 Abdominal CT with contrast enhancement. (A) Axial view, (B) an enlarged axial view, and (C) a three-dimensional image of the arteries. The site of occlusion was the left superior gluteal artery (A and B, arrows; C, circle). The low-density area in the enlarged axial view was suspected to be a thrombus (B, arrowhead)[89].

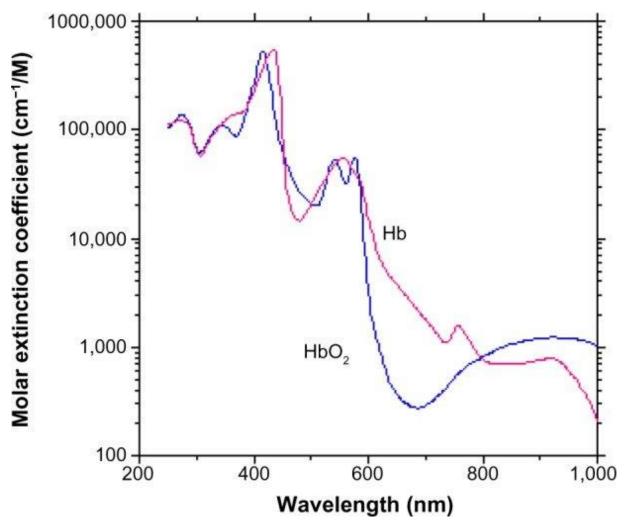

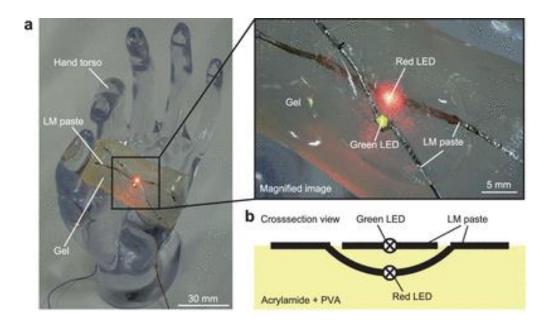

Currently, a portable tool that can visualize blood vessels is in practical use in the medical industry as a vascular imaging tool to help with punctures. Fig. 1-22 shows an illustration of the use of this device. This device can be used at home because it does not require a physician or nurse expertise, like an echo or CT scan, this gadget can be utilized at home. Fig. 1-23 The hemoglobin in red and infrared light absorption spectra is depicted. Hemoglobin in blood vessels tends to absorb infrared light and thus reflects less infrared light than other living tissues. Using this method, the gadget illuminates the skin with infrared light and measures how much light is reflected light to detect blood vessels. However, the device must be utilized at a proper angle and distance from the skin, and the hand-held nature of the device has the drawback that one hand is occupied. Foot care, techniques for preventing foot disease, requires checking blood circulation as well as visually inspecting and palpation of the skin and nail condition of the toes. Therefore, for the vascular visualization device to be a wearable type that allows both hands to be free so that patients can check the blood circulation in their feet as part of foot care.

Fig. 1-22 Hand-held vascular visualization device. (Upper) Accu Vein[90]. (Lower) Vein Viewer Flex[91].

Fig. 1-23 Absorption spectra of the oxygenated and deoxygenated hemoglobin molecules [92].

## 1.8 Smart Skin Display

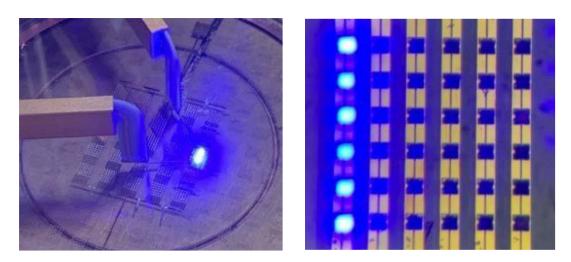

A display that can be affixed to the skin has been proposed [93]. However, the function of skin displays in past research is limited to displaying information. I am suggesting Smart Skin Display, which is depicted in Fig. 1-25. The IR/Red mini-LED, 3D-IC, and micro-LED components of this gadget. The operation flow of Smart Skin Display is shown in Fig. 1-26. Because this device is wearable, it can be palpated with both hands, which is not possible with traditional hand-held devices. As a result, the technology makes it easier for healthcare professionals can use the device

to diagnose ASO. In addition, the device can assist with a puncture in the same way as conventional devices. A puncture is invasive and carries risks such as infection. In addition, the blood vessels' appearance differs from person to person. The strain on the patient is reduced because puncture may be performed reliably, even in patients with poor blood vessel visibility, because of the device's ability to visualize blood vessels. Furthermore, Smart Skin Display also has functions for measuring heart rate and oxygen saturation (SpO<sub>2</sub>) that are not available with conventional devices. Therefore, Smart Skin Display alone can complete the collection of biometric information required for diagnosis.

IR and red light are irradiated onto the human arm, and a photodiode measured the intensity of the reflected light from the subcutaneous tissue and hemoglobin in the 3D-IC chip to monitor pulse wave and SpO<sub>2</sub>. These signals are processed in the 3D-IC and transferred through an LED driver included in the 3D-IC to a blue micro-LED that is stacked vertically on the 3D-IC. In the end, the device will show visual blood information. As previously mentioned, the result information is visualized by a flexible micro-LED display called Smart Skin Display. In this study, a highly functional flexible display that can acquire and interpret biological information was created by combining the dielets with the FHE technology. The specifications for Smart Skin Display are inTable 1-3. For bending durability, the bending radius was set at 2 cm, given that the average human wrist is approximately 5 cm, wide [94]. 1,000 bending cycles were designed to endure bending for more than one year, even when used once a day, designed to endure durability to withstand severe bending of 1 mm is also necessary due to the potential for bending during handling.

There are four key technologies to accomplish the advanced FHE integration, as depicted in Fig. 1-27. 1) Multi-level metallization on a flexible substrate 2) Die shift reduction, 3) Room-temperature bonding of micro-LED, and 4) assembly, bonding, and interconnection of tiny micro-

#### LED on 3D-IC.

This thesis aims to develop these key technologies and create a fabrication process for Smart Skin Display.

Fig. 1-24 Conventional skin display[93]

Fig. 1-25 Concept of Smart Skin Display

Fig. 1-26 Operation flow of Smart Skin Display

Table 1-3 Specification and requirements for Smart Skin Display

| Display                    | resolution                     | Approx. 60 ppi                                                                               |  |

|----------------------------|--------------------------------|----------------------------------------------------------------------------------------------|--|

|                            | Wiring width                   | 50 μm                                                                                        |  |

| Multilayer flexible wiring | Wiring pitch                   | 80 μm                                                                                        |  |

|                            | Number of layers               | 2                                                                                            |  |

|                            | Bending durability in wearing  | 1000 times at a radius of curvature of 20 mm                                                 |  |

|                            | Folding durability in handling | 100 times at a radius of curvature of 1 mm                                                   |  |

| Mini-LED                   | Size                           | IR LED:330 μm (L) x 330 μm (W) x 300 μm (H)<br>Red LED: 370 μm (L) x 370 μm (W) x 300 μm (H) |  |

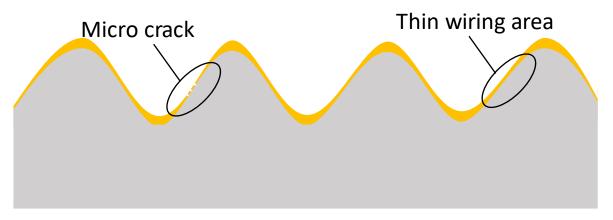

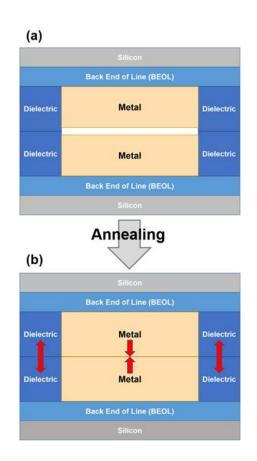

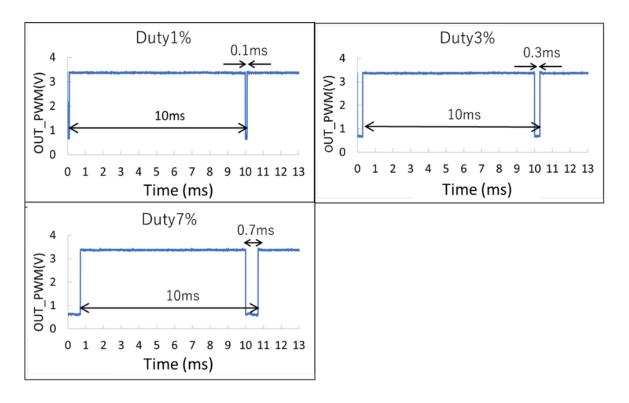

|                            | Dieshift tolerance             | ±10 μm                                                                                       |  |