## MASTER

Simulation and DSE of Neuromorphic Architectures for RSNNs

Willigers, Stefan L.C.

Award date: 2022

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Electrical Engineering Parallel Architecture Research Eindhoven (PARsE)

## Simulation and DSE of Neuromorphic Architectures for RSNNs

$Master's \ Thesis$

Stefan Willigers

Supervision: Sherif Eissa Henk Corporaal

Assessment committee: Sherif Eissa Henk Corporaal Federico Corradi Charlotte Frenkel

August 12, 2022

## Contents

| 1        | Intr | roduction                                   | 3               |

|----------|------|---------------------------------------------|-----------------|

|          | 1.1  | Problem statement                           | 4               |

|          | 1.2  | Contributions & overview                    | 4               |

| <b>2</b> | Bac  | kground                                     | 6               |

|          | 2.1  | Neuromorphic computing                      | 6               |

|          |      | 2.1.1 Biological neurons                    | 6               |

|          |      | 2.1.2 ANNs                                  | 8               |

|          |      | 2.1.3 SNNs $\ldots$                         | 9               |

|          | 2.2  | Neuromorphic hardware                       | 10              |

|          |      | 2.2.1 Hardware design choices               | 11              |

|          | 2.3  | Trace-driven vs execution-driven simulators | 14              |

| 3        | Rela | ated work                                   | 16              |

|          | 3.1  | Neuromorphic hardware                       | 16              |

|          | 3.2  | Neuromorphic hardware simulators            | 17              |

|          | 3.3  | Unexplored approach                         | 19              |

| <b>4</b> | Sim  | ulator                                      | 20              |

|          | 4.1  | Simulator overview                          | 20              |

|          | 4.2  | SNN model                                   | 22              |

|          | 4.3  | Hardware model                              | 23              |

|          |      | 4.3.1 Core                                  | 24              |

|          |      | 4.3.2 Controller                            | 27              |

|          |      | 4.3.3 Mesh                                  | 28              |

|          |      | 4.3.4 Synchronization                       | 29              |

|          | 4.4  | Cost model                                  | 30              |

|          |      | 4.4.1 Memories                              | 30              |

|          |      |                                             | 91              |

|          |      | 4.4.2 Buffers                               | 31              |

|          |      |                                             | $\frac{31}{32}$ |

|          |      | 4.4.3 Memory layout                         |                 |

|          |      | 4.4.3       Memory layout                   | 32              |

|                           | 4.5                    | Software architecture                                                                   | 36 |  |  |  |  |  |  |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| <b>5</b>                  | Exp                    | Experiments 3                                                                           |    |  |  |  |  |  |  |

|                           | 5.1                    | Experimental setup                                                                      | 38 |  |  |  |  |  |  |

|                           |                        | 5.1.1 Networks                                                                          | 38 |  |  |  |  |  |  |

|                           |                        | 5.1.2 Mapping                                                                           | 39 |  |  |  |  |  |  |

|                           |                        | 5.1.3 ALU config                                                                        | 12 |  |  |  |  |  |  |

|                           |                        | 5.1.4 Routing config $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$ | 13 |  |  |  |  |  |  |

|                           |                        | 5.1.5 Memory config $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$  | 13 |  |  |  |  |  |  |

|                           | 5.2                    | Evaluation                                                                              | 15 |  |  |  |  |  |  |

|                           | 5.3                    | Experimental results                                                                    | 15 |  |  |  |  |  |  |

|                           |                        | 5.3.1 Core size                                                                         | 46 |  |  |  |  |  |  |

|                           |                        | 5.3.2 ALU design                                                                        | 19 |  |  |  |  |  |  |

|                           |                        | 5.3.3 NoC design                                                                        | 51 |  |  |  |  |  |  |

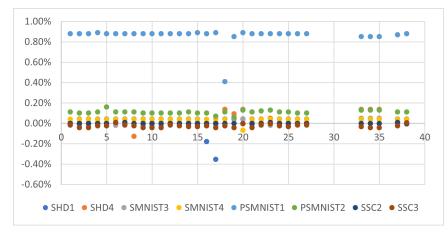

|                           |                        | 5.3.4 Accuracy deviations                                                               | 54 |  |  |  |  |  |  |

| 6                         | Dis                    | cussion 5                                                                               | 66 |  |  |  |  |  |  |

|                           | 6.1                    | Hardware analysis                                                                       | 56 |  |  |  |  |  |  |

|                           | 6.2                    | Experimental analysis 5                                                                 | 57 |  |  |  |  |  |  |

|                           | 6.3                    |                                                                                         | 59 |  |  |  |  |  |  |

|                           | 6.4                    | Future work                                                                             | 59 |  |  |  |  |  |  |

| 7                         | Cor                    | nclusion 6                                                                              | 61 |  |  |  |  |  |  |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                   | dices 6                                                                                 | 66 |  |  |  |  |  |  |

| $\mathbf{A}$              | A Experimental results |                                                                                         |    |  |  |  |  |  |  |

## Chapter 1 Introduction

Machine learning is a branch of AI that uses algorithms and data to perform cognitive tasks. Recently, machine learning has become a hot topic again. This increase in popularity is due to the increase in computation power and data abundance allowing the accuracy of especially neural networks to improve by leaps and bounds. As a result, neural networks have proven effective in a wide range of applications. Effective applications include fields like computer vision which deals with the analysis of image and video data by computers, or the field of natural language processing which tries to interpret natural languages like English, French, German or Dutch. Deep learning has achieved super-human performance in many of these cognitive tasks.

Currently, most of the work in deep learning is in the field of ANNs (artificial neural networks). ANNs can achieve super-human performance on cognitive tasks, but they suffer from being power-hungry and time-consuming to create and run. When looking at the biological counterpart for AI, the brain, we see that the brain consumes less power and learns information easier than current ANN-based systems. Two avenues of research are studying the brain in the context of AI. Cognitive neuroscience tries to decode how the brain works. And neuromorphic AI, which uses neuroscience concepts to improve the efficiency of computers on cognitive tasks. This work's main area of interest will be SNNs (spiking neural networks), part of neuromorphic AI research. SNNs try to improve on ANNs using several principles inspired by the brain. SNNs are also often called the third generation of neural networks [1].

There is already dedicated hardware for running ANNs. Due to ANNs being so popular, this avenue of research is also intensively researched. This popularity results in the more mature hardware specialized in running applications required by the ANN field. There even are frameworks specializing in DSE for ANNs like ZigZag [2]. However, that maturity does not hold for SNN hardware. The design and implementation of efficient hardware for SNNs are compared to ANNs still in their infancy. Hardware specialized in simulating SNNs is called neuromorphic hardware.

## **1.1 Problem statement**

In this work, we want to research neuromorphic hardware and the design choices involved. More specifically, the neuromorphic hardware we want to research is multi-core and therefore has a NoC (Network on Chip). Additionally, we want to do DSE (design space exploration) of different SNN applications and mappings. Using a hardware model, we want to learn what trade-offs are and how significantly they affect the hardware design. More specifically, the questions that we want to answer are as follows:

- What is the effect of core size on the throughput and energy of the chip? Smaller cores cause more traffic, but the memories consume less energy.

- How can core computation unit design affect the area, energy, and throughput? Having more functional units allow more throughput. However, more functional units will increase area and power leakage.

- What is the influence of increasing a router's buffer sizes on the throughput and area usage of the hardware? Increasing buffer sizes of the routers may increase the router's throughput but will increase the area usage of the router.

- Does limiting the number of wires between routers greatly influence the throughput of the hardware? Limiting the number of wires can limit the transfer speed between routers. This limited speed will decrease overall throughput.

## 1.2 Contributions & overview

To enable DSE, we plan to create a simulator that models the behavior of neuromorphic hardware. This simulator will include a cost model that can quantify the area and energy cost of the core and a discrete eventbased simulator that can functionally model the hardware, including the congestion of the NoC. Additionally, the simulator will be execution-driven and, therefore, able to predict accuracies. The hardware will be multi-core and use a 2D-mesh as communication fabric, and the core design will be digital and time-multiplexed. Additionally, the core design will use the axonal approach. To do our experiments, we will train our own networks based on the SRNN (spiking recurrent neuronal network) networks of [3]. Then we will use these networks as a benchmark to evaluate the performance of different hardware configurations. The hardware configurations are made in such a way that they can answer the research questions. The remainder of the work will be as follows: First, we will give a bit of background into SNNs, neuromorphic hardware, and simulators in chapter 2. Then we will investigate the current state of the art and see where we can improve upon it in chapter 3. After researching the state-of-the-art, we will explain the simulator that was built to solve the problem. The explanation of this simulator is given in chapter 4. Finally, we can do our experiments in chapter 5, after which we can discuss the results and the simulator in chapter 6, followed by the conclusion in chapter 7.

# Chapter 2 Background

Before looking at related work, we first need to know some background information to understand the related work. Section 2.1 will look into how neuromorphic computing works. After that, we will look into some choices we can make while designing neuromorphic hardware in section 2.2. Finally, we will look at the design choice of implementing an execution-driven versus a trace-driven simulator in section 2.3, which is an important design decision for simulators.

## 2.1 Neuromorphic computing

To build efficient hardware for SNNs, we first need to know how SNNs actually work. Therefore, we will first look into how biological neurons work and what the interesting properties of biological neurons are in section 2.1.1. We will then see how ANNs work and how they implement some of the ideas of biological neurons in section 2.1.2. Finally, in section 2.1.3 we will look at how SNNs work.

#### 2.1.1 Biological neurons

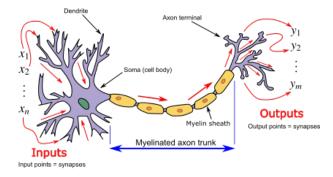

The neurons in SNNs are based on their biological counterparts. There is a large variety in biological neurons [4]. However, all kinds of neurons work according to the following general concept, see figure 2.1. A biological neuron can be divided into three functionally distinct parts [4]: dendrites, axons, and somas. A biological neuron has dendrites which are the input of neurons. These dendrites receive action potentials. Action potentials are rapid changes in the membrane potential of a neuron. The axons have the opposite function. They transmit action potential and are the output of a neuron. This current is transferred to other neurons' dendrites. A synapse connects the dendrites and axons. The sending neuron is called the presynaptic, and the receiving neuron is postsynaptic. Many dendrites feed into a soma. The soma can, in turn, drive multiple axons. The soma is a processing unit and adds a lot of non-linearity to the neuron [4]. The soma holds potential. This potential will rise according to the current flowing from the postsynaptic part of the synapse into the soma. The potential rise in the soma is proportional to how "well-connected" the synapse is. This "connectedness" of the synapse can also change based on effects like, for example, LTP (long-term potentiation) [5]. If the potential in the soma reaches some threshold, the neuron will spike. This spike is an action potential traveling down the axon to another postsynaptic neuron. This spike can then cause an increase of potential in postsynaptic neurons, which can subsequently make these postsynaptic neurons spike. Finally, the exact mechanism that generates the spike will also reset the potential of the soma back to some resting potential.

Figure 2.1: An image depicting a biological neuron from [6]. It shows a simplified overview of a neuron with the dendrites, soma and axons. Additionally, it shows how the action potential from the dendrites is fed into the soma and how a spike generated in the soma travels down to the axons.

Biological neurons have several remarkable features that make them interesting [7]:

1. Spikes: In the brain, biological neurons communicate by using spikes. These spikes typically have a duration of 1-2 ms and amplitude of 100 mV [4]. Even if the spikes vary slightly, it does not matter for the information-carrying ability of the spike. The information-carrying ability will stay the same as long the timing stays consistent. This resiliency is because the timing of neurons largely carries the information in the brain and which neurons fire rather than the value of the action potential [4, 7].

2. Sparsity: Most of the time, the neurons in the brain are silent and do not spike [8]. This sparsity is good for efficiency because silent neurons consume less energy by not spending the energy on generating spikes. As the generation and transmission of spikes by cerebral neurons consume a significant part of the energy budget in the cerebral cortex [9], this can result in substantial energy savings.

**3.** Static suppression: The sensory system is more reactive to changes than static information. An example of this reactivity is the visual system. The visual system is, for example, quick to adapt to changes in color brightness [10].

### 2.1.2 ANNs

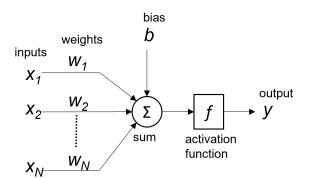

ANNs work differently from their biological counterparts [11]. Figure 2.2 shows a visual reference. Additionally, equation 2.1 shows a simplified equation describing an ANN neuron that can also be used as a reference. Generally, ANNs are functional and do not have a time dimension, unlike their biological counterpart. Exceptions to this functional model are recurrent architectures like RNNs [12], LSTMs [13] and GRUs [14].

$$y = f(\sum_{i=1}^{N} x_i w_i + b)$$

(2.1)

Figure 2.2: Graphical depiction of the ANN neuron model.

A neuron will receive a set of inputs  $x_i \in \mathbb{R}$  and produce a single output  $y \in \mathbb{R}$ . This is done by multiplying each of the inputs  $x_i$  with the corresponding weight  $w_i \in \mathbb{R}$ . The weights  $w_i$  control how important each of the inputs is. During training, the weights are changed to minimize the difference between the predicted y and the desired y. In addition to the weights, a bias  $b \in \mathbb{R}$  is added, which biases the neuron. Finally, an activation function f maps the summed potential to the output activation. The goal f is to add non-linearity. If this is not done, the neuron will only be able to model linear relations, meaning that the output is only a linear combination of the input. Even if more neurons are added in series, i.e., more layers are added, the output will still be a linear combination of the input.

Their biological counterparts primarily inspire ANNs. The weights model the synapse "connectedness", the activation function models the soma, the inputs  $x_i$  model the dendrites, and finally, the output y models the axon. However, this likeness of ANN neuron model to their biological counterpart does not result in any of the remarkable features of biological neurons mentioned earlier exhibiting themselves. SNNs try to remediate the lack of these features.

### 2.1.3 SNNs

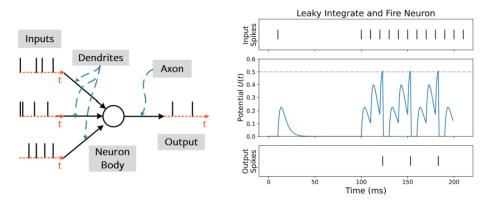

SNNs are a new third generation of deep learning models that tries to improve on the biological inaccuracies of ANNs, the second generation of neural networks [1]. SNNs are similar to ANNs in that they can model identical topologies. This similarity means that SNNs can model fully connected, convolutional, and recurrent layers similarly to ANNs. However, the difference between the two is in the neuron model. Whereas the neuron model of an ANN is purely functional<sup>1</sup>, the neuron models of SNNs always have a state. In the same way that there are many possible activation functions in ANNs, SNNs have many different neuron models. The most ubiquitous and straightforward neuron model is LIF (Leaky Integrate-and-Fire).

A LIF neuron tries to model a biological neuron. The explanation of the LIF neuron model is, therefore, also comparable to the one given in section 2.1.1. An example of how the neuron model works is shown in figure 2.3. A LIF neuron works as follows [7]: Unlike ANN models, the LIF is not purely combinatorial and has a state variable: the potential. This neuron potential resembles the potential of the soma in a biological neuron. If the potential exceeds some threshold, then the neuron will spike, and the potential will be reset to  $0^2$ . LIF neurons also have an exponential decay, meaning that the potential will decrease exponentially over time.

Figure 2.3: Figure from [7] showing the dynamics of a LIF neuron.

Equation 2.2 shows the equation for a LIF neuron model. LIF neurons a persisting potential u(t). The potential of the neuron changes according

<sup>&</sup>lt;sup>1</sup>Once again, except for RNNs, LSTMs, and GRUs

<sup>&</sup>lt;sup>2</sup>Actually resting potential, but the resting potential is assumed to be 0

to the input current I(t), resistance R, and decay rate  $\tau_m$ . The leakage will exponentially decay the potential with a rate of  $\tau_m$ . The left term on the right side will, henceforth, be called the decay term, and the right term will be, henceforth, the input term. If the potential exceeds some threshold  $\theta$ , the neuron will fire, which means the potential is reset to 0. Equation 2.3 shows that the amount of current received is proportional to the spikes and weights. Whenever a spike  $s_i(t)$  arrives on synapse *i* at time *t*, then the potential is increased proportional to the weight  $w_i$ .

$$\tau_m \frac{du}{dt} = -u(t) + I(t) \cdot R \tag{2.2}$$

$$I(t) = \sum_{i=1}^{N} s_i(t) \cdot w_i$$

(2.3)

## 2.2 Neuromorphic hardware

Unlike CPUs (central processing unit) and GPUs (graphic processing units), neuromorphic hardware does not adhere fully to standard Von Neumann architecture [15, 16, 17, 18]. Instead of having a large shared memory that each PE (processing element) shares, each PE accesses the local memory next to it. This locality of memory reduces the latency and energy overhead caused by expensive memory access and limits the effects of the Von Neumann bottleneck.

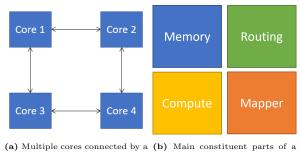

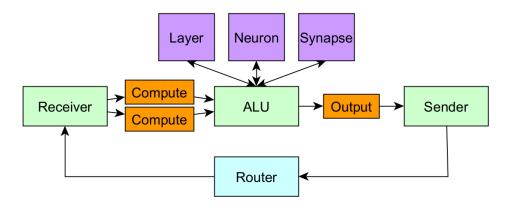

Figure 2.4 shows an example model of a neuromorphic multi-core chip. A neuromorphic processor consists of several cores connected by a communication fabric; see figure 2.4a. Figure 2.4b shows a typical digital neuromorphic core. A neuromorphic core consists of multiple functional components: a router or an I/O interface that handles the sending or receiving spikes. A mapper unit that is responsible for mapping outgoing spikes to the target cores' addresses. It also consists of memory to store synapses and neuron states and an ALU unit that can emulate the required neuron operations that need to be supported. Most designs do not exactly follow this scheme of separation into these exact functional components. Some, for example, have multiple separate pieces of memory [17, 19]. However, the memory, compute, routing and mapping are always in there in some form and therefore are the most unifying aspects of a digital neuromorphic core.

(a) Multiple cores connected by a (b) Main constituent parts of a 2D-mesh NoC

(b) Core.

Figure 2.4: Simplified overview of multi-core neuromorphic mesh.

## 2.2.1 Hardware design choices

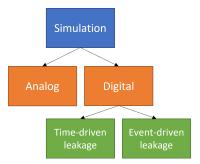

There are multiple techniques to simulate SNNs; see figure 2.5. An SNN can be simulated either using digital hardware or using analog hardware. One approach is analog hardware where a physical model is constructed that models the dynamics of the SNN neuron model. The other is a digital hardware where the formulas governing the dynamics are simulated. The digital hardware can simulate the decay in two ways: time-driven and event-driven. We will explain more about the difference between these two ways in the section about digital hardware. This choice between time-driven and event-driven is essential as it will significantly affect the design of a neuromorphic chip.

Figure 2.5: A tree showing the difference choices that can be made when simulating an SNN.

#### Analog hardware

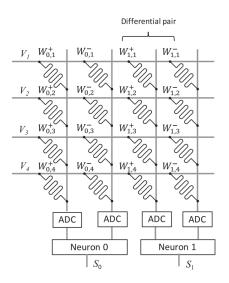

There are two ways to model neurons in the analog domain: analog CMOS [20] and memristor-based. Memristor-based setups are commonly used in a crossbar arrangement to model all-to-all synaptic connections between inputs and outputs. We will explain more about these memristor-based crossbars as they have gained popularity recently.

These crossbars can perform parallel matrix-vector multiplication with very low energy requirements [21]. Figure 2.6 shows such a crossbar. The general concept is as follows [22]: There is an array of horizontal word lines and vertical bit lines. A memristor then connects these. A memristor is a circuit component that can modulate its conductance [21]. Synapse weights can then be stored in these modulated conductances. So, when a spike arrives on a synapse, the top word line can be set to high. Then an amount of current will flow, proportional to the memristor state, from the word line to the bit line. After which, an ADC (analog-digital converter) can read the output value on the bit line. A CMOS (Complementary metaloxide-semiconductor) circuit can then use this output value to simulate LIF behavior. This circuit is digital. One bit line for the negative values and one bit line for positive values is used because memristors can not store negative values. Although this analog design may look like the perfect solution, it still has some problems. NVM (non-volatile memory) technologies like memristors can suffer from limited read endurance [23], meaning that the weight value would have to be rewritten after a certain amount of reads. In addition they can suffer from several defects and variabilities [22, 21].

Figure 2.6: A simplified example from [22] of an RRAM-based crossbar.

#### **Digital hardware**

Digital simulation emulates the differential equations governing the neurons. For linear models, the input term of section 2.1.3 only changes the potential when a spike arrives and therefore is easy to implement. One can change the potential of the neuron whenever a spike comes in. However, the decay term is a problem. The decay term changes the potential over time. It is, therefore, more difficult to calculate what the potential should be at some later point in time. Luckily the decay is exponential, and the solution for exponential decay is already known. Equation 2.4 shows the solution to the decay term of equation 2.2. Here, t' is the time the potential needs to be known, and t is the time of the last known potential.

There are two approaches to using this solution: event-driven [19] and time-driven [18]. The time-driven takes constant steps, meaning that t' - tis constant. Equation 2.5 shows the solution to the decay for time-driven simulation. The equation assumes a discretization such that t' = t + 1. An advantage of these constant steps is that the term  $\exp(-\frac{t'-t}{\tau_m})$  becomes constant and therefore possible to precompute. As a result, the computations are significantly simplified because no exponential calculations and storing the last known potential are needed. The signal to apply the decay can be issued in many ways, in ODIN [17], the signal is manually triggered by an event sent to the core, while for TrueNorth [18], the signal comes from a clock-based 1000 Hz signal.

On the other hand, an event-driven simulation has no such assumption; in event-driven designs, t' can take any value as long as  $t' \ge t$ . Equation 2.6 shows that only the time of equation 2.4 has to be discretized. A consequence of variable time steps is that in addition to u(t), the t also needs to be stored because the step sizes are not constant. However, the amount of computation in an event-driven simulation is proportional to the number of spikes, not the number of timesteps. This proportionality of computation to the number of spikes can be advantageous if the number of spikes is sufficiently sparse spatially and in time.

$$u(t') = u(t) \cdot \exp(-\frac{t'-t}{\tau_m}) \tag{2.4}$$

$$u[t+1] = u[t] \cdot \exp(-\frac{1}{\tau_m})$$

(2.5)

$$u[t'] = u[t] \cdot \exp(-\frac{t'-t}{\tau_m}) \tag{2.6}$$

#### Synchronization

If neurons spread over multiple cores have to generate spikes and apply decay simultaneously, then each should share the same sense of time. However, this synchronization is not always required. For example, ODIN [17] only has a way to trigger a leakage event manually, and the ODIN chip immediately spikes when the threshold is reached.

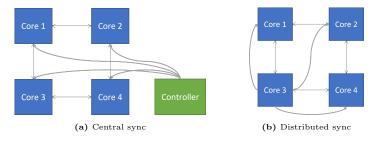

Nonetheless if there is synchronization, then there are many approaches to doing it. We will distinguish between two different directions: A central synchronization approach [18] where the control to advance to the next timestep is centered on one component. Fig 2.7a shows an example of central synchronization where a central controller sends a synchronization event over the communication fabric every 1ms to synchronize. On the other hand, when using distributed sync [16] shown in figure 2.7b, all cores decide together to advance to the next timestep. Several different implementations of distributed synchronization are possible. One implementation requires sending a done signal to a central controller, which, when receiving all done signals, will send a synchronization event to all cores. In this case, the synchronization is not spatially distributed but distributed in terms of control. Another implementation requires each core to send synchronization events to the neighboring cores to signify that the current core is done. An example of this implementation is Loihi [16]. In this case, the synchronization is distributed spatially and in terms of control.

Figure 2.7: Synchronization methods

## 2.3 Trace-driven vs execution-driven simulators

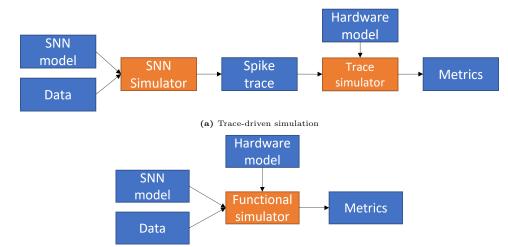

When designing hardware simulators, one can choose between an executiondriven [24, 22] and a trace-driven simulator [25, 23]. Figure 2.8 shows the difference between an execution-driven and trace-driven simulator using a visual diagram. The main essence of the figure is that an execution-driven simulator has a "built-in" SNN simulator. The execution-driven simulator does both the SNN and hardware simulation. In contrast, a trace-driven simulator outsources this to a separate external SNN simulator. Each approach has different pros and cons. Trace-driven simulators have no model of the SNN. Thus spike drops or other events happening out of order can not influence the neuron dynamics and, therefore, the simulators are less flexible in the hardware details they can model accurately.

Ultimately, this comes down to a trade-off between more abstraction or less abstraction. A more abstract model will have fewer assumptions and details and be applicable in more situations. However, a more detailed model can simulate specific scenarios more accurately. A more abstract model will also be faster to simulate as the simulator must simulate fewer details. Trace-driven simulators are, in this case, the more abstract model. They apply to more simulations, e.g., changing neuron model, and they are faster run, but they will lose some accuracy in simulations, e.g., can not predict model accuracy. Finally, using a non-self-written simulator can save

work, which is another advantage for trace-driven simulators.

(b) Execution-driven simulation

Figure 2.8: Trace-driven vs execution-driven simulator. Blue boxes show inputs/outputs. Orange boxes show programs.

# Chapter 3 Related work

After knowing some of the background information about neuromorphic hardware and neuromorphic hardware simulator we can take a look at what the other works do. Research on neuromorphic hardware is needed such that a hardware model that is relevant to the current SOTA (State Of The Art) can be implemented. Section 3.1 will look into some of the neuromorphic hardware chips. Section 3.2 will look into some of the simulators that are used to simulate neuromorphic hardware. This knowledge is need to to know whether we can find a way to improve or take a different approach. Finally, in section 3.3 we can put together what we learned about simulators and neuromorphic hardware and determine the type of hardware and the kind of simulator we would like to implement.

## 3.1 Neuromorphic hardware

One of the earlier big neuromorphic processors developed is TrueNorth [18]. It is a neuromorphic processor developed by IBM. It is fully digital and does time-driven SNN simulation. TrueNorth's NoC is an asynchronous 2D-mesh. The core supports multiple neurons by time multiplexing. The synchronization is done centrally by a clock running at 1000 Hz. Therefore, the TrueNorth processor is a prime example of the central synchronization paradigm. Interestingly, even though the processor is digital, it still implements a digital crossbar. The main goals of the TrueNorth processor were to minimize energy consumption, maximize throughput, have a real-time operation, have scalability, be defect tolerant, and have one-to-one equivalence between hardware and software.

ODIN [17] is different in that it only has one core instead of many cores. ODIN can simulate both a LIF neuron and phenomenological models for the Izhikevich neuron model. ODIN does not have synchronization. The closest resemblance to synchronization is a manually triggered leakage event. ODIN neurons immediately trigger if they reach threshold. ODIN also implements a phenomenological model that mimics but not is Izhikevich model. A phenomenological model rather than a differential equation is simulated and, therefore, does not fit either event-driven or time-driven simulation. Unfortunately, the small size of ODIN limits the applicability to anything else than edge computing applications.

Loihi [16] is a neuromorphic processor developed by Intel. It has 128 cores that are each able to simulate 1024 neurons. Like TrueNorth, it is connected by an asynchronous 2D mesh, but unlike TrueNorth, the synchronization is not global but distributed using barrier sync messages. The Loihi paper does not give enough information about the core design to know whether it uses event-driven or time-driven simulation. Unlike TrueNorth and ODIN, Loihi focuses more on having a very flexible neuromorphic processor. Loihi, for example, has a reconfigurable on-chip learning engine. Loihi even keeps track of spike traces, which is essential for some learning algorithms.

NeuroEngine [19], takes a clear event-driven simulation approach. The main contributions are in the proposal of several techniques to increase the simulation efficiency of two-stage neuron models. Two-stage neuron models are a special class of neuron models where instead of the potential increasing instantly on an input spike arriving, the potential increase slowly over time. The authors theorize that this non-instant increase could allow the network to model more complex dynamics and reach higher accuracy. The synchronization scheme is once again not clearly defined in the paper.

The SpiNNaker [26, 27] and SpiNNaker2 [28] are computer clusters. Unlike other neuromorphic processors, this architecture uses a specialized ARM core. The choice of a general-purpose ARM core increases the system's flexibility significantly. The system can simulate a vast range of SNN topologies and neuron models. The SpiNNaker system can run a time-driven [29] simulation. No literature could be found that claimed that it could also do event-driven simulation.

## 3.2 Neuromorphic hardware simulators

There is already some research in using hardware simulators to evaluate neuromorphic hardware. However, interestingly, there is a significant variety in the methods of these simulators and the modeled hardware.

PyCARL [25] simulates hardware in a trace-driven way primarily focused on crossbar-based architecture. The central concept of this tracedriven approach is to get a trace of spikes from an external SNN simulator like CARLsim [30]. This trace is then simulated on a hardware model to extract metrics. This trace consists of the time and neuron of each spike in the network. PyCARL does acknowledge that hardware details can affect the accuracy of the SNN simulation. To monitor the accuracy impact of the simulated hardware, they added the spike disorder and the inter-spike interval distortion metrics. Nonetheless, these metrics can only provide estimates of the model's accuracy. Running a dataset on the simulator and reading the accuracy will not work as it is trace-driven. On the other hand, the simulator can extract information like latency, throughput, and energy of the hardware design. These metrics can help estimate congestion of the NoC, which most of the experiments also test.

NeuroXplorer [23] shares some of the same authors as PyCARL. It is, therefore, no surprise that this work improves on its predecessor PyCARL. The most relevant difference is that, compared to PyCARL, which is only compatible with CARLsim, this framework is compatible with many other neuromorphic simulators like Brian [31], and Nest [32]. The model accuracy metrics are the same as PyCARL. Yet, in terms of hardware metrics, this work has more metrics. In addition to the metrics of PyCARL, the model also focuses on metrics monitoring the crossbar like circuit aging, resource utilization, and endurance.

The work [22], henceforth, called the system level simulator, also focuses on crossbar-based architectures. However, in addition to focusing on different aspects of RRAM, the paper also has a different approach to simulating. This work uses an execution-driven simulator, simulating the neuronal dynamics and evaluating accuracy.

NEUTRAMS [24] is another execution-driven simulator. However, this simulator has a decoupling between the functional and timing models. The user can then give the time that a certain operation should take, independent of the functionality. This decoupling means that the user can, for example, configure that a synaptic operation should take a certain number of cycles. Simulators like the earlier mentioned system-level simulator, NeuroXPlorer, and PyCARL do not explicitly show any flexibility in changing the timing parameters of the core independently from functionality. This flexibility in the timing model allows the user to model more scenarios. In addition, the NEUTRAMS simulator also claims to be amiable to changing the execution substrates, e.g., ANNs vs SNNs. All of these options allow the NEUTRAMS simulator to be very flexible.

Although not neuromorphic hardware simulators, Compass [33], NengoLoihi [34], and the Intel lava framework [35] also simulate SNNs. But these simulators mostly emulate execution semantics. Simulating execution semantics can be helpful in some scenarios, like investigating scalability. Still, these simulators do not model any buffers, NoC, or other hardware mechanics and are, therefore, not considered neuromorphic hardware simulators.

## 3.3 Unexplored approach

A large part of the related work focuses on simulating crossbar-based architectures. Simulators like PyCARL, NeuroXPlorer, the system level simulator, and NEUTRAMS all focus on crossbar-based architectures. However, section 2.2 shows that not all hardware follows this crossbar-based architecture. Moreover, this focus on crossbar-based architectures results in few simulators supporting architectures that use a digital time-multiplexed core like Loihi.

What can also be seen is that most simulators either choose to do a trace-driven simulation or an execution-driven simulation of a crossbar. The trace-driven designs are acceptable. However, they do lose all knowledge of the neuron model being simulated. This means that after the trace is extracted, no design exploration in, for example, quantization of the neuron model can be done. Also, fewer different hardware models can be explored in a detailed way because some hardware models may let spikes drop in sacrifice for more efficient hardware. If a trace-driven simulator is used then the accuracy effects of dropping spikes can not be determined. Thus, an execution-driven simulator will allow the design of both hardware that does and does not drop spikes.

Most of the execution-driven simulators are like the system-level simulator which focuses on the execution-driven simulation of a crossbar with an emphasis on simulating low-level electrical circuits. As a result of focusing on these low-level mechanics, these execution-driven designs are less flexible. For example, it makes it more challenging to run different neuron models. An exception to this rule is, for example, turning LIF into an IF (integrate-and-fire) neuron model by setting leakage to 0. But then, the processor simulates a more complicated neuron model while the processor could use a less complex one. NEUTRAMS does not take this approach and can create a high-level crossbar simulator by adding abstractions in the right places. Yet, NEUTRAMS currently is still quite focused on crossbar-based architectures. Also, NEUTRAMS is a clock-driven simulator, which can be non-ideal in terms of performance.

The direction of a digital architecture-focused simulator that can do an execution-driven simulation focusing on high-level aspects and modelling non-crossbar-based hardware would be interesting to research. Unfortunately, not many simulators can be found that take this direction. If this simulator is made event-driven, it is even possible to have a configurable core timing model like NEUTRAMS. This event-driven simulation will result in a large amount of flexibility.

## Chapter 4 Simulator

In the previous section, we learned what the current SOTA is doing regarding hardware and simulators. Now that we know the current SOTA and how we want to improve upon it, we can discuss the simulator that was built. Firstly, in section 4.1 we will look at a quick overview of the constituent programs of the simulator. In section 4.2 we will look at our SNN model. In section 4.3 we will look at the hardware model we want to evaluate and use for the simulator. In section 4.4 we will look at how we can quantify the energy and area cost for each of our hardware components. Finally, in section 4.5, we will review the simulator's software architecture shortly.

## 4.1 Simulator overview

Firstly, we will make the simulator source code available as open source. The source code can be found at https://github.com/tetanw/SpikingDSE. The simulator consists of several separate programs that together form the complete simulator. The implementation of these programs use C#. The rest uses Python. The simulator produces energy, latency, and area numbers given a hardware model, SNN model, cost model, and input traces. The simulator is execution-driven, but it is also possible to do trace-driven simulation in the future by extending the simulator (see section 4.5). The hardware focus of the simulator will be on digital mesh-based neuromorphic hardware that is multi-core. The SNN focus will be on simulating the SRNN networks of [3]. This work was selected for its good performance on a wide range of benchmarks. Even better, the source code was available for use. The networks are recurrent though so the hardware should be able to simulate recurrent SNN networks.

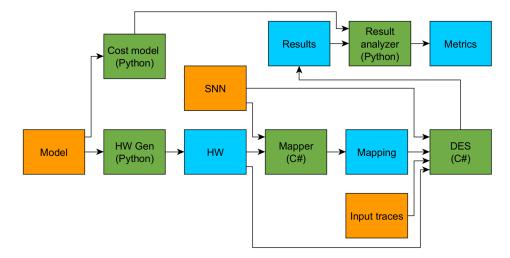

Figure 4.1 shows an overview of the constituent programs of the simulator. The main program is the DES (discrete-event simulator). It is a discrete-event simulator. Discrete-event simulations model a system as a series of events happening at increasing discrete times. More specifically, it is a process-based (or process-oriented) discrete-event simulation [36]. The process-based part means that the simulated system is viewed as many communicating parallel processes. This process-based DES design of the simulator is based on SimPy [37], and POOSL [38].

Figure 4.1: Simulator overview. The orange boxes show inputs, the green boxes show the programs, and finally, the blue boxes show intermediate results.

The main function of the DES is to produce results like how many packets a router handled, how many memory accesses each core did, how much time an inference took, etc. Creating these results needs a specification of the hardware model. This HW specification can, for example, contain how many cores the hardware consists of, parameters of each core, locations of cores on the mesh, buffer sizes of routers, etc. But most importantly, it also contains parameters regarding how much time each operation takes. Because the simulator is discrete-event based, the latencies are also parameters. The advantage of having latencies as parameters is that the simulator is more flexible. The disadvantage is that it requires an effort from the user to find realistic values for these parameters. Moreover, these parameter values may not always be readily available.

The other program either produces input files needed for the DES or analyzes the results of the DES. The SNN model describes the SNN architecture that the hardware simulates. Additionally, the simulator needs input traces. These input traces contain which neuron spikes at which timestep in the input layer. The model file is an enriched version of the hardware file. In addition to all the information about the HW, it contains memory size parameters. The HW generator generates the HW specification file based on the model file. The model file makes more assumptions about the hardware. For example, the model files assume that all cores are homogeneous in size, whereas, for the simulator, this does not necessarily have to be the case. By keeping the HW and model file separate, the DES does not have these assumptions like homogeneity and can, therefore, be more flexible. The mapper creates a mapping of the layers of the SNN to the cores. The mapper is part of the experimental setup and will be explained in section 5.1.2. The cost model calculates the energy cost or area cost of certain operations. For example, given synapse size in bits and the maximum number of synapses that a core may store, it can calculate the synapse memory size. The cost model can then use this memory size to calculate the leakage, dynamic read energy, area, etc. The result analyzer can then use this cost model and the results from the DES to calculate the metrics.

## 4.2 SNN model

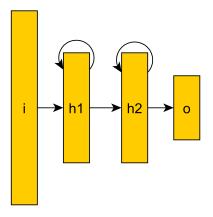

The simulator needs a description of the SNN model. The simulator assumes that an SNN network consists of a series of layers. More specifically, the simulator expects an input layer followed by any number of hidden layers followed by an output layer. Figure 4.2 shows an example of such an SNN. Input layer "i" is followed by a series of hidden layers "h1" and "h2", ending with an output layer "o". Henceforth, a connection from one layer to another will be called a forward connection. A connection between a layer and itself will be called a recurrent connection.

Figure 4.2: Example of what an SNN model should look like. It consists of an input layer "i" followed by recurrent hidden layers "h1" and "h2", and finally, output layer "o".

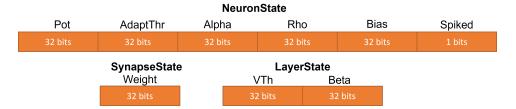

Each layer should also have a size in terms of the number of neurons in that layer. Additionally, different sets of parameters are required depending on the layer type. There are two layer types supported by this simulator ALIF and LI, both of which are from [3]. An ALIF layer requires passing the weights, decay constants, biases, etc. These parameters need to come from a trained PyTorch model. Section 5.1.1 explains more about this parameter extraction and the origin of these trained models. The output layer of [3] requires a separate layer implementation as it is functionally different compared to the ALIF layers. Henceforth, the name of this output layer will be the LI layer. Running the LI requires fewer parameters as it is a simpler version of the ALIF layer. It only requires weights, decay constants, and threshold voltage. In figure 4.2, "h1" and "h2" would be ALIF layers, and "o" would be the output layer of [3] as these are the only hidden and output layer types available.

The simulator can also split layers into multiple parts if a core can not fully fit a layer due to constraints. The word layer, in this simulator, actually means a subset of a layer's neurons which can be the full layer but does not have to be. So, a layer part. The layer splitting is a complicating factor in the design of the hardware. If the layer is recurrent and is split into multiple parts located on different cores, then spikes need to be sent between cores to communicate the recurrent spikes. Likewise, the layer before the splitted layer must send the spikes to multiple destinations.

## 4.3 Hardware model

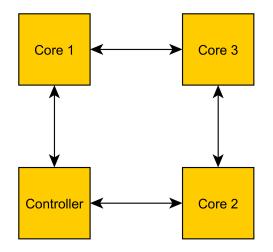

Figure 4.3 shows a general model of the hardware. As mentioned earlier, the hardware will focus on simulating mesh-based chips. The number of slots to fit cores or controllers in the width and height of the mesh is configurable. In the case of figure 4.3 the hardware model is configured with a width of 2 slots and a height of 2 slots. In addition, the hardware model will always have the controller on the bottom left slot of the mesh, with cores filling the remaining slots.

**Figure 4.3:** An example of a possible configuration of the hardware model. The figure shows a mesh of 2 by 2 with a controller on the bottom-left and cores all around connected by links.

The remainder of this section will discuss how the synchronization (section 4.3.4) works and discuss the three big component parts of the hardware model: the core (section 4.3.1), the controller (section 4.3.2), and the mesh (section 4.3.3).

#### 4.3.1 Core

Unlike TrueNorth and Loihi, the core design for this simulator uses the concept of layers. Although, especially Loihi and DYNAPs [15] try to limit the memory size on the chip needed to store the connectivity. We also chose to limit the memory size. We chose a layer-based system because it is closest to how the SRNN model of [3] is trained. The implementation of this work does not allow connection between all neurons. Like ANNs, it limits connectivity by grouping neurons in layers and limiting layers to be connected in an acyclic way.

Figure 4.4: Simplified overview of core. Green shows the three main components. Orange shows the buffers. Purple the memories. And light-blue the router.

Figure 4.4 shows an overview of the core's hardware model. The core has three main components: the receiver, ALU, sender, and two buffers: the compute and output. The receiver is responsible for receiving packets from the mesh and handling them correctly. There are two compute buffers. One buffer for the current timestep's spikes and one buffer for the next timestep's spikes. The ALU reads the current timestep's buffer, and the next timestep's buffer is filled with spikes generated by other cores' spikes for the next timestep. Therefore two buffers are needed. If the receiver receives a spike packet, it should be queued in the compute buffer of the next timestep. If the receiver receives a sync packet, it should signal the ALU to start synchronizing the compute buffer of the next timestep. The sender's job is to wait for packets in the output buffer and send them to the router.

The ALU is the most complicated part of the core. When a synchronization signal comes in from the receiver, the ALU will read spike events until the buffer is empty. Each spike packet will result in the core updating the potentials of the relevant layer. After all, spikes are processed, the ALU must synchronize all neurons. This synchronization includes applying leakage and checking whether the threshold has been reached, among other things. Connected to the ALU are the layer, neuron, and synapse memories. These memories must be written to and read for the ALU to do its job. The layer memory stores information about where the neurons and synapses are stored, network parameters, connectivity data, etc. The neuron memory stores the potential and other neuron parameters. The synapse memory stores the synapse weights. Section 4.4.3 describes what the memory looks like in-depth.

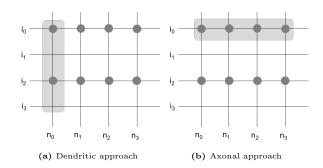

The core has to update the potentials of all neurons when a spike is received. The TrueNorth paper [18] documents two approaches: the dendritic and axonal approaches. Figure 4.5 shows these two approaches. The dendritic approach gets the neuron state from memory once and then integrates all input synapses. The axonal approach sees every input spike as an event that updates neuron potentials.

The advantages and disadvantages of each approach are as follows. Firstly, the dendritic approach requires that all spikes need to be stored before synchronizing, whereas the axonal does not. On the other hand, this means that the axonal approach can update as the spikes come in, which can be an advantage for the axonal approach in certain circumstances.

The dendritic approach only requires getting the neuron state as often as there are neurons in a layer, whereas the axonal approach requires more neuron state accesses. Namely, the number of neuron state accesses depends on the number of neurons in a layer and then more depending on the number of spikes. However, this is eased by not having to fetch the whole neuron state while integrating but only the neuron potential. On the other hand, the dendritic approach must fetch the spiking state of the same input neuron multiple times. So, the axonal approach results in more neuron state accesses and the dendritic approach in more spiking state accesses. Finally, the axonal approach will comparatively perform better in sparse scenarios as the number of fetches scales with the number of spikes.

The axonal approach is advantageous in terms of throughput. The dendritic approach has constant working time<sup>1</sup>. In contrast, the amount of time for the axonal approach is more proportional to the number of spikes. So once again, the axonal approach will likely work better in case of high sparsity. Therefore, this work uses the axonal approach because the benchmarks can have relatively high sparsity.

## ALU

The ALU will integrate the spikes followed by synchronizing the neurons. Parallelism is a configurable parameter that denotes the number of neurons

<sup>&</sup>lt;sup>1</sup>this does not necessarily have to be the case

**Figure 4.5:** Integration approaches. The vertical axis show the input neurons. The horizontal axis the neurons of the layer to be updated. The dots on the intersection show waiting spikes. The image shows that for the dendritic approach you iterate over all input connection on each neuron whereas for the axonal approach you update all neurons on a layer on receiving a spike.

during synchronization and the number of neurons during integration that is updated simultaneously. For example, when the parallelism is 4, then the ALU will perform four synaptic operations at the same time and synchronize four neurons at the same time.

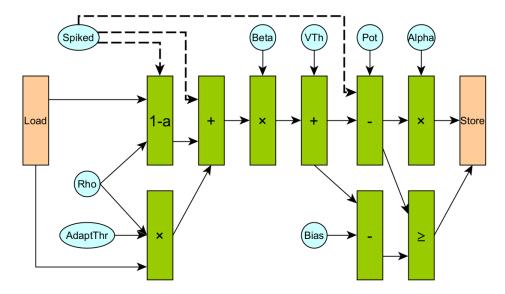

One of the most important design decisions for the ALU is how many functional units of each kind are needed. The more functional unit can increase the throughput but take up more area and contribute to leakage. The two processes that the ALU needs to perform are integration and synchronization. The most complicated of these is synchronization. Figure 4.6 shows a dataflow graph for the synchronization of the neurons.

**Figure 4.6:** Dataflow for synchronization of a neuron. The green boxes show the operations. The blue circles show the variables used in the operations. The dotted line denotes that the operation will only happen when **Spiked** is true.

The latency of synchronizing a neuron and integrating a synapse are

configurable in the simulator. The user can change two parameters: the latency and the initiation interval. The latency describes the time it takes for a value to go from load to store. The initiation interval is the amount of time between operations, i.e., inverse of the throughput. Three designs are possible. A fully serial design where each operation happens in series. A parallel design that still is serial but that will do as much in parallel as possible. The latency will be the same for both the serial and parallel design. Finally, there is a pipeline design. This design schedules the operation in a pipeline. This design will have about the same latency as fully parallel but have a lower initiation interval.

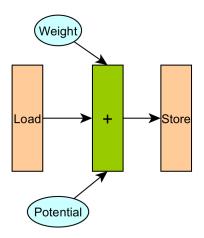

Comparatively, the integration of a spike is easy. Figure 4.7 shows the data flow for that process. Here not much design is possible. It is assumed that the integration uses the same functional units as the synchronization process.

Figure 4.7: Dataflow for integrating a spike for an ALIF neuron. The green boxes show the operations. The blue circles show the variables used in the operations.

### 4.3.2 Controller

The controller has multiple responsibilities. Firstly, it handles the input layer. Meaning that from the controller the input spikes are sent to the first hidden layer. Secondly, the controller handles the output layer. Meaning it also receives the spikes from the final hidden layer. Layers mapped to the core are assumed to take no time and energy. This also implicates that the input and output layer consume no energy. Finally, the controller is responsible for orchestrating the synchronization. This explained in more detail in section 4.3.4. The controller has no configurable parameters regarding latencies for receiving spikes or regarding synchronization. These parameters can be added in future works to make the simulator more accurate.

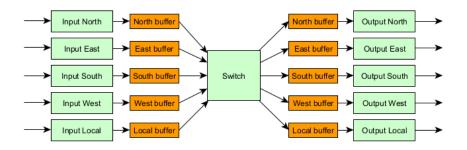

#### 4.3.3 Mesh

The mesh consists of many connected routers. The simulator uses a packetswitched router with input and output buffers. Most routers are virtualchannel based. However, this combination of input and output buffers allows for the evaluation of the difference between input buffering and output buffering. Additionally, the model chosen by the simulator is simpler to implement.

Figure 4.8 shows an overview of the router design used in this simulator. The green show boxes show processes, and the orange boxes show buffers. The inputs are responsible for receiving the transmitting packet. The input buffers will store the packets after being received. The outputs are responsible for sending the packets onto the next router. More precisely, they read a packet from the output buffer and send it to an input buffer of another router. The switch is responsible for moving a packet from an input buffer to the correct output buffer.

The routing policy is XY-routing. XY-routing is required to prevent deadlocks due to cyclic dependencies when routing packets. The router also uses round-robin arbitration to guarantee that one direction does not starve all other directions. The round-robin arbitration works as follows: it stores the direction in which the switch switched the last packet. Then, when a new packet is available for routing, the direction after the last switched direction is checked first.

Figure 4.8: Model of an XY-Router as used in the simulator. Orange boxes show buffers. Green boxes show processes.

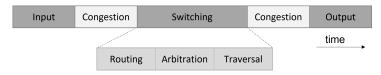

Figure 4.9 shows a diagram depicting the latencies that a packet encounters when travelling through a switch. First, it will encounter latency on the input. This latency is equal to the transfer latency parameter if it is non-local input and the input transfer latency if not. The reasoning behind this differentiation is that local connections may be faster because the local connection is closer to the core. The same latencies also hold for the output link. If the router switch is already busy or the output is busy, the packet may have to wait in the buffer. This waiting is the congestion. Then comes the switching delay. The simulator assumes that the delay in routing, arbitration, and traversal can be summarisable into one number, the switching delay.

Figure 4.9: Diagram of the latencies that a packet can encounter when traversing a router.

#### 4.3.4 Synchronization

This hardware model uses a distributed synchronization approach. However, it is quite an unusual variant as it uses the controller to decide when to continue instead of all cores deciding together.

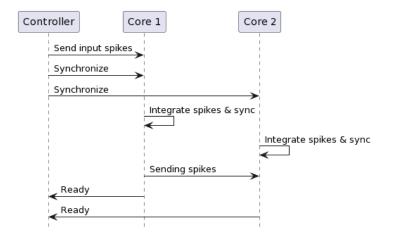

Figure 4.10 shows how synchronizing two cores in practice. First, the controller sends the spike events from the input layer to the first hidden layer in each step. Then the controller sends a synchronization event that prompts the cores to start consuming the spikes in the compute buffer. After integrating the spikes in the compute buffer (see section 4.3.1), the core synchronize each neuron. After completion of the synchronization of all neurons, each core will report that it is ready to the controller. A new synchronization event will be issued if the controller has a message from each relevant core that it has completed synchronization. A relevant core is a core that has mapped layers. If there are no layers on a core, then it is not involved in synchronization.

Figure 4.10: The sequence of action that the hardware goes through when doing one timestep. This is an example of a hypothetical hardware with one controller and two cores.

This scheme, however, has a problem. The core should only report that it has completed synchronizing after the spiking events generated during the synchronization have arrived at their destination cores. However, because of the packet-switched mesh, a core can not know when a spike has arrived. As a result, it is possible that a core already got a synchronization signal before the spike from that timestep could arrive at the compute buffer. Thus there is a race condition. This race condition influences the accuracy of the simulation. This race condition should be relatively rare, so this defect is allowed.

## 4.4 Cost model

The cost model assumes that the hardware will run at 100 MHz with a core voltage of 1.1 V, a temperature of 25 °C, and that a 40 nm fabrication process is used. The cost model also assumes some level of power and clock gating. As a result, if a core does not have any layers, then it is assumed that the core does not contribute to energy consumption. Additionally, the idle energy consumption of functional units is assumed to be zero.

In section 4.4.1 and section 4.4.2 we will give the memory and buffers an area and energy cost. Section 4.4.3 will show the memory layout. After this section we should know the depth and width of each memory and how each parameter is laid out in the memories. In section 4.4.4 and section 4.4.5 we will look at energies and area for the core and the router. Finally, we will look how the earlier individual energy and area consumption sum up to a model for the whole chip in section 4.4.6.

#### 4.4.1 Memories

Numbers of a commercial 40 nm SRAM memory library are used to find good memory models for the simulator. The version of memory used has a mux factor of 4 and uses the dense memory type. The simulator requires a model for the area, static power, and dynamic energy. Although the value of these characteristics can depend on many variables, only two will be considered the size of the memory in bits S and the width of the memory in bits W.

The area usage of the memory logically depends mostly on the number of the memory capacity in bits. If the memory is small, then the area usage will be mostly dominated by the peripheral circuitry. Equation 4.1 shows the formula used to determine a memory's area. This equation model has an R-squared<sup>2</sup> value of 0.9986 Thus, it is quite a good fit.

$$A_{mem} = (0.4586 \cdot S + 12652) \cdot 10^{-6} \quad [mm^2] \tag{4.1}$$

$<sup>^{2}</sup>$ R-squared is a value denoting which proportion of the variance of the data is explained by the model. So, it measures how well a model fits the data. A value of 1 is a perfect explanation of variance.

Similarly, the leakage also linearly depends on the capacity of the memory. Equation 4.2 shows the amount of leakage for a certain memory size S. The fit for this equation has an R-squared value of 0.9968, so it is also an accurate fit.

$$P_l = (8 \cdot 10^{-5} \cdot S + 1.822) \cdot 1.1 \cdot 10^{-6} \quad [W]$$

(4.2)

Finally, the dynamic read and write energy are more complicated as they also depend on the width of the memory. Equation 4.3 and equation 4.4 show the write and read energy respectively. The W parameter signifies the width of the memory in bits. Do keep in mind that for the neuron and synapse memory the width is not the size of a neuron and a synapse itself as described in section 4.4.3, but instead need to still be multiplied by the parallelism P. So, the hardware model assumes that an increase in parallelism on the ALU will also increase the width of memory access. The fitting for this equation was done using a Moore-Penrose inverse, giving a least-squares solution. Overall, the error between data and model is less than 20% for both the read and write energy. The model even becomes more accurate with an increase in memory size.

$$E_w = (3.32 \cdot 10^{-5}S + 0.20 \cdot W + 3.71) \cdot 10^{-12} \quad [J]$$

(4.3)

$$E_r = (4.68 \cdot 10^{-5} S + 0.31 \cdot W + 3.23) \cdot 10^{-12} \quad [J] \tag{4.4}$$

Equation 4.5 shows the total energy consumption of the memory for one inference, where  $N_r$  is the number of rows read from memory,  $N_w$  is the number of rows written to memory, and t amount of time that the inference took.

$$E_{mem} = E_w \cdot N_w + E_r \cdot N_r + P_l \cdot t \quad [J]$$

$$(4.5)$$

#### 4.4.2 Buffers

The hardware model assumes that both the compute and output buffer are FIFO buffers. Each of these buffers will block if it is full. The cost model will also assume that the FIFO buffers are implemented using SRAM. In addition, the cost model assumes that dequeuing a value from the buffer only requires a memory read, and enqueueing a value only requires a memory write. Counters are typically required to store the next available space to read and write, especially in the case of ring buffers. The cost model assumes that these are implemented as registers. Thus, they do not cause extra rows to be read and written to the SRAM memory. The cost model also assumes that these registers' read and write energies are also zero.

### 4.4.3 Memory layout

Section 4.3.1 explained how the core works functionally but did not yet describe how the memory in the buffers and the memories are laid out. An explanation of different parameters of the cost model is needed first. Table 4.1 describes these parameters.

| Parameter           | Description                                       |  |  |  |

|---------------------|---------------------------------------------------|--|--|--|

| N <sub>neuron</sub> | Number of neurons on a core                       |  |  |  |

| $N_{syn}$           | Number of synapses on a core                      |  |  |  |

| Nlayer              | Number of layers on a core                        |  |  |  |

| N <sub>split</sub>  | Number of times a layer can be split              |  |  |  |

| $N_{w,x}$           | Number of slots of the mesh in the width          |  |  |  |

| $N_{w,y}$           | Number of slots of the mesh in the height         |  |  |  |

| N <sub>fanin</sub>  | Maximum fan-in synapses                           |  |  |  |

| $\dot{N_{types}}$   | Number of different packet types                  |  |  |  |

| P                   | Numbers of neurons/synapses executed concurrently |  |  |  |

Table 4.1: The parameters used in memory layout model

#### Mesh packets

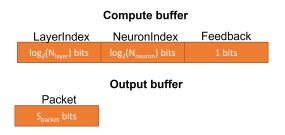

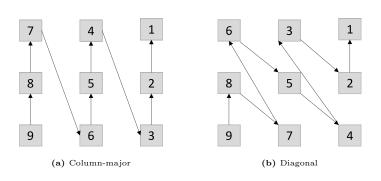

To dimension the router's buffers, the size of the different type of packets need to be known. The system uses three kinds of packets: the spike packet, the sync packet, and the ready packet. Figure 4.11 shows the memory layout for each packet type. The packet should always denote the destination core of the packet. The packet also holds the packet type. This way, the core or controller will know which kind of packet was received. The largest packet kind should dimension the input and output buffer width for the router. For this system, this will always be the spike packet. The size of the largest packet, i.e., the spike packet, will be called  $S_{packet}$ . The depth of a router's buffers is a configurable parameter.

| Spike                                     |                                           |                                             |                                             |                                              |          |  |  |  |  |

|-------------------------------------------|-------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|----------|--|--|--|--|

| DestCoreX                                 | DestcoreY                                 | Туре                                        | LayerIndex                                  | NeuronIndex                                  | Feedback |  |  |  |  |

| $\log_2(N_{w,x})$ bits                    | log <sub>2</sub> (N <sub>w,y</sub> ) bits | log <sub>2</sub> (N <sub>types</sub> ) bits | log <sub>2</sub> (N <sub>layer</sub> ) bits | log <sub>2</sub> (N <sub>neuron</sub> ) bits | 1 bits   |  |  |  |  |

| Sync & Ready                              |                                           |                                             |                                             |                                              |          |  |  |  |  |

| DestCoreX                                 | DestcoreY                                 | Туре                                        |                                             |                                              |          |  |  |  |  |

| log <sub>2</sub> (N <sub>w,x</sub> ) bits | log <sub>2</sub> (N <sub>w,y</sub> ) bits | log <sub>2</sub> (N <sub>types</sub> ) bits |                                             |                                              |          |  |  |  |  |

Figure 4.11: Memory layout of all mesh packet types.

#### Core buffers

Figure 4.12 shows the memory layout of the core's buffers. The compute buffer will hold the spikes until a synchronization event arrives. It must therefore be able to store the information regarding a spike. For that, it needs the layer that received the spike, the neuron that spikes in the previous layer, and whether it is a feedback spike. The compute buffer should be able to hold two times the maximum number of spikes according to the fan-in of the core, because there are actually two buffers. It should contain the spikes of the current timestep, and it should hold the spikes of the next timestep already being received. So, the the compute buffer should be able to hold  $2 \cdot N_{fanin}$  items. The output buffer will store the packets ready to be sent on the mesh and, therefore, should have a width equal to the packet size. The depth is configurable.

Figure 4.12: Memory layout of the core's buffers.  $S_{packet}$  is the size of a packet.

#### Core memory

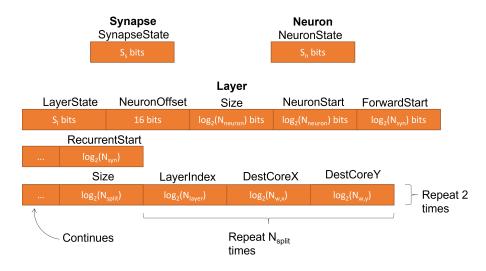

Figure 4.13 shows the memory layout of the neurons, layers, and synapses. The figure shows the names of the parameters corresponding to a certain piece of memory and the number of bits. The neuron, synapse, and layer should contain all parameters required to simulate a neuron, which will be stored in the NeuronState, SynapseState, LayerState respectively. Section 5.1.5 will contain more details on what these states contain for the experiments. The NeuronOffset is important when a layer is split. For example, if a layer has a size of 32 neurons and is split into two parts of 16, then the second part will have a layer offset of 16 neurons. Of course, the size corresponds to the size of the layer mapped onto the core. In our earlier example, both parts would have a size of 16 neurons. The NeuronStart, ForwardStart, and RecurrentStart denote where in the memories the start address of the neuron and the start of the forward and recurrent synapse for that layer are. Finally, the layer also needs to store the fanout for the layers. This fanout requires storing the coordinates of the cores and the layer address on the destination core. The core requires two rows of fanouts, one for the forward connections and one for recurrent connections.

The number of rows in the synapse, neuron, and layer memory will be  $N_{syn}$ ,  $N_{neuron}$ , and  $N_{layer}$  respectively. The compute's parallelism will affect the width and number of rows of the synapse memory and the neuron memory. For example, if the parallelism is two, the neuron memory will be twice as wide and half as deep. However, parallelism does not influence the layer memory.

Figure 4.13: Memory layout of the neuron, synapse, and layer memory.  $S_s$ ,  $S_n$ , and  $S_l$  describe the synapse, neuron and layer state sizes. These are described in section 5.1.5.

#### 4.4.4 Core

The energy and area numbers for the ALU on the core are based on the work of [39]. The work documents leakage power, area, and dynamic energy for several different types of functional units. Specifically, the 10 ns number should be used as the hardware model assumes 100 MHz.

Equation 4.6 shows the are usage of the the ALU.  $\mathbb{F}$  denotes the set of all functional units. N(f) denotes the number of functional units of type f on the core. N(f) is a model parameter as this depends on how the ALU is designed (see 4.3.1). A(f) denotes the area consumption of functional unit f. This area consumption comes from [39].

$$A_{alu} = \sum_{f \in \mathbb{F}} A(f) \cdot N(f) \quad [mm^2]$$

(4.6)

Equation 4.7 shows the energy consumption of the ALU. The first term is the dynamic energy consumption of the ALU and the second the leakage of the ALU. E(f) is the dynamic energy consumption of the functional unit according to [39]. And the  $N_O(f)$  is the number of operation of that type performed on that functional unit. This parameter is a result of the DES. t is the amount of time the inference took. Finally,  $P_l(f)$  is the leakage corresponding to the functional unit, also from [39].

$$E_{alu} = \sum_{f \in \mathbb{F}} E(f) \cdot N_O(f) + t \cdot \sum_{f \in \mathbb{F}} N(f) \cdot P_l(f) \quad [J]$$

(4.7)

Finally, equation 4.8 and 4.9 show the the area and energy consumption of a whole core respectively.

$$A_{core} = A_{alu} + A_{neuron} + A_{syn} + A_{layer} + A_{compute} + A_{output} \quad [mm^2] \quad (4.8)$$

$$E_{core} = E_{alu} + E_{neuron} + E_{syn} + E_{layer} + E_{compute} + E_{output} \quad [J] \quad (4.9)$$

#### 4.4.5 Routers

Each router will also have an energy and area consumption. The area that the switch takes up is difficult to quantify and will therefore not be considered. Therefore only the area of all memories is used. Equation 4.10 shows this equation.  $A_{r,input}$  and  $A_{r,output}$  are the areas of the input and output buffers, respectively.

$$A_{router} = 5 \cdot A_{r,input} + 5 \cdot A_{r,output} \quad [mm2] \tag{4.10}$$

The energy consumption of the router is based on [40]. The router design assumed for the work assumes a virtual-channel router which is different from this work that assumes a router that assumes a router with an input and output buffer. However, the energies should not be too different. Additionally, the numbers of this work are for a 130 nm process while the model of the simulator assumes a 40 nm. Therefore a correction needs to be applied. This correction will only correct for the difference in core voltages. The work does not mention the core voltage used for the chip. So it is assumed that a core voltage of 1.2 V was used. This means that all numbers needs to be corrected by a factor:  $C_f = \frac{1.1^2}{1.2^2}$ .

Equation 4.11 shows a modified version of equation 2 of [40]. The equation of [40] assumes that the amount of hops per packet are counted. However, for the simulator this is not feasible. Therefore, the simulator counts the the number of hops per router  $N_h$  and the number of packets switches  $N_s$ . This is enough to make an equivalent equation. The length of the links L are modelled by equation 4.12. This equation assumes that the router, the ALU, and the memory, among others fit perfectly together. Realistically, this is not the case, but this will still give a good indication.

$$E_{router} = ((1.37 + 0.12L)N_h + 0.98N_s) \cdot C_f \cdot 10^{-12} \quad [J]$$

(4.11)

$$L = \sqrt{A_{router} + A_{core}} \quad [mm] \tag{4.12}$$

#### 4.4.6 Chip total

Finally, the total area and energy consumption of chip are described by equation 4.13 and 4.14 respectively.  $\mathbb{R}$  is the set of all routers, and  $\mathbb{C}$  is the set of all active cores. An active core is a core with at least one layer mapped to it. The controller's slot will not contribute to the area of the chip. Additionally, the energy consumption of the controller is not considered.

$$A_{chip} = (N_{w,x} \cdot N_{w,y} - 1) \cdot (A_{core} + A_{router}) \quad [mm^2]$$

$$(4.13)$$

$$E_{chip} = \sum_{c \in \mathbb{C}} E_{core,c} + \sum_{r \in \mathbb{R}} E_{router,r} \quad [J]$$

(4.14)

# 4.5 Software architecture

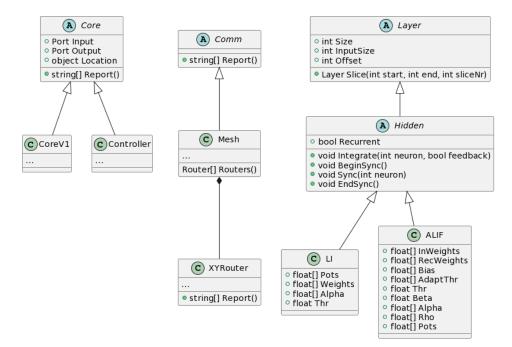

Since the simulator is a research tool, it is written in such a way that it is extensible. Figure 4.14 shows the decomposition that enables this flexibility<sup>3</sup>. For example, a user can implement custom hidden layers. This new custom implementation could be a neuron model with different mechanics. Or interestingly, a custom implementation of a hidden layer could use a trace file instead of computing the numbers on the fly. This way, the simulator can become trace-driven. The figure shows that ALIF and LI are implementations of this hidden layer class. A hidden layer implementation requires a description of how it syncs, how it integrates, and whether it is recurrent. In addition, the layer requires the size of the layer in neurons and the input size. The input size is the size of the previous layer.