### MASTER

Large-Block Multi-rate Streaming Sort

van Valenberg, Damy F.B.

Award date: 2022

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Mathematics and Computer Science Architecture of Information Systems Research Group

### Large-Block Multi-rate Streaming Sort

Master Thesis

$\begin{array}{c} {\rm Damy \ van \ Valenberg}\\ (2087728) \end{array}$

Supervisors: Prof.dr.ir. C.H. van Berkel Dr. R.H. Mak Dr.ir. R. Jordans

Version 1.0

Vught, July 2022

### Preface

Before you lies the thesis "Large-Block Multi-rate Streaming Sort". The purpose of this research is to improve upon or find a new solution for streaming sorting. The thesis has been written to fulfil the graduation requirements for the Master's degree in Embedded Systems at the Eindhoven University of Technology. I started the research in July 2021 and should be finished in July 2022.

This project was chosen in consultation with Kees van Berkel. The research was conducted solely for the Eindhoven University of Technology. For me, the research was a lot more difficult than initially expected. Fortunately, I was still able to provide an answer to the research question with a design and partial implementation in StaccatoLab. Also, a novel design for parallel sorting with higher-throughput was found.

I would like to thank my supervisor Kees van Berkel for the excellent guidance, pushing me out of my comfort zone and for keeping me critical at my own work. I would also like to thank my family and friends for keeping me motivated and all advice.

I hope you enjoy reading my thesis.

Damy van Valenberg

Vught, June 2022

### Abstract

Sorting is an important problem in computer science. It is a very fundamental concept used in many other algorithms, but is also critical for the performance of databases, for example. If large data sets or high-performance sorting is required, sorting using only the CPU is often infeasible, and often only hardware sorting can satisfy the requirements. The simplest solution is sorting on the GPU, but an FPGA or ASIC can also be used. In this research, we find a solution for the following problem:

How can a streaming sort

- of large blocks (of variable size) of key-value pairs be achieved

- with a fixed rate greater or equal to two

- while minimizing memory resources and traffic

- given it will be modelled in StaccatoLab

- with possibly an FPGA with external memory implementation?

The research is split up in three phases. In the first phase, some optimizations are made for the baseline sorter, such as minimizing the memory usage and solving the variable block sizes. During the second phase, the single rate sorter is parallelized, such that it becomes a multi-rate sorter. This increases the throughput of the sorter. The parallelization uses a novel method. The design is pipeline-friendly, which allows very high clock rates. The example provided in this research uses a parallelization of P = 4, and a clock frequency of 200 MHz, with a key-value pair size of 128 bits, this results in a throughput of 12.8 GB/s. This throughput is enough to fully saturate the bandwidth of the DDR3-1600 DRAM memory onboard the Xilinx VC707. But higher parallelization and clock frequencies are also possible as long as the input and output mediums can handle the throughput.

In the final phase of the research, the focus lies on sorting large blocks/data sets. The data is so large, that it must be stored in external memory or even external storage. It is also found that sorting is limited by the bandwidth of the external memory, which means that the reads and writes to the external memory must be kept as low as possible. Moreover, it is important to guarantee 100% bandwidth utilization of the external memory/storage, such that there is no loss of throughput. The result is a very efficient sorter, which is compared to another existing work, and reduced the sorting time of sorting 0.5 GB from 2390 seconds to 1650 seconds on the same hardware. This is a reduction of approximately 31% of sorting time.

## Contents

| Co            | itents                                                                                                                                                                                                                                    | iv                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| $\mathbf{Li}$ | of Figures                                                                                                                                                                                                                                | vi                                                  |

| $\mathbf{Li}$ | of Tables v                                                                                                                                                                                                                               | <b>/ii</b>                                          |

| 1             | Introduction                                                                                                                                                                                                                              | 1                                                   |

| 2             | Background information         2.1 Dataflow                                                                                                                                                                                               | <b>2</b><br>3<br>4<br>4<br>4<br>5<br>5<br>7         |

| 3             | Existing research                                                                                                                                                                                                                         | 9                                                   |

| 4             | Problem description 1                                                                                                                                                                                                                     | 10                                                  |

| 5             | 5.1       Baseline       1         5.2       Caching       1         5.3       Memory usage       1         5.3.1       Removing slack       1         5.3.2       Adding indexing       1         5.4       Variable block sizes       1 | <b>12</b><br>12<br>13<br>13<br>13<br>14<br>16<br>17 |

| 6             | 5.1       Sorting networks       1         5.2       Parallel sorting       2                                                                                                                                                             | <b>19</b><br>19<br>21<br>21<br>21                   |

| 7            | Multi pass sorting                                                                                          | 26 |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|              | 7.1 K-way merge                                                                                             | 28 |  |  |  |  |

|              | 7.2 Design                                                                                                  | 28 |  |  |  |  |

|              | 7.3 Buffer sizing                                                                                           | 29 |  |  |  |  |

|              | 7.4 Implementation                                                                                          | 31 |  |  |  |  |

|              | 7.4.1 StaccatoLab $\ldots$ | 31 |  |  |  |  |

|              | 7.4.2 Larger implementations                                                                                | 32 |  |  |  |  |

|              | 7.4.3 Results $\ldots$                                                                                      | 33 |  |  |  |  |

| 8            | Improvements                                                                                                | 35 |  |  |  |  |

| 9            | Conclusions                                                                                                 | 36 |  |  |  |  |

| Bi           | bliography                                                                                                  | 37 |  |  |  |  |

| A            | ppendix                                                                                                     | 39 |  |  |  |  |

| $\mathbf{A}$ | Flag derivation                                                                                             | 39 |  |  |  |  |

| В            | Single pass sorting code                                                                                    | 42 |  |  |  |  |

| С            | C Multi-rate sorting code 48                                                                                |    |  |  |  |  |

| D            | D Multi pass sorting code 55                                                                                |    |  |  |  |  |

## List of Figures

| 2.1 | Dataflow graph                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | FIR filter as a dataflow model                                                                                                                |

| 2.3 | Radix sort double buffering implementation                                                                                                    |

| 2.4 | Pseudocode for the merge function of the merge sort                                                                                           |

| 2.5 | Merge sort, divide and conquer strategy 8                                                                                                     |

| 2.6 | Pseudocode for the complete merge sort                                                                                                        |

| 4.1 | System overview                                                                                                                               |

| 5.1 | Merge sort implementation for $N = 8$                                                                                                         |

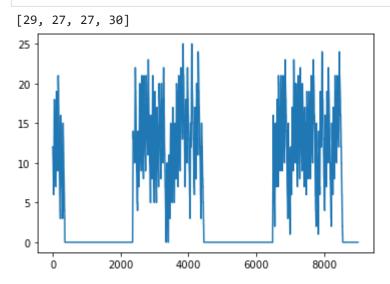

| 5.2 | Memory usage trace for the merge stage $n = 8$                                                                                                |

| 5.3 | Memory usage comparison for a single stage with key size, $k=128 \ldots \ldots \ldots 16$                                                     |

| 5.4 | Split (spl) node sending all blocks of size 1 to edge A (flow only view) 16                                                                   |

| 5.5 | Split (spl) node code                                                                                                                         |

| 6.1 | Bitonic merge sort                                                                                                                            |

| 6.2 | Batcher Odd-Even Mergesort 21                                                                                                                 |

| 6.3 | Terabyte sort merger                                                                                                                          |

| 6.4 | Minimum select design for $P = 4$                                                                                                             |

| 6.5 | Logarithmic plot of the comparator count for designs 1 and 2                                                                                  |

| 6.6 | Multi-rate first two stages                                                                                                                   |

| 6.7 | Multi-rate last stages                                                                                                                        |

| 6.8 | Memory usage multi-rate sorter                                                                                                                |

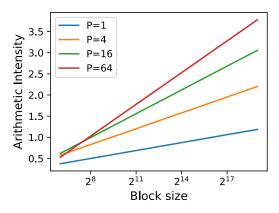

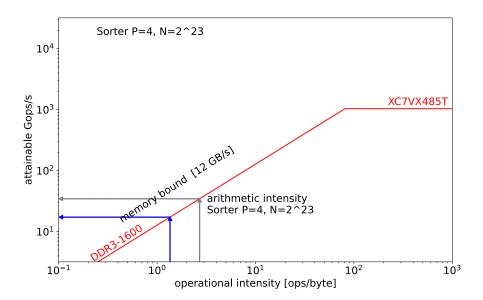

| 7.1 | Difference in arithmetic intensity for several levels of parallelism $(P)$                                                                    |

| 7.2 | Roofline for a block size of 128 MB. The operational intensity is half the arithmetic                                                         |

| 7.3 | intensity for two passes                                                                                                                      |

| 1 2 |                                                                                                                                               |

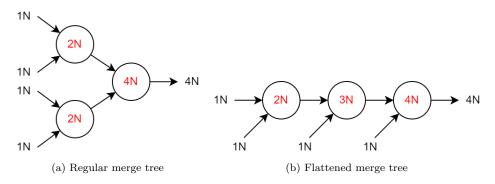

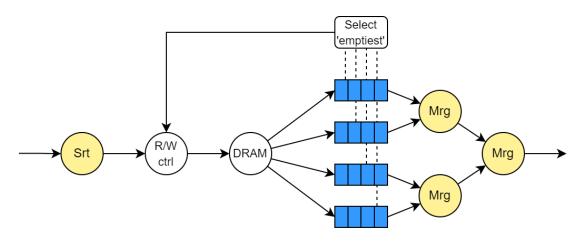

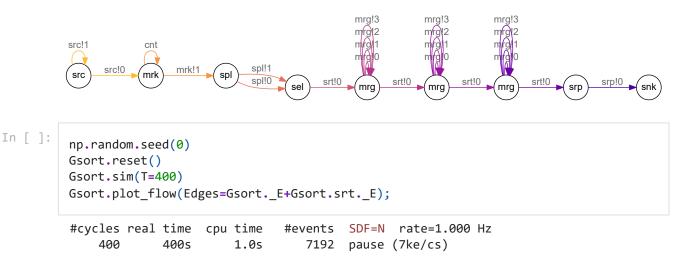

| 7.4 | 4-way merge tree variants $\dots \dots \dots$ |

## List of Tables

| 2.1 | List of comparison sort algorithms                                                                                                                                                                                                                                              | 6                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5.1 | Merge stage input/output data                                                                                                                                                                                                                                                   | 17                         |

| 6.1 | Table of the comparator count for designs 1 and 2                                                                                                                                                                                                                               | 23                         |

| 7.2 | Arithmetic intensity with a block size of $N = 1024$ pairs (16 KB) Optimal solutions for two passes. N is in number of pairs (128-bit per pair) Optimal solutions for three passes. $N * K^2 = 1$ GB for all solutions Required N, K and passes to sort 0.5 GB for P 1 up to 32 | 26<br>32<br>33<br>33<br>34 |

|     | 512 GB expected sorting performance with the proposed design                                                                                                                                                                                                                    |                            |

# Chapter 1 Introduction

Sorting is a very well-known problem in computer science. It is often at the core of almost every application that processes data. For example, databases depend heavily on sorting [17], selecting and sorting millions of records. Efficiency of the sorting process is critical for these systems. Some database systems even use hardware acceleration using FPGA's to improve sorting performance[4]. Besides direct applications of sorting, there are also numerous algorithms that depend on sorting. For example, searching, checking for uniqueness, min/max selection and many more. Any minor improvement in sorting performance could potentially have a significant impact on many future systems.

The research focuses on finding a solution for a streaming sort implementation in hardware, specifically an FPGA. The research is split up in three parts. In the first part, a single-rate streaming sorter is designed and implemented. A single-rate streaming sorter takes in a stream of unsorted data and produces a stream of sorted data. The streams have a rate of one, so one value enters, and one value exits each clock cycle (hence, the single-rate). In the second part, the single-rate solution is parallelized, such that the sorter can process more than one value in one clock cycle. As a result, the input, and output streams also transfer multiple values each cycle. This sorter is called a multi-rate streaming sort. In the last part of this research, a multi pass sorter is designed. In which case, data is temporarily stored in external memory. This is needed when the unsorted data set is so large that it no longer fits in the internal memory of the FPGA.

There is a lot of existing work on sorting in hardware. But most research focuses on batch sorting, not streaming sorting. There is one very detailed paper, 'Terabyte Sort on FPGA-Accelerated Flash Storage'[9], by Sang-Woo Jun, Shuotao Xu and Arvind. The paper was published in 2017 and contains a lot of design, implementation, and performance details. The performance seems good and is realistic. This paper was mainly used as a benchmark to compare to this research.

### Chapter 2

### **Background** information

### 2.1 Dataflow

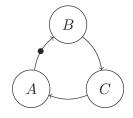

For this research, dataflow is used to solve the sorting problem. There are many variants of dataflow. Most relevant are static dataflow, cyclo-static and dynamic dataflow. Every dataflow graph contains nodes, edges and tokens. A basic (flow only) dataflow graph is shown in figure 2.1. It contains three nodes (A, B and C) and the nodes are connected by (directional) edges. The edge between node A and B contains a token, indicated by the black dot on the edge. A token can contain data, which can be a single value or a complex structure (such as tuples). An edge can also store more than one token. The number of tokens it can store is also called slack. The tokens on the edges always have FIFO behaviour. In static dataflow, if a token is present on every input edge of a node, the node will fire, consuming the input tokens and producing a token on every output edge using its output function(s). In cyclo-static dataflow, the firing is controlled by a finite state machine (FSM). The state machine uses firing rules that indicate which input tokens will be consumed and which output tokens will be produced. In dynamic dataflow, the FSM of a node is dependent on the data in a token.

Figure 2.1: Dataflow graph

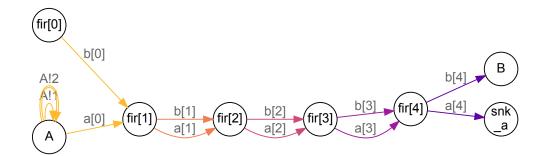

StaccatoLab[1] is a tool developed by Kees van Berkel. This tool is used to model and simulate dataflow graphs. There are many problems that can modelled using a dataflow graph. One simple example is digital audio filters. In figure 2.2 a FIR (finite impulse response) filter is shown that was modelled in StaccatoLab. Models in StaccatoLab can be thoroughly analysed, since the input and output can be fully simulated. StaccatoLab helps to calculate the throughput and latency of the model (and many other statistics). This also makes it simple to calculate the required clock frequency if the model is to be implemented in hardware.

Besides simple filters, there are also many other algorithms that can be modelled. For example, a data stream can be inverted, selecting minimum or maximum values from a stream, or even sorting, which is the main focus of this research project. The dataflow graphs can also be converted to hardware implementations. It should be possible to do this conversion automatically, which is a feature that is still in development in StaccatoLab.

Figure 2.2: FIR filter as a dataflow model

Traditionally, most implementations of algorithms are designed with memory-based computing in mind. In which data is read/written from/to a shared memory to achieve the desired result. The memory bandwidth is often limiting the throughput. Caching or shared memory modules used in GPU's can increase performance significantly. In dataflow, the design and implementation is based on the data and how this moves through the graph. The edges in dataflow graphs are often just registers or a small block of ram (BRAM) when it is transformed to an FPGA implementation. The registers and BRAM can be read/written independently, which allows many reads and writes each cycle. Sorting is also often limited by the memory bandwidth. This is why sorting is an interesting subject to be modelled with dataflow. Moreover, dataflow simplifies designing for a known throughput. For example, it is often easy to ensure that a graph will fire every cycle (although not always possible). In which case, the throughput is mainly dependent on the clock frequency. This also makes for a very efficient design, since the used hardware will often have a high utilization.

All the nodes of a dataflow graph can fire independently. This makes parallelism easy to implement. Without going into too much detail, the FIR filter implementation from figure 2.2 uses pipelining behaviour. The FIR filter must do four multiplications with a coefficient and the input data and sum the results for the correct output. These multiplications and additions are done in each fir[1]..fir[4] stage. By using pipeline parallelism, it is possible to stream this FIR filter, so each cycle one output is produced. An example of another form of parallelism, that is not pipeline behaviour, would be to duplicate this FIR filter implementation one or more times. This allows processing of multiple independent streams, essentially raising the throughput. This can be useful when filtering audio with both a left and right channel, for example, since these streams are independent.

### 2.2 Sorting definition

As said before, sorting plays an important part in computer science. But what is sorting, actually? Let's first define a sorted list. Assume there is a list A, and  $a_i$  is the element in list A at index i. Then the list A is sorted when it satisfies the following condition  $\forall [0 \le i < |A| - 1 : a_i \ge a_{i+1}]$ . More specifically, this defines the descending order. The ascending order is defined as follows,  $\forall [0 \le i < |A| - 1 : a_i \le a_{i+1}]$ . Note that a list can contain any type of data (numbers, strings, etc.) as long as the relation ' $\le$ ' and ' $\ge$ ' can be defined for all the elements in the list. A list is considered unsorted when it satisfies neither the descending nor ascending condition. Sorting is the process that converts an unsorted list (or sorted if the state of the list is unknown) into a sorted list, without removing or adding values. Sorting can be done using a sorting algorithm.

Sorting can be done on the CPU, but is also regularly done on the GPU or even specialized hardware, such as an FPGA. The idea of hardware sorting is to improve the performance compared to sorting on the CPU, since an FPGA can achieve a very level of parallelism. This also frees the CPU to do other tasks. In most cases, a block of data is provided to the sorting hardware via

some kind of shared memory. When the hardware has finished sorting, the data should be sorted in the same or another block of shared memory.

There are different implementations of sorting algorithms in hardware. Two classifications are important. Firstly, an implementation can be either a batch sorter or a streaming sorter. Secondly, an implementation can be either sequential or parallel. These two classifications are independent of each other. What they exactly mean will be described in the next sections.

### 2.2.1 Batch sorting

One of the most common ways to implement a hardware sorter is to connect the hardware to the CPU using shared memory. The shared memory is the bridge between the CPU and sorting hardware. The CPU signals the sorting hardware when it has finished copying the unsorted data to the shared memory. The sorting hardware will then start sorting using its algorithm. The hardware will signal the CPU once it has finished sorting. The CPU can then read the sorted output from shared memory.

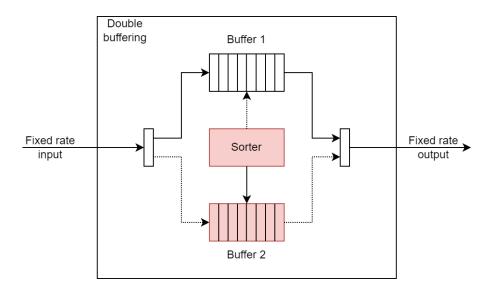

This is an easy way to implement a sorter. However, there are some issues with this approach. Often the processing time is not constant (this depends on the sorting algorithm), which makes performance analysis more difficult. Another issue is that the next block of data cannot be copied to the shared memory until the hardware has finished sorting. This issue could be resolved by using double buffering. But, as a consequence, this would also mean you need twice the amount of memory.

### 2.2.2 Streaming sort

In the case of a streaming sort, a constant stream of data is provided to the hardware. The samples from the stream arrive at a fixed rate. For example, every cycle, one sample is provided to the sorter. Interestingly, the hardware sorter can already start sorting when the first sample arrives. And actually the sorter should start the sorting immediately because otherwise the input values must be buffered, which would increase the memory required. A good streaming sorter implementation will often have a low latency and a fixed throughput. However, since the sorter needs to start sorting when not all data is available yet, only a few sorting algorithms can be used. Most sorting algorithms require all data before they can start the sorting process.

Such an input stream could be from a sensor, which periodically measures something, or an audio source, for example. Or if the FPGA is integrated in a PC, this could be a PCIe data stream. This makes streaming sorters very useful for real-time applications. The main advantage of a streaming sorter is that the values do not have to be stored in external memory, which reduces hardware resources and power consumption.

#### 2.2.3 Dataflow rate

In dataflow, a common characteristic of any design is the dataflow rate. It indicates how many tokens are consumed (and produced) every clock cycle. A graph with rate 1 consumes 1 token each cycle. A graph with a rate of 0.5 consumes 1 token every 2 cycles. However, a graph can also have a rate larger than 1. A graph with rate 2 consumes 2 tokens each cycle.

Note that a multi-rate (rate > 1) streaming sort has a higher throughput than a streaming sort with a rate of 1 assuming the clock frequency is the same, which will be explained now.

#### 2.2.4 Throughput

Throughput is one of the metrics which can be used to measure the performance of a system. Throughput can be measured (or calculated) at the input or output of a system. In the case of sorting, the input and output throughput should be equal. This is because the number of tokens in the system should remain constant, as there is a finite amount of memory to hold the tokens.

For a streaming sorter, the throughput is directly related to the dataflow rate. The data consumed each cycle is determined by the token size and dataflow rate, which can be multiplied to get the total input size to the system. If the input size is multiplied again by the frequency of the system, the result shall be the throughput, as shown below.

$Throughput = Clock \ frequency \times rate \times token \ size$

Throughput can be expressed in different units. The most common units are bits per second (also known as bitrate) or bytes per second, and are often combined with metric prefixes. For example, 1,000 bit/s = 1 kbit/s or another example, 1,000,000 bytes/s = 1 MB/s.

#### 2.2.5Latency

Latency is defined as the time delay between the input and the output of a system. It can be measured in different ways. Consider the following case, a large block of data is consumed element by element on the input and later produced element by element on the output. Then the latency can be measured from the first input to the first output, or from the first input to the last output, etc. So, for latency, it is always important to explicitly indicate or check what is meant.

#### 2.2.6Sorting algorithms

There are many sorting algorithms. One of the main characteristics used to compare these algorithms is the performance. For this, the big O notation is used. This indicates how the performance will be affected if the number of items to be sorted increases. For example, the insertion sort has a worst-case performance of  $\mathcal{O}(n^2)$ . So, as the number of items to be sorted increases linearly, the sorting time increases quadratic.

Sorting algorithms are also distinguished by being a comparison sort or not. Comparison sorts, sort a list of data only by comparing elements. Comparison sorts have been proven to be limited to  $\mathcal{O}(n \log n)$  as the average case performance [8]. Non-comparison sorts are not bound to this limit. However, they often have other constraints, such as limited key size or range. The most well-known comparison sorting algorithms with their performance is shown in table 2.1.

The most important non-comparison sorts are the counting and radix sort. They are used in many sorters, since they perform extremely well. Counting sort has an average case performance of  $\mathcal{O}(n+r)$ , where r is the range of the keys. Radix sort has an average case performance of

$\mathcal{O}(n \cdot \frac{k}{d})$ , where k is the size of the key and d is the digit size. [19]

The radix sort is often implemented in software running on the CPU or the GPU. Its performance can be better than a simple merge sort. The "Designing Efficient Sorting Algorithms for Manycore GPUs" [18] paper shows an implementation which is faster than a merge sort on the GPU. Although the radix sort is not limited to a software implementation (as shown in the paper "FastRadix: A Scalable Hardware Accelerator for Parallel Radix Sort" [12]), it becomes unpractical to implement standalone on an FPGA as a streaming sort. Radix sort requires all data of the block before it can start the sorting process. This has several unwanted consequences for a streaming sort implementation. Most importantly, the hardware implementation would not be able to accept new incoming values (which will arrive every cycle, since a streaming sort is required) until the sorting is complete. This means the incoming values need to be stored/buffered. before they can enter the sorter. This would most likely be done using double buffering, which will significantly increase the memory usage. An example of what such an implementation would look like is shown in figure 2.3. Sorting algorithms that behave like batch sorters often require this double buffering solution to turn them into streaming sorters. Another result is that all data needs to be stored in the same BRAM. Every BRAM block in an FPGA often has two read/write ports. As a result, a very high memory throughput could be reached if these BRAMs are used independently in parallel. But if all the data needs to be stored in 'joined' BRAM blocks, this limits the read/write operations to two per cycle.

| Name                 | Best $(\mathcal{O})$ | Average $(\mathcal{O})$ | Worst $(\mathcal{O})$ | Method                   |

|----------------------|----------------------|-------------------------|-----------------------|--------------------------|

| Quicksort            | $n\log n$            | $n\log n$               | $n^2$                 | Partitioning             |

| Merge sort           | $n\log n$            | $n\log n$               | $n\log n$             | Merging                  |

| Introsort            | $n\log n$            | $n\log n$               | $n\log n$             | Partitioning & Selection |

| Heapsort             | $n\log n$            | $n\log n$               | $n\log n$             | Selection                |

| Insertion sort       | n                    | $n^2$                   | $n^2$                 | Insertion                |

| Block sort           | n                    | $n\log n$               | $n\log n$             | Insertion & Merging      |

| Timsort              | n                    | $n\log n$               | $n\log n$             | Insertion & Merging      |

| Selection sort       | $n^2$                | $n^2$                   | $n^2$                 | Selection                |

| Cubesort             | n                    | $n\log n$               | $n\log n$             | Insertion                |

| Shellsort            | $n\log n$            | $n^{4/3}$               | $n^{3/2}$             | Insertion                |

| Bubble sort          | n                    | $n^2$                   | $n^2$                 | Exchanging               |

| Exchange sort        | $n^2$                | $n^2$                   | $n^2$                 | Exchanging               |

| Tree sort            | $n\log n$            | $n\log n$               | $n\log n$             | Insertion                |

| Cycle sort           | $n^2$                | $n^2$                   | $n^2$                 | Selection                |

| Library sort         | $n\log n$            | $n\log n$               | $n^2$                 | Insertion                |

| Patience sorting     | n                    | $n\log n$               | $n\log n$             | Insertion & Selection    |

| Smoothsort           | n                    | $n\log n$               | $n\log n$             | Selection                |

| Strand sort          | n                    | $n^2$                   | $n^2$                 | Selection                |

| Tournament sort      | $n\log n$            | $n\log n$               | $n\log n$             | Selection                |

| Cocktail shaker sort | n                    | $n^2$                   | $n^2$                 | Exchanging               |

| Comb sort            | $n\log n$            | $n^2$                   | $n^2$                 | Exchanging               |

| Gnome sort           | n                    | $n^2$                   | $n^2$                 | Exchanging               |

| Odd–even sort        | n                    | $n^2$                   | $n^2$                 | Exchanging               |

Table 2.1: List of comparison sort algorithms with their corresponding complexity in big- $\mathcal{O}$  notation. [19]

Figure 2.3: Radix sort double buffering implementation

### 2.3 Merge sort

The merge sort algorithm lends itself extremely well to hardware implementations, which will be shown later (in chapter 5.1). The merge sort is a simple sorting algorithm, and has a complexity of  $\mathcal{O}(n \log n)$ , which means it scales optimal for a comparison sorting algorithm.

The core of the merge sort is the merge function. It takes in two sorted lists, which it merges to produce one sorted output list. The merging is done by only looking at the front of each list, since they contain the lowest elements. The lowest of the two elements is removed from the corresponding list and is appended to the back of the output list. This process is repeated until both lists are empty. Pseudocode for the merge algorithm is shown in figure 2.4.

```

function merge(left, right) is

var result := empty list

while left is not empty and right is not empty do

if first(left) <= first(right) then

append first (left) to result

left := rest(left)

else

append first (right) to result

right := rest(right)

// Either left or right may have elements left; consume them.

// (Only one of the following loops will actually be entered.)

while left is not empty do

append first (left) to result

left := rest(left)

while right is not empty do

append first (right) to result

right := rest(right)

return result

```

Figure 2.4: Pseudocode for the merge function of the merge sort[20]

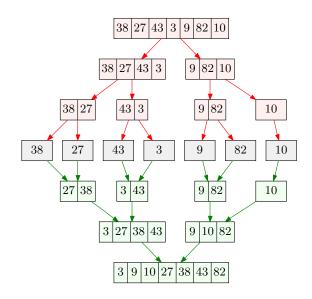

The merge sort algorithm uses the divide and conquer strategy to sort an input list with random data. This is well illustrated in figure 2.5. The unsorted list on top in red is broken up into smaller parts, until only one element remains in all lists. The merge function is then used to build increasingly larger lists (in green), until the final output list is produced. The pseudocode for the complete merge sort algorithm can be seen in figure 2.6.

Figure 2.5: Merge sort, divide and conquer strategy[7]

```

function merge_sort(list m) is

//\ Base \ case. A list of zero or one elements is sorted, by definition.

if length of m \ll 1 then

return m

// Recursive case. First, divide the list into equal-sized sublists % \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}

consisting of the first half and second half of the list.

// This assumes lists start at index 0.

var left := empty list

var right := empty list

for each x with index i in m do

if i < (length of m)/2 then

add x to left

else

add x to right

//\ Recursively sort both sublists.

left := merge_sort(left)

right := merge_sort(right)

// Then merge the now-sorted sublists.

return merge(left, right)

```

Figure 2.6: Pseudocode for the complete merge sort[20]

# Chapter 3 Existing research

Finding applicable, high-quality papers of existing work also makes up a large part of the research. Many papers exist about dataflow, but none that combine dataflow with sorting. But, papers about sorting algorithms are plentiful. Most FPGA implementations use some kind of merge sorter or a combination with another sorter, such as sorting networks. Sorting networks also seems to be an important part of many implementations. There are also many papers that use the parallelism of the GPU with different algorithms. Most of the GPU papers seem irrelevant, since there is a too much of a difference between a GPU and an FPGA, but these could be used to compare performance. Some papers are discussed in the next paragraphs.

The paper "Terabyte Sort on FPGA-Accelerated Flash Storage" by Sang-Woo Jun, Shoutao Xu and Arvind[9] was by far the most important for this research. This paper gives an in-depth design and implementation of a parallel hardware sorter. The smallest part or core component of their sorter is actually a streaming sort. Not only that, it is also a multi-rate sorter, which is helpful for the second phase of the research. This component is reused in other components that are required to create a larger sorting network. The streaming sorter uses merge sorting as a sorting algorithm. The streaming sorter has a throughput of 4 GB/s at 125 MHz. The paper also gives a solution for sorting large data-sets (up to 1 TB, hence the name of the paper). They utilize a 1 TB PCIe SSD to load and store the data. All things combined make the paper very valuable to this research.

Another paper called "Hardware Acceleration of Sorting Algorithms Using Reconfiguration Technics" by Pawel Russek and Kazimierz Wiatr ([17]) contains in depth information about the implementation of sorting nets for FPGA's. This paper connects closely with the previous paper by Sang-Woo Jun. It includes half cleaners, but also full sorting nets, which will be useful again for implementing a multi-rate design. Moreover, it also includes some practical limits for the sorting nets.

NVIDIA published a paper in 2009 called "Designing Efficient Sorting Algorithms for Manycore GPUs" written by Nadathur Satish, Mark Harris and Michael Garland ([18]). The paper claimed to have the fastest sorter at that time. It combines radix sort, counting sort and merge sort into one sorting algorithm. The sorting is done in parallel on the streaming processors of a GPU. The NVIDIA GPU's contain many layers of memory[13]. It has external memory, L2 cache and L1 cache. This is not available in an FPGA, since that only has BRAM. The bandwidth of the external memory (GDDR5X) of a GTX 1080 is around 320GB/s, which is much higher than that compared of the DDR3 dram of 12.8GB/s used in this research. The architecture differs too much to adapt the implementation for hardware/dataflow. But, it shows how fast the radix sort can be.

Finally, in the paper "FastRadix: A Scalable Hardware Accelerator for Parallel Radix Sort" by Xingyu Liu and Yangdong Deng ([12]) they also implemented a radix sort in hardware. They propose the "FastRadix" hardware accelerator, which differs slightly from the standard radix sort. The sorter was implemented on an FPGA and works together with the CPU. The paper includes some implementation details about their radix sort, which can be very valuable if, at a certain point, a radix sorter will be designed in StaccatoLab for the research project.

# Chapter 4 Problem description

As said in the introduction, sorting is a basic but also crucial problem. In software, the problem has been very well researched, and most recent improvements come from using the GPU. But when sorting in hardware, there are many ways to implement a single algorithm as there is a lot more freedom in the architecture. This makes hardware sorting so interesting. The most common hardware implementations use an FPGA or ASIC. In this research, the main focus lies on FPGA's, but is also applicable to an ASIC. A hardware sorter is often used as a form of hardware acceleration as part of a server, but could also be used standalone. Both the FPGA and ASIC are capable of achieving a very high level of parallelism, which can increase the performance of such algorithms drastically. As a consequence of using hardware acceleration, the CPU will also be freed to do other work while the hardware is sorting.

Existing research focuses mainly on batch sorting. There are only few existing streaming sort solutions. This research project will take a step even further. The focus will be on creating an efficient streaming sort implementation in StaccatoLab with a data-rate larger than 1 for any data block size. This research will explore some new area's and will hopefully be able to improve the existing implementations. A minor improvement to existing sorting solutions could already have a significant impact because sorting is so essential to many other (aforementioned) applications.

For the final design, the target will be to sort large data sets that will not fit inside the memory of an FPGA. As a result, the FPGA must fall back to external memory, such as DRAM or even other (external) storage, such as an SSD or HDD. The data sets could even be so large, that the FPGA would require multiple passes over the data, which means the same data must be read and written multiple times from/to external memory.

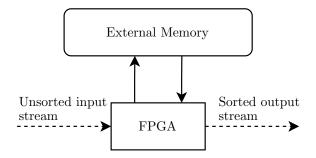

A very basic diagram of the system is shown in figure 4.1. This is not a design to solve the problem, but is shows the environment in which the problem exists. The hardware which will be used for the research is the same as the hardware used in the Terabyte sort paper. Namely, the Xilinx VC707 Evaluation Kit. It contains a Virtex-7 (XC7VX485T-2FFG1761C) as the FPGA and the board has 1 GB of DDR3-1600 memory.

Figure 4.1: System overview

Sorting is almost always done using a key-value pair. The keys are what is looked at for the sorting. The value is not used for the sorting itself, but it contains the reference to the actual data. Using a key-value pair avoids having to move a large amount of unused data around. For this research, both the key and value are assumed to be 64-bit, so one key-value pair is 128-bits in total.

The research question is formulated as follows:

How can a streaming sort

- of large blocks (of variable size) of key-value pairs be achieved

- with a fixed rate greater or equal to two

- while minimizing memory resources and traffic

- given it will be modelled in StaccatoLab

- with possibly an FPGA with external memory implementation?

The research question is divided up into three parts. In the first part, a baseline solution is analysed and improved to sort small (but variable) block sizes at rate 1, using minimal internal memory. The second part will use the knowledge of the first part to parallelize the solution and make it multi-rate. In the final part, multi pass sorting is researched to be able to sort the large block sizes.

There could be many solutions for each sub problem, which makes it extra important to properly compare the solutions. Each solution will be measured/analysed by the following statistics:

- Throughput (bytes per second) or sorting time (total seconds)

- Comparators used

- BRAM (internal memory) used

- DRAM (external memory) used

## Chapter 5

## Single pass sorting

### 5.1 Baseline

The merge sort algorithm has multiple phases. Each phase merges two sorted lists from the previous phase to create a sorted list that has the length of both input lists combined. So, each phase produces a sorted list twice as large as the previous phase. If the phase is defined as  $1 \leq p$ , then  $n = 2^p$  is the size of the sorted output list. For an unsorted list of size N (for now N is assumed to be a power of two), there are  $log_2(N)$  phases. In the last phase  $n = 2^{log_2(N)} = N$ . In a first phase, the inputs are two lists containing one element and the output will be a list containing n = 2 elements in sorted order. But there will be N/2 sorted lists (of size 2) produced. In any phase, to produce a list of size n, at least n - 1 comparisons are required in the worst case. So for a list of size N, a phase requires  $\frac{N}{n} * (n-1)$  comparisons. But, each phase will of course process exactly N elements. The  $\frac{N}{n}$  number of lists produced in each phase are completely independent, which actually means that once two lists are available, the next phase of the merge sort can already start. This allows a pipelining behaviour. In hardware, each phase is modelled as a stage. Each stage has a rate of 1 and processes N elements. As a result, in the long run, each stage has a throughput of 1 and a utilization of 100%.

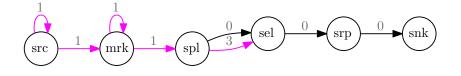

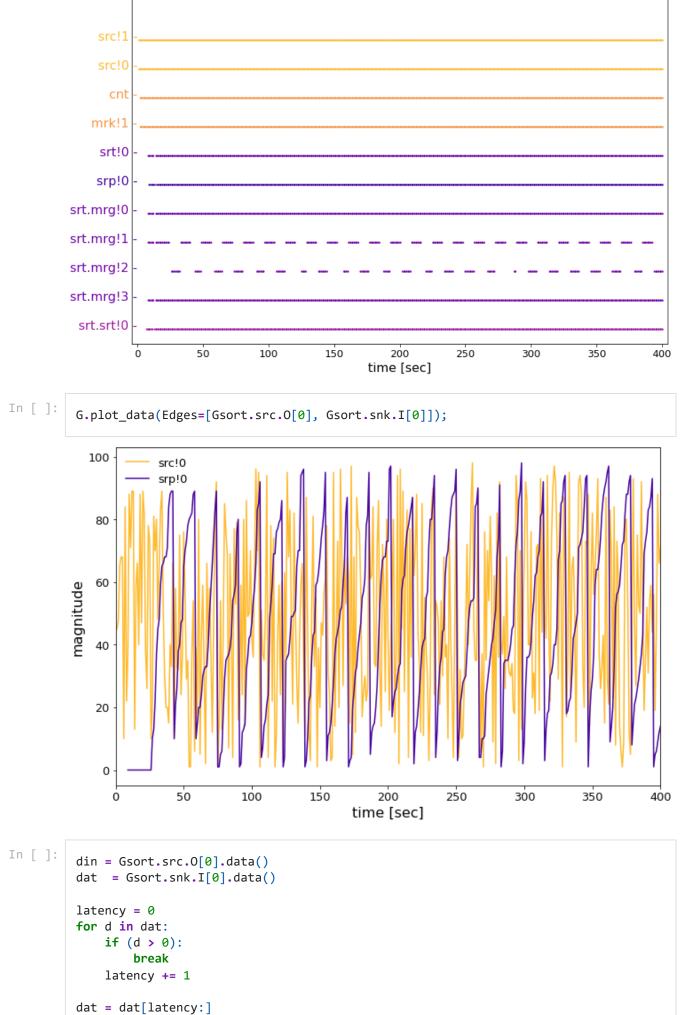

In 1991 Edward Ashford Lee published a paper which presents a streaming merge node for two monotonically increasing input streams in dataflow[10]. This is essentially one stage of a complete merge sorter. The book 'Mutli-Processor System-on-Chip: Vol. 2'[1], gives a full implementation of a merge sorter in StaccatoLab, which were based on the findings of Lee. Figure 5.1 shows the implementation of the merge sorter in StaccatoLab. The implementation sorts blocks of size N = 8. The src node produces a random data stream with values between 0 and 100. The srt node is the first stage that does a merge sort. It takes two tokens, sorts them, and produces them back on its output edge (producing n = 2 sorted list). The next stage of the merge sorter actually includes two nodes, namely the spl and mrg nodes. The spl node is basically a switch to move the sorted sub-lists from the previous stage to the correct input edge for the mrg node. Once there are tokens on both the spl!0 and spl!1 edges, then the mrg node will start merging these two sub-lists to produce a sorted list of length N = 4. The next stage again consists of the spl and mrg nodes. Note that this spl node switches lists of size N = 4. The last mrg node produces a list of size N = 8. The number of stages the merge sorter has is equal to  $\log_2(N)$ .

This implementation has a rate of 1. Which means that each cycle, one token is consumed, and one token is produced. That makes this implementation a streaming sort. The average latency of a token is also relatively low and equal to exactly  $N + 2 \cdot (\log_2(N) - 1)$ .

Figure 5.1: Merge sort implementation for N = 8

### 5.2 Caching

The spl!0 and spl!1 edges from figure 5.1 quickly become too large when N is increased for the edges to be stored in registers. For these edges, BRAM would be used instead of registers. The mrg node compares the front of the spl!0 and spl!1 edges, so it reads these from the BRAM every cycle. The BRAM in an FPGA are dual port, so it is possible to do one write and one read simultaneously each cycle. And since the spl!0 and spl!1 do not share the same BRAM module, it is possible to read from both edges in the same cycle as well. But when merging two lists, only the smallest value is sent to the output, the larger value will be used next cycle in the front of both lists, it is possible to remove one of the reads. Essentially, this means that each cycle only one value is read from the spl!0 or spl!1 edge, but never both. This is useful later on, when the spl!0 or spl!1 will be combined into one edge / one BRAM.

### 5.3 Memory usage

Using Little's Law, it is possible to determine how many tokens will be in the system as a long-term average. Little's Law is defined as follows[11]:

$L = \lambda W$

- L the average number of tokens in the system.

- $\lambda$  the average number of tokens arriving in the system per cycle.

- W the average processing time / latency per token.

Since the system is a streaming sort,  $\lambda$  will be equal to 1, which means the average number of tokens in the system is equal to the latency. However, another important note is that because the system is a streaming sort, the number of tokens in the system does not change after the startup period. This means that the number of tokens will always be equal to or less than our latency  $(N + 2 \cdot (\log_2(N) - 1))$ . When deriving the current memory usage from the graph (which is equal to the sum of the slack of all the edges), this is equal to  $2N - 2 + 2 \cdot (\log_2(N) - 1)$ . Hence, N - 2 registers are always empty. If these registers could be removed, this would be a reduction of almost a factor of 2.

### 5.3.1 Removing slack

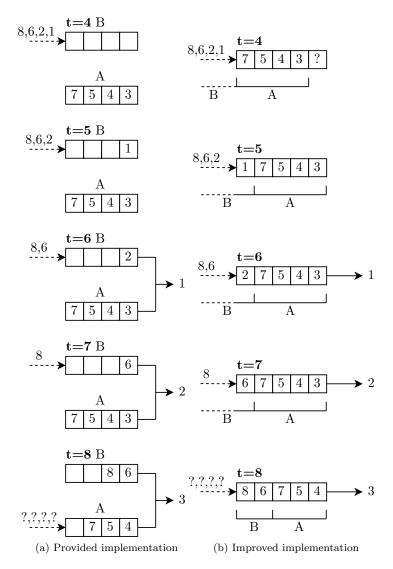

Figure 5.2(a) illustrates the problem in the current design. The spl!0 edge (from figure 5.1) contains list A, and edge spl!1 will contain list B as it arrives. At t = 4, the A list has already fully arrived and has filled up the buffer. The buffer is the slack/capacity of each edge in this case. At t = 5 the first token from the B list arrives at the edge. Now the merger will take the lowest valued token (in this case from the B list) and produce it on the output edge. So, at t = 6, the value 1 is produced and the next value of B arrived. At t = 7, again the B token was produced,

since it had the lowest value. At t = 8, the token in the A list is produced. Observe that now the B edge also contains 2 tokens, but the A edge contains 3 tokens.

After the initialization phase, on average only  $\frac{5}{8}$  of the slack of the mrg node edges is utilized, which can also be seen in figure 5.2(a). Note that neither the slack of the A nor B edges can be reduced. The A edge will always fill up when a new sorted list arrives. And the B edge will be filled in the extreme case when all values of A are lower than all values of B. One of the ways to reduce the memory usage, is first to make the realization that the A and B edges combined use exactly  $\frac{5}{8}$  places of the buffers. More specific n/2 + 1 per merge node. So, what can be done is that the A and B lists can be combined into one buffer. Since this can no longer be stored as slack on edges, the implementation becomes slightly more complicated, but the idea remains the same. Figure 5.2(b) shows how this works. At t = 4, the buffer is still being filled from the initialization phase. At t = 5, the buffer is filled with both the A list and the first value of B. At t = 6, the first value of B was produced on the output and the next value of B was placed in the buffer. At t = 8, the value of A list was removed, since it had the lowest value. Note that B now fills more of the buffer, and the A list fills less of the buffer.

In this implementation, all places in the buffer would always be filled. So, the memory utilization is 100%. The rate and latency remain unchanged from the baseline implementation.

#### 5.3.2 Adding indexing

Another problem arises with the proposed solution, however. The buffer stores two FIFO queues in a shared space. This results in four cases of where tokens are placed and removed, listed below.

- 1. Take head from queue A, store new element at end of A

- 2. Take head from queue A, store new element at end of B

- 3. Take head from queue B, store new element at end of A

- 4. Take head from queue B, store new element at end of B

This prevents the implementation of a single ring buffer, since there are multiple heads and tails. As a result, this would require shifting (of parts) of the buffer, which is not feasible for large buffers and would certainly not be possible to do in a single cycle. If shifting is not allowed, a new element must be stored at the place where an element will be removed. Since, there are no guarantees if this will be (at the tail) in queue A or B, it is required to keep track where elements are stored. This adds a layer of indirection.

Because of the indirection, it is now also required to store these references to the elements, which in turn adds more memory. Zooming in again on a single merge stage, the input is two blocks of length n/2 and the output will be one block of length n. The buffer size will be n/2 + 1 (as shown in 5.3.1). The length of queue A and B will both be n/2 at maximum, so n places are required for the indices in total. The indices require at least  $\lceil \log_2(n/2+1) \rceil$  bits to store the highest index. The maximum block size will always be equal to a power of two, so  $\log_2(n)$  can be used instead, which has the same value when n is a power of two. Thus, the memory usage is increased for each stage with  $n * \log_2(n)$  bits.

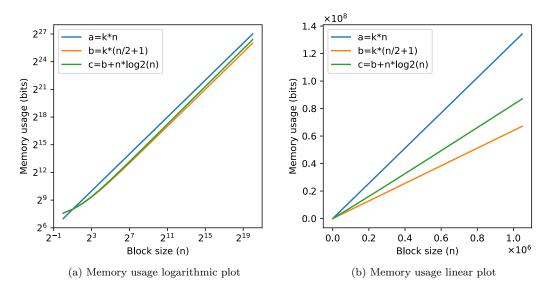

Note that the key-value pair size is also critical to determine if this indirection is beneficial for the memory usage. A larger key-value size will profit more than a small size. If the key-value size is small enough, it will even have the opposite effect and cost more memory to have this layer of indirect. For this research problem, the key-value pair uses 128-bits (64-bit key, 64-bit value), so here it will still be beneficial. Figure 5.3 shows how much memory each approach uses for a key-value size of 128-bits up to  $n = 2^{20}$ . The total memory usage of this solution still grows faster than the baseline solution in relation to n. However, the reference solution would only be worse after around  $n > 2^{85}$ , which will never be a problem (the FPGA used only has  $2^{25}$  bits of memory, which already exceeded at  $n > 2^{21}$ ). With an element size of 32-bits, this referencing solution

Figure 5.2: Memory usage trace for the merge stage n = 8

would only be beneficial up to around  $n = 2^{21}$ , which could have been a problem if such a small element size were used.

Figure 5.3: Memory usage comparison for a single stage with key size, k=128

### 5.4 Variable block sizes

The baseline solution can only sort block sizes of exactly N. Also, N must be a power of two. As stated in the problem description, the sorter should be able to sort any block size as long as the block size is smaller than the designed N. For example, if the sorter is configured for maximum size N, that sorter should be able to sort any block of size (S) as long as  $1 \le S \le N$ .

Consider the case where N = 2 and all blocks have a length of 1. Then it is important to alternate each block over the A and B edges, since if all blocks would enter the A edge, the select node would never fire, as illustrated in figure 5.4. The figure is a flow only view, so the numbers on each edge indicate the number of tokens, not values.

Figure 5.4: Split (spl) node sending all blocks of size 1 to edge A (flow only view)

Instead of sending blocks to a single edge, blocks will be equally distributed over the two edges. But currently there is the issue that blocks cannot be kept apart. For an input stream where the block size for every block is 1, then the output stream should be equal to the input stream (FIFO behaviour). However, if there is a block on edge A and edge B, it cannot be known which block must be selected. The solution used is to add a block number to each block. This way, it is also possible to sort on the 'oldness' of elements. The block number is combined with the value in a tuple, and will look like this: (blocknr., key). Now it is possible to do a lexicographical comparison on the elements, this way older blocks will always be considered to have 'a lower value', thus being output first. Blocks with the same block number will still be sorted by their key.

The current firing finite state machine (FSM) still expects elements of the same block on the A and B edges, which can also no longer be guaranteed with variable block sizes. Just adding the block number is not enough to make this sorter functional. The FSM would require a new design,

or, another approach is to simplify the FSM and add another value to the lexicographical ordering. Let's call this value rank, and insert it between the block number and the key: (blocknr., rank, key).

Each stage of the merge sorter sorts an increasing number of elements. E.g. the first stage sorts a block of two elements. The second stage sorts four elements, the third stage eight elements, etc. Using the rank, these elements are grouped together. So, elements that should be in the same block as a merge stage output will have the same rank. Generating the ranks is done by simply adding the count / index of the element in the block. So, the first element gets a rank of 0, the second element gets a rank of 1, the third element a rank of 2, etc. In each merge stage, the rank is divided by 2 (a simple bit shift), such that the group of each rank get larger at each merge stage as explained above. Table 5.1 shows an example of a small block of N = 4 with the inputs of each stage and the final output. Note that elements with the same block number and rank are always in sorted order.

|        | Stage     | 1          | 2          | Output     |

|--------|-----------|------------|------------|------------|

|        | Element 0 | (0, 0, 79) | (0, 0, 62) | (0, 0, 17) |

| Inputa | Element 1 | (0, 1, 62) | (0, 0, 79) | (0, 0, 62) |

| Inputs | Element 2 | (0, 2, 17) | (0, 1, 17) | (0, 0, 74) |

|        | Element 3 | (0, 3, 74) | (0, 1, 74) | (0, 0, 79) |

Table 5.1: Merge stage input/output data

Having the rank and block number is now also sufficient to ensure that the A and B edges shall always be filled. The elements in the same block can be alternated between the A and B edges by checking if the rank is odd or even (the last bit). However, for a stream of blocks with a length of one, all elements would still be sent to the same edge, so the same can be done with the block number. The blocks are alternated over the A and B edges by checking the oddness of the blocknumber. This is combined with the rank check by a simple XOR. Figure 5.5 shows the implementation of the split node.

```

class Split(Node):

def __init__(self, I=[]):

super(Split, self).__init__(I=I)

pass0 = Rule(I=(1,), O=(1,0)) # Output to edge A

pass1 = Rule(I=(1,), O=(0,1)) # Output to edge B

self.set_fsm([Select([pass0, pass1])])

self.set_fs([lambda x: (x[0] & 1) ^ (x[1] & 1)]) # pass0 if 0, pass1 if 1

self.set_fo([lambda x: (x[0],x[1]//2,x[2]), lambda x: (x[0],x[1]//2,x[2])])

```

Figure 5.5: Split (spl) node code

### 5.5 Implementation

All the previous discussed improvements are combined into one implementation. The code for the single-rate sorter is attached as appendix B.

A significant drawback of the block number and rank becomes visible when calculating the overhead. To guarantee uniqueness for the block and rank numbers, both need at least  $\lceil \log_2((N + 1)/2) \rceil = \log_2(N)$  bits (since N is a power of two). Although, the rank does lose a bit after every stage. Adding the block and rank numbers increases the memory requirement for the FPGA when implemented in hardware. For small values of N, the extra memory is not significant, but at  $N = 2^{20}$ , it adds 40 bits to each 128 bit key-value pair, which is an increment of  $\approx 31\%$ . But an even more important concern is how this affects the comparators. The Xilinx VC707 uses DSP slices as a comparator. Only, each DSP slice has a bit-width of 48-bits. Since the key size is

64-bits, this requires at least 2 DSP slices. Meaning, 32-bits are left for the block number and rank. It is important to stay at or below this number when choosing the maximum block size. The maximum block size (N) is limited to  $2^{16}$ , otherwise it would use more DSP slices. This translates to a block size of 1 MB. These overheads become significantly smaller for multi-rate sorting, as will be shown next chapter.

Formula 5.1 can be used as an approximation for the total memory usage of all stages combined for any block size N and key-value pair size k.

$$\sum_{p=2}^{\lceil \log_2(N) \rceil} (k+2*\log_2(N))*(2^{p-1}+9)+2^p*p$$

(5.1)

# Chapter 6

### Multi-rate sorting

Multi-rate sorting will require multiple inputs and outputs to be consumed and produced each cycle. So, for example, a multi-rate sorter of rate four, consumes four inputs and produces four outputs in one cycle. StaccatoLab does not provide a way to consume multiple tokens in one cycle, so instead inputs and outputs will be bundled in one token as a tuple, e.g., (a,b,c,d), where a, b, c and d are all independent key-value pairs. Let us call the sorting rate P. The tuple token width is then equal to P, such a token will also often be called an element. If P > 1 is used in a sorter, this is then considered a parallel sorter.

### 6.1 Sorting networks

A regular merge sort has no way of sorting multiple values in a single cycle. A component must be created that can take in P inputs and produce P outputs in a single cycle to create a multirate sorter. The most common way to do this is utilizing the well-researched sorting networks. Sorting networks are based on one component with two inputs and outputs. The inputs are compared and swapped if necessary such that the outputs are in a non-decreasing order. Using this 'swap' component, it is possible to construct a network with multiple inputs and outputs, such that all outputs are in sorted order. Sorting networks are often illustrated with horizontal and vertical lines. The data from an input follows the horizontal line from left to right and can be swapped with another horizontal line via a vertical line. The vertical line represents such a 'swap' component. Figure 6.1 shows such a large sorting network. If the direction of the 'swap' components are all the same, then the arrowheads are often omitted. There are two important properties of any sorting network. The first is the total number of comparators needed (which is equal to the amount of 'swap' components). The second is the depth of the sorting network. The depth is equal to the maximum number of comparators that can be encountered on any path. There are many variants of the sorting networks. Each variant having a different purpose. For example, minimizing these two factors, total comparator count and depth. Some sorting networks are known to be optimal [5][6]. For example, the minimal depths are known until P = 18 and the minimal size until P = 12. There are many ways to construct larger sorting networks, but these are not optimal. Sorting networks scale poorly, known (practical) implementations often have  $O(n \log^2 n)$  space complexity, which is why P should be minimized if possible.

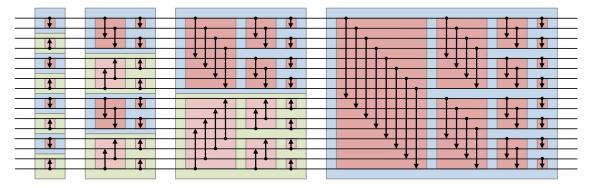

Ken Batcher published two sorting networks in 1968[2]. These are both very commonly used to implement such a network. The first network is the bitonic merge sort. Figure 6.1 shows the implementation of the network for P = 16. The input of each stage (each blue and green block in the figure) is a bitonic sequence. A bitonic sequence is defined as follows.

$$x_0 \leq \ldots \leq x_k \geq \ldots \geq x_{n-1}$$

for some  $k, 0 \leq k \leq n$

In each stage the two previous stages are merged, so it should be obvious that k = n/2 at the input of each stage. However, each stage can actually sort any bitonic sequence for any k[15]. This

is an important fact for the next section. What can already be noticed is that the merger of each stage in the single-rate sorter has two sorted inputs. So, if one of those inputs would be 'flipped', this is a bitonic sequence. Thus, only requiring the very last stage of the bitonic merge sort (for size P). This saves many comparators. Equation 6.1 can be used to calculate the comparators of the last stage of the bitonic sorter (thus requiring a bitonic sequence as input). k is used to denote the degree of the sorting network. A sorting network of degree k has  $2^k$  inputs.

$$\begin{cases} s(1) = 1\\ s(k) = 2s(k-1) + 2^{k-1} \end{cases}$$

(6.1)

This recursive formula can also be simplified to a non-recursive variant, given by equation 6.2 below.

$$s(k) = k * 2^{k-1} \tag{6.2}$$

Observe that the depth of the last stage is simply equal to the degree (k) of the sorting network.

Figure 6.1: Bitonic merge sorter, source: Wikipedia[3]

The other sorting network is Batcher's odd-even merge sort. This method performs well to minimize the comparator count of the sorting network compared to other methods. However, it does not have the same property as the bitonic sort, namely that the last stage can sort a bitonic sequence[15]. So, Batcher's odd-even merge sort has a lower comparator count only if the input is not guaranteed to be a bitonic sequence. A visualization for P = 8 is shown in figure 6.2. It is very similar to the bitonic merge sort. The number of comparators for the last stage is reduced by  $2^{k-1} + 1$  compared to the bitonic merge sort, as shown by equation 6.3.

$$o(k) = k * 2^{k-1} - 2^{k-1} + 1$$

(6.3)

The total number of comparators is then shown in equation 6.4.

$$\begin{cases} h(1) = o(1) = 1\\ h(k) = 2 * h(k-1) + o(k) \end{cases}$$

(6.4)

And this can also be written as the non-recursive variant shown in equation 6.5

$$h(k) = 2^{k-2} * ((k-1) * k + 4) - 1$$

(6.5)

The depth of the output stage is the same as that of the bitonic variant, so for all stages this is equal to equation 6.6. And in the non-recursive variant, equation 6.7.

$$\begin{cases} d(1) = 1\\ d(k) = d(k-1) + k \end{cases}$$

(6.6)

$$d(k) = (k+1) * k/2 \tag{6.7}$$

Figure 6.2: Batcher Odd-Even Mergesort, source: Wikipedia[14]

### 6.2 Parallel sorting

The first idea to create a parallel sorter might be to duplicate the single rate solution P times. Using some kind of parallel merge, these P input streams could be merged. However, there is a problem with this idea. Let's call these sorters  $S_0...S_P$ . Then for example, if all output elements from  $S_0$  are less than the elements of  $S_1...S_P$ , then this would require P elements from  $S_0$  every cycle (until all elements from  $S_0$  are depleted). Thus, the sorters must also have a rate of P, which means the 'single-rate' sorters cannot be used. Also note that the utilization over the long term will be equal to 1/P for each sorter  $S_i$  (and even lower for preceding stages). So, this is not a very efficient design (since it leads to a very low utilization and high resource cost).

Another idea could be to parallelize the merge stages themselves. Currently, for the single-rate sorter, the input stream is split into two inputs at the split node. The merge node then sorts these two input streams. The split node can easily divide the inputs at rate P, so the only thing required to make this work is to find a solution for a merge node that can sort two input streams with a rate of P.

### 6.3 Design

A parallel merge node would have two inputs. Again, let's call these A and B. And let's call the elements  $a_i$  with  $a_0$  being the front of the A input. And do the same for  $b_i$ , with  $b_0$  being the front of the B input. Then since it is a merge sort, we assume that  $\forall_{i,j} [0 \leq i < j < N : a_i \leq a_j \wedge b_i \leq b_j]$ , in other words, the inputs of A and B will already be sorted. The problem to solve for the parallel merge node is that the P lowest value elements should be output. However, these could be all in A or all in B or a combination. This means there are 2 \* P candidates that must be considered for only P outputs. Another factor that must be considered is, what happens with the P elements that were not the lowest?

### 6.3.1 Design 1 (Feedback loop)

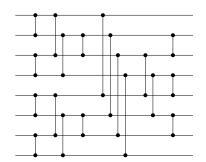

Two papers that implemented the merge sort and solved this problem used some form of a feedback loop[9][16]. One such design is shown in figure 6.3(a). This is a merger with P = 4. However, it can be seen, that a sorting network of size 2 \* P is required. The sorting network is shown in figure 6.3(b). The bitonic half-cleaner isolates the lower half values from the higher values. This is why the bitonic sorters can also be separated from the half-cleaner and the sorting of the smaller halves can be done at a later stage. Note that this is not done in the feedback loop, since there is no register between the half cleaner and the bitonic sorter. There is only one register present, the single blue box after the bitonic sorter, in the feedback loop. So, this could be considered as one edge with a slack of one in StaccatoLab.

There is one important drawback in this design. Since 2 \* P values are sorted each cycle, the *P* highest values must be fed back into the sorter, hence the feedback loop. However, these must be immediately available, since they could contain the lowest values that must be output in the next

Figure 6.3: Terabyte sort merger (where P = 4), from [9]

cycle. For example, consider the following inputs with P = 2: A = [0, 0, 2, 2], B = [1, 1, 3, 3]. In the first cycle the front of A is compared with the front of B, the lowest values will be the output ([0,0]), the highest values ([1,1]) will be fed back into the sorter. The second cycle the [1,1] is expected as the output, so this loop must already be present at the input of the bitonic sorter. Although this is possible (as shown in the existing paper), this creates a critical path that cannot be pipelined. So, this could limit the possible clock rate when implemented in hardware. Also note that this would get worse as P grows.

#### 6.3.2 Design 2 (Min select)

For the second design, the idea was based on the fact that only the P lowest values are required to be sorted each cycle. So, if these P values can be selected from A and B, then there is no need to have such a feedback loop as in the previous design. Actually, selecting the P lowest values is not that difficult. Let us define a new variable k as the number of elements that should be picked from the (front of the) A input. Then, the number of elements picked from the (front of the) B input will be equal to P - k elements, such that we have a total of P elements. This k will be picked in such a way that these elements  $\{a_0..a_k\} \cup \{b_0..b_{P-k}\}$  is the subset containing the smallest values from the A and B inputs. Note that such a k does exist, as shown by the formula below, for which a full proof is provided in Appendix A. In the special cases,  $a_0 \ge b_{P-1}$  and  $b_0 > a_{P-1}$ , k = 0 and k = P can be used respectively.

$$\forall_{i,j} [0 \le i < j < P : a_i \le a_j \land b_i \le b_j] \Longrightarrow$$

$$(\exists_k [1 \le k < P : a_{k-1} < b_{P-k} \land b_{P-k-1} \le a_k] \lor a_0 \ge b_{P-1} \lor b_0 > a_{P-1})$$

Consider the following example, where P = 4, A = [0, 2, 4, 6] and B = [1, 3, 5, 7]. Then k = 2 should be selected such that the minimum set is equal to [0, 2, 1, 3]. Also note that k = 2 satisfies the  $\exists$ -formula, since  $a_1 < b_2 \land b_1 \leq a_2$  is indeed satisfied.

In hardware, this k can be found by testing all combinations, but combining the comparisons will result in exactly P comparisons total. This is because the second comparison in the  $\exists$ -formula is the negation of the first formula for k-1:  $\neg(b_{P-(k-1)-1} \leq a_{k-1}) \equiv b_{p-(k-1)-1} > a_{k-1} \equiv a_{k-1} < b_{P-k}$ .

When the P smallest elements are selected, the values can be arranged in the following sequence  $(a_0..a_k, b_{P-k}..b_0)$ , which is a bitonic sequence. This sequence can then be sorted by a bitonic sorting network as described in chapter 6.1. Note that this design can easily be pipelined, since there is no feedback loop. Figure 6.4 illustrates a simplified version of the design.

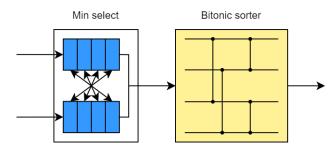

Figure 6.4: Minimum select design for P = 4

### 6.4 Implementation

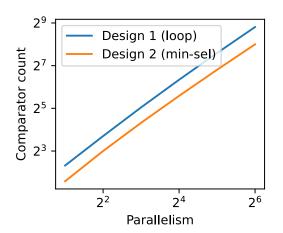

To fairly compare the designs, the comparator count per stage must also be calculated. For design 1, it is assumed that only 1 comparator is needed to make a selection between the A and B queues (this is possible if the multiplexers use the same select signal, which would come from 1 comparator). The total comparator count is then equal to  $1+s(\log_2(2P)) = 1+\log_2(2P)*P$  (using equation 6.2). The comparator count for design 2 is equal to  $P+s(\log_2(P)) = P + \log_2(P)*P/2$ . All practical values for P until P = 64 are shown in figure 6.5 and in table 6.1. Note that any P higher than 64 would probably be unrealistic, since this would create very long (critical) paths.

The maximum depth will be calculated from register to register. For design 1 this is simply  $\log_2(P) + 1$  (on the loop). For design 2, it depends on if there is a register between the minimum selection and bitonic sorter stage. In the final implementation this is the case, so then the maximum depth is equal  $\log_2(P)$  (otherwise it would be the same as that of design 1).

| Р        | 2 |    | 8  |    |     | 64  |

|----------|---|----|----|----|-----|-----|

| Design 1 | 5 | 13 | 33 | 81 | 193 | 449 |

| Design 2 | 3 | 8  | 20 | 48 | 112 |     |

Table 6.1: Table of the comparator count for designs 1 and 2.

Figure 6.5: Logarithmic plot of the comparator count for designs 1 and 2.

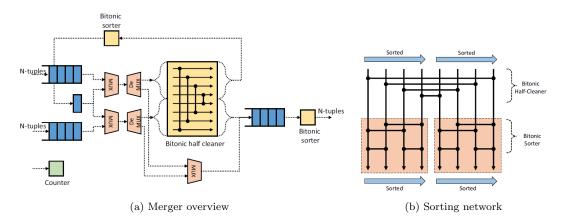

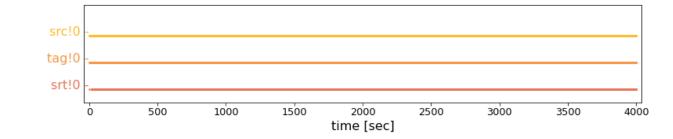

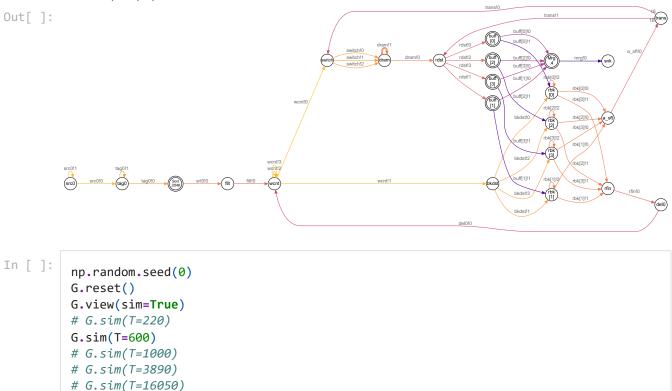

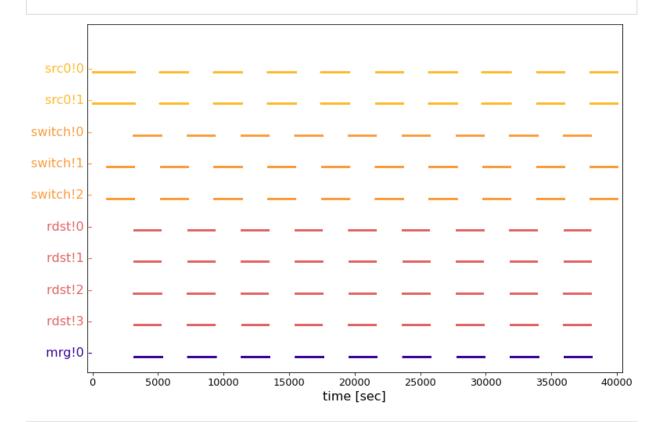

From all the discussed differences between design 1 and 2, it can already be seen that design 2 is better. This is why design 2 was implemented in StaccatoLab and will be compared to the implementation of the Terabyte sort paper as a reference. The sorting is still very similar to the single rate sorting. Figure 6.6 shows the first two stages. The first stage is simply the 'net' node. This is an odd-even merging network to sort the unsorted tuples from the input. A bitonic sorter cannot be used for this, since the input is not a bitonic sequence. Fortunately, this node will only be used once and is always the first stage. The second stage is the 'spl', 'pss' and 'bnet' nodes. The 'spl' node is functionally the same as that of the single rate sorter. It moves the tuples to the correct edge based on the rank and block number. The 'pss' node does the minimum value

selection and outputs a tuple which values form a bitonic sequence. The 'bnet' finally sorts this bitonic sequence (using Batcher's bitonic sorter), such that the output tuple is fully sorted.

Figure 6.6: Multi-rate first two stages

In chapter 5.3.1 it was explained that the memory requirement can be halved by storing the A and B inputs in block memory (on a self loop). For the single rate implementation, it was possible to combine all the required logic in one node. For the multi-rate design, it would also be possible to implement all of this in the 'pss' node. However, this node was already very complex and adding this functionality (also with the references etc.) would make this unmanageable. So instead, this functionality was kept separate. Storing the A and B inputs is now managed by the 'buf' node, which can be seen in figure 6.7. From the 'buf' node, there are two edges to the 'pss' node. These edges represent the A and B inputs and have a small fixed slack. The 'buf' node does not know whether it needs to produce an A or B input for the 'pss' node. So, there is a signal back from the 'pss' node which signals if the last consumption was from the A or B input. Using this signal, the 'buf' knows which input/edge it should refill.

Because of this feedback loop, some latency is present. As a result, the slack of the inputs of the 'pss' node must be sufficiently large such that it always has and A and B input (otherwise the node cannot fire). This extra slack adds a small (fixed) amount of extra memory for each stage. This is the reason that for stages two and three, the 'spl' node is still used (figure 6.6). Stages four and beyond use the 'buf' node.

Figure 6.7: Multi-rate last stages

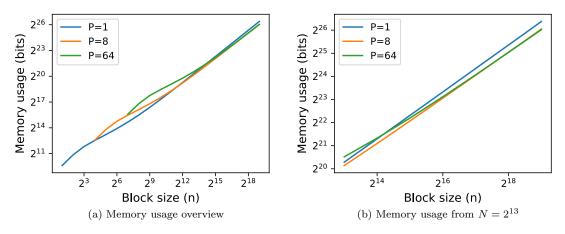

As a final implementation detail, the rank, and block number are attached to the tuple and not for every value in the tuple. This essentially reduces the relative memory overhead of these additional values. Unfortunately, this does constrain the variable block size to be a multiple of P. It is still possible to sort blocks that are not a multiple of P by adding padding values. However, this is not automatically managed by the sorter. The total memory consumption calculation is shown as formula 6.8. The formula has not changed much from the single rate formula, but the element size is now k \* P and there are few stages to sum.

$$\sum_{r=2}^{\lceil \log_2(N/P) \rceil} (P * k + 2 * \log_2(N)) * (2^{r-1} + 9) + 2^r * r$$

(6.8)