## MASTER

Scheduling policy to control interference between tasks in an LED driver Literature study, Design and Implementation

Popa, Stefan

Award date: 2022

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Mathematics and Computer Science Interconnected Resource-aware Intelligent Systems Research Group

# Scheduling policy to control interference between tasks in an LED driver

Literature study, Design and Implementation

Stefan Popa

Supervisors: Geoffrey Nelissen - TU/e Erik de Wilde - Signify

Eindhoven, September, 2022

# Abstract

An LED driver has multiple tasks that need to be executed in parallel. Its core functionality is that of a power supply. To implement that, several control tasks need to be executed at constant intervals. A communication protocol is also run to provide remote control capabilities. The signals for this communication protocol are captured through an interrupt. The communication interrupt is unscheduled and can interfere with control tasks. In this thesis, the current implementation is analysed. Then, three solutions to the problem are proposed. The first one is changing the scheduling algorithm of the system. The second one is using a server to manage the interrupt. The third solution is to limit the preemption of control tasks. The theoretical and practical aspects of the solutions are examined. It is concluded that only limiting the preemption of control tasks is an improvement over the current implementation.

# Contents

| Co            | onten        | nts                                                                                 | $\mathbf{iv}$ |

|---------------|--------------|-------------------------------------------------------------------------------------|---------------|

| $\mathbf{Li}$ | st of        | Figures                                                                             | vii           |

| $\mathbf{Li}$ | st of        | Tables                                                                              | viii          |

| 1             |              | oduction                                                                            | 1             |

|               | 1.1          | Context and Background                                                              | $\frac{1}{2}$ |

|               | 1.2          | Use cases                                                                           | $\frac{2}{2}$ |

|               |              | 1.2.1       Overview                                                                | 2<br>3        |

|               |              | 1.2.2       Differential components         1.2.3       DALI communication protocol | 4             |

|               | 1.3          | LED Driver and Software Components                                                  | 5             |

|               |              | 1.3.1 Controllers and other circuit-related features                                | 6             |

|               |              | 1.3.2 DALI Implementation                                                           | 6             |

|               |              | 1.3.3 EEPROM synchronization                                                        | 7             |

|               | 1.4          | Current Implementation                                                              | 7             |

|               | 1.5          | Problem Description                                                                 | 8             |

|               | 1.6          | Goal and approach of the research                                                   | 9             |

|               | 1.7          | Contributions                                                                       | 9             |

|               | 1.8          | Thesis outline                                                                      | 10            |

| <b>2</b>      | Stat         | te-of-the-Art                                                                       | 11            |

|               | 2.1          | Scheduling algorithms                                                               | 11            |

|               |              | 2.1.1 Rate-monotonic scheduling                                                     | 12            |

|               |              | 2.1.2 Deadline monotonic scheduling                                                 | 12            |

|               |              | 2.1.3 Earliest deadline first                                                       | 13            |

|               | 2.2          | Scheduling sporadic tasks                                                           | 13            |

|               |              | 2.2.1 Fixed priority servers                                                        | 14            |

|               | 0.9          | 2.2.2 Dynamic priority servers                                                      | 15            |

|               | $2.3 \\ 2.4$ | Interrupt analysis                                                                  | 15<br>16      |

|               | $2.4 \\ 2.5$ | Limited Preemption                                                                  | 16            |

|               | 2.0<br>2.6   | Real Time Operating Systems                                                         | 16            |

|               | 2.0          | 2.6.1 Requirements for the real-time operating system                               | 16            |

|               |              | 2.6.2 Options                                                                       | 17            |

|               |              | 2.6.3 Scheduler implementation                                                      | 18            |

| 3             | Syst         | tem Model                                                                           | 19            |

| 9             | 3.1          | Notions and Definitions                                                             | 19            |

|               | 3.2          | Software Modules                                                                    | 20            |

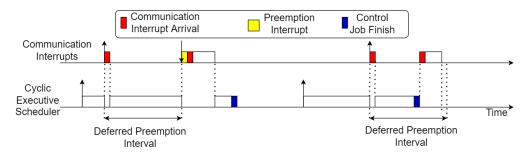

|               | 3.3          | Cyclic Executive Scheduler                                                          | 21            |

|   | <ul><li>3.4</li><li>3.5</li><li>3.6</li><li>3.7</li></ul> | Cooperative scheduler24DALI timing requirements243.5.1 Reception analysis243.5.2 Transmission analysis26Reduced System Model26Summary of the system model27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | The                                                       | coretical analysis 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 4.1                                                       | Initial system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 4.2                                                       | Proposed solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.3                                                       | Deadline-Monotonic Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                                           | 4.3.1 Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                           | 4.3.2 Analysing the overhead of the RTOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.4                                                       | Earliest Deadline First                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                           | 4.4.1 Processor Demand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                           | 4.4.2 Worst case response time analysis $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 4.5                                                       | Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.6                                                       | Limited Preemption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                                                           | 4.6.1 Response time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 4.7                                                       | Conclusions of theoretical analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5 | Ana                                                       | alysis of an RTOS Overhead 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.1                                                       | Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                           | 5.1.1 Context switch with delayUntil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                           | 5.1.2 Semaphores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                           | 5.1.3 Task Notifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6 |                                                           | eRTOS Port 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | $6.1 \\ 6.2$                                              | Functionality selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 0.2                                                       | DTOS coloction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                           | RTOS selection         45           6.2.1         ExcePTOS Setup           46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 63                                                        | 6.2.1 FreeRTOS Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 6.3                                                       | 6.2.1         FreeRTOS Setup         46           Task priority assignment         46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.4                                                       | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | $6.4 \\ 6.5$                                              | 6.2.1FreeRTOS Setup46Task priority assignment46Task design46Initialization sequence47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.4<br>6.5<br>6.6                                         | 6.2.1FreeRTOS Setup46Task priority assignment46Task design46Initialization sequence47Alternative implemenation47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 6.4<br>6.5<br>6.6<br>6.7                                  | 6.2.1 FreeRTOS Setup46Task priority assignment46Task design46Initialization sequence47Alternative implementation47Results48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br>Imp                           | 6.2.1 FreeRTOS Setup46Task priority assignment46Task design46Initialization sequence47Alternative implemenation47Results48proving QoS by Controlling Interference and Response Jitter49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7 | 6.4<br>6.5<br>6.6<br>6.7                                  | 6.2.1 FreeRTOS Setup46Task priority assignment46Task design46Task design46Initialization sequence47Alternative implemenation47Results48proving QoS by Controlling Interference and Response Jitter49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

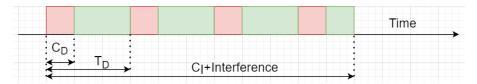

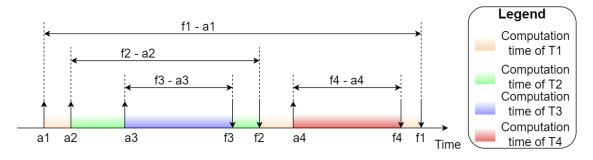

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br>Imp                           | 6.2.1FreeRTOS Setup46Task priority assignment46Task design46Initialization sequence47Alternative implemenation47Results48proving QoS by Controlling Interference and Response Jitter497.1.1Delay types49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br>Imp                           | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50                                                                                                                                                                                                                                                              |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1             | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         7.1.3       Variable Jitter       50                                                                                                                                                                                                                 |

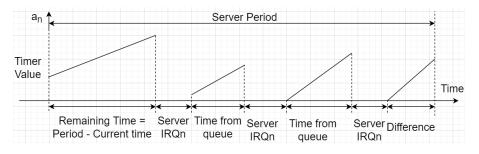

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br>Imp                           | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       52                                                                                                                                                                                                                                      |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1             | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         7.1.3       Variable Jitter       50         Server       52       52         7.2.1       Server Variants       53                                                                                                                                   |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1             | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       50         Server       52         7.2.1       Server Variants       53         7.2.2       Overhead       54                                                                                                                           |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1             | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       50         Server       52         7.2.1       Server Variants       53         7.2.2       Overhead       54         7.2.3       Response time       55                                                                                |

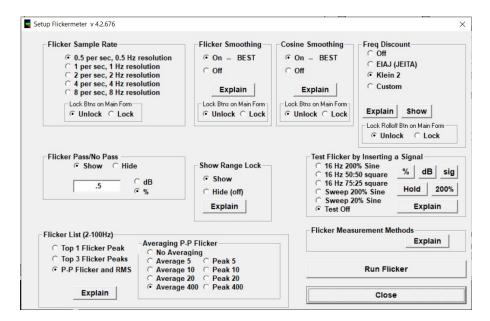

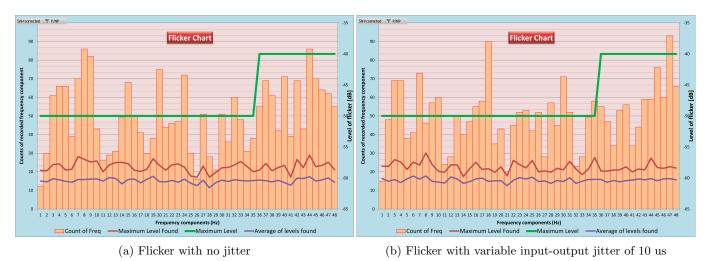

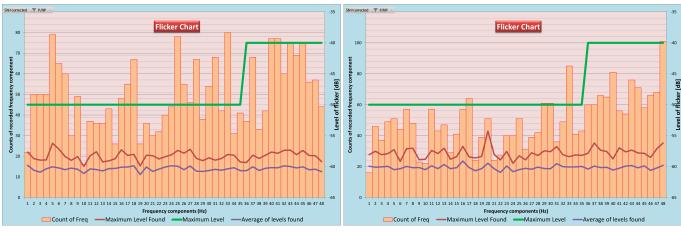

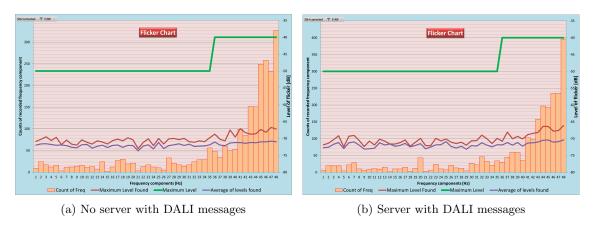

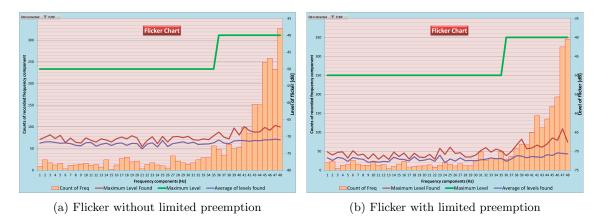

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1<br>7.2      | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       52       52         7.2.1       Server Variants       53         7.2.2       Overhead       54         7.2.3       Response time       55         7.2.4       Light Flicker       56                                                    |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1             | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       50         Server       52         7.2.1       Server Variants       53         7.2.2       Overhead       54         7.2.3       Response time       55         7.2.4       Light Flicker       56         Limited Preemption       57 |

| 7 | 6.4<br>6.5<br>6.6<br>6.7<br><b>Imp</b><br>7.1<br>7.2      | 6.2.1       FreeRTOS Setup       46         Task priority assignment       46         Task design       46         Initialization sequence       47         Alternative implemenation       47         Results       48         proving QoS by Controlling Interference and Response Jitter       49         Jitter interference on controllers       49         7.1.1       Delay types       49         7.1.2       Static Jitter       50         Server       50         Server       52         7.2.1       Server Variants       53         7.2.2       Overhead       54         7.2.3       Response time       55         7.2.4       Light Flicker       56         Limited Preemption       57 |

| 8 | Ref | ection and Conclusion       | 61 |

|---|-----|-----------------------------|----|

|   | 8.1 | Research questions          | 6  |

|   | 8.2 | Investigated Solutions      | 65 |

|   |     | 8.2.1 Scheduling Algorithms | 6  |

|   |     | 8.2.2 Server                | 6  |

|   |     | 8.2.3 Limited Preemption    | 6  |

|   | 8.3 | Future Work                 | 6  |

# List of Figures

| 1.1  | Examples of an LED driver and load                                            | 2  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | UML Component Diagram of the Driver                                           | 3  |

| 1.3  | Use case diagram of the system in which the driver operates                   | 3  |

| 1.4  | Workbench                                                                     | 4  |

| 1.5  | Example of a DALI system[2]                                                   | 5  |

| 1.6  | UML Class diagram of the driver                                               | 5  |

| 1.7  | Generic block diagram of the controllers                                      | 6  |

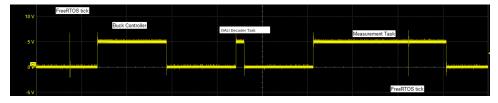

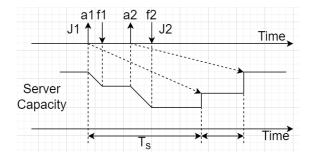

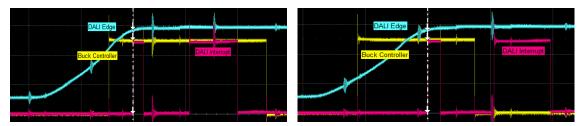

| 1.8  | DALI interrupt interfering with the buck controller after an edge is received | 8  |

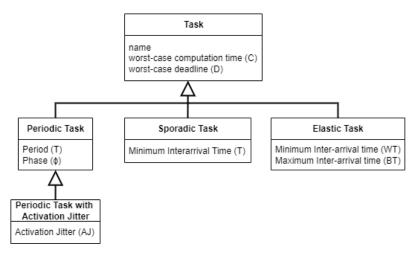

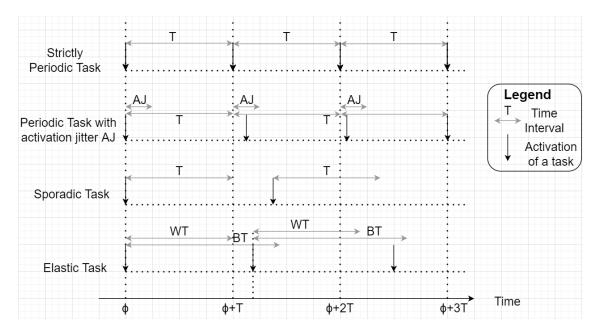

| 3.1  | Task classification and attributes                                            | 19 |

| 3.2  |                                                                               | 20 |

| 3.3  |                                                                               | 23 |

| 3.4  |                                                                               | 25 |

| 3.5  | -                                                                             | 26 |

|      |                                                                               |    |

| 4.1  | 1                                                                             | 29 |

| 4.2  |                                                                               | 33 |

| 4.3  | 1 0                                                                           | 37 |

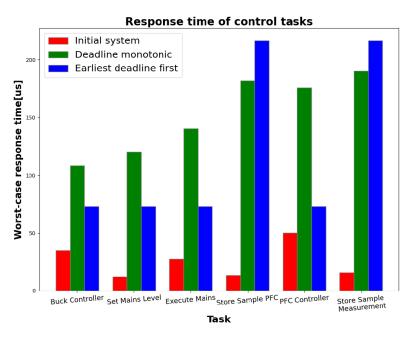

| 4.4  | Worst-case response time for control tasks                                    | 38 |

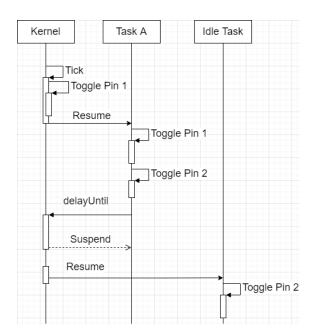

| 5.1  | Experiment 1 with context switch                                              | 40 |

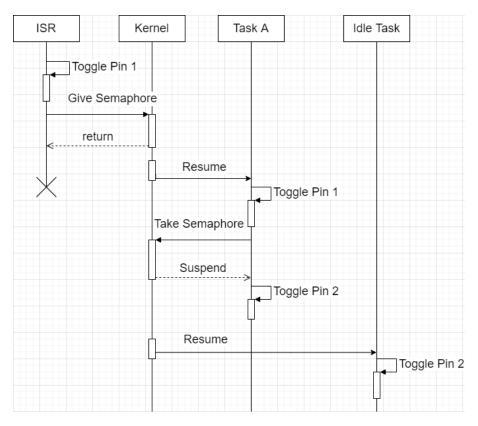

| 5.2  |                                                                               | 42 |

|      |                                                                               |    |

| 6.1  | 1                                                                             | 48 |

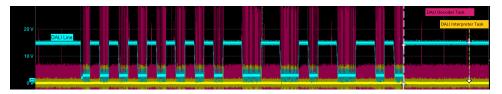

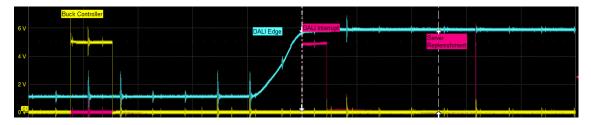

| 6.2  | Reception of a DALI message                                                   | 48 |

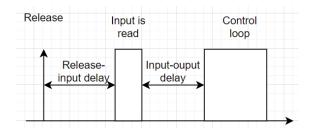

| 7.1  | Potential delays in the control task                                          | 50 |

| 7.2  |                                                                               | 50 |

| 7.3  |                                                                               | 51 |

| 7.4  |                                                                               | 52 |

| 7.5  |                                                                               | 53 |

| 7.6  |                                                                               | 54 |

| 7.7  |                                                                               | 54 |

| 7.8  |                                                                               | 55 |

| 7.9  |                                                                               | 57 |

| 7.10 |                                                                               | 57 |

|      |                                                                               | 58 |

|      |                                                                               | 60 |

|      |                                                                               |    |

# List of Tables

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$                                           | System interrupts7Feature Comparison of XMC 1402 and XMC 44008                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2$                                                                        | Notations Overview11Schedulability tests and maximum dimension of servers[3]14                                                                                                                                                                                          |

| 3.1<br>3.2<br>3.3                                                                   | Tasks executed in the cyclic executive scheduler21Schedule of the cyclic executive scheduler23Reduced System Model26                                                                                                                                                    |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \end{array}$ | Response time formulas for the initial system29Response times for the initial system29Deadline monotonic priority assignment31Deadline monotonic analysed priority assignment31Response times(us)33RTOS overhead34EDF Analysis Results36Response times when using EDF36 |

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\$                                  | Experiments with delayUntil() API40Overhead of delayUntil() API41Experiments with semaphore API41Experiments with semaphores as events42Overhead of semaphore API43Responsiveness of semaphores as events43Overhead of task notifications44                             |

| 6.1                                                                                 | Architecture of RTOS port of the use case                                                                                                                                                                                                                               |

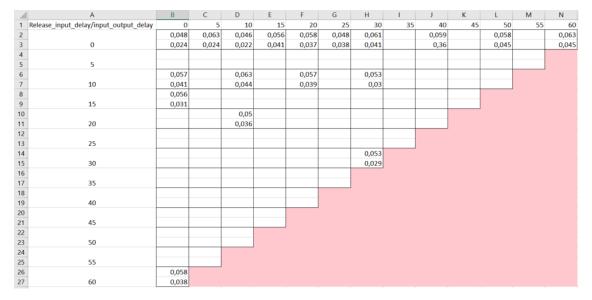

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                                     | Server implementation overhead55Response times with server (us)56Light Flicker Tests of Server56Limited Preemption Overhead (ns)58Response times with limited preemption (us)59                                                                                         |

| 7.6                                                                                 | Light Flicker Tests of Limited Preemption    60                                                                                                                                                                                                                         |

# Listings

| 1.1 | Main Loop                                                               | 7  |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | Cyclic Executive Scheduler workflow                                     | 22 |

| 4.1 | DALI interference computation                                           | 32 |

| 4.2 | Worst-case response time computation                                    | 32 |

| 4.3 | Best-case response time computation                                     | 32 |

| 4.4 | Response Time Analysis Algorithm, taking into account the RTOS overhead | 34 |

| 6.1 | FreeRTOS Generic Task Implementation                                    | 46 |

| 6.2 | FreeRTOS Generic Timer callback function implementation                 | 47 |

# Chapter 1 Introduction

This thesis concerns real-time scheduling policies for a real-time system. Real-time systems are computing systems that aim to create a response to events within a predictable window of time. The predictability of real-time systems is critical to their operation, ensuring that the system functions correctly. Real-time systems are often found at the border between the cyber and physical world, enabling the control of physical processes while being able to interact with the digital world. They are usually implemented with an embedded microcontroller, and their applicability ranges from small consumer electronics to safety-critical systems such as aeronautics and medical devices.

The functionality of a real-time system is often realised by several tasks. These tasks must be executed in conformance with timing requirements, which may differ for each task. One simple but common way to classify tasks is based on their deadlines. There are hard and soft real-time tasks. Hard real-time tasks' deadlines need to be met to ensure the functionality of the system. On the other hand, soft real-time tasks have deadlines that do not need to be met, but if they are missed, it affects the quality of service(QoS) of the system proportionally to the time passed after the deadline. Moreover, some tasks do not have a clear deadline, with their execution constraints coming from their purpose. To ensure the correct behaviour of the system, hard real-time tasks have their QoS maximised. Another way of classifying real-time tasks is based on their arrival patterns. Some tasks arrive periodically, while others arrive sporadically. The main focus of this thesis is to explore existing scheduling algorithms and implement an adequate solution to schedule the tasks of a lighting driver used in smart LED lighting devices.

In this chapter, the context and background for the thesis are presented, and we introduce the problem that is addressed in this thesis. Then the research goal and approach are presented, together with the main contributions of this thesis.

# 1.1 Context and Background

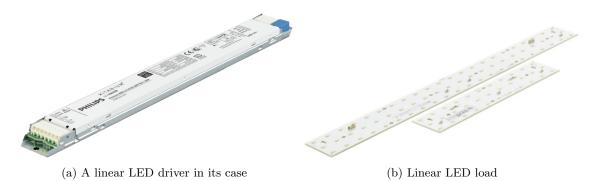

The project is done at the LED Electronics department of Signify, whose aim is to design and develop LED drivers. This is part of the technological development around light. Light is an essential part of the natural environment, which makes it an integral part of many applications. In the last decades, the advent of the light-emitting diode (LED) enabled more efficient and versatile lighting applications. A central device in many such applications is the driver. Such a driver can be seen in Figure 1.1a. The main function of the driver is to supply electrical power to the LED load. One example of such an LED load can be seen in Figure 1.1b. The load displayed in the figure is called linear due to the shape the LEDs are arranged in. The driver has to ensure that the electric current that goes to the load is stable and at the desired level, to create a qualitative lighting experience. On top of this functionality, the driver may communicate with a local area controller, which is a device that can be used by humans to configure and send commands to the

driver, and optionally receives input from a sensor and other devices, increasing the possible use cases of LED systems.

Figure 1.1: Examples of an LED driver and load

In recent years, improvements in the areas of embedded computers, actuators and more accurate sensors shaped the technology used for a lighting driver. The driver was initially an analog power supply with no additional features, such as controlling the driver remotely or determining the remaining lifetime of the device. Adding them increased the usability and marketability of the driver. To implement them, a microcontroller was added to the driver. The addition of the microcontroller to the driver made possible a digital implementation of the power converters, ensuring the stable output of power. All functionality is structured in software modules, which are further structured in tasks. Two particular kinds of tasks are control and communication tasks. Control tasks are periodic tasks without a precise deadline but whose functionality depends on executing them as fast as possible. On the other hand, communication tasks have a precise deadline dictated by the protocol they implement, and if they do not meet their deadline, the protocol will not be satisfied. This thesis will study different scheduling algorithms that can be used to accommodate the timing requirements of these two types of tasks. While the problem, solution and approach are meant to be general, a particular use case will be employed to illustrate the concepts better and allow practical validation.

## 1.2 Use cases

#### 1.2.1 Overview

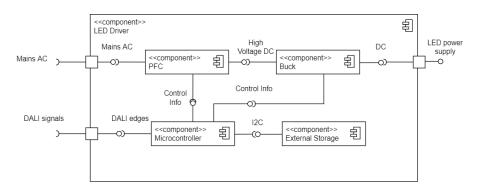

The system considered in this thesis consists of a lighting system with one LED load. The system can be controlled remotely. It contains a light emitter(i.e., the LED load), its driver, a local area controller and a power supply. The components of the driver, as well as the interactions between them, are captured in a component diagram. The diagram is shown in Figure 1.2.

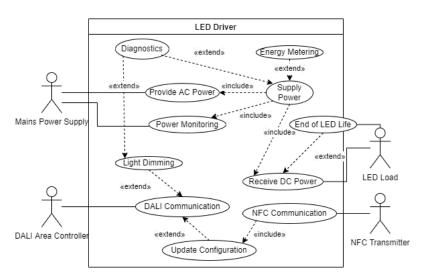

The possible interactions of the driver with the actors around it are shown in Figure 1.3. The first actor included in the system is the local area controller. Its purpose is to specify the characteristics of the light being emitted, such as dimming level or warmth. The controller passes its commands to the LED driver using DALI, which will be described in more detail in subsection 1.2.3. Apart from that, the driver can be configured through near-field communication(NFC), which is incorporated into the external storage. On the electrical input and output, the driver is supplied by mains with alternative current (AC), which is then converted to direct current (DC) to supply the LEDs.

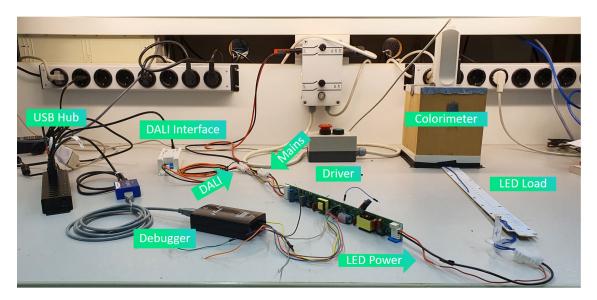

A picture of the components of the system, as they are laid out on the workbench, can be seen in Figure 1.4. A USB hub connecting the computer to various components can be seen on the left. The computer uses an interface to the DALI protocol. The LED load can be seen on the right. In the middle, there is the LED driver that is used. It has three wired connections to the mains

Figure 1.2: UML Component Diagram of the Driver

Figure 1.3: Use case diagram of the system in which the driver operates

power supply, the communication line, and the LED load. In the upper right corner, a colorimeter can be seen. It is used to measure light flicker.

#### **1.2.2** Electrical Components

The main purpose of the driver is to supply power to the light emitters, being an AC-DC power supply. The electronic components decrease the power factor of the driver, leading to increased power consumption and even fines from the electricity supplier. The power factor of a device can be increased by a power factor corrector (PFC).

AC power is composed of a voltage and current wave, which are not necessarily in phase. The difference between the phases of the two waves creates a difference between the apparent power consumed by the device, which is the power the device draws from the mains, and the real power, which is the power that is used by the device. The power factor is the ratio between the real and apparent power, having values between -1 and 1. Having a poor power factor can be penalised by the electricity supplier through extra costs, so it is not desirable.

The circuits of the driver decrease the power factor because they contain inductors and capacitors that shift the current and voltage waves, decreasing the real power used by the driver. To increase the power factor of the driver, a correction needs to be applied, and the circuit that realises it is called power factor corrector (PFC). The PFC contains a transistor that is switched on and off to achieve the correction. However, while the PFC increases the power factor, its circuit creates DC electricity that has a very high voltage. To bring the voltage down to the levels accep-

Figure 1.4: Workbench

ted by the light emitter, a buck converter circuit is used. Both the PFC and the buck converter employ transistors to control their behaviour. Their transistors are switched on and off based on a duty cycle determined by a controller, ensuring the output level of each circuit corresponds to the desired one. Both the PFC and the buck converter have a dedicated controller.

The driver contains an ARM M0 microcontroller that executes the controllers of the PFC and buck converter. The microcontroller also implements the DALI communication protocol, which allows the driver to communicate with a local area controller that plays the role of a master of a set of light emitters. Moreover, the driver has an external memory module, which communicates with the microcontroller using the I2C protocol. The memory module is used to store configuration and diagnostics data in a non-volatile form. Other features provided by the driver are monitoring of the mains, energy metering, diagnostics, and estimation of the end-of-life (EOL) of the LED load.

The emitters that produce light are light-emitting diodes (LEDs). The load controlled by the driver consists of multiple LEDs connected in parallel or series.

#### **1.2.3 DALI communication protocol**

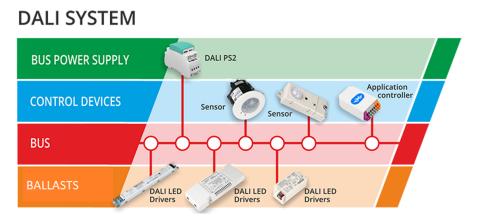

Digital Addressable Lighting Interface [1] (DALI) is a standardised wired communication protocol dedicated to digital lighting control. The DALI protocol adheres to the master-slave design pattern. There are three types of devices: control devices, input devices, and control gears. Control devices play the role of masters, being application controllers. Input devices consist of sensors detecting the state of the environment. They can be queried by the control device. Control gears consist of lighting actuators, usually the driver of the lighting device. The control devices and the control gear are connected through a wired bus. An example of such a DALI system can be seen in Figure 1.5.

At the physical layer, connections are realised through a two-wire bus. The protocol is a digital one, using logic high and low signals across the wires. The nominal voltage of the bus is 16V, with the logic high represented by a voltage level between 9.5 and 22.5V. The logic low is represented by a voltage below 6.5V. The rise and fall time of an edge is capped at 15 us. The bus can also act as a power supply for the sensors connected to the network.

At the data link layer, messages are marked by start and stop framing. At the networking layer, a DALI network can have 64 short addresses, which may be used by either slaves or masters. Slaves can be logically grouped, and there can be up to 16 groups. Masters are able to send 16-bit

Figure 1.5: Example of a DALI system[2]

forward frames to control gear and 24-bit frames to input devices, and they receive 8-bit backward frames as a reply.

DALI also allows the definition of scenes, in which every device has a particular setting to create a lighting scene in the room they are deployed. Information about group membership and scene-setting is stored locally in each slave. Slaves can be addressed in three modes: individually, through their group or all at once through a broadcast. There are three types of commands that can be issued by masters: instructions, configuration and queries.

# **1.3 LED Driver and Software Components**

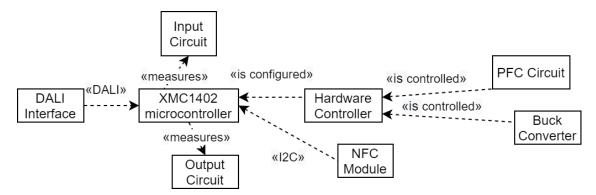

The elements on the LED driver employed in the use case can be seen in Figure 1.6. The driver converts the AC supplied by the mains to the DC required by the LED load. Its circuits are split into four parts. The input circuit converts the current from AC to DC. The second part is the PFC circuit, which corrects the poor power factor introduced by the driver. The third part is a buck converter that lowers the voltage to the level that is required by the LEDs. This is done both to bring the voltage to the normal functioning parameters of the LED load as well as to implement light dimming to the desired level. The fourth part is the output circuit that passes current to the LEDs. The computation power is given by an XMC1402 microcontroller mounted on the driver.

Figure 1.6: UML Class diagram of the driver

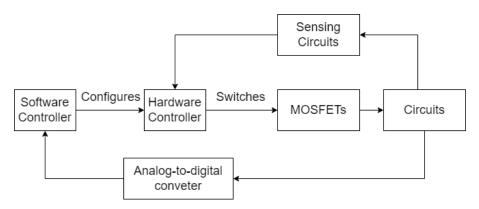

#### 1.3.1 Controllers and other circuit-related features

The PFC and buck converter are controlled digitally. A general block diagram for the controllers can be seen in Figure 1.7. Their controllers consist of two parts. The first one is a cycle-by-cycle controller implemented by configurable hardware, switching the transistors with high frequency. This controller reacts to current fluctuations in the circuit. The second controller is a feedback controller implemented by software. The feedback is received from the bus voltage, measured at different points in the circuit for the PFC and the buck converter controllers. The bus voltage is measured by an analog to digital converter. The output of the software controller is a pulse width modulation(PWM) signal that configures the hardware controllers. The PWM signal is generated by capture and control units(CCU), which are part of the industrial control peripherals of the microcontroller. The software controllers must be executed at a fixed frequency for the quality of the light to be at an acceptable level.

Figure 1.7: Generic block diagram of the controllers

As already said, other features implemented on the controller are mains monitoring, energy metering, diagnostics, and estimation of the EOL of the LED load. Mains monitoring serves two purposes. Firstly, the driver detects whether the power source is AC or DC, together with the frequency of AC. This makes the driver capable of using both AC and DC from the power supply, adapting the behaviour of the PFC controller accordingly. Secondly, the driver stores its configuration parameters in non-volatile memory when the power supply is stopped. To do this, it uses a narrow window of time between the moment the stop is detected and when the power actually stops. Energy metering is used to measure the energy efficiency of the driver. The diagnostics feature enables the driver to auto-detect malfunctions. Estimation of the EOL of the LED load facilitates timely replacement and continuous service for the load. These features have hard real-time requirements because their functionality relies on storing parameters of the current of the circuit at a fixed frequency. Another reason for measurements at fixed intervals is that they are not done by sampling the analog lines directly but rather by reading sampled values from dedicated registers, which are overwritten each time a new value is taken.

#### 1.3.2 DALI Implementation

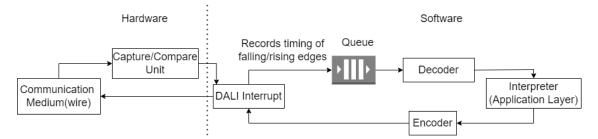

The DALI protocol is implemented on several layers. The hardware support is provided by the CCU. When receiving, the CCU captures the timestamps of rising and falling edges, and when transmitting, it times the interval between outgoing edges. The CCU communicates with the microcontroller through interrupts, which happen when either two edges are detected on the wire that connects the master to the slave or when a new edge is sent from the slave to the master.

The generated interrupt stores received edges in a queue or sets the line to the corresponding value when transmitting. The edges are picked up by a decoder, which assembles the DALI message and makes it available for an application layer interpreter, that reacts accordingly.

#### 1.3.3 EEPROM synchronization

As mentioned in section 1.2, the driver uses an external memory EEPROM module. This is used to store non-volatile data. As the EEPROM module is external to the microcontroller of the board, reading and writing to it create a large latency. To ameliorate this, the microcontroller keeps a cache of the EEPROM in the flash memory. The content of the two is synchronised when the number of write modifications in the cache passes a threshold. Moreover, the EEPROM module can also be accessed through NFC, and when that happens, the cache needs to be synchronised. The microcontroller uses an interrupt to signal when the EEPROM has been accessed through NFC. The I2C protocol is used to communicate with the external EEPROM. The protocol is handled by the Universal Serial Interface Channel (USIC), which decreases processing time.

# **1.4** Current Implementation

The current firmware of the driver assigns tasks to two different schedulers. The first scheduler runs inside the process context. That scheduler is implemented as the main loop of the program. It schedules tasks that do not have hard real-time requirements. The scheduler is cooperative and non-preemptive, iterating through all events and executing the triggered events until completion. This logic can be seen in Listing 1.1. It supports both sporadic and periodic tasks. The tasks' period is maintained by software timers, which are updated with a frequency of 1 kHz.

```

for (;;) {

update_system_time();

for each event e {

if (e is triggered) {

execute_associated_callback();

}

}

}

```

#### Listing 1.1: Main Loop

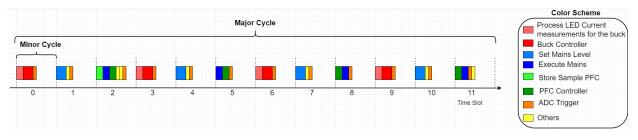

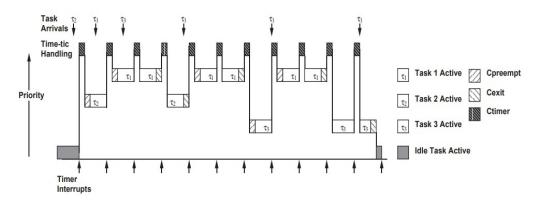

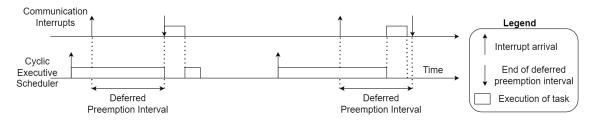

Tasks which have hard real-time constraints are executed by a cyclic executive scheduler divided into twelve time slots. Tasks handled by this scheduler correspond to features related to circuit control and measurement. A timer is used to call the scheduler at a frequency of 12 kHz at the beginning of each time slot. The assignment of tasks to time slots determines the frequency at which they are executed. Since the high-frequency scheduler functions off an interrupt, and the low-frequency one is executed in process context, the former can interrupt the latter and thus ensures that its tasks are executed on time.

There are four interrupts used in the system, seen in Table 1.1. As seen from the priority assignment, the DALI protocol interrupt has a higher priority than the cyclic executive scheduler and can interfere with it. This is because DALI does not have any error correction mechanism, and therefore misses are not allowed. The interrupt is triggered when the driver is receiving a message, and it detects an edge on the DALI line or when the timer triggers when transmitting.

| Function                   | Priority (0=highest) | Frequency        |

|----------------------------|----------------------|------------------|

| DALI Protocol              | 0                    | Sporadic         |

| Cyclic Executive Scheduler | 1                    | $12\mathrm{kHz}$ |

| Cooperative Scheduler      | 3                    | $1\mathrm{kHz}$  |

| NFC Busy                   | 3                    | Sporadic         |

| Table 1.1 | 1: | System | interrupts |

|-----------|----|--------|------------|

|-----------|----|--------|------------|

Infineon XMC1000/4400 microcontroller The driver has an embedded microprocessor to handle communication and control the circuits that regulate the power it outputs to the LEDs. The current design uses an Infineon XMC1402 microcontroller, which contains an ARM Cortex-M0

processor. However, in future iterations, a move towards an XMC4400 with an Arm Cortex-M4 processor is considered. This would make more space and processing power available on the platform, as seen in Table 1.2. The increase in capacity opens the door to future features that will complement the existing ones, and this is part of the trend described in section 1.1. One disadvantage is that the new processor lacks some of the peripherals that the old one has, but that would be solved with other models that also use a Cortex-M4 core. One example of such a lacking peripheral is the LED brightness & color control module, which handles LED color and brightness transitions. Therefore the XMC4400 will also be considered throughout the thesis to compare the performance of the solution on two platforms as well as to create a solid base for future iterations of the product.

| Feature | Processor      | Processor Speed   | RAM             | Flash            | Peripherals clock |

|---------|----------------|-------------------|-----------------|------------------|-------------------|

| XMC1402 | Arm Cortex M0  | 48 MHz            | $16\mathrm{kB}$ | $64\mathrm{kB}$  | 96 MHz            |

| XMC4400 | Arm Cortex M4F | $120\mathrm{MHz}$ | $80\mathrm{kB}$ | $512\mathrm{kB}$ | 120 MHz           |

| Table 1.2: I | Feature | Comparison | of XMC | 1402 | and | XMC 44 | 100 |

|--------------|---------|------------|--------|------|-----|--------|-----|

|--------------|---------|------------|--------|------|-----|--------|-----|

# 1.5 **Problem Description**

Multiple software tasks need to run simultaneously on the same processor: the control software, DALI and I2C communication. The controllers are crucial in ensuring that the emitted light meets the quality standards. At the same time, the DALI communication needs to be handled within the time constraints of the protocol. Otherwise, the device would not be compatible with other devices on the market and would not receive a certification. These conflicting requirements make scheduling tasks difficult.

The difference between the DALI and I2C protocols is that I2C has the advantage of having direct memory access and hardware decoders. The reception and transmission of messages at the physical layer are performed by hardware. This leaves only the application layer to the processor. As the application layer does not have strict timing requirements, it can be executed in the background as part of the cooperative scheduler. On the other hand, DALI is a domain-specific communication protocol. Because its use is not widespread, it does not benefit from hardware support. Thus, DALI messages need to be received and decoded by the microcontroller. The part with the strictest timing requirement is the reception and transmission of signals on the communication medium, i.e. on the wire.

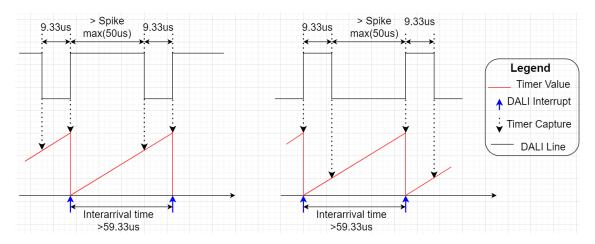

The timing requirements of the physical layer of the DALI interrupt are different between the case when the driver is transmitting and when it is receiving messages. When receiving, the timing of incoming signals is recorded by the CCU. The DALI interrupt must read the registers of the CCU and store the recorded timing before other signals come. If other signals come before that happens, they will overwrite the registers. The timing requirements are more relaxed when the driver is transmitting messages, as it controls the timing of the signals. It must nevertheless meet the requirements of the DALI protocol.

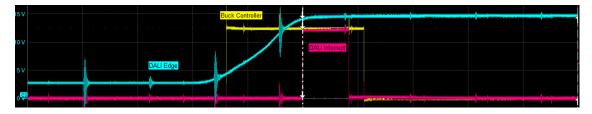

Thus the microcontroller must handle a task with strict timing requirements. To do that, it uses an interrupt. The interrupt has the highest priority in the system. When it triggers, it

Figure 1.8: DALI interrupt interfering with the buck controller after an edge is received

interferes with control tasks from the cyclic executive. This interference can be seen in Figure 1.8. Moreover, the interrupt is sporadic and unscheduled, and there is no protection for the execution of the control tasks. Thus, it interferes with them, creating spikes in the output current, and decreasing the lighting quality. The expectation is that a more flexible and robust solution would enable the two types of tasks to execute with limited interference.

# **1.6** Goal and approach of the research

Given the challenges laid out in section 1.5, the goal is to introduce a new scheduling policy for the tasks that are executed on the driver such that the interference between the communication protocol and the control tasks is controlled, taking into account the real-time attributes and requirements of both task category.

This involves choosing or designing an algorithm which guarantees that the functional and QoS requirements of the lighting application and of the communication protocol are met. Moreover, the interference between tasks needs to be controlled. The algorithm will be theoretically analysed to guarantee this. Then, a practical implementation will be created to test the theoretical results.

The research question that stems from the problem description is, therefore:

How can a real-time scheduling policy be applied to a subset of tasks executed on an LED driver, such that all tasks meet their deadlines, and the interference between communication-related tasks and control-related tasks is controlled?

Specifically, for the specific use case considered in this project, we must control the interference between tasks such that the flickering of the light is below a predefined threshold, the hard realtime timing requirements of the DALI communication protocol are respected, and the response time of the control tasks is minimised. The above research question sprawls other questions related to the steps that must be taken to answer the main question, reflecting the approach that will be used.

- 1. How can the system's tasks be modelled, and what properties and requirements can be derived from the model?

- 2. Which scheduling policy may produce a schedule for the tasks running on the LED driver, such that all tasks meet their deadlines?

- 3. What techniques can be used to control the interference between control and communicationrelated tasks?

- 4. How can the policy producing a valid schedule with the least amount of interference be implemented on the targeted specific platform?

- 5. How does the produced implementation compare with an existing implementation in terms of interference and response time?

# 1.7 Contributions

The contributions of this thesis reflect the research questions and can be summarised as follows:

- 1. A study and review of the state-of-the-art real-time scheduling algorithms for a single-core real-time platform

- 2. A scheduling policy for an LED driver, together with a theoretical analysis

- 3. A technique for controlling the interference between the communication and control-related tasks

- 4. A proof-of-concept implementation of the proposed algorithm on the targeted hardware to assess its performance and industrial applicability.

- 5. An evaluation of the proof-of-concept implementation

# 1.8 Thesis outline

The remaining chapters of this thesis are organised in the following way. Chapter 2 provides an overview of the state-of-the-art algorithms for real-time scheduling on single-sore platforms. Chapter 3 describes how the driver system can be modelled. Chapter 4 presents three different theoretical solutions together with their analysis. Chapter 5 shows how an RTOS can be evaluated for the given use case. Chapter 6 presents how a subset of the system can be ported to FreeRTOS. Chapter 7 presents different implementations of solutions that directly control the DALI interrupt. Chapter 8 contains conclusions and reflections.

# Chapter 2

# State-of-the-Art

This chapter will present a survey of the relevant literature and technologies related to the topic. It is presented in two parts. The first part covers literature about different scheduling algorithms and techniques. The second part presents different operating systems available on the market, which may be used as a platform for implementing the algorithms.

# 2.1 Scheduling algorithms

The kind of tasks and constraints that the scheduling algorithm needs to accommodate are laid out in section 3.7. There are periodic hard-real time tasks without a well-defined deadline, but with QoS inverse proportional to the jitter and interference experienced, and sporadic tasks with hard deadlines. Thus the system needs to deal with a mixed task set. This section will present different algorithms that can be used to schedule periodic hard-real time task sets on a uniprocessor platform. They provide guarantees that the tasks meet their deadlines, together with various techniques to study their jitter.

Of the few algorithms designed to schedule periodic tasks, the simplest one is the cyclic executive. It involves having the processor time divided into time slots, each executing tasks in a sequence that repeats itself. This is the method currently used on the LED driver. Its simplicity makes it highly analysable and easy to use. However, there are some drawbacks of this method, outlined in [3], which appear under certain conditions. The first one is poor management of overhead situations, in which a task exceeds its execution budget and may overrun the next timeslot. The second one is its sensitivity to changes. When a task is redesigned and requires more computation time or a higher frequency, a new scheduler needs to be computed and analysed. Another problem is that aperiodic tasks are hard to integrate into the schedule.

Before presenting other algorithms, an overview of notations is needed to establish common ground, as many papers define their own different notations. Table 2.1 summarizes the notations used in this section. Another useful notion is the concept of a necessary and sufficient condition for the schedulability of a task set under a given algorithm. If a task set is schedulable by the algorithm, it is implied that it meets the necessary condition. On the other hand, if a task meets a sufficient condition, the task set is schedulable.

| Table | 2.1: | Notations | Overview |

|-------|------|-----------|----------|

|       |      |           |          |

| Notation                                         | Explanation                                         |

|--------------------------------------------------|-----------------------------------------------------|

| Г                                                | Set of tasks                                        |

| $C_i$ Worst-case execution time of task $\tau_i$ |                                                     |

| $T_i$                                            | Period of task $\tau_i$                             |

| $D_i$                                            | Deadline of task $\tau_i$ , relative to its release |

| $W_i$                                            | Worst-case response time of a task $\tau_i$         |

| Notation                       | Explanation                                                               |  |  |  |

|--------------------------------|---------------------------------------------------------------------------|--|--|--|

| $B_i$                          | Best-case response time of a task $\tau_i$                                |  |  |  |

| $U_i = C_i / T_i$              | Processor utilization factor of task $\tau_i$                             |  |  |  |

| $U = \sum_{i=1}^{n} (C_i/T_i)$ | Total processor utilization for a task set                                |  |  |  |

| IT                             | Least utilization bound of an algorithm - the maximum total utilization   |  |  |  |

| $U_{lub}$                      | for which a task set is schedulable given a certain scheduling algorithm. |  |  |  |

| $U_p$                          | Total utilization of periodic tasks in a task set                         |  |  |  |

| $U_s$                          | Server utilization                                                        |  |  |  |