### MASTER

FPGA-based Advanced Motion Controller Development and Design Automation

Gao, Yidan

Award date: 2022

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Mathematics and Computer Science

# FPGA-based Advanced Motion Controller Development and Design Automation

Master Thesis

Gao Yidan (1352806)

TU/e Supervisor: Dip Goswami ASMPT Supervisors: Kai Wa Yan Dragan Kostić Mark Wijtvliet

version 11

Eindhoven, May 2022

# Abstract

There is a popular trend to implement control systems on field-programmable gate array platforms for optimal hardware resources and fast computing speeds. Norm optimal iterative control is a high-complexity control algorithm which is hard to implement on a resource-constrained FPGA because it involves matrix operations. This project focuses on implementing a norm optimal iterative learning control algorithm on FPGA through programming with MATLAB and aims on providing an improved model with lower cost of lookup tables, flip-flops and digital signal processors.

# Preface

I would like to thank Dip Goswami, my university supervisor, and Kai Wa Yan, my company supervisor, for giving me the opportunity to conduct research in collaboration with Eindhoven University of Technology (TU/e) and ASM Center of Competence. I'd like to thank Kai Wa Yan for his advice and assistance; whenever I asked for it, he always responded quickly, providing me with valuable advice and positive feedback, encouraging me to solve one problem after another throughout this project. I'd like to thank Dip Goswami for providing me with this opportunity to complete my graduation project after I contacted him and for his prompt assistance. I'd like to thank Dragan Kosti for his encouragement and for discussing issues with me, as well as for providing constructive feedback on control systems. I'd like to thank Mark Wijtvliet for his advice on hardware programming as well as his prompt feedback on my work. Finally, I'd like to thank my mother and father for their unwavering support of my study abroad plans, always supporting all my decisions.

# Contents

| Co            | ontents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vii                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{Li}$ | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                                                                                     |

| $\mathbf{Li}$ | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xi                                                                                                                     |

| 1             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                      |

| <b>2</b>      | Problem Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                                                      |

| 3             | Related work         3.1       Computation load reduction of NOILC         3.2       ILC Implementation on FPGA         3.3       Matrix Multiplication         3.3.1       Timing and Power Improvement         3.3.2       Resource Utilization Optimization         3.4       High-Level Synthesis         3.5       FPGA programming by MATLAB Simulink                                                                                                                                                      | <b>5</b><br>5<br>6<br>6<br>7<br>7                                                                                      |

| 4             | Proposed approach         4.1       Preliminary         4.2       Norm-optimal Iterative Learning Control         4.3       NOILC with Classical Method         4.3.1       Definition of Matrix Multiplication         4.3.2       Matrix Multiplication Computation in Parallel         4.3.3       Resource utilization Model         4.4       NOILC with Improved Method         4.4.1       Matrix Multiplication by Column Combination Method         4.4.2       NOILC Implementation by Improved Method | <b>9</b><br>10<br>13<br>13<br>13<br>14<br>16<br>16<br>17<br>19                                                         |

| 5             | Experimental Setup         5.1       Platform         5.2       NOILC with Classical Matrix Multiplication         5.2.1       NOILC Implementation         5.2.2       Number of Samples Reduction         5.2.3       Word Width         5.3       NOILC with Improved Matrix Multiplication         5.4       Matrix Multiplication Utilization Test         5.5       HDL Properties Setting Up                                                                                                              | <ul> <li>23</li> <li>24</li> <li>24</li> <li>24</li> <li>24</li> <li>24</li> <li>26</li> <li>27</li> <li>28</li> </ul> |

| 6  | Per   | formance Evaluation                                                 | <b>31</b> |

|----|-------|---------------------------------------------------------------------|-----------|

|    | 6.1   | NOILC Simulation                                                    | 31        |

|    | 6.2   | Resource Utilization Analysis                                       | 33        |

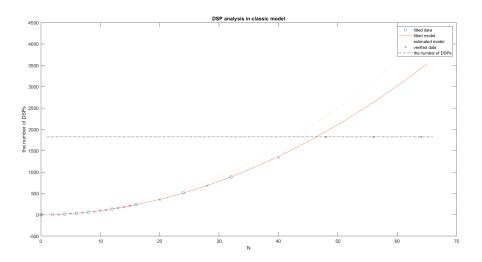

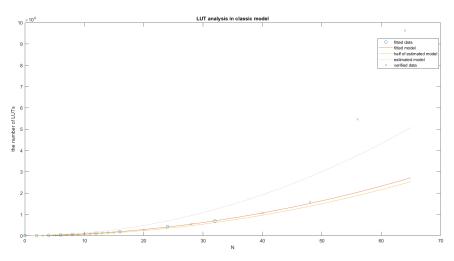

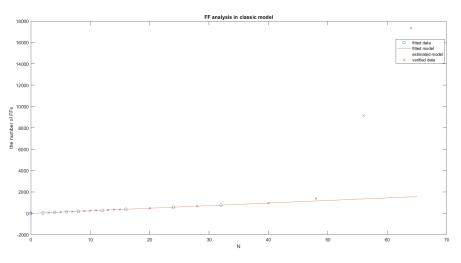

|    |       | 6.2.1 Classical Matrix Multiplication                               |           |

|    |       | 6.2.2 Improved Matrix Multiplication                                |           |

|    |       | 6.2.3 The Comparison of the classical Model with the Improved Model |           |

|    | 6.3   | NOILC implementation on FPGA                                        | 39        |

| 7  | Con   | nclusion                                                            | 43        |

| Bi | bliog | graphy                                                              | 45        |

# List of Figures

| 4.1  | Block diagram of basic feedback control system with a feedforward signal 1       | 10 |

|------|----------------------------------------------------------------------------------|----|

| 4.2  | Block diagram of ILC control [73]                                                | 11 |

| 4.3  | Original ILC working flow                                                        | 12 |

| 4.4  |                                                                                  | 13 |

| 4.5  |                                                                                  | 14 |

| 4.6  |                                                                                  | 14 |

| 4.7  | A terrible design of a deserializer when $N = 4$ , bit-width = 1                 | 15 |

| 4.8  | Right vector-matrix multiplication 1                                             | 17 |

| 4.9  |                                                                                  | 20 |

| 5.1  | The chosen platform: Zedboard                                                    | 23 |

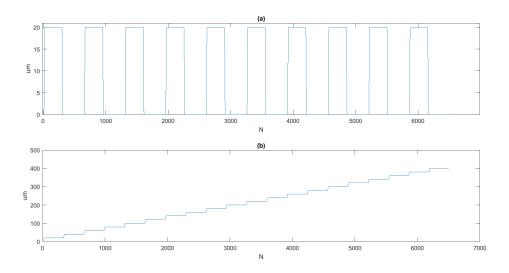

| 5.2  | Two reference position signals with different lengths                            | 25 |

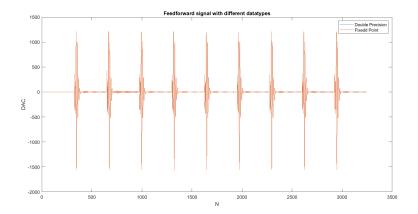

| 5.3  | 0 , , , , , , , , , , , , , , , , , , ,                                          | 26 |

| 5.4  |                                                                                  | 26 |

| 5.5  |                                                                                  | 27 |

| 5.6  |                                                                                  | 28 |

| 5.7  | HDL generation for a <i>Gain</i> block with chosen <i>Adaptive Pipelining</i> 2  | 28 |

| 6.1  |                                                                                  | 31 |

| 6.2  |                                                                                  | 32 |

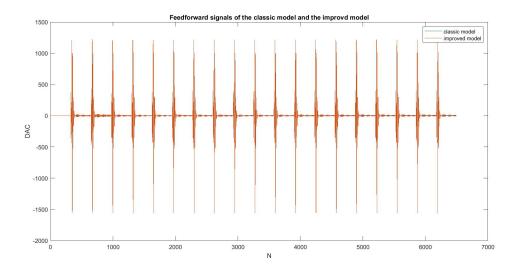

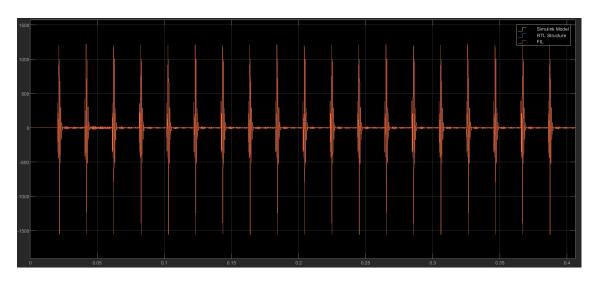

| 6.3  | Feedforward signals of NOILC model with classic matrix multiplication and im-    |    |

|      | 1                                                                                | 33 |

| 6.4  | 1                                                                                | 34 |

| 6.5  | T                                                                                | 34 |

| 6.6  | 1                                                                                | 34 |

| 6.7  |                                                                                  | 36 |

| 6.8  | 1 1                                                                              | 38 |

| 6.9  | 1 1                                                                              | 38 |

| 6.10 | 1 1                                                                              | 38 |

| 6.11 | The testing result of the improved NOILC in the hardware by FPGA-in-the-loop . 4 | 40 |

# List of Tables

| 4.1 | The resource utilization assumption for the classical NOILC implementation | 16         |

|-----|----------------------------------------------------------------------------|------------|

| 4.2 | The resource utilization assumption for the improved NOILC implementation  | 19         |

| 4.3 | Comparison of resource usage of the classical and the improved methods     | 21         |

| 0.1 |                                                                            | <u>م</u> ۲ |

| 6.1 | Resource utilization of classical matrix multiplication                    | 35         |

| 6.2 | Resource utilization of improved matrix multiplication model               | 37         |

# Chapter 1 Introduction

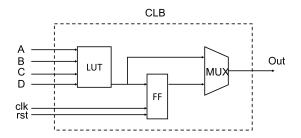

The complexity and performance of field-programmable gate arrays (FPGAs) have been growing exponentially. Due to its high loop rates (tens to hundreds of MHz) and its parallel execution model, the FPGAs are also increasingly being employed as a control system deployment platform [52]. In 2022, the FPGA chips in Kintex UltraScale+ series are equipped with up to 1.2M configurable logic blocks [17], far exceeding the XC2064, the first FPGA product [20]. The FPGAs consist of a series of grid blocks, which can be programmed. The designed circuits on the chips can be modified by designers to programme specific arithmetic operations. Even though CPUs have faster clock rates, FPGAs have higher throughput because FPGAs are designed for single functions that perform parallel calculations, whereas CPUs lack sufficient parallel processing support. Graphics processing units (GPUs) excel at parallel execution, but they are both expensive and power-hungry. Because of the additional delay on the logical block and inner routing, FPGAs, in general, are slower than GPUs. However, Shuichi Asano has shown that when all the processing units are busy with operations, FPGAs are able to perform comparable number of operations per time unit as GPUs [23]. In addition, the FPGAs consume much less power than GPUs when they perform the same function [34]. Application-specific integrated circuits (ASIC) are another option because they outperform GPUs and FPGAs in arithmetic operations. However, they are pricey and cannot be reconfigured like FPGAs. As a result, rather than being used during the design process, ASICs are typically used after the designed processes have been completed. Furthermore, FPGAs typically allow connection to almost any external device, whereas GPUs do not.

The FPGAs are programmed using hardware programming languages, eg, VHDL or Verilog, which require designers to be experienced in hardware programming and knowledgeable in the architecture of logical blocks and memories. Hardware programming languages require not only logical thinking but also basic knowledge of hardware circuits. Furthermore, these languages can handle not only sequential instructions but also concurrent executions. These characteristics make hardware languages more complicated than higher-level programming languages such as C. MAT-LAB allows designers to generate the hardware configurations without deep knowledge of VHDL or Verilog. MATLAB generates the hardware projects and interfaces based on Simulink models. When writing code, designers usually take a long time to debug while automatic code generation would have almost no syntax error but achieve the same function. Furthermore, Simulink provides many models on different levels, from lookup tables (LUTs), the basic logical units in the FPGAs, to User-Defined Functions which could be customized by designers. As a popular and common tool, MATLAB and Simulink are useful to designers, e.g. control engineers, who are often not skilful in hardware programming.

Control systems are widely applied in modern society from electrical devices in daily life to high-speed, high-precision machines in industries. Actuators in control systems are typically expected to maintain a stable state or to accurately meet requirements. A control system is designed to control machines or systems to fulfil requirements [43]. The most popular controller is proportional-integral-derivative (PID) controller, which was first mathematically analysed by Nicolas Minorsky (1922) based on his observation of how helmsmen steer, which is based on the current direction error, the error in the past, and the rate of change of error [58]. Nowadays, actuators which require high precision are mostly controlled by feedback systems, especially in high precision industries. A feedforward signal can be added to reduce error. Feedforward control systems can be designed based on prior knowledge of the control target [59].

Iterative learning control (ILC) is first proposed by Murray Garden in 1967 [42] and it became widely known since 1984. The ILC algorithm generates a feedforward signal to improve control performance [61]. When a system performs the same task repeatedly, it is assumed that the error is also repetitive. ILC is able to trace this error and reduce it to smaller errors after some iterations. Thus, for a repetitive input, ILC helps systems to achieve higher accuracy and reduce settling time. Gunnarsson and Norrlöf minimizes the ILC algorithm in 2001, where the input does not have to be repetitive, allowing a small variation for motion tasks [45], Jin (2018) provided a novel ILC algorithm permitting iteratively varied input and random initial position [50]. Normoptimal iterative learning control (NOILC) is one extension of ILC algorithms which optimizes the 2-norm of error [63]. It consists of two filters represented as two-dimensional matrices whose sizes are dependent on the number of data samples in each iteration [75]. These two filters are also designed by adjusting three weighting matrices to achieve different targets [27][72]. The output feedforward signal calculation for the next iteration is based on filtering the error signal and the previous feedforward signal.

Including ILC, there exist many control algorithms that use matrix operations in their calculation such as quadratic dynamic matrix control [65], dynamic matrix control [35], linear quadratic regulator control [41], and multiple-input-multiple-out PID control algorithms. Because matrices operations are frequently of high complexity, these control algorithms with matrix operations frequently encounter resource issues while implemented on the FPGA platforms. As a result, they are usually implemented on computers with a lot of memory, however, the real-time ability of a control system may lose by CPU implementation. Due to the time limitation, even though there exist other similar algorithms, in this project only NOILC is implemented.

The main purpose of this project is to implement the ILC algorithm on an FPGA. Besides the implementation, the resource utilization for the ILC model is reduced, allowing a system with a large number of samples to be implemented on the chosen FPGA and the resource utilization is predicted before the final implementation by a proposed model.

# Chapter 2

# **Problem Statement**

Because of the high computational complexity of the matrix multiplication in NOILC algorithm, when the scalar of an NOILC is larger, like sampled for more than hundreds of or even thousands of times for one tried signal, the implementation of NOILC requires huge resources including memory and logic units. However, FPGAs are usually not designed with huge resources. There do exist FPGAs with a large number of resources but they are typically more expensive. Thus, implementing NOILC on a relatively cheap FPGA is a challenge. In addition, the actual resource utilization is not provided until the final implementation when the HDL code is generated by MATLAB. As a result, generating a complete project every time the designer wanted to know the amount of resources used would be extremely time consuming. To solve these problems, there are two main contributions in this thesis:

- 1. The improved NOILC algorithm which utilizes fewer resources on the board but achieves the same functions.

- 2. The resource model for the improved and classical NOILC algorithms to estimate the resource utilization in the design process in MATLAB.

## Chapter 3

# **Related work**

## 3.1 Computation load reduction of NOILC

The ILC algorithm cannot avoid utilizing two square matrices as filters for computation. Because of its high complexity  $\mathcal{O}(n^2)$  [30], the computation load would increase sharply with the rising in the number of samples. With assuming the number of samples to be N,  $2 \times (N^2 + N)$  elements joint the computation and  $2 \times N^2$  multiplications are required to complete the NOILC algorithms [30]. Thus, for a large project, the required resource would increase to an affordable number.

A recent study on decreasing the computation load for norm-optimal ILC algorithm for both linear time-invariant (LTI) and linear time-varying (LTV) systems is published in 2016 [75] by Zunder, Bolder, Koekebakker and Oomen. They propose a resource-efficient ILC reducing the computational load from  $\mathcal{O}(N^3)$  to  $\mathcal{O}(N)$  by exploiting state-space descriptions and inversion techniques. They have shown that the new approach is able to generate the same control signal with a much lower computational cost. Moreover, this approach has been successfully executed on a host computer with a large task where the number of samples is 100000 by the same group [74]. Unfortunately, in this approach, its state-space update in real-time may cost much more power than the traditional norm-optimal ILC algorithm since not only the input signal, position error, is transmitted from ARM to FPGA but also the updated state-space. For every sample, the space-state has to be recomputed. In addition, a part of the calculation is inverse, from time N to time 1, providing difficulty in the calculation. When compared to the method proposed in this report, much more power is consumed because more data is communicated between the ARM and FPGA, and it is more complex, making implementation more difficult.

### 3.2 ILC Implementation on FPGA

Fei et al. have implemented a combination of model predictive control (MPC) and ILC in a digital signal processing/field programmable gate array (DSP-FPGA)-based azimuth axis platform of a telescope to control a permanent magnet synchronous motor [39]. The propose of this paper is to minimize the speed ripple. The reason why they choose ILC algorithms is to suppress periodic torque pulsations because the onset of torque pulsation in permanent magnet synchronous motor control systems is primarily related to rotor position, which results in periodic oscillations in motor torque and speed. In this paper, they do not improve the ILC algorithm, and the resource used is not mentioned. Qiu et al. have implemented a combined disturbance-observer-based control and iterative learning control design on an FPGA platform for pulsed superconducting radio frequency cavities [64]. They demonstrated that combining the ILC algorithm speeds up the system's convergence. Similarly, they did not mention of the ILC's resource consumption or the algorithm's improvement. They emphasized on the system's convergence speed.

Awan in 2012 implemented the NOILC algorithm on an FPGA applying it to a Gantry robot proving that the calculation time is reduced from 830ms (implemented on the FPGA) to 1.47ms (implemented on software) [24]. The FPGA-based implementation is several hundred times faster than the software. However, the controller requests a large storage space to store the trial data, the input signal for each iteration, which is restricted by the design and cost of chips. The authors have not improved the storage or resource utilization of NOILC during the implementation. They mentioned that the limitation of memory and power should be solved in the future while the aim of this thesis is to solve the restriction of resources.

### 3.3 Matrix Multiplication

#### 3.3.1 Timing and Power Improvement

Considering that in most situations, ILC cannot avoid matrix operation. Matrix multiplication is the most expensive computation in ILC. Thus, decreasing the resource utilization would be helpful for ILC implementation. Many previous works on implementing matrix multiplication on an FPGA have focused on reducing latency and power consumption [48][22][56]. To achieve shorter latency or less power consumption it always sacrifices some area which means higher resource utilization [48]. There are exceptions, however, and the methodology proposed by Campbell and Khatri in 2006 can reduce not only the computation time but also the resources utilization [31].

Parallel computing is that multiple computations or processes are executed at the same time by employing more than one processing units. It is effective in reducing computational latency [47]. The basic idea is to use multiple processors to collaboratively solve the same problem, i.e. the problem to be solved is broken down into several parts, each of which is computed in parallel by separate processors.

Pipelining is parallel execution at the instruction level which is a significant method in performance optimization especially in decreasing the execution time for a loop which repeats one instruction many times [21] which is taken off in 1969 [44]. Pipelining results in quasi-parallel implementation of a program in which multiple instructions are simultaneous executed. Because pipelining increases the throughput by executing multiple data-independent instructions at the same time, it is not efficient if only one instruction is executed. But for multiple instructions who do not read the output data of other instructions when they are simultaneous executed, using the parallelism principle of pipelining can actually increase the throughput by several times. Each pipeline stage has its own combined logical datapath within it, with no multiplexing of resources between them, so the area overhead is relatively high. But the effect of pipelining is achieved by allowing different pipeline stages to do different things at the same time, improving performance, optimising timing and increasing throughput rates.

Pipelining is helpful in increasing the throughput but the crucial restriction in ILC implementation is that the resource on a FPGA may not enough for ILC implementation.

### 3.3.2 Resource Utilization Optimization

Fox, Otto and Hey 1987 proved that decomposing matrices into smaller square sub-matrices is efficiently matrix multiplication [40]. The PUMMA algorithm proposed by Choi et al. in 1994 extended the Fox algorithm to a two-dimensional block curtain data distribution. It solves the problem of GPU based matrix multiplications where the sizes of matrices are usually larger than the shared memory of GPUs [33]. In 1995 van de Geijn and Watts proposed a simpler and more efficient matrix product algorithm called SUMMA [70] which achieves overlapping between com-

puting and communications. Different from CANNON [32] which restricts that the matrices have to be a square matrix with the same size, SUMMA allows arbitrary sizes of matrices to do multiplication operations. This algorithm has been enhanced to support 64-bit floating-point FPGA matrix multiplication (Dou, Vassiliadis, Kuzmanov & Gaydadjiev, 2005) [37] which is acceptable for arbitrary matrix sizes [70]. During the calculation, matrices are split into sub-matrices and parallelly process these sub-matrices. By doing so, matrices with large sizes are able to be implemented on a resource-constrained platform and shorten the computation time from sequential block matrix multiplication. The floating-point operations per second in this design [37] are at least 1.7 times faster than the related design in [69] and up to 18 times faster than the design in [66], assuming they implemented on the same chip.

Lin, So and Leong (2011) have shown that dense and sparse matrix multiplications based on an FPGA are restricted by different factors. The sparse matrix multiplication is constrained by the input/output memory while the computation of dense matrices is limited by the computation limitation [57]. Kestur, Davis and Chung provided a new coding encoding method in 2012 which decreases the memory accesses by 25% on average compared with compressed sparse row format for the sparse matrix examples [53]. The storage requirement is decreased significantly due to the new encoding method, however, the problem of limited computational units cannot be solved by it.

Decomposing matrices into smaller sub-matrices is helpful in implementing ILC algorithms because it decrease the memory accesses and restricted the usages of multipliers which are the goal of this project. The method proposed in this report also decomposes the matrices into columns for calculations based on the particularity of matrix-vector multiplication.

## 3.4 High-Level Synthesis

High-Level Synthesis (HLS) is an automated design process that takes an algorithm description as input to create the digital hardware that implements the required functionality [62]. Control algorithms are typically written in higher-level programming languages such as C, but the platforms that run these control algorithms frequently require HDLs. High-level programming languages are frequently more user-friendly than hardware languages. As a result, when using FPGAs or ASICs for data path implementation, HLS has emerged as an alternative to HDL[28]. Although HLS allows for rapid prototyping of any stochastic algorithm, there are limitations in terms of performance, memory bandwidth, and the number of logics when compared to manual design by domain experts [54]. Considering that HLS is able the partly restrict the performance of HDL codes by instructions in the high-level languages which MATLAB cannot achieves. The codes generated by HLS may has higher performance on latency, area, power, etc. However, MATLAB has a distinct advantage in that the designer can view the entire system model more intuitively.

## 3.5 FPGA programming by MATLAB Simulink

Haldar et al. (2001) used MATLAB to assist in the generation of HDL code, reducing design time from days to minutes [46]. Siwakoti and Town have designed FPGA-based digital controllers in MATLAB Simulink [67]. Different from the traditional manual HDL coding method, they generate the code by using the HDL generator provided by MATLAB. Jiang and Mangharam (2013) have utilized MATLAB and Simulink to create the first-of-its-kind electrophysiological model of the hear. They generated the VHDL code of this model directly through MATLAB and Simulink and implemented it on the real-time hardware for testing. The generated VHDL code is efficient and helps them to achieve the implementation of multiple versions of the model on the FPGA [49]. Weinmann created embedded MEDUMAT Transport software for healthcare workers in 2014 by creating the model in MATLAB and generating the HDL code through MATLAB after verifying the simulated result was correct. He found that with the help of MATLAB, the code development and review were accelerated by 50%, meanwhile more versions of the model are developed [38]. When designers are unfamiliar with hardware languages, FPGA programming through MATLAB has been shown to be easier for designers to implement models and may be more efficient than traditional programming methods in the design process. In terms of resource utilization, latency, energy consumption and etc., no evidence has been found that MATLAB-generated HDL code outperforms hand-written code by professional engineers. FPGA programming by MATLAB is more helpful for those who are not familiar with hardware languages and try to implement an operational hardware project.

# Chapter 4 Proposed approach

The NOILC contain two matrix multiplications which are used to filter the input signal, position error, and the feedforward signal from the current iteration. Due to the high complexity of the matrix multiplication and other matrix operations in the NOILC, NOILC is hard to be implemented on the FPGA. This chapter aims to introduce two methods to implement the NOILC algorithm on the FPGA and predict the resource utilization of these two methods.

### 4.1 Preliminary

An arbitrary matrix named A with m rows and n columns is represented in bold,  $\mathbf{A} \in \mathbb{R}^{m \times n}$ . One element in the  $k^{th}$  row  $(1 \le k \le m)$  and  $l^{th}$  column  $(1 \le l \le n)$  of matrix **A** is indicated as  $A_{k,l}$ . The  $k^{th}$  row of matrix **A** is 1 by N vector  $A_{r,k}$  and the  $l^{th}$  column of matrix **A** is N by 1 vector  $A_{c,l}$ .

$$\mathbf{A} = \begin{bmatrix} \mathbf{A}_{\mathbf{c},1} & \mathbf{A}_{\mathbf{c},2} & \dots & \mathbf{A}_{\mathbf{c},\mathbf{l}} & \dots & \mathbf{A}_{\mathbf{c},\mathbf{n}} \end{bmatrix}$$

(4.1)

$$\begin{bmatrix} \mathbf{A}_{\mathbf{r},1} \\ \mathbf{A}_{\mathbf{r},2} \end{bmatrix}$$

$$= \begin{vmatrix} \vdots \\ \mathbf{A}_{\mathbf{r},\mathbf{k}} \end{vmatrix}$$

(4.2)

$$\begin{bmatrix} \vdots \\ \mathbf{A_{r,m}} \end{bmatrix}$$

$$= \begin{bmatrix} A_{1,1} & A_{1,2} & \dots & A_{1,l} & \dots & A_{1,n} \\ A_{2,1} & A_{2,2} & \dots & A_{2,l} & \dots & A_{2,n} \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots \\ A_{k,1} & A_{k,2} & \dots & A_{k,l} & \dots & A_{k,n} \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots \\ A_{m,1} & A_{m,2} & \dots & A_{m,l} & \dots & A_{m,n} \end{bmatrix}$$

$$(4.3)$$

The NOILC system implemented in this project is a single-in, single-out (SISO) linear control system. The design is in a discrete-time domain where the sample period for the input and output are both Ts and the sampling frequency is  $f_s = 1/Ts$ . For the NOILC system in this project, the input of the system is a repetitive signal. In this project, the repetitive signal is the reference position signal. This signal is repeatedly entered until the system stops. Each repetition is called as one iteration. The length of the input signal in one iteration is assumed as N, where  $N \in \mathbb{Z}^+$ . The vector constructed by all samples of an arbitrary signal s in iteration j is  $\mathbf{s}_j \in \mathbb{R}^N$  where the  $i^{th}$  sample of the signal is the  $i^{th}$  element of the vector. The  $i^{th}$  sample of the signal s with length

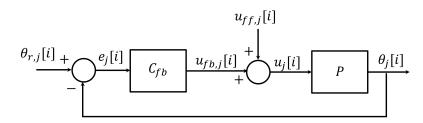

Figure 4.1: Block diagram of basic feedback control system with a feedforward signal

N in the  $j^{th}$  iteration is denoted as  $s_j[i]$ , i = 1, 2, ..., N. Iterations are indexed as a positive integer j without an upper bound considering that a system can run forever,  $j \in \{1, 2, ..., \infty\}$ .

$$\mathbf{s}_{\mathbf{j}} = \begin{bmatrix} s_j[1] \\ s_j[2] \\ \vdots \\ s_j[i] \\ \vdots \\ s_j[N] \end{bmatrix}$$

(4.4)

Figure 4.1 depicts a classic feedback control model in the discrete-time domain. The feedback controller is  $C_{fb}$  in the z-domain and the plant is P also in z-domain. The input signal of the feedback control is the reference position  $(\theta_{r,j}[i])$  and the output is the encoder measurement  $(\theta_j[i])$ . The reference position is the expected trace of the actuator and the encoder measurement is the measured position of the actuator. The signal position error,  $e_j[i]$ , is the difference between  $\theta_{r,j}[i]$  and  $\theta_j[i]$ , calculated by Equation 4.5. The output signal of the feedback controller is called  $u_{fb,j}[i]$ , the feedforward signal is  $u_{ff,j}[i]$  and the sum of them is the control signal  $u_j[i]$ . The reference position has a finite length, and the length for each execution remains constant. The goal of this control system is to minimize the position error,  $e_j[i]$ . As the input signal of the output signal of the feedback controller,  $u_{fb,j}[i]$  is calculated after the signal  $\theta_{r,j}[i]$  input to the system from the outside. The output signal of the feedback controller,  $u_{fb,j}[i]$  to help with speeding up the convergence. The sum of them is the control signal  $u_j[i]$  which will be applied to the plant. The output of the plant is measured to compute the current position error forming a close loop.

$$e_j[i] = \theta_{r,j}[i] - \theta_j[i] \tag{4.5}$$

### 4.2 Norm-optimal Iterative Learning Control

The input signal of a single-in-single-out NOILC in this project is repetitive. The input signal in this thesis is the position error  $e_j$  from the  $j^{th}$  iteration, and the output signal is the feedforward signal  $u_{ff,j+1}$  which will be added to the feedback control signal  $u_{fb,j+1}$  in the  $j+1^{th}$  iteration. In the discrete-time domain, both input and output are one-dimensional signals. The sample periods of these two signals are both  $T_s$ . In each iteration, the number of output samples should be the same as the input samples which is the scalar of the input,  $N \in \mathbb{N}^+$ . The aim of this NOILC system is to generate a feedforward signal helping the control system to decrease the error and speed up the convergence.

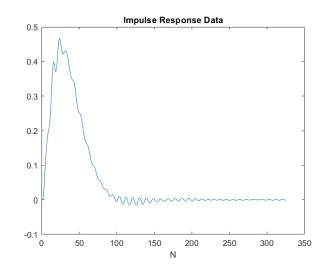

L is a learning filter and Q is a robustness filter [29]. For simplicity, two matrices are two N by N matrices which are calculated offline,  $\mathbf{L}, \mathbf{Q} \in \mathbb{R}^{N \times N}$ . The values of these two matrices are based on three weighting matrices,  $\mathbf{W}_{\mathbf{e}}, \mathbf{W}_{\mathbf{f}}$  and  $\mathbf{W}_{\Delta \mathbf{f}}$  [29] [72] and the impulse response **PS** of the close-loop from  $u_{ff,j}$  to  $\theta_j$  in Figure 4.1.  $\mathbf{W}_{\mathbf{e}}$  is set to determine the weighting of error.

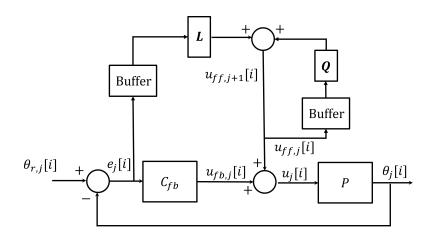

Figure 4.2: Block diagram of ILC control [73]

$\mathbf{W}_{\Delta \mathbf{f}}$  controls the convergence speed and the sensitivity to iteration varying distributed and  $\mathbf{W}_{\mathbf{f}}$  influence the robustness with respect to model uncertainty [29]. In discrete-time domain, the process sensitivity function in Equation 4.6 can be represented by convolution matrix **PS** which is constructed by the impulse response data PS(i) of the close-loop system from  $u_{ff,j}$  to  $\theta_j$ , where i is time,  $i = 0, 1, \ldots N - 1$  [26].

$$\frac{\theta_j(s)}{u_{ff,j}(s)} = PS(s) = \frac{P(s)}{1 + P(s)C_{fb}(s)}$$

(4.6)

$$\mathbf{PS} = \begin{bmatrix} PS(0) & 0\\ \vdots & \ddots\\ PS(N-1) & \dots & PS(0) \end{bmatrix}$$

(4.7)

With assuming the input and output as  $\theta_j$  and  $\mathbf{u_{ff,j}}$ , the response of the system is in Equation 4.8 and Equation 4.9, where  $\theta_j$  and  $\mathbf{u_{ff,j}}$  are vectors composed by signals  $\theta_j$  and  $u_{ff,j}$  in the  $j^{th}$  iteration.

$$\boldsymbol{\theta}_{j} = \mathbf{PS} \cdot \mathbf{u}_{\mathbf{ff}, \mathbf{j}} \tag{4.8}$$

$$\begin{bmatrix} \theta_j(0) \\ \dots \\ \theta_j(N-1) \end{bmatrix} = \begin{bmatrix} PS(0) & 0 \\ \vdots & \ddots \\ PS(N-1) & \dots & PS(0) \end{bmatrix} \begin{bmatrix} u_{ff,j}(0) \\ \dots \\ u_{ff,j}(N-1) \end{bmatrix}$$

(4.9)

The objective is to find the  $\mathbf{u_{ff,j}}$  with the minimizes the cost function j in Equation 4.10 [73].

$$j = \mathbf{e}_{\mathbf{j+1}}^{\mathbf{T}} \mathbf{W}_{\mathbf{e}} \mathbf{e}_{\mathbf{j+1}} + \mathbf{u}_{\mathbf{ff},\mathbf{j+1}}^{\mathbf{T}} \mathbf{W}_{\mathbf{f}} \mathbf{u}_{\mathbf{ff},\mathbf{j+1}} + (\mathbf{u}_{\mathbf{ff},\mathbf{j+1}} - \mathbf{u}_{\mathbf{ff},\mathbf{j}})^{T} \mathbf{W}_{\Delta \mathbf{f}} (\mathbf{u}_{\mathbf{ff},\mathbf{j+1}} - \mathbf{u}_{\mathbf{ff},\mathbf{j}})$$

(4.10)

With the knowledge  $\mathbf{e}_{j+1} = \mathbf{e}_j - \mathbf{PS}(\mathbf{u}_{\mathbf{ff},j+1} - \mathbf{u}_{\mathbf{ff},j})$ , the cost function can be rewrite as

$$\jmath = [\mathbf{e_j} - \mathbf{PS}(\mathbf{u_{ff,j+1}} - \mathbf{u_{ff,j}})]^T \mathbf{W_e}[\mathbf{e_j} - \mathbf{PS}(\mathbf{u_{ff,j+1}} - \mathbf{u_{ff,j}})] \\ + \mathbf{u_{ff,j+1}^T} \mathbf{W_f} \mathbf{u_{ff,j+1}} + (\mathbf{u_{ff,j+1}} - \mathbf{u_{ff,j}})^T \mathbf{W_{\Delta f}}(\mathbf{u_{ff,j+1}} - \mathbf{u_{ff,j}}).$$

$$(4.11)$$

When the cost function is minimized,  $\frac{\partial j}{\partial \mathbf{u_{ff,j+1}}} = 0$ . The optimal feedforward signal in the j+1 iteration is represented as

$$\mathbf{u_{ff,j+1}} = [(\mathbf{PS})^T \cdot \mathbf{W_e} \cdot \mathbf{PS} + \mathbf{W_f} + \mathbf{W_{\Delta f}}]^{-1} \{ (\mathbf{PS})^T \cdot \mathbf{W_e} \cdot \mathbf{e_j} + [(\mathbf{PS})^T \cdot \mathbf{W_e} \cdot \mathbf{PS} + \mathbf{W_{\Delta f}}] \mathbf{u_{ff,j}} \}.$$

(4.12)

FPGA-based Advanced Motion Controller Development and Design Automation

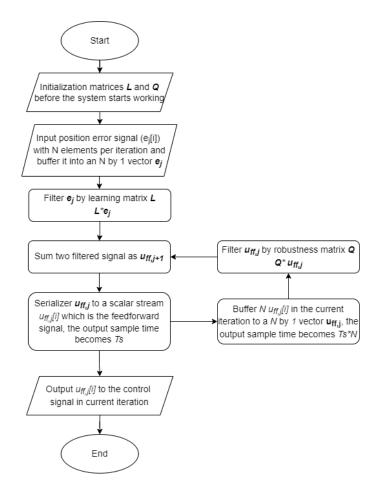

Figure 4.3: Original ILC working flow

Based on Equation 4.12,  $\mathbf{L}$  and  $\mathbf{Q}$  can be calculated based on the Equation 4.13 and Equation 4.14 [73].

$$\mathbf{L} = [(\mathbf{PS})^T \cdot \mathbf{W}_{\mathbf{e}} \cdot \mathbf{PS} + \mathbf{W}_{\mathbf{f}} + \mathbf{W}_{\Delta \mathbf{f}}]^{-1} [(\mathbf{PS})^T \cdot \mathbf{W}_{\mathbf{e}}]$$

(4.13)

$$\mathbf{Q} = [(\mathbf{PS})^T \cdot \mathbf{W}_{\mathbf{e}} \cdot \mathbf{PS} + \mathbf{W}_{\mathbf{f}} + \mathbf{W}_{\Delta \mathbf{f}}]^{-1} [(\mathbf{PS})^T \cdot \mathbf{W}_{\mathbf{e}} \cdot \mathbf{PS} + \mathbf{W}_{\Delta \mathbf{f}}]$$

(4.14)

With the knowledge of matrices **L** and **Q**, the ILC algorithm can be simply considered as a sum of two products of matrix multiplications.  $u_{ff,j+1}$  is the sum of filtered  $e_j$  in the current iteration and the filtered  $u_{ff,j}$  in the current iteration. The NOILC update equation is presented in the Equation 4.15.

$$\mathbf{u_{ff,j+1}} = \mathbf{L} \cdot \mathbf{e_j} + \mathbf{Q} \cdot \mathbf{u_{ff,j}}$$

(4.15)

The ILC control diagram is presented in Figure 4.2. The two buffers in the diagram is used to converge two one-dimension signals  $e_j[i]$  and  $u_{ff,j}[i]$  into two N by 1 vectors  $\mathbf{e_j}$  and  $\mathbf{u_{ff,j}}$ . After buffering the position error in the  $j^{th}$  iteration into an N by 1 vector,  $\mathbf{e_j} \in \mathbb{R}^N$ , it is right multiplied by **L**. At the same time, the feedforward signal in the  $j^{th}$  iteration is also buffered to an N by 1 vector,  $\mathbf{u_{ff,j}}$  and right multiplied by **Q**. The sum of these two results is the vector of the feedforward signal,  $\mathbf{u_{ff,j+1}} \in \mathbb{R}^N$ , which is added to the control signal in the  $(j+1)^{th}$  iteration after  $\mathbf{u_{ff,j+1}}$  being serialized into the one-dimension signal  $u_{ff,j+1}$ . The whole workflow is presented in Figure 4.3.

### 4.3 NOILC with Classical Method

#### 4.3.1 Definition of Matrix Multiplication

The classical matrix multiplication takes  $\mathcal{O}(n^3)$  computations [76] to calculate two matrix with  $\mathcal{O}(n^2)$  elements. Considering the inputs of the computation to be a *m* by *p* matrix **A** and a *p* by *n* matrix **B**, the result matrix **C** will be an *m* by *n* matrix.

$$\mathbf{C} = \mathbf{A} \times \mathbf{B} \tag{4.16}$$

(4.17)

| [ C <sub>1,1</sub> | <i>C</i> <sub>1,2</sub> | ••• | $C_{1,n}$ |   | $\begin{bmatrix} A_{1,1} \end{bmatrix}$ | A <sub>1,2</sub> |     | $A_{1,P}$ | <i>B</i> <sub>1,1</sub> | $B_{1,2}$ | ••• | $B_{1,n}$ ] |

|--------------------|-------------------------|-----|-----------|---|-----------------------------------------|------------------|-----|-----------|-------------------------|-----------|-----|-------------|

|                    |                         |     |           |   |                                         | A <sub>2,2</sub> |     |           |                         | $B_{2,2}$ | ••• | $B_{2n}$    |

| :                  | ÷                       | ۰.  | :         | = | :                                       | :                | ۰.  | :         | :                       | :         | •.  | :           |

| $C_{m,1}$          | $C_{m,2}$               | ••• | $C_{m,n}$ |   | $A_{m,1}$                               | $A_{m,2}$        | ••• | $A_{m,P}$ | $B_{P,1}$               | $B_{P,2}$ | ••• | $B_{P,n}$   |

Figure 4.4: classical Matrix Multiplication Operation

During the computation, each element in matrix **C** is concerned with one row in matrix **A** and one column in matrix **B** like Figure 4.4 presented. For any element  $C_{i,j}$ , in the  $k^{th}$  row and  $l^{th}$  column equals to the sum of dot products of the whole  $k^{th}$  row of matrix **A** and the whole  $l^{th}$  column of matrix **B** shown in Equation 4.18. Thus, p multiplications and additions are required to compute one element in the output. In total  $p \times m \times n$  multiplications and additions are required to complete a matrix multiplication.

$$C_{k,l} = A_{k,1} \times B_{1,l} + A_{k,2} \times B_{2,l} + \ldots + A_{k,q} \times B_{q,l} + \ldots + A_{k,p} \times B_{p,l}, q \in \{1, 2, \ldots, p\} \quad (4.18)$$

$$=\sum_{q=1}^{p} A_{k,q} \times B_{q,l} \tag{4.19}$$

### 4.3.2 Matrix Multiplication Computation in Parallel

To ensure sufficient computing time, all calculations are designed to be performed simultaneously by employing multiple processing units. The number of employed processing units equals to the number of multiplications for each iteration. Each processing unit performs the required multiplication operations at the same time. Based on the multiple DSP cores on the FPGA, the FPGA is able to break the matrix multiplication, into separate scalar multiplications. Each DSP core executes one scalar multiplication. Thus, scalar multiplication operations in a matrix multiplication are able to be processed at the same time rather than waited to be processed in series. The computation time could be saved but a lot of DSP cores are employed to achieve the matrix multiplication. Since the number of required DSP cores may exceed hundreds or even thousands where only tiny FPGAs are designed with such a number of DSPs and these FPGAs are usually expensive [4], all multiplication operations can be performed at the same time, but it is costly.

For one matrix multiplication in the ILC system,  $N^2$  multipliers are required. This number increases to a huge scalar with the rising of N. Moreover, ILC operates two matrix multiplications which double the utilization of multipliers. Generally, FPGAs are not designed with so many DSPs, XC7Z100 in the Zynq-7000 family contains the maximum number of DSPs which is 2020 [19]. There exist FPGA boards with thousands of DSPs but those are much more expensive [4]. When the system has a small N, it is possible to implement the NOILC by the method mentioned in this section.

Figure 4.5: Diagram of classical NOILC Implementation

#### 4.3.3 Resource utilization Model

The diagram in Figure 4.5 is a NOILC system constructed with the classical matrix multiplication in parallel. Signal  $e_j$  and  $u_{ff,j}$  have to be buffered into a vector for computation. Thus, in the buffering step also called deserializing step, at most 2N samples need to be saved in the chip. Assuming the bit-width of  $e_j$  and  $u_{ff,j}$  is bW,  $2bW \cdot N$  bits need to be saved in storage blocks. The vector can be either stored in a block RAM or in distributed memory in an FPGA directly. Commonly saving a large vector in block RAMs would be an advisable choice since distributed memory in an FPGA is restricted. However, considering that all the elements have to be computed at the same time, it is hard to send hundreds of or even thousands of elements from block RAMs to operational blocks in a relatively short period of time. Thus, these elements would be better stored in the distributed RAMs in the FPGA. The deserializing step would be achieved by adopting flip-flops (FFs).

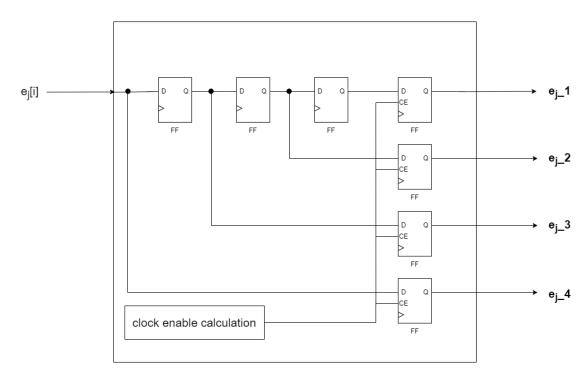

Figure 4.6: The functional diagram of a describing when N = 4, bit-width = 1

The description of the step must be able to buffer a scalar stream into a N by 1 vector and output all elements in the vector after receiving the final element. Therefore, as the bit-width is bW, there should exist  $N \cdot bW$  of data FFs connected with a clock enable signal which guarantees elements in the vector output at the same time and additional N-1 FFs help to buffer

the earlier elements like Figure 4.6 shown. Thus, bW(2N-1) FFs are required to achieve the buffering function for one matrix multiplication in the ILC algorithm. To realize the number of input elements and prevent the deserializer outputting until enough elements have been buffered, it needs an adder to count the number of elements N and a comparer to compare the result of the adder with N.  $\lceil log_2(N) \rceil$  FFs and  $\lceil log_2(N) \rceil$  LUTs constitute an adder and  $\lceil log_2(N) \rceil$  FFs constitute a comparer. The  $\lceil x \rceil$  rounds the element x to the nearest integer which is greater or equal to itself. The clock enable signal for the FFs in the deserializer mentioned before should not be an external signal. It should be calculated based on the input sample period and the size of buffered vector. An adder and a comparer are required to calculate the clock enable signal and an additional LUT might be required to control the level of the clock enable signal applied to the FFs. A deserializer does not need any digital signal processing (DSP) blocks and required the total number of FFs, LUTs are:

$$U_{LUT} = 2 \times (1 + 4 \times \lceil \log_2(N) \rceil) \tag{4.20}$$

$$U_{FF} = 2 \times (bW \times (2 \times N - 1) + 2 \times \lceil log_2(N) \rceil)$$

$$(4.21)$$

$$U_{DSP} = 0. (4.22)$$

There are more efficient deserializer designs. The two sets of adders and comparers, for example, perform the same purpose. A deserializer can be designed with just one adder and one comparer. The suggested constitution is nearly the worst case scenario, utilizing as much resources as possible. As a result, if the actual resource on the platform is more than the calculated resource, the design will not fail due to a lack of resources. There do exist the designs of the deserializer which consumes more resources like the design in Figure 4.7 where the signal output from the first FF in the first line is same with the output of the FF in the fourth line. The six FFs output of the first line are repeating the same behaviours of the FFs in the first line. The weakness of the design like this is able to be optimized by the synthesis tool. Thus, the design in Figure 4.7 is not considered to be the worst design and the resource utilization is not predicted based on it.

Figure 4.7: A terrible design of a deserializer when N = 4, bit-width = 1

To guarantee that two matrix-vector multiplications in ILC output their results simultaneously,  $2 \times N \times N$  multipliers are required to achieve this parallel execution since there exist two vectormatrix multiplications in 4.15. There exist two buffered vectors, two matrices which can be either saved in block RAM or distributed RAM in the FPGA. Usually, such a large amount of data should not be stored in distributed memory but in the worst situation, MATLAB may design to store these elements in distributed memory because matrices are not changed by time and all of the elements join the multiplications in every iteration. To consider the worst situation, two matrices are assumed to be saved in distributed memory built up by LUTs. For  $2 \times N \times N$  elements,  $bW \times 2 \times N \times N$  LUTs are cost, and each multiplier needs one DSP to complete operation. The resources required for the multiplication part are:

$$\begin{cases} U_{LUT} = bW \times 2 \times N \times N \\ U_{FF} = 0 \end{cases}$$

(4.23)

(4.24)

$$U_{FF} = 0 \tag{4.24}$$

$$\left(U_{DSP} = 2 \times N \times N.\right.$$

(4.25)

Table 4.1: The resource utilization assumption for the classical NOILC implementation

|                           | LUTs                                              | FFs                                     | DSPs   |

|---------------------------|---------------------------------------------------|-----------------------------------------|--------|

| Deserializer (2)          | $2(1+4\lceil log_2(N)\rceil)$                     | $2(bW(2N-1) + 2\lceil log_2(N) \rceil)$ | 0      |

| Matrix multiplication (2) | $2 \times bW \times N^2$                          | 0                                       | $2N^2$ |

| Total                     | $2(bW \times N^2 + 1 + 4\lceil \log_2(N) \rceil)$ | $2(bW(2N-1) + 2\lceil log_2(N)\rceil)$  | $2N^2$ |

According to the above assumptions, the total resource utilization before serializing is in the Table 4.1. According to the table, it is clear that the utilization of DSP is quadratically increasing with N. When the FPGA platform does not have enough physical DSPs, to achieve the function of the design, MATLAB might allowed one DSP to process more than one multiplications in series. Because the input data cannot be processed directly, part of them have to be stored and wait to be processed until the physical DSPs finish the previous multiplications. So does the output of DSPs must wait for all products computed. Thus, more data has to be stored for waiting, more FFs are employed to achieve the storage. Moreover, more selections are made to decide which multiplication or addition is going to be performed and more LUTs are utilized for the selection. Thus, when N rises to a large number resulting insufficient DSPs, this process leads to the surge in the utilization of LUTs and FFs. The actual resource utilization becomes unpredictable. To achieve an ILC system running on cost-optimized devices or mid-range devices, the utilization of DSPs has to be decreased.

#### 4.4NOILC with Improved Method

The number of elements of position error, N, in factories ranges from hundreds to thousands. In the last section, it is proved that when more than one multiplications have to share one physical DSP to achieve computations, with the increase of N, the required LUTs and FFs may increase to a huge number. This number is probably larger than the number of FFs and LUTs the board actually has leading to the system cannot be executed on the selected FPGA platform. Therefore, in order to ensure that the algorithm can operate even with a large N, the resource utilisation of the algorithm should be improved.

#### Matrix Multiplication by Column Combination Method 4.4.1

Because the dramatic increase in LUTs and FFs occurs when there are not enough DSPs, for the current algorithm, the core of resource utilization reduction should be reducing the DSP usage. In the previous approach, with the increase of N, the usage of the DSPs is quadratic growth  $(DSPs=2N^2)$ . Thus, it is better to limit the growth of DSP utilization to linear growth or even slower.

Block matrix multiplication mentioned in Section 3.2 decreases the actual resource utilization on the FPGA. Considering that in NOILC, only when enough of elements are entered, the vector can be buffered by these elements. The N-size-vector buffering process requires  $T_s(N-1)$  to complete. Block matrix multiplication still needs to buffer a smaller vector spending time in an iteration. The best solution is that the system would not waste time in buffering.

If elements from the input position error and feedforward signals in the current iteration,  $e_j[i]$  and  $u_{ff,j}[i]$  can be processed in time rather than waiting until all samples are buffered into two vectors, the computation time would not be as narrow. Thus, the allowable computation time for all multiplications increases from  $T_s$  to  $N \times T_s$ , the length of one iteration.

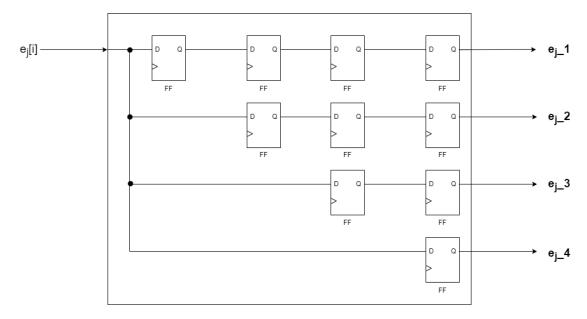

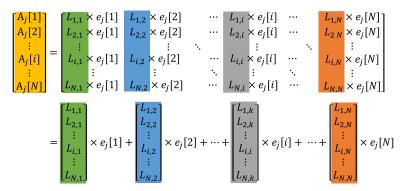

Figure 4.8: Right vector-matrix multiplication

For one matrix multiplication, **L** multiplying with the position error  $\mathbf{e}_{\mathbf{j}}$ , in ILC system, we assume its result as an N by 1 vector  $\mathbf{A}_{\mathbf{j}}$ . There is an N by 1 vector on the right side of multiplication, visualizing from Figure 4.8, the  $i^{th}$  element of  $\mathbf{e}_{\mathbf{j}}$  is only operated with the  $i^{th}$  column of **L**. Thus, the result vector  $\mathbf{A}_{\mathbf{j}}$  can be represented by Equation 4.26.

$$\mathbf{A}_{\mathbf{j}} = \sum_{i=1}^{N} (e_j[i] \times \mathbf{L}_{\mathbf{c},\mathbf{i}})$$

(4.26)

where  $\mathbf{L}_{\mathbf{c},\mathbf{i}}$  is the  $i^{th}$  column of matrix  $\mathbf{L}$ .

$$\mathbf{L} = \begin{bmatrix} \mathbf{L}_{\mathbf{c},\mathbf{1}} & \mathbf{L}_{\mathbf{c},\mathbf{2}} & \dots & \mathbf{L}_{\mathbf{c},\mathbf{i}} & \dots & \mathbf{L}_{\mathbf{c},\mathbf{N}} \end{bmatrix}$$

(4.27)

$$\begin{bmatrix} L_{1,i} \end{bmatrix}$$

$$\mathbf{L}_{\mathbf{c},\mathbf{i}} = \begin{bmatrix} L_{2,i} \\ \vdots \\ L_{i,i} \\ \vdots \\ L_{N,i} \end{bmatrix}, \mathbf{L}_{\mathbf{c},\mathbf{i}} \in \mathbb{R}^{N}$$

$$(4.28)$$

#### 4.4.2 NOILC Implementation by Improved Method

According to Equation 4.26, if at the time when  $e_j[i]$  enters the ILC system, the corresponding vector  $L_{c,i}$  is selected to operate with  $e_j[i]$  while the product is buffered for later accumulation. It works the same on the Q filter part. Because the matrices **L** and **Q** are calculated off-line, the values are available to be stored before the system starts working. Thus, elements from the position error and feedforward signal do not need to be buffered into two vectors and the computations do not need to wait until the last  $T_s$  in each iteration.

When the column combination is performed, the number of multipliers required grows linearly with the number of items in one iteration (N). N multipliers are utilized to compute  $e_i[i] \times \mathbf{L}_{\mathbf{c},\mathbf{i}}$ .

To decrease the number of multipliers, the multiplication between  $e_j[i]$  and  $\mathbf{L_{c,i}}$  is arranged in series by decreasing the sample time of  $e_j[i]$  from  $T_s$  to  $T_s/N$ , multiplying  $e_j[i]$  with N elements in  $\mathbf{L_{c,i}}$  serially. The allowable computation time for each matrix multiplication becomes  $T_s/N$ . When the sampling frequency is 10 kHz and the number of elements N is 1000 samples per iteration, the allowable computation time for one multiplication should be 100 ns. Therefore, the clock frequency must be larger than 10 MHz which is supported by almost all FPGA boards. In this case, as long as the computation time for each multiplication operation is within the limitation of selected FPGAs, only one multiplier is required for one matrix multiplication. The DSP utilization is restricted to a very small range which would not increase with N. The number of DSPs on a platform would not limit the implementation of NOILC on FPGA.

The buffered product of each column should be added together and output as the feedforward signal after being serialized. If the addition process does not start until the last product result is calculated in one iteration,  $N \times N$  elements need to be stored. Because the signal  $e_j[i]$  does not need to be buffered, the multiplications between  $e_j[i]$  and element in  $\mathbf{L}_{\mathbf{c},\mathbf{i}}$  are processed immediately after receiving  $e_j[i]$ . The addition operation in matrix multiplication does not need to wait for the completeness of the multiplication operation. Thus, the accumulation and multiplication can be processed synchronously.

$$\mathbf{u}_{\mathrm{ff},j+1} = \mathbf{L} \cdot \mathbf{e}_{\mathbf{j}} + \mathbf{Q} \cdot \mathbf{u}_{\mathrm{ff},\mathbf{j}}$$

$$\begin{bmatrix} u_{ff,j+1}[1] \\ u_{ff,j+1}[2] \\ \vdots \\ u_{ff,j+1}[2] \\ \vdots \\ u_{ff,j+1}[n] \end{bmatrix} = \begin{bmatrix} \sum_{k=1}^{N} (e_{j}[k] \times L_{1,k}) \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{2,k}) \\ \vdots \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{i,k}) \\ \vdots \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{n,k}) \end{bmatrix} + \begin{bmatrix} \sum_{k=1}^{N} (u_{ff,j}[k] \times Q_{1,k}) \\ \sum_{k=1}^{N} (u_{ff,j}[k] \times Q_{i,k}) \\ \vdots \\ \sum_{k=1}^{N} (u_{ff,j}[k] \times Q_{n,k}) \end{bmatrix}$$

$$\begin{bmatrix} u_{ff,j+1}[1] \\ u_{ff,j+1}[2] \\ \vdots \\ u_{ff,j+1}[n] \end{bmatrix} = \begin{bmatrix} \sum_{k=1}^{N} (e_{j}[k] \times L_{1,k} + u_{ff,j}[k] \times Q_{1,k}) \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{2,k} + u_{ff,j}[k] \times Q_{2,k}) \\ \vdots \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{2,k} + u_{ff,j}[k] \times Q_{2,k}) \\ \vdots \\ \sum_{k=1}^{N} (e_{j}[k] \times L_{n,k} + u_{ff,j}[k] \times Q_{n,k}) \end{bmatrix}$$

$$(4.31)$$

Because the products from one column do not interact with each other and are computed sequentially, they can be buffered into a N by 1 vector and added with other buffered products. After storing the first column's product vector into distributed memory, the vector is allowed to be updated, becoming the product vector of the next column in the following sample time by reusing the same storage. The updated vector is then added to the stored vector, and the sum of them is saved in the same memory location as the stored vector. By doing so, the accumulation is completed after N repetitions of the same process. The accumulation is the final result of this matrix multiplication at the last sample time in each iteration, after the last column products being added. N adders are required for accumulation, and the permitted calculation time for one matrix multiplication in NOILC becomes  $N \cdot T_s$ ; additionally, only 2N elements must be arranged to store in the chip.

Based on the Equations (4.29 - 4.31) it is clear that the  $k^{th}$  element of  $u_{ff,j+1}$  equals to the sum of N times addition  $(u_{ff,j+1}[i] = \sum_{k=1}^{N} e_j[k] \cdot L_{i,k} + u_{ff,j}[k] \cdot Q_{i,k})$ . By breaking the multiplication and addition in matrix multiplication into two parts, this method provides

an opportunity to perform the multiplication of  $e_j[i + 2]$  and elements  $\mathbf{L}_{\mathbf{c},\mathbf{i+2}}$  and addition  $e_j[i + 1] \cdot \mathbf{L}_{\mathbf{c},\mathbf{i+1}} + \sum_{k=1}^{i} (e_j[i] \cdot \mathbf{L}_{\mathbf{c},\mathbf{k}})$  at the same time. According to Equation 4.31, adding the two products before buffering them into vector and then buffering them into a vector for accumulation has the same result with adding the two accumulated vectors. The benefit of adding two products before buffering is that N adders for one matrix multiplication would be saved and the storage for the 2N elements would not need to be arranged anymore.

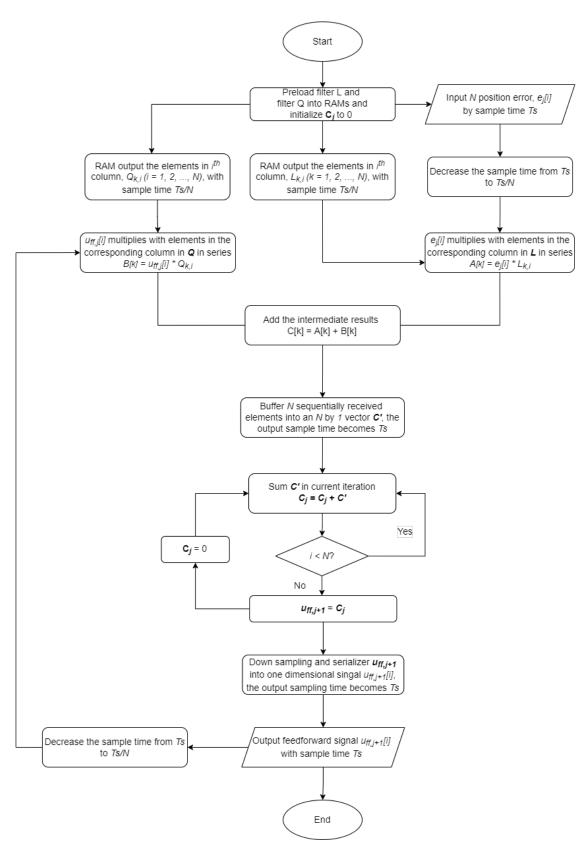

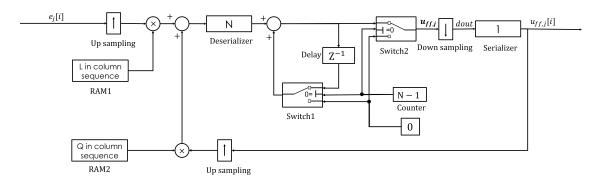

The workflow of the ILC system implemented by the column combination method is shown in Figure 4.9. Since the matrices  $\mathbf{L}$  and  $\mathbf{Q}$  are known and would not be changed anymore for a specific system, these two matrices can be preloaded into block RAMs, otherwise, saving these two matrices in distributed memory would waste a lot of FFs, even use up all FFs when N is large. After the system start, elements of  $e_j$  enter the ILC system with sample period  $T_s$ . Then the sample period of  $e_j$  reduces to  $T_s/N$  to multiply with the N elements from the corresponding column of matrix  $\mathbf{L}$  sequentially. At the same time, the sample period of the feedforward signal  $u_{ff,j}$  also reduces from  $T_s$  to  $T_s/N$  and multiplies with the elements in the corresponding column of the matrix  $\mathbf{Q}$ . The products from  $e_j[i]$  and N elements of  $\mathbf{L}_{c,i}$  are added with the products of  $u_{ff,j}[i]$  and N elements of  $\mathbf{Q}_{c,i}$ . These N additions will be buffered into a N by 1 vector for accumulation. At the start of each iteration, the adding factor should be initialized to zero. After N addition operations in the accumulation process, the result is the vector of the feedforward signal which needs to be serialized and output with sample time  $T_s$ .

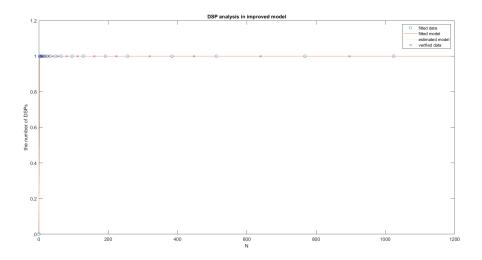

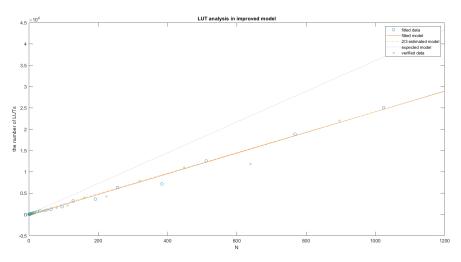

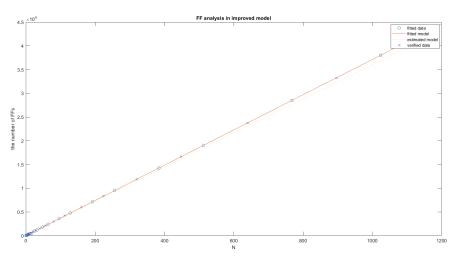

#### 4.4.3 Resource Utilization Model

By using the column combination method described in Section 4.4.2, only two DSPs are utilized for two matrix multiplications regardless the value of N. The utilization of DSPs would not increase with the growth of N. Thus, for a system with a large N, the number of DSPs on the FPGA is also sufficient. The addition of two products needs one adder. Considering the bit-width, bW LUTs are required for the adder. To buffer the sum of two products into a N by 1 vector, a deserializer is necessary which requires  $1 + 4\lceil log_2(N) \rceil$  LUTs and  $bW(2N-1) + 2\lceil log_2(N) \rceil$  FFs as mentioned in Section 4.3.3. The elements of matrices **L** and **Q** can be stored in block RAMs because the elements are used sequentially.

Only N adders are required for accumulating the sum of products. The total number of LUTs required is  $bW \times N$ . To achieve the loop of accumulation, the system needs a switch, a counter and a constant 0. The constant 0 is to initialize the storage at the start of each iteration. An another switch is required to identify whether output the final result at the end of each iteration. To count for number N, it needs  $2 \times \lceil log_2(N) \rceil$  LUTs and  $\lceil log_2(N) \rceil$  FFs as described in Section 4.3.3. One LUT is necessary for constant 0. The inputs and outputs of two switches are both N by 1 vectors, therefore each switch needs to do N selections which requires  $bW \times N$  LUTs.

|                         | LUTs                                            | FFs                                  | DSPs |

|-------------------------|-------------------------------------------------|--------------------------------------|------|

| Deserializer            | $1 + 4\lceil log_2(N) \rceil$                   | $bW(2N-1) + 2\lceil log_2(N) \rceil$ | 0    |

| Multiplier(2)           | 0                                               | 0                                    | 2    |

| Adder of products       | bW                                              | 0                                    | 0    |

| Counter                 | $2\lceil log_2(N) \rceil$                       | $\lceil log_2(N) \rceil$             | 0    |

| Constant 0              | 1                                               | 0                                    | 0    |

| Adders for accumulation | $bW \cdot N$                                    | 0                                    | 0    |

| Switch (2)              | $2bW \cdot N$                                   | 0                                    | 0    |

| Total                   | $3bW \cdot N + 6\lceil log_2(N)\rceil + bW + 2$ | $bW(2N-1) + 3\lceil log_2(N) \rceil$ | 2    |

Table 4.2: The resource utilization assumption for the improved NOILC implementation

#### 4.4. NOILC WITH IMPROVED METHOD

Figure 4.9: Improved ILC working flow by using Column Combination Method

|                  | LUTs                                              | FFs                                     | DSPs   |

|------------------|---------------------------------------------------|-----------------------------------------|--------|

| Classical method | $2(bW \times N^2 + 1 + 4\lceil \log_2(N) \rceil)$ | $2(bW(2N-1) + 2\lceil log_2(N) \rceil)$ | $2N^2$ |

| Improved method  | $3bW \cdot N + 6\lceil log_2(N) \rceil + bW + 2$  | $bW(2N-1) + 3\lceil log_2(N) \rceil$    | 2      |

Table 4.3: Comparison of resource usage of the classical and the improved methods

The total resource cost for the improved method is in Table 4.2. Compared with the classical implementation method in table 4.1, the rise of LUTs becomes a linear with the development of N, and the use of DSPs is a constant. In this project, only 2 DSPs are utilized. The usage of FFs linear increases with the growth of N. Since the computation time for multiplication is related to the number of elements in one iteration, for a system with a huge N, the computation time for multiplication may decrease to  $10^{-10}$ s which is almost impossible to be processed. In this case, more multipliers should be utilized to do multiplications in parallel, reducing calculation time. Another disadvantage of this design is that the sample frequency of the output feedforward signal may not be  $f_s$ . The sample frequency of the output signal  $u_{ff,j+1}$  is possible to be faster than  $f_s$  because the sampling frequency of the signals  $e_j$  and  $u_{ff,j}$  in the previous step is raised in order to achieve multiplication. Before adding the feedforward signal with the feedback control signal, the sampling frequency of  $u_{ff,j+1}$  must be decreased to  $f_s$  by downsampling.

# Chapter 5 Experimental Setup

An FPGA is required to process the projects while constructing a NOILC system on an FPGA platform. To simulate execution, control systems should be constructed in MATLAB Simulink. When the simulation results show that the systems converge and that the feedforward signals created by ILC help in reducing error and speeding up convergence, the HDL projects of ILC algorithms are generated via the FPAG programming process provided by MATLAB. Finally, the project may be executed on the selected FPGA board, and the actual resource utilization can be checked in the project files.

## 5.1 Platform

Not all the FPGA devices on the market are supported by the FPGA programming of MATLAB. Zedboard is one of the supported hardware devices, meanwhile, meanwhile, at \$475, Zedboaed is not prohibitively pricey [18]. Zedboards can process designs based on Linux, Windows, and other real-time operating systems [18]. The Zynq chip can be divided into two parts, processing system (PS) and programmable logic (PL) [19]. PS is a traditional processor equipped with a dual-core ARM Cortex-A9 processor, memory, timer, various communication interfaces for external devices, etc. Zedboard is designed with Xilinx XC7Z020 as a programmable logic device which contains 53200 LUTs, 106400 FFs, 220 DSP slices and 4.9Mb total block RAM [19]. PS is interconnected with PL via internal high-speed buses.

Figure 5.1: The chosen platform: Zedboard

### 5.2 NOILC with Classical Matrix Multiplication

#### 5.2.1 NOILC Implementation

A traditional feedback control system is made up of two major components: a controller and a plant. This control system's objective is to ensure that the actuator controlled by the motor goes to the specified position. As a result, the plant in this project is a continuous actuator directed by a motor. The signal  $\theta_j$ , on the other hand, is the measured encoder position in the discrete-time domain, reading data based on the sampling frequency. Because MATLAB is more likely to report errors when developing HDL projects for hybrid systems than when developing projects for exclusively discrete systems. Thus, despite the fact that the plant should be designed in the continuous-time domain, the simulated plant is constructed in the discrete-time domain. The feedback control system is constructed based on a given simulated model with a sampling frequency 16 kHz.

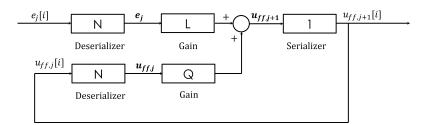

In order to buffer the one-dimensional input signal  $e_j[i]$  and output signal  $u_{f,j}[i]$  into two N by 1 vectors, two buffers are required. In Simulink, the component *Buffer* is able to achieve this function [5]. The component *Gain* [12] is able to perform multiplication with provided gain factors which can be either scalars, vectors or matrices. These gain factors are kept in distributed memory and are connected to the same clock signals as the multipliers. Thus, the input signals are multiplied by these factors as long as the multiplications are processed. These gain factors are accompanied by the multipliers to guarantee that as long as the input signal comes, multiplications would be processed. Two *Gain* components achieve the vector-matrix multiplications by providing matrices L and Q as gain factors. After adding the two products, the final vector  $\mathbf{u_{ff,j}}$  should be converted into a one-dimensional signal again, which is also achievable by *Buffer*. However, *Buffer* does not support the HDL code generation in MATLAB. The substitutes for buffers are *Deserializer1D* [9] and *Serializer1D* [14] who convert a one-dimensional signal into vectors and vectors into lower dimension signal respectively.

#### 5.2.2 Number of Samples Reduction

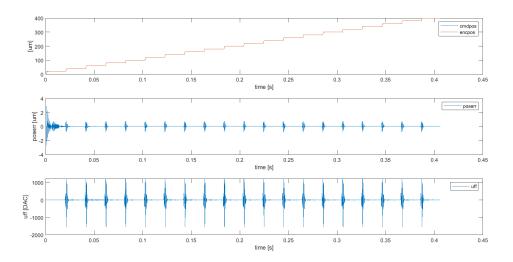

The reference signal contains 650 samples at 16 kHz sampling frequency in each iteration (Figure 5.2 (a)), which cannot be implemented on the chosen Zedboard because the number of expected multipliers (422500) is much greater than the number of DSPs a Zedboard has (220). To implement the current NOILC algorithm on the chip, the number of samples has to be reduced without influencing the convergence of the system.

Currently, after reaching the predicted location from the initial position, the trace of the reference position remains in the current state for a short time before returning to the initial position to await movement in the next iteration. However, ILC cannot identify whether the command position is back to the initial position or not since once the control system converges, the signal  $e_j$  reduces to almost zero and the input signal to ILC is the position error. Therefore, the reference position does not have to return to the initial position but increases directly based on the convergence state forming as a stair-step signal. The number of required samples to achieve convergence becomes only half of the original one as 325 as figure (b) in Figure 5.2.

#### 5.2.3 Word Width

The NOILC is implemented on the FPGA while the feedback control part is programmed on the ARM. The communication between these two parts is based on the AXI4 interfaces arranged by Simulink. Because the datatype is not specified by the designer during the simulation, MATLAB utilises double precision as the datatype. To transmit data between ARM and FPGA, the signal  $e_j$  and  $u_{ff,j}$  would be better to be converted to a signed fixed-point data type. With the help of

Figure 5.2: Two reference position signals with different lengths

the feedforward signal generated by NOILC, the error starts to reduce and gradually approaches a value of 0 from the second iteration. Thus, the maximum difference between the reference position signal and encoder measurement signal should be in the first iteration. In contrast, the signal  $u_{ff,j}$  remains at 0 in the first iteration and it has the computed output from the second iteration. The values of  $u_{ff,j}[i]$  remain stable after the system becomes convergent which may take several iterations. Based on the maximum values and the minimum values of signal  $e_j$  and  $u_{ff,j}$  measured in the simulation, the shortest word length to ensure the system working correctly can be confirmed. But overflow easily happens because the result from the hardware cannot be totally the same with the simulation result. In this project, to preserve the storage on FPGA, the shortest world width is chosen. The minimum and maximum values of  $e_j$  and  $u_f f$  in 10 iterations are:

- max  $e_j$ : 394.7204

- min  $e_j$ : -368.8130

- max  $u_{ff,j}$ : 1223.8462

- min  $u_{ff,j}$ : -1560.7651.

The data type must be signed and it needs at least 11 bits for the integer part  $(log_2(1560) = 10.60733031)$ . After measuring the fractional part, the word width of signals is 24 bits with 12 bits of fraction, 11 bits of integer and 1 signed bit. According to Figure 5.3, the signal in fixed point is almost overlapping with the signal in double precision. The maximum difference in 10 iterations is around 1 um which is acceptable. Thus, the NOILC part is implemented with 24 bits signed fixed-point format.

Figure 5.3: The feedforward signal  $u_{ff,j}$  with different data types

#### 5.3 NOILC with Improved Matrix Multiplication

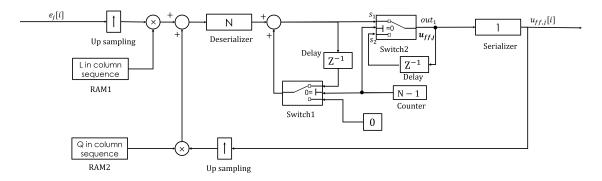

To construct the improved model described in Section 4.4.2 in MATLAB Simulink, two RAMs are required to store the elements of matrices  $\mathbf{L}$  and  $\mathbf{Q}$ . Two Product [13] components are utilized as multipliers. An adder is followed by the multipliers outputting the sum of products. A Deserializer1D described in Section 5.2.1 is utilized as a buffer to convert the one-dimensional sum to a N by 1 vector. Two Switch [15] components, an Adder [3], a UnitDelay [16] for storing the sum of all computed column products, a Counter [8] and a Constant 0 [7] constitute a for loop for the accumulation of all the column products in one iteration. The output of the loop is the final result  $\mathbf{u}_{\mathbf{f},\mathbf{j}}$ . The loop initializes the storage as zero at the start of each iteration, making sure that the values in the previous iteration would not affect the calculation in the current iteration. The vector  $\mathbf{u}_{\mathbf{ff},\mathbf{j}}$  is converted into one-dimensional signal  $u_{ff,j}$  by the Serilizer1D after downsampling. The signal  $u_{ff,i}$  is added to the control signal before the plant and multiplied with elements in Q in the next iteration. It is worth noting that MATLAB Simulink does not allow the interaction of two signals with different sample rates, such as addition and multiplication, otherwise, MATLAB reports errors. If all of these signals have a relationship and their sample rates vary, the sampling rates in Simulink must be altered until they are constant. Thus, two upsampling components and one downsampling component are used to ensure that the output signal has the same sampling frequency as the input signal.

Figure 5.4: Diagram of NOILC implementation with improved method

#### 5.4 Matrix Multiplication Utilization Test