## MASTER

Automatic target-specific code-generation from Simulink to composable multi-core platforms

Xiao, Liyin

Award date: 2021

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Electrical Engineering Electronic Systems Research Group

## Automatic target-specific code-generation from Simulink to composable multi-core platforms

Master Thesis Preparation Report

Liyin Xiao

Supervisors: Dr. Dip Goswami Mojtaba Haghi

1.0 version

Eindhoven, August 2021

## Abstract

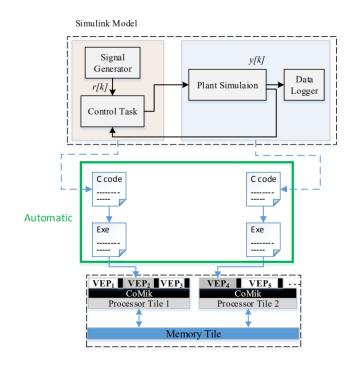

This thesis provides the implementation of feedback control applications which are designed in Simulink model-based environment. The targeted embedded platform for implementation is CompSOC, a predictable and composable system-on-chip. Simulink provides an Embedded coder which can automatically generate the code of a model-based simulation. Then a part or the whole of the simulation is uploaded and executed on CompSOC platform. The target-specific simulations are either processor-in-the-loop or hardware-in-the-loop simulations.

The purpose of this study is to build an automatic code generation tool targeting the predictable and composable multi-core platforms. To this aim, the generated code should be compiled to an executable which has real-time temporal behavior. It also should be able to be divided to separate executables where each part is executed on a separate core of the platform. PIL is a simulation method which compiles the generated code from the feedback control model and then upload and run the code on the embedded platform. HIL or external mode simulation is a method which is used in the development and testing of control systems with complex operations. To implement PIL and external mode simulations on the embedded platform successfully, A framework in Simulink environment is proposed to enable automatic code-generation, compile and execution on the targeted embedded platform.

# Preface

I would like to extend my deepest gratitude to my head supervisor Dip Goswami for his patience and thorough feedback on my thesis. Without his consistent and illuminating instruction, this thesis could not have reached its present form. I shall extend my thanks to my project tutor Mojtaba Haghi for all his kindness and help. He is a patient person who led me into the world of research. I would also like to thank my parents. Without their constant encouragement this work may never have been finished.

# Contents

| ontents                                                                                                                                                                                                                                                                                                                                                                         | $\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of Figures                                                                                                                                                                                                                                                                                                                                                                   | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Introduction         1.1       Composable Multi-core Platform         1.2       Problem Definition                                                                                                                                                                                                                                                                              | <b>1</b><br>2<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The Composable multi-core platform2.1Virtual processors2.2TDM schedule policy on CompSOC                                                                                                                                                                                                                                                                                        | <b>4</b><br>4<br>4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIL and external mode simulations         3.1       Development environment         3.1.1       Hardware         3.1.2       Software                                                                                                                                                                                                                                           | <b>6</b><br>6<br>6<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2       Control application                                                                                                                                                                                                                                                                                                                                                   | 7<br>7<br>9<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3       PIL Simulations         3.4       HIL Simulations         3.5       Simulink model and code generation         3.5.1       Simulink Model         3.5.2       Code Generation                                                                                                                                                                                         | 9<br>9<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Single-Core simulations implementation         4.1       Control Design and Implementation         4.2       As-fast-as-possible Scheduling         4.3       Real-time scheduling                                                                                                                                                                                              | <b>15</b><br>15<br>16<br>17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Automation for multi-core implementation         5.1       The multi-core scheduling         5.2       The shared memory block         5.2.1       To the shared memory         5.2.2       From the shared memory         5.3       Choose specific tile and partition slot         5.4       The hexFile         5.5       CaseI: model-based controller and hard-coded plant | <b>19</b><br>19<br>20<br>21<br>22<br>23<br>24<br>25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                 | st of Figures         Introduction         1.1 Composable Multi-core Platform         1.2 Problem Definition         The Composable multi-core platform         2.1 Virtual processors         2.2 TDM schedule policy on CompSOC         PIL and external mode simulations         3.1 Development environment         3.1.1 Hardware         3.1.2 Software         3.2 Control application         3.2.1 State-Space Model         3.2.2 Considered cases         3.2.3 Discrete State-Space Model         3.2.4 HIL Simulations         3.5 Simulink model and code generation         3.5.1 Simulink Model         3.5.2 Code Generation         3.5.3 Code generation with Real-Time Workshop         Single-Core simulations implementation         4.1 Control Design and Implementation         4.2 As-fast-as-possible Scheduling         4.3 Real-time scheduling         4.3 Real-time scheduling         5.1 The multi-core scheduling         5.2 The shared memory         5.2.1 To the shared memory         5.2.2 From the shared memory         5.2.3 Choose specific tile and partition slot         5.4 The hexFile |

### CONTENTS

| 6  | 6.1<br>6.2 | erimental Results         Single core implementation         Automated multi-core integration         Results and Analysis         6.3.1 | $\begin{array}{c} 29\\ 30 \end{array}$ |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 7  | 7.1        | Conclusions and future plan<br>Conclusion                                                                                                |                                        |

| Bi | bliog      | graphy                                                                                                                                   | 38                                     |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$                                         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{1}{2}$                                                                     |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| $2.1 \\ 2.2$                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\frac{4}{5}$                                                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11       | The motion system       The feedback control model in Simulink environment       1         The feedback control model in Simulink environment       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $     \begin{array}{c}       1 \\       2 \\       3 \\       3     \end{array} $ |

| $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ \end{array} $ | 2-DOF controller configuration       1         As-fast-as-possible Scheduling       1         The naive composition of rt_OneStep       1         The specific TLC code and its corresponding generated embedded code for rt_OneStep       1         The composition of new rt_OneStep       1         The specific TLC code and its corresponding generated embedded code for rt_OneStep       1         The specific TLC code and its corresponding generated embedded code for realtime       1         The specific TLC code and its corresponding generated embedded code for realtime       1         TDM schedule       1 | .6<br>.6<br>.7<br>.7                                                              |

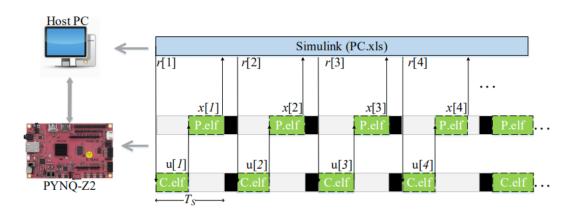

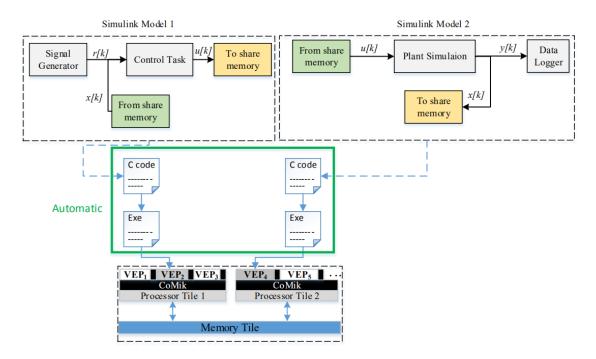

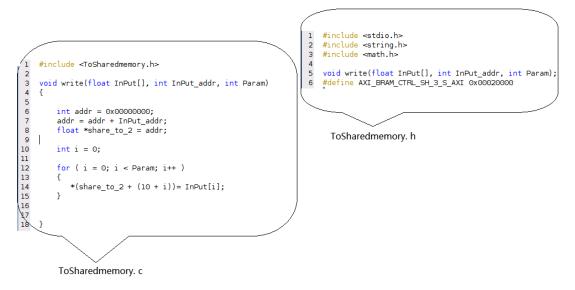

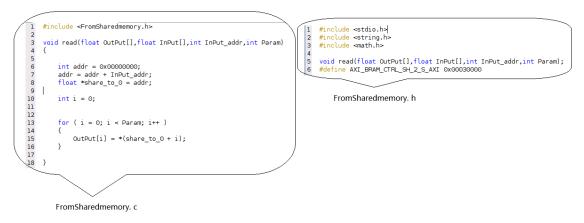

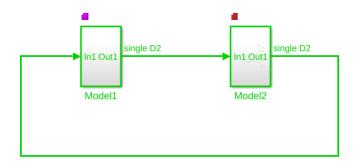

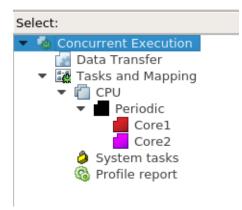

| 5.12<br>5.13<br>5.14                                                              | The multi-core scheduling1The third level of automation for multi-core code generation.2legacy write2ToSharedMemory2ToSharedmemory block2legacy read2FromSharedMemory2FromSharedmemory block2System target file2Configuration Parameters dialog box2runAvrDude(hexFile)2Control task2Plant simulation2Hardware architecture2                                                                                                                                                                                                                                                                                                     |                                                                                   |

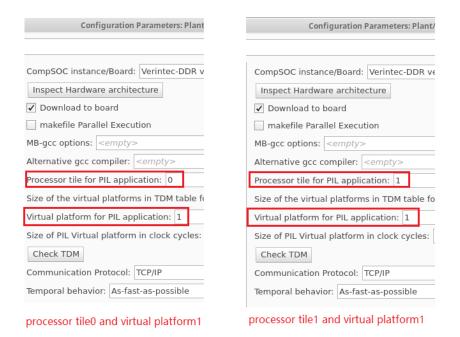

| $5.17 \\ 5.18 \\ 5.19$                                                                             | The plant model    2      Processor tile and virtual platform    2      External mode configuration1    2                                    |                  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|

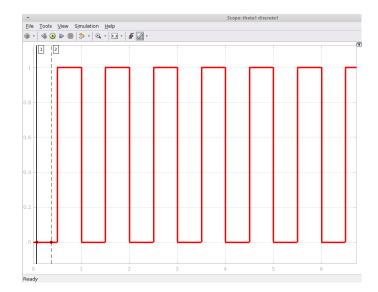

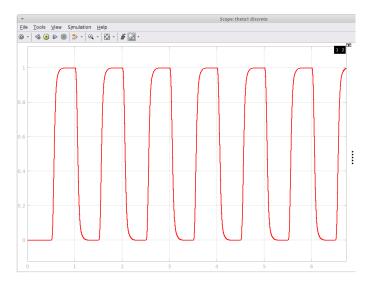

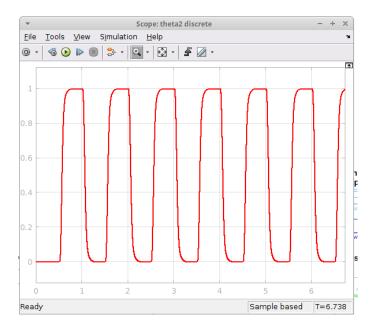

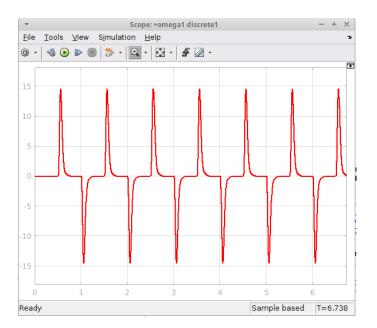

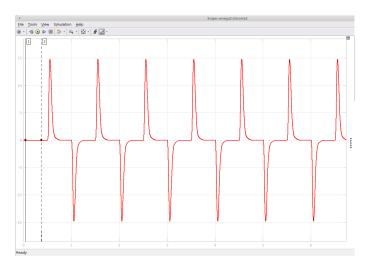

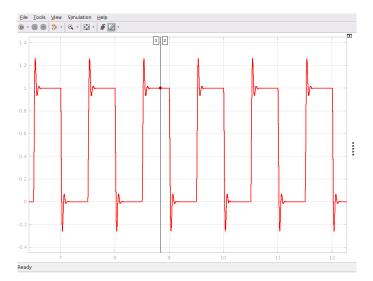

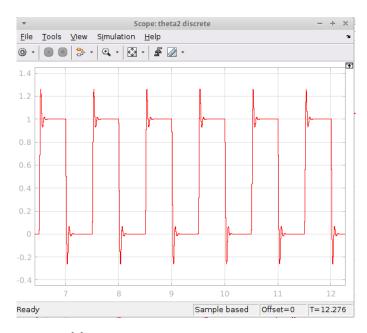

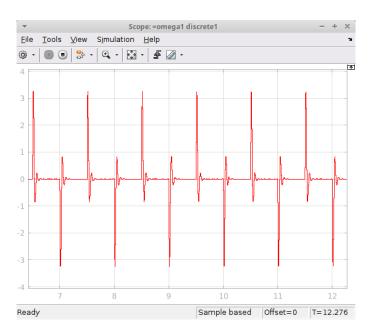

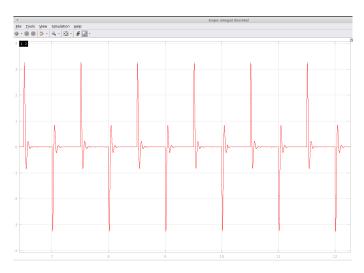

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \end{array}$ | Pulse signal input                                                                                                                           | 1<br>1<br>2<br>2 |

| 7.1<br>7.2<br>7.3                                                                                  | The final level of automation for multi-core code generation3The model is partitioned to execute concurrently3Multicore target architecture3 | -                |

# Chapter 1 Introduction

Nowadays, the implementation of digital control applications on embedded platform became a hot research topic since embedded implementation causes several uncertainty in stability and performance. Embedded implementation is widely used in many industrial topics such as aircraft autopilots, mass-transit vehicles, oil refineries, paper-making machines, and countless electromechanical servomechanisms[1].

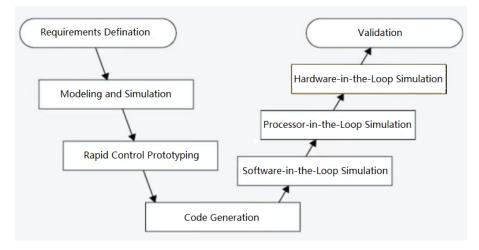

The process of design and implementation of a digital controller consists of specific steps. Figure 1.1 demonstrates a V-step model of these steps. The control design usually starts from model-in-the-loop (MIL) simulations in model-based simulation environments. In this step the controller is designed in a way to verify control performance requirements. The next step is called processor-in-the-loop (PIL) which has a non real-time nature. In such simulation, the designed controller (and possibly the model of the system under study) is executed on the embedded platform. This simulation enables the designer to verify the functional correctness of control code while executed on the platform. This step consists of platform-specific code generation for the control application, uploading and execution of the code on the platform, and the measurement of the execution times of different tasks. The final step of the implementation is called the hardware-in-the-loop (HIL). In this step, a real-time simulation verifies the temporal behavior of the controller on the platform in aspects such as real-time execution, periodicity, interruptions with other applications on the platforms and so on.

Figure 1.1: V-steps of Model

Embedded implementation of feedback control applications presents several challenges in terms of stability and performance [2]. In the controller design phase, a common assumption is that control tasks/software execute periodically, sequentially and without jitter. On widely used platforms

such as Raspberry Pi, dSPACE and arduino, strictly periodic, jitter-free execution is difficult to achieve due to interference from system tasks with other applications that share platform resources. The tailored embedded platforms for real-time applications are interesting targets for control applications [5]. These platforms offer properties such as determinism in execution times and composability in multi-application scenarios (which guarantees interference free execution of applications). These properties guarantee periodic and jitter-free execution of the control applications. In this thesis we focus on developing a implementation framework for such platforms and specifically on a certain platform called CompSOC. Before we continue further, we first describe the platform.

## 1.1 Composable Multi-core Platform

The embedded platform used in this project is called CompSOC[6] which is designed for executing multiple embedded applications. By using Time Division Multiplexing arbitration (TDM), this platform meets the requirements of predictability and composability, which guarantee noninterference execution for feedback control applications[5]. For this reason, CompSOC platform is chosen for the control application.

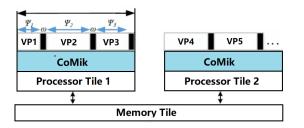

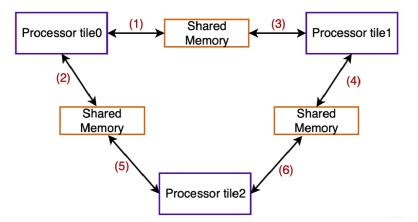

The Figure 1.2 shows the composition of CompSOC platform[5] which is a tile-based architecture. Each tile contain its own processor with unique data memory (DMEM) and instruction memory (IMEM). As a result, the two processor tiles can access to each other using Direct Memory Access (DMA) through its communication memory (CMEM).

TDM scheduling policy on CompSOC guarantees an isolated and non-interference implementation for each application since this platform uses a predictable and composable micro-kernel (CoMiK). This kernel creates multiple virtual processors (VPs) and each VP uses part of hardware resources. Under TDM scheduling manner, the utilization of these VPs will not affect each other. Therefore, the platform is composable and achieves real-time performance. Figure 1.2 shows the TDM scheduling with three partition slots on the first tile.

Figure 1.2: The composition of CompSoC platform

## 1.2 **Problem Definition**

In this project, we present an HIL framework for model-based simulations targeting composable multi-core platforms. The framework is an add-on code-generation tool to Simulink [6] environment. The framework enables the designer to start from a model-based simulation environment (Simulink) to complete all the steps of the V-model (which are MIL, PIL, and HIL) within the same environment.

The framework is able to generate the target-specific code for both PIL and HIL simulations, build an executable out of the generated code and upload it on the platform. Since the platform is multi-core and is able to run a number of applications simultaneously, the framework enables to choose the specific core and its scheduling, on which the simulation will execute.

The goals of this project is to develop an HIL framework which has the following features:

- It automatically generates the target-specific HIL code for FPGA-based embedded platform CompSOC from any Simulink models (www.mathworks.com).

- It automatically uploads and executes HIL codes on the platform either with a real-time or *as-fast-as-possible* timing fashion.

- It allows for online data logging and parameter tuning while the simulation is running on the platform.

- It Enables the designer to specify the scheduling of the targeted core on the platform.

- It allows the user to divide a single simulation to different tasks and execute them on different cores of the platform.

The rest of this report is organized as the following: Chapter 2 discusses the composable multi-core platform, Chapter 3 describes the PIL and external mode simulations . Chapter 4 indicates single-core simulations implementation. Chapter 5 describes automation for multi-core implementation. Chapter 6 gives the Experimental Results. Chapter 7 imagines the future plan.

## Chapter 2

# The Composable multi-core platform

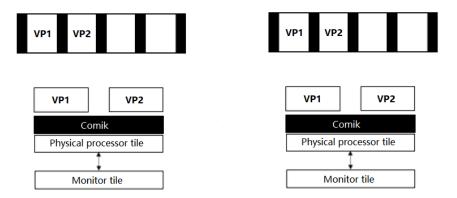

The embedded platform considered in this project is CompSOC which has a tile-based architecture. Figure 2.1 illustrates a possible composition of CompSOC, which normally consists of processor tiles and monitor tiles. The processor tile is mainly made up of a MicroBlaze soft-core processor which plays a role in processing.

Figure 2.1: High-level overview of a possible composition of CompSOC

## 2.1 Virtual processors

As illustrated in Figure 2.1, processor tiles consist of a physical Microblaze processor that has an instruction memory (imem) and a data memory (dmem). These memory are tightly coupled. Since real-time applications can share the processor resources with other applications, a composable and predictable micro-kernel is introduced to create multiple virtual processors (VPs) which can be considered as processing resources [9]. CoMik uses TDM schedule policy to divide the processor into TDM partition slots. Each VP takes up part of the processing resource available on the physical processor that is allocated in a TDM schedule policy.

## 2.2 TDM schedule policy on CompSOC

A periodic time-division-multiplexing (TDM) policy is applied on all processors aiming at achieving real-time performance with cycle accurate time division. This schedule policy help to maintain the

properties of predictability and composability on this platform. Because each VP utilizes part of the processing resource, they will not affect each other using TDM schedule policy. Therefore, the composability on this platform is guaranteed. The application which executed on the platform will be allocated to a single partition slot and waiting for starting a new CoMiK slot. Predictability is also a vital property which is needed to be able to guarantee that worst-case performance and deterministic execution times are met for real-time applications.

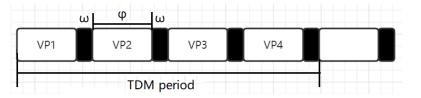

The TDM frame include two kinds of slots, the partition  $slots(\varphi)$  and the CoMik  $slots(\omega)$ . Figure 2.2 illustrates a possible schedule of one TDM period with four CoMik slots and four partition slots which could be different.

Figure 2.2: The TDM schedule policy

In this instance, the TDM period could be calculated as below:

$$P_{TDM} = \sum_{i=1}^{N} \varphi_i + N \times \omega.$$

where N represents the number of slots.  $\varphi_i$  and  $\omega$  represent the clock cycle of different partition slots and CoMik slots. TDM scheduling is achieved by a periodic interrupt that indicates a context swap between two different virtual processors. Then CoMik's interrupt routine is considered to execute the context swap, which preserve the previous VP's related context and arrange the next VP[5].

## Chapter 3

# PIL and external mode simulations

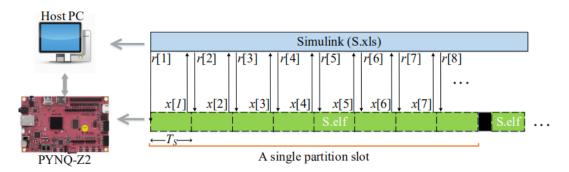

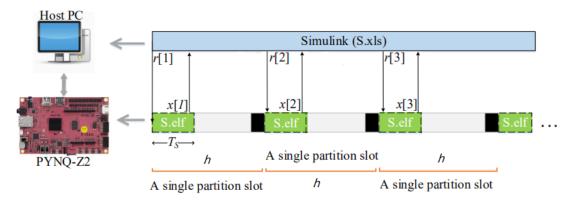

This chapter explores the inner workings of the MATLAB-CompSOC integration tool and Simulink code generation. This includes an introduction to how this tool handles control tasks, and how Simulink generates code from its model diagrams.

## 3.1 Development environment

### 3.1.1 Hardware

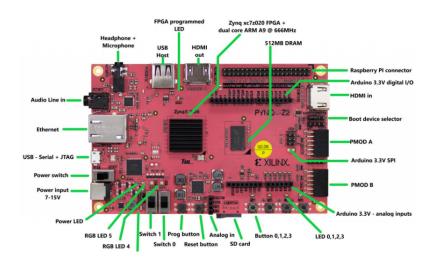

The FPGA board chose in this project is PYNQ-Z2 which is cheap, small, and requires minimal power consumption. This board is based on Xilinx Zynq System on Chip (SoC) and designed to support an open-source framework PYNQ ( (Python Productivity for Zynq). The board uses the 650MHz dual-core Cortex-A9 processor by ARM which, importantly, includes 1G Ethernet and USB 2.0 High-bandwidth peripheral controllers that can be connected with PC through Ethernet or USB[7]. Figure Figure 3.1 shows the composition of this board. This allows generated codes to run on the hardware platform.

Figure 3.1: PYNQ board overview

### 3.1.2 Software

The system is modeled in Matlab R2018b, one of the most common tools for mathematical and technical calculations.

## **3.2** Control application

#### 3.2.1 State-Space Model

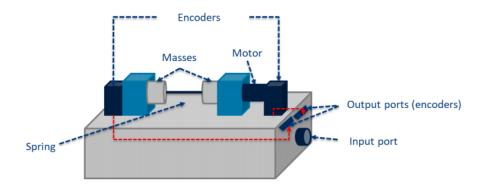

The control application considered in this project is a dual rotary fourth-order single input multiple output (SIMO) motion system as depicted in Figure 1.2. It consists of two masses which are connected by a spring. In addition, there is a motor as the input to drive the first mass. The attached sensors are used to measure the angular position of both masses.

Figure 3.2: The motion system

Based on the description above, the equation of corresponding state-space representation is given below[7]:

$$\dot{X(t)} = AX(t) + BU(t), \tag{1}$$

Y(t) = CX(t),

where constant matrices A, B and C denote the state matrix, the input matrix and the output matrix respectively. X(t) is the state array of the system and U(t) is the control input and Y(t) is the output of the system. System states X consist of the velocity of two masses and the displacement of two masses:  $X(t) = [\theta_1, \theta_2, \omega_1, \omega_2]^t$ ,

The differential equations for the system are given as

...

$$J_1 \ddot{\theta_1} = K_m i_m - k(\theta_1 - \theta_2) - d(\dot{\theta_1} - \dot{\theta_2}) - b(\dot{\theta_1} - \dot{\theta_2})$$

$$J_2 \ddot{\theta_2} = -k(\theta_2 - \theta_1) - d(\dot{\theta_2} - \dot{\theta_1}) - b(\dot{\theta_2} - \dot{\theta_1})$$

These equations can be simplified to :

$$J_1\dot{\theta_1} = K_m i_m - k(\theta_1 - \theta_2) - (d+b)(\dot{\theta_1} - \dot{\theta_2})$$

(3.1)

$$J_2 \ddot{\theta}_2 = k(\theta_1 - \theta_2) + (d+b)(\dot{\theta}_1 - \dot{\theta}_2)$$

(3.2)

Now, to derive the state-pace model of the system, we consider the states vector as

$$x = [\theta_1, \theta_2, \omega_1, \omega_2]$$

where  $\omega_1 = \dot{\theta_1}$  and  $\omega_2 = \dot{\theta_2}$

Thus, we define our states as :

$$x_1 = \theta_1$$

$$x_2 = \theta_2$$

$$x_3 = \omega_1 = \dot{\theta_1}$$

$$x_4 = \omega_2 = \dot{\theta_2}$$

$$\dot{x_1} = x_3$$

$$\dot{x_2} = x_4$$

$$\dot{x_3} = \ddot{\theta_1} = \frac{K_m i_m}{J_1} - \frac{k}{J_1} (\theta_1 - \theta_2) - \frac{(d+b)}{J_1} (\dot{\theta_1} - \dot{\theta_2})$$

$$\dot{x_4} = \ddot{\theta_2} = \frac{k}{J_2} (\theta_1 - \theta_2) + \frac{(d+b)}{J_2} (\dot{\theta_1} - \dot{\theta_2})$$

Substituting above values in equations (3.1) and (3.2), we get,

$$J_1 \ddot{x_1} = K_m i_m - k(x_1 - x_2) - (d+b)(x_3 - x_4)$$

(3.3)

$$J_2 \ddot{x_2} = k(x_1 - x_2) + (d+b)(x_3 - x_4)$$

(3.4)

We also know that,

Input to the system  $= u = i_m$  and, Output of the system  $= y = x_1$

Thus, we can now write the state-space model for continuous time as,

$$\dot{x} = Ax + Bu$$

y = Cx

$$\implies \begin{bmatrix} \dot{x_1} \\ \dot{x_2} \\ \dot{x_3} \\ \dot{x_4} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ -\frac{k}{J_1} & \frac{k}{J_1} & -\frac{(d+b)}{J_1} & \frac{(d+b)}{J_1} \\ \frac{k}{J_2} & -\frac{k}{J_2} & \frac{(d+b)}{J_2} & -\frac{(d+b)}{J_2} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ x_4 \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ \frac{k_m}{J_1} \\ 0 \end{bmatrix} u$$

(3.5)

and for output,

$$\implies y = \begin{bmatrix} 1 & 0 & 0 & 0 \end{bmatrix} x \tag{3.6}$$

and matrix A, B, C can be expressed as follows,

$$A = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ -7.08 \times 10^4 & 7.08 \times 10^4 & -1.1 \times 10^6 & 1.1 \times 10^6 \\ 7.08 \times 10^4 & -7.08 \times 10^4 & 1.1 \times 10^6 & -1.1 \times 10^6 \end{bmatrix},$$

(2)

$$B = \begin{bmatrix} 0 \\ 0 \\ 1.173 \times 10^4 \\ 1 \end{bmatrix},$$

(3)

$$C = \begin{bmatrix} 1 & 0 & 0 & 0 \end{bmatrix}, \tag{4}$$

#### 3.2.2 Considered cases

The calculated values for K and F as described in the table 3.1.

| Gains used in u[k]   |       | Values             |

|----------------------|-------|--------------------|

| 5*Feedback Gain $K$  | $k_1$ | 5.822990811552409  |

|                      | $k_2$ | -5.822992246204845 |

|                      | $k_3$ | -0.180024323629381 |

|                      | $k_4$ | 0.180023422504676  |

|                      | $k_5$ | 0.516351924157763  |

| Feedforward gain $F$ | -     | 0.0000014346524431 |

Table 3.1: Calculated values of Feedback Gain K and Feed-forward gain F

#### 3.2.3 Discrete State-Space Model

Since the embedded platform usually works at discrete time. Hence, the continuous state-space model should be discretized to fit for the sampling period of the controller. The discrete state-space model can be defined as:

$$x(k+1) = \phi x(k) + \Gamma u(k), \tag{5}$$

$$y(k) = Cx(k),$$

where,

$$\phi = e^{Ah}, \Gamma = \int_0^h e^{As} B ds, \tag{6}$$

and h is the sampling period between two samples. Our control task is to design u[k] which makes y[k] follow r[k].

## 3.3 PIL Simulations

PIL is a simulation method which compiles the generated code from the feedback control model and then upload and run the code on the embedded platform. In this control application, the digital controller is realized by a FPGA-based embedded control system.Because traditional model-based simulation is not often sufficient to exactly capture control dynamics. This method increases the realism of the simulation and provide communication with specific hardware platforms. In PIL the target platform is not a real time environment and the communication with the external embedded platform is given by using specific functions installed in a simulation integrated environment.

The progress from model-based simulation to implementation on an platform requires developers to communicate the computer platform with the aimed embedded hardware. The targetspecific object code generated in the host PC and is then downloaded to the target embedded platform for compiling and execution. The simulation tool in Simulink environment, running on the host PC, then communicates with the downloaded software.

## 3.4 HIL Simulations

HIL simulation is a method which is used in the development and testing of control systems with complex operation. With HIL simulation the physical part of the control system is replaced by a simulation, using a mathematical model that fully describes the important dynamics of the physical model. HIL simulation can be performed directly with Real-Time Workshop, which using a computer as a host and a target in simulation.

In this project, both model and controller are compiled and then upload and run the generated code on the embedded platform.

## 3.5 Simulink model and code generation

The control application is built in Simulink environment according to the previously shown mathematical model. The code generation is done with Real-Time Workshop, which generates the files that are uploaded and executed on the platform.

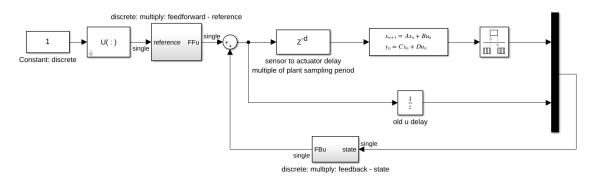

## 3.5.1 Simulink Model

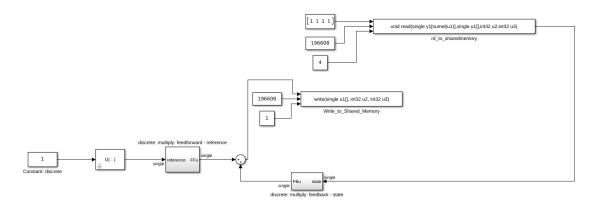

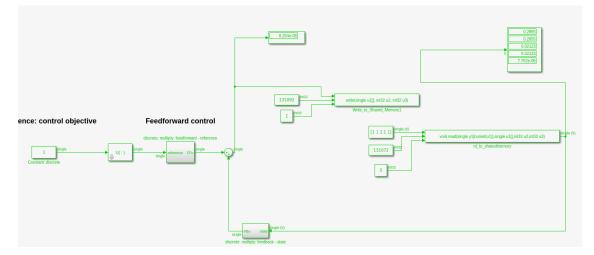

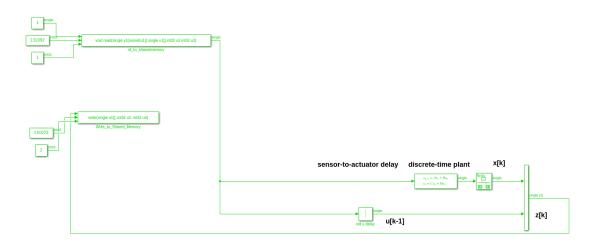

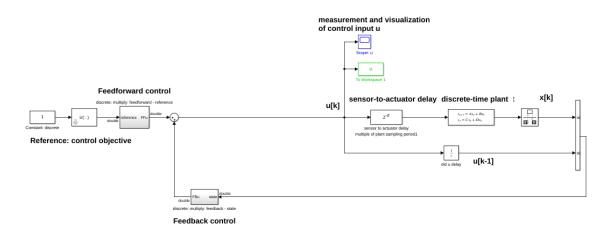

Implementing the control application (Eq. 5 and Eq. 6) in Simulink with reference r[k] and states x[k] as inputs, and resulted y[k] and new states x[k] as output, this simulink model can be seen in Figure 3.3:

Figure 3.3: The feedback control model in Simulink environment

## 3.5.2 Code Generation

Code generation is a complex process that involves a large number of intermediate files. The Simulink environment provides a Embedded coder tool which can transform a Simulink model to a targeted platforms' programming code such as C/C++. [8]. After the code is generated, the user can build and run the compiled code by clicking the Build icon. The code generator builds the executable and generates the Code Generation Report.

In order to generate code successfully, the first step is to specifying code generation settings in the Configuration Parameters dialog box. Next is to choose the appropriate solver and code generation target, and checking the model configuration for execution efficiency. The process starts with the user's Simulink model which is converted to the intermediate Real Time Workshop (RTW) document by SFunctions. The RTW document is then converted to C using Target Language Compiler (TLC) files. In Figure 3.4 the process and associated file types are enumerated.

| Simulink | SFunctions | Real-Time | Code       | Embedded |

|----------|------------|-----------|------------|----------|

| Model    |            | Workshop  | Generation | Code     |

| .mdl     | .mex       | .rtw      | .tlc       | .c       |

Figure 3.4: Code generation process

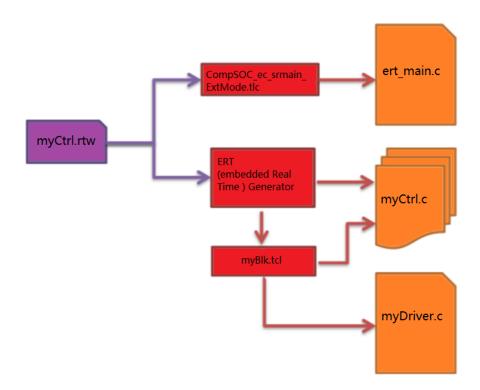

The Target Language Compiler (TLC) is a tool originally developed for the Matlab Real-Time Workshop. It then became the integral part of Matlab Embedded Coder. It enables the user to generate embedded C code directly from Simulink model via using the complete RTW document. This embedded code consists of three groups: entry point, tasks, and auxiliary. The transition from the RTW document to embedded C can be seen in the flowchart Figure 3.5.

Figure 3.5: Code generation from Real-Time Workshop document

The Embedded Real Time (ERT) generator is a particular set of TLC files specialized to generate codes targeting embedded platforms. It is always used for creating the tasks. This generator calls related TLC files for each block described in the RTW document to generate its specific embedded code. The generated file is a set of files that can be built into an executable. The executable can then be uploaded and executed on the embedded platform. They have the same name as the initial Simulink model, but with a different suffix and file extension [9].

## 3.5.3 Code generation with Real-Time Workshop

A Simulink model has been built, then the next is to generate the code for the feedback control application. Code generation ensures that the code is generated in a effective way, in order to cope with memory space and speed of the embedded platform.

The Code Generation Options is found under C/C++ Code in the Code menu. Clicking this button will open the Configuration Parameters dialog. A system target file is chose,  $CompSOC\_ec.tlc$ , with the target set for CompSOC embedded platform. The language which is uploaded and executed on the platform is set to C. This can be seen in the Figure 3.6.

| ▼ Configu                                                                                                       | ration Parameters: assig                                             | nment1_2019_Simulink/Configuration (Active) | - | + | × |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------|---|---|---|

| <b>Q</b> Search                                                                                                 |                                                                      |                                             |   |   |   |

| Solver<br>Data Import/Export<br>Math and Data Types<br>Diagnostics<br>Hardware Implementat<br>Model Referencing | Target selection<br>System target file:<br>Language:<br>Description: | CompSOC_ec.tlc Browse                       | · |   | • |

Figure 3.6: Configuration Parameters

The option for solver type is Fixed-step solvers which solve the model at fixed time intervals

from the start time to the stop time of the simulation. The size of time intervals is set in the Fixed-step size option which determines the fundamental sample time. Figure 3.7 depicts these options.

| ▼ Config                                                      | uration Parameters: assignment1_2019_Simulink/Configuration (Active) - | + × |

|---------------------------------------------------------------|------------------------------------------------------------------------|-----|

| <b>Q</b> Search                                               |                                                                        |     |

| Solver                                                        | Simulation time                                                        |     |

| Data Import/Export<br>Math and Data Types                     | Start time: 0.0 Stop time: inf                                         |     |

| <ul> <li>Diagnostics</li> <li>Hardware Implementat</li> </ul> | Solver selection                                                       |     |

| Model Referencing<br>Simulation Target                        | Type: Fixed-step    Solver: auto (Automatic solver selection)          |     |

| <ul> <li>Code Generation</li> <li>Optimization</li> </ul>     | ▼ Solver details                                                       |     |

| Report<br>Comments                                            | Fixed-step size (fundamental sample time): 0.00001                     |     |

Figure 3.7: Solver diagram

In the interface dialog, the external mode option is selected because the simulation use the I/O drivers to communicate with the embedded platform, the application stores contiguous response data in memory accessible to Simulink until a data buffer is filled. This can be seen in Figure 3.8.

| <b>Q</b> Search                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Solver<br>Data Import/Export<br>Math and Data Types<br>Diagnostics<br>Hardware Implementation<br>Model Referencing<br>Simulation Target | Software environment         Code replacement library:         None         Shared code placement:         Auto         Support:       Ifoating-point numbers         Image: Imag | •             |

| <ul> <li>Code Generation</li> <li>Optimization</li> </ul>                                                                               | Code interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| Report<br>Comments<br>Symbols                                                                                                           | Code interface packaging: Nonreusable function<br>Remove error status field in real-time model data structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •             |

| Custom Code<br>Interface                                                                                                                | Data exchange interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| Code Style<br>Verification<br>Templates<br>Code Placement                                                                               | Array layout:     Column-major       External functions compatibility for row-major code generation:     error       Generate C API for:     Column-major                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>~</b>      |

| Data Type Replacement<br>CompSOC options<br>Coverage                                                                                    | signals parameters states root-level I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| Coverage                                                                                                                                | ASAP2 interface  External mode  External mode configuration  Transport layer: tcpip  MEX-file name: ext_comm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

|                                                                                                                                         | MEX-file arguments: '10.42.0.229' 1 9876                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

|                                                                                                                                         | <u>O</u> K <u>Cancel H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>A</u> pply |

Figure 3.8: Interface diagram

The *ert\_code\_template.cgt* file is chosen for both header and source templates. File customization template is used to customize the generated code with a CFP template file.

The *CompSOC\_ec\_file\_process.tlc* file is used in this thesis to call a code template API to emit the code into specified sections of generated source and header files. This can be seen in Figure 3.9.

| ▼ Config                                                      | guration Parameters: assignment1_2019_Simulink/Configuration (Active) - + >                  |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>Q</b> Search                                               |                                                                                              |

| Solver                                                        | Code templates                                                                               |

| Data Import/Export<br>Math and Data Types                     | Source file template: ert_code_template.cgt Browse Edit                                      |

| <ul> <li>Diagnostics</li> <li>Hardware Implementat</li> </ul> | Header file template: ert_code_template.cgt Browse Edit                                      |

| Model Referencing                                             | Data templates                                                                               |

| Simulation Target<br>Code Generation                          | Source file template: ert_code_template.cgt Browse Edit                                      |

| Optimization                                                  | Header file template: ert_code_template.cgt Browse Edit                                      |

| Report<br>Comments                                            | Custom templates                                                                             |

| Symbols<br>Custom Code                                        | File customization template:         CompSOC_ec_file_process.tlc         Browse         Edit |

| Interface                                                     | Generate an example main program                                                             |

| Code Style                                                    |                                                                                              |

Figure 3.9: Templates diagram

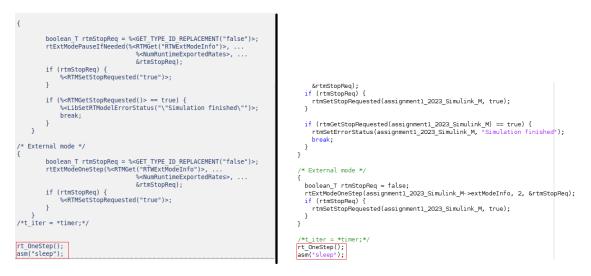

Previously the  $CompSOC\_ec\_file\_process.tlc$  file is chose to call a code template. From Figure 3.10, the extra file  $CompSOC\_ec\_srmain\_ExtMode.tlc$  is used to generate the main file which is mean to generate the  $ert\_main.c$  file. This file is provided by Mathworks to be used as a basis for custom modifications, and for use in simulation.

```

CompSOC_ec_file_process.tlc 🗶 🕂

%% Create a simple main.

%if UseRTOS == 0

%if LibIsSingleRateModel() || LibIsSingleTasking()

%if ExtMode

%assign board = FEVAL("CompSOC_ec.Prefs.getBoard")

%%if (board != "mega") && (board != "mega2560")

&assign errTxt = "External Mode is supported on Mega/Mega2560 only (8kB RAM necessary)."

%%<LibReportError(errTxt)>

ssendif

%% We use extra file for main generation with External Mode

%include "CompSOC_ec_srmain_ExtMode.tlc"

%else

%% Simplified main generation w/o External Mode

%include "CompSOC_ec_srmain.tlc"

%endif

<FcnSingleTaskingMain()>

%else

%% For the moment, multitasking is not supported

%include "CompSOC_ec_srmain.tlc"

%<FcnSingleTaskingMain()>

%endif

```

Figure 3.10: The File customization template

Then the next step is to build the Code Generation Report by clicking the Build Model in the tool bar.

The generated report which shows in Figure 3.11 contains header and source-file for the feedback control application, definition files and the file  $ert\_main.c$  which is an example file for developing embedded applications. This file provides a basis for custom modifications, and for use in simulation.  $ert\_main.c$  is generated from  $CompSOC\_ec\_srmain\_ExtMode.tlc$  file which is modified by the customer. This can be seen in the next chapter.

| <b>*</b>                | Code Generatio                        | n Report – +                                          |

|-------------------------|---------------------------------------|-------------------------------------------------------|

| < 🔶 🧟 Find:             | 分 🕹 Match Case                        |                                                       |

| Contents                | Code Generat                          | ion Report for                                        |

| Summary                 | 'Empty sim33                          |                                                       |

| Subsystem Report        |                                       |                                                       |

| Code Interface Report   | Model Information                     |                                                       |

| Traceability Report     |                                       |                                                       |

| Static Code Metrics     | Author                                | young                                                 |

| Report                  | Last Modified By                      | root                                                  |

| Code Replacements       | Model Version                         | 1.180                                                 |

| Report                  | Tasking Mode                          | SingleTasking                                         |

| Coder Assumptions       | Configuration settings at tin         | ne of code generation                                 |

| Generated Code          | Code Information                      |                                                       |

| [-] Model files         | coue mornation                        |                                                       |

| Empty_sim33.c           | System Target File                    | CompSOC ec.tlc                                        |

| Empty_sim33.h           | Hardware Device Type                  | Custom Processor                                      |

| Empty_sim33_private.    | Simulink Coder Version                | 9.0 (R2018b) 24-May-2018                              |

| Empty_sim33_types.h     | Timestamp of Generated<br>Source Code | Wed Oct 7 12:00:50 2020                               |

| [-] Data files          | Location of Generated                 | /home/computation/TEST/Empty_sim33_CompSOC/           |

| Empty_sim33_data.c      | Source Code                           |                                                       |

| [+] Utility files (2)   | Type of Build                         | Model                                                 |

| [+] Interface files (3) | Memory Information                    | Global Memory: 818(bytes) Maximum Stack:<br>80(bytes) |

| Interface files (5)     | Objectives Specified                  | Unspecified                                           |

|                         |                                       | ОК Неір                                               |

Figure 3.11: Code Generation Report

## Chapter 4

# Single-Core simulations implementation

The integration tool provides the module  $ert\_main.c$  as a template example for developing embedded applications. It is provided as a basis for custom modifications, and for use in simulation. In our project,  $ert\_main.c$  is generated from  $CompSOC\_ec\_srmain\_ExtMode.tlc$  file.  $ert\_main.c$  contains two functions, the first one is  $rt\_OneStep$ , which is a timer interrupt service routine (ISR).  $rt\_OneStep$  calls MODEL\_STEP to execute processing for one clock period of the model. As provided, main function is useful in simulation only when it is modified for real-time execution.

## 4.1 Control Design and Implementation

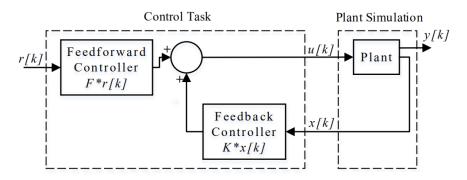

In this project, we will concentrate on the 2-DOF controller configuration presented in [8] and displayed in Figure 4.1. This controller can be defined as:

$$u(k) = Kx(k) + Fr(k), \tag{7}$$

where K represents feedback controller which aims to stabilize the outputs for the system based on an available process model, and F is in terms of feedforward controller which helps to improve the accuracy of the system output. According to Figure 4.1, the reference signal is known beforehand and its scaled velocity, acceleration enable a straightforward feedforward tuning.

Figure 4.1: 2-DOF controller configuration

## 4.2 As-fast-as-possible Scheduling