| MASTER                                                                 |

|------------------------------------------------------------------------|

| Exploring power gating in coarse grained re-configurable architectures |

|                                                                        |

| Carboni Munoz, Felipe A.                                               |

| Award date: 2020                                                       |

|                                                                        |

| Link to publication                                                    |

|                                                                        |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Mathematics and Computer Science Architecture of Information Systems Research Group

# Exploring power gating in coarse grained re-configurable architectures

ES - Master Thesis document

Felipe Carboni M. (0988340)

Supervisors:

ir. Jos Huisken Prof. dr. Kees Goossens Dr. ir. Pieter Harpe Prof. dr. Henk Corporaal

# Contents

| $\mathbf{C}_{0}$ | onter | ats                                              | ii |

|------------------|-------|--------------------------------------------------|----|

| 1                | Intr  | roduction                                        | 2  |

|                  | 1.1   | Re-Configurable Architectures                    | 3  |

|                  |       | 1.1.1 The CGRA                                   | 4  |

|                  |       | 1.1.2 CGRA-Blocks                                | 5  |

|                  | 1.2   | Project problem statement                        | 6  |

|                  |       | 1.2.1 Planning                                   | 7  |

| <b>2</b>         | Stat  | te of the art analysis                           | 8  |

|                  | 2.1   | Current trends in power gating                   | 9  |

|                  | 2.2   | Implementing a power gate circuit                | 10 |

|                  |       | 2.2.1 Sizing of a power gate                     | 11 |

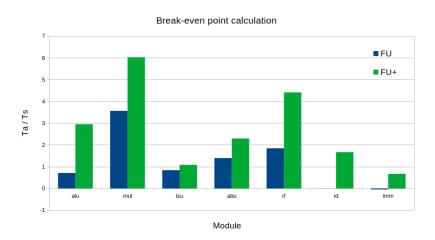

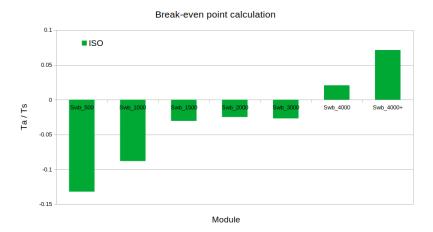

|                  |       | 2.2.2 Trade-offs and break-even point            | 12 |

|                  | 2.3   | Fine grained vs. Coarse grained                  | 15 |

|                  |       | 2.3.1 Fine-grained power gating                  | 15 |

|                  |       | 2.3.2 Coarse-grained power gating                | 16 |

|                  |       | 2.3.2.1 - Ring-based coarse-grained power gating | 17 |

|                  |       | 2.3.2.2 - Grid-based coarse-grained power gating | 17 |

| 3                | Met   | trics                                            | 18 |

|                  | 3.1   | Area overhead (AO)                               | 19 |

|                  |       | 3.1.1 Ring-based power switching                 | 19 |

|                  |       | 3.1.2 Column-based power switching               | 20 |

|                  |       | 3.1.3 "Checkerboard" power switching             | 21 |

|                  | 3.2   | Energy analysis                                  | 22 |

|                  | 3.3   | Performance                                      | 22 |

| 4                | Met   | thodology                                        | 24 |

|                  | 4.1   | Tested designs                                   | 25 |

|                  | 4.2   | Test groups                                      | 26 |

|                  |       | 4.2.1 Switchboxes                                | 26 |

|                  |       | 4.2.2 Functional units                           | 27 |

|                  |       | 4.2.3 Extended functional units                  | 27 |

|                  | 4.3   | First order power switch                         | 28 |

|                  | 4.4   | Synthesis workflow                               | 30 |

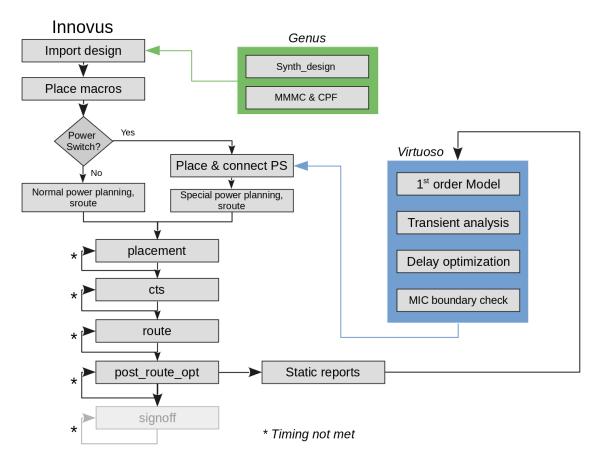

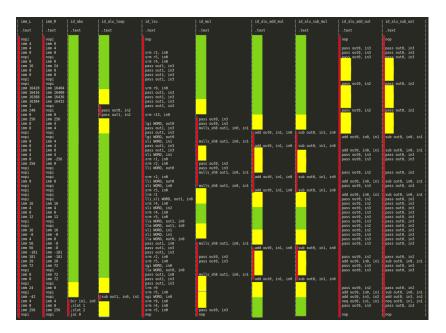

|                  |       | Back-end and testing workflow                    | 33 |

|                           | 4.6<br>4.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35<br>38                                                                                           |

|---------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 5                         | Exp        | perimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                 |

|                           | 5.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                 |

|                           | 5.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                 |

|                           | 5.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                                                 |

|                           | 5.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                                                                 |

|                           | 0.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                                                                 |

|                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                                                 |

|                           |            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                                                                                 |

|                           |            | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                                                 |

|                           | 5.5        | Dynamic power-gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                 |

|                           | 0.0        | 5.5.1 FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                 |

|                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                                                                                                 |

|                           | 5.6        | Static power gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                 |

|                           | 5.0        | Static power gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99                                                                                                 |

| 6                         | Con        | nclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55                                                                                                 |

|                           | 6.1        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                                                                                                 |

|                           | 6.2        | Closing remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58                                                                                                 |

|                           | 6.3        | Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58                                                                                                 |

| $_{ m Bi}$                | bliog      | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                                                 |

|                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

| Αı                        | open       | dices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                                                                                                 |

| Aı                        | _          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>64</b>                                                                                          |

| Aı                        | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                 |

| $\mathbf{A}_{\mathbf{l}}$ | _          | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66                                                                                           |

| A                         | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66<br>66                                                                                     |

| $\mathbf{A}_{\mathbf{I}}$ | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66<br>66<br>67                                                                               |

| Aı                        | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66<br>66<br>67<br>67                                                                         |

| $\mathbf{A}_{\mathbf{l}}$ | .1         | Some poower-analysis elements  Related work in power optimization techniques  .2.1 Active power  .2.1.1 Multi-supply Voltage Domains  .2.1.2 Transistor sizing  .2.1.3 Activity and structural modifications                                                                                                                                                                                                                                                                                                                                                                        | 65<br>66<br>66<br>67<br>67<br>68                                                                   |

| $\mathbf{A}_{\mathbf{I}}$ | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66<br>66<br>67<br>67<br>68<br>69                                                             |

| $A_1$                     | .1         | Some poower-analysis elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69                                                       |

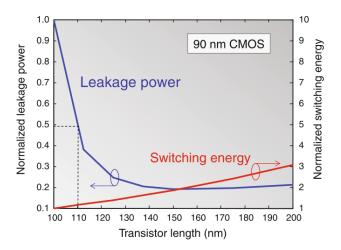

| $A_{l}$                   | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications 2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking                                                                                                                                                                                                                                                                                          | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70                                                 |

| $A_{J}$                   | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries                                                                                                                                                                                                                                                         | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70                                                 |

| $A_{J}$                   | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.2.3 Dynamic optimizations                                                                                                                                                                                                                          | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70<br>70                                           |

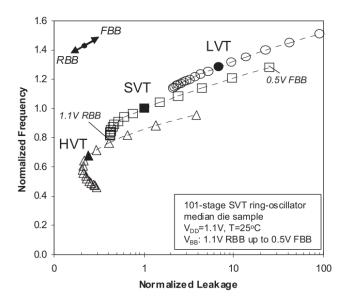

| Aj                        | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing                                                                                                                                                                                                           | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70<br>70<br>71                                     |

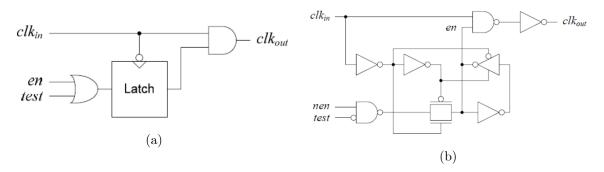

| A                         | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating                                                                                                                                                                                        | 65<br>66<br>66<br>67<br>68<br>69<br>70<br>70<br>71                                                 |

| $A_{j}$                   | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power  2.1.1 Multi-supply Voltage Domains  2.1.2 Transistor sizing  2.1.3 Activity and structural modifications  2.2 Static-power optimizations  2.2.1 Increasing channel length  2.2.2 Circuit stacking  2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations  2.3.1 Body biasing  2.3.2 Clock gating  2.3.3 Power gating                                                                                                                                                            | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70<br>70<br>71<br>71<br>73                         |

| $A_1$                     | .1         | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power  2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization                                                                                                                                     | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>73                         |

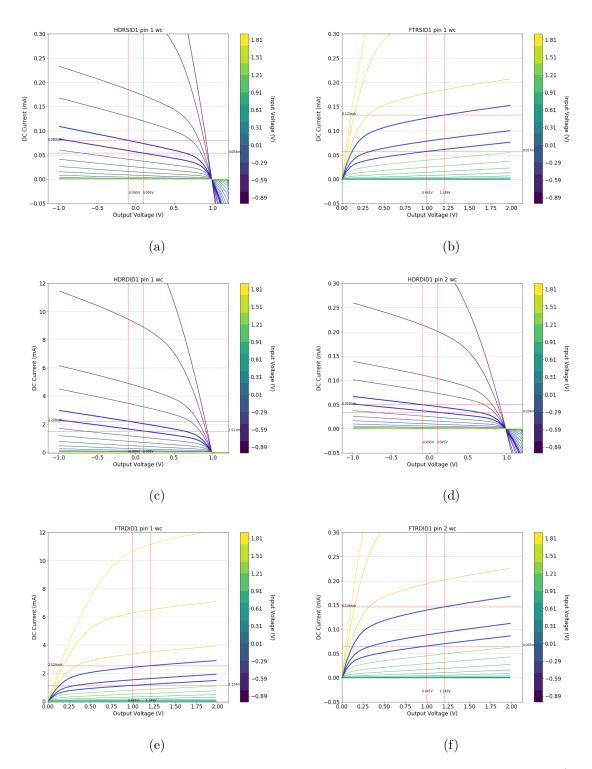

| $A_1$                     | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power  2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations  2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations  2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization  3.1 Current capacity                                                                                                             | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>73                         |

| $A_1$                     | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power  2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization  3.1 Current capacity  3.2 Leakage                                                                                                  | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>69<br>70<br>70<br>71<br>71<br>73<br>73<br>74<br>76       |

| $A_1$                     | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization  3.1 Current capacity 3.2 Leakage 3.3 Dimensions                                                                                     | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>73<br>74<br>76             |

| $A_1$                     | .1 .2      | Some poower-analysis elements  Related work in power optimization techniques  2.1 Active power  2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization  3.1 Current capacity 3.2 Leakage 3.3 Dimensions 3.4 Gate delay                                                                    | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>74<br>76<br>76             |

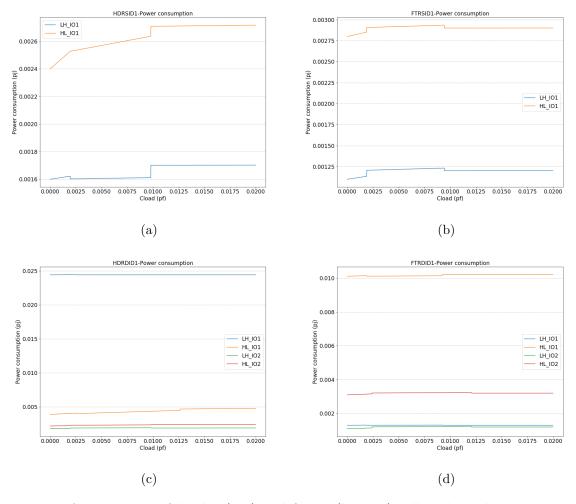

| $A_{\mathbf{j}}$          | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  2.1 Active power 2.1.1 Multi-supply Voltage Domains 2.1.2 Transistor sizing 2.1.3 Activity and structural modifications  2.2 Static-power optimizations 2.2.1 Increasing channel length 2.2.2 Circuit stacking 2.2.3 Multi-threshold libraries  2.3 Dynamic optimizations 2.3.1 Body biasing 2.3.2 Clock gating 2.3.3 Power gating  Power Switch characterization  3.1 Current capacity 3.2 Leakage 3.3 Dimensions 3.4 Gate delay 3.5 Switching power                                                  | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>73<br>74<br>76<br>76<br>76 |

| $A_{\mathbf{j}}$          | .1 .2      | Some poower-analysis elements Related work in power optimization techniques  .2.1 Active power .2.1.1 Multi-supply Voltage Domains .2.1.2 Transistor sizing .2.1.3 Activity and structural modifications  .2.2 Static-power optimizations .2.2.1 Increasing channel length .2.2.2 Circuit stacking .2.2.3 Multi-threshold libraries  .2.3 Dynamic optimizations .2.3.1 Body biasing .2.3.2 Clock gating .2.3.3 Power gating  Power Switch characterization  .3.1 Current capacity .3.2 Leakage .3.3 Dimensions .3.4 Gate delay .3.5 Switching power Isolation cell characterization | 65<br>66<br>66<br>67<br>67<br>68<br>69<br>70<br>70<br>71<br>71<br>73<br>74<br>76<br>76             |

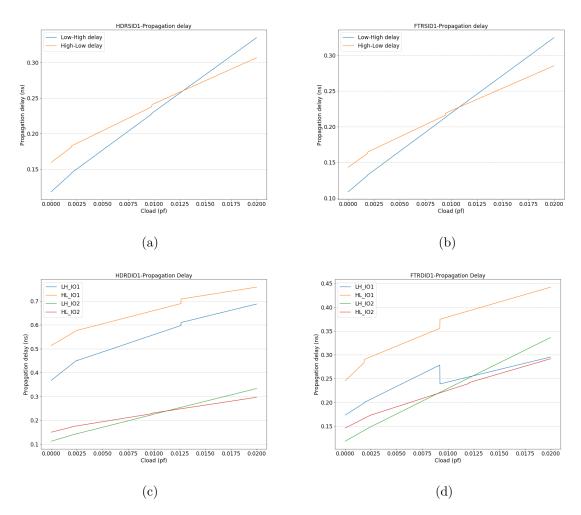

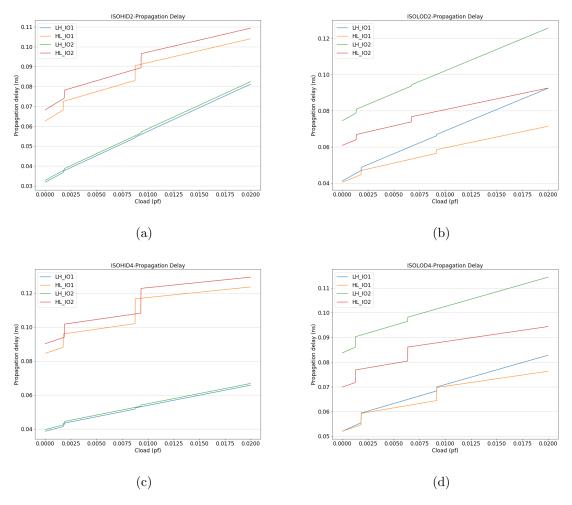

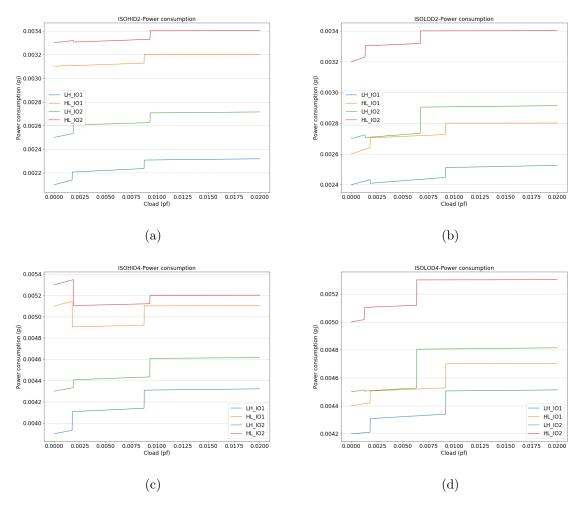

|     | .4.2  | Propagation delay                    |

|-----|-------|--------------------------------------|

|     | .4.3  | Active power                         |

|     | .4.4  | Dimensions                           |

| .5  | The s | witched module characterization      |

|     | .5.1  | Area / density                       |

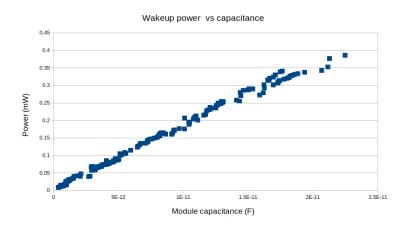

|     | .5.2  | Capacitance                          |

| .6  | Genus | Synthesis flow - synthesis.tcl       |

| .7  | Innov | us - floorplan.tcl                   |

| .8  | Innov | us placement.tcl                     |

| .9  | Innov | us cts.tcl                           |

| .10 | Innov | us route.tcl                         |

| .11 | Innov | us post_route_opt.tcl                |

| .12 | Innov | us report.tcl                        |

| .13 | Some  | design querying functions used (tcl) |

#### Abstract

Power gating is a widely used technique for low power circuit design, which involves selectively shutting-down regions of an integrated circuit, dropping its power consumption to nearly zero, and all while the rest of the chip remains in operation. It may seem as a win-win strategy, however its implementation comes at a cost in a variety of aspects, some of them being power consumption, area and performance. An important body of research has focused on applying this technique and finding the limits on where this technique can be applied. Let it be in terms of scale and granularity, speed and frequency of switching on and off, etc. Thus, it has been of particular interest to explore this technique in the particular context of re-configurable fabrics.

This research explores power-gating as for reducing energy consumption in coarse-grained re-configurable architectures (CGRA) with the aim of exploring the effects of granularity decisions in this regard. For this end, a method is proposed in order to evaluate power-gating on a cell-to-cell basis, considerably outperforming traditional power-gating strategies. This method substantially extended the reach of power gating in the interconnect network, without compromising the interconnect's functionality. Finally, both area and power trade-offs are analyzed in the back-end stage of a CGRA's development.

## Chapter 1

## Introduction

In the past years, the use of application-specific embedded systems has reached the point of becoming a basic need in order to satisfy the market demands for cost, performance and power of newer designs. The industry has increasingly adapted the use of (re)configurable architectures in design flows to reduce the time and costs incurred to bring a product to the market, and integrated on high-performance computing devices.

In this section, we will introduce the concept of re-configurable architectures and more importantly, Blocks, the CGRA designed by the TU/e, which will ber where the focus of this research is. We will also discuss general techniques for power optimization, finalizing with the project problem statement ultimately driving this thesis project.

Traditional CPU's have taken us a long way as the workhorse driving most of our devices, ranging from high-end supercomputers, normal computers and smartphones, to small microcontrollers. The one feature that these processors have in common is their capacity for running virtually any type of operation given their rich instruction sets. This completeness comes however at a great cost in terms of power efficiency and speed. This has become a more present challenge as the complexity and computational power that real-time applications require to be effective. Be it visual processing applications, digital signal processing, or multi-variable simulations.

For this reason, the use of application specific integrated circuits started to take over those individual applications, by sacrificing a rich instruction set, and having a streamlined hardware structure, they were able to outperform CPU's by orders of magnitude in both performance and power consumption.

The rise of application specific integrated circuit presented a much more effective way of dealing with different computational challenges as they can perform several orders of magnitude faster, and more efficiently energy-wise than a multi-purpose chip on similar tasks. However, ASIC's strenght in performance would quickly be shadowed by their lack of flexibility. This gap has given way to re-configurable architectures, which would promise near-ASIC performance by mimicking the hardware of an ASIC. However they bring these benefits at the cost of an interconnect area overhead, and lower power efficiency. Different granularities of reconfigurable chips have been proposed and have reached various levels of industry use, being the most popular the field-programmable gate arrays (FPGA), and the coarse-grained reconfigurable architectures (CGRA). This research is focused on a version of CGRA developed by the TU/e.

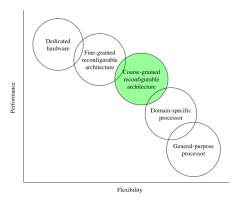

Figure 1.1: Qualitative Flexibility-Performance localization. Source: [7]

#### 1.1 Re-Configurable Architectures

Reconfigurable architectures have increasingly been adopted by industries due to its capacity of adapting an architecture to accelerate defined applications; much like an ASIC, however reversible. This provides a significantly higher performance in both speed and energy utilization [40]. This trend can be supported by looking at the increased use of Xilinx's and now Intel's FPGA's, as well as a broad range of more coarse grained versions of them. Sometimes,

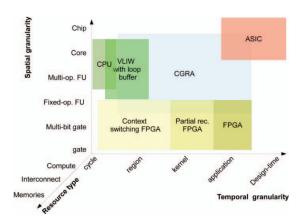

Figure 1.2: Multi-granularity based CGRA definition and comparison. Source: Wijtvliet et al. 2017 [40].

and depending on the type of applications intended, FPGA's can reach better power and performance numbers by locally reducing its per-bit reconfigurability, hence increasing the granularity of its building blocks (see fig. 1.1. for example, the use of multiple DSP's in a standard in FPGA structures.

#### 1.1.1 The CGRA

CGRA's have steadily earning a position between the full reconfigurability of FPGA's and less customizable options, and the major reason for this consists in the recurrent use of predetermined functions that need acceleration which can be implemented in an ASIC-fashion, but wrapped around a re-configurable layer to support it. The boundaries between ASIC's and programmable architectures in modern processor designs are becoming less and less clear as they implement hybrids and accelerators for specific applications.

CGRA's are more generally defined as a reconfigurable architecture that uses hardware flexibility to adapt the data-path at runtime to the application. Hence it becomes an array of configurable functional units that are also spatially programmable. Some academics have proposed methodologies to classify different types of CGRA's to come up with a more robust definition, therefore bringing to light: a) The wide variety of current CGRA designs, and b) The broad possible range of applications in which CGRA's can shine respect to other architectures for a particular application. Wijtvliet et al. [40] proposed a mix of spatial and temporal granularity metrics to classify a wide range of existent CGRA's, see figure 1.2.

This shift back towards more coarse grained accelerators could mark a trend that will provide hybrid FPGA architectures, or namely completely coarse-grained reconfigurable architectures (CGRA's) a space in the market [40] as a more efficient, cheaper, and potentially easier to configure alternative to current FPGA alternatives. It is hard to directly compare CGRA's with FPGA, given that the first has many varieties proposed where few have made it commercially [7].

.

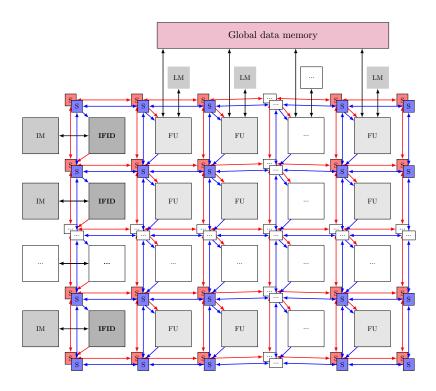

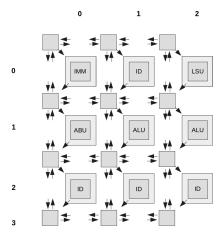

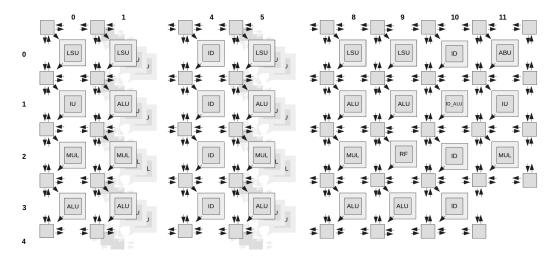

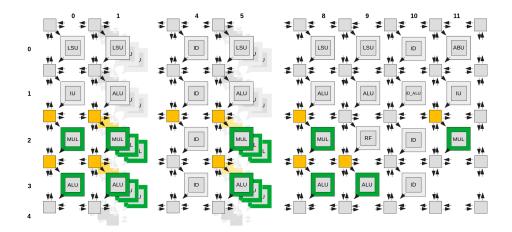

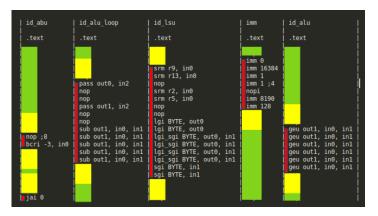

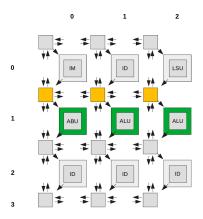

Figure 1.3: Closer look at the structure of Blocks, based on [40]

#### 1.1.2 CGRA-Blocks

The CGRA utilized in this study is called Blocks: a design developed at the Eindhoven University of Technology, which as described by its Wijtvliet, M. as "is somewhere between reconfigurable processors and coarse grained re-configurable architectures". This architecture was designed as a fabric of reconfigurable processors (RP's) that act in a SIMD-VLIW fashion, however with the possibility of extensive explicit bypassing controlled by a specially designed interconnect network that communicates every RP through pre-runtime configured switch-boxes. Figure 1.3 shows the generic structure of Blocks, and one of its main features; the presence of a dual interconnect network. In order to achieve power reduction, the instruction and data paths have separate networks through which they propagate to each of its functional units. This separation allows to reduce the size of the data interconnect, and to exploit instruction re-use.

#### 1.2 Project problem statement

As it has been mentioned in this chapter, the performance that CGRA's can achieve is comparable to that an application specific design. However CGRA's are rather power-hungry mainly due to their massive interconnect network. This issue has been brought up and is one of the main concerns regarding CGRA-based embedded systems [19]. And many strategies have been put in place in order to mitigate the CGRA's power consumption: either by performing the standard power reduction methods discussed in annex .2, or through architecture-specific strategies such as the the interconnect solution in Blocks, or by power-gating sections of the CGRA as it has been applied to FPGA's [5]. For this reason, power gating was chosen as the strategy to study as it targets the most dominant source of power consumption in deepnanometer designs: leakage. Additionally, power gating is a strategy that involves a careful consideration on the architecture it is applied to, the granularity at which it can be applied, and the ways it can be used effectively. Thus, being an area of research with the potential of bringing novelty while attempting to solve a major challenge in the advance of the CGRA as a standard platform.

Power gating has become almost mandatory in VLSI designs since the leakage is a dominating factor in newer CMOS technologies. It has become specially interesting for re-configurable architectures, where based on the mapping of a function major parts of the architecture remains unused. Power gating comes with logic overhead besides the required power switches themselves, and this overhead logic needs to provide logical isolation and valid logic signals while turned off for each of the switched modules' outgoing wires. This leads us to having to seriously investigate the granularity at which power gating can be applied. This is specially the case with in coarse grain re-configurable hardware, where there are very clear functional/logical dependencies between coarse-grain blocks.

It is for the reasons just argued, that power gating that it has been taken as the most relevant strategy to reduce the power in newer technologies using accelerators and re-configurable fabrics. The case of the CGRA developed at the Technical University of Eindhoven, would make of a suitable test subject to analyze the trade-offs regarding the granularity at which power gating can be applied. This is a topic in which there is not yet a consensus, or a systematic way to quantify the actual impact of power gates.

#### The problem statement is then an optimization question:

[MQ] At which granularity, in terms of functional units within the context of the coarse grained re-programmable architecture (CGRA), should power gating be applied to be beneficial for power. Analyzing the existing power-switching strategies applied in the industry, and providing results in the context of existing benchmarks and algorithms.

This analysis will weigh present trade-offs based on performance, area, energy savings, and possible flexibility implications of the different granularity settings for these algorithms, and taking into account the overhead of all relevant modifications involved in its implementation.

#### The relevant sub-questions go then as follows:

[SQ1] Analyze the implementation of power gating from the perspective of functional units,

and determine whether is should be added as a default feature of all functional units in the CGRA, investigate the main variables involved and argument a position.

- [SQ2] In terms of Floorplanning and the overall physical design, is what is the impact of the different power switching strategies, and how do they compare with the literature in the context of the CGRA?

- [SQ3] Quantify the overhead coming from isolation cells, and control logic that may be required.

- [SQ4] Can power gating on the CGRA be controlled dynamically e.g. switching functional units on and off during execution? Analyze and quantify. If that were beneficial, how should it be controlled?

#### 1.2.1 Planning

In order to answer these questions, the next chapters are organized as follows:

Chapter 2 introduces the state of the art study on what concerns power gating, analyzing the different aspects that need to be taken into account, as well as drafting an idea of what results were to be expected when applying them to the CGRA.

Chapter 3 introduces the main metrics that will be used to evaluate the power gating strategies adopted in terms of energy and area.

Chapter 4 will review everything related to the workflows and models used to generate the metrics that we need to evaluate. Starting from the specifics of the designs used, tests groups and flows. Finally it introduces the Path traversal algorithm used to optimize power gating in the CGRA.

Chapter 5 showcases the results in terms of the metrics generated by the different strategies applied, the impact that the path traversal algorithm had in the test groups, the overall metrics CGRA-wide both dynamically as well as by switching the CGRA entirely off.

Chapter 6 finally summarizes the results and contrasts it with the initial objectives, highlighting the progress that this research made, as well as the future work that needs to take place.

## Chapter 2

## State of the art analysis

Thus far, this report lit upon what the current trends in low-power designs are, (excluding fully sub-threshold designs), and motivated a research question based on the granularity of power switches on a re-programmable fabric. This section will now place the focus onto latest research in the field of power gating, trying to map what alternatives are out there that may help answer the problem statement. The section will begin with some identified trends, then pass onto some guidelines on the design of power gates in terms of width and other parameters, to then the start drawing a power model for the different case-base that this research will have, all within the context of 40nm-TSMC technology.

#### 2.1 Current trends in power gating

As introduced in section .2.3.3 and in the problem statement, power gating, or power gating, is one of the most attractive and well adopted techniques for power saving in nanometer technology nodes, we have many of today's microprocessors actually applying block-level power gating when the processors are idling [21].

It is however paramount to being able to apply power gating during the activity of these cores, as generally a small portion of them will be active, accelerators, certain IO's and even parts of the memory could be power switched, hence fine-grained run-time power gating (FRPS or FRPG) has been explored [20] to preserve power in a much smaller temporal and spatial granularity. Fine-grained run-time power gating generally depends on a small bit of control circuitry, and has been applied to memories [35], functional units in microprocessors [16] and re-configurable architectures [26].

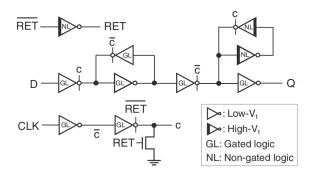

An interesting option to fine-grained run-time power gating, or perhaps a complement, consists in the use of state retention within the power gated blocks (see fig. 2.5), however this solution tends to be quite expensive both in terms of power and area. For this reason, smart classification of registers either via netlist analysis or formal methods [13] have allowed to apply retention to only a subset of the registers that would otherwise be introduced in a block. This state retaining method allows for a stop in processors when for example a cache miss occurs and the processor is stalled, then quickly recover from where it left off after the issue has been solved.

In terms of power gating for memories: memories contribute to nearly half of the leakage in deep-nanometer circuits, however they often cannot afford loosing their state and generally a state-retention based power gating scheme would turn to be too expensive area-wise. Thus, a multi-mode power gating strategy was proposed [11]. It consists of a much bigger switch cell, which supports namely 3 modes: On, while active; Sleep while they are off but with memory retention enabled; and Off for completely shut-off. This has also been explored in prior master projects at the TU/e, by Groot [14] who proposed a switch capable of dropping the voltage of a module low enough to reap benefits in leakage, but high enough to allow registers to be able to keep their state.

There is very limited research particularly concerning power gating in CGRA's, however the closest neighbour to this architecture family are FPGA's, which present a substantially more developed literature in terms of granularity and control. Bsoul [4] explored different ways in which the interconnect could be included into the power-gating scheme and investigated dynamic power gating. Additionally, research on power gating in FPGA's generally aims to target the interconnect networks in their designs, on the one side because the blocks within an FPGA are generally hard-IP blocks, but also because the interconnect network is one of the main sources of power consumption. Partial and total inclusion of the interconnect structures around particular logic clusters have been proposed [5]. The range of solutions seen in FPGA's do not directly apply to the CGRA, however they face similar issues and therefore their approach in their case seems to lay a solid starting point for tackling the challenges (and pros) that the CGRA presents.

To summarize this quick overview of the main trends with respect to power gating:

- 1. Leakage keeps growing.

- 2. Most modern microprocessors apply it at a coarse level, as a standby/ sleep mode, however fine granularity seems to be making big steps due to:

- (a) Vertical integration of power gating in the design flows (eg. Compiler-based power gating + Hardware-based opwer gating).

- (b) Better partitioning algorithms and selective use of state retention.

- 3. Improvements in power gating for memories has led to various new multi-mode power switches.

- 4. Power gating research in CGRA' is still very poor, however there is a much more mature knowledge revolving FPGA research, where schemes have been proposed to power-gate at different granularities, as well as including ways of controlling the power gated blocks at run-time.

### 2.2 Implementing a power gate circuit

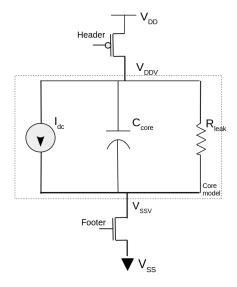

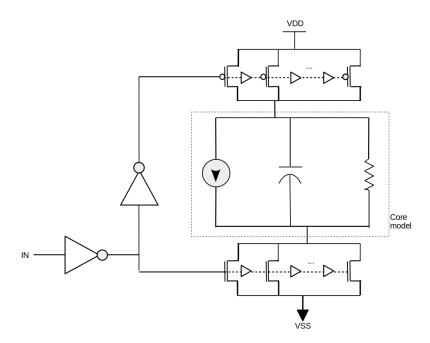

The modeling, and latter implementation of power gates require a number of design decisions that need to carefully be revised, This section will present some of the main challenges that this process takes, and what possibilities are in place to take this research into an implementation, as shown in figure 2.1.

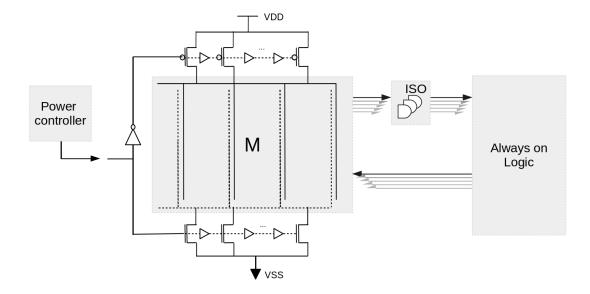

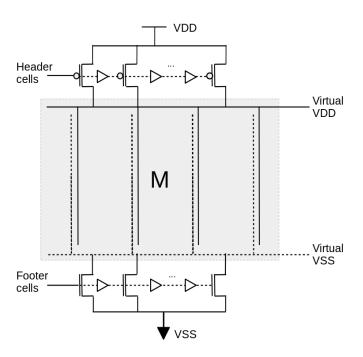

Figure 2.1: Diagram showing the main structures involving a power gating scheme: the controller on the left, the switches themselves (headers and footers on top and bottom of M respectively), the isolation cells on the outputs of the module M, and the always-on block representing the set of non-switched modules.

In the following sections, we will turn into discussing the more practical parts of power gating, treading ever closer to what the final implementation should be.

#### 2.2.1 Sizing of a power gate

The simplest possible way to visualize a power gate is to think about a single single transistor, either PMOS or NMOS (header and footer respectively), then, we can extend this to an array of transistors that act in synchrony as a single switch by inducing a high resistance when the gates are closed. It is used to power gate certain parts of a circuit that are currently not in use. Generally, these sleep transistors are high- $V_t$ .

It is important to remember that the 'optimal' power gating strategy (if any) will depend on specific goals and the actual chosen CMOS technology. Some of these variables are have to do with the use of header and/or footer; if there is any bias; the chosen transistor size and other layout implementation details. We also have to put our search into the context of 40nm bulk CMOS.

Commonly, the minimal sizing of a sleep transistor will depend on the current that the power-gate circuit can draw, and the acceptable IR drop. The following size calculations have been described for both NMOS [1], and for PMOS [17].

We will now perform the estimations for a PMOS. To simplify the analysis, we assume that a single power gate will be used per gated block. We start our analysis by determining the delay of a normal gate delay (eg, in the absence of a PG).

$$\tau_d = \frac{C_L V_{DD}}{(V_{DD} - V_{Tl})^{\alpha}} \tag{2.1}$$

where  $C_L$  is the load capacitance,  $V_{Tl}$  is the threshold voltage of the (low-Vt) transistor, and  $\alpha$  is the velocity saturation index which is technology dependent. Now, in the presence of a sleep transistor, the gate propagation delay inside the power gated block can be calculated as:

$$\tau_d^{PG} = \frac{C_L(V_{DD} - V_{PG})}{(V_{DD} - V_{PG} - V_{TI})^{\alpha}}$$

(2.2)

where  $V_{PG}$  is the voltage drop on the power gate. Now, we would like to find the  $V_{DD}^{PG}$  such that the delay of the transistor without power gates were equal to the delay of the power gated case:

$$\tau_d = \frac{C_L V_{DD}}{(V_{DD} - V_{Tl})^{\alpha}} = \frac{C_L (V_{DD} - V_{PG})}{(V_{DD}^{PG} - V_{PG} - V_{Tl})^{\alpha}}$$

(2.3)

For simplicity, we shall assume  $\alpha = 1$ , hence the 'supply increase ratio'  $\eta$  is:

$$\eta = \left(\frac{V_{DD}^{PG}}{V_{DD}} - 1\right) \tag{2.4}$$

Having this relation, we can define the voltage drop in terms of  $V_{DD}$ , which will help us in the next steps:

$$V_{PG} = \eta V_{DD} \tag{2.5}$$

Assuming that the PG operates in its linear region, its current can be expressed as:

$$I_{PG} = \mu_p C_{ox} \frac{W}{L} \left[ (V_{DD}^{PG} - V_{Th}) V_{PG} - \frac{V_{PG}^2}{2} \right]$$

(2.6)

Where if we substitute  $V_{PG}$  as in equation 2.5, we will get:

$$\left(\frac{W}{L}\right)_{PG} = \frac{I_{PG}}{\mu_p C_{ox} \eta V_{DD} (V_{DD}^{PG} - V_{Th} - 0.5 \eta V_{DD})}$$

(2.7)

This relation puts puts in evidence how the size of the transistor is a function of VDD, and the voltage drop across the power gate (through  $\eta V_{DD}$ ), finally we can calculate the minimal power gate size if we take  $I_{MAX} = I_{PG}$ , where  $I_{MAX}$  is the maximum switching current that the circuit will draw. Repeating the same process, we can get the expression for the size of an NMOS-PG as:

$$\left(\frac{W}{L}\right)_{PG} = \frac{I_{PG}}{\mu_n C_{ox} \eta V_{DD} (V_{DD}^{PG} - V_{Th})}$$

(2.8)

often,  $\mu C_{ox}$  is replaced by the value for trans-conductance  $\beta$ , which makes:

$$\left(\frac{W}{L}\right)_{PG} = \frac{I_{PG}}{\beta \eta V_{DD} (V_{DD}^{PG} - V_{Th})}$$

(2.9)

where  $\beta$  is the transistor trans-conductance,  $\eta$  is the max relative IR drop, and  $V_{DD}^{PG}-V_{Th}$  is the gate-drive voltage. If we now look back at the models presented in section .1, we can start doing the exercise of which power gate would be required for a particular block capacitance.

#### 2.2.2 Trade-offs and break-even point

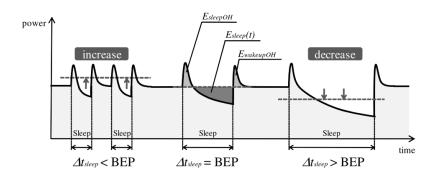

The implementation of power gates comes at a considerable overhead, as it will require the insertion of wide-enough power switches that will supply of a stable  $V_{DD}$  and  $V_{SS}$  regardless of: a) the voltage drop induced by the transistor itself, b) the current draw that the circuit will have during its active period. This switches will still have a certain resistance, and hence burn extra active power, as well as introduce extra power consumption when switching on and off a virtual supply (either  $V_{DD}$  or  $V_{SS}$ ). This introduces an overhead that in principle, should be compensated by the gains of reduced leakage power (see fig 2.2).

Figure 2.2: The power profile of a curcuit with power gating. Source: Kondo 2014 [20]

Most work available present the idea of a break even point (BEP), in which they look towards compensating the overhead that the PG introduces [20, 32]. In this particular case, the overhead is modeled as  $E_{sleepOH}$  and  $E_{wakeupOH}$ , where the energy gain is a function of the time in which the circuit it in shutoff mode  $E_{sleep}(t)$ .

$$E_{savings} = E_{sleep}(t) - (E_{sleepOH} + E_{wakeupOH})$$

(2.10)

Niedermeier [28] digs a little deeper into the breakdown of overhead, not only including the extra power used while switching on and off, but rather including explicitly the impact of architectural changes and supporting cells onto the design, expanding on the active power of isolation cells, and other modules. Here,  $(E_{sleepOH} + E_{wakeupOH}) = E_{overhead}$  is defined by:

$$E_{overhead} = t_{down} * (P_{switch,leak} + P_{iso,leak} + P_{SR,leak})$$

$$+ t_{active} * (P_{iso,active} + \Delta P_{SR,active})$$

$$+ t_{total} * P_{add.modules}$$

$$+ N * E_{poweron}$$

$$(2.11)$$

Indeed, the power gating is worth it only if  $E_{savings} \geq E_{overhead}$ .

Since the implementation of the power gates to be done in this project is going to be a mainly hardware-based solution. Other software-based trade-off and analysis schemes are going to be omitted. The logic behind this analysis however, seems to show quite some clarity about how the power gates's performance will be evaluated power-wise.

As was just mentioned, and added into the trade-offs variables; the implementation of power gates often requires a number of other cells, circuit infrastructure, and control mechanisms to become a viable option. The additions that are required are:

1. Decap cells: in order to avoid the power noise caused by the simultaneous switching of IO buffers and logic. The addition of decap cells can considerably reduce the transition noise. The decap cells commonly use on-chip non-switching capacitors  $C_{ckt}$  or thin-oxide capacitors  $C_{ox}$  [17]. Depending on the noise distribution of the chip or the block in question, decap are distributes around and within the chip to pull noise back to a determined margin. A high capacitance from decap cells is generally used in high performance chips.

Figure 2.3: Illustration on the insertion of decap cells to denoise a power gated block.

Some of the calculation on how much decoupling, and where it should be located, is presented in the work of [17], where an iteration greedy algorithms and identification of highest noise sensitivity are used to place the necessary decap.

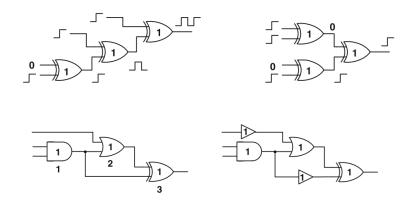

2. Isolation cells: These are simple registers or combinatorial cells that are connected at the outputs of the gated block to prevent the floating outputs of the cut-off circuit to change any states on the parts of the chip that are active. These cells are in the always-on domain and depending on the design and the amount of power islands to be gated, could generate a considerable amount of power overhead [28], there are generally 3 types of standard isolation cells: pull-up, pull-down and with a latch to preserve the last output of the gated block. This last one is generally only used in tandem with state-retention across the power gated block, which can be connected to scan chains or other 'state retention schemes'.

Figure 2.4: schematic of a simple clamp isolation cell

3. Retention registers: one of the challenges of power gates, is that the state of the block that has been shut-off looses its state, since memories and registers are not capable of keeping their information while powered off [33]. Hence, special retention cells have been adopted in most of the commercial standard libraries (eg. TMSC), to support the State retention power gating (SRPG).

Figure 2.5: Illustration of the schematic of a retention cell. Here, a conventional master-slave D-FF is modified for data retention. Here, the when when the power-gated cells (denoted by GL) are shut down, the information is moved to an adjacent latch that is within the always-on domain. Source: Seomun, 2009 [33].

The use of SRPG requires an extra duplicate of the state latches that need to be retained, thus, the area increases by about an unavoidable 30-50% per retained register [33]. This also poses a great challenge in terms of routing overhead, as some of this registers have to be located sometimes deep within shut-off territory [13], as well as reducing the power-saving effectiveness in contrast to a traditional PG scheme.

A more advanced version of SRPG is selective-SRPG or SSRPG, which is done by only choosing and retaining the registers that are essential for retaining the state of a power-gated block. This assumes that only a small subset of the gated FF's is actually essential for a system-wide state retention, which often has its limitations. Some of the processes in which SSRPG is based consist in the classification of a design's FFs to be power gated [12].

#### 2.3 Fine grained vs. Coarse grained

One of the first decisions that the architect has take when planning power gating, is the issue of granularity. Literature often describes granularity as fine and coarse, depending on whether the power gate is located already as part of each standard cell in the library to be used [18]. However this definition has shifted over time as a) per-cell power gating doesn't seem to justify the overhead that it involves, and b) The literature has shifted the understanding of fine-grained power gating (FGPG) to the order of hundreds of cells, whereas coarse-grained power gating (CGPG) generally ranges in the thousands of cells. Our understanding of granularity could have a distinction on the basis of a functional unit in the CGRA. Meaning that FGPG may involve 1 functional units or less, while CGPG would involve an array of functional units.

#### 2.3.1 Fine-grained power gating

in the case of the smallest possible fine-grained power gating, the power-gate is located inside the standard cell, and since it has to be able to supply the worst case current required by that particular cell, the resulting size of that FGPG ends up being comparable to that of the cell itself; even up to x2-4 of the original cell size [18]. It is important to note that for FGPG footer cells are preferred above headers, for the simple reason that NMOS transistors have roughly twice as higher carrier mobility than PMOS transistors, which will proportionally impact the required size of the power gate in question (see equation 2.9), however, due to their increased mobility, NMOS power gates will present more leakage current than PMOS (see equation 8).

One of the advantages of fine-grained power gating is that the design of each power gate individually has very little problems, as the timing impact of the IR drop can be quite predictable, this means that FGPG could be, if it were included in the standard cell libraries, deployed using a 'normal' design flow. However the sizable amount of overhead could barely justify the use of power gates per cell, also specially because most power-gated circuits use at least 8-bit architectures. It becomes then almost natural to group cells into coarser islands and still call it Fine-grained.

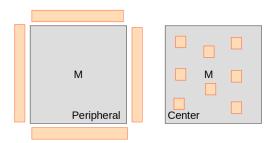

#### 2.3.2 Coarse-grained power gating

In coarse-grained power gating (CGPG), a block of gates is switched by one or a group of power cells. Generally they are placed forming a ring around the gated block or they are distributed within the actual block [18]. This method has been the most used in the past years, as it does not require the extreme area overheads used in fine-grained power gating, however it presents different challenges in regards to the number and size of power gates required for gating a given block. This is due to the difficulties in estimating the worst case current that the gated circuit will draw from the switches.

Figure 2.6: structure of a ring and column based power gating techniques

Each of the two methods have their advantages and disadvantages, and it will ultimately be a decision of the designer, on which of the two shall take place. However, this structural CGPG decision will have implications on further design decisions.

#### 2.3.2.1 - Ring-based coarse-grained power gating

It generally is a good option for small logic blocks where the voltage drop across the switch transistors and the  $VV_{DD}$  mesh can be easily managed.

- + Simpler power plan due to the separation between the Virtual  $V_{DD}$  and the actual  $V_{DD}$ . Sleep transistors are not mixed with the other logic cells.

- + Has little negative impact on placement and routing.

- It does not support retention registers (as the whole block is completely cut from  $V_{DD}$ ).

- Adds a much more significant extra cost compared to a grid approach.

#### 2.3.2.2 - Grid-based coarse-grained power gating

This is a more suitable alternative when large logic blocks are being power gated, as it would supply the  $VV_{DD}$  ( $VV_{SS}$ ) with a better distribution.

- + The switches have to drive smaller portions of the  $VV_{DD}$  every time, compared to the ring based power gating.

- + Requires fewer/smaller sleep transistors for a similar IR drop. Then again, it is because the  $VV_{DD}$ 's are are of much smaller depth.

- + Permanent power supply is available across the power-down domain areas.

- + it provides a better trickle charge distribution for management of in-rush current.

- + has less impact on the area of a power gated block.

- It requires changes on the cell routing and physical synthesis.

- Adds much more complexity to the power routing needs of the design.

There are variations of Grid based implementations of power gates, such as column based and row based. These, they are good for reducing the voltage drop across the  $VV_{DD}$ s but they impact placement and lower metal layers on the design.

The optimal style will depend on:

- 1. Design.

- 2. Library being used and the type of switches available.

- 3. The technology being targeted and its specific leakage characteristics.

- 4. The performance and power goals of the design.

- 5. The use of legacy or highly optimized IP.

## Chapter 3

## Metrics

The last section in the analysis has to do with the design itself on a back-end perspective, this is a more practical and therefore a slightly less explored area experimented with on the research. Its results would shed some extra light and weights on the trade-off analysis of power switches from both a power and a floorplanning perspective.

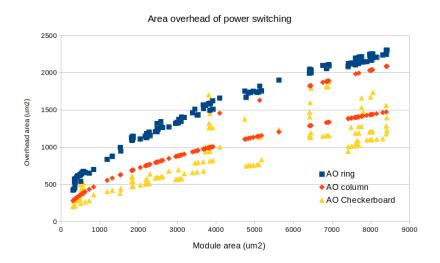

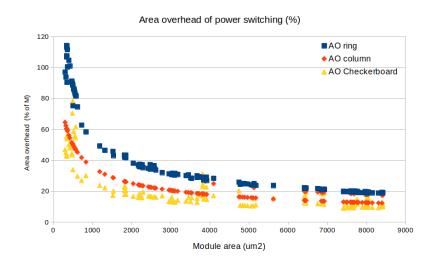

#### 3.1 Area overhead (AO)

As presented in section 2.2, we will discuss the two common schemes for used by designers and their trade-offs, namely the ring-based and column-based power switch insertion, additionally, a derivative of the column-based method, generally called the "checkerboard" method. The first thing we need to find out is how many power switches does the module M require. This information can be obtained by different ways given the tools available and the information that can be gathered from the technology libraries of the TSMC40nm libraries. The most straightforward way of collecting the information about the module M, would be to collect the capacitance, activity factors and energy consumption from Innovus' reports and replicate the 1st order model presented above.

Using the power reports from Innovus, we can collect capacitance, power consumption and the activity factor on which those were calculated. We can thus estimate that the power that the switches need to provide in the worst case as  $power(M)/\alpha$ , in other words, the module power in case of a 100% chance of activity. With that, the translation from power to required current just requires a division over the supply voltage  $V_{dd}$ . Since we are using both headers and footers, we repeat the exercise on both cases:

$$Nr_{PS} = (AP(M)/\alpha)/min(I_{PS})$$

(3.1)

Where the  $I_{PS}$  is the current that the power switch can provide given a designer defined IR drop of 5%. Now, knowing how many power switches of every type we would need, we have to distribute it between big and small making sure there are enough small power switches to ensure that the rush-in current stays below a 5x the normal current threshold through a stepped wake-up chain. Having the number of headers and footers of each type to be used for module M, we can analyze the area impact of adding them to the design: The easiest way would be to add the area of the power switches and isolation cells:

$$AO_{total} = AO_{PS} + AO_{ISO}$$

$$AO_{total} = \sum area_{PS} + \sum area_{ISO}$$

(3.2)

While this analysis holds for the isolation cells, the area overhead of power switches depend on the type of insertion implemented, we therefore will calculate the  $AO_{ring}$  and  $AO_{cols}$  for the ring, column and checkerboard types of switch insertion separately, and therefore is it where the analysis will go. Now, the different methods end up collecting basically the same information and can help contrast the results of each other. We will lean towards the first method in this case as we have a way of simulating on the same principles.

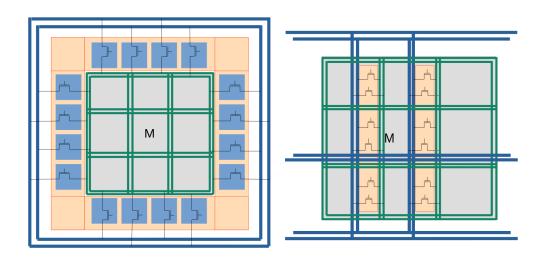

#### 3.1.1 Ring-based power switching

Ring-based power switching, as its name indicates, and as discussed in chapter 2, all power switches are inserted around module M, hence creating a ring around it, as shown in figure 3.1.

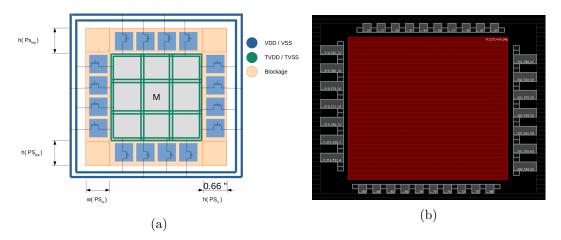

Figure 3.1: Area overhead  $(AO_{ring})$  of a ring-based power switch insertion on the area of M. in theory (a), and in practice (b) generated in Cadence Innovus.

Knowing the number of switches needed and assuming a distribution on all 4 sides of M, we can define  $h(PS_{side})$  and  $w(PS_{side})$  as the maximum height and width of all power switching cells in a particular side plus the separation between the M and the power switches, defined as  $halo_M$ :

$$h(PS_{side}) = max(h(PS_{side})) + halo_M$$

and

$$w(PS_{side}) = max(w(PS_{side})) + halo_M$$

Now, we can estimate  $AO_{ring}$  of as follows:

for the sides:

$$w(M) * h(PS_{top}) +$$

$$w(M) * h(PS_{bot}) +$$

$$h(M) * w(PS_{le}) +$$

$$h(M) * w(PS_{ri})$$

and the corners:

$$h(PS_{ton}) * w(PS_{le}) + h(PS_{ton}) * w(PS_{ri}) +$$

$$h(PS_{bot}) * w(PS_{le}) + h(PS_{bot}) * w(PS_{ri})$$

#### 3.1.2 Column-based power switching

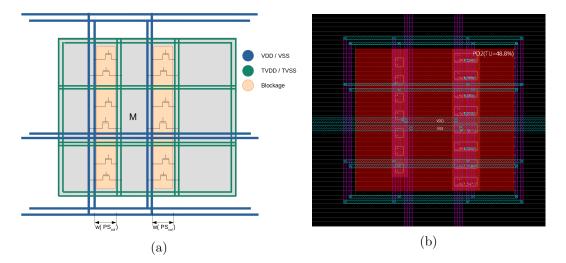

In the case of column based, the switches are placed inside the module M, hence avoiding the requirement for a complete construct around the module as a ring-based scheme would require. This method generally requires less area to be implemented, but increases the routing complexity, as seen in figure 3.3 with respect to 3.1.

Figure 3.2: Area impact of a column-based power switch insertion on the area of M. in theory (a), and in practice (b) generated by Cadence Innovus.

We can estimate calculate the area impact of the power as, given a COL = nr of PS columns in M, and the width of a column defined as the maximum width of the power switches belonging to that particular column  $(PS_{col})$ .

$$w(PS_{col}) = max(w(PS_{col})) + halo_M$$

with makes the area overhead (AO) for columns:

$$AO_{col} = \sum_{i}^{COL} h(M) * w(PS_i)$$

(3.3)

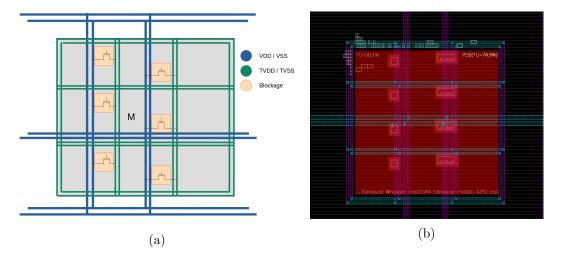

#### 3.1.3 "Checkerboard" power switching

This technically consists in a variation of the column-based power switching, however it places the power switches on every column in a vertical distance to each other, allowing for the blockage that would have been otherwise across the whole column to be interrupted, thus allowing for a minimal area impact on power switching. For this effect, we now have to calculate the area overhead ao per-switch s, and with halo = 1.68um:

$$ao_s = (w_s + 2 * halo) * (h_s + 2 * halo)$$

(3.4)

Where the total overhead of the "checkerboard" switching is the sum of all N individual overheads:

$$AO_{check} = \sum_{i}^{N} ao_{i} \tag{3.5}$$

Figure 3.3: Area impact of a column-based power switch insertion on the area of M. in theory (a), and in practice (b) generated by Cadence Innovus.

#### 3.2 Energy analysis

Energy is probably the prime reason why power switches are installed, however they do present certain drawbacks in this regard. Citing Niedermejer [28], the complete energy savings of a power switch scheme could be calculated as:

$$E_{savings} = P_{mod,leak} * t_{down} + N * E_{powerdown}$$

(3.6)

with N: nr of trantisitons from on to off and  $E_{overhead}$  is defined by:

$$E_{overhead} = t_{down} * (P_{switch,leak} + P_{iso,leak} + P_{SR,leak})$$

$$+ t_{active} * (P_{iso,active} + \Delta P_{SR,active})$$

$$+ t_{total} * P_{add.modules}$$

$$+ N * E_{poweron}$$

$$(3.7)$$

Sufficient data will be gathered to make this calculation applied to the case of the CGRA, and tested for different modes/granularities of power switching. The results generated will be contrasted to those of a flat design and conclusions can be taken from there.

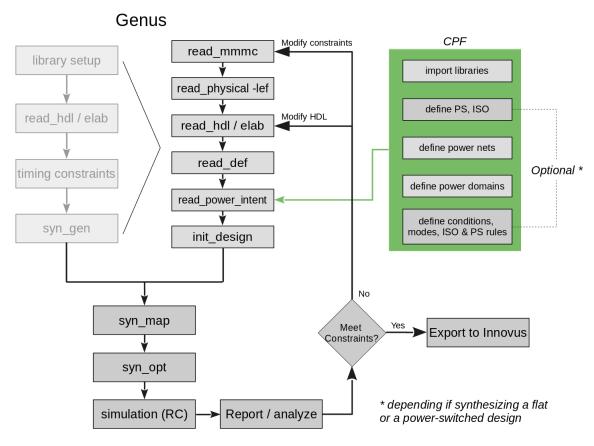

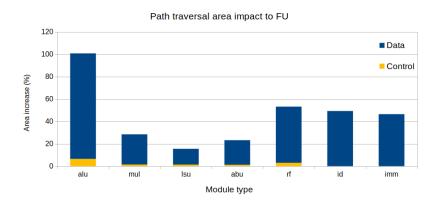

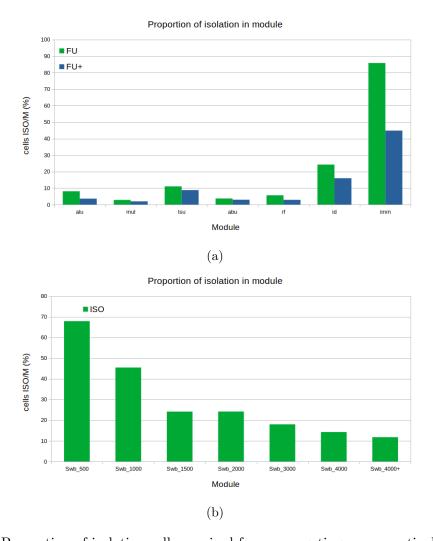

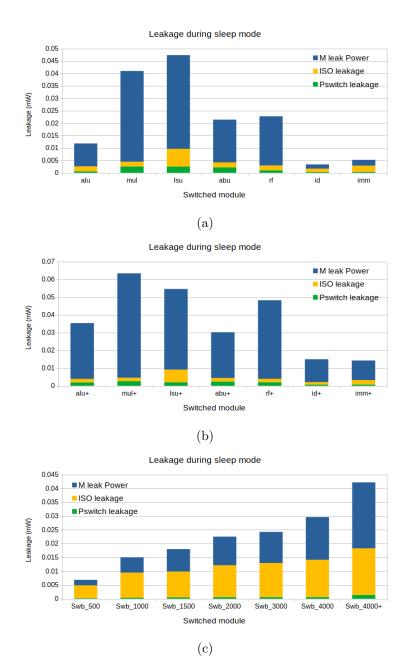

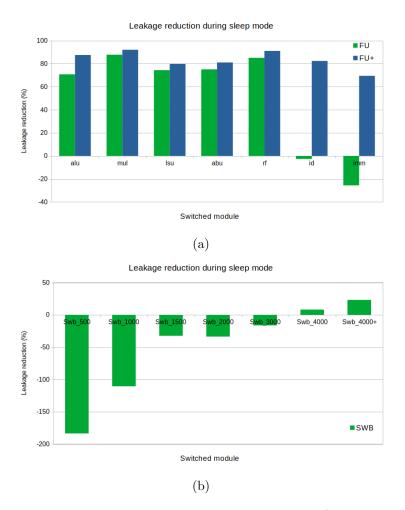

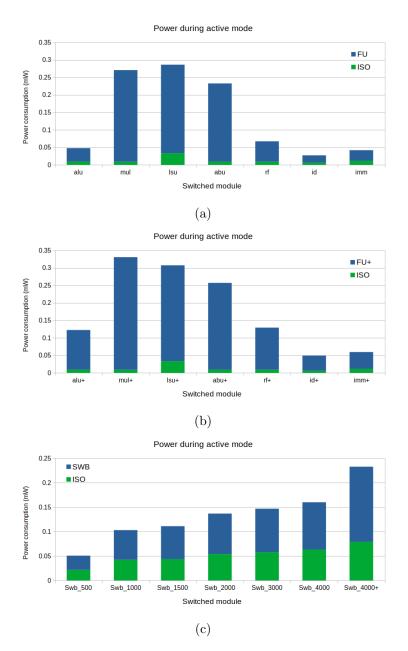

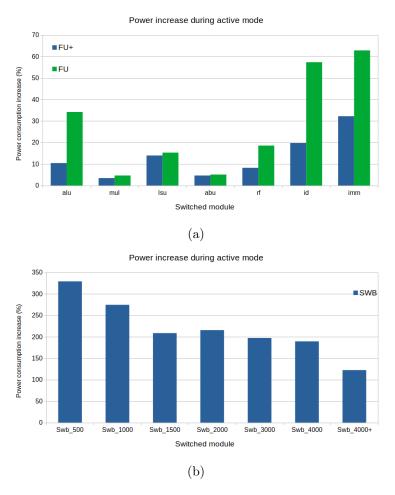

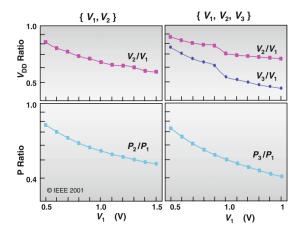

#### 3.3 Performance