#### **MASTER**

Improving low-voltage integrated power devices a simulation and experimental based study

Toonen, J. Award date: 2019

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Faculty Applied Physics

Nanoscience & technology

Photonics and Semiconductor Nanophysics

February 2018 - February 2019

## Improving low-voltage integrated power devices

a simulation and experimental based study

Jelke Toonen

Supervisors:

Ir. A. Mels

Dr. Ir. H.G.A. Huizing

Prof. Dr. Koenraad

In partial fulfilment of a master thesis

# Improving low-voltage integrated power devices: a simulation and experimental based study

#### Master of science thesis

Date: 18 January 2019

Author: J. Toonen

MSc student Applied Physics

Eindhoven University of technology

Faculty of Applied Physics

Department of Nanoscience & Technology

Research group Photonics and Semiconductor Nanophysics

Company supervisors: Ir. A. Mels

Technical Director High Voltage and Power

NXP Semiconductors Nijmegen

Front End Innovation

High Voltage & Power Technology Nijmegen

Dr. Ir. H.G.A. Huizing

Manager High Voltage and Power NXP Semiconductors Nijmegen

Front End Innovation

High Voltage & Power Technology Nijmegen

University supervisor: Prof. Dr. P. Koenraad

Eindhoven University of technology

Faculty of Applied Physics

Department of Nanoscience & Technology

Research group Photonics and Semiconductor Nanophysics

Version: Public

## **Preface**

This thesis on "Improving low-voltage integrated power devices: a simulation and experimental based study" marks the end of my graduation project, which completes my Master of Science in Applied Physics offered at the Eindhoven University of Technology (TU/e). The research presented here is performed in cooperation with NXP Semiconductors located in Nijmegen. This work, as well as my personal development, would have not been possible without the support I received from both NXP and the TU/e.

First of all, I would like to thank Dr. Ir. H.G.A. Huizing for offering me the opportunity to conduct this innovative investigation within the High Voltage and Power Technology group at NXP in Nijmegen. Surrounded by top-of-the-line engineers, scientists and managers, working in this group really pushed my boundaries and served as an ideal learning environment at the verge of my own career. In addition, it also made me develop a passion for the field of device physics, which in my opinion is one of the greatest examples where fundamental understanding of the nature can lead to products used all over the world.

Secondly, I would like to thank Ir. A. Mels for his help whenever it was necessary. As my daily advisor, he had a crucial role in the development of this work. His fast thinking and extensive knowledge of the semiconductor industry always pointed me in the right direction.

Furthermore, I would like to thank Ir. I. Emmerik - Weijland for all her support related to measurements and the interpretation of them. Moreover, the weekly discussions we had were always very fruitful for my deeper understanding of device physics.

Also, I would like to thank all my colleagues in general within the High Voltage and Power Technology group for providing me an enjoyable working environment. Moreover, the wide variety of expertise's available in this group was also a very valuable addition. In particular, Dr. S. Sque and Dr. S. Mehrotra greatly supported me with my simulations, Ir. P. Boos helped me to better understand the processing aspect of semiconductor devices and Ir. E. van der Sar kept a clear overview of the project as well as my role in it.

Finally, I would like to thank my mentor from the TU/e, Prof. Dr. P. Koenraad, for inquiring his contacts for arranging this internship at NXP and for the subsequent supervision of it.

Eindhoven, January 2019

## Summary

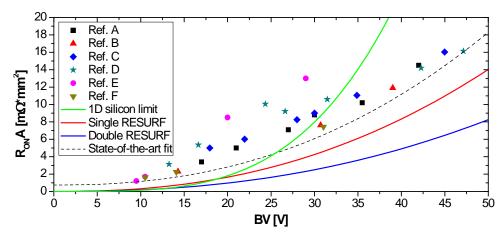

Modern society is more and more dependent on electrical appliances for all kinds of purposes such as comfort, healthcare and communication, putting increasing demands on the performance of Integrated Circuits (IC's). Besides the standard Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET's) for (low voltage) CMOS (Complementary Metal-Oxide-Semiconductor) technology, IC's also contain integrated power devices to handle the higher voltages. Such devices are mostly asymmetrical in nature: they have a MOSFET channel region required for switching and a lowly doped extension of the drain (referred to as drain-extension) to handle the majority of the voltage drop. Integrated power devices are typically used as a switch, requiring that they can handle large currents in the on-state with minimal static power dissipation and that they can sustain a large voltage in the off-state with minimal leakage current. Two important FOM's (figure-of-merits) that capture these requirements are the specific on-state resistance ( $R_{ON}A$ ) and the off-state breakdown voltage (BV), between which a significant trade-off exists (in 1D:  $R_{ON}A \propto BV^{11/3}$  and in 2D:  $R_{ON}A \propto BV^{7/3}$ ) [1].

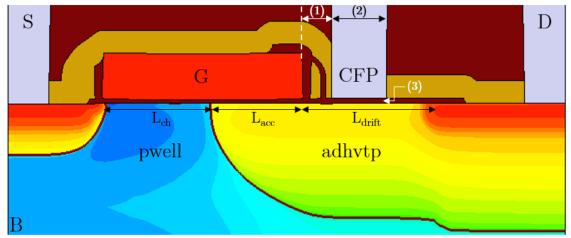

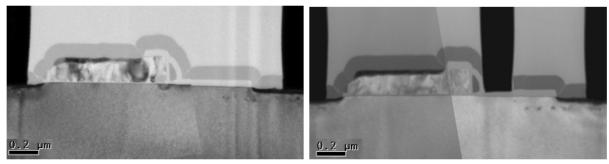

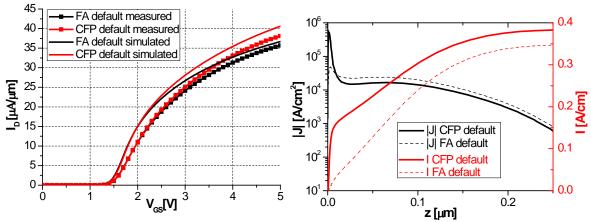

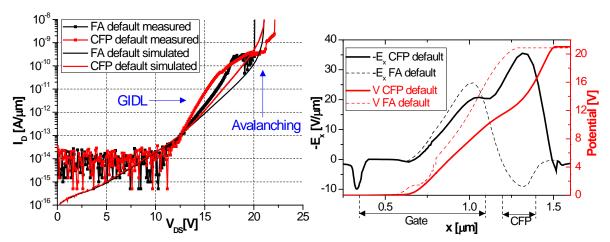

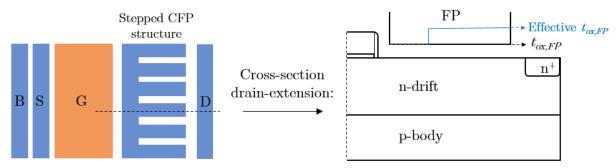

The objective of this thesis is to improve integrated power devices in the existing NXP technology platform to obtain superior R<sub>ON</sub>A-BV trade-off with respect to state-of-the-art devices in the range up to 50V off-state breakdown. For this purpose, two novel concepts, namely oxygen-inserted layer (OIL)- and contact field plate (CFP) technology, are explored by both simulation and experiment. In the OIL approach, a thin film (~10 nm) of reengineered silicon that incorporates partial monolayers of oxygen is buried close to the silicon surface. For CMOS applications, it is demonstrated that this decreases the resistance by an increase in channel mobility [2]–[7]. In the CFP approach, a contact module which is normally used for connecting the source, drain and body, is used as a field plate on top of the drain-extension [8]. This can be used to both optimize the R<sub>ON</sub>A and BV, while no additional masks or process changes (i.e. costs) are needed [9], [10]. For both concepts a full wafer lot was set up, in which the OIL concept is applied to the full range of devices available in the technology platform whereas the CFP concept was only suitable for the 12V device. In addition, for both concepts also simulations are set up in Synopsys Sentaurus<sup>TM</sup> TCAD (Technology Computer-Aided Design), which for the OIL concept are mainly focused on properly integrating the film and for the CFP concept on obtaining electrical characteristics.

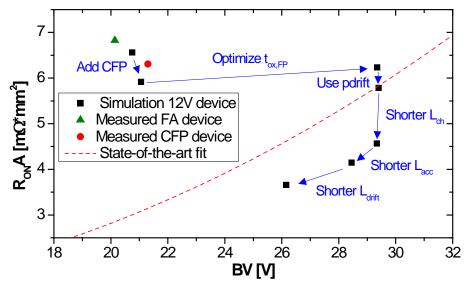

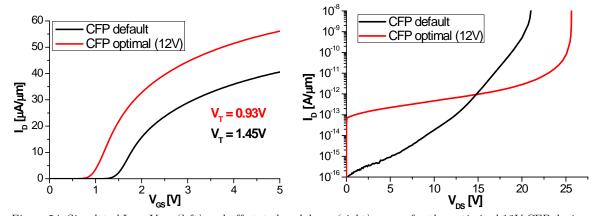

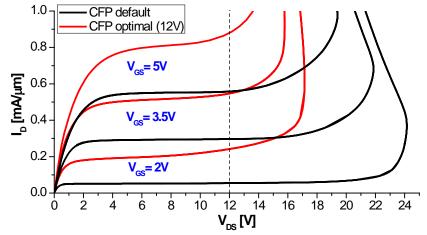

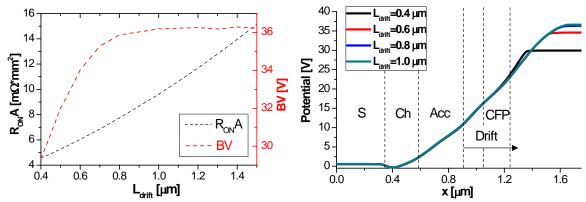

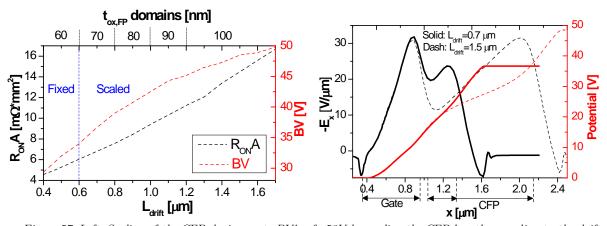

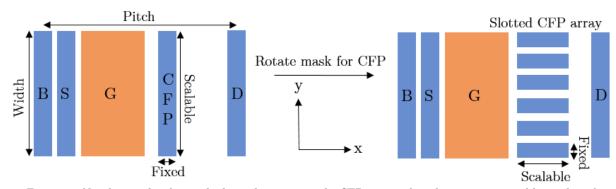

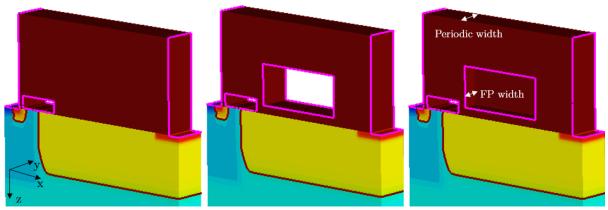

On the wafer lot with the OIL experiments, extensive electrical analysis's have been performed. However, the results that are obtained (which are omitted in this public report for confidentiality reasons) are not conclusive yet. From the wafer lot with the CFP experiments, it became evident from electrical measurements and simulations that the devices were far from optimized. For the BV, the crucial parameter turned out to be the oxide thickness below the CFP ( $t_{ox,FP}$ ), which in this wafer lot was believed to be significantly below the optimum. For the R<sub>ON</sub>A, significant room for improvement is in reducing the lateral dimensions, especially that of the channel. Finally, to show how the CFP devices can be optimized, without using any additional masks (i.e. costs), optimizations are proposed by simulations for the initial 12V application as well as for higher voltages. For the initial (12V) application, the R<sub>ON</sub>A is reduced by ~40% resulting in a device that has the potential to beat state-of-the-art devices by ~20%. Using the same architecture, BV's up to ~35V can effectively be achieved by appropriate scaling of the drain-extension and  $t_{ox,FP}$ . Scaling effectively to higher voltages requires a newly proposed CFP architecture, in which multiple (rotated) contacts are placed in an array along the width of the device.

So, simulation results showed that utilizing the CFP concept and subsequent optimization provides a way to beat current state-of-the-art integrated power devices (for BV's<50V) in the existing NXP technology platform. Moreover, if the OIL works as previously published [2]–[7], this concept has the potential to add additional improvement. In order to demonstrate this on silicon, follow-up cycles are needed for both concepts.

## Abbreviations

CMOS Complementary Metal-Oxide-Semiconductor

CMU Capacitance-Measure-Unit

**DIBL** Drain Induced Barrier Lowering

**DIELER** Dielectric

DG Density Gradient

DOS Density Of States

DUT Device Under InvestigationFET Field-Effect Transistor

FP Field Plate

FOM Figure-Of-Merit

FA Free-Analog

GIDL Gate Induced Drain Leakage

HCI Hot Carrier Injection

**HH** Heavy Hole

IC Integrated Circuit

II Impact Ionization

JFET Junction Field-Effect Transistor

LDD Lightly Doped Drain

LDMOS Laterally Diffused Metal-Oxide-Semiconductor

LH Light Hole

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MST Mears Silicon Technology

NPT Non-Punch Through

OIL Oxygen-Inserted Layer

RESURF Reduced SURface Field

PM Partial Monolayer

PCM Process Control Monitoring

PT Punch Through

SIMS Secondary Ion Mass Spectroscopy SiProt Silicon Protection layer of oxide

SMU Source-Measure-Unit SRH Schockley-Read-Hall

SO Spin-Orbit

SOA Safe Operating Area

SSRW Super-Steep-Retrograde-Well STI Shallow Trench Isolation

TCAD Technology Computer-Aided Design

**TED** Transient Enhanced Diffusion

**TEM** Transmission Electron Microscopy

# Contents

| Chapter            | : 1:     | Introduction and motivation                             | 1  |

|--------------------|----------|---------------------------------------------------------|----|

| 1.1                | Mar      | ket demand                                              | 2  |

| 1.2                | Nov      | el device concepts                                      | 3  |

| 1.3                | Obje     | ective and outline                                      | 5  |

| Chapter            | 2:       | Theoretical background                                  | 6  |

| 2.1                | Basi     | c semiconductor device physics                          | 7  |

| 2.1.               | .1 MO    | SFET                                                    | 8  |

| 2.1.               | .2 Cur   | rent characteristics of a MOSFET                        | 9  |

| 2.1.               | .3 Brea  | akdown in a MOSFET                                      | 11 |

| 2.2                | LDN      | MOS integrated power devices                            | 12 |

| 2.2.               | .1 On-   | state resistance                                        | 13 |

| 2.2.               | .2 Off-  | state breakdown voltage                                 | 15 |

| 2.2.               | .3 Tra   | ditional trade-off                                      | 17 |

| 2.3                | Imp      | roving breakdown - RESURF                               | 17 |

| 2.3.               | .1 Fiel  | d plate assisted RESURF                                 | 19 |

| 2.3.               | .2 June  | ction assisted RESURF                                   | 20 |

| 2.3.               | .3 Ove   | rview current industry standard                         | 21 |

| 2.4                | Imp      | roving on-state resistance - channel mobility           | 22 |

| 2.4.               | .1 Silio | con band structure in the inversion layer               | 24 |

| 2.4.               | .2 Oxy   | gen-inserted layer technology                           | 25 |

| 2.4.               | .3 OIL   | technology - Processing                                 | 26 |

| 2.4.               | .4 OIL   | technology - Super-Steep-Retrograde-Well doping profile | 28 |

| 2.4.               | .5 OIL   | technology - Quasi-confinement                          | 29 |

| 2.4.               | .6 OIL   | technology - LDMOS                                      | 30 |

| $\mathbf{Chapter}$ | 3:       | Simulation methodology                                  | 32 |

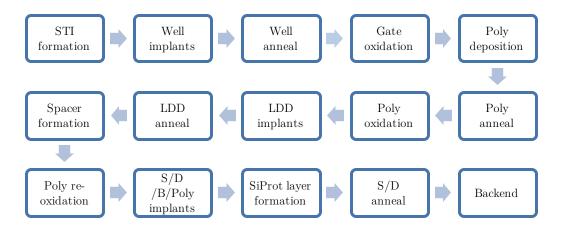

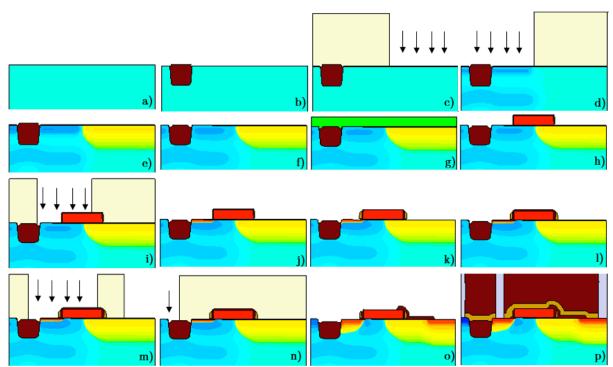

| 3.1                | Proc     | eess simulation                                         | 33 |

| 3.1.               | .1 Pro   | cess flow                                               | 33 |

| 3.1.               | .2 Exa   | mple process simulation                                 | 33 |

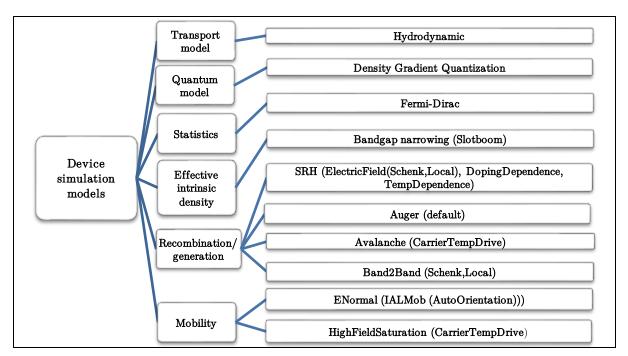

| 3.2                | Dev      | ice simulation                                          | 35 |

| 3.2.               | .1 Phy   | sical models                                            | 35 |

| 3.2.               | .2 Elec  | etrical simulations                                     | 37 |

| Chapter 4:            | Experimental methodology            | 39 |

|-----------------------|-------------------------------------|----|

| 4.1 Exp               | perimental setup                    | 40 |

| 4.1.1 Pro             | be station                          | 40 |

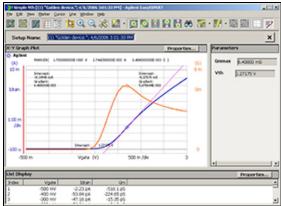

| 4.1.2 De              | vice analyzer and software          | 41 |

| 4.2 Me                | asurement routines                  | 42 |

| 4.2.1 Bas             | sic electrical measurements         | 42 |

| 4.2.2 Rel             | liability measurements              | 42 |

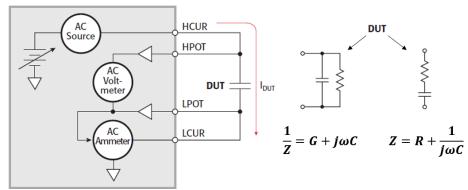

| 4.2.3 Ca <sub>1</sub> | pacitance measurements              | 43 |

| Chapter 5:            | Oxygen-inserted layer devices       | 44 |

| 5.1 Sur               | nmary                               | 45 |

| Chapter 6:            | Contact field plate devices         | 47 |

| 6.1 Dev               | vices                               | 48 |

| 6.2 Res               | sults                               | 49 |

| 6.2.1 Bas             | sic electrical measurements         | 49 |

| 6.2.2 Ele             | ectrical dependencies on dimensions | 54 |

| 6.2.3 Res             | sistance contributions              | 57 |

| 6.2.4 Rel             | liability                           | 58 |

| 6.2.5 Por             | wer losses                          | 60 |

| 6.3 Opt               | timization                          | 63 |

| 6.3.1 12V             | √ application                       | 63 |

| 6.3.2 Hig             | gher voltage applications           | 65 |

| 6.3.3 Ov              | erview - R <sub>ON</sub> A-BV       | 70 |

| Chapter 7:            | Conclusion                          | 71 |

| Chapter 8:            | Outlook                             | 72 |

| Bibliography          |                                     | 74 |

| Appendices            |                                     | a  |

| Appendix .            | A: LDMOS resistance model           | a  |

| A.1 Flat              | band voltage in accumulation region | a  |

| A.2 Resi              | stance separation method            | b  |

| Appendix              | B: Derivations                      | d  |

| B.1 1D k              | oreakdown approximation analysis    | d  |

| B.2 Idea              | l 1D trade-off drift region         | d  |

| B.3 Idea              | l RESURF trade-off drift region     | f  |

| Appendix              | C: Supporting simulations CFP       | g  |

## Chapter 1:

## Introduction and motivation

The High Voltage and Power Technology group within NXP is responsible for developing and enabling new integrated high voltage and power semiconductor technologies. Besides the design of devices, this group is also responsible for the industrialization. Many device types over a wide application range are already delivered by this group which compete at the highest level of power technology in the market. In order to stay one of the market leaders in power technology, the devices should be continuously improved and/or new novel device concepts should be designed. Therefore, a long-term innovation project is initiated within this group. The goal of this project is to propose/demonstrate device concepts that outperform current state-of-the-art integrated power devices in the range up to 50V off-state breakdown, which also have the potential to be integrated in the existing NXP technology platform. Here the specific on-state resistance (on-state resistance times area on the wafer) and the off-state breakdown voltage are the key design targets. In order to obtain a clear overview of possibilities to improve these key design targets, a literature study is conducted. From this literature study, some promising concepts are selected and further explored by simulation and/or experiment in this work.

In this chapter, first the context for the need of this research will be provided. Thereafter, it will be discussed which concepts are currently known from literature to improve integrated power devices and which are particularly explored in this work. Lastly, the objective will be defined and the outline of this thesis will be shown.

#### 1.1 Market demand

The continuous integration of sophisticated electronic technologies like mobile phones and computers in today's modern society, puts more and more demands on current technology. Since the heart of most electronic devices consists of an Integrated Circuit (IC), these must be continuously improved. In order to increase the capacity and the functionality of these IC's, the number of transistors per IC must be increased. One way to do this, is to shrink the size of the transistor. Not only this decreases the cost per transistor, but also lowers the power consumption while the speed and memory capacity go up [11]. Therefore, miniaturization is nowadays without a doubt the largest research interest within the semiconductor industry. Integration of inherently novel 2D/3D device architectures, materials with superior characteristics and/or band structure engineering have gradually become a requirement to keep up with the surprisingly long-lasting prediction set by Moore in 1965 [12]. Yet, for the power semiconductor industry, some of these innovative design trends already became necessary long before their low power counterparts. The range of power semiconductor devices is generally very broad and contains everything from the high power (>10 MW) low switching speed thyristors, the mid-range (1 kW - 1 MW) insulated gate bipolar transistors, to the low power (<1 kW) high switching speed double diffused MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) [9], [13]. Besides the applicable range, power devices can further be subdivided by their orientation. Discrete power devices are vertically oriented such that their drain contact is at the bottom. Integrated power devices on the other hand, are laterally oriented demanding their drain contact at the top. The focus in this research is on integrated power devices in the lower end of the power spectrum, covering the standard (symmetric) MOSFET's suited for low voltage applications and the (asymmetric) Laterally Diffused Metal-Oxide-Semiconductor (LDMOS) devices suited for higher voltage applications.

Power devices are generally used as switches in power conversion systems, where by periodically switching the input current from the source the waveform can be converted and matched to the requirements of the load [10], [13]. An important requirement for such a switch, is that it can sustain a large voltage with minimal leakage current when it is open (off-state). This is generally done by using a so-called drain-extension, which is an extension between the channel and the drain of a MOSFET structure designed to support a large voltage drop. Therefore, an important figure-of-merit (FOM) used to classify the blocking capability of power devices, is the off-state breakdown voltage (BV). Another important requirement for a switch, is that it must be able to handle large currents when it is closed (on-state) with minimal static power dissipation [10], [13]. Therefore, the on-state resistance (R<sub>ON</sub>) between the terminals (i.e. the source and drain), must be as low as possible. The specific on-state resistance (R<sub>ON</sub>A), where A is the device area on the wafer, additionally takes the device dimensions into account [9]. As this indirectly includes the costs of on wafer implementation, R<sub>ON</sub>A is typically used as another important FOM for power devices [9], [14].

So clearly, in optimizing power devices, the BV and  $R_{ON}A$  are the main two key design targets. These design targets however, are both related to the doping concentration and to the length of the drain-extension. This results in that  $R_{ON}A$  increases super linearly with the BV, in particular, for 1D LDMOS devices it can be approximated that  $R_{ON}A$  is proportional to  $BV^{11/3}$  [1]. This illustrates that it is extremely hard to improve one of the two without compromising the other. Too overcome this difficulty, many intriguing ideas and concepts for novel power devices are proposed over the years, some of which are already successfully industrialized. In order to explore and identify such novel concepts for LDMOS devices, a literature study is conducted to provide a clear overview for possible device concepts known from literature. The following section summarizes this literature study and elaborates on which novel device concepts are further explored in this work.

### 1.2 Novel device concepts

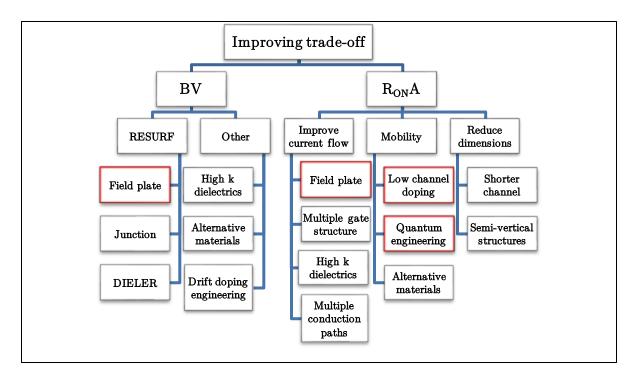

Based on an extensive literature study, an overview is made of novel concepts that can be used to improve the  $R_{ON}A$ -BV trade-off for integrated (LDMOS) power devices (Figure 1). The tree diagram is differentiated in concepts that mainly try to independently improve the BV or the  $R_{ON}A$ , although it must be noted that the two always have a (small) correlation. In the rest of this section, each topic will shortly be discussed.

Figure 1: Schematic tree diagram of novel concepts that are present in the literature to improve the  $R_{ON}A$ -BV trade-off for (LDMOS) power devices. The tree is divided in concepts that mainly try to independently improve the BV or the  $R_{ON}A$ , although it must be noted that the two always have a (small) correlation. The red marked topics are the ones that are further explored in this work.

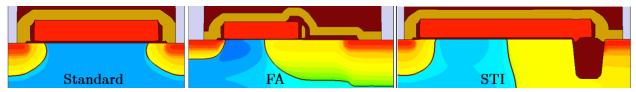

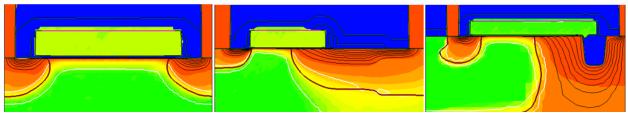

Probably the best-known approach to improve the BV, is by applying so-called RESURF (Reduced SURface Field) [15]. This approach is a collective name for concepts that optimize the lateral electric field distribution in the drain-extension using additional perpendicular fields. There are three typical variations of RESURF: field plate (FP)-, junction- and dielectric (DIELER) RESURF. Field plates are used on top and/or below the drain-extension, where they impose electrostatic boundary conditions. These come in many different variations, such as: extended gate [16], recessed gate [17], metal field plate [8], contact field plate [8], (semi-)resistive field plate [18] or poly field plate [8], [19], [20]. In junction RESURF, one or multiple semiconductor domains are implemented in the drain-extension with opposite doping type to obtain charge balance. Also here variations are possible, such as the number of alternating domains or the dimension in which the junctions are processed [21], [22]. The DIELER RESURF concept employs a structure where the semiconducting material in the drain-extension is interleaved by dielectric layers parallel to the current path. These dielectric layers induce an additional perpendicular capacitance which lowers the lateral electric field [23]–[25].

Other ways to improve the BV, aim to elevate the maximal allowed critical field or to reduce parasitic leakage mechanisms. High k dielectrics, instead of SiO<sub>2</sub>, can be used to reduce gate (or FP) leakage due tunneling suppression [26]. Moreover, high k dielectrics can also be beneficial to improve FP- and DIELER-RESURF [27]. Alternative materials, such as SiC and GaN, have a higher critical field than silicon at which breakdown occurs [14], [28]. The maximum allowed critical field can also be elevated by smart

engineering of the doping concentration in the drain-extension (ideally linearly increasing along the current direction) [29]. Furthermore, this can also be used to optimize the field distribution in RESURF applications [9], [10].

Reducing the R<sub>ON</sub>A by improving the current flow, aims to increase the number of available charge carriers and/or to increase the effective area through which the current flows. A FP can be used to accumulate charge in the drain-extension when a bias is applied, thereby increasing the number of available charge carriers [10]. Multiple gate structures (e.g. FinFET's) both increase the charge density and the effective area through which current flows [30], [31]. To further increase the accumulated charge from gates/FP's, high k dielectrics can be used for the insulating spacer layer to increase the capacitance [32]. Another way to increase the effective area through which current flows, is creating multiple conduction paths from the source to the drain. This can for example be achieved by implementing an additional gate in a trench at the source side, thereby creating an additional (vertical) channel [33].

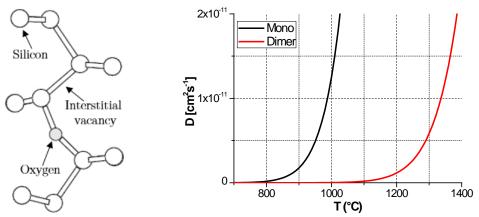

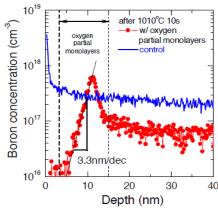

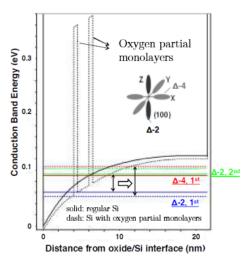

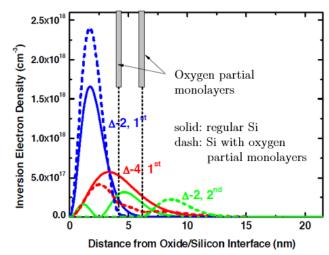

Increasing the mobility for reducing the R<sub>ON</sub>A, can generally be done by reducing scattering events and/or reducing the effective transport mass [34]. A way scattering can be reduced in the channel of MOSFET's, is by ensuring low doping in the channel. This can for example be accomplished by epitaxially growing undoped silicon on diffusion barrier layers, such as carbon doped silicon [35] or oxygen partial monolayers [2]–[7]. Reducing both the effective mass and scattering can be done by changing the quantum mechanical properties of the lattice. Generally, this can be achieved by the use of strain [36], [37] and/or quantization [3]–[7]. Obviously, obtaining better mobility can also be established by using alternative materials with superior transport properties with respect to silicon, such as Ge or GaAs [11], [38].

The last way to improve the R<sub>ON</sub>A, is making the lateral dimensions of the device as small as possible. This is also the most effective way since it both decreases the resistance and the area. While the length of the drain-extension is needed to support a large voltage, the channel region is only used for switching and should be made as small as possible. Ways this can be done are for example using halo implants (i.e. extra doping near the source and/or drain [11], [39]) or using self-aligned source/drain contacts [40]. The area of the device can also be severely reduced by employing semi-vertical structures. This can for example be done by making the channel vertical by integrating the gate in a trench [41] or making part of the drain-extension vertical by integrating a trench in it [42]. This is also done for discrete (vertical) power devices [14], however is much harder for integrated power devices due to requirement of a top drain contact.

Although most of the above discussed concepts have been proven to improve integrated (LDMOS) power devices, industrialization generally remains challenging because of process difficulties and/or large costs. One of the concepts used in this work to improve a LDMOS device is the contact field plate (CFP), which is inspired by L. Wei et al. [8]. In this approach, a contact module which is normally used for connecting the source, drain and body, is placed on top of the drain-extension acting as a field plate. This was proven to improve the reliability, while no additional masks or process changes (i.e. costs) are needed [8]. Additionally, like all FP's, the CFP has also the potential to improve the RonA-BV trade-off which is the main interest in this work.

Another concept that is explored in this work, is oxygen-inserted layer (OIL) technology. This technique is also referred to as Mears Silicon Technology (MST<sup>®</sup>) [43] which is promoted by a company called Atomera. In this technology, a thin film (~10 nm) of reengineered silicon that incorporates partial monolayers of oxygen is buried close to the silicon surface. In doing this, it is demonstrated for CMOS (Complementary Metal-Oxide-Semiconductor) applications that the current performance and reliability of the device go up, while the power consumption and variability go down [2]–[7]. In particular, the main feature of interest is a decrease in resistance due to an increase in channel mobility. This enhancement can be contributed to both quantum engineering and low channel doping. For integrated power devices however, this technology is not demonstrated yet and will be examined for the first time in this work.

### 1.3 Objective and outline

The objective of this thesis is to improve integrated power devices in the existing NXP technology platform to obtain superior R<sub>ON</sub>A-BV trade-off with respect to state-of-the-art devices in the range up to 50V off-state breakdown. For integrated power applications, the technology platform contains both normal MOSFET's suited for the lower voltages and LDMOS devices for the higher voltages. The two concepts that are being explored for improving the devices, OIL- and CFP technology, will be investigated both by simulation and experiment. In addition, the OIL concept is investigated for the full range of devices available in the technology platform (<50V) whereas the CFP concept only is applicable to the 12V Free-Analog (FA) LDMOS type of device.

This thesis is organized as follows:

Chapter 2 provides the essential theoretical background information that is needed to understand this thesis. This chapter will start with the key features of basic device physics, mostly related to the MOSFET. Thereafter, the special class of LDMOS devices as well as their traditional R<sub>on</sub>A-BV trade-off will be introduced. Lastly, the novel ways that are used to improve this trade-off will be explained in more detail.

Chapter 3 focuses on the methodology of the TCAD (Technology Computer-Aided Design) Sentaurus Synopsys<sup>TM</sup> simulation tool used in this work. This simulation tool is used for simulating the processing of devices (e.g. implantation, diffusion and oxidation) as well as for simulating electrical characteristics. This chapter will cover: the most important process steps of NXP's technology platform, an example of a process simulation, the used physical models and the set-up of electrical simulations.

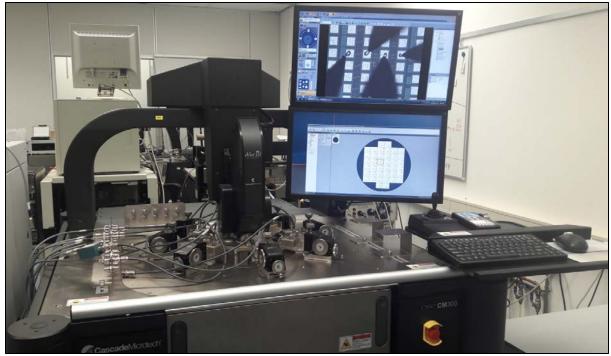

Chapter 4 discusses the experimental methodology that is used to perform electrical measurements on the devices. This includes an elaboration on the hardware setup (probe station and device analyzer) and its use, as well as on the measurement routines that are used to perform a variety of electrical measurements.

Chapter 5 reports on the OIL approach to improve integrated power devices from NXP's technology platform. However, due to confidentially reasons any detailed specifications/results are omitted in this public report. Instead, a summary is given of the proceedings concerning this approach to lower the RonA-BV trade-off. This includes an elaboration on how the wafer lot is set up, which devices are studied, which experiments are performed and how the results are analyzed.

Chapter 6 reports on the CFP approach to improve the 12V FA device from NXP's technology platform. First, it will be discussed what this device looks like with the CFP and what kind of variations are present on the wafer lot. Thereafter, results from electrical measurements will be shown and substantiated by simulations. Lastly, optimized versions will be proposed by simulation for the initial 12V application as well as for higher voltages.

Chapter 7 summarizes the most important conclusions reached in this work and reflects on whether the objective has been accomplished.

Chapter 8 provides an outlook for future work in which specific recommendations are done for potential follow-up work, including additional silicon cycles.

## Chapter 2:

## Theoretical background

The semiconductor industry, which is responsible for the fabrication and design of semiconductor devices, became a profitable business around 1960 [1], [11], [14]. Since that time, it has evolved to a major global industry of almost half a trillion US dollars [44]. One of the reasons it could become so large, is the solid foundation of basic physical understanding of semiconductors, which emerged from successful developments in other fields of physics. By quantum mechanical treatment of the microscopic crystal structure, the energy band structure can be derived which reflects the macroscopic properties of the semiconductor. From this band structure, carrier concentrations can be computed using the Fermi-Dirac distribution derived from statistical thermodynamics. These in turn, can be used to predict measurable quantities such as the current using transport physics. Despite many simplifications made along the way, this approach is capable of reproducing the output characteristics of many semiconductor devices with practical accuracy. Thereby making it a powerful tool for the understanding, development and design of semiconductor devices.

In this chapter, the theoretical background will be covered that is necessary to understand this thesis. The first section serves as introductory theory and recapitulates the most important basic semiconductor device physics. In the section thereafter, attention will be devoted to LDMOS integrated power devices, which are the special class of devices that are of interest in this research. The last two sections elaborate on ways that are used in this work to improve the traditional trade-off for integrated power devices.

### 2.1 Basic semiconductor device physics

One of the biggest advantages of using semiconductors for devices, is that the electrical characteristics can easily be altered by the use of doping (n- or p-type). Moreover, when a junction between a p-type and a n-type semiconductor region is formed, interesting physics arises which is current rectifying in nature. Generally, most semiconductor devices contain at least one such a pn-junction, such that the device characteristics and operation are inherently connected to it. In addition, also most of the terminology and concepts that are used in the analysis of devices also appear in the discussion of the pn-junction. Therefore, before going into more complex devices, some of the most important physics and results of the pn-junction will be briefly recapitulated here.

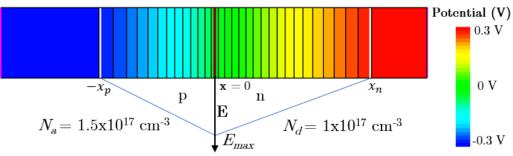

When a uniformly doped p-type material (acceptor doping concentration  $N_a$  [cm<sup>-3</sup>]) forms a junction with a uniformly doped n-type material (donor doping concentration  $N_d$  [cm<sup>-3</sup>]), a very large concentration gradient at the junction for both holes and electrons will exist. Therefore, majority electrons in the n-region will diffuse to the p-region and majority holes from the p-region will diffuse to the n-region. As a result, positive donor charge is left behind in the n-type material and negative acceptor charge in the p-type material (Figure 2). This region is referred to as space charge region or depletion region (ranging from  $-x_p$  [cm] to  $x_n$  [cm]), no mobile charges are present here. The space charge within the depletion region sets up an electric field pointing from the n- to p-region (Figure 2). Consequently, there will be a potential drop along the depletion region which is called the built-in voltage  $(V_{bi} [V])$ . This  $V_{bi}$  produces a drift force  $(\infty -\nabla V)$  that works in the opposite direction as the diffusion force  $(\infty \nabla n \text{ and } \infty \nabla p)$  resulting from the carrier concentration gradient at each edge of the depletion region. In thermal equilibrium, these forces exactly cancel each other (Fermi level constant through the system). [11]

Figure 2: Simulation of a pn-junction at zero bias  $(V_R=0V)$  where  $N_a=1.5x10^{17}$  cm $^3$  and  $N_d=1x10^{17}$  cm $^3$ . Here the color indicates the magnitude of the electrostatic potential, the black lines the equipotential lines, the white lines the depletion boundaries and the brown line the junction boundary between the n-type and p-type material. Also, the electric field distribution is illustrated.

Without rigorous derivation, the most important electrostatic characteristics of an ideal pn-junction with an arbitrary bias  $(V_R \ [V])$  applied to the n-region are given below: [11]

$$\begin{split} V_{bi} &= \frac{k_B T}{e} \ln \left( \frac{N_a N_d}{n_i^2} \right) \\ x_n &= \left( \frac{2\epsilon_s (V_{bi} + V_R)}{e} \left( \frac{N_a}{N_d} \right) \left( \frac{1}{N_a + N_d} \right) \right)^{\frac{1}{2}} & \& \quad x_p = \left( \frac{2\epsilon_s (V_{bi} + V_R)}{e} \left( \frac{N_d}{N_a} \right) \left( \frac{1}{N_a + N_d} \right) \right)^{\frac{1}{2}} & b \\ E(-x_p \leq x \leq 0) &= \frac{-eN_a}{\epsilon_s} (x + x_p) & \& \quad E(0 \leq x \leq x_n) = \frac{-eN_d}{\epsilon_s} (x_n - x) \\ E_{max} &= -\frac{2(V_{bi} + V_R)}{x_n + x_p} & d \end{split}$$

Here E(x) is the electric field distribution [V/cm],  $E_{max}$  the maximum electric field [V/cm],  $\epsilon_s$  the dielectric permittivity (for Si: 11.7 $\epsilon_0$ , where  $\epsilon_0$ =8.85x10<sup>-14</sup> F/cm), e the elementary charge (1.6x10<sup>-19</sup> C),

T the temperature [K],  $k_B$  the Boltzmann constant (1.38x10<sup>-23</sup> J/K) and  $n_i$  the intrinsic carrier concentration (for Si: 1.5x10<sup>10</sup> cm<sup>-3</sup>).

In contrast to Figure 2, in semiconductor devices there will always be a bias applied to the pn-junction such that it is no longer in thermal equilibrium (Fermi level not constant through the system). When  $V_R$  is positive (reverse bias configuration), the total potential barrier becomes larger than the zero-bias case. Moreover, since the electric field originates on positive charge and terminates at negative charge, the number of positive and negative charges in the depletion region must increase. As a result, the space charge width  $(x_n+x_p)$  increases with applied reverse bias voltage (Equation (1b)). The increased potential barrier withholds the majority electrons in the n-region to diffuse into the p-region and the majority holes in the p-region to diffuse into the n-region, such that there is essentially no (significant) current. When  $V_R$  is negative (forward bias configuration), the total potential barrier is lowered. By the same reasoning as before, the depletion width now decreases with increasing applied forward bias voltage. Due to the decreased electric field (or potential barrier) in the depletion region, the electrons in the n-region and holes in the p-region are now no longer held back. Hence, there will be a diffusion current of electrons from the n-to p-region and of holes from the p- to n-region. [11]

So, current can flow through the pn-junction when forward biased but is blocked when reverse biased. This characteristic can easily be used to make an electrical switch (i.e. a transistor) by combining two pn-junctions. The most used transistor in modern IC technology is the MOSFET and will be discussed next.

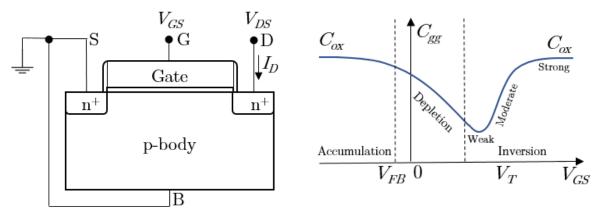

#### **2.1.1 MOSFET**

In general, a MOSFET consists of a source (S), drain (D), gate (G), body (B) and insulating spacer layer below the gate (Figure 3 (left)). The source and drain terminals are both highly doped silicon (n<sup>+</sup> in n-type and p<sup>+</sup> in p-type). The voltage across the channel is applied to the drain such that the current flow corresponds with the carriers (electrons in n-type, holes in p-type) flowing from the source to the drain. The body is respectively p/n-type doped silicon for n/p-channel devices. The gate is a highly conducting material (highly doped polysilicon) on top of an insulating material (generally SiO<sub>2</sub>). In the ideal case, there is no current through the oxide to the gate terminal. In the rest of this section, only the n-channel MOSFET will be considered. For the p-channel MOSFET, the same arguments and relations apply only with holes being the charge carrier and with reversed current directions and voltage polarities.

Figure 3: Left: Schematic representation of a n-channel MOSFET (S=Source, G=Gate, D=Drain and B=Body). Right: Typical low frequency gate capacitance ( $C_{gg}$ ) characteristic of a n-channel MOSFET. Here also the accumulation, depletion and inversion regimes are indicated. [11]

Switching of the device is controlled by the voltage on the gate. The Metal-Oxide-Semiconductor (MOS) structure basically acts as a parallel plate capacitor, such that understanding its behavior can best be understood by looking at the gate capacitance  $(C_{gg})$  as a function of the gate voltage  $(V_{GS})$  (Figure 3 (right)). Depending on the sign of  $V_{GS}$ , the carriers can either be attracted towards the Si-SiO<sub>2</sub> interface

(accumulation) or pushed away from it (depletion) resulting in a space charge region. When  $V_{GS}$  becomes higher than a certain threshold voltage  $(V_T \ [V])$ , the minority carrier concentration (electrons) at the Si-SiO<sub>2</sub> interface becomes higher than the majority carrier concentration (holes) in the bulk, an inversion layer is said to be formed. This inversion layer then "connects" the source and drain regions, such that a current can flow  $(I_D \ [A])$ . A MOSFET is therefore said to be in the off-state when  $V_{GS} < V_T$  and in the on-state when  $V_{GS} > V_T$ .

Clearly, the  $V_T$  is one of the important parameters of the MOSFET since it determines whether the device is in the on- or off-state. Therefore, it should always be within the voltage range of a circuit design. It can mathematically be derived by calculating the gate voltage at which the band bending at the Si-SiO<sub>2</sub> interface is such that the Fermi level  $(E_f)$  is at least as far above the intrinsic Fermi level  $(E_{f,i})$  as  $E_f$  is below  $E_{f,i}$  in the bulk. By considering a simplified electrostatic charge distribution, that is approximately valid for MOSFET structures with long and wide channels, it can be derived that  $V_T$  obeys: [11], [39]

$$V_T = \frac{eN_a x_{dT}}{C_{ox}} + V_{FB} + 2\phi_{fp}$$

where  $x_{dT} = \left(\frac{4\epsilon_s \phi_{fp}}{eN_a}\right)^{\frac{1}{2}}$ ,  $V_{FB} = \phi_{ms} - \frac{Q'_{ss}}{C_{ox}}$  and  $\phi_{fp} = \frac{k_B T}{e} \ln(\frac{N_a}{n_i})$  (2)

Here  $\phi_{fp}$  ([J]) indicates the difference between the Fermi level  $(E_f)$  and the intrinsic Fermi level  $(E_{f,i})$ in bulk. The  $x_{dT}$  ([cm]) represents the maximum space charge width at  $V_{GS} = V_T$ , a higher  $V_{GS}$  only increases the inversion charge density at the interface which shields the electric field from further penetrating the silicon. The flat-band voltage  $V_{FB}[V]$ , is defined as the applied gate voltage at which there is no band bending in the silicon (Figure 3 (right)). The capacitance of the MOS capacitor in the strong inversion regime is denoted by  $C_{ox}$  (Figure 3 (right)), which for a simple parallel plate capacitor is given by  $t_{ox}/\epsilon_{ox}$ , where  $t_{ox}$  ([cm]) and  $\epsilon_{ox}$  ([F/cm]) are the oxide thickness and dielectric permittivity respectively. The work function difference  $(\phi_{ms}([J]))$  must be incorporated since the energy difference between the Fermi energy and the vacuum level will be different for silicon than for the gate material. The  $Q'_{ss}$ term ([C/cm<sup>2</sup>]) represents the effective charge per unit area in the oxide at the Si-SiO<sub>2</sub> interface. This oxide charge is extremely unwanted in MOSFET's, but almost inevitable. Already during fabrication this oxide charge exists by e.g. structural defects (dangling bonds) and ionized impurities [45]. During the lifetime of the device, this oxide charge gets even built up more by e.g. ionizing radiation and injection and trapping of hot (high energetic) carriers in the oxide (HCI) [45], [46]. Therefore, the oxide charge can give rise to large unpredictable shifts and instabilities in  $V_T$ . Moreover, if this charge is closely situated near the Si-SiO<sub>2</sub> interface, the mobility is degraded thereby altering the current characteristics. [11], [39]

#### 2.1.2 Current characteristics of a MOSFET

The basic operation of a MOSFET is modulating the channel resistance by the applied gate voltage. The resistance in the channel depends on the dimensions, the mobility and the inversion charge present. In the on-state for  $V_{DS} < V_{GS} - V_T$ , the following expression then applies for the channel resistance  $R_{ch}$  [ $\Omega$ ]: [11], [14], [39]

$$R_{ch} = \frac{L_{ch}}{W\mu_{ch}|Q'_{inv}|} = \frac{L_{ch}}{W\mu_{ch}C_{ox}(V_{GS} - V_T - V_{DS}/2)} \eqno(3)$$

Here  $L_{ch}$  is the length of the channel and W the width of the device, both in [cm].  $|Q'_{inv}|$  is the inversion layer charge per unit area made up from electrons [C/cm<sup>2</sup>]. This charge is a function of the gate voltage and is given by  $C_{ox}(V_{GS} - V_T - V_{DS}/2)$  in the strong inversion regime.  $\mu_{ch}$  is the effective electron mobility in the inversion channel [cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>]. This mobility is typically a factor two lower than in bulk,

because of additional surface scattering due to the gate induced electric field which accelerates the inversion carriers to the surface [14]. In section 2.4, more attention will be devoted to the channel mobility.

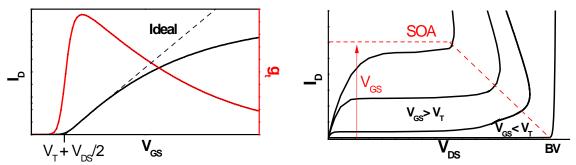

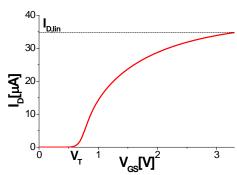

So, when a small drain voltage is applied  $(V_{DS} \to 0)$  and the gate voltage is increased, the inversion charge density starts to increase linearly from  $V_T + V_{DS}/2$  (Equation (3)) such that also  $I_D$  increases ideally linearly (Figure 4 (left)). This purely linear increase however, is not entirely true. Already below  $V_T + V_{DS}/2$  there will be some current flow, which is referred to as subthreshold conduction. This is because before reaching the inversion point, the channel is in the weak/moderate inversion regime (Figure 3 (right)) where  $E_f$  is closer to the conduction band than to the valence band such that the channel has the characteristics of a lightly doped n-type semiconductor. So MOSFET's should always be biased sufficiently below the  $V_T$  in the off-state to minimize off-state power dissipation. Moreover, since the mobility degrades with  $V_{GS}$  (section 2.4), the slope of the  $I_D - V_{GS}$  curve (i.e. the transconductance  $(g_t)$ ) decreases (Figure 4 (left)). [11], [46]

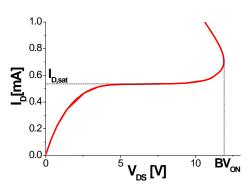

Figure 4: Left: Example of drain current and transconductance as a function of the gate voltage. Also, the ideal drain current is indicated. Right: Example of drain current as a function of the drain voltage for increasing gate voltage. Outside the Safe Operating Area, the current increases uncontrollably due to breakdown mechanisms.

When now  $V_{GS}$  is held constant and  $V_{DS}$  is increased, the typical curves shown in (Figure 4 (right)) are obtained. In the on-state, for  $V_{DS} \to 0$ , the channel acts as an Ohmic resistor (Equation (3)) where the initial slope  $(R_{ch}^{-1})$  is determined by  $V_{GS}$ . As  $V_{DS}$  starts to increase, the voltage drop at the drain side across the oxide decreases, such that the inversion charge density decreases locally. As a result, the incremental resistance increases with increasing  $V_{DS}$  up to the point where the voltage drop across the oxide at the drain is equal to  $V_T$ , such that the inversion charge density becomes zero at the drain terminal (pinch-off). If  $V_{DS}$  increases further, the point where the inversion charge becomes zero moves to the source. At this point electrons are injected into the space charge region and subsequently drift to the drain. For large channels, the drain current then will be constant after the pinch-off. Therefore, the MOSFET is said to be operating in the saturation regime for drain voltages larger than  $V_{DS}(sat) = V_{GS} - V_T$ . In this regime, as well as in the linear regime, the ideal current-voltage relationships follow from the square-law model and are given by: [11], [14], [39]

$$\begin{split} V_{DS} < V_{DS}(sat) \colon & I_D = \frac{W \mu_{ch} C_{ox}}{2 L_{ch}} (2 (V_{GS} - V_T) V_{DS} - V_{DS}^2) \\ V_{DS} > V_{DS}(sat) \colon & I_D = \frac{W \mu_{ch} C_{ox}}{2 L_{ch}} (V_{GS} - V_T)^2 \end{split} \tag{4}$$

It must be noted that these equations do not include non-idealities such as: subthreshold conduction, channel length modulation, mobility variation and velocity saturation. These and other non-idealities however, become only significant for short channel devices [11]. Power devices typically have relatively long channels such that these non-idealities have little influence. In addition, from (Figure 4 (right)) it can also be seen that these equations only hold in the so-called Safe Operating Area (SOA). Outside this regime, the current starts to increase uncontrollably and the device is said to be in breakdown.

#### 2.1.3 Breakdown in a MOSFET

In a MOSFET, several current generation mechanisms must be considered that can make the device go into breakdown. They all have in common that they start occurring when high electric fields are present. The electric fields are generally the highest at pn-junctions and at semiconductor-oxide interfaces, which are therefore the most profound locations for breakdown to set in.

The most destructive physical mechanism, is impact ionization occurring in depleted regions with high electric fields (such as in the reverse biased pn-junction at the drain side). This is the process in which electron-hole pairs are generated by impact of silicon atoms by hot carriers. This is particularly harmful because the generated charge carriers in turn can ionize other silicon atoms resulting in charge carrier multiplication. The efficiency of this process (in 1D) can be expressed by the charge multiplication factor (M): [11], [47]

$$M = \int_0^{W_d} \alpha(E) dx \tag{5}$$

Here  $W_d$  is the depletion width [cm] and  $\alpha$  the reciprocal of the mean free path between two impact ionizations also called the ionization coefficient [cm<sup>-1</sup>]. Note that here it is assumed that the ionization coefficient for electrons is the same as for holes (i.e.  $\alpha_n = \alpha_p = \alpha$ ). This coefficient is a strong exponential function of the electric field as dictated by Chynoweth's law [14]. For analytic derivations however, Chynoweth's law is often approximated by Fulop's power law for silicon:  $\alpha = 1.8 \cdot 10^{-35} E^7$  [14].

The charge multiplication process, depending on M, can result in two destructive breakdown mechanisms. The typical breakdown mechanism considered occurs for  $M \geq 1$  and is called avalanche breakdown. In avalanche breakdown, each charge carrier at least ionizes one other atom thereby resulting in a self-amplifying (uncontrollable) current. For M < 1 on the other hand, before avalanche breakdown sets in, snapback breakdown may already make the device uncontrollable. This is a second order effect caused by the parasitic bipolar (npn) formed by the source-body-drain structure. While the generated electrons flow to the drain, the holes flow to the body terminal resulting in a voltage difference between the source and body due to the resistance of the body. This may forward bias the source-body junction resulting in a positive feedback loop. Part of these injected electrons then diffuse to the drain resulting in a positive feedback loop. This type of breakdown can be recognized by a negative slope in the  $I_D - V_{DS}$  curve, as can be seen in Figure 4 (right). Both the impact ionization based breakdown mechanisms are considered as abrupt on the  $I_D - V_{DS}$  curve due to the self-amplifying nature. [11], [47]

Next to the previously discussed abrupt breakdown mechanisms, there are also more subtle mechanisms that are typically less destructive. One of them is (near) punch-through breakdown. Punch-through is the effect when the depletion region of the drain junction fully extends to the depletion region of the source junction. In that case, the energy barrier between the source and drain is completely gone resulting in a large drain current. Although, also already before punch-through is reached, the drain current rapidly starts to increase. This is due to a phenomenon called drain induced barrier lowering (DIBL), which is the lowering of the energy barrier due to the interaction of the source and drain depletion regions. Since the drain current depends exponential on the barrier height, the current increases rapidly with  $V_{DS}$  when the near punch-through condition is reached. This breakdown mechanism can be suppressed by using extra doping in the body near the source and the drain, which are also called halo implants. [11], [39]

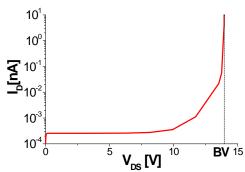

Another subtle breakdown mechanism is Gate Induced Drain Leakage (GIDL). This drain leakage mechanism is due to quantum mechanical band-to-band tunneling. In the presence of high electric fields ( $\sim > 80 \text{ V/µm}$ ), such as in heavily doped pn-junctions or MOS structures, phonon-assisted band-to-band tunneling generally cannot be neglected. GIDL in particular, relates to the band-to-band tunneling near the Si-SiO<sub>2</sub> interface below the gate which becomes significant when there is a large voltage difference between the drain and the gate. This leakage mechanism is typically the most dominant one before impact ionization based breakdown mechanisms set in. [47], [48]

An elegant approach to reduce breakdown effects, without affecting the device's geometry or dimensions, are LDD (Lightly Doped Drain) implants [11], [39]. In this approach, lightly doped regions are situated next to the drain and the source of the same type of doping. The reduced doping gradient in going from the channel to the source/drain lowers the (peak) electric field and thereby reduces breakdown effects. This type of concept is actually also used for (LDMOS) power devices, in which the drain is extended by a lower doped region to achieve high breakdown voltages.

## 2.2 LDMOS integrated power devices

Integrated power devices need to handle large currents in the on-state and reach high (off-state) breakdown voltages. One way to accomplish this, would be by simply upscaling the standard MOSFET structure. This however, is beyond certain voltages not a cost-efficient and straightforward way to increase the voltage and current handling capabilities. For example, if the off-state breakdown voltage and the device dimensions are to be scaled with a factor k (>1), the doping in the substrate should be scaled with  $k^{-1}$  (<1) [11]. This leads to large modifications in  $V_T$  (Equation (2)). Moreover, the mobility in the inversion channel is relatively low compared to the bulk mobility [14], such that an even longer inversion channel would not be efficient. Therefore, generally the way to go for power devices is a drain-extension. This is a lowly doped region connecting the channel with the drain, with respectively n/p-type doping for a n/p-channel MOSFET. For integrated applications, such a device is typically called a LDMOS (laterally diffused MOS) and is shown in the left figure below. It should be mentioned that this name convention originally refers to devices in which the channel is implemented by lateral diffusion, however is nowadays generally also used to refer to drain-extended devices fabricated by other techniques as well [49].

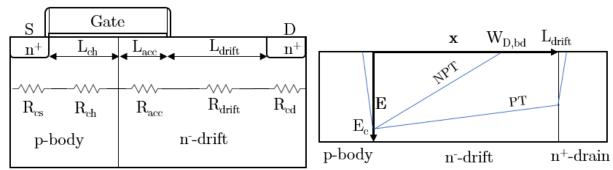

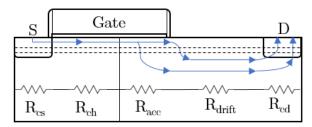

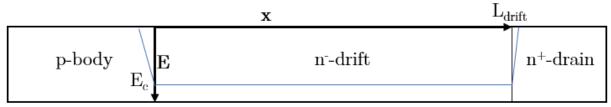

Figure 5: Left: Schematic illustration of a LDMOS power device, which has a lowly doped drain-extension that connects the channel to the drain. Here also the different series resistance contributions are indicated. Right: Schematic illustration for a simplified 1D off-state breakdown analysis of the LDMOS device (in which  $L_{acc}$  can be set to zero) for both the NPT (non-punch through) condition and the PT (punch through) condition.

Just as in the normal MOSFET, for sufficient gate bias an inversion layer forms in the p-body below the gate in which electrons are injected for  $V_{DS}>0$ . Only now after passing through the inversion layer, the electrons flow into the drain-extension where they are accelerated to the drain by the electric field. Commonly, there is also some gate overlap on the drain-extension ( $L_{acc}$ ), as depicted in Figure 5 (left). In the on-state, this enhances the population of charge carriers near the surface (accumulation), which can be beneficial for the resistance. In the off-state, this extended gate works as a field plate which optimizes the electric field in the drain-extension and thereby increases the off-state breakdown voltage (subsection 2.3.1 will go more into detail about field plates). [1]

In order to handle large currents in the on-state and to block large drain-to-source voltages in the offstate, both the on-state resistance (R<sub>ON</sub>) and the off-state breakdown voltage (BV) must be optimized as much as possible without compromising the other. This is therefore the main task in designing power devices (for switching applications). Hence, in the rest of this section these two key design targets will be discussed in more detail for the LDMOS power device.

#### 2.2.1 On-state resistance

The R<sub>ON</sub> of the LDMOS can be decomposed in several contributing resistances, as shown in Figure 5 (left). These resistances are in series such that for R<sub>ON</sub> [ $\Omega$ ] in the linear regime ( $V_{DS} < V_{DS}(sat)$ ), the following equation can be written: [50]

$$R_{ON} = \frac{\partial V_{DS}}{\partial I_d} = R_{cs} + R_{ch} + R_{acc} + R_{drift} + R_{cd}$$

$$\tag{6}$$

The typical drain bias that is used in NXP's technology platform to measure the  $R_{ON}$  in this regime is 0.1V at full gate drive. The advance of measuring (and modeling) in this regime is that non-idealities caused by significant drain bias are limited [11], [46]. For example, for a small channel length of 0.2  $\mu$ m the lateral field is 0.5 V/ $\mu$ m, which is significantly below the 3 V/ $\mu$ m at which the electron velocity starts to saturate [46]. The limitation of this and other non-idealities makes it relatively easy to obtain expressions for the individual resistance contributions:

Source and drain resistance ( $R_{cs} + R_{cd} = R_{sd}$  [ $\Omega$ ])

These resistances consist of the metal-silicon contact resistances (which depend on the work function of the metal and the doping concentration at the surface) and of the resistances in the highly doped source/drain regions itself [14]. These resistances are relatively small and are only weakly dependent on the terminal voltages [46], such that for simplicity they are assumed to be constants.

#### Channel resistance $(R_{ch} [\Omega])$

The channel resistance  $(R_{ch})$  for an intrinsic MOSFET was already given by Equation (3). However, the correction for the average channel potential  $(-V_{DS}/2)$  is not valid for a LDMOS device since there is an additional voltage drop over the drain-extension. The resistance of the drain-extension  $(R_{acc}+R_{drift})$  is typically must larger than  $R_{ch}$ , such that the average channel potential safely can be omitted for a low drain bias (such as  $V_{DS}$ =0.1V). The channel resistance is then given by: [14], [50]

$$R_{ch} = \frac{L_{ch}}{W\mu_{ch}|Q'_{inv}|} = \frac{L_{ch}}{W\mu_{ch}C_{ox}(V_{GS} - V_{T})} \tag{7}$$

Accumulation resistance ( $R_{acc}$  [ $\Omega$ ])

The accumulation resistance  $(R_{acc})$  is the resistance in the silicon area where the gate or field plate overlaps the drain-extension and in literature is most commonly expressed as: [14], [50]

$$R_{acc} = \frac{L_{acc} K_{acc}}{W \mu_{acc} |Q'_{acc}|} = \frac{L_{acc} K_{acc}}{W \mu_{acc} C_{ox} (V_{GS} - V_T)}$$

(8)

Here  $K_{acc}$  is a factor (<1) to account for current spreading [-],  $L_{acc}$  the length of the accumulation region [cm],  $|Q'_{acc}|$  the accumulation charge per unit area [C/cm²] and  $\mu_{acc}$  the mobility in the accumulation layer [cm²V-¹s⁻¹]. The mobility in the accumulation layer is generally higher than in the inversion layer, since the charge carriers are distributed further from the interface than in the inversion layer [14], thereby reducing surface roughness scattering. It has been reported to be ~80% of the bulk mobility [14].

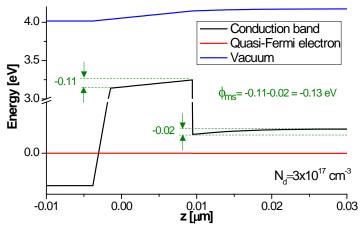

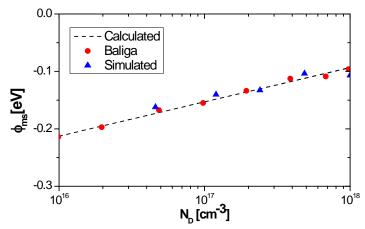

Although Equation (8) describes an inverse  $V_{GS}$  dependence as is expected for accumulated charge, one consideration on which this equation is based may not be fully valid in this work. Namely, it is assumed that the accumulation charge is built up from the channel threshold voltage. Obviously, this is theoretically not true because the charge is accumulated from the flat-band voltage  $(V_{FB})$  of the accumulation layer [51], [52]. So, unless  $V_{T,channel} \approx V_{FB,accumulation\ layer}$ , this equation cannot be assumed to be trustworthy. In Appendix A.1, it is shown how  $V_{FB}$  can be calculated and what values can be expected for the

accumulation regions in this work. For a typical donor doping concentrations of  $10^{17}$  cm<sup>-3</sup>,  $V_{FB}$  is approximately -0.15V [14]. Typical threshold voltages are in the range from 0.5 - 1.5V, so clearly the condition does not apply. The alternate proposal for the accumulation resistance would then be:

$$R_{acc}^* = \frac{L_{acc} K_{acc}}{W \mu_{acc} C_{ox} (V_{GS} - V_{FB})} \tag{9}$$

One final thing that should be mentioned about Equations (8) and (9), is that it is assumed that the accumulation region is not biased (or equivalently  $V_{DS} \rightarrow 0$ ). Taking this into consideration, would effectively increase  $V_{FB}$  by the average potential in the accumulation region  $(\overline{V_{acc}})$ . For a low drain bias however (such as  $V_{DS}$ =0.1V),  $\overline{V_{acc}}$  is typically negligible because most of the voltage is already supported over the drift region.

Drift resistance  $(R_{drift} [\Omega])$

The resistance of the drift region is just that of a doped semiconductor sheet and is typically expressed as: [50]

$$R_{drift} = \frac{L_{drift}}{eN_d \mu_n d_{eff} W} \tag{10}$$

Here  $d_{eff}$  is the effective well thickness in the drift region to account for the unequal distribution of the current flow in the drift region (current spreading) [cm],  $L_{drift}$  the length of the drift region [cm],  $N_d$  the donor concentration in the drift region [cm<sup>-3</sup>] and  $\mu_n$  the bulk mobility appropriate to  $N_d$  [cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>]. This equation implies that  $R_{drift}$  is constant and independent of any of the terminal voltages, which is particularly true in the limit that  $V_{DS} \rightarrow 0$ . If however this limit is not valid,  $R_{drift}$  is typically related to  $V_{DS}$  and  $V_{GS}$  by phenomena such as the Kirk effect, JFET resistance (subsection 2.3.2), self-heating and quasi saturation (velocity saturation in drift region) [53]–[55]. For this work, it is assumed that  $V_{DS}$ =0.1V is sufficient low for this simplification to be usable.

Total resistance  $(R_{ON}/\Omega]$ )

Filling in all the resistance contributions (Equations (7), (9) and (10)) in Equation (6) and setting  $R_{cs}+R_{cd}=R_{sd}$ , gives the following expression for  $R_{ON}$  valid for low drain bias:

$$R_{ON} = \frac{L_{ch}}{W\mu_{ch}C_{ox}(V_{GS} - V_T)} + \frac{L_{acc}K_{acc}}{W\mu_{acc}C_{ox}(V_{GS} - V_{FB})} + \frac{L_{drift}}{eN_d\mu_n d_{eff}W} + R_{sd} \tag{11} \label{eq:Ron}$$

It must be mentioned that in this equation the mobility reduction with increasing  $V_{GS}$  in inversed/accumulated layers is not accounted for. These mobility reductions are typically modeled as: [46]

$$\mu_{ch} = \frac{\mu_{0,ch}}{1 + \theta_{ch}(V_{GS} - V_T)} \quad \& \quad \mu_{acc} = \frac{\mu_{0,acc}}{1 + \theta_{acc}(V_{GS} - V_{FB})}$$

(12)

Here  $\mu_{0,ch}$  and  $\mu_{0,acc}$  are the zero-field bulk mobilities in the channel and accumulation region respectively  $[{\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}]$  and  $\theta_{ch}$  and  $\theta_{acc}$  are technology defined constants [-]. Including these in Equation (11) would result in two additional (constant) series resistances proportional to the  $\theta$  constants, which have the same effect on  ${\rm R}_{\rm ON}\left(V_{GS}\right)$  as  $R_{sd}$  and  $R_{drift}$ .

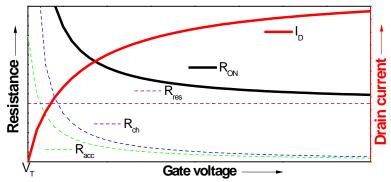

To give an impression of the influence of the various resistance contributions on the  $R_{ON}$  and on the linear drain current as a function of  $V_{GS}$ , Equation (11) is used to generate an example which is shown in Figure 6. Here  $R_{res}$  denotes the constant resistance contributions. From Figure 6, it can be seen that after the current rises rapidly due to the fast decrease in  $R_{ch}$  and  $R_{acc}$ , its starts to saturate because  $R_{res}$  becomes

dominant. Typically, especially for large drift regions,  $R_{drift}$  will be the largest contribution to  $R_{res}$ . Therefore, for proper modeling of LDMOS devices, incorporation of the mobility reduction with increasing  $V_{GS}$  is not as crucial as for standard MOSFET's.

Figure 6: Typical example of the  $R_{\rm ON}$ , as well as its contributions, and the linear drain current as a function of  $V_{\rm GS}$  for a n-type LDMOS device. The current starts rising rapidly due to the fast decrease in  $R_{\rm ch}$  and  $R_{\rm acc}$  and eventually saturates because  $R_{\rm res}$  becomes dominant. Here  $R_{\rm res}$  denotes the constant resistance contributions ( $R_{\rm sd}$  and  $R_{\rm drift}$ ). In addition, also the mobility reduction in inversed/accumulated layers can be incorporated in  $R_{\rm res}$ , although can typically be neglected with respect to  $R_{\rm drift}$ .

It must again be noted that Figure 6 is just an example. The distribution of the various contributions to the total resistance very depends on the application voltage. For high breakdown voltages (>25V), the drift region will be relatively long such that  $R_{drift}$  will be dominant [50]. For lower breakdown voltages however, the drift region will be short such that  $R_{ch}$ ,  $R_{acc}$  and  $R_{drift}$  may be on the same order [50]. The relative contributions to the resistance are particularly of interest for identifying possibilities for optimization. In Appendix A.2, a method is proposed to separate the different resistance contributions in a LDMOS device based on the theory in this subsection.

To compare the total on-state resistance of power devices, it is convenient to use the specific on-state resistance ( $R_{ON}A$  [ $m\Omega \cdot mm^2$ ]), which was already stated to be an important FOM in section 1.1. This is just the  $R_{ON}$  multiplied by its surface area (A), in which the total length of the device (pitch) is the distance from the middle of the body contact to the middle of the drain contact (since the body and drain contacts are shared). The other important FOM, namely the BV, will be discussed next.

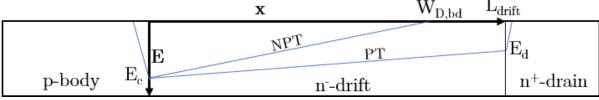

#### 2.2.2 Off-state breakdown voltage

When the LDMOS device is in the off-state and a positive drain voltage is applied, the junction between the body and the drain-extension is reverse biased. The doping of the drain-extension is typically lower than that of the channel region, such that the junction is usually assumed to be one-sided (i.e.  $p^+n$  or  $pn^-$ ). As a result, the depletion region mainly extends into the drain-extension (Equation (1b)), such that most of the applied voltage is supported there. Depending on the length of the drain-extension and its doping, two situations can then be considered. The non-punch through situation (NPT), in which the electric field at the drain edge remains zero. And the punch-through condition (PT), in which the depletion region fully extends to the drain such that the electric field at the drain edge is non-zero. In Figure 5 (right), these situations are sketched for a simplified 1D off-state breakdown analysis. Note that  $L_{acc}$  is set to zero here as the influence of the gate can be neglected in one dimension. Most devices are generally designed to operate in the PT condition, since this yields better  $R_{ON}A$ -BV trade-off (as will be shown in Appendix B.2) [1]. However, breakdown related relations are typically only derived for the NPT case since this results in much more manageable expressions. Moreover, these are independent of  $L_{drift}$ , such that a closed form equation can be obtained for the  $R_{ON}A$ -BV trade-off. [1], [14], [56]

For the NPT case, using Equation (1c) (in the limit that  $N_d \to 0$ ) together with Fulop's approximation, it can then be derived by using Equation (5) (with M=1) that the BV due to avalanche breakdown and corresponding depletion width  $(W_{D,bd})$  for silicon are given by: (derivation in Appendix B.1) [14]

$$BV = 5.34 \cdot 10^{13} \cdot N_d^{-\frac{3}{4}} \tag{13}$$

$$W_{D\,,bd} = 2.67 \cdot 10^{10} \cdot N_d^{-\frac{7}{8}} \tag{b}$$

Here  $N_d$  denotes the donor concentration of the lowly doped drift region [cm<sup>-3</sup>]. Note that this BV only applies for a one-sided planar junction. In practice, the junction between the drain-extension and the body can be curved which enhances the electric field at the edges. This limits the breakdown to about 80% of the planar junction [14].

Generally, the voltage drop over the drift region can be obtained by integrating the electric field over the drift region:

$$V_{drift} = -\int_0^{L_{drift}} \vec{\boldsymbol{E}} \cdot \vec{\boldsymbol{dl}} = -\int_0^{L_{drift}} E_x(x,y) dx \tag{14}$$

At breakdown conditions (situation sketched in Figure 5 (right)), this then gives:  $BV = E_c W_{D,bd}/2$ . Using the equations in (13), the following expression can then be derived for the critical field: [14]

$$E_c = 4010 \cdot N_d^{\frac{1}{8}} \tag{15}$$

The critical electric field  $(E_c)$  is a particular useful parameter for identifying the onset of avalanche breakdown. This is because the impact ionization coefficient  $(\alpha)$  depends strongly on the electric field [14]. Avalanche breakdown can therefore usually be assumed to occur whenever the electric field approaches the critical electric field locally at some point in the device. As a rule of thumb,  $E_c$  is typically assumed to be on the order of 20 V/µm for silicon [9], [10].

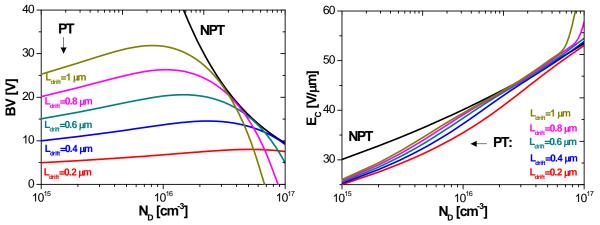

Too check how the solutions of the NPT case compare to the solutions of the PT case, the BV and  $E_c$  are plotted in the figure below for both cases for five different drift lengths. For the BV of the PT case the expression in reference [56] is used, this is also used to derive  $E_c$  in a similar manner as Equation (15) was derived.

Figure 7: BV (left) and  $E_c$  (right) for the NPT- and PT case for five different drift lengths. The PT solutions converge to the NPT solutions for increasing doping concentration and length of the drift region. Note that when the NPT and PT curves cross,  $W_{D,bd} = L_{drift}$ , such that the transition from PT to NPT occurs.

From Figure 7, it can be seen that with increased doping concentration and length of the lightly doped drift region, the BV and  $E_c$  of the PT case converge to the NPT case. Note that when the NPT and PT curves cross,  $W_{D,bd} = L_{drift}$ , such that the transition from PT to NPT occurs. In this work, typically  $L_{drift} \approx 0.4 \ \mu \text{m}$  and  $N_d \approx 10^{17} \ \text{cm}^{-3}$ , for which the PT and NPT solutions are very close together such that the less complex NPT solutions safely can be used in further analysis.

Now that the two most important FOM's (i.e. R<sub>ON</sub>A and BV) for (LDMOS) power devices are discussed in more detail, it will be explained why it is hard to optimize one without comprising the other

#### 2.2.3 Traditional trade-off

The compromise between the BV and  $R_{ON}A$  is often referred to as the traditional trade-off in the power semiconductor device industry. In order to fully evaluate this trade-off, all components of the LDMOS that affect the field distribution, resistance and/or pitch should be taking into consideration. However, since the "intrinsic MOSFET" part (i.e. the channel region) does not support a large fraction of the off-state voltage, it can be approximated that it only adds a (small) offset to the  $R_{ON}A$  in the trade-off. On the other hand, the drain-extension supports most of the off-state voltage and is typically also the largest contributor to the  $R_{ON}A$ . Consequently, the trade-off between the BV and  $R_{ON}A$  finds its largest origin in the properties of the drain-extension and will therefore only be discussed for the drain-extension of the LDMOS. [1], [14]

In order to support a high BV over the drain-extension, it became evident from the previous subsection that the drift doping should be low enough (Equation (13a)). Moreover, since a low doping concentration results in a large depletion width (Equation (13b)),  $L_{drift}$  needs to scale accordingly. Unfortunately, both these requirements compromise the resistance of the drift region (Equation (10)). From a 1D analysis of an ideal LDMOS with a lowly uniformly doped drift region, the ideal trade-off between the specific onstate resistance of the drift region and the BV can be approximated by: (derivation in Appendix B.2)

$$R_{drift}A_{drift} \left[\Omega \cdot cm^{2}\right] = R_{drift} \cdot WL_{drift} = \frac{9.18 \cdot 10^{-15}}{d_{eff}} \cdot BV^{\frac{11}{3}}$$

(16)

It must be noted that Equation (16) will mostly be valid for LDMOS devices in the higher voltage range, since there the BV will approximately be fully supported by the drain-extension.

One way to break the ideal 1D trade-off limit, is the so-called RESURF concept. This concept enables to improve the BV without compromising the R<sub>ON</sub>A and will be the topic of the next section.

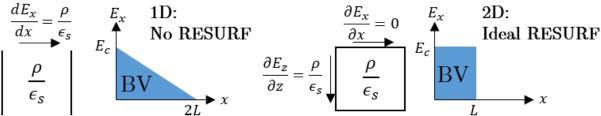

## 2.3 Improving breakdown - RESURF

Using the Reduced SURFface Field (RESURF) effect [15], the drain-extension in LDMOS devices can be designed in such a way that the (off-state) breakdown voltage is maximized without sacrificing the on-state resistance. From subsection 2.2.2, it became evident that it can be assumed that breakdown occurs whenever the electric field becomes larger than the critical field  $(E_c)$  at a certain location in the silicon. Therefore, the maximal BV is obtained whenever the electric field is equal to  $E_c$  everywhere along the drain-extension. In other words, the BV is maximized by ensuring that the electric field along the current direction (x) in the drain-extension obeys  $\frac{\partial E_x(x,y)}{\partial x} = 0$ . This is the ideal RESURF condition.

In general, to design a drain-extension that obeys this condition, one has to mathematically describe the electric field distribution within the drain-extension. For an electrostatic system, the two relevant Maxwell equations are respectively Gauss's law and Faraday's law: [57]

$$\nabla \cdot \vec{E} = \frac{\rho}{\epsilon_s} \quad \& \quad \nabla \times \vec{E} = -\frac{\partial \vec{B}}{\partial t}$$

(17)

Here  $\rho$  denotes the charge density [C/cm<sup>-3</sup>],  $\vec{E}$  the electric field [V/cm],  $\vec{B}$  the magnetic field [Vs/cm<sup>2</sup>] and t the time [s]. Since the system is assumed to be static, the time derivative is zero, meaning that the electric field is a conservative vector field such that it can be written as the gradient of a scalar potential:  $\vec{E} = -\nabla V(\vec{r})$ . Substituting this into Gauss's law, then yields Poisson's equation: [57]

$$\nabla^2 V = -\nabla \cdot \vec{E} = -\frac{\rho}{\epsilon_s} \tag{18}$$

Here V is the electrostatic potential [V]. For a 1D drain-extension,  $\frac{dE_x(x)}{dx} = \frac{\rho}{\epsilon_s}$ , such that the RESURF condition cannot be met since  $\rho \neq 0$ . For a 2D drain-extension however,  $\frac{\partial E_x(x,z)}{\partial x} + \frac{\partial E_z(x,z)}{\partial z} = \frac{\rho}{\epsilon_s}$ , the ideal RESURF condition can be satisfied if there is a field present perpendicular to the current direction with gradient:  $\frac{\partial E_z(x,z)}{\partial z} = \frac{\rho}{\epsilon_s}$ . In Figure 8, both these cases are illustrated. For identical  $E_c$  and BV, an ideal 2D drain-extension only needs half of the length as compared to the 1D case. [10]

Figure 8: Illustration of the RESRUF concept. For identical  $E_C$  and BV, a RESURF optimized (2D) drain-extension only needs half of the length compared to the 1D case. [15]

An additional advantage of using the RESURF concept, is that the drain-extension can be higher doped, thereby lowering  $R_{drift}$  (Equation (10)). While increasing the doping concentration would lead to a reduction of the BV for a 1D device (Equation (13a), RESURF can be used to counterbalance the increase in charge density by a higher perpendicular field gradient [10]. This combined with the optimized field distribution, reduces the traditional trade-off to: (derivation and full expression in Appendix B.3)

$$R_{drift} A_{drift} \left[ \Omega \cdot cm^2 \right] = \frac{1.64 \cdot 10^7}{d_{eff} N_d} \left( \frac{1}{\mu_n(N_d)} \right) BV^{\frac{7}{3}}$$

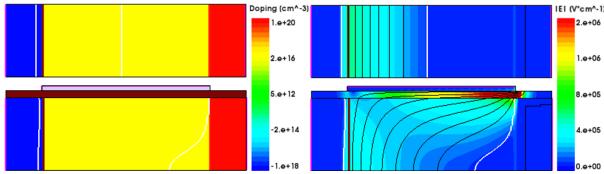

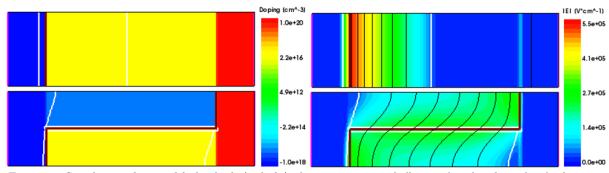

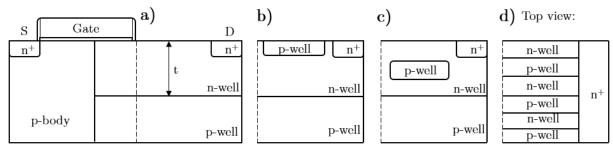

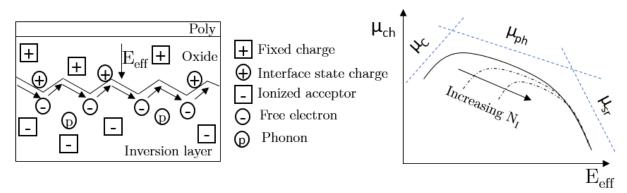

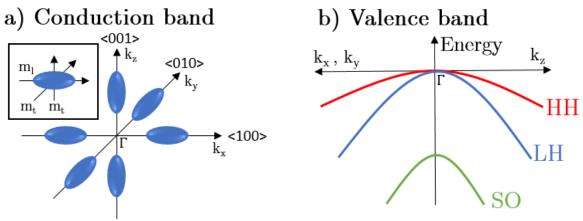

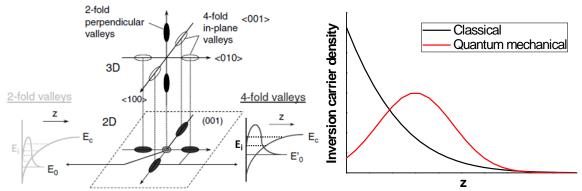

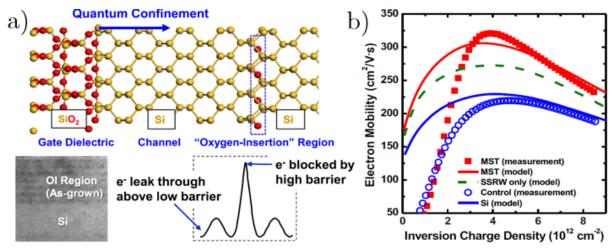

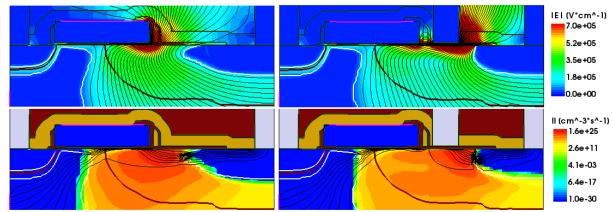

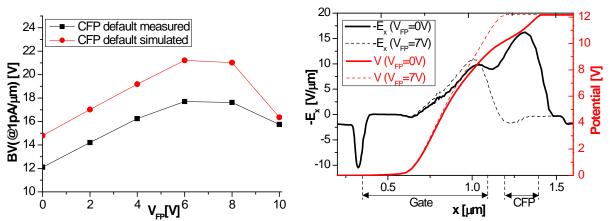

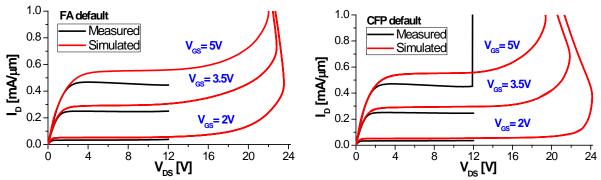

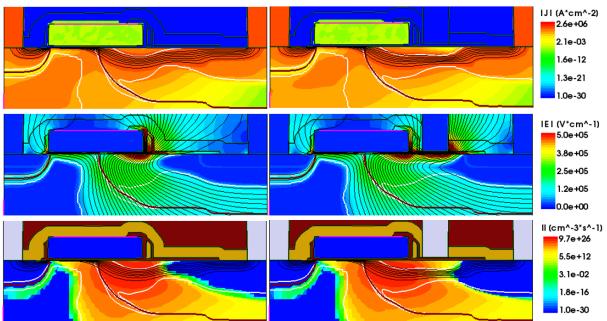

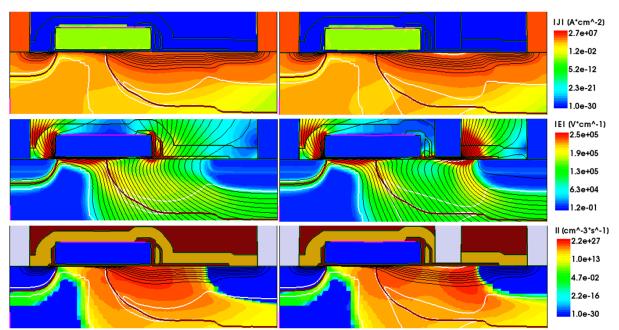

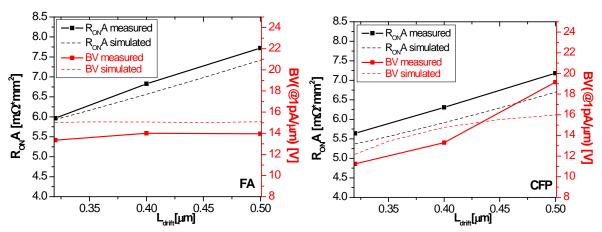

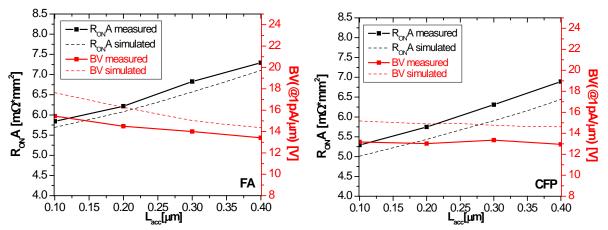

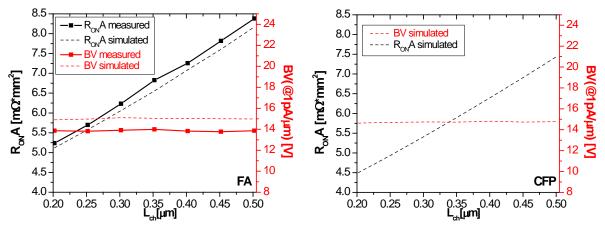

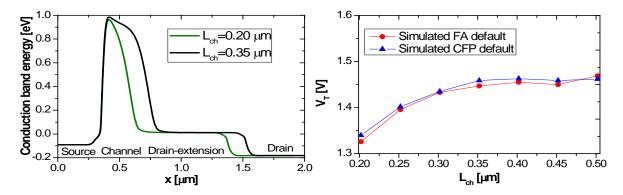

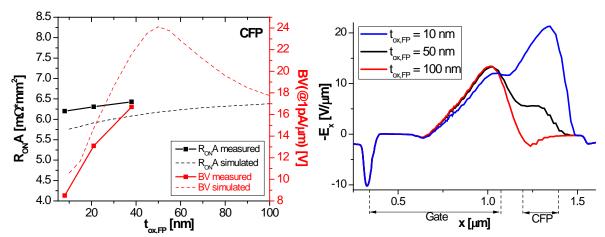

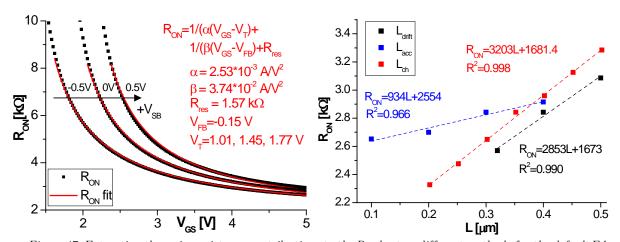

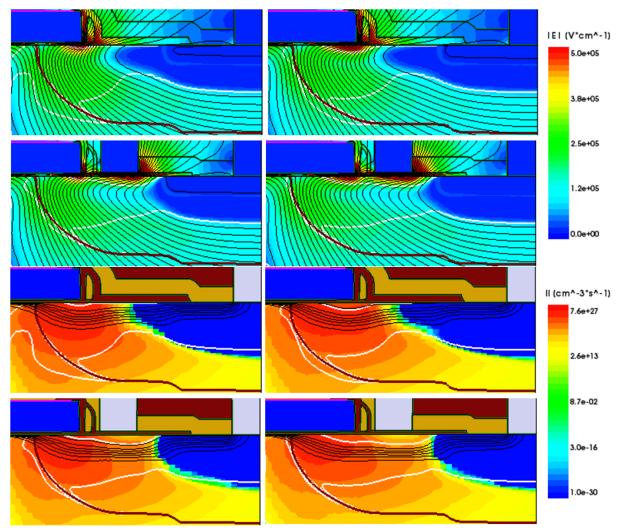

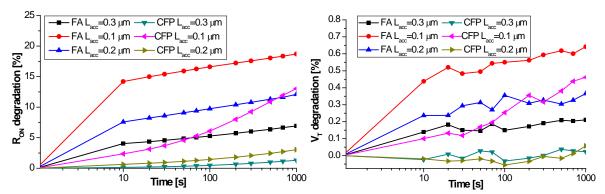

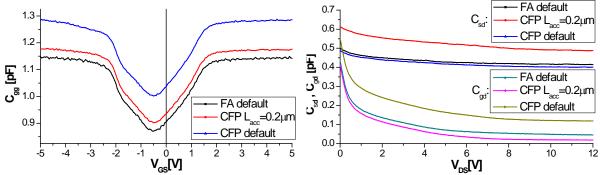

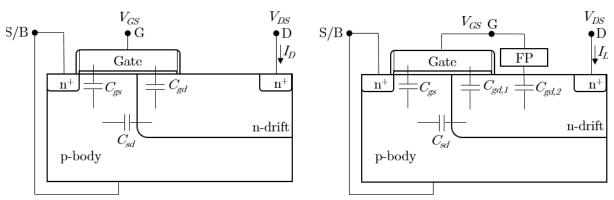

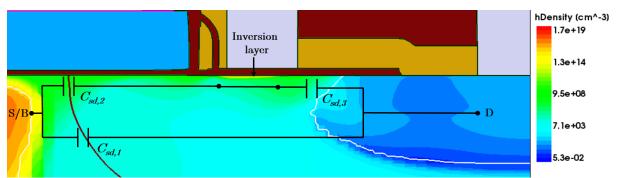

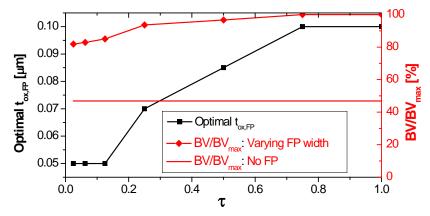

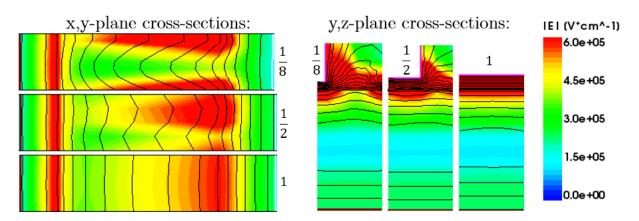

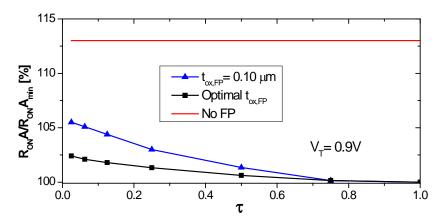

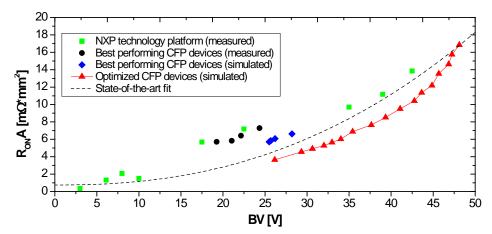

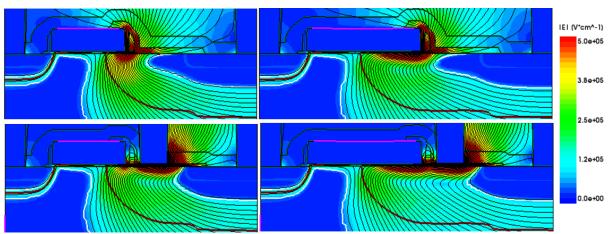

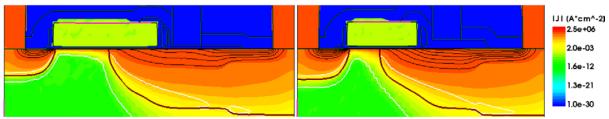

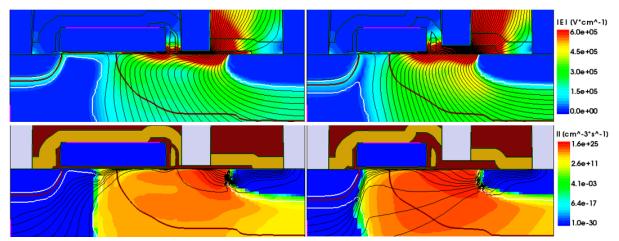

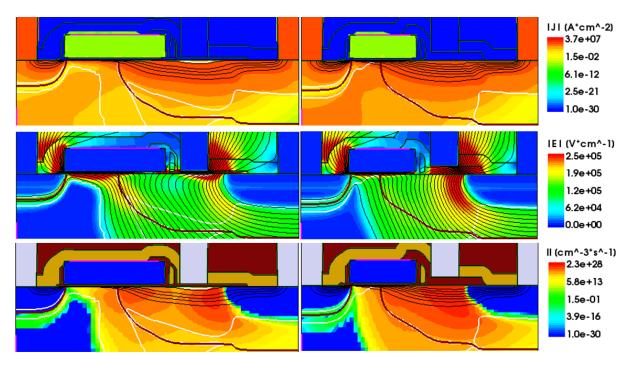

(19)