| MASTER                              |

|-------------------------------------|

| Efficient mapping of EEG algorithms |

|                                     |

| Heredia Cervantes, A.               |

| Award date: 2019                    |

|                                     |

| Link to publication                 |

|                                     |

|                                     |

|                                     |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Department of Electrical Engineering Electronic Systems Research Group

# Efficient Mapping of EEG Algorithms

Master Thesis

Alejandro Heredia Cervantes Student number: 1037414

Committee Members:

Jos Huisken

Barry de Bruin

Henk Corporaal

Rudolf Mak

## Contents

| Co | onten                                             | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii                                                                                     |  |  |  |  |  |  |  |

|----|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| A  | crony                                             | 7ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iv                                                                                     |  |  |  |  |  |  |  |

| 1  | Introduction                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |  |  |  |  |  |  |  |

| 2  | Rela<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5           | The generic Electroencephalography (EEG) processing pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>3<br>4<br>4<br>5<br>5<br>6<br>6                                                   |  |  |  |  |  |  |  |

| 3  | <b>Pro</b> 3.1                                    | blem statement Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                                                                      |  |  |  |  |  |  |  |

| 4  | Background 4.1 The seizure detection EEG pipeline |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |  |  |  |  |  |  |  |

| 5  | <b>Refe</b> 5.1                                   | erence application benchmark Reference EEG application benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>11</b><br>11                                                                        |  |  |  |  |  |  |  |

| 6  | Algo 6.1                                          | Fast Fourier Transform (FFT) mapping  6.1.1 The Cooley-Tukey Fast Fourier Transform (FFT)  6.1.2 FFT analysis and expected performance on the Blocks CGRA  6.1.3 Single Butterfly analysis  6.1.4 Parallel Butterfly analysis  6.1.5 Efficient FFT algorithms  6.1.6 Mapping results  6.1.7 Energy efficient FFT architectures in the literature  6.1.8 Possible optimizations  Discrete Wavelet Transform (DWT) mapping  6.2.1 DWT Introduction  6.2.2 Filter-Based Discrete Wavelet Transform (FWT)  6.2.3 Lifting-Based Discrete Wavelet Transform (LWT)  6.2.4 Factorization of the DB4 wavelet into lifting steps  6.2.5 LWT analysis and expected performance on the Blocks CGRA | 13<br>13<br>14<br>15<br>17<br>18<br>19<br>22<br>23<br>24<br>24<br>24<br>25<br>26<br>27 |  |  |  |  |  |  |  |

|                             |       | 6.2.6   | LWT analysis parallel channels                                            | 28        |  |  |  |  |

|-----------------------------|-------|---------|---------------------------------------------------------------------------|-----------|--|--|--|--|

|                             |       | 6.2.7   | Mapping results                                                           | 29        |  |  |  |  |

|                             |       | 6.2.8   | Efficient DWT architectures in the literature                             | 30        |  |  |  |  |

|                             |       | 6.2.9   | Possible optimizations                                                    | 31        |  |  |  |  |

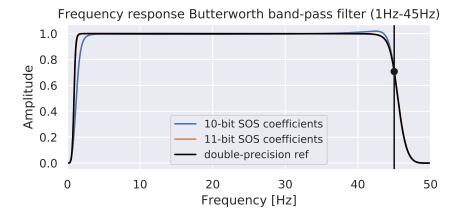

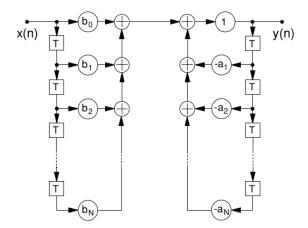

|                             | 6.3   | Butter  | rworth Mapping                                                            | 31        |  |  |  |  |

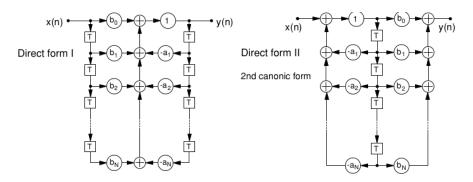

|                             |       | 6.3.1   | Direct $10^{th}$ order Infinite Impulse Response (IIR) Butterworth filter | 32        |  |  |  |  |

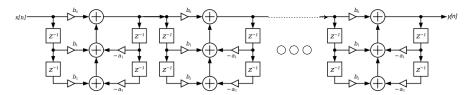

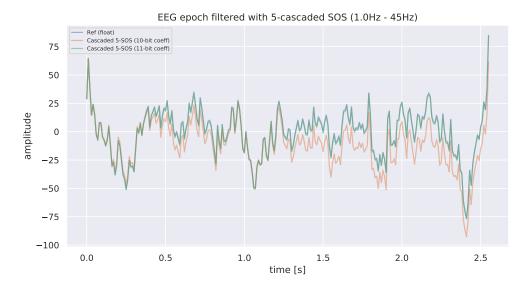

|                             |       | 6.3.2   | Cascaded Second Order Sections (SOS)                                      | 33        |  |  |  |  |

|                             |       | 6.3.3   | Fixed-point implementation                                                | 34        |  |  |  |  |

|                             |       | 6.3.4   | Computational complexity                                                  | 34        |  |  |  |  |

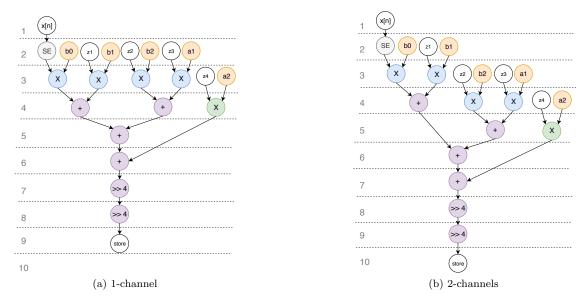

|                             |       | 6.3.5   | Expected performance in the <i>Blocks</i> CGRA                            | 35        |  |  |  |  |

|                             |       | 6.3.6   | Expected performance Parallel Channels                                    | 36        |  |  |  |  |

|                             |       | 6.3.7   | Cascaded SOS Butterworth mapping results                                  | 36        |  |  |  |  |

|                             |       | 6.3.8   | Butterworth filters in the literature                                     | 37        |  |  |  |  |

|                             |       | 6.3.9   | Possible optimizations                                                    | 38        |  |  |  |  |

| 7                           | Per   | formar  | nce comparison                                                            | 40        |  |  |  |  |

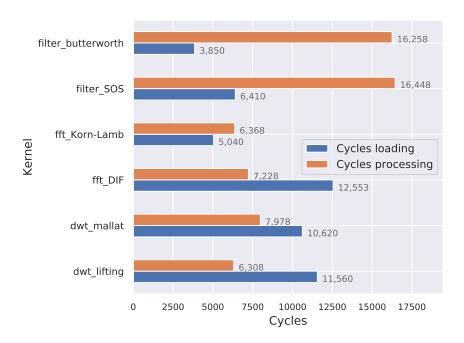

|                             | 7.1   | Cycle   | count                                                                     | 40        |  |  |  |  |

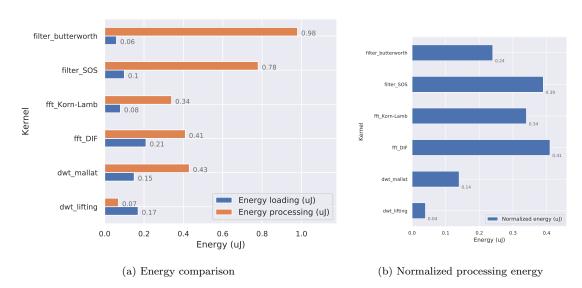

|                             | 7.2   | Energ   | y comparison                                                              | 41        |  |  |  |  |

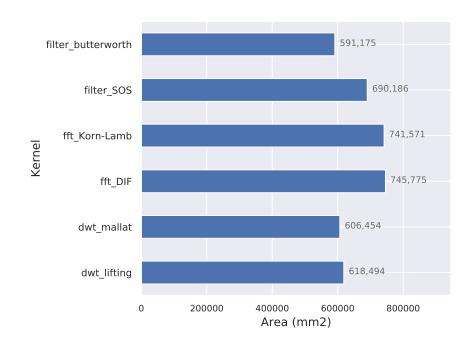

|                             | 7.3   | Area    | comparison                                                                | 42        |  |  |  |  |

| 8                           | Blo   | cks ins | stance sizing and shortcomings                                            | 44        |  |  |  |  |

|                             | 8.1   |         | sizing                                                                    | 44        |  |  |  |  |

|                             | 8.2   | Blocks  | s shortcomings                                                            | 44        |  |  |  |  |

| 9                           | Ene   | ergy M  | odel                                                                      | 46        |  |  |  |  |

|                             | 9.1   |         | aple of energy models in the literature                                   | 46        |  |  |  |  |

|                             | 9.2   |         | nergy model construction problem                                          | 47        |  |  |  |  |

| 10                          | Con   | clusio  | ns                                                                        | 48        |  |  |  |  |

|                             |       |         |                                                                           |           |  |  |  |  |

| Bi                          | bliog | graphy  |                                                                           | 49        |  |  |  |  |

| Aı                          | ppen  | dix     |                                                                           | <b>52</b> |  |  |  |  |

| A Analysis Polyphase Matrix |       |         |                                                                           |           |  |  |  |  |

### Acronyms

ABU Accumulate-Branch Unit. 10, 29

```

AGU Address Generation Unit. 22

ALU Arithmetic and Logic Unit. 8, 10, 16, 17, 20–22, 27, 29, 34, 35, 37, 44, 45, 48

ApEn Approximate Entropy. 9

ASIC Application Specific Integrated Circuit. 4

ASIP Application Specific Instruction-Set Processor. 5

BTU Butterfly Unit. 22

cA Approximation Coefficients. 24, 25, 27

cD Detail Coefficients. 24, 25, 27

CGRA Coarse Grain Reconfigurable Array. ii, iii, 1, 3, 5–8, 10, 13, 14, 18, 19, 21, 22, 25, 27,

34-36, 40, 42-45, 47, 48

CORDIC Coordinate Rotation Digital Computer. 4

DFT Discrete Fourier Transform. 13

DIF Decimation In Frequency. 14, 18, 19, 22, 23

DIT Decimation In Time. 14, 18, 19

DSE Design Space Exploration. 6

DSP Digital Signal Processing. 38

DWS Dynamic Warping Similarity. 9

DWT Discrete Wavelet Transform. ii, iii, 2, 4, 9, 13, 24–26, 28, 30, 31, 41, 48

EDA Energy-Delay-Area. 1, 8

EDS Euclidean Distance Similarity. 9

EEG Electroencephalography. ii, 1–5, 8–12, 18, 23, 24, 26, 28, 29, 31, 36, 40, 41, 44, 48

FFT Fast Fourier Transform. ii, 4, 5, 13–15, 17–24, 41, 42, 44, 45, 48

FIR Finite Impulse Response. 4, 31

```

FPGA Field Programmable Gate Array. 22, 23, 30, 31, 38

FU Functional Units. 1, 5–8, 13, 15, 20, 23, 28–30, 36, 38, 41, 42, 44

FWT Filter-Based Discrete Wavelet Transform. ii, 13, 24, 25, 28, 29, 42, 44

ID Instruction Decoder. 42, 44, 48

IIR Infinite Impulse Response. iii, 4, 13, 31–34, 36–38, 44

**IMM** Immediate Unit. 10, 27, 29, 44, 47

**ISA** Instruction Set Architecture. 45, 47, 48

**ISS** Instruction-Set Simulator. 47

**LSU** Load-Store Unit. 10, 15–18, 20, 21, 23, 27–30, 36–38, 42, 45, 48

**LWT** Lifting-Based Discrete Wavelet Transform. ii, 13, 24–31, 40–42, 44, 45, 48, 53

MAC Multiply-Accumulate. 33

MUL Multiplier. 8, 10, 16, 17

PCA Principal Component Analysis. 4

**RF** Register File. 6, 8, 10, 20, 27, 29, 30, 44, 48

RISC Reduced Instruction Set Computer. 8

**ROM** Read-Only Memory. 22

**SIMD** Single Instruction Multiple Data. 10

**SOS** Second Order Sections. iii, 13, 32–41, 44, 45, 48

**SP0** Smooth-Padding of order 0. 31

SVM Support Vector Machine. 4, 9

**SWB** Switch Boxes. 10

VLIW Very Long Instruction Word. 6, 10, 46, 47

### Chapter 1

### Introduction

EEG is a monitoring method to record electrical activity of the brain [43]. It is used in a variety of fields and application areas, such as *Brain computer interfaces (BCI)* for game development and wellness[20], and in the medical area as an aid to treat patients with brain-related diseases.

So far, the conventional EEG monitoring/recording devices are cumbersome due to the many connections needed from the electrodes attached to the scalp and a computer used to process the samples, this makes them far from ideal for every day use. Wireless battery-powered EEG monitoring systems that improve the patient EEG experience and make EEG devices least obtrusive are already available on the market [12, 15, 13, 16, 14, 11] but energy efficiency is still a challenge.

In conventional EEG processing platforms the processing and classification are done off-chip using machines that do not have energy constraints. However, off-chip processing would require to send big amounts of raw data and hence it is not suitable for wearable battery-powered EEG system as the energy required for the wireless data transmission is prohibitive. For an 8-channel EEG system, transmitting the raw EEG data by means of a low power radio for off-chip processing consumes around 1.32 mW, reducing the battery life to only a few hours. When feature extraction and classification are done on-chip, the energy consumption is reduced by 13x and 80x respectively [1] and the battery life is prolonged up to a full day.

On-chip processing requires energy efficient processors however even current low-power general purpose processors (CPUs) cannot provide the efficiency required for wireless battery-powered EEG systems. On the other hand, specialized hardware provides high energy efficiency at the cost of flexibility<sup>2</sup>. This is an issue because the optimal EEG processing pipeline is application dependent [23]. This fact and the constant development of new EEG algorithms require efficient EEG systems to include programmable hardware solutions that balance the flexibility-efficiency problem. CGRA architectures can help to achieve efficient and flexible EEG platforms. However, sharing programmable hardware among a set of algorithms requires a detailed analysis for proper sizing of the reconfigurable fabric because it cannot be modified after fabrication.

The contributions of this work are:

- Analysis of the features of an EEG pipeline and how to map them to the *Blocks* CGRA identifying: ideal speed-up, possible optimization opportunities and limitations.

- Evaluation of the efficiency of a variety of EEG features running in a platform composed by a RISC-V core + CGRA.

- The proposition of an energy-efficient CGRA architecture that can be used to compute a set of EEG features. The main goal of this flexible architecture will be to minimize the Energy-Delay-Area (EDA) product, having as key metrics the Functional Units (FU) utilization and memory traffic.

<sup>&</sup>lt;sup>1</sup>Training of the classifier is done off-chip and off-line.

<sup>&</sup>lt;sup>2</sup>Research on Flexibility is been carried on in the Electronic Systems group at the TU/e, in this dissertation processor flexibility refers to the ability to run/modify different algorithms on the same hardware

The rest of the document is structured as follows. Chapter 2 starts by presenting a generic EEG pipeline, then related work on energy-efficient EEG platforms are revisited. The seizure detection application and the EEG platform used in this thesis are introduced in chapter 4. From this seizure detection application, the *Power per Band*, DWT and the Butterworth filter were selected for implementation and their analysis and the results of the mapping are shown in chapter 6. In chapter 7 a comparison of the mapped features in terms of cycle count, energy consumption and area is presented. Initially, the proposition of an energy model was intended as one of the contributions of this work. However, it was not carried out and chapter 9 explains the reasons. Chapter 8 explains the proposed size for the *Blocks* template and the encountered shortcomings. Finally, the conclusions and future work for this thesis are presented in chapter 10.

### Chapter 2

### Related Work

EEG monitoring/processing is used in applications that range from brain computer interfaces to seizure detection and classification in medical applications. It is obvious that different applications have different requirements. However, they all follow a common pipeline structure, presented in section 2.1. Energy efficiency and flexibility are the major problems in wearable EEG platforms. Therefore, some approaches taken in the literature that deals with the efficiency-flexibility problem are presented in sections 2.2 to 2.4. The chapter finalizes discussing CGRA architectures in the context of wearable EEG platforms.

### 2.1 The generic EEG processing pipeline

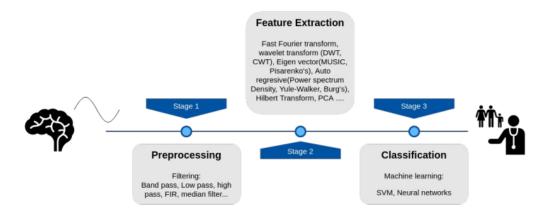

The optimal EEG pipeline is application dependent, nonetheless, there are common features used in a generic EEG pipeline which is shown in figure 2.1. The features are organized into 3 stages:

- Signal preprocessing: can include filtering, trimming of the EEG data resampling, signal segmentation and signal selection. The objective is to remove noise and other artifacts such as motion or channel interference, in other words, the data is prepared for further stages.

- Feature extraction: in this stage, features in the frequency domain, time-frequency domain and spatio-temporal domain are extracted using various signal processing algorithms.

- Classification: In this stage, the data is classified using machine learning algorithms that take as input the features extracted from the feature extraction stage.

Figure 2.1: Generic EEG pipeline

This generic EEG pipeline is customized depending on the target application. An example can be seen in [24], here the sampled signals enter a dimensionality reduction block (preprocessing stage) which computes the mean value, household reduction, accumulation and Principal Component Analysis (PCA) that reduces the input (channels) from 23 to 9 variables. The dimensionality reduction in the preprocessing stage reduces both the memory requirements as well as the computation needed in further stages of the EEG pipeline. In the feature extraction stage, DWT is used and the energy per band is estimated. Finally in the classification stage, a Support Vector Machine (SVM) classifier is implemented.

### 2.2 Energy efficiency in wearable EEG processing platforms

In conventional EEG processing platforms the processing and classification are done off-chip using processing platforms that do not have energy constraints. Off-chip processing is not suitable for wearable battery-powered EEG system as the energy required for the wireless data transmission is prohibitive. For and 8-channel EEG system, transmitting the raw EEG data by means of a low power radio for off-chip processing consumes around 1.32 mW. When feature extraction and classification<sup>1</sup> are done on-chip, the energy consumption is reduced by 13x and 80x respectively [1].

Using on-chip processing avoids the energy overhead of wireless communication of raw EEG data. As a consequence, the platform in which all the computations are carried out needs to be energy efficient as well. Low-power general purpose processors (CPU) offer flexibility as the algorithm can be easily modified or updated, on the other hand, CPUs are not energy efficient as the operations need to be done entirely by software, increasing the cycle count which in turn increases the energy consumption. On the other side of the spectrum we have the Application Specific Integrated Circuit (ASIC)s, which have high energy efficiency but at the cost of flexibility. An intermediate point is a combination of CPU plus hardware accelerators, which balance the flexibility-efficiency problem.

### 2.3 Energy efficient EEG platforms

To show the effects of hardware accelerators, in [21] accelerators for four common signal processing algorithms were designed, namely FFT, Coordinate Rotation Digital Computer (CORDIC), Finite Impulse Response (FIR) filter and median filter. As an experiment to measure the improvement, the algorithms were implemented in a 16-bit microcontroller with a hardware multiplier and compared against the same kernels executed by the accelerators. The platform was fabricated in the 13um CMOS technology. The results, presented in Table 2.1, indicate that the energy saved by using accelerators range from 133x to 215x compared to the corresponding microcontroller implementation.

On-chip processing and the use of hardware accelerators are needed in order to build battery-powered EEG detection systems. An example of this is [21], the authors also implemented applications for EEG and ECG in the same platform, achieving energy savings of 10.2x and 11.5x respectively. In [36] a platform for epileptic seizure detection using a 32-bit microcontroller (ARM Cortex-M3) and a 16-bit FFT processor is proposed. In contrary to [21], here only a 256-FFT accelerator is designed. The pipeline has the following stages: sampling of the signal, conversion to the frequency domain using a 256-FFT, computation of the energy per band, median filter, IIR filter and comparison against a reference (prediction). All stages are executed by software except the FFT. To measure the gains, the pipeline was entirely implemented in the Cortex-M3 including the FFT, this approach uses  $29.3\mu W$  at  $1.0~\rm V$ . The pipeline was also implemented using the Cortex-M3 and the FFT accelerator, the voltage was kept the same (1.0 V). The hardware FFT based implementation of seizure detection consumes  $1.6\mu W$  at  $1.0~\rm V$ , achieving an improvement of 18x in the power consumption of the application.

<sup>&</sup>lt;sup>1</sup>Training of the classifier is done off-chip.

Fully dedicated hardware solutions are also available. [45] presents an ultra low power scalable EEG platform, in which a certain degree of customization can be achieved by selecting some parameters according to the user needs, such as the number of channels (1, 2, 4, 8), system clock frequency (64, 128, 256, 512 kHz) and system operating modes (bipolar, referential or average referential). However, we are bounded to the same algorithm and the given operation modes since the algorithm can not be updated once the system is fabricated on silicon. This is perhaps the major disadvantage of fully dedicated hardware solutions.

Table 2.1: Energy consumption of signal processing tasks: CPU + multiplier vs Hardware accelerator. Measurements @ 1V 10 MHz. Table taken from [21]

| Operation           | CPU & Multiplier<br>Total Energy<br>(nJ) | Accelerator<br>Total Energy<br>(nJ) | Reduction from<br>Accelerators | Accel. Equivalent Gate Count |

|---------------------|------------------------------------------|-------------------------------------|--------------------------------|------------------------------|

| 32-tap FIR Filter   | 176                                      | 1.22                                | 144.4x                         | 11 k                         |

| 512-pt FFT          | 82148                                    | 616                                 | 133.3x                         | 24 k (logic)                 |

| $\sin x (CORDIC)$   | 279                                      | 1.30                                | 215.2x                         | $9.3 \mathrm{\ k}$           |

| 65-pt Median Filter | 114                                      | 0.79                                | 149.9x                         | 37 k                         |

### 2.4 Flexibility in wearable EEG systems

From [1, 21, 36, 45] we have seen that a CPU in combination with (good) hardware processors can reduce both, the energy consumption and area utilization at the cost of flexibility. Flexibility, the ability to run different (or improved) algorithms, is an important characteristic desirable in consumer electronics which, due to the short time-to-market, usually require modification of the application after fabrication. In the context of EEG processing platforms, a flexible solution is needed as the features computed in the EEG pipeline may differ from patient to patient [41]. This is why an energy-efficient full-programmable solution that can cope with health monitoring related applications and algorithms is needed.

# 2.5 Coarse Grain Reconfigurable Architectures in wearable EEG systems

A promising solution for wearable energy efficient EEG processing systems is the use of CGRAs, composed of FU with a connection between them that can be reconfigured at run time. This means that a programmer can modify the interconnect and instantiate an Application Specific Instruction-Set Processor (ASIP) needed for the current computation, enabling the possibility of mapping different kernels to the same CGRA fabric.

However, CGRAs also share the disadvantages of the hardwired solutions, meaning that it is not possible to add more FU once it is fabricated on silicon. For this reason, an in-depth analysis of the properties of each kernel is required in order to obtain the optimal CGRA dimensions.

#### 2.5.1 Architecture exploration in CGRAs

Architecture exploration in CGRAs is a challenge due to the many possible design choices such as FU, connections, placement and routing, etc. For this reason, even for a single application, finding the most optimal architecture is challenging and involves many trade-offs. Many works have been done that attempt to address the architecture exploration in CGRAs.

An interesting, yet limited approach is given in [38]. In this paper the authors propose a CGRA architecture that has as goals high performance and easy architecture exploration. They

present table 2.2, in which they show that homogeneous FU arrays have the lowest Design Space Exploration (DSE) complexity compared to heterogeneous and hybrid arrays but at the cost of more area overhead.

In order to mitigate the DSE complexity of Heterogeneous arrays and to keep the area as low as possible they have grouped the FUs in the architecture in a sub-array creating what they call mini cores, which are arrangements of four different FUs of an arbitrary type. Using this approach they form mini-cores that implement the complete instruction set and some sort of homogeneous array and hence reducing the design space.

|                           | Reusability | Scalability | DSE<br>Complexity                                        | Area overhead                                         |

|---------------------------|-------------|-------------|----------------------------------------------------------|-------------------------------------------------------|

| Homogeneous<br>FU array   | High        | High        | Low                                                      | High                                                  |

| Heterogeneous<br>FU array | Low         | Medium      | High                                                     | Medium                                                |

| Hybrid<br>MC array        | High        | High        | $\begin{array}{c} {\rm Medium}/\\ {\rm Low} \end{array}$ | $egin{array}{l} { m Medium}/ \\ { m Low} \end{array}$ |

Table 2.2: Comparison distinct array types. Table taken from [38]

A different approach is taken in [3]. Here the authors perform a systematic architecture exploration using a flexible architecture template (Adres) that includes a tightly coupled Very Long Instruction Word (VLIW) processor and a CGRA and integrate it into the same platform, they use their own toolchain (Compiler based on dataflow analysis and graph transformations).

In their experiments<sup>2</sup>, they mapped various kernels from the multimedia and telecommunications domain onto different *Adres* instances using their toolchain while systematically changing parameters such as the number of FUs and Register File (RF)s, the interconnection topology, the operation set each FU supports, and the sizes of the distributed RFs. The goal of the authors is to see the effects of modifying the design parameters rather than to achieve a full design space exploration.

In general, due to all the possible combination of design choices and the complexity of current architectures, even with the help of a compiler, a full design space exploration is not yet possible.

### 2.6 Size a CGRA for a set of algorithms

As mentioned before, a CGRA will only have the Functional units given at design time. If we intend to use the same CGRA for a given set of algorithms, it is required to first map all the algorithms in the set to the CGRA architecture, the final CGRA size is given by the union of the sets of functional units required to run the desired algorithms.

However, the problem of optimally mapping an application (or set of applications) onto a CGRA is NP-complete [46] and still a research topic. The huge design space, the complexity of current CGRAs and the poor compiler support make the mapping problem a big drawback when using CGRA architectures. These factors make even more difficult to take advantage of the application parallelism using minimum hardware resources.

#### 2.6.1 Mapping an algorithm onto a CGRA architecture

When the input algorithm is represented as a data-flow graph (DFG), and the CGRA target architecture, including blocks and their connectivity, is also represented as a graph, then the mapping problem is to embed the applications dataflow graph onto the device graph [5].

$<sup>^2</sup>$ To reduce the impact of the scheduling heuristic's inherent randomness, the authors scheduled each kernel five times with different random seeds and select the best result.

Several approaches have been taken in the literature when it comes to CGRA application mapping which range from novel techniques that try to map an application up to proposals that use a more regular Processing Element (PE) structure that makes the work of the compiler a bit easier.

In [46] the authors formulate the application mapping problem considering the routing of PEs the shared resource constraint and the interconnection. They also developed an Integer Linear Programming (ILP) solution and a graph drawing based approach to map the applications onto a CGRA. To measure their solution, the authors use two cost functions that involve: a) Utilizing less number of rows in the CGRA and b) Minimizing the total connection length between PEs. The limitation of this approach is that the proposed ILP model to obtain the application mapping is only applicable to moderate sizes of CGRAs due to high time complexity.

Another very interesting approach is presented in [27]. The paper presents a unified approach combining heuristics and an exact method for application mapping to various CGRA types by using backward simultaneous scheduling and binding (which usually is done sequentially) combined with dynamic graph transformations. The proposed method has as input a functional specification written in C/C++ and the targeted CGRA model, for which they also propose a modelling convention, then the application is compiled to obtain the Control Dataflow Graph (CDFG) using a GCC front-end. The CDFG and the CGRA model are used to generate the mappings using the proposed algorithm. According to the paper, the CGRA model is very flexible and can represent a CGRA with different characteristics such as homogeneous or heterogeneous tiles, with/without RF, regular/specific interconnect, multicycle operations among others. They have tested the proposed method by mapping nine algorithms used in signal processing applications, while varying the CGRA size, RF size and number of tiles. Metrics such as success rate, latency, diversity and efficiency are considered to measure the results of the mapping algorithm. They claim that the proposed method has the highest success rate, good latencies and a good solution space exploration compared with the state of the art.

The authors in [5] propose a more complete approach, they present a unified framework that includes a generic architecture description language, architecture modelling, application mapping algorithms and finally synthesizable logic for physical implementation. In other words it is a generic framework that can be applied to any CGRA, the only drawback is that the target CGRA needs to be modelled using their architecture description language. In this work, they define the cost of a mapping as the summation of all used routing nodes and all used functional unit nodes within the CGRA model (graph).

Although there are more approaches to the problem of the application mapping onto a CGRA, the vast majority need some sort of constraints to be used as a starting point, such as number of FUs, CGRA layout, number of connections/ports, etc. to then generate the dataflow graph and finally map the application.

### Chapter 3

### Problem statement

Because of the rapid development of new (computational intensive) EEG algorithms, energy efficiency and flexibility are vital characteristics in wireless battery-powered EEG platforms. CGRAs can enable low-power EEG platforms to compute and modify a set of algorithms running on them. However, CGRAs need to be properly instantiated to efficiently accommodate the application. This facts raises the research question of *How can we define a common reconfigurable architecture for the computation of a set of EEG features with a focus on energy efficiency*.

### 3.1 Contributions

The main contributions of this thesis are:

- Analysis of the EEG features and how to efficiently map them to the *Blocks* CGRA identifying: ideal speed up, possible parallelization opportunities and limitations.

- Evaluation of the efficiency of a variety of EEG features on a platform with a feature-specific CGRA + Reduced Instruction Set Computer (RISC) based processor architecture in terms of speed, area, and power.

- Additionally, we identify possible alternatives for features that cannot be efficiently computed in the CGRA.

- An energy model based on the previous results that incorporates the cost per Arithmetic and Logic Unit (ALU)/Multiplier (MUL) operation, RF and memory accesses, the interconnect, and the cost of idling (FU utilization) and reconfiguration.

- Using this model we propose an energy-efficient CGRA architecture that can be used to compute a set of EEG features. The main goal of this flexible architecture will be to minimize the EDA product, having as key metrics the FU utilization and memory traffic.

### Chapter 4

### Background

### 4.1 The seizure detection EEG pipeline

The EEG processing pipeline considered in this dissertation is based on [41]. In this paper a total of 26 features are computed on the platform explained in section 4.2. The sampling is done using 24 electrodes at a sampling frequency of 100 Hz and the signal is processed in epochs with a duration of 2 seconds each. In the filtering stage a 10<sup>th</sup> order Butterworth band-pass filter (0.5 Hz - 45 Hz) is used to remove the slow drift artefacts and to suppress the interference of the power line (50 Hz), the extracted features are used for a seizure detection application.

The main difference of [41] compared to other EEG pipelines is in the features extracted from the EEG signal. They have proposed new features that improve the classification performance when combined with the common EEG features. These new features are based on synchronization methods and in the spatio-temporal domain methods. The most important features in this EEG pipeline are:

- Frequency domain

- -Spectral analysis: Estimates the strength of different frequency components (the power spectrum) of a signal.

- Non-linear features

- -Approximate Entropy (ApEn): Used to to measure regularity in the signal.

- $-Hurst\ exponent.$

- Time-Frequency domain

- DWT: Computes both frequency and location information (location in time) of a signal.

- -Standard deviation: Quantifies the amount of variation or dispersion of a set of data values.

- Spatio-Temporal domain *Hilbert transform*: Measure the instantaneous phase of a signal.

- Synchronization based methods

- -Maximum linear cross-correlation: Measure for lag synchronization of two signals

- -Dynamic Warping Similarity (DWS): used to characterize the similarity among EEG channels

- -Euclidean Distance Similarity (EDS): Used as a comparison with the DWS.

- Post-processing

- -Moving average of EEG features, average feature on multichannel

Finally, for the Classification stage, a SVM is used for a binary classification (seizure, no seizure). Recordings from 29 epilepsy patients with intellectual disability are used for training and validation of the model.

### 4.2 EEG processing platform overview

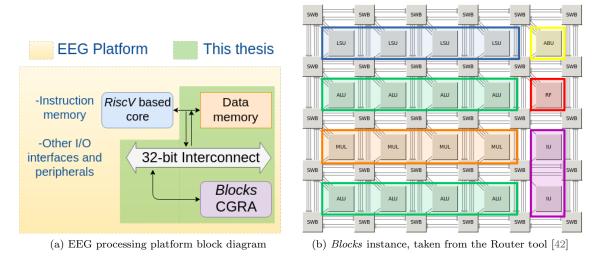

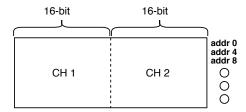

The block diagram of the EEG processing platform used in this thesis is shown in figure 4.1a, the yellow shaded rectangle represents the complete system  $^1$ . The main components are a RISC-V based core, an instance of the Blocks CGRA, a data memory shared between the core and the Blocks instance, connected by a 32-bit bus. The green shaded rectangle contains the elements that are going to be considered in this thesis. Figure 4.1b shows the instantiation of the Blocks CGRA used as a starting point, it is further explained in section 4.3.

Figure 4.1: EEG processing platform and Blocks CGRA

### 4.3 The *Blocks* architecture

The CGRA architecture is based on [42], the difference compared to other CGRA architectures is that the control and data path are independent from each other connected (with buses) to the functional units. The width of the bus (represented by the grey arrow 4.1a) that connects the memory arbiter to the shared data memory is a design parameter that can be selected between 8, 16 or 32 bit wide. In this thesis the platform has a 32-bit bus, which allows a complete word to be read from the data memory in each transaction, taking 3 cycles each.

Currently there are six kind of FU in the *Blocks* architecture: the Load-Store Unit (LSU), the RF, the ALU, the Immediate Unit (IMM), the Accumulate-Branch Unit (ABU) and the MUL. From which each LSU has access to the shared data memory and its own local memory of size 256 words by 32 bit.

Furthermore, the instruction fetch and instruction decoder units can be arbitrarily connected to any other functional unit. This makes it possible to instantiate VLIW-Single Instruction Multiple Data (SIMD) processors that tightly adapts to the application needs in terms of computation. It is also possible to bypass the register file and send directly the values that are required in other stages of the pipeline, reducing the data memory accesses and hence, the energy consumption. In contrary to other CGRA architectures, the *Blocks* architecture is designed with energy efficiency in mind, offering reconfigurability at a functional unit level (ALU, RF, etc.)

The Blocks instance used in this thesis is shown in figure 4.1b. It contains 4 LSU (their corresponding data memories are not shown in the figure), 8 ALU, 4 MUL, 1 ABU, 1 RF and 2 IMM. The architecture also contains Switch Boxes (SWB) that enables runtime reconfiguration. The instruction fetch/decoder units are not shown.

<sup>&</sup>lt;sup>1</sup>Other peripherals and the core's instruction memory are not shown because are out of the scope of this work.

### Chapter 5

### Reference application benchmark

In this chapter the results of an initial benchmark of the EEG reference application is presented. The goal is to obtain the cycle count and energy consumption which will be used to identify the bottlenecks in the pipeline and also as a metric for the comparison of the mappings explained in chapter 6.

### 5.1 Reference EEG application benchmark

An initial benchmark of the (fixed point) EEG application [41] implemented in C  $^1$  was performed. The cycle count and power consumption where taken from the netlist simulation reports and used to compute the energy consumption. The benchmark was run on the RISC-V core, which was synthesized for a maximum frequency of 100MHz in a commercial 40nm technology using the  $Cadence\ Genus$  compiler and simulated using the  $Cadence\ Incisive$  simulator.

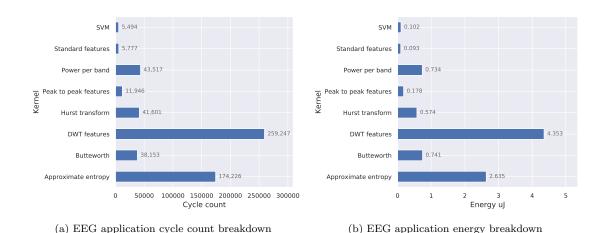

The application contains the features explained in chapter 4.1. The runtime and energy breakdown of the application are presented in figures 5.1a and 5.1b.

Is clearly seen that the *DWT features* kernel has the largest cycle count, 1.48x, 5.9x and 6.7x larger when compared to the *Approximate entropy*, the *Power per band* and the *Butterworth* features respectively. As expected the features with the largest cycle count are also consuming the most energy.

Figure 5.1: EEG application benchmark results

<sup>&</sup>lt;sup>1</sup>The C implementation of the algorithms were obtained from the *Brainwave* repository.

From this set, the  $Power\ per\ band$ , the  $DWT\ features$  and the Butterworth filter were selected. The choice was made based on the computation time and in the importance of the kernel in other EEG applications in the literature.

Finally, table 5.1 shows a detailed breakdown of the selected features. It is clearly seen that the calculation of the main components have the largest cycle count and therefore will be the target for the mapping.

Table 5.1: Detailed cycle count breakdown for selected features

|                | Feature calculation | Main components calculation                            | Other calculations |

|----------------|---------------------|--------------------------------------------------------|--------------------|

| Power per band | 3,246               | FFT = 40,271                                           | N/A                |

| DWT features   | 10,101              | DWT-Decomposition=23,388<br>DWT-Reconstruction=213,779 | 13,007             |

| Butterworth    | N/A                 | IIR = 38,153                                           | N/A                |

### Chapter 6

### Algorithm mapping

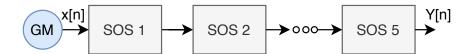

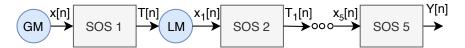

This chapter presents the analysis of the expected performance and the explanation of the FFT, DWT and the Butterworth filter mappings into the Blocks CGRA. For the FFT two algorithms were mapped, the Korn-Lambiotte and the generic Cooley-Tukey DIF. In case of the DWT, the LWT algorithm was mapped and compared against the existing FWT(Mallat algorithm) version. For the Butterworth filter, a cascaded SOS filter was mapped and compared against the existing  $10^{th}$  order IIR mapping.

The results of the energy consumption presented in each section correspond only to the FUs involved in the computation of each algorithm. The total energy consumption (which includes the energy consumed when loading a kernel to the Blocks CGRA), the delay and area are shown in a global comparison in chapter 7 for all the mappings. It is important to keep in mind that 16-bits are used to represent every input in the 256-sample epoch which is stored in the global memory of the platform. For the evaluation, the Blocks mappings were synthesized in a commercial 40nm technology using the Cadence Genus compiler and simulated using the Cadence Incisive simulator.

### 6.1 Fast Fourier Transform (FFT) mapping

This section starts with a brief explanation of the FFT algorithm, their classification and modifications for use in parallel computation. Then, the analysis of the expected performance for a 256-point FFT is shown. Next, the results of the mapped algorithm followed by a review of efficient FFT implementations in the literature are presented. The section concludes pointing to possible optimization opportunities.

#### 6.1.1 The Cooley-Tukey FFT

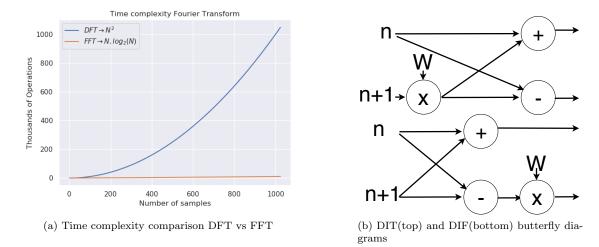

The Fast Fourier Transform is an algorithm to efficiently compute the Discrete Fourier Transform (DFT) of an N-point length input sequence. Although there are many algorithms to compute the DFT, the FFT is still the widely used due to its simplicity and ease of implementation.

The FFT follows a split and conquer approach, which results in considerably savings in computation time. Specially if the input sequence has an even number of samples, i.e., N = 2n samples. By using the FFT algorithm the time complexity is reduced to  $N \bullet log_2(N)$ , which is lower compared to the time complexity of the direct DFT of  $N^2$  [6], figure 6.1a shows the comparison.

Intuitively the input vector x of length N is divided, into two smaller vectors of length N/2, containing the even and odd indexes, this operation is repeated until we obtain a length N=2. This is the smallest DFT and it is called a *Butterfly*, which can be decomposed into 2 complex additions and 1 complex multiplication, the diagram is shown in figure 6.1b. There are two variations of this FFT algorithm, Decimation In Time (DIT) and Decimation In Frequency (DIF) they both have the same time complexity but differ in the way of dividing the input sequence, and

in the butterfly structure<sup>1</sup>.[19]

The equation 6.1 shows the expression for the Cooley-Tukey radix 2 DIT FFT:

$$Y[k] = \sum_{n=0}^{\frac{N}{2}-1} x[2n] \bullet \omega_N^{kn} + \omega_N^k \sum_{n=0}^{\frac{N}{2}-1} x[2n+1] \bullet \omega_N^{kn}$$

(6.1)

Where N is the sequence length,  $\omega_N$  represents the twiddle factors for a N-point input sequence, x is the array containing the N elements, n is the index of a given sample, k is the phase angle and Y represents the array that contains the Fourier coefficients. The number of stages that compose an N-point FFT and the number of butterflies needed in each stage are given by equations 6.2 and 6.3 respectively.

$$N_{stages} = log_2(N_{points}) \tag{6.2}$$

$$N_{butterflies/stage} = \frac{N_{points}}{2} \tag{6.3}$$

Figure 6.1: FFT time complexity plot and Butterfly diagram

#### 6.1.2 FFT analysis and expected performance on the *Blocks* CGRA

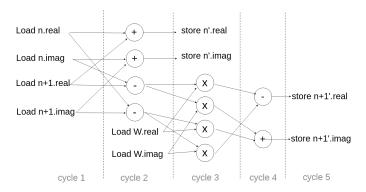

In this thesis, the reference implementation is based on a radix 2 DIF algorithm and computes the FFT of a 256-point sequence length. The mappings on the CGRA are also based on a radix-2 DIF algorithm and its variations. The basic structure is the butterfly, for this reason the analysis starts by looking at the ideal execution of a single butterfly. Taking care that the dependencies between operations are not violated, and assuming an infinite bandwidth for the interconnect, and that all operations take 1 cycle, it is possible to perform a single butterfly in 5 cycles, figure 6.2 shows the timing diagram for a DIF butterfly. This model will be used as a base to analyse the ideal FFT in the *Blocks* architecture.

The number of stages is calculated using the equation 6.2 as  $stages = log_2(256) = 8$  stages, each requiring 256/2 = 128 butterflies.

<sup>&</sup>lt;sup>1</sup>The DIT algorithm splits the input sequence into even and odd samples and perform the complex multiplication at the beginning of the butterfly whereas the DIF algorithm splits the sequence into a first and a second half and the complex multiplication is carried out at the and of the butterfly.

Figure 6.2: Diagram of an ideal Butterfly with parallel execution of operations.

### 6.1.3 Single Butterfly analysis

The analysis starts by making the following assumptions:

- The number of availbale FU are shown in figure 4.1b.

- The hardware is utilized 100% of the time.

Because of the fact that the input data is read from the global memory and the intermediate results are stored in local memories in each LSU, it is possible to group the 8 stages of the FFT, based on the location of their reading/writing operations, into three (imaginary) categories. Group 1: containing stage 1, group 2: containing stages 2-7 and group 3: containing stage 8. The idea behind this is that, in the ideal case the input data has to be read from the global memory only in the first FFT stage, and has to be written back to the global memory only in the last FFT stage, using the local memories of the LSUs to store the results from intermediate stages, figure 6.3 depicts the idea.

Figure 6.3: Grouping the stages of a 256-point FFT.

Next we assume that the butterflies in all the stages are perfectly pipelined and that we don't have any loop overheads or other index calculations. Then the cycle estimation is done using following formula:

$$\left\lceil \frac{operations_{type}}{resource_{type}} \right\rceil = cycles_{type} \tag{6.4}$$

Where  $operations_{type}$  is the total number of operations of the same type and  $resource_{type}$  is the number of available resources for executing a given operation type. The result  $cycles_{type}$  indicate the number of cycles needed to perform an arbitrary number of operations in the available resources for that type.

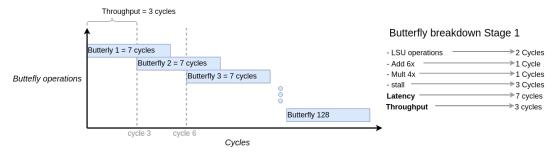

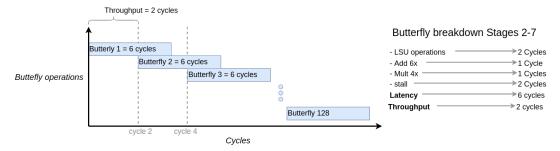

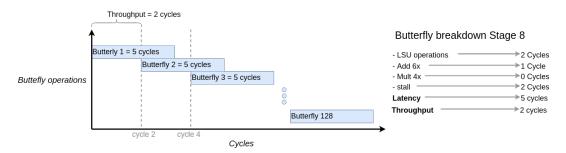

Taking the store/load cost equal to 3 cycles the formula 6.4 is applied on the model of the ideal butterfly yielding the results in table 6.1, it shows the breakdown of the latency for a single butterfly in the different stages of the FFT. This information is used to build the time diagram and butterfly breakdown shown in figures 6.4, 6.5 and 6.6 for the first, second and third phases respectively.

After obtaining the timing diagrams the cycle count for each phase is calculated using the following expression:

$$Stage_n = ((stall_{cycles} \times (Butterflies_{stage} - 1)) + Latency_{cycles})$$

(6.5)

| Stage  | LSU operations                | ALU operations                | MUL                           | Load<br>stall                 |                               | Latency single butterfly |

|--------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------|

| 1      | $\lceil rac{6}{4}  ceil = 2$ | $\lceil rac{6}{8}  ceil = 1$ | $\lceil rac{4}{4}  ceil = 1$ | $\lceil rac{6}{2}  ceil = 3$ | implicit                      | 7                        |

| 2 to 7 | 2                             | 1                             | 1                             | $\lceil rac{2}{1}  ceil = 2$ | implicit                      | 6                        |

| 8      | 2                             | 1                             | 0                             | implicit                      | $\lceil rac{4}{2}  ceil = 2$ | 5                        |

Table 6.1: Butterfly breakdown per stage in cycles for a single butterfly

Figure 6.4: Ideal Butterfly pipeline 1<sup>st</sup> stage (left), butterfly breakdown (right)

Figure 6.5: Ideal Butterfly pipeline for stages 2-7 (left), butterfly breakdown (right)

Figure 6.6: Ideal Butterfly pipeline  $8^{st}$  stage (left), butterfly breakdown (right)

Where  $stall_{cycles}$  is the cost in cycles for loading two numbers from the global/local memory,  $Butterflies_{stage}$  is the number of butterflies per stage,  $Butterfly_{cycles}$  is the number of cycles for a butterfly operation in the stage and  $num_{stages}$  is the number of stages contained in the group. After substitution of the values in the equation 6.5 we obtain an estimated cycle count of 338, 1560 and 259 cycles for the first stage, the second to seventh and for the last stage respectively. The calculations are shown in equation 6.6.

$$Stage_1: (3 \times 127) + 7 = 388 \ cycles$$

$Stage_{2-7}: ((2 \times 127) + 6) \times 6 = 1560 \ cycles$

$Stage_8: (2 \times 127) + 5 = 259 \ cycles$  (6.6)

Adding the partial results per stage yields a total of  $EstimatedFFT_{cycles} = 2,207$  cycles for the complete 256-point FFT. Finally the ideal speed up, given the hardware shown in figure 4.1b, can be calculated as:

$$Ideal\ speed\ up = \frac{referenceFFT_{cycles}}{EstimatedFFT_{cycles}} = \frac{43,517}{2,207} = 19.71 \tag{6.7}$$

It is clear that this ideal speed up of 19.71 is optimistic, because the analysis is not considering loop overheads, address calculations or other steps needed to prepare the operands in the butterflies (such as sign extension and shifting) that are most of the times present in a physical implementation. However, it can be used as an upper bound that further implementations should try to approximate.

### 6.1.4 Parallel Butterfly analysis

The possibility of computing two butterfly operations in parallel was explored by following the same analysis explained in section 6.1.3, this time assuming that twice the amount of resources are available. The results are presented in table 6.2. It is possible to see that the latency of the fist and the last stages increases due to the stall cycles generated by the conflicting memory operations.

Table 6.2: Butterfly breakdown per stage in cycles for x2 butterflies assuming double resources

| Stage  | LSU operations                 | ALU operations                  | MUL                           | Load<br>stall                  | Store<br>stall                | Latency single butterfly |

|--------|--------------------------------|---------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------|

| 1      | $\lceil rac{12}{8}  ceil = 2$ | $\lceil rac{12}{16}  ceil = 1$ | $\lceil rac{8}{8}  ceil = 1$ | $\lceil rac{12}{2}  ceil = 6$ | implicit                      | 10                       |

| 2 to 7 | 2                              | 1                               | 1                             | $\lceil rac{2}{1}  ceil = 2$  | implicit                      | 6                        |

| 8      | 2                              | 1                               | 0                             | implicit                       | $\lceil rac{8}{2}  ceil = 4$ | 7                        |

Using the equation 6.5 and the latency per stage shown in the table above, an estimated cycle count per stage equal to 772, 1560 and 515 for the first, second to seventh and for the last stage respectively is obtained. The calculations are shown in equation 6.8.

$$Stage_1: (6 \times 127) + 10 = 772 \ cycles$$

$Stages_{2-7}: ((2 \times 127) + 6) \times 6 = 1560 \ cycles$

$Stage_8: (4 \times 127) + 7 = 515 \ cycles$  (6.8)

Adding the partial results per stage gives a total of 2,847 cycles for the complete 256-point FFT, and a speed-up of 15.28 as shown in equation 6.9 below. This shows that computing two butterfly operations in parallel decreases the potential speed-up compared to processing a single butterfly operation.

$$Ideal\ speed\ up = \frac{referenceFFT_{cycles}}{EstimatedFFT_{cycles}} = \frac{43,517}{2,847} = 15.288 \tag{6.9}$$

### 6.1.5 Efficient FFT algorithms

Several variations based on the Cooley-Tukey algorithm exist that intend to efficiently fit parallel architectures, examples of these algorithms are the *Pease* and the *Korn-Lambiotte* adaptations for vector computers which are revisited in [40]. Although the algorithms compute the same result and have similar number of operations, the performance depends on how well the structure of the data flow (load/store patters) of a given algorithm fits the target architecture. In [9] the authors present a good overview of some FFT radix-2 variants. The discussion is presented by classifying the algorithms into two categories:

- Recursive algorithms, which are based on the principle of locality and hence perform better on systems with memory hierarchy, fig. 6.7a.

- Iterative algorithms, which perform the transform stage by stage, fig. 6.7b

(a) Recursive algorithm. The shaded blocks indicate the order of computation, darker shade blocks are computed first.

(b) Iterative algorithm. Each stage is completed before the next starts.

Figure 6.7: FFT algorithm classification

Recursive algorithms are not suited for this thesis due to the fact that the *Blocks* CGRA does not count with a data cache, instead it has a local memory per LSU that can fit the entire input data. Furthermore, implementing complex control flow in *Blocks* is expensive and for this reason only iterative algorithms with simple control flow and high regularity are further considered.

Three iterative algorithms are selected based on their constant geometry and the regularity between stages, i.e., the number of blocks and their vectors length are the same in all the stages of the transform. These algorithms are better suited to parallel architectures since the butterfly operations can be performed as vector operations or as parallel butterflies, furthermore, the constant geometry facilitates the control flow in a CGRA implementation. The selected algorithms are explained next and summarized in table 6.3, the iterative Cooley-Tukey algorithm is included as a mean of comparison.

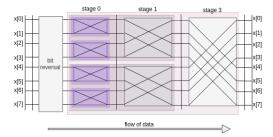

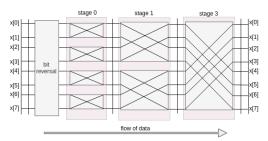

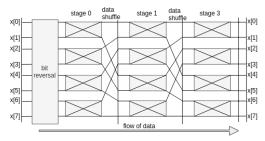

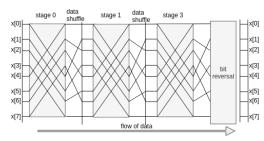

- Iterative Cooley-Tukey: Can be computed in place, requiring N complex locations for the input data, the geometry changes between stages and a bit reversal phase is needed.

- Pease and Korn-Lambiotte: Cannot be performed in place, hence 2N complex locations are required. The geometry is constant and the control flow independent of the stage, a bit reversal phase is needed. The Pease algorithm performs the complex multiplication at the beginning of each butterfly (DIT Butterfly), and the bit reversal phase at the end of the transform and vice versa for the Korn-Lambiotte algorithm (DIF Butterfly).

- Stockham: cannot be done in place and requires 2N complex locations, the geometry is constant between stages but it requires a vector shuffle that depends on the stage. The advantage of this algorithm is that no explicit bit reversal phase is required.

From these three algorithms, the *Korn-Lambiotte* is the best fit for the platform. This is because, as mentioned before, the *Korn-Lambiotte* algorithm is based on the DIF Butterfly. This

(a) Example of an 8-point Pease FFT

(b) Example of an 8-point Korn-Lambiotte FFT

Figure 6.8: Flow of data in the *Pease* and *Korn-Lambiotte* algorithms

| Algorithm                          | In-place | Memory<br>Requirements | Geometry between stages         | Bit-reversal<br>phase                                   |

|------------------------------------|----------|------------------------|---------------------------------|---------------------------------------------------------|

| $Cooley	ext{-}Tukey \ (Iterative)$ | yes      | N complex locations    | Vector length and geometry vary | yes,<br>at the beginning for DIT,<br>at the end for DIF |

| Pease                              | no       | 2N complex             | Fixed geometry and              | Yes,                                                    |

| 1 euse                             | no       | locations              | permutations                    | at the beginning                                        |

| Korn-Lambiotte                     | no       | 2N complex             | Fixed geometry and              | Yes,                                                    |

| Rom-Lamoione                       | no       | locations              | permutations                    | at the end                                              |

| Stockham                           | no       | 2N complex             | Vector shuffle vary             | No,                                                     |

| Sweknam                            | no       | locations              | vector snume vary               | self sorting                                            |

Table 6.3: FFT algorithms summary

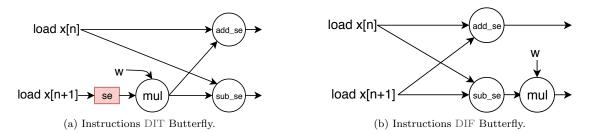

is illustrated in figure 6.9 that shows the instructions required to compute both Butterfly structures in the *Blocks* CGRA. The nodes marked with add\_se and sub\_se represent the instructions "sign-extend the inputs and add/subtract" currently available in the *Blocks* Instruction Set Architecture (ISA), the nodes marked mul represent a multiplication. In figure 6.9a a red shaded rectangle represent the extra sign-extension needed in the DIT Butterfly before the multiplication.

Figure 6.9: Blocks instructions for computing the DIT and DIF Butterfly operations.

### 6.1.6 Mapping results

The results for the Korn-Lambiotte and the  $Cooley-Tukey\ DIF$  mappings are shown in table 6.4. The obtained speed-up compared to the FFT running in the RISC-V core was 6.83x and 6.02x for the Korn-Lambiotte and the  $Cooley-Tukey\ DIF$  mappings respectively. It is important to note that the cycle count includes the stall cycles caused by conflicting memory accesses and the extra stall cycles caused by the AXI bridge that is used in the bus of the platform, which stalls 3 cycles in every memory accesses.

The achieved energy consumption was 0.34uJ and 0.41uJ for the *Korn-Lambiotte* and for the *Cooley-Tukey DIF*, which corresponds to an improve of 2.16x and 1.8x respectively.

Table 6.4: Simulation results

|                  | Cycle count | Speed-up | Energy (nJ) |

|------------------|-------------|----------|-------------|

| Cooley-Tukey DIT | 7,228       | 6.02     | 0.40        |

| Korn-Lambiotte   | 6,055       | 6.83     | 0.33        |

| RISC-V           | $43,\!517$  | 1        | 0.73        |

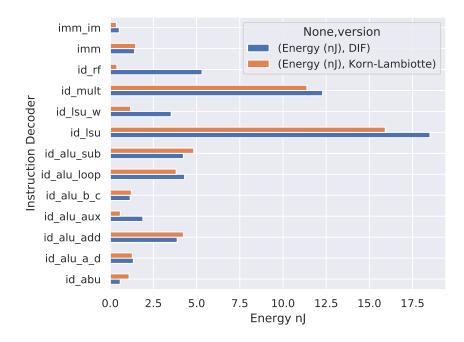

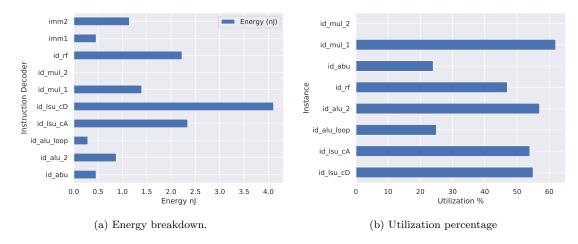

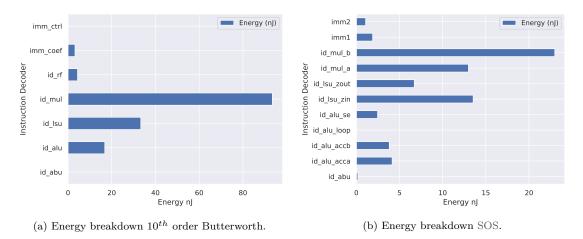

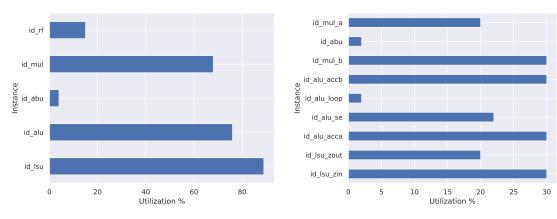

The energy breakdown for both mappings is shown in figure 6.10. The horizontal axis represents the energy in nano Joules, and the labels on the vertical axis represents the instruction decoders used in the design. The energy of the FUs are included in their respective instruction decoder, i.e. The label  $'id\_abu'$  represent the energy used by the instruction decoder  $'id\_abu'$  plus the energy of the FU 'abu'.

#### Differences in the energy consumption

There are three main differences in the energy consumption of both FFT versions:

- In the RF and ALU used for the loop calculations: As expected, it is possible to see that in the Korn-Lambiotte version the RF and the ALU responsible for the loop calculations (labeled as 'id\_alu\_aux' in figure 6.10) consume less energy compared to the Cooley-Tukey DIF version. This is due to the regular structure of the Korn-Lambiotte algorithm in which all the stages are exactly the same, avoiding the need of loop calculations and the storage of their control variables in the RF.

- In the twiddle factor LSUs: The structure of the Korn-Lambiotte allows a maximum reuse of the twiddle factors in every stage, this is clearly seen in the energy consumption of the LSUs responsible to load the twiddle factors, labeled as 'id\_lsu\_w' in figure 6.10, on which the energy consumption is less than half in the Korn-Lambiotte mapping when compared to the Cooley-Tukey DIF.

- In the input data LSUs: Due to the regularity of the *Korn-Lambiotte* algorithm, the LSUs responsible for loading the input data can efficiently use their automatic address generation capabilities without the need to reconfigure them after every block<sup>2</sup>. This is seen in figure 6.10, where the 'id\_lsu' uses less energy in the *Korn-Lambiotte* mapping.

Furthermore, there is a small difference in the energy used by the multipliers ( $iid\_mult'$ ), however, this is because a small implementation optimization in the Korn-Lambiotte version on which the multiplications in the first stage where optimized away. This was done in order to prove that because of the regularity of the Korn-Lambiotte algorithm is it possible to further reduce the energy consumption of the multipliers without significant overhead.

The rest of the instruction decoders and their corresponding FUs consume a similar amount of energy in both versions, which is expected as the computational complexity is the same in both algorithms.

#### Similarities in the energy consumption

The similarities shared by both versions are:

• It is possible to see that in both the *Korn-Lambiotte* and the *Cooley-Tukey DIF* mappings, the LSUs and the multipliers are consuming the largest amount of energy when compared to the other units.

Figure 6.10: Korn-Lambiotte and Cooley-Tukey DIF energy breakdown.

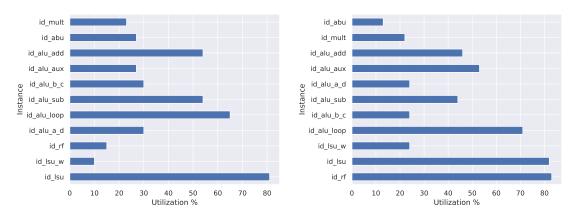

$\hbox{(a) Utilization breakdown $\it Korn-Lambiotte$ mapping.} \quad \hbox{(b) Utilization breakdown $\it Cooley-Tukey DIF mapping.}$

Figure 6.11: Utilization comparison of the Korn-Lambiotte and Cooley-Tukey DIF mappings.

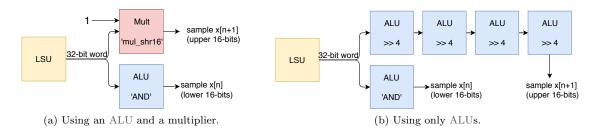

Furthermore, figure 6.11 shows the utilization of both mappings where it is possible to see that in the *Blocks* CGRA, the LSUs responsible for loading the input data are the bottleneck in a FFT. The reason for this is that, although currently the data-path used in the *Blocks* instantiation is 32-bit wide, each LSU has to load two 16-bit values sequentially. It is possible to load both 16-bit values in a single cycle if they are aligned in memory, however, splitting the upper and lower halves of this word is expensive. Figure 6.12a shows the first option, which uses an ALU to obtain the lower 16-bits, and a multiplier<sup>3</sup> to obtain the upper 16-bits. The second option is shown in figure

<sup>&</sup>lt;sup>2</sup>Every LSU can be configured to compute internally the address for the next load operation. This is done by writing the stride into a configuration register which is added to the address counter after every load operation.

$<sup>^3</sup>$ The multiplier in the *Blocks* CGRA counts with the instruction ' $mul\_shr16$ ', which multiply two values and shift-right the output result by 16 bits to obtain the upper 16-bits.

6.12b, in which only ALUs<sup>4</sup> are used to split a 32-bit word.

Both splitting alternatives are expensive, the first one would require 2048 extra multiplications to split the 32-bit word, and the second one would decrease the utilization of the hardware when software pipelining is applied due to the chain of shift operations. For these reasons, the sequential load of the input values was chosen as the best option.

Figure 6.12: Options for splitting a 32-bit word in the *Blocks* CGRA.

### 6.1.7 Energy efficient FFT architectures in the literature

Because of the fact that the FFT is widely used there are many energy efficient FFT implementations. However the efficiency is relative to the application domain. This section presents some state of the art implementations, organized in two subsections depending on the approach: custom-hardware based and custom-algorithm/mapping based. It is important to note that although the approach is different the common factor is that a trade-off between area, energy, flexibility and delay is done on most of the architectures.

#### Based on custom-hardware

An example of this if given in [25]. Although the design aims to be low power, It is implemented in a Field Programmable Gate Array (FPGA) and focused on low latency applications, the energy efficiency comes from the parallelism of the implementation which is based on a custom 64-point 8-parallel FFT architecture, composed of an Address Generation Unit (AGU) and a custom Butterfly Unit (BTU)s. Here a trade-off between energy efficiency and area was done.

An efficient and scalable implementation is given in [28]. Here the goal is to have a configurable BTU able to process radix-2 or radix-4 operations for 8 to 1024 points FFTs. A dedicated Read-Only Memory (ROM) is used to store the twiddle factors near the BTU, the proposed design also uses an AGU and double buffering for latency hiding of input/output data transfers. The results were compared against the *xilinx logicore IP FFT*, the proposed design can operate at 217 MHz compared to the 189 MHz of the *Xilinx IP* at a lower area cost (1/3), the latency however is 1.5 times larger than that of the *Xilinx IP*. In this case there is a trade-off between area and latency.

Another example of the area and energy trade-off is done in [4]. They propose a low power variable length FFT processor. The main features of this work are the combination of scaling factors for the input data and a tailored constant multiplier array in the butterfly unit that use a mechanism to decide whether to use the multiplier array or complex multipliers during the computation. This method saves about 20% of the power consumption compared to the pure complex multiplier implementation. Furthermore, a simple trounding strategy is used to shorten the word length after a multiplication. Although rounding is more accurate, the authors claim that it increases the critical path delay and the energy consumption. The proposed FFT processor is composed of an AGU, a custom DIF BTU, a twiddle factor ROM and a scaling factor generator unit.

<sup>&</sup>lt;sup>4</sup>The ALU in the *Blocks* CGRA has shift-right by 1-bit and by 4-bit instructions

#### Based on custom algorithms/mapping

Efficient implementations based on stock resources are also available in the literature, an example is [17], which proposes an efficient mapping of the pipeline single-path delay feedback FFT to FPGAs. They mention that it is not only the FFT architecture that affects the results but also the mapping to the hardware. To prove it, they optimized the radix-2 FFT algorithm for the Virtex-4 and Virtex-6 FPGAs, performing transformations that improve the resource usage and resource utilization, specially in multipliers and memories. This was combined with pipelining in order to improve the delay. As a result they obtained a reduced area and an increased throughput per slice of 350% and 400% for the virtex-4 and Virtex-6 respectively compared to the literature. Due to the tailored mapping, in this case the trade-off is between energy efficiency-area and portability.

### 6.1.8 Possible optimizations

This chapter concludes by proposing the following optimizations based on the observations made during the state-of-the-art literature review and on the results of the *Korn-Lambiotte* algorithm mapping.

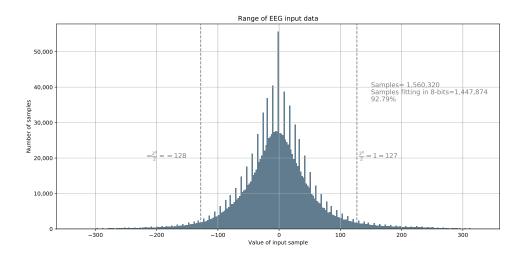

- Reduced precision for complex numbers: Limited bandwidth is one of the bottlenecks in this kernel. The first situation is during the first and the last stages of the FFT in which two complex values, currently represented by 32-bit each, need to be read/written using the 32-bit bus that connects the LSUs to the data memory, meaning that 62 bits are scheduled to be transferred in the same cycle. In Blocks, when two memory transactions whose added bandwidth is bigger than the bus bandwidth are scheduled in the same cycle will stall other FU until the memory transaction is complete. It is not possible to reduce the number of operands needed in the butterflies to avoid the stall cycles, however it is possible to reduce the number of bits used to represent the complex values. Using 16 bits to represent each complex number (8-bits for each, the real and imaginary parts) would allow to transfer the two complex inputs needed in the first and the last stages without stall cycles. On the other hand, using 8-bits for each component of a complex number means that samples with values outside the range -128 to 127 would need to be clipped and hence the accuracy could drop. Figure 6.13 shows the distribution of the EEG input data<sup>5</sup> used to test and develop the algorithms, the dashed lines represent the minimum and the maximum signed values that can be represented by 8-bits. This data set is composed of about 1.5 million samples from which 92.7% fit in 8-bits. Although the value of most of the samples are in the 8-bit range, rigorous checking is still needed to verify that the results are still accurate enough for the EEG application.

- Preloaded Twiddle factors: Currently, the twiddle factors are copied from the global memory and stored in the local memories of the corresponding LSU. Since the twiddle factors do not change, a possible improvement is to have dedicated memory locations in a local memory to store the twiddle factors (pre-loaded values).

- Real Korn-Lambiotte FFT algorithm: The implemented algorithms assume complex input values. However, when the input data is composed of real values only the first half of the transform is used, i.e. The second half is a mirrored version of the first half and it is therefore discarded. The EEG dataset is composed of real values only, so by using a real FFT algorithm the required computations could be reduced by half. In [35] the authors show how to implement a real-valued transform using some of the most popular FFT algorithms. The Korn-Lambiotte algorithm could be modified to perform a real-value transform.

A working reference implementation is provided in [33], this is a good starting point for further improvements because it is based on the general radix-2 DIF algorithm that suits the *Blocks* architecture.

$<sup>^5</sup>$ See section 4.1 for more details.

Figure 6.13: Data distribution of the EEG dataset.

### 6.2 DWT mapping

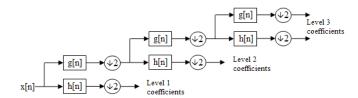

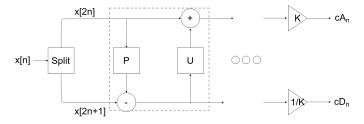

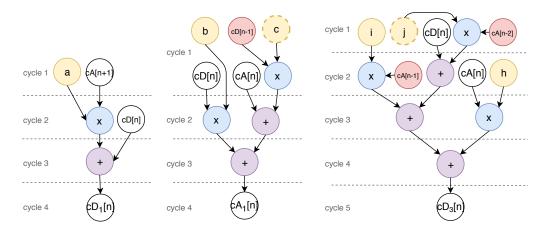

This section presents the DWT mapping and it is structured as follows, first a brief overview of both methods the FWT (Mallat algorithm) and LWT is presented. Note that this brief explanation is to provide an intuitive idea of how the DWT works, [39] provides an in-depth mathematical explanation and [18] gives a practical approach focussed on the LWT. An explanation of how to derive the lifting equations is also provided in this chapter. The chapter concludes presenting the expected performance analysis followed by the mapping results and possible optimizations.

### 6.2.1 DWT Introduction