## MASTER

Software for interfacing and management of multiple FPGAs for high performance computing in data centres

Vallavanthara, Amal Jose

Award date: 2018

Awarding institution: Technische Universität Berlin

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Fraunhofer Heinrich-Hertz-Institut

Master Thesis

# Software for interfacing and management of multiple FPGAs for high performance computing in Data Centres

Student Amal Jose Vallavanthara ID: 396462

Supervisor: Prof. Dr.-Ing. R. Orglmeister, TU BerlinExaminer: Prof. Dr.-Ing. Benno Stabernack, Fraunhofer HHI

Technical University of Berlin, Faculty of Electrical Engineering and Computer Science Department of Electronics and Medical Signal Processing Berlin, October 1, 2018

# Contents

| Ał | ostrac | ct        |                                                     | 1  |

|----|--------|-----------|-----------------------------------------------------|----|

| 1  | Intro  | oductio   | n                                                   | 3  |

|    | 1.1    | Applic    | cation Scenario                                     | 3  |

|    | 1.2    | Defini    | tion of Goals of the work                           | 4  |

|    | 1.3    | State     | of the Art                                          | 5  |

| 2  | The    | oretica   | background                                          | 7  |

|    | 2.1    | PCI e     | xpress and Nallatech Board                          | 7  |

|    |        | 2.1.1     | PCI Express                                         | 7  |

|    |        |           | 2.1.1.1 Structure                                   | 7  |

|    |        |           | 2.1.1.2 Address Space                               | 9  |

|    |        | 2.1.2     | Compute Acceleration Card - Nallatech 510T [1718]   | 10 |

|    | 2.2    | Linux     | Kernel - Memory allocation and parallel programming | 12 |

|    |        | 2.2.1     | Kernel Space memory                                 | 12 |

|    |        | 2.2.2     | User Space Memory                                   | 13 |

|    |        | 2.2.3     | Parallel programming                                | 14 |

|    | 2.3    | DMA       | Memory mapping                                      | 15 |

| 3  | Spe    | cificatio | on                                                  | 17 |

|    | 3.1    | Driver    | Development                                         | 17 |

|    |        | 3.1.1     | Connecting User Application to FPGA                 | 19 |

|    |        | 3.1.2     | Read and write the Device File                      | 21 |

|    |        | 3.1.3     | Input-output Control                                | 22 |

|    | 3.2    | DMA       | transfer                                            | 24 |

|    |        | 3.2.1     | Design of DMA transfer                              | 24 |

|    |        |           | 3.2.1.1 User Space to kernel space                  | 24 |

|    |        |           | 3.2.1.2 Kernel Space to FPGA                        | 25 |

|    |        | 3.2.2     | DMA Controller                                      | 27 |

|    |        |           | 3.2.2.1 Read and write DMA descriptor format        | 31 |

|    |        | 3.2.3     | Algorithms for efficient DMA transfer               | 33 |

|    |        |           | 3.2.3.1 Polling                                     | 33 |

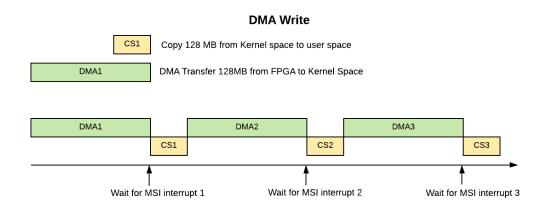

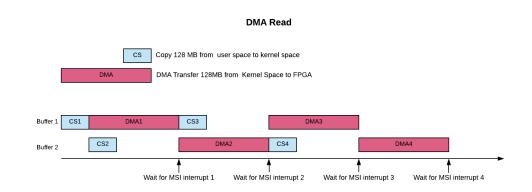

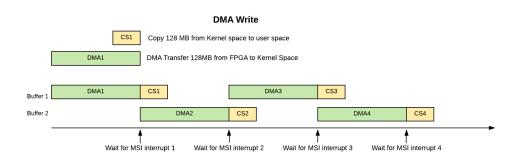

|    |        |           | 3.2.3.2 MSI - Minimal Performance                   | 36 |

|    |        |           | 3.2.3.3 MSI - Maximal Performance                   | 38 |

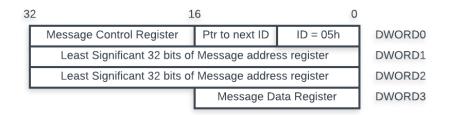

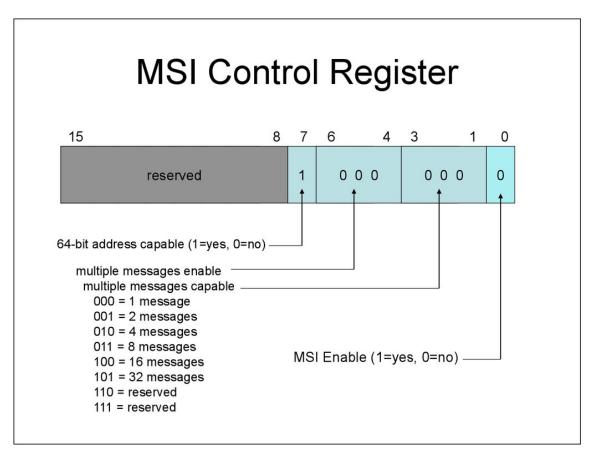

|                         | 3.3                                                  | MSI in                                                                   | terrupts                                                                       |                                                                                                                                        | 40                                                                                                                  |

|-------------------------|------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                         |                                                      | 3.3.1                                                                    | MSI capa                                                                       | ability register $\ldots$                             | 41                                                                                                                  |

|                         |                                                      |                                                                          | 3.3.1.1                                                                        | Capability ID                                                                                                                          | 42                                                                                                                  |

|                         |                                                      |                                                                          | 3.3.1.2                                                                        | $Message \ Address \ Register \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                  | 42                                                                                                                  |

|                         |                                                      |                                                                          | 3.3.1.3                                                                        | Message Data Register                                                                                                                  | 42                                                                                                                  |

|                         |                                                      |                                                                          | 3.3.1.4                                                                        | $Message \ control \ register \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                  | 43                                                                                                                  |

|                         |                                                      | 3.3.2                                                                    | Interrupt                                                                      | t Handling                                                                                                                             | 44                                                                                                                  |

|                         | 3.4                                                  | PIO re                                                                   | ead/write                                                                      |                                                                                                                                        | 45                                                                                                                  |

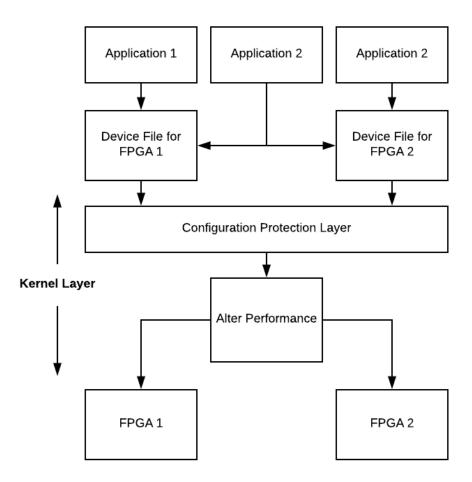

|                         | 3.5                                                  | Real-ti                                                                  | me Perfo                                                                       | rmance Altering                                                                                                                        | 46                                                                                                                  |

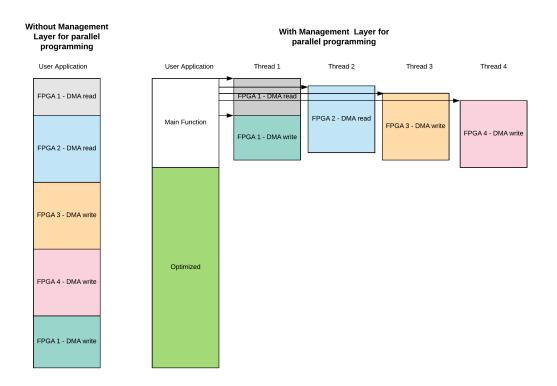

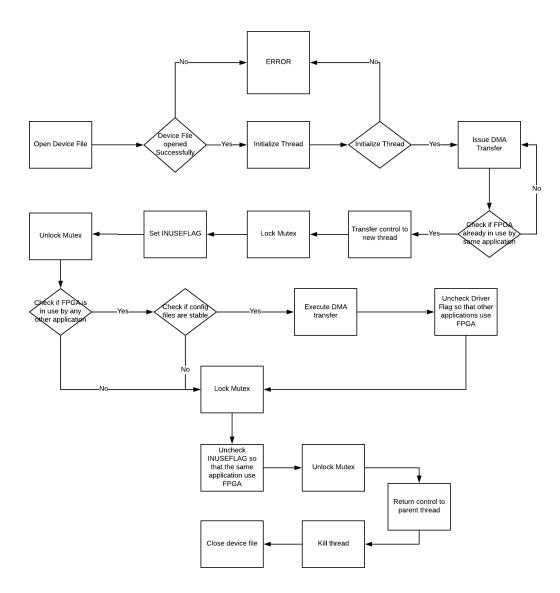

|                         | 3.6                                                  | Manag                                                                    | gement So                                                                      | ftware for parallel programming                                                                                                        | 48                                                                                                                  |

|                         | 3.7                                                  | Acquis                                                                   | ition, stor                                                                    | rage and display of FPGA Parameters                                                                                                    | 51                                                                                                                  |

|                         |                                                      | 3.7.1                                                                    | Telegraf                                                                       |                                                                                                                                        | 51                                                                                                                  |

|                         |                                                      | 3.7.2                                                                    | InfluxDE                                                                       | 3                                                                                                                                      | 54                                                                                                                  |

|                         |                                                      | 3.7.3                                                                    | Grafana                                                                        |                                                                                                                                        | 54                                                                                                                  |

|                         |                                                      | 3.7.4                                                                    | Overall s                                                                      | structure                                                                                                                              | 55                                                                                                                  |

|                         | <b>_</b> .                                           | l Decia                                                                  | n and \//                                                                      | orkflow                                                                                                                                | 57                                                                                                                  |

| 4                       | Fina                                                 | Desig                                                                    | n and vvo                                                                      | SKIIOW                                                                                                                                 | 51                                                                                                                  |

| 4<br>5                  |                                                      | C                                                                        | n and wo                                                                       |                                                                                                                                        | 59                                                                                                                  |

| -                       |                                                      | Evalua                                                                   | ntion and                                                                      |                                                                                                                                        |                                                                                                                     |

| -                       | Test                                                 | <b>Evalua</b><br>Test er                                                 | <b>ation and</b><br>avironmer                                                  | Results                                                                                                                                | 59                                                                                                                  |

| -                       | <b>Test</b><br>5.1                                   | <b>Evalua</b><br>Test er                                                 | <b>ation and</b><br>avironmer<br>esults                                        | <b>Results</b><br>nt                                                                                                                   | <b>59</b><br>59                                                                                                     |

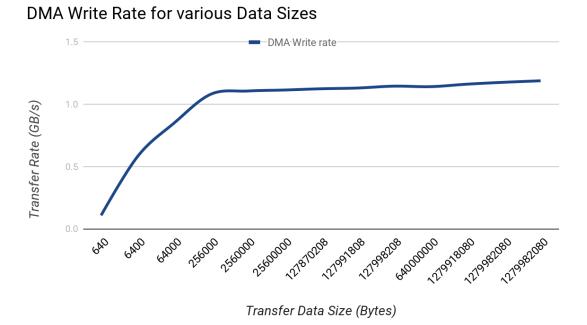

| -                       | <b>Test</b><br>5.1                                   | <b>Evalua</b><br>Test en<br>Test R                                       | ntion and<br>nvironmer<br>esults<br>DMA the                                    | <b>Results</b><br>nt                                                                                                                   | <b>59</b><br>59<br>61                                                                                               |

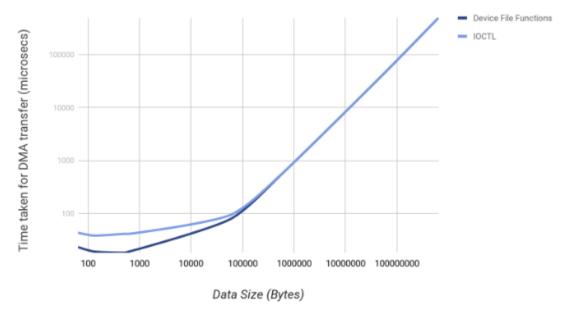

| -                       | <b>Test</b><br>5.1                                   | <b>Evalua</b><br>Test en<br>Test R<br>5.2.1                              | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v                         | Results           at                                                                                                                   | <b>59</b><br>59<br>61<br>61                                                                                         |

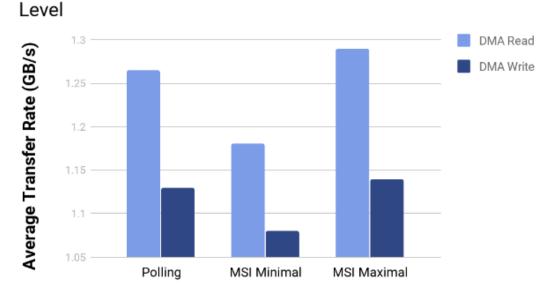

| -                       | <b>Test</b><br>5.1<br>5.2                            | <b>Evalua</b><br>Test en<br>Test R<br>5.2.1<br>5.2.2<br>5.2.3            | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v                         | Results         nt                                                                                                                     | <b>59</b><br>59<br>61<br>61<br>63                                                                                   |

| 5                       | <b>Test</b> 5.1 5.2 <b>Sum</b>                       | <b>Evalua</b><br>Test en<br>Test R<br>5.2.1<br>5.2.2<br>5.2.3            | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v<br>Compari              | Results         nt                                                                                                                     | <b>59</b><br>61<br>61<br>63<br>64                                                                                   |

| 5<br>6<br>A             | Test<br>5.1<br>5.2<br>Sum<br>User                    | Evalua<br>Test en<br>Test R<br>5.2.1<br>5.2.2<br>5.2.3<br>mary a<br>APIs | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v<br>Compari              | Results         nt         roughput         roughput         vs Device File Functions         son of Performance levels         e Work | <ul> <li><b>59</b></li> <li>61</li> <li>61</li> <li>63</li> <li>64</li> <li><b>65</b></li> </ul>                    |

| 5<br>6<br>A<br>B        | Test<br>5.1<br>5.2<br>Sum<br>User<br>Para            | Evalua<br>Test en<br>Test R<br>5.2.1<br>5.2.2<br>5.2.3<br>mary a<br>APIs | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v<br>Compari<br>nd Future | Results         nt         roughput         roughput         vs Device File Functions         son of Performance levels         e Work | <ul> <li><b>59</b></li> <li>61</li> <li>61</li> <li>63</li> <li>64</li> <li><b>65</b></li> <li><b>67</b></li> </ul> |

| 5<br>6<br>A<br>B<br>Lis | Test<br>5.1<br>5.2<br>Sum<br>User<br>Para<br>st of l | Evalua<br>Test er<br>Test R<br>5.2.1<br>5.2.2<br>5.2.3<br>mary a<br>APIs | ntion and<br>nvironmer<br>esults<br>DMA the<br>IOCTL v<br>Compari<br>nd Future | Results         nt         roughput         roughput         vs Device File Functions         son of Performance levels         e Work | <ul> <li>59</li> <li>59</li> <li>61</li> <li>63</li> <li>64</li> <li>65</li> <li>67</li> <li>71</li> </ul>          |

# List of Abbreviations

| FPGA                 | Field Programmable Gate Array              |

|----------------------|--------------------------------------------|

| DMA                  | Direct Memory Access                       |

| IRQ                  | Interrupt Request                          |

| PCI                  | Peripheral Component Interconnect          |

| PCIe                 | Peripheral Component Interconnect Express  |

| PCX                  | Peripheral Component Interconnect eXtended |

| MSI                  | Message Signal Interrupt                   |

| PIO                  | Programmed Input/output                    |

| MMIO                 | Memory-mapped Input/Output                 |

| PC                   | Personal Computer                          |

| IOCTL                | Input Output Control                       |

| $\mathbf{SoC}$       | System on Chip                             |

| DDRAM                | Double Data Rate Random-access memory      |

| RAM                  | Random-access memory                       |

| InfluxDB             | Influx Database                            |

| $\operatorname{SQL}$ | Structured Query Language                  |

| IP                   | Intellectual Property                      |

| HPC                  | High Performance Computing                 |

| TFLOP                | Tera floating point operations per second  |

| OS                   | Operating System                           |

| DWORD                | Double Word                                |

| DDR4                 | Double Data Rate Fourth-generation         |

| SDK                  | Software Developer's Kit                   |

| GPU                  | Graphics processing unit                   |

| TPU                  | Tensor processing unit                     |

| ASIC                 | Application-Specific Integrated Circuit    |

|                      |                                            |

# Declaration by the candidate

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been listed.

Berlin, October 8, 2018

Signature

# Acknowledgement

I thank God almighty for the blessings he had bestowed on me at every stage of my project. I express my heartfelt gratitude to Prof. Dr.-Ing. R. Orglmeister, Technical University Berlin and Prof. Dr.-Ing. Benno Stabernack, Fraunhofer HHI for being my thesis supervisors. I would also like to thank Mr.Steinert Fritjof, Fraunhofer HHI for guiding me through the implementation work. I extend my gratitude to Fraunhofer HHI for employing and trusting me with the project. Last but not the least, I would like to thank my professors and colleagues for the continued support. I thank my family for the continuous support and the belief in me.

# Abstract

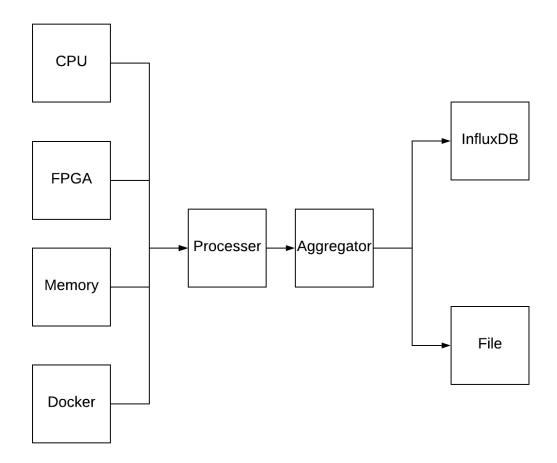

With the rise of new technologies like blockchain, Artificial Intelligence, Internet Of Things, the demand for high performance computing is at its peak. Optimization in processors are reaching a normalcy. This leads to the need of clustering large number of ASICs, FPGAs, GPUs and TPUs to perform tasks. However, with the increase of cores leads to increase in communication and management overheads. This leads to the need for coherent services and driver management tools for efficient control of the devices and data transfer between the cores. The thesis proposes a driver program which is used for communication between the host PC with multiple Intel FPGAs. The driver will be able to automatically detect and enumerate the FPGAs connected to the host device. Initial steps include sending and receiving data over PIO through PCI express. The overall functioning and optimization schemes of the PCIe will be studied in detail and implemented. Later, DMA access will be implemented for faster data transfer between FPGAs. Choosing the right size of the tokens in DMA transfer is of utmost importance for the overall speed of data transfer and this varies from device to device. Various token sizes for transfer would be analyzed and the best possible case will be implemented. The driver will be capable of management of the different accelerators. The user gets real time information about the parameters of the FPGA. It would also warn the user in case of inappropriate levels of these parameters. This would enable the user to manage, maintain and control the FPGAs connected to the server seamlessly. The SDK will be developed to enable developers to use the functions without the need for understanding the minute framework details. In a nutshell, the work would also provide a software layer that simplifies integration of FPGAs into user applications and environments. It would consist of tools and libraries to discover, enumerate, access, control and manipulate FPGAs. The project would also include test programs to test its usability and to make sure that the management software is implemented in perfection.

# 1 Introduction

# 1.1 Application Scenario

FPGA based accelerators are employed in a wide range of industries including communication, aerospace, defense, medical electronics, video and image processing, broadcasting, automotive, security systems, high-performance computing, cryptography, artificial intelligence, blockchain, etc. FPGAs are particularly beneficial compared to ASICs because the cost is much lower especially for low volume productions. The time to market for an application is also tremendously lower. FPGAs are increasingly adopted in enterprises, scalable Data centers and high-performance computing centers in large numbers. FPGAs are adopted as accelerators because complex problems in today's industries cannot be solved by faster CPUs. They require hardware specific acceleration.

These huge enterprises have a heavily armed IT team to manage and maintain the FPGAs. However, many at times, the IT team isn't fully knowledgeable in the hardware level details of the FPGAs. Therefore they need an out of the box solution to manage and control the FPGAs. This brings the need for a comprehensive package which could be installed and used following a simple instruction set. The package should contain pre-developed tools which could be used to obtain FPGA parameters like working conditions, throughput, temperature, etc. A user-friendly GUI showcasing all the above parameters of every FPGA would give the IT personals the ability to manage and maintain all its FPGAs with ease.

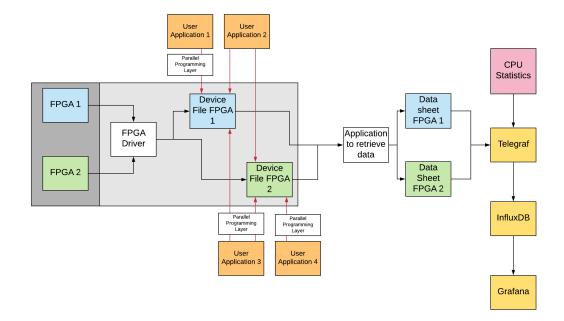

The above is from the perspective of IT personals in charge of installation and maintenance of the FPGAs. Another perspective to be considered is from the developer point of view. The developer needs to use the FPGAs seamlessly in their user applications. These developers need not know the hardware level details of the FPGA. They need their user applications to enumerate, access, control and perform operations on the FPGA. They need user applications to read and write data to the FPGA with maximum efficiency. The developer needs to have a test environment to verify if the FPGAs are operating sustainably and synchronously with their application. These would require robust test APIs which can give immediate inspection results. The main purpose of FPGAs is to speed up the process. Therefore parallel programming is an indispensable element of FPGA usage. Therefore parallel programming APIs also need to be developed so that the user application can perform operations on multiple FPGAs simultaneously.

In the particular case, the software is developed for an on-demand cloud-based HPC cluster

solution provider which owns huge data centers and rents out its FPGA platform and environment to clients to build test, simulate or run client applications. There would be times when the FPGAs are shared among multiple clients. Therefore it is essential for the different clients to be able to access the FPGAs simultaneously. There are cases where multiple FPGAs need to be accessed by the same client simultaneously. Therefore serial and parallel programming should be possible hand in hand. It would be an added selling point for the solution provider if the clients could view the performance of the FPGAs from anywhere around the world through a user-friendly interactive GUI.

In many cases, the performance of the driver needs to be varied. For instance, in cases of usage within data centers, a huge amount of resources such as memory and CPU power are available. Therefore, the driver would work at maximum efficiency in terms of latency. However, if the FPGAs are to be used for development in a resource constrained server, the available memory, power and cycles are limited. Therefore the driver should trade-off overall speed to balance out all the other requirements. This arises the need for performance altering of the system driver. In many enterprises, altering the performance of FPGAs in real time is also a necessity. For instance, during the daytime, services which are customer oriented should be prioritized. But during nighttime, when the customers are not so active, operations and services within the enterprise could be provided more resources. Therefore the driver software should be able to modify its resource usage in real time without affecting the sustainability of the platform.

# 1.2 Definition of Goals of the work

Clear cut goals of the project were pre-defined so as to ensure speedy and efficient development:

- Build a Character Device Driver to control and manage the FPGAs connected through PCIe to the host server.

- Huge Data centres would have hundreds of FPGAs running in parallel. The driver should detect and enumerate the FPGAs for management.

- The driver should be able to perform PIO read and write to each of the 16 sockets of the FPGAs. The number of sockets might vary depending on the FPGAs.

- The driver should be able to perform DMA read/write operations from the user space of the host server to the FPGA. This DMA transfer should be optimized in terms of throughput, power consumption, latency, memory requirements, etc.

- The driver should be able to switch between polling and MSI interrupts to determine completion of DMA transfers. MSI interrupts are efficient, but more complicated and less versatile. Therefore depending on the platform the user should be able to switch between the two.

- User space APIs to control and manage the FPGAs are to be developed. These APIs gives the users the ability to control and manage the FPGAs without the need to know the hardware level details. This enable speedy development of softwares and applications.

- User friendly APIs and informative Documentation allows easy integration of the FPGAs and its APIs into user applications.

- The driver could be used in different kinds of platforms and environments. Therefore depending on the performance requirement, the performance of the FPGA need to be altered.

- There are instances where several FPGAs need to be controlled from the same application simultaneously. Separate APIs need to built be for this purpose.

- A test environment needs to be built which would test the sustainability and portability of the FPGA, the driver and platform. Test APIs are required to verify if all the above requirements of the software are fulfilled all the time.

- For efficient control and management of the FPGAs, a user friendly GUI is to be developed which would showcase FPGA parameters like temperature, performance level, read and write throughput from anywhere around the world.

# 1.3 State of the Art

The section analyses the technological analysis and literature work done by experts in the field. [KB12] shows a PCIe device driver using Xylinx FPGA used in IceCube Neutrino Observatory(South Pole). It has a performance of upto 784MB/s for a 4 lane generation PCIe bus. The [KMB14] also shows that the performance can be tremendously increased by using a motherboard with a better chipset. The size of the buffer would also increase the data rate. In 2014, [RCC<sup>+</sup>14] shows PCIe core adopted a new strategy wherein the DMA descriptor list is stored inside the FPGA rather than the central memory. With this approach a peak data transfer rate through the PCIe of upto 3.4GB/s was achieved. [ZLBAM15] uses IOCTL functions to control the DMA read and write operations from the user space.

[CPCAKMN18] writes about the PCIe DMA design for an FPGA developed for the detector system at CERN LHC designed to study the properties of Quark Gluon Plasma. It is the interface between the online-offline computing system and Common Readout Unit(CRU). The design involves loop back flow of data for high performance data transfer. The length, source and destination address are programmed into the descriptor table. The descriptor table is then transported into the FPGA. Once the data transfer according to the descriptor is complete, it updates the status register with the value 1. The paper mentions that a major bottleneck for the implementation and increased latency was the register configuration for source and destination addresses. This created dead time between two consecutive DMA data transfers. They reduced the dead time by looping over descriptor tables. This ensured pipelining of descriptors. A series of tests were conducted to choose the appropriate number of descriptors for maximum performance. Finally 128 descriptors were chosen and they were able to achieve upto 6GB/s throughput in Gen3 8 lane mode. The design needs to make sure some additional processes are performed to make sure that dead time for DMA transfers is limited. [CPCAKMN18] states that the polling to check DMA status affects the DMA performance considerably. It also states that future work is to consider developing the same project on PCIe40 card.

[PDL15] implements PCIe readout with a throughput of upto 12GB/s using 16 lane PCIe. The driver is developed for the LHCb experiment at CERN. The current hardware clocks at 1.1 MHz and they need an upgrade to 40 Mhz. After careful consideration, they chose the PCIe Gen3 technology. Performance analysis on i7-3820 CPU and i7-4770 CPU, shows a variation of upto 10 percent. This shows the performance of the DMA operation is highly dependent on the host platform as well.

# 2 Theoretical background

# 2.1 PCI express and Nallatech Board

### 2.1.1 PCI Express

PCIe was designed to add more features and performance to the older PCI [RB05]. PCIe was designed such that it would be software compatible with PCI. This was done to make sure that the older systems would be able to detect and configure the new PCIe without the PCI express features. Therefore PCIe was designed with the same usage model and software compatibility. However, they do come with differences, for instance, PCIe is designed on serial bus technology whereas PCI was based on parallel bus [Abr15]. This reduced the number of lines connecting the PCIe endpoint to the host PC thereby reducing the complexity and cost. This increased the transaction frequency thereby increasing the overall read and write throughput. Generation 3 of PCIe supports up to 8 GBps of transaction rate theoretically. It has scalability where by the number of lanes used per device can be varied. The data-sheet provides the specification for usage from 1 lane all the way up to 32 lanes. The lane width and the speeds are negotiated between the host complex and the endpoint device during the enumeration process. Either the end point card or the root complex can decide on the maximum lanes and throughput to be used. It is to be noted that both the PCIe and PCI are only software compatible. Therefore a PCIe device cannot be inserted into a PCI slot or vice versa.

Root complex is basically the host controller present on the server and provides slots on which other PCIe cards can be connected. PCIe has its own memory address space which can be either 32 or 64 bit. This address space is visible only to the PCIe devices such as root complex, PCIe endpoints, switches and bridges. Switches are used to connect multiple PCIe devices to the root complex. These switches can be used when the board doesn't contain sufficient slots for all the endpoint devices.

#### 2.1.1.1 Structure

The root complex connects the external PCI and PCI devices to the CPU [Abr15]. The CPU initially accesses the root complex to configure the root complex IP and then finally the external devices connected through the root complex [RB05]. Once the endpoint devices are configured, the CPU uses the root complex for all further transactions with the endpoint.

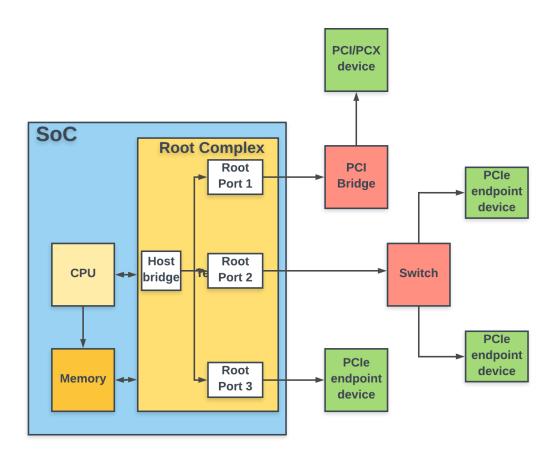

Figure 2.1: PCIe structure diagram

The root complex can send interrupts to the CPU for any event completion of the root complex or of any of the endpoint devices. The root complex has direct access to the PC memory. This capability is employed to perform high-performance DMA transfers between the endpoint devices and the host PC. To enable DMA transfer, the root complex must first provide the 'Bus Master' status to the endpoint device. Further, it should send addresses in the host PC's memory to which DMA transfer should be performed by the endpoint device. Devices are to be connected to the root complex through the root ports. Figure 2.1 shows the particular root complex has three root ports embedded into it. The first root port is connected to the PCI device through the bridge. PCI-X (Peripheral Component Interconnect eXtended) devices can also be connected using PCX bridges. Multiple PCIe devices are connected to the 2nd root port using a PCIe switch. A PCIe device is connected directly to the third root port.

PCIe uses point to point topology. In the mechanism, a single point to point bus would connect two devices. The root complex contains a host bridge which connects the root ports to the CPU. The root ports are all simple Virtual PCI-PCI bridges. A root complex may have multiple Virtual PCI-PCI bridge. The host bridge is connected to the Virtual PCI-PCI bridge through Bus 0. Each of this Virtual PCI-PCI bridge spawns separate

buses through which other PCI devices can be connected. A switch inturn has multiple Virtual PCI-PCI bridges. The root complex is connected to the Switch through the Virtual PCI-PCI bridge which in turn spawns out a new bus. The multiple endpoint devices are connected to the switch through new Virtual PCI-PCI bridges which in turn spawns out a new bus for each of the devices. Each of the buses would be given a bus number or an ID during the enumeration process by the host PC. These given buses numbers will be used henceforth for routing the data. Each bridge or switch contain information about 3 buses [KMB14]:

- Primary Bus number: The bus number through which the particular device is connected to the root complex.

- Secondary Bus Number: The lowest bus number which is greater than the primary bus number.

- Subordinate Bus number: The highest Bus number which is connected to the switch or bridge.

Any transaction to a bus number equal to or greater than Secondary Bus Number and less than or equal to Subordinate Bus number will be routed through the switch/bridge [Zha10]. PCIe uses lesser number of lanes compared to the PCI because of serial transactions. Each lane consists of 2 pairs of RX and TX lines. PCIe, unlike PCI, has no separate IRQ lines.

#### 2.1.1.2 Address Space

The root complex can access the PCIe configuration space using the PCIe address space [Abr15]. The PCIe configuration space provides the server all the required information about the device. This information is used to enumerate the device and to allocate sufficient resources to the device by the server. PCIe address isn't a physical entity and is completely virtual. It is a list of information used in the transaction layer packet to identify the destination and source of the packet. The root complex comprises of root registers which store the IP of the devices. It registers information like the clock frequency, the vendor ID, device ID, lane widths, transaction speeds, address translation unit, etc. The address space and vice versa. The root complex also has the configurable address space. It is used by the CPU to access the PCIe address space. Every root complex contains the following 4 address spaces associated with them according to PCI specification:

- Configuration Space

- IO space

- Message Space

- Memory Space

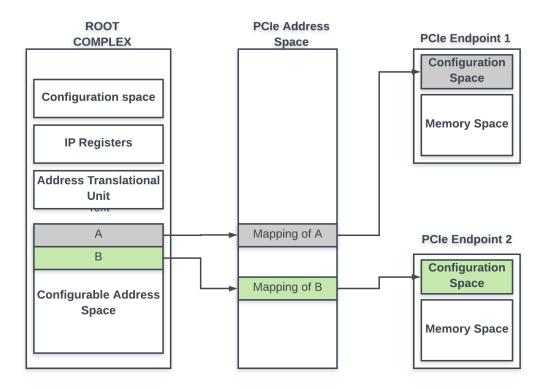

Figure 2.2: PCIe Address Space

All the above address spaces except memory space have physical addresses associated with them. The configuration space contains all the information required by the root complex about the device. This includes device ID, vendor ID, MSI capability, device class and other various capabilities of the device. It has various registers to configure the capabilities of the device. For example, changing the configuration values can put the device to a lower power state or disable interrupts. These kinds of additional capabilities were added to PCIe by including a bigger configuration space. The size was increased from 256 Bytes (in PCI) all the way up to 4KB. The first 64 bytes is called standardized headers and are of 2 types-type 0 and type 1. Type 1 is used by root ports, switched and bridges. Type 0 is used by the end point devices and holds all the information regarding its configuration. A PCIe Address Space is created as shown in Figure 2.2. it maps the Configuration space of the endpoint devices to the configuration space of the root complex memory. This mapping is virtual and there is no physical PCIe address space as such.

# 2.1.2 Compute Acceleration Card - Nallatech 510T [1718]

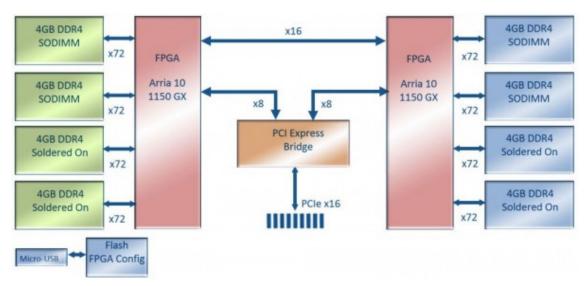

It is an accelerator card for high-performance applications in Data Centers. The board is specifically designed to house 2 FPGAs (Intel Arria 10) to deliver maximum per watt performance. It uses 16 lanes Gen 3 PCIe cards. The 16 lanes are split up among both the FPGAs. Its characteristics are as follows :

- Performance upto 3 TFLOPs

- 75 GBps Peak DDR4 Memory bandwidth

- Upto 150 GBps Aggregate memory bandwidth

It has already been employed in the following markets:

- HPC

- Datacenter

- Compute, Network and storage

- Communications

- Industrial, Broadcast

- Automotive

- Medical

Figure 2.3: Nallatech Board

The actual performance of data transfer between FPGA and server is highly dependent on the host server's hardware specifications and operating system. It contains 8 banks of DDR4 SDRAM. Each of the bank is of 4GB. Therefore, the system houses a total of 32GB memory with a transfer rate of 2133 MT/s. The card is designed to deliver upto 225W power consumption. But the actual power consumption is highly dependent on the application running on it. The power is derived from 12V PCIe slot and one 8 pin AUX connector. It has inbuilt sensors to detect voltage and temperature variations. The board is designed so that the developer need not know the hardware level details and can instead use the top layer abstraction for speedy software development.

# 2.2 Linux Kernel - Memory allocation and parallel programming

The kernel is the core of the PC that acts as an inter-connecting bridge which connects the user programs/applications to the underlying hardware. In short, kernel is where the operating system of the device operates. The kernel performs the management operations at the hardware level including data processing, memory and task management. Since a number of applications need to use the hardware at the same time, proper synchronization and control of the kernel are of paramount importance. Clear steps should be taken so that no application can take control or hack into the kernel and control the rest of the system. The segregation is also done to make sure that no bugs in any userspace application affect the rest of the system. Thus, the system memory is divided into two regions:

- 1. Kernel Memory

- 2. User Space Memory

# 2.2.1 Kernel Space memory

The operating system runs in the kernel of the system. Usually, in x86 architectures, there are 4 rings of operation. Ring 0 - Kernel Mode, Ring 1 and 2 - usually used by Device drivers, Ring 3 - User Mode. Ring 1 and 2 have "higher" privileged mode of access in a way that they can use kernel memory space and hypervisor pages, but they can't use a privileged instruction. So this is the ideal place for drivers. The initial section of the kernel memory is contiguously mapped and is called the lowmem. This is done to help in easy memory mapping for transfer of data. When a memory is required by an application, it is not continuously allocated in the kernel memory. It is allocated based on the flags the user specifies and the available free space. This is performed with the mechanism of virtual addressing. Virtual addressing gives the user application the notion that all the allocated memory is continuous even though in the actual physical memory the allocation is disjointed and separated. The virtual memory gives the user the abiloity to use some parts of its hard drive as if it were its RAM.

- Set up the driver configuration such that the driver is loaded during boot time. This gives a higher rate of successful allocation as the memory is usually free during boot time and other applications may not have already procured the available memory. This, however, is not suitable for a driver which needs to be modular and portable.

- 2. Use \_GFP\_DMA while allocating using kmalloc. The memory of the kernel space is divided into 3 zones: normal zone, DMA capable zone and high memory zone. Usually kmalloc allocates memory in the normal zone. But setting flags would make sure that the memory is allocated in either of the other two zones. These zones are platform dependent. In x86 architectures, DMA zone lies in the first 16MB of the RAM. This is also dangerous because the allocation fails in case the first 16MB of RAM is already filled.

```

#include<linux/slab.h>

void *kmalloc(size_t size, int flags);

```

Kmalloc allocation can be made contiguous in physical memory by using the right flags [5018]. In x86 architecture, the maximum contiguous memory that can be allocated is 4 MB. Any allocation more 4 MB needs to be allocated separately. In the particular implementation which uses more memory, the memories are allocated separately of 1MB size each. The argument of kmalloc 'size\_t size' is the length of the buffer that needs to be allocated and the second argument 'int flags' is the flags that need to be considered during allocation. One can also pass multiple flags using the OR operation. GFP\_KERNEL is the flag used for allocation. This is used particularly in cases where the allocation is not needed to be atomic. This is because, in case the memory allocation fails, kmalloc puts the process to sleep until sufficient memory is freed to allocate successfully.

# 2.2.2 User Space Memory

Userspace memory also popularly called userland is where all the user applications are implemented. They have no access to the kernel functionalities unless used in privileged mode. All the applications written in this space need to be transferred to the kernel space before they can be used by device drivers for passing the data to the external devices through the PCI express. This can be achieved by using the copy\_to\_user and copy\_from\_user functions available in the library include <asm/uaccess.h> [5018].

int copy\_to\_user(void \*dst, const void \*src, unsigned int size);

The copy\_to\_user function copies 'size' amount of bytes from the kernel memory space pointed by src pointer to the user space memory location pointed by dst\* [Mad17]. It initially checks if the source and destination addresses are accessible. If they are accessible then, it moves on to check if the memory location is pinned to memory because the virtual address page table could change at any time.

```

int copy_from_user(void *dst, const void *src, unsigned int size);

```

The copy\_from\_user function copies 'size' number of bytes from the user space to the kernel space memory pointed by the src and dst pointers [Mad17]. The kernel page fault handler treats this as an inaccessible address rather than a kernel code bug if the memory is not accessible by the function. This is an added ability/feature of the function. The user space applications can communicate with the kernel through system calls. In addition, ioctl(input-output control) function can be used to control the modules in the kernel.

#### 2.2.3 Parallel programming

For simultaneous access of multiple FPGAs, parallel programming is an indispensable tool. This can be achieved in the systems by using multi threading. A thread is an independent stream of instructions that can act independently from the main function [BB18]. On running a developed program, the process is created by the operating system. A process contains an overhead with the following parameters:

- 1. Process ID, process group ID, user ID, and group ID

- 2. Environment

- 3. Working directory.

- 4. Program instructions

- 5. Registers

- 6. Stack

- 7. Heap

- 8. File descriptors

- 9. Signal actions

- 10. Shared libraries

- 11. Inter-process communication tools (such as message queues, pipes, semaphores, or shared memory).

A thread uses some of the above parameters owned by the main function. They run as independent entities and duplicate only some of the above basic resources (Registers, Stack pointers, Scheduling properties, etc). Pthreads is a standard specified by the IEEE POSIX 1003.1c standard (1995) for multi threading applications. Creating and managing threads can be performed by much lower resources and overhead as compared to a process [BN11]. Pthreads enable efficient data transfer between different entities. Any number of threads can be created using the following command:

```

pthread_create(&tid, NULL, start_fn, arg);

```

It is common that the different threads try to access the same registers or resources. If multiple threads access access and change the memory simultanoeusly, it could cause inconcourrency in the memory. Therefore the idea of mutex is introduced. This makes sure that once a thread accesses and locks a resource, it cannot be altered by any other thread. This locking and unlocking can be performed by using the following command [Ber96]:

```

pthread_mutex_lock(m)

...

pthread_mutex_unlock(m)

```

# 2.3 DMA Memory mapping

There are basically two types of mapping for DMA read/write:

1. Streaming DMA mapping

This kind of mapping is done when the mapping is done right before a read or write is performed and then once the task is complete, it frees the memory. This provides the capability to optimize immensely for an application-specific task. However, the process of mapping and unmapping for every read and write creates too much overhead and decreases the overall efficiency.

2. Coherent DMA Mapping

In this mechanism, the mapping is performed on detection and enumeration of the device initially. Once the mapping is performed, it remains until the memory is freed during unloading of the module. This is specifically done when both the device and the PC needs to see changes made in the memory in real time. The memory

needs to be updated with the need for separate software flushing. Most importantly, memory access should be possible to access by both the device and the PC in parallel. Therefore the mechanism is also called synchronous mapping.

#

The function allocates a buffer of length 'size' for the device 'pdev' for the bus address \*dma\_handle and returns a virtual address that points to the bus address and can be used by the driver for all further operations. The FPGA memory is not cache coherent to the PC because the onboard DDR-RAM could change independently. The memory should be deallocated before the device driver is unloaded. A maximum of 4096 bytes of data can be contiguously allocated by the PC. In case more memory needs to be DMA mapped, they should be broken down and split into smaller non-contiguous memory blocks as is implemented in later sections. The DMA controller used by the FPGA uses scatter gather mechanism of DMA transfer. By scatter gather mechanism, it enables data from different locations to be transferred in bursts to locations that are separated from each other. Thus the data is being gathered from different locations in the source memory and then scattered in different locations in the destination device memory.

# **3** Specification

# 3.1 Driver Development

A device driver controls, manages, directs and monitor an external device connected to the host PC. An external device like a mouse, FPGA, keyboard can be controlled by a software or another hardware which in turn is controlled by a software. The FPGA in this implementation is connected to the host PC through the PCIe bus. A device driver is broadly divided into 2 parts :

- 1. OS Specific

- 2. Device Specific

The OS specific part basically deals with how the kernel deals with the external device. It is highly dependent on the operating system. Thus, a Linux, MacOS and windows driver vary highly. The device specific part of the driver is the same irrespective of the OS platform the driver is hosted on. The part needs to be programmed based on the data sheet provided by the vendor. The data sheet includes specifics like the programming, operations, registers, performance, etc.

The device driver in Linux provides an interface for the user in the user space to the kernel space through system calls [XL17]. This system calls is the methodology in which users can interact with the kernel to control, modify, operate a hardware related service, creation or operation of new processes or even basic scheduling of processes. In Linux systems, the drivers can be broadly classified into three:

- 1. Packet-oriented

- 2. Block-oriented

- 3. Byte oriented or character devices

The particular implementation uses the character vertical because the application demands byte-oriented accessibility. Linux character drivers have an advantage that they can be loaded and unloaded on the fly. In the case of windows, the system needs a reboot to enable and disable the device driver. The kernel architecture of Linux is designed such that these dynamically loadable drivers are called modules and built into individual files. These files have a .ko extension and are called kernel objects. To dynamically load or unload a module, the user can use the following commands insmod <kernel object> - loads a driver

rmmod <module> - unloads a driver

lsmod - lists all current drivers

modprobe <module> - loads the module and all its dependencies

These modules are located by design in the /lib/modules/<kernel\_version>/kernel in the root directory.

The driver does not contain a main() function. It uses the headers files from the source code of the kernel and not from the standard '/usr/include' as it is linked/loaded to the kernel [5018]. The kernel used for the particular implementation is 3.10.0-862.el7.x86\_64. The module's constructor is invoked on loading the file using *insmod*. The destructor is called on unloading the driver using *rmmod*. These two functions are named by module\_init() and module\_exit() in the kernel headers [Lae12]. Note that to build the file one needs to have the kernel headers installed on the host PC. It is usually installed at /usr/src/linux and should be verified before building the driver. The developer can also install the source code using the command line [5018]:

```

Linux - yum install kernel-devel

Mandriva - urpmi kernel-source

Ubuntu - apt-get install Linux-source

```

The driver uses *printk* statements to debug and print information to the user. The syslog daemon picks the messages from the log buffer and redirects the messages to the devices based on the configuration file /etc/syslog.conf. The developer has the option to print the statements only during debugging rather than the bombing the kernel's log throughout. These can be controlled by setting the log levels for each *printk* statement. The various *printk* log levels are given by the following table.

The developer has the option to set each *printk* statement to different levels. The developer can choose to view only a certain level or higher log messages during debugging. The log level helps the kernel determine if the message is of utmost importance or not even necessary at all and can decide if it should be shown at all. To change the log level to be shown, the user can simply write into the file /proc/sys/kernel/printk. Reading this file gives information regarding the log level chosen by the developer for the particular console and the default log level.

Macros \_\_init and \_\_exit is used at the beginning of the functions to show that it is to be built along with the kernel. Thus the system loads the driver on bootup and unloads the driver during system shutdown. These functions are executed once on bootup and shutdown. It is not relevant in case the driver is to be dynamically loaded and unloaded. All functions with the \_\_init keyword are saved in the init section of the kernel. This optimizes the system as once it is loaded during boot time, the function is removed from

| Name         | String | Meaning                                                  |  |  |  |  |

|--------------|--------|----------------------------------------------------------|--|--|--|--|

| KERN_EMERG   | "0"    | Emergency messages, the system is about to crash or      |  |  |  |  |

|              |        | is unstable                                              |  |  |  |  |

| KERN_ALERT   | "1"    | Something bad happened and action must be taken          |  |  |  |  |

|              |        | immediately                                              |  |  |  |  |

| KERN_CRIT    | "2"    | A critical condition occurred like a serious hardware/-  |  |  |  |  |

|              |        | software failure                                         |  |  |  |  |

| KERN_ERR     | "3"    | An error condition, often used by drivers to indicate    |  |  |  |  |

|              |        | difficulties with the hardware                           |  |  |  |  |

| KERN_WARNING | "4"    | A warning, meaning nothing serious by itself but might   |  |  |  |  |

|              |        | indicate problems                                        |  |  |  |  |

| KERN_NOTICE  | "5"    | Nothing serious, but notably nevertheless. Often used    |  |  |  |  |

|              |        | to report security events.                               |  |  |  |  |

| KERN_INFO    | "6"    | Informational message e.g. startup information at driver |  |  |  |  |

|              |        | initialization                                           |  |  |  |  |

| KERN_DEBUG   | "7"    | Debug messages                                           |  |  |  |  |

| KERN_DEFAULT | "d"    | The default kernel loglevel                              |  |  |  |  |

Table 3.1: printk Message logging Levels

the RAM. This optimizes the PC because if the host PC is shutting down it doesn't need to clear the RAM anyway. The kernel can decide if the exit section needs to be invoked at all based on the situation, thus optimizing the host PC. A user can communicate with the driver of any device only through its character device file linked to it using the Virtual File System [JC05]. When the user performs any operations on the device file, it is translated by the VFS to its corresponding functions in the kernel space. These functions perform the required actions in the low hardware level.

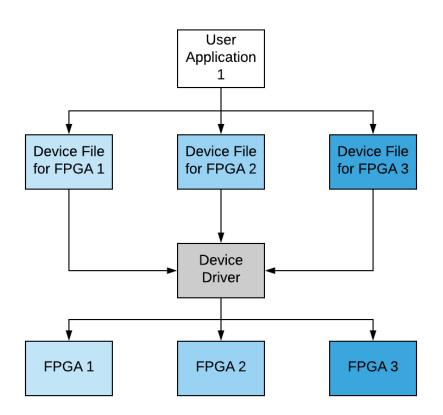

# 3.1.1 Connecting User Application to FPGA

A complete connection from the user to the endpoint device actually involves the synchronized connection of the following four entities:

- Application

- Device File

- Device Driver

- FPGA

Each of these entities can exist independently but to truly connect from the user to the FPGA, each of the entities should be linked to each other. The driver is linked to the FPGA by low-level device specific operations. The driver is linked to the device file by appropriate registration. The application connects to the device file by using open system call functionality from the userspace. The application can connect to the device file using the file name. The file name in the implementation is 'intelfpgadev<fpga number>' By

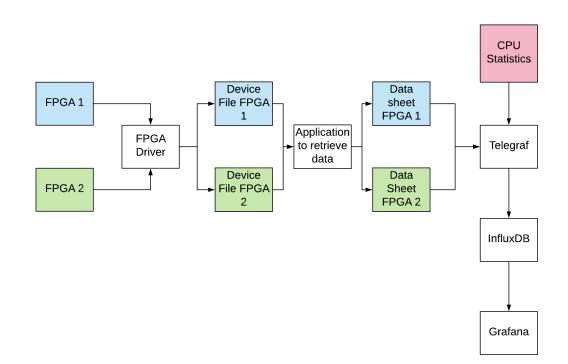

Figure 3.1: General Working Scheme of a Driver

using the required <fpga number> the application can connect to the device file of any of the FPGAs. The connection between the device file and device driver uses a combination of numbers called the major number and minor number to establish the link. It is a pair <major, minor> defined as dev\_t in linux/types.h. The driver can be connected to the device file by the following steps [JC05]:

1. Register the major and minor number of the device file.

The following function dynamically allocates a free major number to the device file and sets cnt as the minor number [5018].

2. Link the device file operations to the driver functions.

Device files were created automatically by the kernel itself in earlier versions of Linux. However, from kernel version 2.4, the kernel only populates the device information and device class into the /sys window. The udev uses this information to create the device file [1218]. Udev can then be configured to modify the device file names, permission and types. The driver initially only needs to set in the right information into the /sys window. The device class can be created by using the following function [5018]:

```

struct class *fpgaclass = class_create(THIS_MODULE, "FPGA_class_name");

```

Further, the device major and minor number can be linked by using the function:

device\_create(fpgaclass, NULL, <device number>, NULL, "<device name>");

On unloading the driver initially the device should be destroyed and then the class should be deleted. The following functions should be invoked in the same order:

```

device_destroy(fpgaclass, <device number>);

class_destroy(fpgaclass);

```

The device file is like any other Linux file and hence any operation applicable on an ordinary file is possible with device files. The only difference is that for device files, there is a VFS layer underneath which converts the operations into functions in the kernel level. The VFS should be informed about the link between the file and driver. This basically consists of two steps[1218]: Populate the file operations structure (struct file\_operatons) with the desired operations to be performed by the driver ( .open, .close, .read, .write, .probe) and then initialize the character device structure using cdev\_init(). Finally pass the initialized structure to the VFS using the function cdev\_add() from the header <linux/cdev.h> [JC05].

## 3.1.2 Read and write the Device File

By using the above functions, the system creates the following device files in /dev

/intelfpgadev1

/intelfpgadev2

Now on performing a read operation using the .read from the device file, the VFS in the kernel decodes the major and minor number and directs the message to the appropriate driver function defined by the structure file\_operations. It performs the read operation that has to be hardcoded by the developer in the driver. It finally returns the number of bytes that is read. The driver reads the data from the external device and then writes them into the specified buffer in the user space. The write operation performs the opposite. The user specifies the number of bytes to be written from the user space into the external device. The system actually reads the data from the user space and then writes them into the external space [Buc04].

#### 3.1.3 Input-output Control

Input/Output Control (ioctl) is a system call available in almost all driver categories [1218]. The advantage is that it can be used for all control operations of the external device. In addition, it can be used for changing the parameters or operations of the driver by itself. This is achieved by its arguments: command and argument. The command is the number that represents the action to be performed. The arguments are the list of values that need to be passed from the user space to kernel space or vice versa to perform the operations. The ioctl() function implements a switch() such that based on the command number, it can choose what operations to perform. The following is the function definition [5018]:

```

long ioctl(struct file *f, unsigned int cmd, unsigned long arg);

```

Where: struct file \*f is the pointer to the device file int cmd - command number for the operation to be performed unsigned long arg - structure containing all variables to be passed from user to kernel space or vice versa

It is initialized by filling the structure file\_operations with the appropriate function pointer .ioctl just like .read, .write, .open, described earlier. The function is invoked from the user space just like pread, pwrite, open, close functions. The developer should use a number that is unique throughout the system to issue an ioctl command. Else, it could cause errors such as issuing the right command to the wrong device. To create unique command codes, the bitfields of the command number has been split up. It uses 4-bit fields which have the following meaning [1218]:

[bits 7:0] Original command number - defined as per our requirement.

Another issue that arises with the ioctl function is the second argument. The second argument passes a pointer to a structure with several variables. It is the driver's duty to make sure that the pointer in the user space is accessible by the driver in the kernel space. This can be checked by using the access\_ok() function. It checks that the pointer is located in a region that is accessible by the driver. It also ensures that the pointer is not present in the kernel space. In the implementation ioctl is used for the following purposes by including the command number in system calls :

#### FPGARDGETTRANSFERRATE

To obtain the transfer rate of the last DMA read in  $\mathrm{GB/s}$

#### FPGAWRGETTRANSFERRATE

To obtain the transfer rate of the last DMA write in GB/s

#### FPGAMSIINT

To manually enable MSI interrupts to determine read or write completion

#### FPGAPOLLINT

To manually enable polling to determine read or write completion

#### FPGAWRITEDMA

To write data from user space to FPGA through ioctl function

### FPGAREADDMA

To read data from FPGA to user space through ioctl function

### FPGAPERFORMANCE

To control the performance level of the FPGA driver. The driver has 3 levels of operation based on memory and speed constraints.

#### FPGATEMPERATURE

To read the temperature of the FPGA through ioctl function

### FPGAGETPERFLEVEL

To obtain the performance level that the FPGA driver is currently working on

### FPGAGETNUMOFDEVICES

To obtain the number of FPGAs that the driver has successfully enumerated and connected

# 3.2 DMA transfer

#### 3.2.1 Design of DMA transfer

Implementation of DMA transfer between the host PC and the FPGA is the precarious and most complex section of the implementation. The user has all its data in the user space. However, there is a separation between the user space and kernel Space. A possibility to solve the issue is by mapping the user space to the kernel space from which data is transferred [XL17]. However, this mapping of DMA for character device files causes a lot of complications as shown in section 3.2.1.1. Therefore the data needs to be copied from the user space to the kernel space and then to the FPGA. This causes an increase in latency in data transfer and decreases the performance of the whole system because of the additional copy operation. Efficient algorithms need to be implemented to make sure that the data transfer from the user space to kernel space and from the kernel space to the FPGAs take place parallely without causing much utilization of the PC and time overheads. From a software engineering point of view, the efficiency can be increased by the formula [RG95]:

$$Tn = [f + (1 - f)/N] * T1$$

-Where f is the task that cannot be parallelized. 1 - f is the section that can be parallelized by N different threads/processors. Then Tn is the efficient timing derived from parallisation by N threads and T1 is the naive timing.

However, the optimization task has to keep in mind the available resources as well. In huge data centers with plenty of available resources in terms of memory and CPU power, timing efficiency is the only parameter to be considered and optimized. But in cases where the FPGA is to be used on the go, optimization should be done considering other parameters like memory usage, power optimization, etc.

DMA transfer has to be done in two phases:

- 1. Data needs to be transferred between user space and kernel space

- 2. Data needs to be transferred between kernel space and the FPGA

#### 3.2.1.1 User Space to kernel space

The first question that arises is can't the user space and kernel space be memory mapped. It is not the best option for character devices because of the following reasons.

1. In kernel mode, the code has complete and unrestricted access to the memory and underlying hardware. This is a serious threat as the it would create vulnerabilities to malicious activities. Hackers could use the loophole to disrupt the security of the device.

- 2. Crashes in Kernel mode are catastrophic, they would crash the whole PC and in worst case affect the operating system is such a way that there is no comeback. So it wouldn't be a good idea to let a device driver to device the fate of the entire PC where many applications run in parallel.

- 3. Kernel Mode code has higher performance. The only extra time consumption is the time taken to transfer data from user space to kernel space. If this latency is overcome, using driver in kernel space is beneficial. The following section elaborates on how to reduce this time and increase performance.

## 3.2.1.2 Kernel Space to FPGA

The ideology for DMA mapping is that an external device will be able to perform and control the data transfer without the CPU usage of the server [Buc04]. By letting the external device control the DMA transfer, the PC doesn't lose clock cycles and can be revert to perform more indispensable tasks. The DMA transfer is performed by the DMA controller in the FPGA using 128 descriptors (Detailed explanation in section 3.2.2).

The driver is implemented by 3 different mechanisms. The DMA read and write command can be performed from user space by using the APIs developed. The 2 APIs used are:

void dmaread(ssize\_t file, char \*buf, u\_int64\_t len, u\_int64\_t off) void dmawrite(ssize\_t file,char \*buf, u\_int64\_t len, u\_int64\_t off)

Dmaread API transfers data from the host PC user space to the FPGA. Dmawrite API transfers data from the FPGA to the host PC user space. The user has to pass the following arguments while invoking the function in case of DMA read:

- Driver file opened using opendriver function ( the number that is used to reference the FPGA)

- The pointer to the data that is to be transmitted.

- The size of data to be transmitted

- The offset address location in the FPGA to which data needs to be transmitted.

In the present driver, the read is done through driver built-in function .read. Additional capability is also provided for the driver to implement using input-output control functions (ioctl). In the kernel driver, the function copy\_from\_user is used to transmit data from the user space to the kernel space [Lin12].

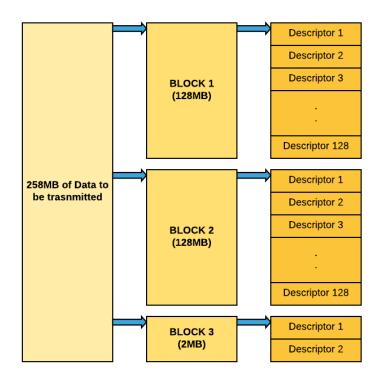

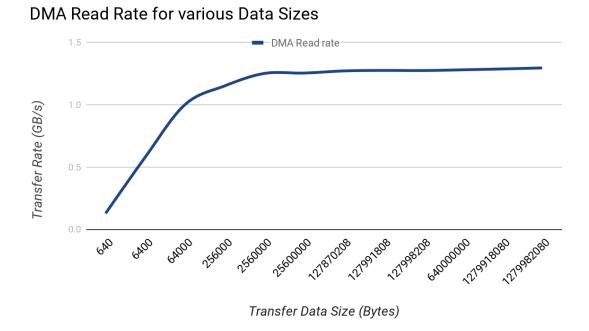

The next step in DMA transfer is to calculate the number of descriptors required to transmit the data. Each descriptor can send a maximum of 1MB of data. There are only 128 descriptors in total. So in case, the user needs to transmit 8.5MB of data, the driver needs to deploy 9 descriptors. The first 8 descriptors transfer 1MB each. The final descriptor transmits the last 0.5MB of data. In cases where the user needs to transmit more than 128MB of data, complex algorithms are developed such that the data is transmitted in blocks of 128MB each. Each block consists of 128 descriptors which transmit 1MB of data each. Algorithms are also developed such that the offset address from which data needs to be read and the destination address to which the data needs to written is calculated for each descriptor within each block.

The above algorithm divides the total data size by 128 to calculate the number of blocks because the DMA controller of the FPGA possesses only 128 descriptors. The total data size is divided by 1 to calculate the number of descriptors because the Data size transferred per descriptor is 1 MB. In figure 3.2, 258 MB of data needs to be transferred by DMA write. 258 MB of data is split into 3 blocks. The first 2 blocks transfer maximum capacity of 128 MB using 128 descriptors each. The third block transmits 2 MB using only 2 descriptors.

In this mechanism of data transfer, buffers of 1 MB are used to transfer data. This basically involves two steps:

- 1. Transfer of data from user space to kernel Space

- 2. Transfer of data from kernel Space to FPGA memory

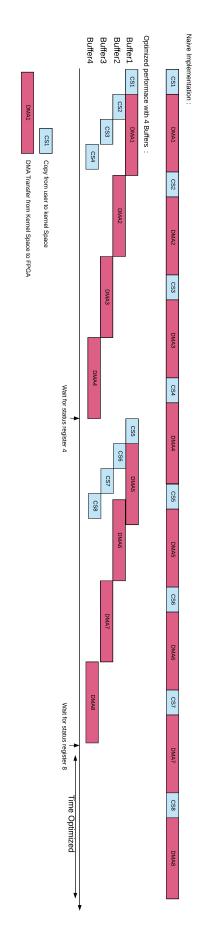

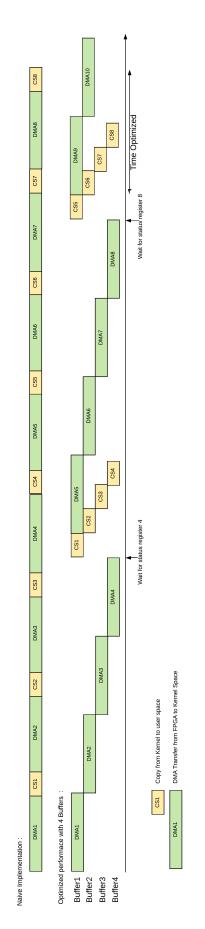

The maximum efficiency from the driver point of view can be derived if the above two operations are done in parallel. Transfer of data from User Space to Kernel space takes

Figure 3.2: Splitting Data Chunks for DMA Transfer

around 11 percent of the total time to transfer data from the user space all the way to the FPGA memory [WsCTS03]. This 11 percent time is the maximum that the driver could save if an efficient parallel algorithm is implemented.

| Naive Implementation :             |                      |                            |                            |                      |                            |                            |                      |  |  |  |  |

|------------------------------------|----------------------|----------------------------|----------------------------|----------------------|----------------------------|----------------------------|----------------------|--|--|--|--|

| Copy to<br>Kernel<br>Space         | DMA transfer to FPGA |                            | Copy to<br>Kernel<br>Space | DMA transfer to FPGA |                            | Copy to<br>Kernel<br>Space | DMA transfer to FPGA |  |  |  |  |

| Maximum Parallelization Possible : |                      |                            |                            |                      |                            |                            |                      |  |  |  |  |

| Copy to<br>Kernel<br>Space         |                      | Copy to<br>Kernel<br>Space |                            |                      | Copy to<br>Kernel<br>Space |                            |                      |  |  |  |  |

|                                    | DMA transfer to FPGA |                            | DMA transfer to FPGA       |                      |                            | DMA transfer to FPGA       |                      |  |  |  |  |

Figure 3.3: Maximum Parallelization Possible for DMA transfer

### 3.2.2 DMA Controller

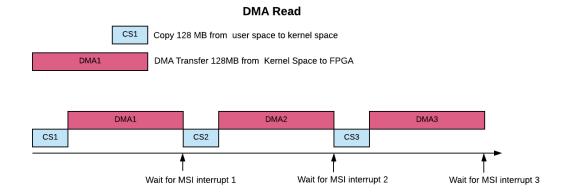

The DMA controller present in the FPGA controls the read and write operations of the FPGA. The particular FPGA supports 128 descriptors each for read and write operations. The read and write are from the point of view of the FPGA. They are controlled by the

read data mover and the write data mover. The read data mover transfers data from the PCIe address space in the root complex memory to the FPGA memory. The write data mover transfers data from the FPGA memory to the PCIe address space in the root complex memory. Initially, the driver should program the 128 descriptors and its contents in the PCI address space. The descriptors basically consist of information regarding the length, source and the destination address for each data transfer. the DMA controller works similar to Intel FPGAs as mentioned in [Ua17a]. In addition to the descriptors, the PCIe address space in the root complex memory should also have 128 status registers each of 1 DWORD. In the particular implementation, each DWORD is 4 Bytes. The status table consisting of 128 DWORDS. On completion of the task by each DMA descriptor, the status register corresponding to the descriptor byte is updated. The DMA controller has the capability to update the corresponding status register by a single 'Done' bit after completion of each and every enabled descriptor. This option can be enabled by setting the configurations in the DMA controller table. Polling can be done by the root host PC to check if the descriptor task is completed. In addition, the DMA controller sends an MSI interrupt after completion of all the enabled descriptors. Receiving MSI interrupts rather than polling will not improve the latency by a considerable amount but in turn, saves clock cycles of the host PC as it can avoid polling to check if the status register has been updated. The descriptor table is located in the PCIe address space in the root complex memory after the 128 status registers. The 128 status registers and the descriptors should be in a 32-byte boundary in the root complex memory [Ua17a].

The descriptors are numbered from 0 to 127. Therefore Descriptor would have ID 0, the second descriptor would have ID 1 and so on until the 128th Descriptor has ID 127. The RD DMA LAST PTR is a location 0x010 in the descriptor table. A read from this register specifies the last ID of the descriptor that was read. To trigger more reads one should write the ID of the descriptors to be read. The user could trigger all the descriptors by writing the last ID of the descriptor to be enabled. To enable all the 128 Descriptors, the ID number 127 should be written into RD DMA LAST PTR. For example, if the read ID at RD DMA LAST PTR is 71 and the user needs to enable 3 more descriptors, the user should fill in the details of the Descriptors of ID 72 73 and 74. Finally, the user should write 74 to the location RD DMA LAST PTR. The same is applicable for DMA write. The user should similarly use the RD\_DMA\_LAST\_PTR register at location 0x110. It is important to note that the descriptors could have out of order completion i.e. Descriptor ID 72 could complete before Descriptor ID 73. The MSI interrupt is shot the moment ID 73 is completed. Therefore the MSI interrupts cannot be completely depended on for deciding whether all the descriptors have completed their tasks. Many commercial systems are based on out-of-order completion so as to optimize the access to host memory channels. This is especially the case when the descriptors transfer data of different lengths. To overcome this issue, the implementation of the driver has taken the following steps:

• All the descriptors except the final descriptor transfers data of the same length.

| Address Offset | Register                      | Description                        |

|----------------|-------------------------------|------------------------------------|

| 0x0000         | RC Read Status and Descriptor | Specifies lower 32 bits of the 32- |