| MASTER                                                                         |

|--------------------------------------------------------------------------------|

| Resource virtualization for mapping multiple applications on the same platform |

|                                                                                |

| van Hintum, M.M.W.                                                             |

| Award date:<br>2007                                                            |

|                                                                                |

| Link to publication                                                            |

|                                                                                |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# Marc van Hintum RESOURCE VIRTUALIZATION FOR MAPPING MULTIPLE APPLICATIONS ON THE SAME PLATFORM

### RECOURCE VIRTUALIZATION FOR MAPPING MULTIPLE APPLICATIONS ON THE SAME PLATFORM

#### MARC VAN HINTUM

MSc

Embedded Systems Computer Science & Engineering Technical University Eindhoven

Jan 2007

From an engineering perspective, there are two ways to make something bigger: One is to make it physically bigger, (and human beings spent a lot of time making things physically bigger, working out ways to deliver more power to systems, working out ways to actually build bigger buildings, working out ways to expand territory, working out ways to invade other cultures and take over their territory, etc.) But there's another way to make things bigger, and that's to make things smaller. Because the real size of a system is not how big it actually is, the real size is the ratio between the biggest part of a system and the smallest part of a system. Or really the smallest part of a system that you can actually put to use in doing things.

— Seth Lloyd, Moore's Law and the Ultimate Laptop

Marc van Hintum: Recource Virtualization for Mapping Multiple Applications on the Same Platform, MSc, © Jan 2007

SUPERVISORS: prof. dr. ir. Jef van Meerbergen ir. Marino Strik

LOCATION: Eindhoven

TIME FRAME: Jan 2007 I dedicate this thesis report to my loving grandfather, who died unexpectedly during the time I was writing this work.

The increasing complexity of systems-on-chip enabled by technology scaling drives the increase in design effort. Changes are required in system-on-chip development to drive improvements in effectiveness to reduce (non-recurring engineering) cost and improve time-to-market.

To deal with these requirements a platform-based approach is advocated. Intellectual Property blocks are reused to reduce design effort. Furthermore complete platforms are reused to evolve product emphasis once performance requirements have been satisfied in a certain application domain.

However, scaling a design causes a shift in performance bottleneck from computation toward communication. Arbitration to shared resources (i.e. remote memory) can cause serious latency issues as it is a non-scalable bottleneck in the architecture. Furthermore, resource sharing also causes inter-dependencies between jobs that are mapped on the architecture. Integration or evolvement of resources changes all temporal behavior, where complete system verification is required to validate end-to-end behavior.

This thesis contributes to these issues by introducing a hardware platform, based on the Æthereal network-on-chip, that is optimized for streaming applications. Virtualization of the platform enables a compositional mapping of jobs on the architecture such that all interdependencies between these jobs are completely removed. By removing all inter-dependances the strictest form of compositionality is obtained. All additional costs for the strictest form of compositionality are accepted for this thesis. The resulting system allows for individual verification of jobs instead of extensive simulation of all possible mappings on the architecture.

#### ACKNOWLEDGMENTS

I would like to express my gratitude for all the help and support I have received throughout this graduation project. In special I would like to thank my supervisors Jef van Meerbergen and Marino Strik for giving me the opportunity to work at NXP Semiconductors and for giving me advise and suggestions for improvement during the period of my thesis.

I would like to thank Andreas Hansson for his constant support and encouragement. For giving me advise, suggestions, critique and directions to successfully fulfill my thesis assignment.

Furthermore I would like to thank all members of the Hydra and Æthereal project within NXP research, especially Kees Goossens, Marco Bekooij and Martijn Coenen. I would like to thank the members of the PreMaDona project within Eindhoven University of Technology for the opportunity to join them in many interesting meetings.

#### **CONTENTS**

```

1 INTRODUCTION

1.1 Problem description

1.2 Contribution

1.3 Organization

2 FUTURE TRENDS TOWARDS COMPLEX SYSTEMS

2.1 Deep sub-micron problems

2.1.1 Timing

Power

2.1.2

Yield

2.1.3

9

2.2 Memory

2.3 Application domain

2.3.1 Streaming applications

2.4 Architecture 13

2.4.1 Low-latency

2.4.2 Push architecture

A COMPOSITIONAL DESIGN APPROACH

3.1 Predictability

17

3.2 Compositionality

3.3 Virtualization

COMPOSITIONAL PLATFORM-BASED SYSTEM-ON-CHIP DESIGN

22

4.1 Design decisions and constraints

4.2 Interconnect

23

4.2.1 Network-on-Chip

4.3 Degrees of compositionality

PLATFORM SPECIFICATION

5.1 Hardware platform

5.2 Æthereal Network-on-Chip

5.2.1 Contention resolution

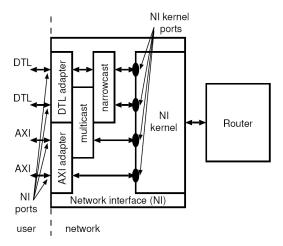

5.2.2 Network Interface

5.3 Processing elements

5.4 Memory

36

5.5 Arbiter

37

5.6 Implementation constraints

IMPLEMENTATION

41

6.1 Virtualization of the hardware platform

41

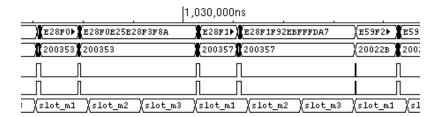

6.2 Transaction-based valid signalling

6.3 AMBA AXI shell

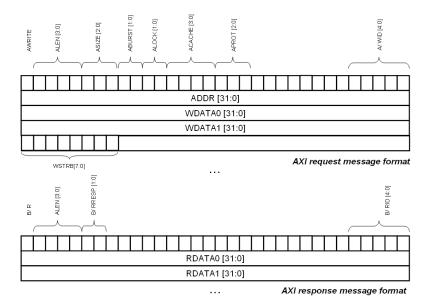

6.3.1 Message format

6.3.2 AMBA AXI target shell

6.3.3 AMBA AXI initiator shell 49

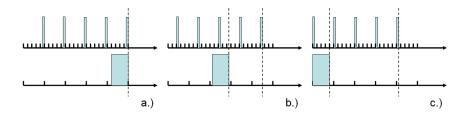

6.4 Slot-time derivation

6.5 Configuration

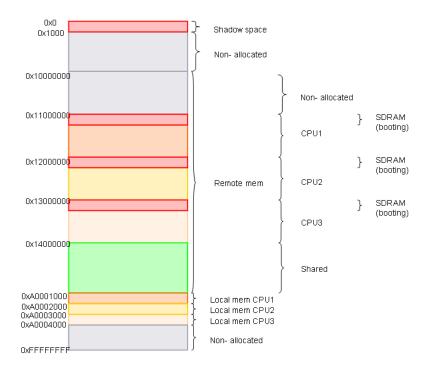

6.5.1 Address map

```

#### 6.5.2 Network configuration 53

- 7 RESULTS AND RECOMMENDATIONS 54

- 7.1 Use-case 54

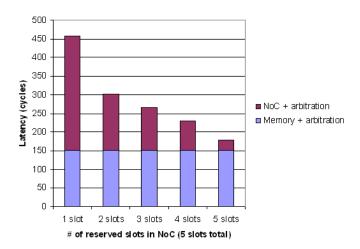

- 7.2 Results 54

- 7.3 Cost analysis 56

- 7.3.1 Parallel connections 7.3.2 Dynamism 60 7.4 Recommendations 61

- 7.4.1 Related issues 62

- 8 conclusions 64

- 9 FUTURE WORK 66

- BIBLIOGRAPHY 68

#### LIST OF FIGURES

| Figure 1  | System-on-Chip 1                    |

|-----------|-------------------------------------|

| Figure 2  | Design productivity gap 6           |

| Figure 3  | Trends for power efficient SoC 8    |

| Figure 4  | Application graph 11                |

| Figure 5  | Multiprocessor design template 14   |

| Figure 6  |                                     |

| Figure 7  | Protocol overview 24                |

| Figure 8  | Network services 25                 |

| Figure 9  | Task mapping 26                     |

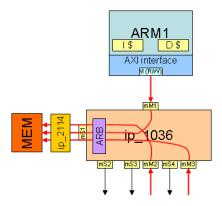

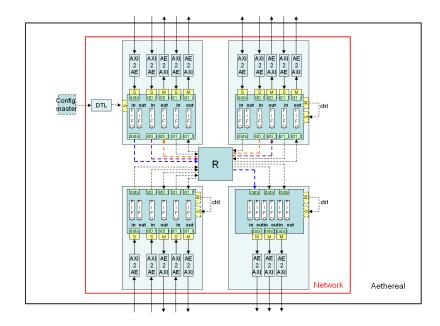

| Figure 10 | Hardware platform 29                |

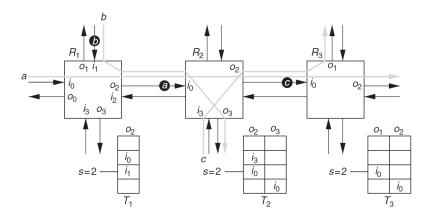

| Figure 11 | Contention-free routing 31          |

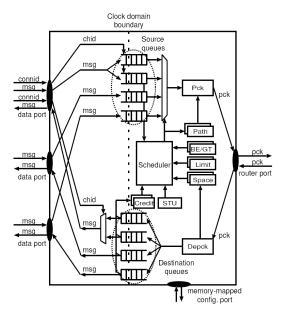

| Figure 12 | NI architecture 33                  |

| Figure 13 | NI kernel 34                        |

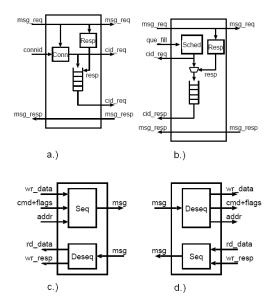

| Figure 14 | NI shell examples 35                |

| Figure 15 | Multiplexing 37                     |

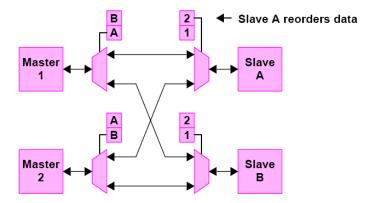

| Figure 16 | Re-ordering deadlock 39             |

| Figure 17 | Write-interleave blocking 40        |

| Figure 18 | TDMA optimization 42                |

| Figure 19 | Read transaction scheduling 44      |

| Figure 20 | Transaction signalling 45           |

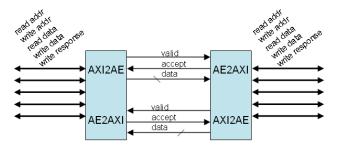

| Figure 21 | Combined AXI shells 46              |

| Figure 22 | Example of an AXI message format 47 |

| Figure 23 | Address map 52                      |

| Figure 24 | Configuration 53                    |

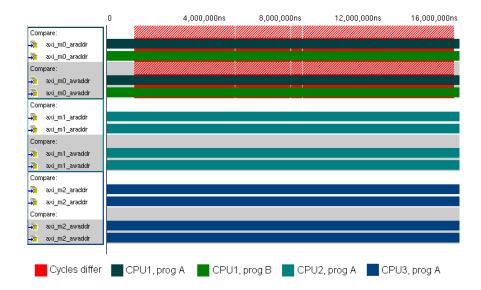

| Figure 25 | Compositionality waveform 55        |

| Figure 26 | Granularity 56                      |

| Figure 27 | Latency contribution 59             |

| Figure 28 | Dedicated channel 61                |

| Ü         |                                     |

## LIST OF TABLES

| Table 1 | Design cost 3                                |  |

|---------|----------------------------------------------|--|

| Table 2 | The three degrees of compositionality 27     |  |

| Table 3 | Memory controller, throughput and latency 36 |  |

| Table 4 | Cache influence 55                           |  |

|         |                                              |  |

#### ACRONYMS

AHB Advanced High-performance Bus

- AMBA Advanced Microcontroller Bus Architecture

- AXI Advanced eXtensible Interface

- BE Best-Effort

- CMOS Complimentary Metal Oxide Semiconductor

- CPU Central Processing Unit

- DDF Dynamic Data Flow

- DMA Direct Memory Access

- DSM Deep Sub-Micron

- DSP Digital Signal Processor

- DTL Device Transaction Level

- FFT Fast Fourier Transform

- FIFO First In First Out

- FSM Finite State Machine

- GALS Globally asynchronous and locally synchronous

- GS Guaranteed Service

- IP Intellectual Property

- IR drop Voltage drop in the supply lines

- Iso-osi International Standard Organization's Open System

Interconnect

- ITRS International Technology Roadmap for Semiconductors

- ммю Memory-Mapped Input/ Output

- MPSoC Multi-Processor System on Chip

- NI Network Interface

- NoC Network-on-Chip

- NRE Non-Recurring Engineering

- NuMa Non-Uniform Memory Access

- OCP Open Core Protocol

- PMAN Circuit-based interconnect for video streaming

- Qos Quality of Service

- RC delay Delay in interconnect lines

- RISC Reduced Instruction Set Computer

- ROM Read Only Memory

RTL Register Transfer-Level

SDRAM Synchronous Dynamic Random Access Memory

Soc System-on-Chip

SRAM Static Random Access Memory

TCL Tool Command Language

TDMA Time-Division Multiple Access

TDMC Time-Division Multiplexed Circuit-Switching

VLIW Very Long Instruction Word

XML eXtensible Markup Language

1

#### INTRODUCTION

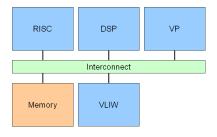

To meet the computational requirements of modern day applications in domains as multimedia and automotive, the processing power of *systems-on-chips* (SoC) has to increase. Single general-purpose processors are typically not efficient enough to suffice these high computational demands, and would lead to unacceptable power dissipation. In these cases the use of scalable and power efficient *multiprocessor system-on-chip* (MPSoC) platforms is advocated.

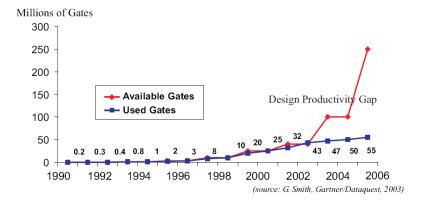

This is supported by the so-called *design productivity gap*, which states that the expected scaling towards smaller dimensions, as predicted by *Moore's law*, will continue for the foreseeable future but our ability of designing embedded systems cannot keep up with this technology scaling. In other words, *deep sub-micron* (DSM) technology enables designers to build more *complex systems*<sup>1</sup>, but the design effort is not a linear function of the size of the design. *Platform-based* SoC design promises to boost productivity by minimizing the effort to add components to a given design.

Figure 1. System-on-Chip

The importance in this is the fact that the manufacturing *non-recurring engineering* (NRE) cost of designing these complex systems rapidly becomes the greatest threat to continuation of the semiconductor roadmap, as stated by the *International Technology Roadmap for Semiconductors* (ITRS) [10]. The designer is faced with extreme challenges that arise with the additional complexity of SoC design caused by the consumers demand for increased functionality and lower cost. These challenges diverse from DSM problems (i.e. timing, power consumption and yield)

<sup>1</sup> Referring to the exponentially increasing transistor counts enabled by smaller feature sizes making it possible to integrate complete systems with many hardware resources including not only storage and processing functions but also peripherals and interfaces on a single chip

via architectural problems and application software all the way to verification.

Rapid technology change shortens product life cycles and makes time-to-market a critical issue for semiconductor customers [10], while NRE costs are in the order of millions of dollars (table 1). To avoid an explosion of the design costs reuse is advocated. The abstraction level is raised from standard cells to complete *Intellectual Property* (IP) blocks i.e. CPU, DSP, memory and interconnect. Platform-based design shortens the SoC design process by making use of reusable groups of cores to form a complete hardware platform. This enables integration of reusable and configurable IP blocks unspecific for a certain application domain.

IP reuse is only one of the challenges accompanied with the attempted closure of the design productivity gap. The ITRS lists several more of these challenges, they include [10]:

- *Reuse* support for hierarchical design, heterogeneous SoC integration (modeling, simulation, verification, test of component blocks) especially for analog/mixed-signal

- Verification and test specification capture, design for verifiability, verification reuse for heterogeneous SoC, system-level and software verification, verification of analog/mixed-signal and novel devices, self-test, intelligent noise/delay fault testing, tester timing limits, test reuse

- Cost-driven design optimization manufacturing cost modeling and analysis, quality metrics, co-optimization at die-packagesystem levels, optimization with respect to multiple system objectives such as fault tolerance, testability, etc.

- Embedded software design predictable platform-based electronic system design methodologies, codesign with hardware and for networked system environments, software verification/analysis

- Reliable implementation platforms predictable chip implementation onto multiple circuit fabrics, higher-level handoff to implementation and

- Design process management design team size and geographic distribution, data management, collaborative design support, "design through system" supply chain management, metrics and continuous process improvement

Most products fit in a larger family of products. The members of such a product domain share a lot of functionality and features. It is attractive to share implementations, designs et cetera between those members to increase the efficiency of the entire company. Once performance requirements have been satisfied in a particular application domain, in order to remain viable and competitive, the product emphasis must evolve. An example is the mobile phone, were bluetooth, a digital camera and MP3 encoder are integrated in the more advance products within the family, while the basic functionality is the same. Next to IP

reuse complete hardware platforms are reused and migrated across a family of products.

In practice many difficulties pop-up when product developments become coupled. Integration of IP blocks to enhance or extend functionality creates new dependencies as shared resources such as interconnect and memory often do not scale with product evolvement. Interference at these resources results in major latency issues when scaling the design. In combination with the increasing cost of wires due to the silicon process evolution the bottleneck in system performance shifts from computation to communication. Consequently, the contention at shared resources puts high demands on arbitration to ensure system performance requirements. When a certain requirement is established in a application domain, integration or evolvement of resources change data traffic patterns and hence it must be re-ensured that performance requirements are met.

Many applications, such as for audio and video compression, have hard real-time timing requirements (i.e. latency and throughput) to guarantee a certain quality. If these requirements are not met the quality of the audio or video may not suffice to consumer standards. Arbitration can cause timing requirements of one job to be met at the cost of missing the requirements of other jobs. Consumers expect a predictable *quality-of-service* (QoS) of systems. Therefore, timing requirements must be verified before a product is made available on the market.

|                                       | Cost for typical IC design |       |                 |       |               |       |                |       |  |

|---------------------------------------|----------------------------|-------|-----------------|-------|---------------|-------|----------------|-------|--|

| Feature dimension (transistor count)  | 0.18µm<br>(30M)            |       | 0.13μm<br>(47M) |       | 90nm<br>(54M) |       | 65nm*<br>(60M) |       |  |

|                                       | \$M                        | %     | \$M             | %     | \$M           | %     | \$M            | %     |  |

| Generation of spec<br>and spec to RTL | 0.283                      | 10.0  | 0.428           | 9.6   | 1.143         | 12.6  | 3.023          | 16.3  |  |

| RTL to netlist (verification)         | 1.621                      | 57.1  | 2.419           | 54.0  | 4.178         | 46.1  | 7.187          | 38.7  |  |

| Netlist to GDSII                      | 0.639                      | 22.5  | 1.132           | 25.3  | 2.535         | 28.0  | 5.534          | 29.8  |  |

| Validation                            | 0.295                      | 10.4  | 0.498           | 11.1  | 1.207         | 13.3  | 2.807          | 15.1  |  |

| TOTAL                                 | 2.838                      | 100.0 | 4.477           | 100.0 | 9.063         | 100.0 | 18.551         | 100.0 |  |

Note:

\* Estimate

Source:\*\*GLOBAL SYSTEM IC (ASSP/ASIC) SERVICE MANAGEMENT REPORT, IBS INC. July 05

Table 1. Design cost

Meeting design constraints can require many design iterations (*design closure*). This becomes even more true with the increasing flexibility of MPSoCs, where the enormous amount of possible combinations of applications and there non-deterministic behavior make it very difficult to valide the timing requirements. To come back at the example of the mobile phone, an MPSoC-based mobile phone may execute an MP3 decoder to produce music, while the user also writes a text message concurrently to downloading a new ring tone in the background. The user should not experience significant quality drops or delays when

activating or de-activating applications.

Interference between integrated IP blocks causes unpredictable behavior, which makes it difficult if not impossible to verify that timing requirements are met at design-time. Simulation can only be used to demonstrate that timing requirements are met for a particular set of input stimuli and therefore does not guarantee correct behavior. Moreover, simulation is time-consuming. Predictable platform-based system design is advocated to reduce design cost and time-to-market by enabling system analysis at design-time to ensure QoS.

Note that predictability is not only endangered by interference at shared resources, but by all uncertainties introduced in the design process (i.e. unpredictable IP behavior). The essence of QoS is therefore the offering of a predictable system behavior to the consumer. In order to predict the behavior of a complete system the behavior of all resources must be predictable and hence every resource must provide OoS.

#### 1.1 PROBLEM DESCRIPTION

Increased functionality and heterogeneity of MPSoC enables efficient parallel processing of jobs on a system. This increases computational power and minimizes power dissipation but on the other hand evokes a new set of problems. Dynamic market behavior results in short product life cycles and consequently high NRE design costs. These NRE design costs largely result from verification effort (see table 1). Uncertainties in resource behavior make it difficult to guarantee that a certain QoS is met. This motivates the emphasis on the analysis and prediction of the behavior of an application instead of the need for extensive simulation. Therefore, it is essential to enable a predictable mapping of the application onto the architecture.

Predictability (3.1.1) is a valuable asset that deals with uncertainties that are introduced by resources. This can be obtained by either removing or bounding these uncertainties. Predictability is a non-trivial issue and motivation of many research groups. In order to close the design productivity gap the emphases should be on predictable platform-based system design methodologies [10].

One of the causes of unpredictable behavior is due to interference at the shared resources (computation, communication and storage). Interference between resources make system behavior unpredictable. Jobs become dependant on each others temporal behavior as they share resources, and put high demand on the arbitration of contention points. A more relaxed but valid requirement that can be established is that once the temporal behavior of a job mapped on a system is predicted or simulated, that behavior is still valid for any composition of other jobs in the system. This deals with the compositionality of an architecture.

Compositionality (3.2.1) makes a design more reliable as it guarantees a certain amount of shared resources to be available for each job. Compositionality relates to the uncertainties in the availability of shared resource and thus is a necessary prerequisite for predictability, as is shown in section 3.2.2. This allows the designer to do individual analysis or simulation of jobs instead of exhaustive simulation of all

possible mappings of the system.

#### 1.2 CONTRIBUTION

This report tries to contribute to the closure of the design productivity gap by introducing the first steps towards predictable platform-based design. This report presents a compositional platform-based design methodology. First latency issues are addressed to minimize the effect of performance bottlenecks caused by resource sharing. Resource sharing creates dependances between jobs as they content for the same resource. Resource contention points put high demands on arbitration to guarantee performance requirements, which requires many design iterations. Therefore secondly compositionality is introduced, which decreases verification effort by enabling independent subsystem verification. The aim for this thesis is to prove the concept of compositionality in its strictest form, which is that the behavior of a job is not effected by other jobs on a cycle-true level. For this thesis all the costs for obtaining the strictest form of compositionality are excepted.

Compositionality is achieved by means of *virtualization* (3.3.1). This essentially means that resources are virtually divided in such a way that the temporal behavior of one job does not effect the temporal behavior of another job. This gives a job the illusion that it is running on its own virtual platform. This report thus introduces resource virtualization for mapping multiple applications on the same MPSoC based platform.

#### 1.3 ORGANIZATION

The rest of the thesis is organized as follows. Chapter 2 looks into the trends in SoC design and addresses latency issues caused by the scaling of designs enabled by DSM technologies. Based on these findings it introduces an architecture that is optimized for streaming applications. In Chapter 3 predictability and compositionality are defined and virtualization is introduced as a new design methodology. In chapter 4 the concept of virtualization is applied on the proposed architecture. Chapter 5 specifies the IP blocks that form the actual hardware platform. Chapter 6 discusses the implementation detail needed to obtain the hardware platform. Experimental results and analysis of the results are shown in chapter 7. Chapter 8 summarizes the conclusions of this thesis and chapter 9 ends with directions for future work.

#### FUTURE TRENDS TOWARDS COMPLEX SYSTEMS

As predicted in 1965 by Gordon E. Moore , co-founder of Intel, the complexity of integrated circuits roughly doubles every 2 years. The original statement is the following:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer.

Gordon E. Moore - "Cramming more components onto integrated circuits", Electronics Magazine 19 April 1965

In the foreseeable future this trend is expected to continue (figure 2). This enables the design of complex SoCs, though as stated in the introduction the downside is that the design effort for such complex systems rapidly becomes the bottleneck for continuation of the semiconductor roadmap.

Figure 2. Design productivity gap [18]

Challenges have to be met to overcome these issues resulting in the increase of complexity. This leads to requirements for new methods

and techniques to enhance productivity, controllability and quality of hardware components. To get a better insight in these issues this chapter focuses on the root causes for the increasing complexity of SoC design. This means approaching the problem from a deep sub-micron (DSM) perspective. Furthermore, the trends in resolving these issues are discussed.

#### 2.1 DEEP SUB-MICRON PROBLEMS

This section is about issues related to deep sub-micron problems. Deep sub-micron technology relates to the decrease in feature sizes towards only fractions of a micron, allowing for billions of transistors on a single die, possibly running at gigahertz frequencies. Improved microprocessor performance results largely from this technology scaling, which lets designers increase the level of integration at higher clock frequencies [26]. Though deep sub-micron technologies enhance possibilities in semiconductor integration, its complexity hampers the verification and test process and face the designer with several major technology challenges. These consequences become even greater when scaling the design towards higher dimensions.

In this report the DSM problems are divided into three groups, namely *timing*, *power* and *yield*. The following sections show how these DSM problems propagate through several architectural levels all the way to the software applications that are ran on such a systems. It introduces a new design methodology that raises the abstraction level from these DSM problems to complete hardware blocks. Furthermore, latency issues are addressed to minimize the effect of shared resource bottlenecks.

#### 2.1.1 Timing

In the early days of SoC design the main challenge was to optimize a design for speed. This issue was mainly addressed by advantages in IP performance. However, with the increase of the number of IP blocks on a chip the length of the wires connecting them (interconnect) also has increased. With the silicon process evolution the RC-delay of wires becomes much larger than the gate delay and thus the dominant factor in chip performance. Consequently, timing has become one of the most important DSM challenges and the main driver for performance limitation.

In [33] there are listed several consequences of this change in the main driver for performance limitation. First the placement and routing of the wires becomes important and hence many layout iterations are needed. This is the problem of *timing closure*. Secondly, RC delays in supply lines leads to voltage loss or so-called IR-drop associated with current peaks. Third, similar effects happen in clock lines, which causes skew problems. The arising wire delays to connect IPs now become a dominant factor. To minimize this effect, global wires should be decoupled from the local wires of an IP, i.e. clock lines become too long and consequently too slow for a SoC to be synchronized with only one clock. The future trend is now towards *globally asynchronous and locally*

synchronous (GALS) [25].

As the bottleneck changes from computation to communication, communication becomes a central concern. This causes a shift from a computation to a communication-centric approach [5, 7]. Reuse of communication structures is advocated which supports the use of *Network-On-Chip* (NoC)[5, 6, 18, 33], since on-chip networks are scalable, flexible and reusable communication structures that decouple local and global wires so that it allows for GALS.

#### 2.1.2 *Power*

The second group of problems are power related. Power dissipation is a major concern especially for mobile and wireless (nomadic) applications, where dissipation constrains can be as low as 1 Watt. This has formed the main reason to drop the supply voltage. However, for CMOS technology the drop in supply voltage typically has a negative effect on the performance. This effect on performance can be limited somewhat by scaling the threshold voltage but this again results in increased static power dissipation.

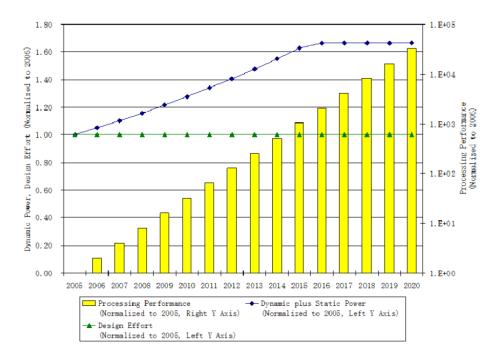

Figure 3. Trends for power efficient SoC [11]

In [11] several trends for power efficient SoC drivers are given. They are partly based on the model created by the Japan Semiconductor Technology Roadmap Design Working Group and are shown in figure 3. The application domain is "Mobile Consumer Platforms". This is a domain that is rapidly evolving and the application domain specific to this thesis. The ITRS lists several aspect of the model including [11]:

- Its typical application area is electronic equipment categorized as "Mobile Consumer Platforms" because this application area will make rapid progress in the foreseeable future across semiconductor technology generations.

- From the typical requirements of this type of SoC ("Mobile Consumer Platforms") an explosive increase of processing power is required under some upper bound for battery life.

- As a result, the requirement for processing power will be 1000x in the next ten years, while the requirement for dynamic power consumption will not change noticeably.

- The life cycle of "Mobile Consumer Platform" products is short, and will stay short in the future. Therefore, the design effort cannot be increased it needs to stay at the current level for the foreseeable future.

Note that the different requirements coincide. As shown in the figure there is a need for an explosive increase in processing power while power consumption and design effort stay near constant. With the already mentioned design productivity gap (see figure 2) and timing closure this seems as an impossible task. Solving this asks for a completely new design methodology. The future trend is now towards platform-based MPSoC design. Multiprocessors offer a cost-efficient high-performance platform to meet the throughput and latency requirements of this application domain by virtue of parallel processing. Platform based design simplifies the SoC design process by making use of reusable groups of cores to form a complete hardware platform.

#### 2.1.3 Yield

Finally there is the problem of yield. Currently inspection systems are expected to detect defects of sizes scaling down in the same way or even faster as feature sizes required by technology generations. Noise and variability have negative impact on yield and the problem of finding yield relevant defects becomes a major issue. In [12] it is stated that the signal-to-noise ratio for defect inspection tools was identified by the community as the most important challenge for yield enhancement. Noise can come from sources as the supply, the substrate, from inductive effects, capacitive coupling between neighboring wires (crosstalk), from alpha particles and other forms of radiation that injects charges [33]. Variability [27] is a major concern for predictability. It relates to the fact that identical transistors can show different electrical behavior. This causes the need for reliable systems to be designed using unreliable components. Abstraction to a higher granularity is one of the methods for solving this issue, making the design error tolerant. Though the importance of this subject, it is not within the scope of the thesis and is therefore not discussed in the continuation of this report.

#### 2.2 MEMORY

With the evolvement of MPSoC and hence the increase in processing performance one of the pressing obstacles is the disparity between memory and processor speed. This gap is referred to as the *memory gap*. On-chip memory blocks are reasonably fast but with the increase in capacity this advantage is quickly disappearing, where also the amount of chip area it occupies is increasing significantly. Off-chip memory can have virtually no capacity limitations, but is slow and needs a high amount of interface pins and therefore is often limited to one. Although a remote (shared) memory provides a large amount of available memory to a processor, communication latency is often an issue. This can mostly be hidden by caches, but still the combination of multiple processors and a scarcity of - relative slow - memory blocks leads to resource sharing and hence high demands on communication and memory resource arbitration. Shared memory becomes a non-scalable bottleneck in the architecture.

To give an example, if there is a 3% cache miss rate and every cache miss resolves into an extra 20 clock cycles penalty then 60% of the time the processor would stall. When fetching instructions and data from shared memory this poses several questions:

- Is it possible to reduce¹ the number of low-latency requests to external SDRAM?

- Does the problem come from the architecture or is it a fundamental requirement from the application domain?

The designer of a specific architecture should be aware of this problem and the posed questions. Interference at shared resources such as memory should be minimized to decrease the number of stall cycles due to arbitration. Trends are towards *Non-Uniform Memory Access* (NuMa) architectures [9] where embedded local memories are introduced that are kept close the the processor units. Distributing memory decreases the amount of sharing and furthermore the memory access time to on-chip local memory is smaller than the access time to a remote off-chip memory, thus decreasing latency and the number of accesses to the remote memory.

The memory issue appears throughout many of the application domains and is considered an architectural problem. In the following sections the requirements of the application domain are investigated to identify whether the latency requirements can be relaxed. The consequences of the architecture are discussed and an architectural template is introduced to address this issue.

#### 2.3 APPLICATION DOMAIN

In this chapter the application domain "Mobile Consumer Platforms" is introduced. This application domain is rapidly evolving and dominant in many technology offices [11]. The reason not to choose for a general purpose approach is that this statement may be too strong. By narrowing the scope to a more select application domain the architecture can

Relax vs. remove

Architecture vs. application

<sup>1</sup> Relax the timing requirements of low-latency requests or remove low-latency requests

be optimized for this, as is shown later on. However, making the scope too small would again lead to high - NRE - design and mask costs.

Applications in this domain often have high requirements on power consumption. As the application domain is focussed on nomadic applications, the system is often battery driven. To increase battery lifetime, power consumption should be as low as possible. Furthermore consumer demands raise computational requirements to enable applications with high demands on processing power.

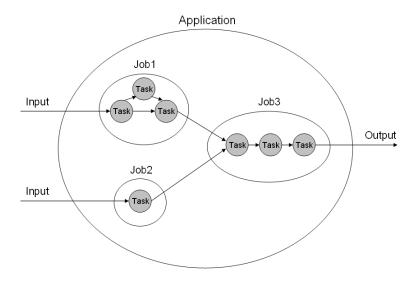

Figure 4. Application graph

To execute these applications they are mapped onto an architecture. In order to more accurately specify applications, the description of applications may require a somewhat more extended view. This description is used throughout the report. An application that is ran on a system can consist of several jobs. These jobs, in turn, can consist of several tasks possibly executed in parallel (see figure 4), which are mapped onto a certain *Processing Element* (PE). It is up to the designer to make the most optimal mapping of the application onto the architecture.

The support of a complete product family such as for "Mobile Consumer Platforms" requires flexible SoCs, which advocates the use of programmable multiprocessor systems. The advantage of the flexibility introduced by MPSoC is that multiple applications can be mapped on the same platform. Single general-purpose processors are typically not power efficient enough to suffice the high computational demand in this application domain and would lead to unacceptable power dissipation.

Often different tasks can have different requirements (i.e. computational and memory requirements). This advocates the use of different PEs, and thus a *heterogenous MPSoC*. However, the designer has to make the tradeoff between the amount of flexibility and performance of such a SoC. The use of dedicated hardware increases performance

but decreases the flexibility of the SoC. As explained this tradeoff is also dependent on the power dissipation limit, which for the "Mobile Consumer Platforms" is one of the driving constraints.

#### 2.3.1 Streaming applications

So far the only assumption that is made is that the application domain is "Mobile Consumer Platforms". As briefly discussed efficiency can be gained when a system has a specific behavior characteristic for the application domain. Note that optimization of a system for a specific behavior does not imply that the system does not work anymore for other applications. When analyzing system behavior two sorts of data streams are identified, namely *low-latency* and *latency-tolerant* data streams.

Low-latency data streams are data streams for which late arrival of the data will result in many processor stall cycles. Data/ instruction misses have typically low-latency requirements because access latency of remote memory reads causes processor stall cycles, thereby making latency to SDRAM critical. As mentioned in section 2.2 latency can be somewhat hidden by caches, but when a next instruction is not available in the cache (read miss) the data still has to be fetched from a higher level memory (i.e. remote memory) where access times may exceed tolerable timing requirements.

Latency-tolerant data streams are less dependant on latency, e.g. the processor does not stall if the latency is somewhat bigger. Sometimes techniques can be applied where low-latency data streams can be made latency-tolerant. Examples are write streams where latency is hidden by using buffers; as long as the consumer of data has enough data left in a buffer the producer can be slowed down.

A characteristic behavior of systems within the application domain "Mobile Consumer Platforms" is the use of data streams. Applications in this domain are often referred to as *streaming* applications. In [33] a more specific description of streaming applications is given.

The main characteristic is a repetition of the same function over and over again on new input data. The function can show data dependent behavior. Streaming applications are conveniently represented as graphs, e.g. dataflow graphs. An important characteristic is an explicit separation of variables in internal variables, which are local to the computation in the node and external variables, which are communicated over the edges. Data abstraction in the form of tokens is possible. For example for video applications tokens can be pixels, blocks, lines, stripes, frames, etc... Tokens are produced and consumed in fifo order. Random access is still possible within a token and also to the local state. Dynamic applications and bursty behavior can be modeled using dynamic dataflow (DDF). As a result many dynamic applications can be modeled, e.g. coding, motion compensation, graphics, etc... It is not streaming anymore if random access is needed to a dataset, which is too large to fit in local memory and thus must be stored in SDRAM. An example is H264 where motion vectors must be detected in 5 frames.

Streaming data allows for optimization due to the explicit separation of variables in internal variables. Streaming data can thereby be produced independent of the consumption of the data, where data can be buffered if the production rate is higher than the consumption rate. The producer thereby does not stall if the consumer is not able to process the data immediately. If the buffers are kept close to the consuming processor, i.e. in a local on-chip memory instead of a off-chip shared memory, the consumer has low-latency access to that data. In this case latency is hidden by the buffers, making the data stream latency-tolerant.

#### 2.4 ARCHITECTURE

In the previous sections several trends and challenges are discussed, summarized they include: deep sub-micron effects, computation versus communication, heterogenous multiprocessor SoC, global asynchrony, design productivity gap and the memory gap. These trends and challenges ask for a completely new design methodology.

The design of complex systems requires a lot of effort and specific knowledge. This not only implies complying to functional requirements but also means that the non-functional requirements, i.e. timing, power and area, have to be met. In order to minimize effort for designing these complex systems one needs to abstract from the DSM problems and emphasize on a higher level of abstraction were complete IP blocks are reused. Hence, the level of abstraction should change from standard cells to complete IP blocks such as CPUs, DSPs and memories. Reusability has been recognized as a basic principle for enhancing productivity and quality of engineering products [10].

With the evolvement of the application domain "Mobile Consumer Platforms" next to timing also power dissipation becomes an important non-functional requirement. We have seen that the lowering of the supply voltage does not suffice to solve this problem. As discussed in the previous section MPSoCs become an interesting alternative to single general-purpose processors.

As the introduction of MPSoC is accompanied with the shift towards a communication-centric design approach, the reuse of standardized communication structures is advocated. Reuse not only addresses complete hardware blocks, but also integration and verification of composed systems. Standardized communication structures and interfaces support reuse, since IPs with standardized interfaces can be easily integrated and exchanged and also the communication structure itself is reused. NoC is a promising solution offering interfaces to integrate IPs and is suitable for GALS to minimize the effect of long wires.

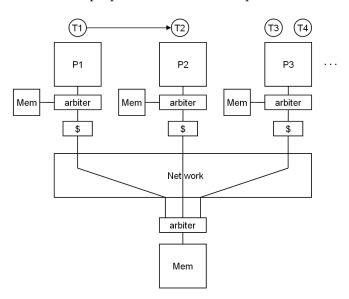

In [15] a MPSoC template is proposed, which is adopted for this report. The template is shown in figure 5. The architecture corresponds to the technology trends mentioned in this report. The platform-based design abstracts from most of the DSM problems which minimizes design effort, where the on-chip network enables decoupling of computation and communication and allows for heterogeneous multiprocessor and GALS. This is further explained in chapter 4.

The architecture has a large remote - shared - memory space capable

Figure 5. Multiprocessor design template

of storing all data, like instructions and local state. To minimize latency due to interference caused by multiple processors accessing the shared memory caches are introduced. In [16] a consistency model is proposed, which ensures this system to be software cache coherent and memory consistent in order to solve inter-task interference in the cache.

Furthermore, the architecture is a NuMa architecture where on-chip local memory is available, which enables remote memory access optimization and provides shorter access times by bypassing the global interconnect. This is explained in the previous section and is applied in this design. The local memory can be used for buffers, buffer administration and possible some data and state variables but might be too small to store all this information.

#### 2.4.1 Low-latency

In section 2.2 two questions are stated, namely whether it is possible to reduce the number of low-latency requests to external SDRAM and if the number of accesses to shared memory is a problem that comes from the architecture or whether it is a fundamental requirement from the application domain. In section 2.3 we have seen that by choosing a more specific application domain hardware optimizations can be made to reduce latency. In this section these optimizations are discussed.

As a first optimization, efficiency of the system is improved by allowing latency-tolerant data streams to bypass the cache. This is especially useful for streaming applications, where the written data is not used anymore by the producer. In this way the cache is used more optimally because the extra available cache lines can now be used for low-latency data

To reduce the number of low-latency request to off-chip shared

Figure 6. Peer-to-peer streaming

memory, [15] introduces buffers in on-chip local memory to enable peer-to-peer streaming. In this way a processor that produces data can directly write this data in the local memory of the consuming processor (see figure 6). This is not possible when only caches are used because caches do not allow a write from the network [15]. The advantages of this so-called *push architecture* are discussed in the next section. To enable peer-to-peer streaming point-to-point connections must be provided by the network and the platform must contain local memories for consuming PEs.

The proposed architecture template suits perfectly for the application domain "Mobile Consumer Platforms", as tokens can be produced by a streaming application on one PE and consumed by another PE. This allows for peer-to-peer communication, as produced streaming data is often not reused by the producer and therefore can be buffered in the local memory of the consuming party. Data is thus pushed to the consumer which has positive effects on efficiency.

#### 2.4.2 Push architecture

The advantage of pushing (writing) data instead of pulling (reading) it from the producer is that pushing data does not have to be effected by the latency of the network. When pulling data, first a request is done to the producer. Then data is send from the producer to the consumer. In this way the network is traversed twice, doubling the latency. Request can be pipelined for optimization, but this is not always possible (i.e. due to incorrect branch prediction).

For pushing data the network only is traversed once, where latency can be hidden by buffers. No request is done but the producer constantly tries to push data to the consumer. Note the requirement for a buffer in the local memory of the receiving party in order to store the data that cannot be processed immediately and flow control to ensure that data is not send if the buffer is full [2]. The consumer then has low-latency access to the data, as the data buffer is stored in the local on-chip memory and not in remote off-chip memory. Hence, latency-tolerant write streams are send to the on-chip local memories of consuming PEs and low-latency read requests access local on-chip memory.

For protocols such as AXI, where also for write commands response messages are generated, writes have to be posted. Normally, the write response is generated by the slave party. This makes the behavior of a write identical to that of a read, where for a read the response message is simply the read data coming back. For posted writes, the response data is generated by the network, thereby removing the latency needed to send the request over the network and the response back.

#### A COMPOSITIONAL DESIGN APPROACH

The previous chapters show that closing the design productivity gap involves tackling some challenges. Platform-based design is advocated, which benefits the design of more complex systems. However, when scaling the design new problems appear. Bottlenecks shift from computation to communication as latency becomes an important performance limiter. The previous chapter introduced an architecture designed to minimize latency.

Contention at shared resources not only results in latency, also the behavior of a system becomes difficult to predict due to the uncertain load of the contention point. This makes the effect of other jobs on the behavior of a certain job uncertain. A predictable system allows for analysis instead of simulation, which result in decreased verification time and actual proof of system behavior. System analysis requires predicable arbitration and QoS of all resources. Trends in future SoC design envision predictability as a valuable asset to the architecture [10].

The goal of this thesis is to introduce a compositional platform-based design methodology and give proof of concept, as stated in section 1.1. Compositionality is part of any predictable design (3.2.2) and allows for individual subsystem simulation instead of complete system simulation. This chapter gives an overview of the definitions related to compositionality.

#### 3.1 PREDICTABILITY

To be able to reason about the timing behavior of a system, i.e. to prove that throughput and latency requirements are met, the system should provide a predictable QoS. Predictability enables the designer to do analytical reasoning about the end-to-end behavior of a system and thus derive the minimum hardware to meet these timing requirements, which decreases the number of design iterations caused by intensive simulation and verification.

Unpredictability obviously is not a desired property. A simple example is that when a certain job gets more resources assigned one would predict the system to perform better. Unfortunately with current systems this is not always the case. Predicability enables the designer to make a tradeoff between the percentage of resources assigned to a certain job and the quality (i.e. the execution time or the number of missed deadlines) of the design. An increase in the percentage of available resources for a subsystem could result in a higher quality but decreases the available resources and thus quality of other subsystems.

In this report predictability is defined as follows:

**Definition 3.1.1 (Predictability)** A system is defined as predictable if bounds on the temporal behavior of one job can be derived at design time

This definition should be clarified. If one could reason about the behavior of a system, and guarantee that a system will end up in a certain state within a certain moment in time, the system is predictable. This statement is a bit vague, for instance the meaning of the word "certain". This can be made more specific by defining "certain" as "bounded". Bounding uncertainties enables predictability. If the temporal behavior of a system can be guaranteed to be within fixed bounds, the system is predictable. The key is in the size of the bounds which should be as small as possible, i.e. nobody is interested in the prediction that a system finishes within an infinite amount of years or with a 100% miss rate of deadlines.

Deriving these bounds can be done by modeling the application with data flow graphs [1]. Predictability of the system allows for a predictable mapping of an application on the architecture, which enables the derivation of best-case as well as worst-case performance and derivation of the minimum hardware requirements in order to meet these requirements.

Predictability deals with uncertainties of resources which should either be removed or at least bounded in order to provide predictable QoS. The uncertainties that endanger predictability are introduced by the hardware (i.e. cache line replacement policy and resource arbitration), the software application (i.e. conditional branches) and the environment (i.e. user input). These uncertainties make it difficult to reason about the temporal behavior of a job. In [24] uncertainty in the resource supply is distinguished from the uncertainty in the resource demand. The uncertainty in the resource supply is due to resource arbitration in the hardware of the multiprocessor system. The uncertainty in the resource demand is due to the data value dependent processing in the application and external events from the environment. In [24] also a solution is provided to bound these uncertainties. They are listed in the following two paragraphs.

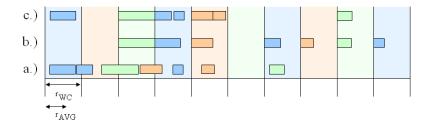

The uncertainty in resource supply is bounded by making use of predictable hardware arbitration schemes. An arbitration scheme is predictable in the case it is known how long it maximally takes before a resource becomes available. The minimal time that the resource stays available must also be known. An example of a predictable arbitration scheme for resource access is *Time-Division Multiple Access* (TDMA). In this scheme, it is guaranteed that the resource can be obtained after a fixed amount of time and that during a fixed amount of time the resource stays available. The specifics of this scheme are discussed later.

The uncertainty in the resource demand is bounded by making use of admission control and hardware resource budget enforcement. Admission control takes care that sufficient hardware resources are available when a job is started. If there are insufficient resources available in the system then the user is notified that the job is rejected. Resource budgeting guarantees that a task of a job gets a certain amount of memory, bandwidth and processor cycles. By enforcing budgets it becomes impossible for a job to claim more resources than its budget. This scheduling technique is referred to as *non-work-conserving* scheduling.

Due to these enforced budgets the interference of tasks of different jobs is bounded. With enforced resource budgets, it looks for a job as if it runs on its own private hardware. In other words, resource budget enforcement creates for each job its own virtual platform with private hardware resources.

Optimizations can be achieved by allowing for *work-conserving* scheduling. This essentially means that if part of a budget is not used, it can be used by any other job. Hence, budgets are only enforced when multiple jobs claim the same budget. In this way budget utilization is optimal: resources are only idle when there is no traffic send. Note that it is still possible to derive worst-case behavior, but the average behavior is expected to be better [34].

A predictable system can only be achieved when all resources provide QoS. If one resource in a chain of predictable resources does not provide QoS, this removes the predictability and thus the QoS of the complete system.

#### 3.2 COMPOSITIONALITY

Compositionality is a subset of predictability and deals with uncertainties introduced by sharing resources. Sharing resources introduces dependencies (contention) between jobs, which make jobs influence each others behavior making the composed system unpredictable.

In [20] a system is defined as compositional with respect to a specific property if the system integration will not invalidate this property once the property has been established at the subsystem level. This statement is too general as in this thesis we focus on the temporal behavior of jobs.

Therefore, the compositional property specific for this thesis is temporal behavior. Hence, the mapping of a job on an architecture is compositional if its temporal behavior is not effected by the temporal behavior of other jobs. More formally compositionality can be defined as followed:

**Definition 3.2.1 (Compositionality)** A system is defined as compositional if the temporal behavior of one job is completely independent of other jobs [20]

Compositionality does not require the behavior of a job to be predictable, hence uncertainties in i.e. conditional branches in the software and user input from the environment do not endanger compositionality (a job may harm itself as long as it does not harm other jobs in the system). Although compositionality does not make a system predictable, it does give several important properties to the system, i.e. if the behavior of one job can be verified, its behavior is identical (at a cycle-true level) if composed with any number of other jobs that are concurrently run on that system.

With the parallelism introduced by MPSoC many of these jobs can be active at the same time. When designing such a job the resource usage of the other jobs is often a unknown factor. Furthermore, the flexibility of MPSoCs causes the possibility of the number of sets of jobs that can be active at the same time, referred to as a use-cases, to be enormous. For example, when a certain application contains 10 jobs that can be

ran in parallel, the total amount of use-cases corresponds to an order of  $2^{10}$ . Obviously it becomes impossible to verify the correct behavior of all these use cases. Not even mentioned here are the transactions between use-cases, which for this example could possibly explode to  $2^{10^9}$ . It is desired only to verify the behavior of the 10 individual jobs and so cover all the use-cases. Again this confirms with the design productivity gap, which states that the design effort should be linear to the size of the design.

Compositionality is a necessary condition for predictability, the proof of this is given below.

**Proof 3.2.2 (Compositionality**  $\subset$  **predictability)** *Assume: Task* A *can effect the temporal behavior of task* B *and task* A *is not known at design time Proof: Task* B *depends upon the the behavior of task* A *but the behavior of task* A *cannot be predicted and thus the temporal behavior of task* B *cannot be predicted*

Temporal compositionality is endangered by uncertainties due to interference at shared resources like processing elements, shared memory and the interconnect. The uncertainties can be bounded by making it mandatory for a job to reserve these resources at startup. Reservation then bounds the time it takes for a resource to become available (resource supply) and the time is stays available for that job (resource demand), without effecting the resource utilization of other jobs. As the aim for this thesis is to prove compositionality in its strictest form, there is not any variance in these bounds. Bounding these uncertainties makes the behavior of a shared resource predictable, and hence provide QoS. Therefore a compositional system can only be achieved when all shared resources provide QoS.

#### 3.3 VIRTUALIZATION

Reservation bounds interference of shared resources and gives each job the illusion as if it is acting on its own virtual platform, thus introducing compositionality. This implicitly assumes that the uncertainties in resource supply and demand are bounded, which can be achieved in several ways using different concepts and techniques. One of these concepts is to virtually present a resource as several separate independent resources [32]. This method to implement compositionality is referred to as *virtualization* and is defined as;

**Definition 3.3.1 (Virtualization)** *Virtualization is the process of presenting the complete set of resources in such a way that the temporal behavior of one job does not effect the temporal behavior of another job. Each job thus obtains its own virtual platform.*

Virtualization requires the arbitration of resource contention points to provide predictability and thus bound resource demand. The arbiter has to ensure that the shared resource is accessed in such a way that jobs only use assigned budgets (or unused budgets for work-conservative scheduling), where assumptions have to be made or techniques have to be implemented to ensure that budgets are enforced. For this thesis

report we opt for the strictest form of compositionality, where there is not any variance in bounds. Jobs only use assigned budgets and unused budgets are not exploited. In this way jobs do not influence each other on a cycle-true level. This is not true for work-conserving scheduling, for which more refined techniques are needed to show that the property of compositionality is obtained [24].

Shared resources have to deal with inter-dependencies of different jobs, as they are not allowed to influence each others behavior. Therefore, every shared resource has to guarantee that when the resources is reserved by a certain job, the resource provides a *guaranteed service* (GS) to that job, disregarding the behavior of other jobs. This GS bounds the uncertainties in resource supply. The combination of resource reservation and GS enables predictability and hence ensures QoS of the shared resources.

With the decision to virtualize the system the designer has to accept that there are consequences with respect to probable cost constraints, i.e. timing and power consumption. This due to the fact that guaranteed service require resource reservation for worst-case scenarios, which can be expensive. For example, guaranteeing throughput for a stream of data implies reserving bandwidth for its peak throughput, even when its average is much lower. As a consequence, when using guarantees, resources are often underutilised. As the arbitration is decided to be non-work-conserving unused budgets are not assigned to pending requests of other jobs. One has to consider whether the increases in speed and energy consumption even out the increase in scalability and analysability. For this thesis all extra cost is excepted for obtaining the strictest form of compositionality.

In chapter 6 the implementation details of virtualization of the hardware platform are explained. In the following chapter the conceptual details of the compositional hardware platform are discussed. A system is computational just in case adopting the computational stance to that system offers useful generalizations and predictions about the operation of the system, over and above those generated by not adopting such a stance.

> — Istvan Berkeley, Re: Searle's challenge, The Monist Interactive Issue

> > 4

## COMPOSITIONAL PLATFORM-BASED SYSTEM-ON-CHIP DESIGN

In chapter 2 several problems are listed that contribute to the increased complexity for the design of a hardware platform. They concerned DSM problems as they propagate through the design phases. This has set the context of a new design methodology. A MPSoC platform is introduced that complies with the new technology trends. In chapter 3 virtualization is introduced as a method to enable compositionality. In this chapter virtualization is adopted to the proposed MPSoC platform to obtain a compositional platform design.

#### 4.1 DESIGN DECISIONS AND CONSTRAINTS

Several design decisions and constraints are made based on the observations in chapter 2 and 3 that influence the platform. These decisions include:

- Resource virtualization requires resource reservation at every resource contention point. Therefore, every shared resource must be scheduled with a predictable hardware arbiter and has to provide guaranteed services (hence a shared resource must provide QoS). Shared resources are scheduled based on a non-work-conserving scheduling technique

- The architecture can provide a small amount of local memory to a PE. However, the size is too small to store all instruction, state variables and data. Instructions are therefore stored in remote memory

- The architecture allows for streaming optimization, because it is a characteristic for many of the applications within the "Mobile Consumer Platforms" application domain. Therefore the interconnect has to support point-to-point connections

The latter two items are based on the support of streaming applications to address latency issues. The first item is key in obtaining a compositional platform. This requires the arbitration to shared resources to be predictable and all shared resources to provide GS. For now it is assumed that the memory is chosen such that it provides QoS and the PEs are not shared by jobs. Note that as PEs are not shared

they do not have to provide QoS. What remains is the interconnect that must arbitrate contention points with a predictable hardware scheduler and provide GS to the connected IPs.

It is not realistic to make the assumption for the interconnect. As the platform design is communication-centric the interconnect plays an important role in the design process. Based on the mentioned decisions and constraints there are several requirements for the interconnect. These are further analyzed in the following sections.

#### 4.2 INTERCONNECT

As discussed in chapter 2 wires rapidly become the bottleneck in SoC design. The communication architecture becomes a key element in the design flow. Currently, bus based interconnects are most frequently used. Advantages of a bus based interconnect is that it is a simple architecture, has low area cost and is easily extendable [6, 21, 18, 4]. However, despite bus evolvement in order to address drawbacks of bus based SoC design (i.e. ARM AMBA AXI protocol and multilayered bus design), bus based interconnects still have some disadvantages.

One of these disadvantages is scalability. With the increasing complexity of SoC design more IPs have to be connected resulting in increasing wire lengths. Intrinsic parasitic capacitance and resistance can become quite high, where the increased propagation delay may exceed a specified clock domain. As discussed in the section 2.1.1 SoC design concerns the deep sub-micron aspect, in particular the local and global physical wires on a chip. Local wires of an IP and the global wires connecting it to other IPs are often not distinguished in current day SoC design. As a result, the timing correctness of different IPs is inter-dependent: correcting a timing violation in one IP may invalidate the timing of another. Hence, the process of verifying the timing of the SoC as a whole (global timing closure), does not necessarily converge to a solution, and is specific for each design.

Communication should be decoupled from computation in order to solve this. The use of NoC is advocated [3, 4, 5, 6, 13, 18, 19, 21, 31, 33] as NoC can provide decoupling between computation and communication and furthermore the reusable communication structure scales very well for large designs.

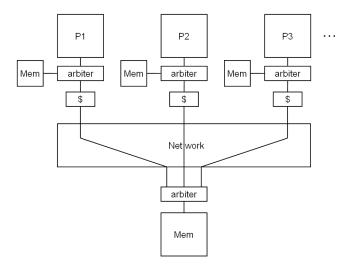

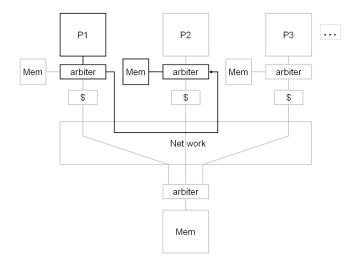

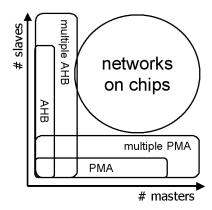

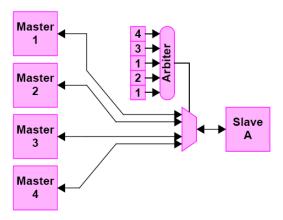

An issue related to the use of on-chip networks which should be noticed is that current bus-like interconnects often use communication protocols such as AHB, AXI and PMAN. These protocols assume the use of respectively one master and one-to-many slaves and one slave and one-to-many masters, as can be seen in figure 7. This is not optimal for NoC design, since NoC provides the resources to establish communication between one-to-many masters and one-to-many slaves. Thus for future improvement this report envisions the importance that any interconnect, but especially NoC, provides flexibility with respect to communication protocols.

Figure 7. Busses are limited by the number of masters that can be active simultaneously and concentrators like PMAN by a limited number of slaves. Network on Chip allow the combination [33]

#### 4.2.1 Network-on-Chip

In the previous sections we identified that the NoC could help in improving scalability, integration and reusability of a SoC. The reason for this can be deducted from the properties of a NoC, namely that NoCs [13, page 2]:

- A.) Structure and manage wires in deep sub-micron technologies,

- B.) Use wires efficiently through sharing,

- c.) Scale better than busses,

- D.) Are programmable for multiple and new task graphs, and

- E.) Decouple computation from communication through well-defined interfaces, enabling IP blocks and interconnect to be designed in isolation, and to be integrated more easily.

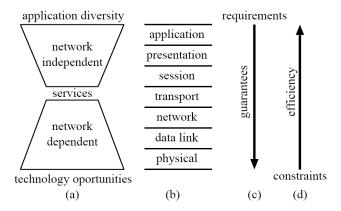

As mentioned in item "E" the communication goes through well-defined interfaces. This ensures that the implementation details of the interconnect are hidden and computation and communication can be decoupled (figure 8a). The reason for this is that NoCs are traditionally designed using layered protocol stacks, where each layer provides a well-defined interface which decouples service usage from service implementation. This is shown in figure 8b.

The goal of this thesis is to introduce a compositional architecture. This effects the interconnect as it has to provide compositionality to the connecting IPs. As mentioned in chapter 3 this requires a guaranteed service from the interconnect.

Figure 8. Network services: a.) Hide the interconnect details and allow the construction of diverse applications on top of them b.) Are built using a layered approach c.) Are driven by the application requirements d.) Their efficiency relies on technology and network organisation [8]

Most of the current interconnects, as well as NoCs have been built to offer *best-effort* (BE)¹ communication services [28]. BE communication infrastructures are not analyzable because the behavior of IPs and interconnect may be inter-dependent² as it does not take the communication of other tasks in account. Therefore, they require simulations to verify if the specified requirements are fulfilled. Because for complex chips the interconnect is a central component in the system, complete system simulations are required for system verification.

As mentioned in the previous chapter, covering worst-cases for all configurations is not possible through simulations, because they are based on sample (demanding) stimuli, which are never guaranteed to cover worst-case and corner cases. If any change, the system has to be resimulated again. In [28] three main problems with such systems are indicated: 1) long simulation times at each change, 2) numerous changes because of inter-dependencies which lead to change side effects, and 3) worst-case behavior is not necessarily covered.

To solve these problems, the use of throughput and latency guarantees is advocated [8]. The guarantees can be seen as requirements from the application (figure 8c). These guaranteed services make sure each IP module (i.e. computation and memories modules) can be designed in isolation, because the interconnect requirements are made explicit. As the communication has a guaranteed behavior, the composed system will function according to the specifications provided all IP modules meet their specifications. If IP modules have predictable behavior, the system behavior can be formally verified, without the need of simulations. If IP modules do not have predictable behavior, providing guarantees in the interconnect is still useful. This is because of the

<sup>1</sup> As the name suggest BE performs a communication action as soon as this is possible, thus if the connection is not used for another communication actions

<sup>2</sup> To avoid congestion in the lay out, the number of global wires should be minimized. This means that wires must be shared and hence bandwidth becomes a shared resource

system compositionality resulted from offering guarantees: the system does not need to be simulated as a whole, but simulating only IP modules is enough. Moreover, there are no inter-dependencies and therefore modifying parts of the system does not affect other parts of the system. Hence, by definition guaranteed services result in virtualization of the on-chip network.

However, as is explained in the previous chapters resource virtualization, e.g. network virtualization, has consequences with respect to probable cost constraints (figure 8d), which have to be considered by the designer.

#### 4.3 DEGREES OF COMPOSITIONALITY

The platform is now adopted such that all shared resources provide predictable QoS, thereby achieving compositionality by means of virtualization. To show that the platform is compositional, an application is mapped on the hardware platform.

In section 2.3 a more detailed view on applications is given, where applications are divided into jobs that can consist of multiple tasks. The designer must map the tasks to PEs in such a way that an optimal system is obtained. Figure 9 shows an example task mapping of an application onto the proposed architecture template.

Figure 9. Task mapping

The application consists of three independent jobs, where job 1 is composed out of tasks T1 and T2 and jobs 2 and 3 are composed out of respectively T3 and T4. To prove compositionality of this system the behavior of each job must be shown to be independent of the behavior of other jobs. In this report three degrees of compositionality are identified. They are listed in table 2.

| Degree        | Description                    | Status        |

|---------------|--------------------------------|---------------|

| First degree  | Tasks are independent,         | supported     |

|               | at most one task per PE        |               |

| Second degree | Tasks may be inter-dependent,  | supported,    |

|               | at most one task per PE        | not optimized |

| Third degree  | Tasks may be inter-dependent,  | not supported |

|               | multiple tasks per PE possible |               |

Table 2. The three degrees of compositionality

The first degree of compositionality can be obtained if in figure 9 the dependency between tasks T1 and T2 is removed and T4 is left unmapped. Thus, three independent tasks, T1, T2 and T3, are mapped to respectively PE1, PE2 and PE3. Proof of first degree compositionality can then be given by showing that the behavior of the three tasks is independent on a cycle-true bases.

The figure shows that jobs may contain tasks that are mapped on different PEs (T1 and T2). This places dependencies on the behavior of the involved PEs, i.e. one task T1 may produce data for task T2 on a different PE. Proof of second degree compositionality is then given be showing that the behavior of the dependant PEs is not influenced by the behavior of the rest of the PEs. Thus, the behavior of T3 (T4 is not allowed since shared PE is not supported) is independent of the behavior of tasks T1 and T2. Optimizations are addressed in section 2.4.1, i.e. by writing data directly from producer to consumer, off-chip memory is not used for communication. The hardware for this optimization is available, only the buffers that are needed in the local memories are not [2].

The figure also shows that T3 and T4 share a PE. From section 3.3 can be concluded that sharing the PE endangers compositionality. In order to obtain third degree compositionality the PEs must provide QoS (i.e. predictable scheduling) to the mapped tasks, which is assumed not to be the case. Furthermore, task switching is complicated and requires i.e. caches to be either split or flushed before the next task is executed. These inter-task dependencies are addressed in [16]. For this architecture sharing of the PEs makes all resources shared resources. For reasons of complexity PEs are not shared in this design. The mapping of task T4 is therefore not allowed.

The goal of this report will be to proof first degree compositionality. Therefore, the architectural template is implemented. This is explained in the upcoming chapters.

The chessboard is the world, the pieces are the phenomena of the universe, the rules of the game are what we call the laws of nature.

— T.H. Huxley, A Liberal Education, 1868

# 5

#### PLATFORM SPECIFICATION

In the previous chapter an architecture template is proposed that enables compositionality. In order to give proof of concept this template is implemented by creating the corresponding hardware platform. Therefore, the building blocks of the platform are specified. This chapter introduces the compositional MPSoC hardware platform.

#### 5.1 HARDWARE PLATFORM

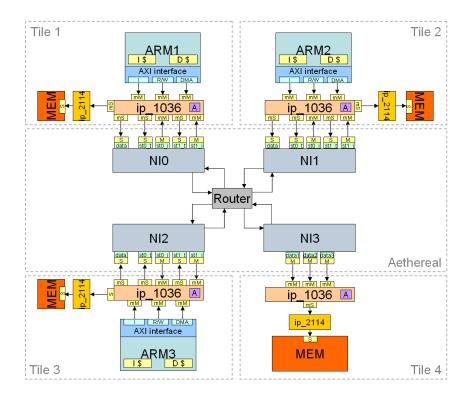

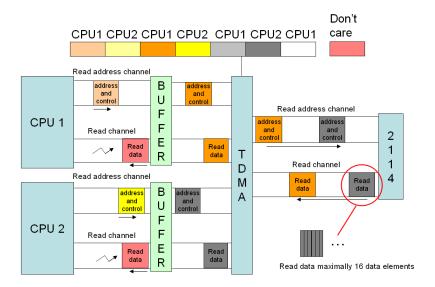

To minimize the design effort IP blocks are reused as much as possible. This results in a hardware platform where only two blocks have to be implemented, namely an AXI shell (adapter) for Æthereal and an arbiter providing compositionality (discussed in chapter 6). In figure to the hardware platform is shown. The figure contains the following blocks;

- ARM11, Model of the ARM1176JZ-s. The ARM11 has separate caches for instruction and data. The ARM11 has four ports, an instruction port, data port, DMA port and peripheral port (not visible in the figure).

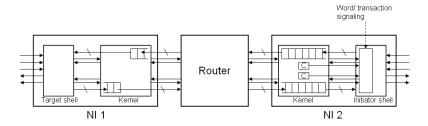

- Æthereal, fully connected instance of Æthereal (point-to-point connections instantiated at startup), where the NIs provide an AXI compliant communication interface by means of AXI shells

- ip\_1036, AXI Bus-based interconnect that multiplexes the data on the ports depending on the address. Each ip\_1036 has a arbitration block inside. Except for the arbitration in the ip\_1036 at the remote memory side, where the arbiter is changed to provide compositionality, the arbitration block is standard round-robin as deployed from the reuse database. Arbitration is performed per (mirrored) slave port.

- ip\_2114, AXI memory controller used to access embedded SRAM