#### MASTER

Level one cache performance in a multiprocessor memory hierarchy

Cabrita Alves Martins, C.A.

Award date: 2005

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

## Level One Cache Performance in a Multiprocessor Memory Hierarchy

By C.A. Cabrita Alves Martins

October 2005

Eindhoven University of Technology (TU/e) Philips Semiconductors DSP Innovation Center (DSP-IC)

Professor: Prof. dr. ir. J. van Meerbergen (Philips Research, TU/e)

> Supervisors: ir. H. Dijkstra (DSP-IC) Dr. ir. M. Bekooij (Philips Research)

# Abstract

From the highest level of perspective, the system under study is a multiprocessor system where several processing blocks share access to a level two (L2) cache memory. The audio processing block of the PNX4010 is composed of two Dual REAL RD16025 Audio DSPs. The audio solution for the PNX4010 contemplates the use of level one (L1) cache memories. Cache memory is a small, fast memory unit located between the DSP and the next levels of memory. Dynamic behaviour of caches makes them difficult to apply in real-time DSP applications. This thesis focuses on the L1 cache performance in this context. Trace-driven simulation is a type of simulation where a trace record derived from an application execution is applied to a cache profiler (C model). With this type of simulation, it is possible to explore a wide range of cache configurations, isolate cache events and perform a study at a cycle level in a single processor context. The application traces used in the study were developed in such a way that they do not consider the presence of the cache in the system. The simulations produced accurate figures for the cache performance within a specific context. When the scope increased for real-time execution, factors like scheduling and interrupts caused by external agents should be taken into account. This was not achieved using trace-driven simulation. The decision was to move onto Instruction Set Processor Simulation (ISS Simulation) were the application is under our control and allows extending the scope of the study to a multiprocessor context. The streaming applications are modelled with SDF graphs. The SDF graph can be transformed to an HSDF and it is shown that the HSDF graph can be used to derive the minimal throughput of the system. Simple streaming applications are simulated in the ISS simulator assuming that external sources copy and read blocks of data to and from the data memory.

# Acknowledgments

This thesis is a result of my graduation project performed at Philips Semiconductors DSP Innovation Center in Waalre. I would like to express my gratitude to Professor Jef van Meerbergen, Harry Dijkstra, Marco Bekooij and all the people involved for giving me the opportunity to carry out the work for this Master's thesis at Philips Semiconductors DSP-IC. The obtained results would not have been possible without the help, confidence and many hours of their valuable time to have interesting discussions in order to provide me with useful feedback, which helped me to address the problems from another perspective. I also like to thank all the people at the DSP-IC that in a way or another helped me during the course of this past seven months.

# **Table of Contents**

| Chapter 1.  |                                                  | . 8 |  |  |

|-------------|--------------------------------------------------|-----|--|--|

| Introductio | on                                               | . 8 |  |  |

| 1.1         | Background                                       |     |  |  |

| 1.2         | Problem Definition                               | 10  |  |  |

| 1.3         | 1.3 Outline of the thesis                        |     |  |  |

| 1.4. Ref    | Perences of Chapter 1                            | 11  |  |  |

| Chapter 2.  | -                                                | 12  |  |  |

| Trace-driv  | en L1 cache profiler                             | 12  |  |  |

| 2.1         | Application trace file                           | 12  |  |  |

| 2.2         | The stand-alone profiler                         | 13  |  |  |

| 2.3         | Cache model in the stand–alone profiler          | 14  |  |  |

| 2.3.1       | Block placement, replacement and identification. | 14  |  |  |

| 2.3.2       |                                                  |     |  |  |

| 2.3.3       |                                                  |     |  |  |

| 2.4         | Cache performance issues                         |     |  |  |

| 2.4.1       | *                                                |     |  |  |

| 2.4.2       |                                                  |     |  |  |

|             | Cache model assumptions                          |     |  |  |

|             | Cache Metrics                                    |     |  |  |

|             | Simulation Example                               |     |  |  |

|             | erences of Chapter 2                             |     |  |  |

|             |                                                  |     |  |  |

| -           | che profiling                                    |     |  |  |

|             | Case study                                       |     |  |  |

| 3.1.1       | 5                                                |     |  |  |

| 3.1.2       |                                                  |     |  |  |

| 3.1.2       |                                                  |     |  |  |

| 3.1.4       |                                                  |     |  |  |

| 3.1.5       | • •                                              |     |  |  |

| 3.1.6       | 1 51                                             |     |  |  |

|             | Application and trace analysis                   |     |  |  |

|             | Cache architecture                               |     |  |  |

|             | Debug information produced by the profiler       |     |  |  |

|             | Cache performance                                |     |  |  |

|             | Cache Behaviour                                  |     |  |  |

|             | Supply and consumption of data samples           |     |  |  |

| 3.6.2       |                                                  |     |  |  |

| 3.6.3       | •                                                |     |  |  |

|             | Results, Conclusions and Proposals               | 20  |  |  |

| 3.7.1       | Cache architecture                               |     |  |  |

| 3.7.1       |                                                  |     |  |  |

|             |                                                  |     |  |  |

| 3.7.3       |                                                  |     |  |  |

| 3.7.4       |                                                  |     |  |  |

| 3.7.5       | $\mathcal{O}$                                    |     |  |  |

| 3.7.6       |                                                  |     |  |  |

| 3.7.7       |                                                  |     |  |  |

| 3.7.8       | 1                                                | 41  |  |  |

| 5.8. Ket    | erences of Chapter 3                             | 41  |  |  |

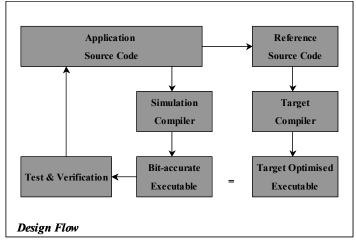

| Chapter 4                                                                | 42 |

|--------------------------------------------------------------------------|----|

| Instruction Set Simulator                                                | 42 |

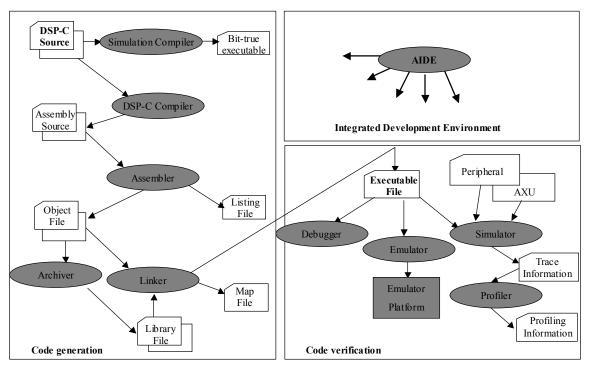

| 4.1 Integrated Development Environment                                   | 42 |

| 4.1.1 Basic Design Flow                                                  | 42 |

| 4.1.2 Development flow                                                   | 43 |

| 4.1.3 Summary of IDE main features                                       | 44 |

| 4.2 Supported Hardware Resources                                         | 45 |

| 4.2.1 DSP subsystem                                                      | 45 |

| 4.2.2 Peripherals                                                        | 46 |

| 4.3 Profiling                                                            | 47 |

| 4.4. References of Chapter 4                                             |    |

| Chapter 5                                                                | 50 |

| Processor Architecture, Model of Computation, communication & Scheduling | 50 |

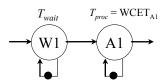

| 5.1 The Processor Template                                               |    |

| 5.2 Actors and communication                                             | 50 |

| 5.3 Model of computation, Communication and Scheduling                   | 53 |

| 5.4 Conclusions                                                          | 60 |

| 5.5 References of Chapter 5                                              | 60 |

| Chapter 6                                                                |    |

| Simulation of Streaming Applications in the ISS Simulator                | 62 |

| 6.1 Single processor simulation                                          | 62 |

| 6.2 Multiprocessor Simulation with communication via shared memory       | 65 |

| 6.3 Multiprocessor Simulation with communication via shared memory       | 68 |

| 6.4 Conclusions                                                          | 68 |

| Chapter 7                                                                | 70 |

| Conclusions and Future Work                                              | 70 |

| 7.1 References of Chapter 7                                              | 71 |

| Appendix A                                                               | 72 |

| MP3 Decoder and AAC Decoder Case Study                                   | 72 |

| A.3 XY\$ vs X\$ Y\$ model profiling results                              | 73 |

| A.4 Cache Size, Line size and associativity level                        | 74 |

| A.5 Algorithm Behaviour                                                  | 77 |

| A.6 Impact of data types                                                 | 79 |

| A.7 Granularity                                                          |    |

| A.8 Cache behaviour as function of time                                  | 81 |

# Table of figures

| Figure 1 - RD16025C1 Memory Hierarchy PNX4010                                                   | 8   |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 2 –Block diagram of the DSP                                                              | 9   |

| Figure 3 – Simulation set-up                                                                    | 13  |

| Figure 4 – Cache allocation according to the DSP address                                        | 14  |

| Figure 5 – PLRU cache line replacement algorithm                                                | 15  |

| Figure 6 - Prefetching                                                                          | 16  |

| Figure 7 – Write functional model                                                               |     |

| Figure 8 – Cache performance design space exploration                                           |     |

| Figure 9 – Icache and Dcache configuration of the example                                       |     |

| Figure 10 - Cache simulation example                                                            |     |

| Figure 12 – MP3 decoder flow diagram                                                            |     |

| Figure 13 – AAC decoder flow diagram                                                            |     |

| Figure 14 – MP3 decoder trace                                                                   |     |

| Figure 15 - AAC decoder trace                                                                   |     |

| Figure 16 – Reference cache architecture                                                        |     |

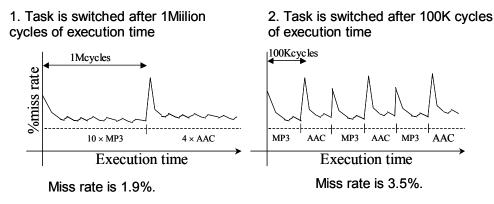

| Figure 17 – Task-switching simulation as function of execution time                             |     |

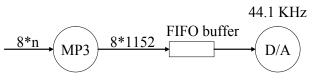

| Figure 18 – Consumption of data by D/A task                                                     |     |

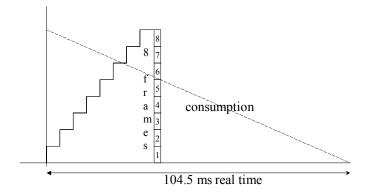

| Figure 19 - Consumption of data by D/A task<br>Figure 19 - Real time execution for MP3 decoder  |     |

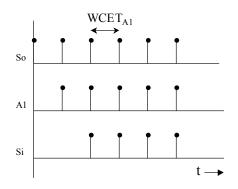

| Figure 20 - Execution time of an actor                                                          |     |

| Figure 22 – Time wheel TDMA                                                                     |     |

| Figure 22 – Time wheel TDWA<br>Figure 23 – Design flow                                          |     |

|                                                                                                 |     |

| Figure 24 – Development flow                                                                    |     |

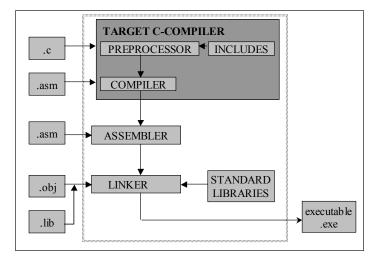

| Figure 25 – Simulation compiler                                                                 |     |

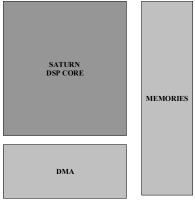

| Figure 26 – Saturn DSP block Diagram                                                            |     |

| Figure 28 – Processor template                                                                  |     |

| Figure 29 – Communication via shared memory                                                     |     |

| Figure 30 – Communication via DMA                                                               |     |

| <i>Figure 31 – C-heap protocol example</i>                                                      |     |

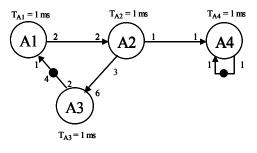

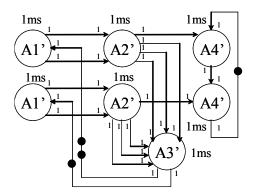

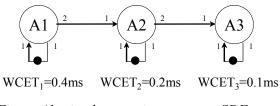

| Figure 32 - SDF graph                                                                           |     |

| Figure 33 – HSDF graph obtained after transformation of the SDF in Figure 32                    |     |

| Figure 34 – streaming application described as an HSDF graph                                    |     |

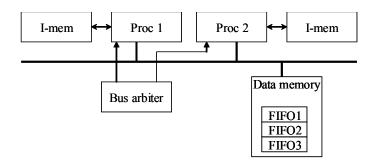

| Figure 35 – multiprocessor system with centralized data memory                                  |     |

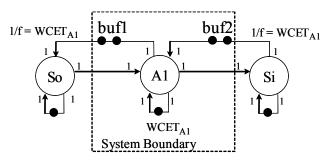

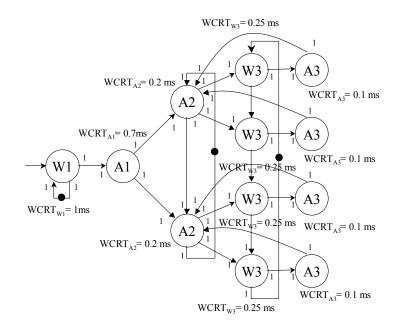

| Figure 36 – Implementation-aware HSDF graph of A1 given RR arbitration                          |     |

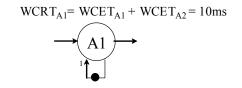

| Figure 37 – implementation-aware HSDF graph                                                     | 56  |

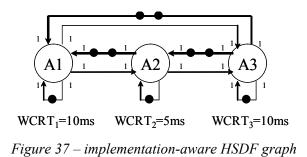

| Figure 38 – The state changes of an HSDF graph from the example                                 | 57  |

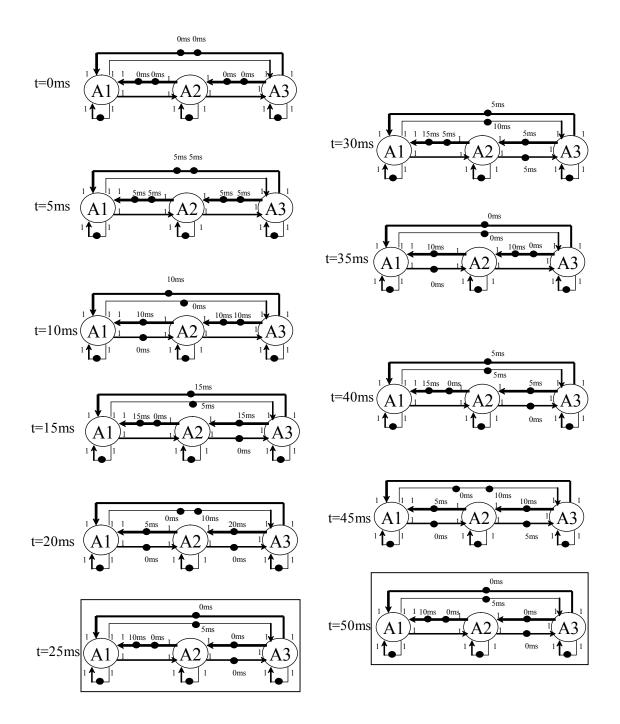

| Figure 39 – HSDF graph that is used to prove that, given a strict periodic source and sink, the |     |

| FIFO buffers at the input and at the output have sufficient capacity.                           |     |

| Figure 40 – implementation-aware HSDF if TDMA or RMS is applied                                 | 59  |

| Figure 41 – implementation-unaware SDF graph                                                    | 59  |

| Figure 42 - HSDF graph obtained after transformation of the implementation-unaware SDF of       | f   |

| <i>Figure 41</i>                                                                                | 59  |

| Figure $43$ – timeline representing the execution of the HSDF graph of figure 5.12              |     |

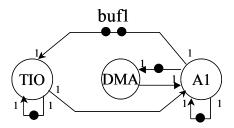

| Figure 44 – Processor connected to peripheral TIO                                               |     |

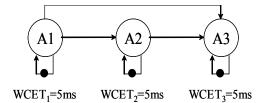

| Figure 45 – SDF graph                                                                           |     |

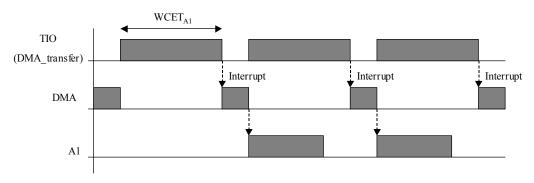

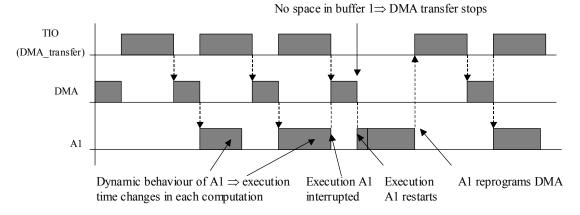

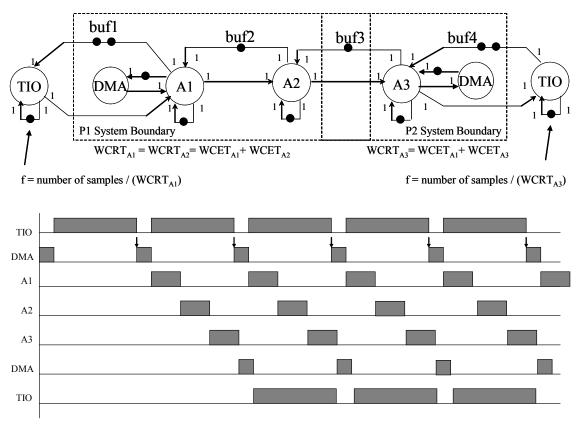

| Figure 46 – Timeline execution of actors                                                        |     |

| Figure 47 — timeline execution of actors when problem occurs                                    |     |

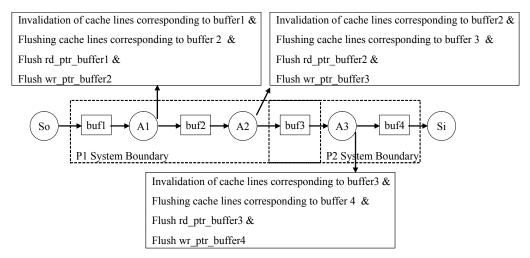

| Figure 48 – Streaming application mapped onto multiprocessor architecture                       |     |

| Figure 49 – Maintaining data coherence between cache and memory                                 |     |

|                                                                                                 | ~ / |

| Figure 50 – HDSF graph of the streaming application and timeline execution        |    |

|-----------------------------------------------------------------------------------|----|

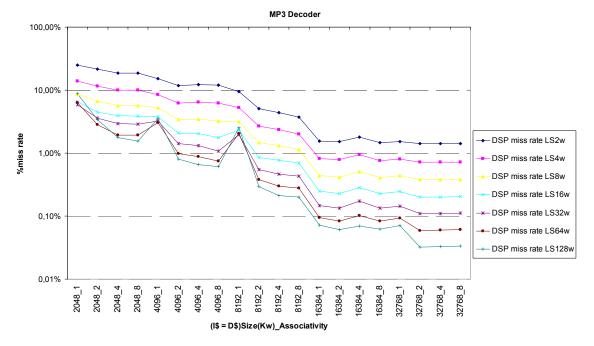

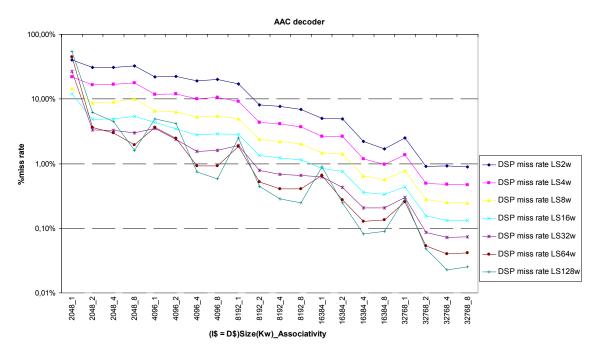

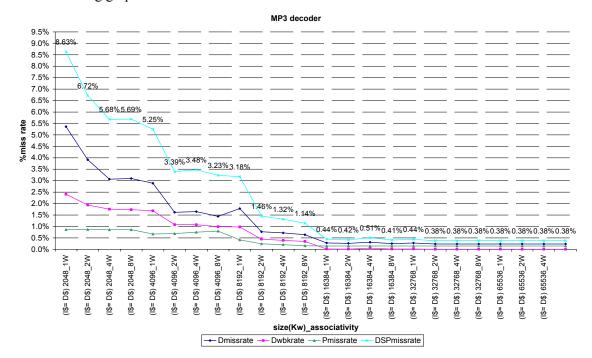

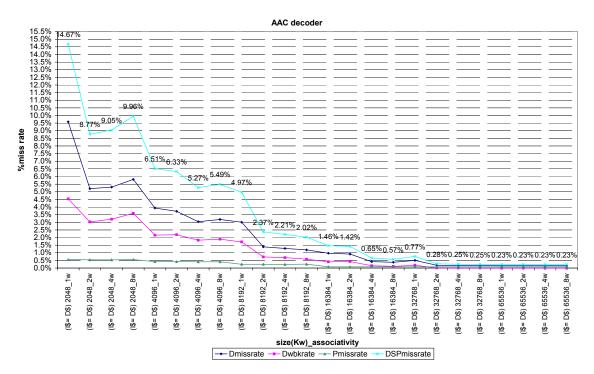

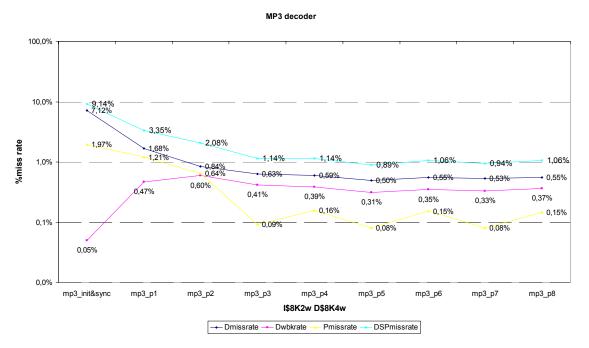

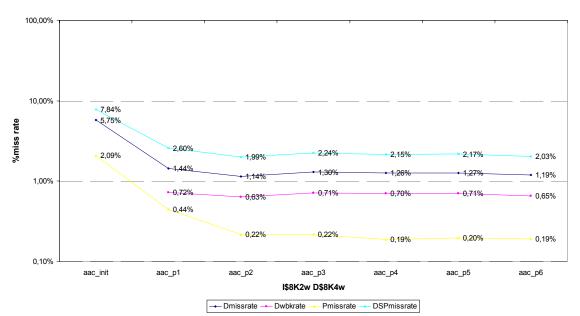

| Figure 51–MP3 decoder miss rate as function of the cache configuration            |    |

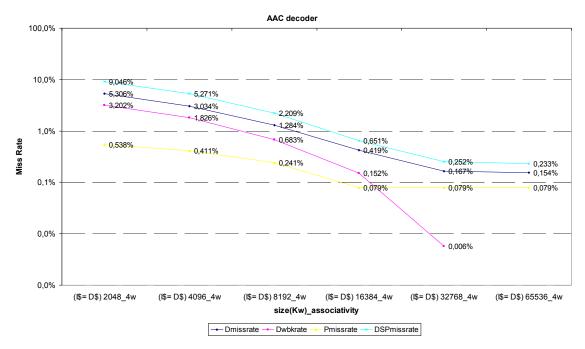

| Figure 52 - AAC decoder miss rate as function of the cache configuration          | 74 |

| Figure 53 – MP3 decoder miss rate as function of the cache configuration          | 75 |

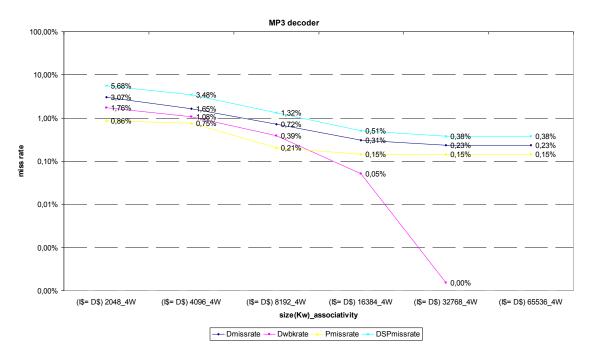

| Figure 54 - AAC decoder miss rate as function of the cache configuration          | 75 |

| Figure 55 – log-log scale of the MP3 miss rate as function of cache configuration |    |

| Figure 56 - log-log scale of the MP3 miss rate as function of cache configuration |    |

| Figure 57 – MP3 miss rate as function of the procedure calls                      |    |

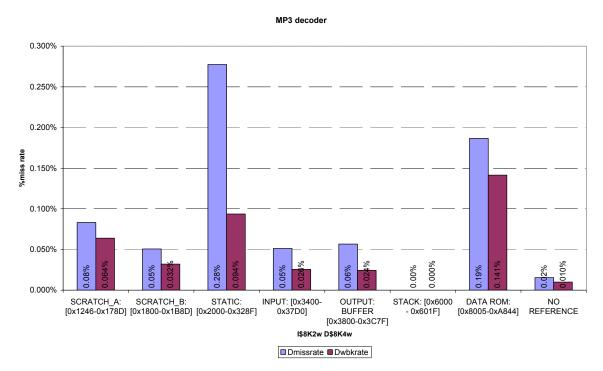

| Figure 59 – MP3 miss rate as function of data type segments                       | 79 |

| Figure 60 – AAC miss rate as function of data type segments                       | 80 |

| Figure 61 – Miss rate as function of application granularity                      | 81 |

| Figure 62 – Miss rate as function of execution time.                              | 82 |

|                                                                                   |    |

## Chapter 1 Introduction

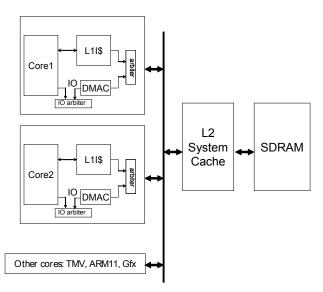

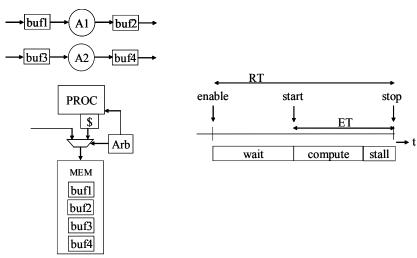

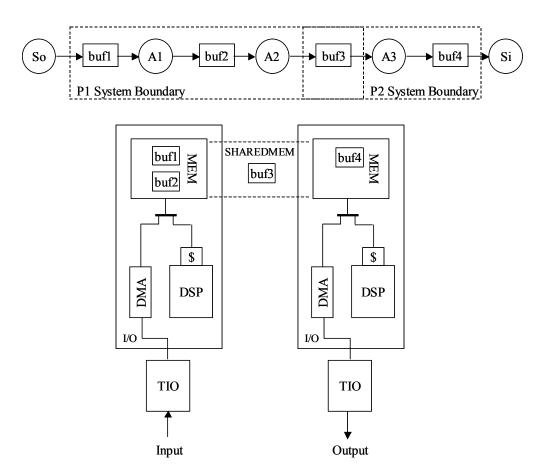

A memory hierarchy is organized into several levels – each smaller, faster, and more expensive than the next level. The levels of the hierarchy usually subset one another. All data in one level can also be found in the level below, and so on until we reach the bottom of the hierarchy. The importance of memory hierarchy has increased with advances in performance of processors. The memory hierarchy is used to overcome the processor-memory performance gap. Consumer electronics devices like smart phones are incorporating all sorts of applications like for example personal information management applications with mobile phone capabilities. All these different applications are mapped onto a heterogeneous multiprocessor system. From the highest level of perspective the system under study is a multiprocessor system composed of several distinct processing blocks: an ARM processor, a Trimedia processor and an audio processing block composed of two DSP processors. The processing blocks share the access to a level 2 cache via a bus.

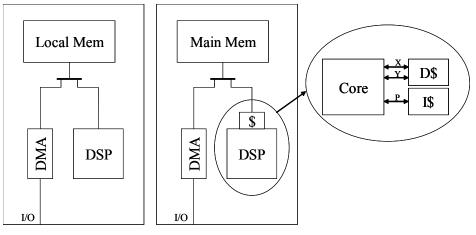

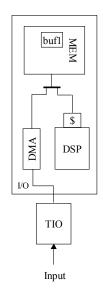

Figure 1 - RD16025C1 Memory Hierarchy PNX4010

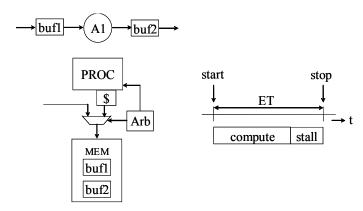

The first part of this thesis focuses in the L1 cache performance of the audio processing block. It describes the model of the cache using a stand-alone profiler, which is a C program that mimics the behaviour of the cache. A trace application is applied to the profiler. From the simulation results conclusions can be drawn about the cache architecture and cycle behaviour for audio streaming applications.

The second part extends the scope and describes the modelling and simulation of a streaming infrastructure mapped onto a multiprocessor system. Analysis techniques are used to derive the temporal behaviour of the streaming application, which is described as a Synchronous Data Flow (SDF) graph and it is constructed in such a way that the worst-case arrival times of data can be observed. The guaranteed minimal throughput of the system is derived from the SDF graph using Maximum Cycle Mean (MCM) Analysis. An Instruction set simulator is used to verify the cycle true implementation. From the simulation results it can for example be concluded how the

performance of the application can be improved by applying different mappings of the application.

This work builds on existing programming environments, cache profiler and ISS Simulator available and developed at the DSP-Innovation Centre of Philips Semiconductors.

### 1.1 Background

While caches are familiar in RISC processors they have only been recently introduced in the world of DSPs. The main reason why caches have not been used in DSP processors is because they bring a fair amount of unpredictability into hardware systems. As DSP applications became more powerful and larger, there is a need to improve the memory system. The use of caches in DSP processors can be motivated partly by cost as a relatively small amount of cache memory can approximate the performance of a much larger local memory at a significantly lower cost. Thus, DSPs can become cost-effective solutions for a much wider range of applications.

Cache memory is a small, fast memory unit located between the CPU and the main storage unit. The cache makes use of the principle of locality; it typically stores the most recently used instructions and data and hence, increases the probability of finding information locally without having access the main memory. Classic concerns when using a cache is to maintain coherence between cache and main memory, and the criteria needed to refresh cache memory as the program is executed. Typically two cache architectures are used: the Harvard, where instructions and data caches are separate; and the Von Neumann, where instructions and data are unified.

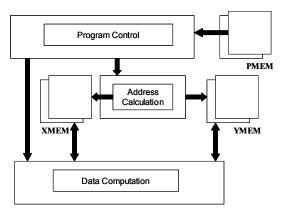

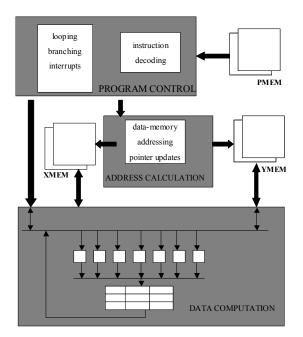

The DSP Saturn has a double Harvard architecture with two data memory spaces (X, Y), and one program memory space (P). These three memory spaces are completely independent. The DSP can perform three different tasks:

- Control the program flow

- Calculate data-memory addresses and access data memory,

- Execute the operations on the actual data.

As these tasks are relatively independent from each other, the DSP architecture is divided into three main blocks to support these activities and it is shown in *Figure 2*.

Figure 2 – Block diagram of the DSP

According to [1], two factors reduce the utility of caches in DSP applications: the data access patterns and real-time constraints. DSP applications tend to process large amounts of data and usually DSP applications display very strong locality in instructions accesses. Dynamic behaviour of caches makes them difficult to apply in real-time DSP applications. From the programmer viewpoint, it is hard to know what will be in the cache at the moment his program is executed.

Some caches provide features to help programmers design real-time applications, for example, the possibility to pre-load and lock segments of the cache. Using such a feature, portions of the cache can be loaded with specified blocks of instructions and data, and then locked so that the loaded instructions or data cannot be removed from the caches. Once portions of the cache have been locked portions become deterministic. The trade-off is that the effectiveness is reduced for the remaining instructions and data because the remaining cache size available is reduced.

DSP applications execution is typically dominated by a number of loops, making instructions caches appear attractive. Consumers typically have high expectation about the quality delivered by multimedia devices like DVD-players, audio, and television sets. These devices process data streams and have strict throughput and latency requirements. In order to meet these requirements the system must behave in a predictable manner such that it is possible to reason about its timing behaviour. The use of analytical methods is desirable because simulation can only be used to demonstrate that the system meets its timing requirements given a particular set of input stimuli. The design and programming of these real-time multiprocessor systems should be such that the real-time constraints are met, and the desired audio and video quality is delivered.

For performance and power-efficiency reasons, more than one processor often performs the processing in these systems. In many of these systems the input data is often provided by an external source, which provides a new input sample with a certain periodicity. This source can be an A/D converter and similarly and after processing the data is consumed by a D/A converter. These systems are often designed as hard real-time systems because input samples must be processed in time and output samples must be produced in time, since otherwise the input buffer overflows or the output buffer under-runs.

The analysis techniques that are described in this thesis are applicable for multiprocessor systems that execute applications described as Synchronous Data Flow (SDF) graphs. In [2] the temporal behaviour of the system is derived by constructing a SDF graph of the application that not only models the computation and the communication, but also, the effects on run-time arbitration. The guaranteed minimal throughput of the system is derived from the SDF graph by using Maximum Cycle Mean analysis [3].

### **1.2 Problem Definition**

There are several goals in this thesis:

Trace-driven L1 cache simulation (single processor context):

- Assess the L1 cache architecture.

- Derive L1 cache performance figures.

- Derive the cycle behaviour for a single and multitask simulation.

Model and Simulation (ISS simulation) of streaming applications (multiprocessor system context):

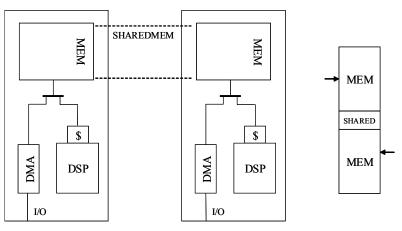

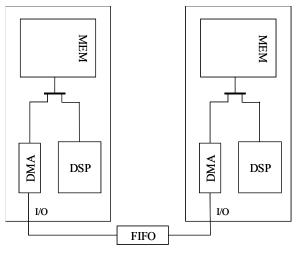

- Shared memory multiprocessor architecture.

- Study alternative architecture.

- Derive predictability of the systems and reason about system parameters.

- Implement test cases to show benefits and drawbacks of both architectures and model of computation.

### **1.3 Outline of the thesis**

This thesis is organized as follows. In the next Chapter, the trace-driven cache profiler is described. Chapter 3 presents a case study; from the simulation results, conclusions and proposals are derived. Chapter 4 describes the ISS simulator. In Chapter 5, the multiprocessor architecture is introduced along with the model of computation that is used to describe the streaming application. In Chapter 6, an example-streaming infrastructure is implemented and simulated. Finally, in Chapter 7 conclusions are drawn and recommendations are given.

### 1.4. References of Chapter 1

- [1] Lapsley Phil, Bier Jeff, Shoham Amit and Lee Edward. *DSP Processor Fundamentals: Architectures and Features*. IEEE Press. 1997.

- [2] Marco Bekooij, Orlando Moreira, Peter Poplavko, Bart Mesman, Milan Pastrnak, Jef L. van Meerbergen: *Predictable Embedded Multiprocessor System Design. SCOPES 2004:* 77-91]

- [3] F Bacelli, G Cohen, G.J. Olsder, and J-P. Quadrat, *Synchronization and Linearity*, John Wiley & Sons, Inc., 1992

# Chapter 2 Trace-driven L1 cache profiler

Caches are very important to embedded computer systems, especially due to the performance gap between microprocessors and memories is continuously becoming wider and the memory plays an important part in the overall performance. Simulation is an indispensable tool in the design of any computer system and can take many forms. Trace-driven cache simulation is frequently used to evaluate memory hierarchy performance and has been especially useful to evaluate cache performance. With this method, a software model of the cache being simulated is driven with a trace of memory references and can be used for system architecture study, determining cache miss-rates, bus traffic levels, or effective memory access times et al.

In Trace-driven simulation, a trace of instructions executed by the processor is recorded in a file and then later interpreted by the simulator. For memory hierarchy studies it is desirable to use long address traces that are accurate representations of real workloads. The software model is written in C and is open for modification – given enough time it can be created with whatever level of detail is needed to obtain results with the desired precision. In contrast, there is no control over the accuracy or completeness of the input trace data. The simulations are repeatable and allow cache design parameters to be varied so that effects can be isolated.

This chapter focuses in the cache profiler developed at the DSP-IC centre and is organized as follows. Section 2.1 describes the trace file format of the trace applications used in the simulations. Section 2.2 explains the simulator set-up and the simulation options. Section 2.3 describes the features modelled in the stand-alone profiler. In Section 2.5, the simulation assumptions are stated. The metrics used in the simulation are presented in Section 2.6. Finally, a small example illustrates the cache simulation.

## 2.1 Application trace file

A trace data record is a packet of information produced each time a traced event occurs during execution of an application, examples of traced events are a Read and Write. Trace data records contain metrics, which are relevant to a particular event. For example a time stamp, an event identifier and a memory address. The trace must contain enough information to reproduce the application behaviour.

According to [3], the process of generating a trace file can be difficult. In order to generate a trace file that can guarantee that the simulation is accurate several requirements must be fulfilled:

- The simulation must be correct.

- The simulator must also consider the behaviour of hardware components interacting with the processor, including peripheral devices.

- The simulator must take into account the timing of each instruction. This is necessary so that interrupts caused by external agents and timer ticks can be processed at precisely the right moments.

- The software being simulated requires real-time execution.

In the cache profiler, the program reads trace input from stdin. Each line of the trace file contains one record with following format:

[Timestamp][Memory][Type of access][Memory Address]

Exemplified as follows

```

8787 ZM R 011A

8787 YM R 6FF5

8787 XM W 9FF5

```

Where Z refers to the program memory, X and Y to the data memory, R for read access and W for write access. The address is a hexadecimal byte-address between 0 and FFFF. It is important to notice that the DSP processor can issue references to the three memories in the same cycle.

### 2.2 The stand-alone profiler

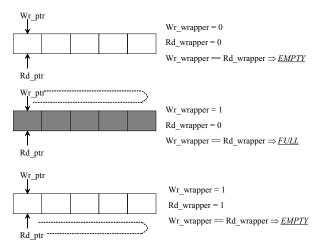

The profiler reads the new request arrivals from the trace file. When the request arrives in the profiler it checks the contents of the cache to see whether the corresponding content is present. If yes, the cache is left unchanged, otherwise the reference of the file corresponding to the request is fetched into the cache, which corresponds to a hit miss. If needed some data or instruction lines are removed from the cache according to a predefined removal policy. The simulator behaves in such a way that the output numbers realistically represent the cache events.

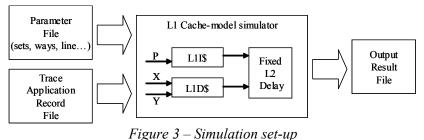

*Figure 3* illustrates the simulation set-up. Simulation results are determined by the input trace and the cache parameters, which are the input of the simulator in the format of a trace file and parameter file that specifies the cache configuration

0

The L1 cache parameters are set with a parameter file, which specifies:

- One or more application traces.

- Output result file

- Cache prefetch

- Number of ways

- Number of sets

- Line size

- Way locking

Through the command line it is possible to setup simulation alternatives. It is possible to explore the cache memory model by defining the data cache shared or separated for X and Y data; set the cache line replacement algorithm for three possible options; specify if the profiler uses one or more trace files, which means that a task-switching scenario is simulated. The profiler can produce extensive debug information. For each address related with a cache event can be associated a label. For example, a label that indicates if it is a read or write miss, the way, the set allocated, etc.

### 2.3 Cache model in the stand-alone profiler

The profiler models the behaviour of the cache.

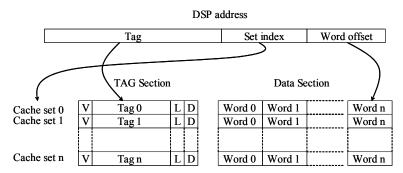

#### 2.3.1 Block placement, replacement and identification.

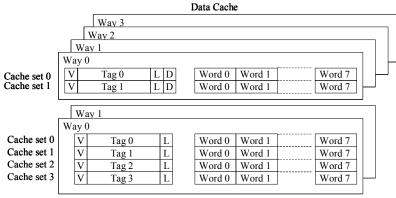

The data block is placed in the cache according to (*block address*) MOD (*Number of sets in the cache*). The cache has a tag address on each cache line that gives the block address. The tag of every cache line that might contain the desired information is checked to see if it matches the block address from the DSP. Also verified are some special bits. There is a way to know that the cache line does not contain valid information, the use of a *valid bit* (V) indicates if the entry contains valid data. In addition, the line also has a *lock bit* (L), which indicates whether a cache line is locked or unlocked, and in the case of the data cache a *dirty bit* (D), which indicates whether the data in the cache differs from its associated contents in the L2 memory. The number of bits for each field is dependent on the size of the cache. For example, a cache with 128 sets and with a line size of 8 words has 7 bits ( $2^7 = 128$ ) in the set index field and 3 bits ( $2^3 = 8$ ) for the offset field. The remaining ones are used for the tag in the tag field. *Figure 4* illustrates the cache set allocation.

Figure 4 – Cache allocation according to the DSP address

A line replacement algorithm has to be implemented in order to allocate a new cache line if n>1 (i.e. cache is a n-way set associative). Three different cache line replacement algorithms can be set: first in fist out (FIFO), least recently used (LRU) and pseudo least recently use (PLRU). In FIFO the oldest cache line is discarded, this method is easier to implement when compared with the other two. In LRU, accesses to lines are recorded and the line discarded is the one that has been least-recently used. This method relies in corollary of locality: if recently used blocks are likely to be used again, then a good candidate for disposal is the least recently used. It is the most difficult method to implement because it can be complicated to calculate the LRU. An easier method to implement is the PLRU because it is based in a binary decision tree. For example, if

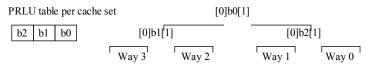

the data cache is four way-set associative, each cache set contains 3-bit PLRU table. Each table entry stores PRLU data and is updated on each read and write access to the associated cache set. *Figure 5* illustrates the PLRU algorithm according to a 4-way set-associative cache.

Figure 5 – PLRU cache line replacement algorithm

On a cache hit the values for b0, b1, and b2 are updated in the PLRU table. If for instance a cache hit occurs in way 3, then b0 and b1 in the PLRU table are both reset. Therefore, a PLRU entry indicates the most recently used way. On a cache miss, the least recently used is allocated, in order to do so the information contained by a PLRU entry is inverted.

### 2.3.2 Memory Management Unit

The behaviour of the cache can be controlled by means of the Memory Management Unit (MMU). The cache MMU allows partitioning of the external L2 memory into segments and for each segment an individual set of attributes can be programmed. A segment is defined by its lower and upper segment address boundaries. The MMU is programmed by application code in order to set an individual set of attributes to the segments defined. The simulator models the integration of a memory management unit for both Icache and Dcache and the effect of this configuration setting can be reproduced. Inside the model the address as read from the application trace is compared to a predefined address range. If the address maps into a segment area, the corresponding segment behaviour is carried out according to the predefined attributes.

The following attributes are modelled and can be applied to MMU data memory mapped segments:

- Division in cached/non-cached memory areas

- Data write mode The data write mode determines which data write policy is applied to a cached segment. Data can be written according to a write-through or a write-back policy.

- Memory sharing Memory sharing determines whether an MMU mapped data memory segment is shared or non-shared memory space.

- Locking, flushing, invalidating cache lines and excluding and locking cache ways.

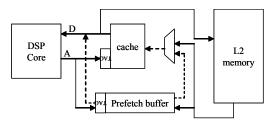

- Program and data hardware prefetching is the process of loading and temporary storing of the nearest next cache line from L2 memory into a prefetch buffer, in parallel with the data or program of the cache line currently being fetched from the cache (see *Figure 6*). The prefetch buffer stores only a single cache line. Only two prerequisites must be fulfilled to start a hardware prefetch: prefetching is enabled and a cache miss occurs

Figure 6 - Prefetching

#### 2.3.3 Write policies

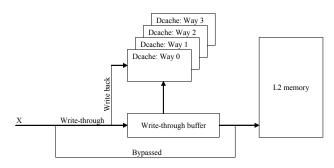

The writing behaviour to an MMU mapped data segment depends on the caching attributes that are applied to the segment. If the address does not match, the record is bypassed. If the address maps into the cached area, the corresponding write behaviour is carried out. *Figure 7* illustrates the functional model used in the simulator.

*Figure* 7 – *Write functional model*

The write-through buffer consists in a number of programmable entries (one to four), containing a whole cache set. The entry stores the cache address (the TAG and the index part of the logical address) and the corresponding cache line data. The write-through buffer entry is written when new write reference is issued by the DSP, all writes are buffered, regardless of whether they hit or miss in the Dcache. If the write-through buffer is full, the entry is first flushed and subsequently re-allocated to the new write reference. The use of the write-though buffer allows the processor to continue execution as soon as data is written to the buffer, thereby overlapping processor execution with memory updating.

In write-through mode, the Dcache is looked up for data reads and writes. Read misses cause a cache line replacement. Read hits cause the data to be read directly from Dcache and writes that hit update the Dcache. Since the data is simultaneously written to the write-through buffer, the Dirty bit will not be set. Write through is easier to implement than write back. The cache is always *clean* and the next level of memory has the most current copy of data.

In write-back mode, the Dcache is looked up for data reads and writes. Read and write misses cause a cache line replacement. Read hits cause the data to be read directly from Dcache. For writes that hit in the Dcache the dirty bit is set to '1' and the data is not written to the write-through buffer. A victimized cache line is written back to the main memory, only if it is dirty. The use of write back reduces the traffic to the memory traffic.

### 2.4 Cache performance issues

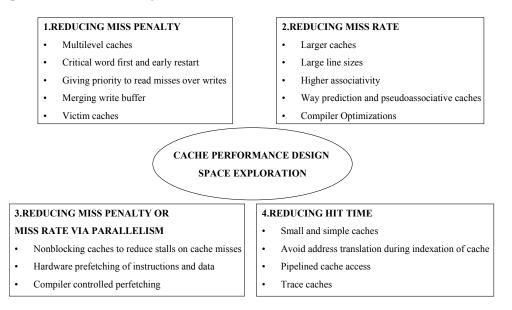

According to [2], the techniques used to improve the cache performance are categorized in four groups: reducing cache miss rate, reducing cache miss penalty, reducing cache penalty or miss rate via parallelism and reducing cache hit time.

Figure 8 – Cache performance design space exploration

*Figure 8* shows 17 possible measures divided in 4 sub-sets. Some of these techniques are addressed in the next with a brief explanation and possible trade-offs.

One method to evaluate cache performance is through the miss rate, which is simply the fraction of cache accesses that result in a miss. Reducing the miss rate is a classical approach for improving the cache performance but it is obvious that the miss rate is not the only component that should be considered. The time that it takes to fetch data from L2 memory upon a miss (i.e. the miss penalty) is just equally important as the miss rate. The hit time or the time that is necessary to access the cache is important because this time can limit the clock cycle rate.

As mentioned in Chapter one, the system being studied has three processing blocks sharing the access to the L2 memory. The miss penalty is dependent on the conflicts on the memory ports of the L2 memory, which relies on misses of other caches. There is no knowledge about the miss rate of other parties and hence, it is assumed an average time for L2 access. The focus is on the L1 miss rate, which is easier to evaluate in this context. The hit time requires a lot of knowledge about the physical implementation, which is out of the scope of this thesis.

The profiler is an open environment, which means that it can be modified. The profiler is an abstract model of the L1 cache that can be modified to incorporate many of the techniques shown above. A trade-off between design time, simulation time, scope and goals of the study confines this work.

The focus of the cache performance is on the miss rate and hence, the techniques that are modelled in the profiler are related with the improvement of the miss rate figure. But not all the techniques to improve the miss rate are considered in the model, either because there was not enough time to be incorporated (e.g. way prediction) or simply because they are not possible to model (e.g. compiler optimizations). Various techniques shown in *Figure 8* are modelled in the profiler and they are explained in the next section.

In [2] a summary table shows the impact on the cache performance and the implementation complexity for each technique. Table 1 shows an illustration of some of the performance trade-offs to consider: +, - and 0 means that the technique improves, hurts and has no meaning in the factor, respectively. The complexity is ranked from 0 to 3, easiest to the hardest, respectively.

| Technique                                              | Miss penalty | Miss rate | Hit time | Hardware complexity                 |

|--------------------------------------------------------|--------------|-----------|----------|-------------------------------------|

| Multilevel caches                                      | +            |           |          | 2                                   |

| Critical word first and early restart                  | +            |           |          | 2                                   |

| Giving priority to read misses<br>over writes          | +            |           |          | 1                                   |

| Merging write buffer                                   | +            |           |          | 1                                   |

| Victim caches                                          | +            | +         |          | 2                                   |

| Larger block size                                      | -            | +         |          | 0                                   |

| Large cache size                                       |              | +         | -        | 1                                   |

| Higher associativity                                   |              | +         | -        | 1                                   |

| Way-predicting caches                                  |              | +         |          | 2                                   |

| Pseudoassociative                                      |              | +         |          | 2                                   |

| Compiler techniques to reduce cache misses             |              | +         |          | 0                                   |

| Nonblocking caches                                     | +            |           |          | 3                                   |

| Hardware prefetching of instructions and data          | +            | +         |          | 2 for<br>instructions<br>3 for data |

| Compiler-controlled prefetching                        | +            | +         |          | 3                                   |

| Small and simple cases                                 |              | -         | +        | 0                                   |

| Avoiding address translation during index of the cache |              |           | +        | 2                                   |

| Pipelined cache access                                 |              |           | +        | 1                                   |

| Trace cache                                            |              |           | +        | 3                                   |

Table 1 – Summary of cache optimization techniques

### 2.4.1 Techniques modelled in the profiler

The techniques shown in *Figure 8* that are modelled in the profiler are:

- Reducing miss rate (Larger caches, larger line sizes, higher associativity).

- Reducing miss penalty (write-through buffer).

• Reducing miss penalty or miss rate via parallelism (hardware prefetching of data and program).

The model that is presented in [2] states that there are three causes for cache misses:

- Compulsory misses The first access to a cache line is always a miss, so the line must be brought into the cache. These are also called cold-start misses.

- Capacity misses if the cache cannot contain all the lines needed during the execution of a program, capacity misses occur because of blocks being discarded and later retrieved.

- Conflict misses Also called collision misses of interference misses. Will occur because of a cache line maybe be discarded and later retrieved if too many blocks map to the same set. Occur when too many lines map to the same set.

The most obvious way to reduce the cache miss rate is by increasing the size of the cache. This will reduce the capacity misses but incurs in a higher cost because the area of the memory is larger. Larger line sizes will reduce compulsory misses because it takes advantage of the principle of spatial locality (i.e. there is high probability that other word in the same line will be needed soon). The trade-off is that increases the miss penalty because larger blocks take more time to be fetched from L2 memory. At the same time, larger lines can increase conflict misses and even capacity misses if the cache is small. There is no benefit in reducing the miss rate if increases the penalty for accessing an L2 memory. Via higher associativity follows the two rules of thumb. The first states that an eight-way set associative cache is for practical purposes as effective in reducing miss rates as a fully associative cache. The second called 2:1 cache rule of thumb states that a direct-mapped cache size N has about the same miss rate as two-way set associative cache of size N/2. Higher associativity comes with the cost of higher hit time, which is the price for using more hardware.

When a cache is in write through mode, a write buffer is needed to reduce the miss penalty, which allows the processor to continue as soon as the data is written to the buffer, thereby overlapping processor execution with memory updating. The cache line present in the write buffer will be flushed when replaced by other line.

Hardware prefetching of instructions and data uses the prefetch of items before the processor requests them. The processor fetches two lines on a miss; the requested line and the next consecutive line. The requested line is placed in the cache and the prefetched line is placed in the prefetch buffer. The prefetch occurs when a cache miss occurs, first it is checked whether the requested cache line is already kept in the prefetch buffer. If so, it will be moved to the chosen victim in the cache. Then, the TAG file is updated. If the requested cache line not kept in the prefetch buffer, it will be loaded and written from the L2 memory into the chosen victim in cache. The potential success of prefetching is either lower miss penalty, or if it is started far in advance of needed, reduction of miss rate. This ambiguity makes this technique be considered in a separate section.

### 2.4.2 Techniques not modelled in the profiler

The techniques not contemplated are explained briefly and based on the descriptions given in [2].

- Critical word first the missed word is requested from the memory first and it is sent to the processor as soon as it arrives, allowing the processor to continue execution.

- Early restart fetches the words in normal order but as soon as the requested word from the block arrives, sends it to the processor in order to continue execution. These last two techniques only benefit designs with large blocks. Given spatial locality, there is more than random chance that the next miss is to the rest of the block.

- Merging write buffer this technique involves the write buffer and improves the buffer efficiency. With *write merging*, the writes correspondent to different lines are merged in one entry. This optimization reduces stalls because the buffer does not fill so quickly and hence, it is not flushed so often.

- Victim caches this buffer holds *victim* lines that are discarded from the cache because of a miss. On a miss the victim cache is verified to see if it contains the desired data. This measure is usually more effective with small and direct mapped caches.

- Way prediction extra bits are kept in the cache to predict the way within the set of the next cache access.

- Compiler optimizations This measure does not imply hardware changes. This technique uses the principle that software can be rearranged without affecting correctness. Techniques like loop interchange, where exchanging the nesting of loops can make the code access the data in the order that is stored. In this case more sequentially is obtained and hence, spatial locality is explored. Another example is blocking, where temporal locality is explored. This technique is used in dealing with arrays; the blocks within the array are formed in order to maximize the access the data present in the cache.

- Non-blocking caches are used to reduce stalls on misses allows the data cache to continue to supply cache hits during a miss. The miss penalty is reduced but it requires out-of-order execution CPU.

- Pseudo associative caches where accesses proceed just as in the direct-mapped cache for a hit. On a miss, however, before going to the next lower level of memory hierarchy, a second cache entry is checked to see if it matches there.

- Compiler-controlled prefetch the compiler inserts prefetch instructions to request data before they are needed.

- Small and simple caches One of the time consuming tasks on a cache access is to compare the index portion of the address and compare it with the address. Smaller and simple caches help the hit time.

- Pipelined cache access pipeline cache accesses so that the effective latency of a firstlevel cache hit can be multiple clock cycles, giving fast cycle time and slow hits.

- Trace caches A trace cache finds a dynamic sequence of instructions including taken branches to load into a cache block.

### 2.5 Cache model assumptions

Assumption 2.1 – Stalls of program and data cache are added unconditionally

The stalls of program and data cache are added unconditionally, but in reality some of the miss events can overlap. The model does not take into account that a stall from program and data cache can happen at the same time, and have overlap in time. In this specific sense, the profiler gives worst-case scenario because the numbers of stalls caused by program and data cache misses are summed.

#### Assumption 2.2 – Not all the stall events are taken into consideration

Stalls caused by the use of the write buffer are not modelled. The addresses with the same tag/set value are allocated to the buffer. A write reference cannot be stored in the buffer if the write's tag/set value does not match. Then the buffer has is flushed. At this moment the data is moved to the L2 memory, this is not counted as a stall-giving event. This can increase the stall figure.

A write queue can be placed in front of the write through buffer that allows scheduling of the flushing process with other L2 memory accesses, this it is not modelled in the profiler. This would prevent the stalling of the core because the writes could be stored in the queue while the write-through buffer is still busy with flushing or waiting for L2 access. This can improve the utilization of the L2 bandwidth.

In addition, the use of a write-queue buffer could signify that a data write miss or a data write back does not always have to give a stall. In this case a write is first stored in a write-queue before it finds place in the cache, and a write-back (=a victimized line which is dirty) is first stored in a victim buffer, which is moved to the memory in conjunction with the read buffer. These are all separate processes managed by a cache controller, which only stall the core when there is a conflict. Especially the execution of write backs can be done in background so the core will not be stalled.

The write-backs could be delayed as outstanding writes to L2 memory, which can take place in the background of the replacement progress in some cases. In that case, no stalls will be introduced. In the profiler, the write-backs are added to the miss rate equation.

Assumption 2.3 – The average number of stall cycles is 3.5

The number of stall cycles in case of a cache line refill depends on the synchronization between the L1 and L2 domain, it can be 3 or 4 cycles depending if it is an odd or even cycle.

### 2.6 Cache Metrics

The simulator outputs the number of misses: Prm (program read misses); Drm (data read misses); Dwm (write misses) and Dwb (data write backs). The results are used to compute the miss rates in the following way:

Data miss rate:

$$Dmissrate = \frac{Drm + Dwm}{\# cpu \, cycles} *100$$

(2.1)

Data write back rate:

$$Dbackrate = \frac{Dwb}{\#cpu cycles} *100$$

(2.2)

Program miss rate:

$$Pmissrate = \frac{Drm}{\#cpu \, cycles} *100$$

(2.3)

Processor miss rate:

$$DSPmissrate = \frac{Drm + Dwm + Dwb + \Pr m}{\# cpu cycles} *100$$

(2.4)

Stall percentage:

$$Stall = \frac{(Drm + Dwm + Dwb + \Pr m) * L2\$latency}{\# cpu cycles} *100$$

(2.5)

### 2.7 Simulation Example

The following example is used to study the model accuracy. Two small trace files identified as task1 and task2 are used, the task switch occurs every five CPU cycles. The caches are of 64 words size (64 x 16 bits) with the configuration seen bellow in *Figure 9*. The Dcache is working in write back mode is a dual ported with shared X and Y data. The cache line replacement algorithm being used is the PLRU.

Instruction Cache

Figure 9 – Icache and Dcache configuration of the example

*Figure 10* shows the predicted behaviour for a simulation using the example traces. The profiler is set-up to use a dual ported unified XY cache and the output results for X and Y memory will be summed and denoted with X reference.

| task1        | event | way         | set  | word | stall cycles |

|--------------|-------|-------------|------|------|--------------|

| 1 ZM R 9000  | miss  | 0           | 0    | 0    | 3.5          |

| 1 XM R A000  | miss  | 0           | 0    | 0    | 3.5          |

| 1 YM R C000  | miss  | 2           | 0    | 0    | 3.5          |

| 2 ZM R 9001  | hit   | 0           | 0    | 1    |              |

| 2 XM R A0D0  | miss  | 1           | 0    | 0    | 3.5          |

| 2 YM R C0D0  | miss  | 3           | 0    | 0    | 3.5          |

| 3 ZM R 9002  | hit   | 0           | 0    | 2    |              |

| 4 ZM R 9003  | hit   | 0           | 0    | 3    |              |

| 4 XM W A003  | hit   | 0           | 0    | 3    |              |

| 5 ZM R 9004  | hit   | 0           | 0    | 4    |              |

| 5 XM W A0D5  | hit   | 1           | 0    | 5    |              |

| 6 ZM R 9005  | hit   | 0           | 0    | 5    |              |

|              | SH    | vitch to ta | sk 2 |      |              |

| 6 YM W C006  | miss  | 0           | 0    | 6    | 3.5          |

| 7 ZM R 9006  | miss  | 0           | 0    | 6    | 3.5          |

| 7 YM W C0D5  | miss  | 3           | 0    | 5    | 3.5          |

| 8 ZM R 9007  | hit   | 0           | 0    | 7    |              |

| 8 YM W CCCC  | miss  | 0           | 1    | 4    | 3.5          |

| 9 ZM R 9008  | miss  | 0           | 1    | 0    | 3.5          |

| 9 XM R AAAA  | miss  | 2           | 1    | 2    | 3.5          |

| 10 ZM R 9009 | hit   | 0           | 1    | 1    |              |

| 11 ZM R 900A | hit   | 0           | 1    | 2    |              |

|              | SH    | vitch to ta | sk 2 |      |              |

| task2        | event      | way     | set | word | stall cycles |

|--------------|------------|---------|-----|------|--------------|

| 1 ZM R EE00  | miss       | 1       | 0   | 0    | 3.5          |

| 1 XM R AA00  | miss       | 2       | 0   | 0    | 3.5          |

| 1 YM R BB00  | miss/wback | 0       | 0   | 0    | 7            |

| 2 ZM R EE01  | hit        | 1       | 0   | 1    |              |

| 2 XM R CC00  | miss       | 3       | 0   | 0    | 3.5          |

| 2 YM R DD00  | miss/wback | 1       | 0   | 0    | 7            |

| 3 ZM R EE02  | hit        | 1       | 0   | 2    |              |

| 4 ZM R EE03  | hit        | 1       | 0   | 3    |              |

| 4 XM W AA03  | hit        | 2       | 0   | 3    |              |

| 5 ZM R EE04  | hit        | 1       | 0   | 4    |              |

|              | switch     | to task | 1   |      |              |

| 5 XM W CC05  | miss       | 1       | 0   | 5    | 3.5          |

| 6 ZM R EE05  | miss       | 1       | 0   | 5    | 3.5          |

| 7 YM W BB06  | miss/wback | 2       | 0   | 6    | 7            |

| 8 ZM R EE06  | hit        | 1       | 0   | 6    |              |

| 8 YM W DD05  | miss/wback | 0       | 0   | 5    | 7            |

| 9 ZM R EE07  | hit        | 1       | 0   | 7    |              |

| 9 YM W CACA  | miss       | 1       | 1   | 2    | 3.5          |

| 10 ZM R EE08 | miss       | 1       | 1   | 0    | 3.5          |

| 10 XM R ACAC | miss       | 3       | 1   | 4    | 3.5          |

| 11 ZM R EE09 | hit        | 1       | 1   | 1    |              |

Figure 10 - Cache simulation example

*Figure 11* shows the expected events of the cache and has the following numbers: Prm = 6, Drm = 10, Dwm = 7, Dwb = 4. The output of the simulator validates the results as it is shown bellow.

RESULTS OF CACHE RUN .... RESULTS OF MEMORY X

number of X reads = 10 number of X writes = 10 number of X read misses = 10 number of X write misses = 7 number of X write backs = 4 ... RESULTS OF MEMORY Z ... number of Z reads = 21 number of Z read misses = 6

*Figure 11 – Output results of the cache simulator*

### 2.8. References of Chapter 2

- [1] K. Flanagan, B. Nelson, J. Archibald, and G. Thompson, *The inaccuracy of trace-driven simulation using incomplete multiprogramming trace data*, In IEEE International Workshop on Modeling, Analysis and Simulation of Computer and Telecommunication Systems. IEEE, 1996.

- [2] John L. Hennessy and David A. Patterson. *Computer Architecture: A Quantitative Approach*. Morgan Kaufmann, 3rd edition, 2003.

[3] Gurindar S. Sohi and Manoj Franklin, *High-bandwidth data memory systems for superscalar processors*, In Proc. of 4th Int. Conf. on Arch. Support for Prog. Lang. and Operating Systems, pages 53--62. ACM, 1991.

# Chapter 3 Level 1 Cache profiling

This chapter describes the process of L1 cache profiling using trace-drive simulation. L1 cache profiling has three major goals. First, assess the cache architecture in order to derive a reference configuration that can provide the basis for further performance improvement. Second, derive performance figures for the cache. Third, perform an analysis at a cycle level. This means evaluation of the cache performance as function of execution time.

The starting point of the L1 cache profiling was that there was little knowledge about the application. The applications were developed without taking in consideration the presence of the cache and hence, so are the traces used in this work. The MST-BB Philips department in Nuremberg provided the traces. The manuals and helpful information provided by Nuremberg proved to be important in this study.

While the idea of trace-driven simulation is simple, it is time consuming since the simulation time is proportional to the length of the trace. For real applications, the traces can easily exceed millions of references. The time spent in simulating and the correctness of the evaluation are essential factors. Trace-driven profiling can easily lead to wrong assumptions, results and conclusions. The profiling process is highly application dependent, which means that knowledge about the application is essential. There are several and very important factors to consider when doing the profiling investigation. Among the key aspects are drawing assumptions regarding the applications, defining how to explore the architecture, evaluation of the accuracy of the trace, assessing the results and evaluate what are the sources of uncertainty in case they exist. These issues are developed in this chapter.

The chapter is organized as follows. Section 3.1 presents a study case based in the MP3 decoder and AAC decoder application traces. The following sections describe the knowledge acquired in the study case. Section 3.2 addresses the application and trace analysis. Section 3.3 describes the approach taken in order to explore the cache architecture. Section 3.4 explains briefly the iterative process between the profiling process and the development of the model. Section 3.6 reflects on what to consider when addressing the cache behaviour. Finally conclusions of the study are derived.

### 3.1 Case study

Two audio application trace files are used in the profiler simulations: the MP3 decoder [1] and the Advanced Audio Coding (AAC) decoder [2]. The MST-BB Philips department in Nuremberg provided the traces. The implementation of the algorithms is out of the scope of this thesis. The overview description of the algorithm presented in this section is based on the user manuals also provided by Nuremberg. The study addresses the goals referred above and describes the process of profiling.

### 3.1.1 MP3 and AAC decoder application and trace analysis

In the MP3 Decoder three main functions are defined, which are called by the DSP main program: MP3\_Init, MP3\_Synchronize and Mp3\_Process (granule based processing). The

function MP3\_Init initialises all static variables of the MP3 decoder and it is only called once at the very beginning of MP3 decoding phase. The initial synchronization is done by function MP3\_Synchronize. This function is called repeatedly until synchronization is achieved or the end of the bit stream is reached. After successful synchronization, the function Mp3\_Process performs header and side information decoding as well as data processing until the end of the bit stream is reached or an error condition occurs. Mp3\_Process performs a granule (sub-frame) based processing and generates per call and per stereo channel 576 output samples (1152 words of 16 bits). The MP3 decoder required memory resources (in 16 bit words) are shown in *Table 2*.

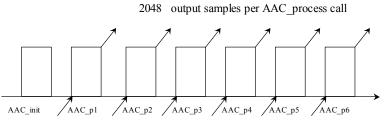

In the AAC Decoder two main functions are defined, which are called by the DSP main program: AAC\_Init and AAC\_Process. AAC\_Init is called once before playing a new AAC file. It may already decode a header found in the input buffer and request more data before calling AAC\_Process. The AAC\_Process procedure decodes one block of data and produces 1024 stereo output samples (2048 words of 16 bits). The required memory resources (in 16 bit words) for the AAC decoder application are shown in table *Table 3*.

The Data types of the applications are defined, according to [3] the data types present in the traces are:

Input/Output – This part of RAM is used for storage of input/output parameters and streaming data of the application.

Static RAM – This part of the RAM remains unchanged between successive procedure calls. Different procedures inside a package (e.g. speech encoder or speech decoder) may use different static RAM sections.

Scratch Data RAM – This part of the RAM is commonly by the subroutines used of all applications and stores intermediate results. No data is kept between successive calls. Scratch data is located in two different RAM banks, called SCRATCH\_A and SCRATCH\_B.

Data ROM – The ROM area is used to store constant values or tables.

Program ROM – The ROM area is used to store program.

Stack – in respect to an object allocated on the stack in connection with a subroutine call.

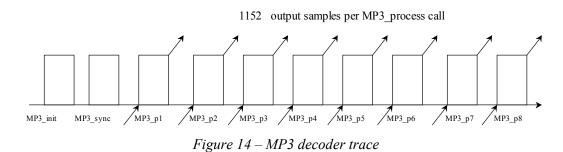

It is possible to track the procedure calls present in the traces by knowing the program address of those calls. This address search is performed in the trace file. This gives a more clear idea about what is present in the trace: what are the functions executed in the trace, how many times they are executed and their duration. The analysis reveals that the MP3 decoder trace contains one call to the initialisation procedure, one to the synchronization procedure and eight calls to the process procedure as shown in *Figure 12*.

Figure 12 – MP3 decoder flow diagram

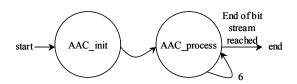

The AAC trace contains one call to the initialisation procedure and six calls to the process procedure, as illustrated in *Figure 13*.

Figure 13 – AAC decoder flow diagram

The memory references present in the traces give some insight about how the algorithms were developed. Using a small program to count the number of reference locations present in the traces, the number for each memory is obtained, the results are shown in *Table 4*. "ZM R" is the number of program reads, which is a number equivalent to the number of DSP clock cycles. The table shows that there is a levelled number between X and Y references which can lead to the conclusion that the algorithm does not explicitly divide X and Y data as in many DSP applications where for example Y data is used for filter coefficients. The same program is used to count the number of different memory references in the traces, *Table 5* confirms the situation. This may be proven to be a decisive factor in the data cache memory model to use and can lead to decisions of using a XY shared data cache model or a separated X and Y model.

An analysis in the trace files reveals the number of samples that are consumed and produced by the algorithms. The MP3 decoder application reads a different number of input data samples in each call of the MP3\_Process procedure, as shown in the *Figure 14* below.

For the AAC trace,

*Figure 15 - AAC decoder trace*

An inspection of the memory events in the input and output buffer data address range show that:

- The cache lines correspondent to the input data samples are not invalidated before a new block is processed (i.e. before a new process routine execution). The analysis shows that the same data is from the input buffer segment read. The profiler includes invalidation and it is unpractical to solve use it because the number input samples read by the MP3 decoder differs from process call to process call. This number must be estimated because new input samples causes cache misses.

- The output data segment is used for intermediate storage of computation results and it is difficult to know at what point in time the output data block is produced just by looking at the trace. The cache lines corresponding to the output samples are not flushed when the data output block processing is produced. The cache lines corresponding to the output data must be updated in the memory once a frame is produced in the end of each call and the data correspondent to the cache lines must be invalidated. Knowing the expected number of output samples (1152 for MP3 and 2048 for AAC), an estimation of the number of cache lines to be flush can be obtained.

For the input stream, the miss rate is for a worst-case situation estimated.

For the MP3 decoder, 977 new data input samples is the worst-case situation, per routine call.

| 977 / 8 = 122.125        | // 8 words is the size of a cache line size assumption   |

|--------------------------|----------------------------------------------------------|

| 122.125 * 8 = 977 misses | // 8 is the number of frames produced in the trace       |

| 977 / 655734 = 0.15%     | // 655734 is the number of DSP clock cycles in the trace |

The estimation of the number of cache line flushes considering a number of 1152 output samples is: 1152 / 8 = 144 cache line flushes.

For the AAC decoder, 1024 new data input samples is the worst-case situation, per routine call.

1024 / 8 = 128// 8 words is the size of a cache line size assumption128 \* 6 = 768 misses// 6 is the number of frames produced in the trace768 / 1711445 = 0.045 %// 1711445 is the number of DSP clock cycles in the trace

The estimation of number of cache line flushed considers 2048 output samples. 2048 / 8 = 512 cache line flushes.

The trace does not consider the invalidation and the flushing of the input/output data samples and hence, the program does not consider the interaction with the cache. The conclusion derived from the estimations is that the I/O data stream may not introduce a big uncertainty in the miss rate and in the stall percentage. The estimation must be used to correct the performance miss rate figure result.

For real-time execution, there is the assumption that a periodic source produces (i.e. transfers to the input buffer) samples, and a periodic sink and consumes samples (i.e., reads from the input buffer), respectively. This can have impact in the cache behaviour and is an uncertainty in the analysis. For example, interrupts coming from an external source that produces (e.g. A/D converter) or consumes (e.g D/A converter) must be considered in the real-time execution because data must be supplied and consumed. No interrupt code is present in the trace, the unpredictability of an interrupt could have consequences that are not easy to estimate because it not possible to predict when the interrupt is going to occur, what happens and what is the impact in the cache performance.

The conclusion here is that the applications perform a block read and write operation to data already available in memory, and is not involved in data IO by interrupt.

From the analysis of the application traces, the following conclusions are stated:

Application trace 3.1: *there is no explicit X and Y data, i.e. the applications uses both with a similar weight.* This factor influences the memory model.

Application trace 3.2: the MP3 trace has duration of 655734 DSP clock cycles correspondent to 3.27 ms of CPU time (200 MHz). Each call to the main routine reads a varying number of samples and produces 1152 samples.

Application trace 3.3: the AAC trace has duration of 1171445 DSP clock cycles correspondent to 5.85 ms of CPU time (200 MHz). Each call to the main routine reads a 1024 input samples and produces 2048 samples.

Application trace 3.4: *the uncertainties related with the I/O stream can be estimated.* The estimation showed that the impact from I/O stream is not significant.

Application trace 3.5: *the trace does not contain interrupt code and does not consider the interaction with the cache.* The application was developed not taken into account the presence of the cache. The simulation assumes that the data is already available in memory.

#### 3.1.2 Cache architecture exploration

The first decision about the cache architecture respects the data memory model. Therefore, it is important to confront different cache memory models. For the study case the following cache models are confronted:

- XY shared cache memory space (double ported memory).

- Separated X data cache and Y data cache memory (one port memory).

*Table 6* shows the results of the simulations using the two models for fixed total sizes of 8Kw and 16Kw. The results show that a data cache model with a shared XY data has a lower miss rate when compared with a separated X and Y data cache model. The double-ported data memory model achieves better performance for several cases when the size is the same.

The conclusions from the results is that in case of separate X\$ and Y\$, a write to X can never be read by Y (and vice-versa) so it gives a miss. This can be done in shared XY, and the current applications exploit this feature, which was confirmed by the application trace analysis for the MP3 or AAC case and this is the reason for the higher miss rate. For the following simulations a share XY\$ data model is used.

Profiling supports the decision on parameters for the cache architecture. The three basic parameters of a cache are the size, the line size, and degree of associativity. In cache designs, the problem often resides in the choice of these three parameters. In order to derive the reference cache architecture some basic parameters are kept fixed and the focus is on these three parameters. It is not reasonable to analyze at this point every possible cache configuration and the focus is on the cache basic parameters. For the simulations, the cache line replacement algorithm is the PLRU and the MMU is programmed in order to set write-back policy for all memory range. In order to get data on the miss rate, a stand-alone trace profiler processes the traces over a wide

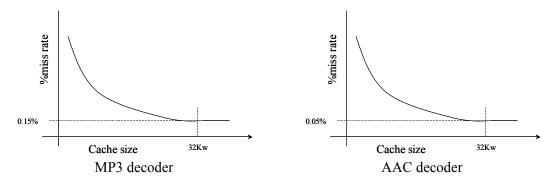

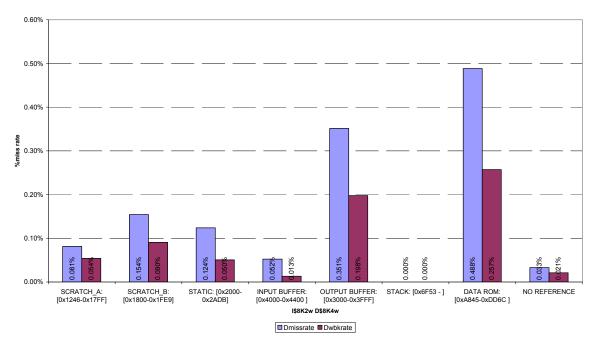

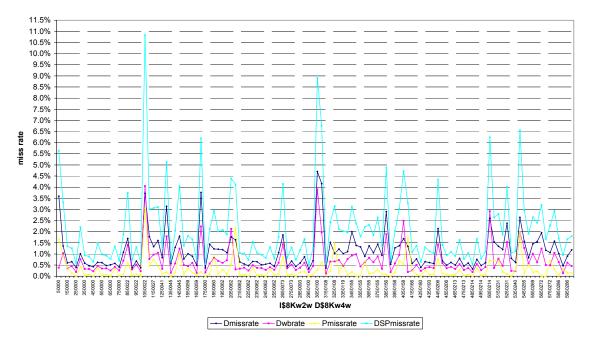

range of cache configurations. In order to simulate several cache configurations in a single run, a script file programmed in perl is used. The program and data cache have the same configuration for each data point. The results are shown in *Figure 51-56*.

The following observations can be derived from the *Figure 51 and 52*:

- The miss rate decreases with bigger the cache line. This is the result of less compulsory misses. We can conclude that there is locality applications

- Decreases with the bigger cache sizes. This is the result of less capacity misses.

- The increase of the cache associativity has a bigger impact with a cache size of 8 Kword (I\$=D\$). This is the result of less conflict misses.

- A direct-mapped cache size 8Kw has about the same miss rate as two-way set associative cache of size 4kw for cache line size of 2, 4 and 8w. For cache lines bigger than 8w, the miss rate of a direct-mapped cache size 8Kw is higher than a n-way set associative cache of size 4kw. This is the result of the increase in conflict misses.

- The flat line indicates that the application fits in the cache and hence. This is the result of compulsory misses.

From figures *Figure 53-6*

- The data cache contributes the most to the overall miss rate percentage (i.e. the data cache misses are dominant).

- The misses of program and data cache are added unconditionally, but in reality some of the miss events can overlap. The model in the profiler does not take into account that a stall from program and data cache can happen at the same time, and can overlap in time.

#### **3.1.3** Reference cache architecture

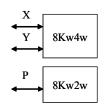

A working assumption for the cache architecture is chosen based on the profiling results and a physical implementation study, which is out of the scope of this thesis. This working assumption leads to an 8 Kw size 4 way-set associative for Dcache and 8 Kw size 2 way-set associative for Icache. The cache line size is 8 words ( $8 \times 16$  bits). The cache architecture is shown in *Figure 16*.

*Figure 16 – Reference cache architecture*

The conclusions for the basic cache architecture configuration:

Cache architecture 3.1: The model for the data cache is a shared X and Y data double ported memory.

Cache architecture 3.2: Instruction cache is a 8Kw size 2 way-set associative memory and the data cache is a 8Kw size 4 way-set associative double ported memory with shared X and Y data. The cache line size is 8 words.

#### 3.1.4 Algorithms dynamic behaviour

The performance impact of each procedure from both algorithms is verified. The simulation is done with the reference architecture. It is possible to track the procedure calls present in the traces by knowing the program address of the process calls. This address search is performed in the trace files. By knowing this, it is possible to know the duration of each process computation. By doing post-processing in the debug data produced by the profiler it is possible to filter the miss rate for each main procedure of the applications.

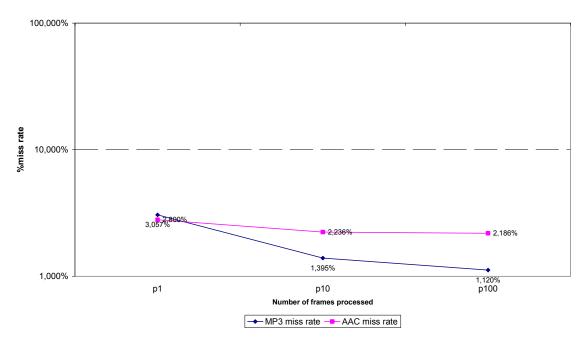

The results are shown in *Table 7-8 and Figure 57-58* and they show clearly that there is a peak in the miss rate at the start of the execution, which is the consequence of a cold start (i.e. compulsory misses). The cache is empty when the initialisation procedure is executed in and noticeable is the dynamic behaviour because there is a significant variation in each process execution, which visible by the fluctuation of the miss rate.

The worst-case execution time of an application is dependent on the input data and sources of dynamism present in the algorithm (e.g. condition statements, data-dependent iterations). The highest and lowest miss rate value per process computation of the applications is:

- MP3 decoder highest value 2.08%, minimum value 0.89%

- AAC decoder highest value 2.60%, minimum value 1.99%

One conclusion is that the worst-case execution time of a task can be estimated with the worstcase value of the miss rate assuming a fixed penalty.

#### 3.1.5 Impact of data types