| MASTER                                                                   |

|--------------------------------------------------------------------------|

| Analysis of automotive traffic shapers in ethernet in-vehicular networks |

|                                                                          |

| The agree with the C                                                     |

| Thangamuthu, S.                                                          |

| Award date: 2014                                                         |

|                                                                          |

| Link to publication                                                      |

|                                                                          |

|                                                                          |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

### Department of Mathematics and Computer Science System Architecture and Networking Group

# ANALYSIS OF AUTOMOTIVE TRAFFIC SHAPERS IN ETHERNET IN-VEHICULAR NETWORKS

Master Thesis

#### SIVAKUMAR THANGAMUTHU

Supervisors:

dr.ir. Pieter J. L. Cuijpers prof.dr. Johan J. Lukkien dr. Nicola Concer

Version 1.0

Eindhoven, August 29, 2015

## **Abstract**

Ethernet is expected to be adopted as the backbone for in-vehicle networks to unify different automotive domains under a single infrastructure. However, the QoS guarantees offered by Ethernet are not sufficient for time-critical control data traffic present in the automotive networks. IEEE 802.1 Time-Sensitive Networking Task Group is working on standardizing different mechanisms that are required to improve the QoS guarantees of Ethernet for automotive and industrial applications. Traffic shaping is one of the mechanisms to improve the end-to-end latency guarantees of Ethernet for the time-critical control data traffic. There are different proposals for a new Traffic Shaper in the IEEE802.1TSN standardization process. The problem is to verify whether these Traffic shapers actually meet the end-to-end latency requirement specified by IEEE802.1TSN and also to identify the best possible Traffic Shaper for automotive network requirements in terms of other performance metrics like configuration complexity and hardware impact. In this thesis work a simulation model is created for three different Traffic Shapers that are proposed in standardization process for shaping the control data traffic. Their performances in terms of end-to-end latency and jitter are compared and verified against the IEEE802.1TSN requirements. Simulation results show that it is possible to achieve the IEEE802.1TSN latency expectation of 100 µs over 5 hops for the control data traffic in all the three traffic shapers under different conditions. Based on the analysis for overall performance, the Burst Limiting shaper is recommended.

## Acknowledgement

I would like to express my sincere gratitude to my supervisor at NXP, Dr. Nicola Concer for his exemplary guidance and support throughout the thesis work. Without his insights and constant motivation this work would not be possible. Special thanks to my supervisor at the university, Dr. Pieter J. L. Cuijpers for his guidance and critical comments to bring out the best in me. I would like to extend my profound gratitude to Prof. Dr. Johan J. Lukkien for his valuable suggestions and his confidence in me to handle this thesis work.

Also, I would like to thank Dr. Bas Luttik and EIT ICT labs for introducing me to this project. Futhermore, I would like to thank NXP Semiconductors for giving me the opportunity to work on this project. Thanks to all the employees and fellow interns at NXP for providing me a friendly environment at work.

I am forever grateful to my parents and my uncle for their love and support, without which this endeavor would not be possible. Finally, my hearty thanks to all my friends for their encouragement, moral support and good times.

"தாமின் புறுவது உலகின் புறக்கண்டு காமுறுவர் கற்றறிந் தார்"

- திருவள்ளுவர்

#### Translation

"Their joy is joy of the entire world, they see; thus more the learners learn to love their cherished lore"

- Thiruvalluvar

#### Meaning

Good scholars will crave to learn more, when they see that while the learning gives joy to them, the entire world also derives joy from it.

## **Table of Contents**

| Abstract                                                    | 11   |

|-------------------------------------------------------------|------|

| Acknowledgement                                             | iii  |

| Abbreviations                                               | viii |

| 1. Introduction                                             | 1    |

| 1.1 Background                                              | 1    |

| 1.2 Context                                                 | 2    |

| 1.3 Basis for the Work                                      | 4    |

| 1.4 Problem Statement                                       | 5    |

| 1.5 Proposed Solution                                       | 6    |

| 1.6 Goals                                                   | 6    |

| 1.7 Methodology                                             | 7    |

| 1.8 Contributions                                           | 7    |

| 1.9 Thesis Structure                                        | 8    |

| 2. State of the Art and Related Work                        | 9    |

| 2.1 State of the Art                                        | 9    |

| 2.2 Related Work                                            | 10   |

| 3. Traffic Classification                                   | 12   |

| 3.1 Prioritization                                          | 12   |

| 3.2 Traffic Types and Priority mapping                      | 13   |

| 3.3 Traffic Specifications in IEEE802.1AVB and IEEE802.1TSN | 14   |

| 4. IEEE 802.1AVB standard                                   | 16   |

| 4.1 IEEE 802.1AS                                            | 17   |

| 4.2 IEEE 802.1Qat                                           | 17   |

| 4.3 IEEE 802.1Qav                                           | 18   |

| 4.3.1 Priority re-mapping                                   | 19   |

| 4.3.2 Transmission Selection Algorithms                     | 19   |

| 4.4 IEEE1722                                                | 21   |

| 5. Traffic Shaping Algorithms for Control Data Traffic      | 23   |

| 5.1 Burst Limiting Shaper                                   | 23   |

| 5.2 Time Aware Shaper                                       | 26   |

| 5.3 Peristaltic Shaper                                      | 27   |

| 6. Simulation Environment                                                            | 30 |

|--------------------------------------------------------------------------------------|----|

| 6.1 Overview of SystemC                                                              | 30 |

| 6.2 SystemC Components                                                               | 31 |

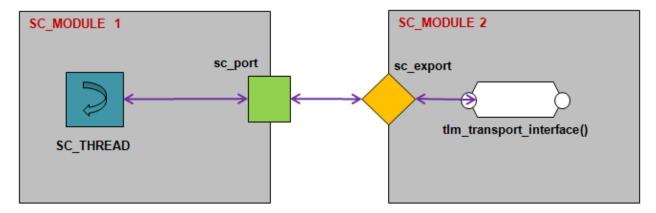

| 6.2.1 SystemC Module                                                                 | 31 |

| 6.2.2 Simulation Processes                                                           | 31 |

| 6.2.3 Port                                                                           | 32 |

| 6.2.4 Export                                                                         | 32 |

| 6.2.5 TLM Interfaces                                                                 | 32 |

| 6.3 Software Architecture                                                            | 33 |

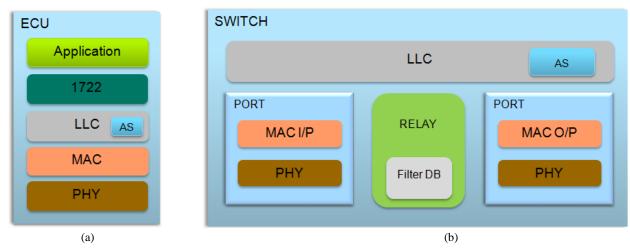

| 6.3.1 End Node (ECU)                                                                 | 33 |

| 6.3.2 Switch                                                                         | 33 |

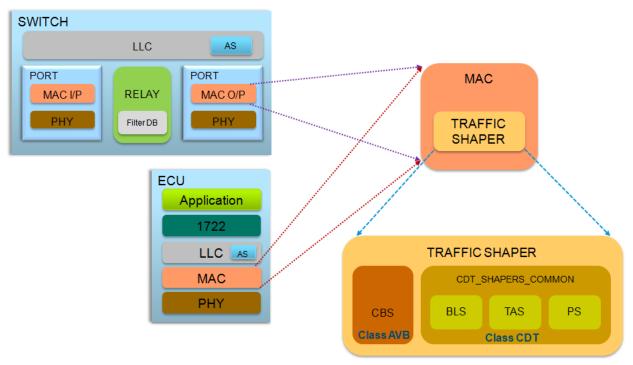

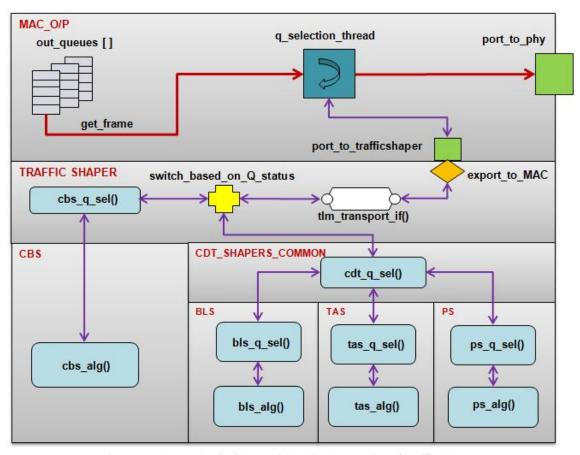

| 6.4 Traffic Shaper Modules                                                           | 34 |

| 6.5 Application Module and Traffic generation                                        | 36 |

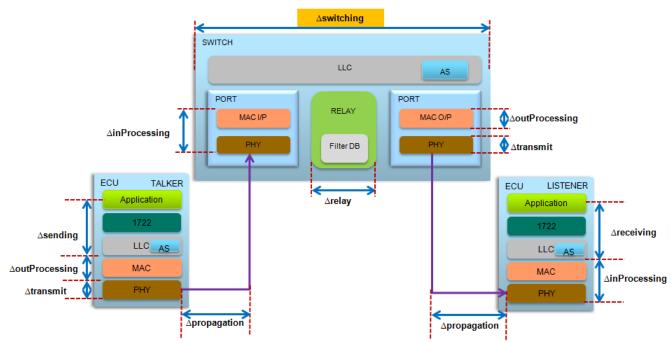

| 6.6 Time Abstraction Model and Delays                                                | 37 |

| 6.7 Assumptions and Restrictions of the simulation model                             | 40 |

| 6.7.1 Assumptions                                                                    | 40 |

| 6.7.2 Restrictions                                                                   | 40 |

| 7. Validation                                                                        | 41 |

| 7.1 Methodology                                                                      | 41 |

| 7.2 Worst Case behavior for end-to-end latency                                       | 41 |

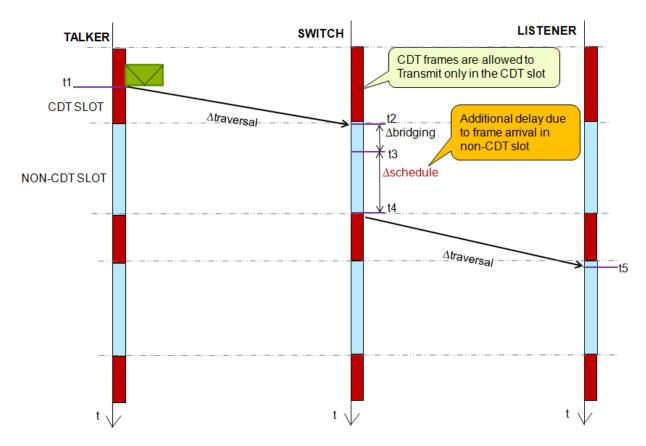

| 7.2.1 Worst case end-to-end latency in a Time Aware Shaper                           | 42 |

| 7.2.2 Worst case end-to-end latency in a Burst Limiting shaper                       | 43 |

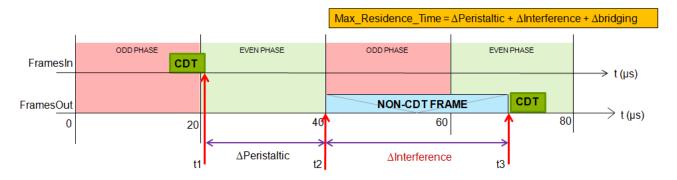

| 7.2.3 Worst case end-to-end latency in a Peristaltic shaper                          | 45 |

| 7.3 Network scenario for validation                                                  | 46 |

| 7.4 Theoretical maximum for end-to-end latency of CDT traffic and Simulation results | 48 |

| 7.4.1 Time Aware shaper                                                              | 48 |

| 7.4.2 Burst Limiting shaper                                                          | 50 |

| 7.4.3 Peristaltic shaper                                                             | 51 |

| 8. Improvements for End-to-End Latency                                               | 54 |

| 8.1 Adjustments in scheduling for Time Aware Shaper                                  | 54 |

| 8.1.1 Improvement results for Time Aware shaper                                      | 56 |

| 8.2 Guard band for Peristaltic Shaper                                                | 58 |

| 8.2.1 Results for Peristaltic shaper with guard band                                 | 59 |

| 9. Test Case                                              | 62 |

|-----------------------------------------------------------|----|

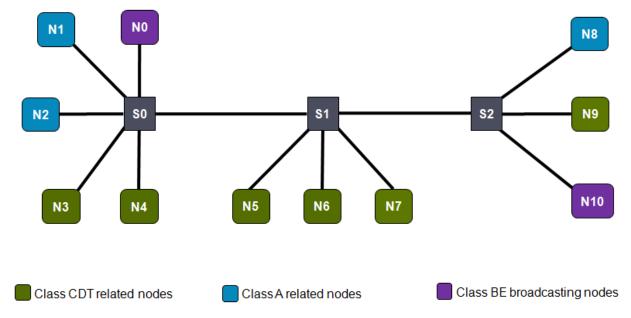

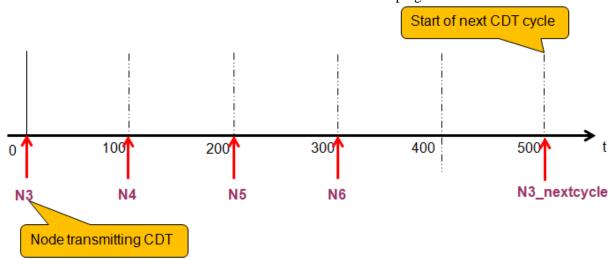

| 9.1 Network Scenario                                      | 62 |

| 9.2 Configurations.                                       | 63 |

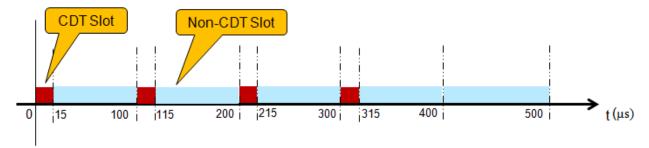

| 9.2.1 Time Aware Shaper                                   | 64 |

| 9.2.2 Burst Limiting shaper                               | 65 |

| 9.2.3 Peristaltic shaper                                  | 65 |

| 9.3 Worst case for CDT and Theoretical end-to-end latency | 65 |

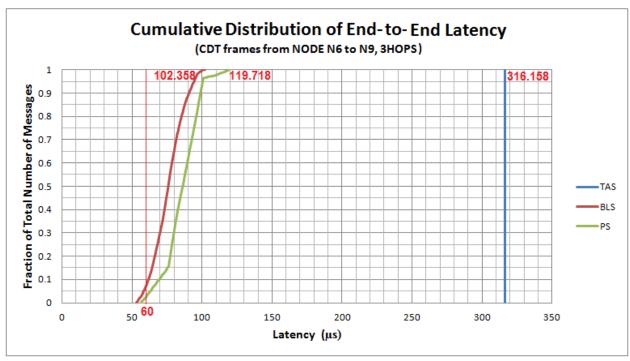

| 9.4 Results                                               | 65 |

| 10. Discussions and Recommendations                       | 69 |

| 10.1 Discussions                                          | 69 |

| 10.1.1 End-to-End Latency for CDT                         | 69 |

| 10.1.2 Maximum Jitter for CDT                             | 69 |

| 10.1.3 Effect of Frame Pre-emption                        | 69 |

| 10.1.4 Addition of New CDT Streams                        | 70 |

| 10.1.5 CDT Streams with Multiple Transmission Intervals   | 71 |

| 10.1.6 Bandwidth Utilization                              | 71 |

| 10.1.7 Impact on hardware                                 | 72 |

| 10.1.8 Overall Comparison                                 | 73 |

| 10.2 Recommendations                                      | 74 |

| 11. Conclusion                                            | 75 |

| 12. Future Work                                           | 76 |

| Bibliography                                              | 77 |

## **Abbreviations**

**ECU** Electronic Control Unit

LIN Local Interconnect Network

**CAN** Controller Area Network

MOST Media Oriented Systems Transport

**ADAS** Advanced Driver Assistance Systems

**IVN** In-Vehicle Network

**TDMA** Time Division Multiple Access

**CSMA** Carrier Sense Multiple Access

MAC Media Access Control

LLC Logical Link Control

**QoS** Quality of Service

**AVB** Audio Video Bridging

**TSN** Time Sensitive Networking

**CDT** Control Data Traffic

Mbps Mega bits per second

**Gbps** Giga bits per second

## 1. Introduction

#### 1.1 Background

Automobiles for human transport have undergone a tremendous evolution since the birth of the first internal combustion engine based car in 1886 [1]. The cars of the present day are becoming more intelligent with a multitude of complex electronic systems inside them. And the number of electronic control units (ECUs) inside a car is steadily increasing due to the performance, safety and comfort requirements. A top of the line modern car can have up to 70 ECUs [2]. This growth in the number of ECUs inside a car has given rise to different in-car networking technologies like LIN, CAN, FlexRay and MOST [3]. All of these networking technologies are optimized for specific use cases. For instance, CAN is a cost-effective relatively low speed bus network used to connect different ECUs. FlexRay with a maximum bandwidth of 10Mbits/s was designed for dependable real-time communication to connect time critical ECUs like the engine control unit. MOST was developed with a focus of transporting high quality audio data between entertainment ECUs inside the car.

The recent developments in the automotive safety systems like ADAS integrate ECUs, camera and radars providing features like Pre-Crash collision warning, Lane departure warning, Pedestrian warning etc.,. IMS Research predicts that by 2017, camera-aided driver assistance systems alone will number 34 million [4]. Additionally, there is a growing demand for in-vehicle multimedia systems with features like engine noise cancellation, engine noise mimicking, external device connectivity for rear-seat entertainment etc.,. A research study from ABI Research predicts that the global connected infotainment shipments will surpass 50 million units by 2017. Moreover, by 2025, every car will have Internet connectivity [4]. These trends and developments are pushing the bandwidth capabilities of the present day in-vehicle network (IVN) technologies to their limits. Besides this, the networking technology used has to be future proof, as it has to withstand, comply and facilitate the addition of other technological developments throughout the lifetime of a vehicle, for e.g. vehicle to vehicle communication, self-driving vehicles etc.,. This demands flexibility in network configuration and network management with minimal cabling complexity. Above all, these additions should not significantly increase the weight and the cost of the vehicle. So a new approach in IVN is necessary to transform the decentralized network islands with different networking protocols to a hierarchical structure. These constraints drive the automotive industry towards the need for a cheap, easy to manage, convergent backbone for the in-vehicle network.

On the other hand, Ethernet has evolved to become the dominant technology for computer networking and it has already entered the automotive domain via the On-Board Diagnostics (OBD) interface. Ethernet could be a possible technology for the future IVN because of its following advantages

- 1. It has grown into an extremely mature technology since its beginning in 1970s [5], with billions of interfaces sold in both consumer and industrial automation domains

- 2. It constitutes a cheap and highly supportive software stack spanning from super computers to small embedded systems with constant evolution from large industries worldwide to adapt to the evolving requirements

3. It is flexible as it is available in different data transmission rates such as 10/100/1000 Mbits/s and can be configured in different types of topologies, redundancy schemes and for different Quality of Service (QoS)

But the recent trigger point for considering Ethernet as a potential technology for the IVN came with the introduction of Broad-R-Reach technology by BroadCom [6] along with the increasing number of works to extend Ethernet's capabilities for real-time guarantees. Broad-R-Reach offers full-duplex switched Ethernet communication over an unshielded twisted pair cable. This provides Ethernet as a cost effective alternative for the backbone of next generation IVN. So, switched Ethernet-based communication is gaining significant importance in IVN. Table 1.0 introduces the different in-vehicle technologies including the possibilities of Ethernet and their typical applications inside the vehicle.

|                           | LIN                 | CAN                        | CAN FD                     | FlexRay                                   | MOST                                   | Ethernet                                                    |

|---------------------------|---------------------|----------------------------|----------------------------|-------------------------------------------|----------------------------------------|-------------------------------------------------------------|

| Standard<br>Release       | 2002                | 1986                       | 2012                       | 2000                                      | 2000                                   | 2011                                                        |

| Raw Data Rate             | 1-20Kbps            | Up to 1Mbps                | Up to 8/10Mbps             | Up to 10Mbps                              | 50 Mbps<br>150 Mbps                    | 100Mbps                                                     |

| Payload                   | Up to 8 B           | Up to 8 B                  | Up to 64 B                 | Up to 254 B                               | 60, 117 or<br>370 B                    | Up to 1500 B                                                |

| Physical<br>Media         | Single<br>Wire      | Unshielded<br>Twisted Pair | Unshielded<br>Twisted Pair | Unshielded Twisted<br>Pair                | UTP/Plastic<br>Optical Fiber           | Unshielded Twisted<br>Pair                                  |

| Topology                  | Bus                 | Bus                        | Bus/Passive Star           | Bus/Star/Mixed                            | Ring                                   | Star/Tree/Ring                                              |

| Automotive<br>Application | Sensors & actuators | 20.0 a 20a, a 20a,         |                            | Distributed control,<br>Backbone, Chassis | Multimedia                             | Diagnostics,<br>Backbone, ECU<br>programming,<br>Multimedia |

| Media Access              | Master-<br>Slave    | CSMA-CR                    | CSMA-CR                    | TDMA                                      | TDMA                                   | Buffered network                                            |

| Error<br>detection        | 8-bit CRC           | 15-bit CRC                 | 17/21-bit CRC              | 24-bit CRC                                | CRC                                    | 32-bit CRC                                                  |

| Redundancy                | NO                  | NO                         | NO                         | Built in: two separate channels           | Double ring,<br>redundancy<br>possible | No, possible via link replication                           |

| Deterministic<br>Behavior | NO                  | NO                         | NO                         | Built in                                  | Built in                               | Via AVB, TSN                                                |

Table 1.1 Different IVN Networking topologies

#### 1.2 Context

The automotive network consists of different types of data traffic which include time-sensitive control data traffic from sensors and between ECUs, real-time audio/video streams and internet traffic. Each traffic type requires a specific QoS. In the traditional IVN, these traffic types are organized in different network domains and handled by separate networks. The cross communication between different network domains happens through network gateways. In IVN with switched Ethernet, ECUs are connected via one or more Ethernet switches that create the backbone of the network and provide connectivity between any pair of ECUs. In addition to offering an increased data rate and bandwidth, the Ethernet IVN backbone

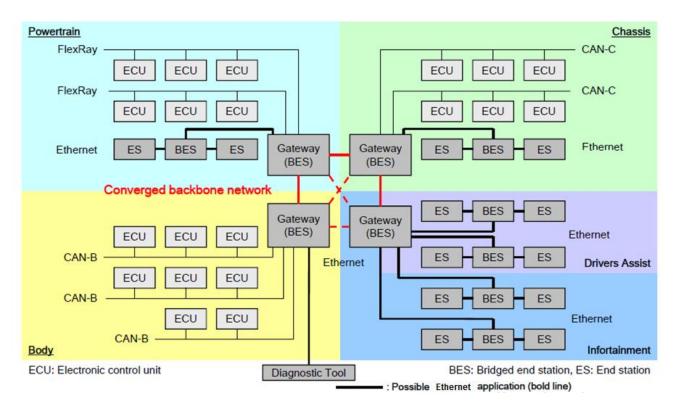

should integrate different automotive network domains. This includes the transportation of time-sensitive data traffic with certain guaranteed QoS in terms of communication latency, reliability and redundancy. Figure 1.1 shows the possibility of converged backbone in IVN.

Figure 1.1 Possible Converged backbone IVN

The traditional Ethernet protocol for computer networks is optimized only for "Best Effort Delivery" of a message [7]. This means that it does not provide any guarantee that data is delivered or that a guaranteed quality of service level is assured. "Best Effort" in many cases, works best for lightly loaded networks where the average delay is the primary metric or for cases where it is difficult to classify the data traffic based on their time sensitiveness. "Best Effort" is not sufficient in cases where the worst case delay is the important metric. In the context of IVN, "Best Effort Delivery" is not sufficient due to the following reasons

- 1. Automotive entertainment and safety systems deal with live audio and video data, which require a fixed end-to-end delay for quality reception

- Control messages from sensors to ECUs and between different ECUs in the automotive control domain have varied but even more stringent end-to-end delay requirements to respond in a timecritical manner

These requirements emphasize that the core aspect of IVN backbone is to deliver data within a certain time window under a specified maximum delay. So, to establish Ethernet as an IVN backbone and to accommodate the time-sensitive traffic from protocols like CAN, FlexRay and MOST in the in-vehicle networking domain, it becomes essential to extend the Ethernet to offer guaranteed QoS in terms of end-

to-end latency for time-sensitive data traffic. The specific requirements for automotive network are detailed in the Chapter 5.

#### 1.3 Basis for the Work

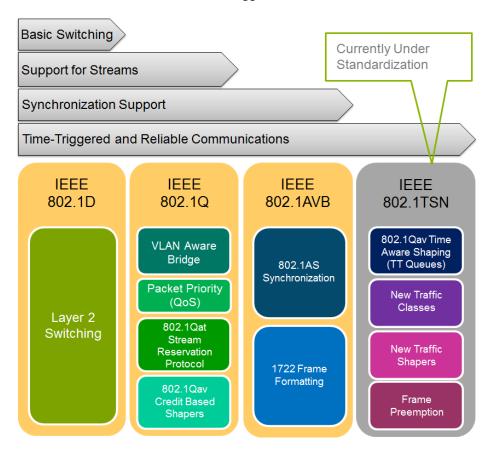

The capabilities of the switched Ethernet to accommodate real-time data traffic have been investigated extensively. Chapter 2 explains more on the approaches and different mechanisms to improve switched Ethernet to offer QoS guarantees for time-sensitive data traffic. In parallel to these works, the switched Ethernet standard itself is being extended to offer QoS guarantees. Figure 1.2 shows the evolution and the current state of Ethernet standards to achieve time triggered and reliable communications.

Figure 1.2 Evolution of switched Ethernet Standards

The basic switching features offered by IEEE802.1D standard were not sufficient for traffic patterns with QoS requirements for streaming or for industrial and automotive domains. IEEE802.1Q standard extended the available features by adding support for Virtual LANs (VLANs) and providing traffic priorities in order to facilitate traffic classification and queuing of different data streams. A brief description of traffic classification is given in Chapter 3. The initial standard IEEE802.1Q-2005 only included a strict priority based transmission selection mechanism for prioritized delivery of streams. This mechanism allows only the highest priority traffic to go first and was inadequate to fulfill hard latency guarantees.

Applications concerning live audio and video require low latency in the order of few milliseconds (maximum 2 ms from the source to destination) in order to achieve media synchronization (lip sync) [7]. Automotive applications involving time-critical control data require even lower latencies in the order of tens of microseconds (e.g. Engine control messages). So, identifying the worst case latency of the network is crucial to guarantee these hard latency requirements.

One of the solutions to achieve low latency in switched Ethernet is to segregate and minimize the interference of non-time-sensitive data traffic with the time-sensitive data traffic through prioritized traffic classification and to improve the traffic shaping mechanism for transmission selection. Traffic shapers, usually present at the egress port of a network element (switch or an end node) are mechanisms to select a specific data stream for transmission, based on different criteria of performance and latency guarantees of that stream. In other words, they prioritize and shape the data traffic from different domains to achieve latency and other QoS guarantees.

Each data traffic class has a specified bandwidth reservation limit and is associated with certain priority. The traffic shaping mechanism being an integral part of the Layer 2 (MAC Layer) of the network element is responsible for selecting the next data traffic class to be transmitted out of the network element based on rules imposed by the priority and bandwidth reservation of that traffic class. By defining and adjusting the rules for transmission selection, it is possible to avoid the interference of low priority traffic with the time-sensitive data traffic thereby guaranteeing the QoS for time-sensitive traffic.

As the standardization moved towards IEEE802.1AVB with a goal to achieve isochronous delivery of messages for audio and video streaming, a substandard IEEE802.1Qav was developed to include a transmission selection mechanism called Credit Based traffic shaper. The Credit Based traffic shaper was a critical part of the IEEE802.1AVB standard for Audio and Video bridging. The traffic shaping mechanism along with the IEEE802.1AS time synchronization standard guarantees QoS for real-time audio and video streams. Thereby, the IEEE802.1AVB enabled switched Ethernet to be used for automotive infotainment systems. A more detailed study of the IEEE802.1AVB standard, Credit Based Shaper and the QoS guarantees delivered by the standard are presented in Chapter 4.

To achieve further lower latencies over Ethernet and to enable a standardized switched Ethernet for industrial and automotive control networks, an enhancement of IEEE802.1AVB standard called IEEE802.1TSN is currently under standardization process. One of the features of IEEE802.1TSN is to introduce a new traffic shaping mechanisms to accommodate and guarantee deterministic end-to-end latency for time-sensitive data traffic. There are different suggestions and proposals from the members of the standardization committee for the new traffic shaping mechanism to be included in addition to the existing Credit Based shaper for audio and video data streams. The IEEE802.1TSN standard and the new traffic shaping mechanisms has a direct impact on the use of switched Ethernet for IVN backbone, as it includes specifications for the time-sensitive control data traffic from protocols like CAN and FlexRay. The IEEE802.1TSN standardization process and the new traffic shapers to improve the QoS of Ethernet for time-sensitive data traffic forms the basis for this thesis work.

#### 1.4 Problem Statement

There are currently three different proposals for the traffic shaping mechanism to be included in the IEEE802.1TSN standard, namely the Time Aware shaper, Burst Limiting shaper and Peristaltic shaper.

Each of these three traffic shaper hardware mechanisms proposed has its own advantages and disadvantages in achieving the goal of very low latency for the time-sensitive control data traffic (100 μs over 5 hops)[8]. Other than the latency requirements for the control data traffic, the automotive industry imposes certain constraints for Ethernet IVN network elements in terms of flexibility to add new data streams, configuration complexity and hardware cost [9]. In order to fulfill these requirements, all the three traffic shaping mechanisms proposed for IEEE802.1TSN standardization process need to be studied, evaluated and compared for feasibility, performance and cost effectiveness.

#### 1.5 Proposed Solution

A hardware implementation for evaluation and performance comparison of all the three traffic shapers is a costly experiment. So the approach is to build to a simulation model of the entire switched Ethernet network including models for switches and end-nodes where each of the traffic shapers can be plugged in as a separate Layer-2 component and evaluated for performance. This solution addresses the following problems

- 1. To evaluate whether the proposed traffic shapers really guarantee the end-to-end latency requirement of  $100~\mu s$  over 5 hops for the time-critical control data traffic in a switched Ethernet network

- 2. To compare the compliance with the standard, configuration flexibility and hardware complexity in terms of memory of all the traffic shapers proposed

- 3. To benchmark the best traffic shaper for the automotive Ethernet IVN requirements

- 4. To provide a software simulation platform for designing and evaluating a new traffic shaper meeting the automotive Ethernet IVN requirements

#### 1.6 Goals

The primary goal of this thesis work is to compare the three different traffic shaping mechanisms for the possibility of achieving the end-to-end latency requirements specified by IEEE802.1TSN standard [8] for time-sensitive control data traffic. Though there is no requirement for message delivery variations (jitter), the control data traffic is ideally intended to have a jitter close to zero. This thesis work aims to identify a traffic shaper with minimal possible jitter for the control data traffic.

In addition to this the thesis work aims to achieve the following goals

- 1. Flexibility in configuration of the transmission period of the Control Data Traffic ranging from 500µs to 1000ms as this is a requirement from the automotive industry for switched Ethernet based IVN [9]

- 2. Fair bandwidth utilization for all traffic classes as per their bandwidth reservation. In other words, the traffic shaping mechanism should adhere to the bandwidth reservations for all traffic classes as specified by the Stream Reservation Protocol of IEEE802.1TSN standard.

- 3. Minimal hardware impact in terms of memory and computational units on the network elements. It is essential to minimize hardware complexity and costs since the traffic shaping mechanism is a hardware part of the network elements (Switches and End nodes).

- 4. Implementation in compliance with or with minimal impact to the other evolving standards in the IEEE802.1TSN standardization process

#### **Secondary Goal**

1. Implementation of different traffic shapers as a plug and play module to the existing SystemC software model at NXP for ease of integration and future analysis

#### 1.7 Methodology

The input for the literature study on the different traffic shaping mechanisms proposed for the IEEE802.1TSN standard is obtained from the IEEE standardization committee presentations, proposals and standard drafts. These proposals are collected, organized and a comparative study is made for benchmarking. Considering the implementation, a simulation model of the automotive Ethernet network according to the IEEE802.1AVB standards is already available at NXP in SystemC. This thesis work uses the existing model as a base framework to implement the benchmarked traffic shapers and to adapt it to the evolving IEEE802.1TSN standards. It is then used for simulative analyses to compare the performances of the three traffic shapers implemented.

The evaluation mechanism involves a validation phase and a testing phase. The validation phase includes the test scenario similar to the one presented in [10] where the authors analyze the impact of one of the traffic shapers (Time Aware Shaper) on the AVB data traffic class. A similar test setup is created and tested for the performance of all implemented traffic shapers. The theoretical maximum end-to-end latency is computed for the worst case behavior in all the three shapers. The simulation results are then compared with the theoretical values for validation. For the testing phase, based on the inputs from NXP, a realistic automotive network scenario is created and tested for latency, bandwidth utilization, memory and other QoS requirements. The results of all traffic shaping mechanisms are compared and the best feasible shaper is recommended based on the overall performance.

#### 1.8 Contributions

This thesis work makes the following contributions

- 1. A compilation of descriptions of three different traffic shaping mechanisms proposed for the IEEE802.1TSN standard

- 2. A software simulation model of three different traffic shaping mechanisms to extend automotive Ethernet IVN to achieve QoS requirements for time-sensitive data traffic

- 3. A simulation environment compatible to both the existing IEEE802.1AVB standard and the evolving IEEE802.1TSN standard which facilitates the configuration of different network topologies and generation of different data traffic classes to analyze the behavior of the automotive IVN

- 4. A modular software implementation of the traffic shaping mechanisms in SystemC to allow the plug and play of different traffic shaping algorithms to the existing Ethernet network element model (Switch and End node).

- 5. Mathematical representation of the worst case end-to-end latency behavior of all the three traffic shapers under considered assumptions

- 6. An analysis and a comparative study of performances of three different traffic shaping mechanisms proposed by the IEEE802.1TSN standardization committee

- 7. A conclusion on the feasible traffic shaper(s) for switched Ethernet IVN

#### 1.9 Thesis Structure

The remaining part of this thesis is organized as follows

Chapter 2 presents the State of the Art and the related works to improve the QoS in Ethernet to accommodate time-sensitive traffic

Chapter 3 gives an overview of the traffic classification and prioritizing features in the IEEE802.1Q standard to include the time-sensitive traffic

Chapter 4 introduces the IEEE802.1AVB standard and gives an overview of the sub-standards included

Chapter 5 explains in detail about the traffic shaping algorithms proposed in the IEEE802.1TSN standard

Chapter 6 explains the simulation environment, the tools used and the implementation of the three different traffic shaping algorithms

Chapter 7 explains the test scenarios for validation phase

Chapter 8 presents the improvements implemented to reduce the end-to-end latency for control data traffic

Chapter 9 includes the test case scenario and results obtained

Chapter 10 includes a detailed discussion on the performance of the three traffic shapers and suitable recommendations

Chapter 11 concludes the thesis work with Chapter 12 briefing the possible future work

### 2. State of the Art and Related Work

This chapter gives an overview of different approaches that facilitate the inclusion of real-time data traffic in switched Ethernet. The correlation between these approaches and the three traffic shaping mechanisms considered is highlighted. Finally, a list of related works in analyzing the individual traffic shaping mechanisms is presented.

#### 2.1 State of the Art

The capabilities of switched Ethernet to accommodate real-time data traffic have been investigated extensively. Two main approaches include the synchronized time-triggered TDMA based medium access approach and the asynchronous event-triggered approach by over-provisioning and prioritizing. The example for the former technique is the TTEthernet (AS6802) [11] and for the later technique it is the IEEE802.1AVB standard with Credit Based Traffic Shaping [12].

TTEthernet offers guaranteed low latencies and finds application in aerospace and aviation industry. It requires static schedule configuration for sending time-triggered traffic in the link. The concept of static scheduling based on the arrival time of all the time-triggered traffic is adapted for the Time Aware traffic shaper [39]. But the problem with static scheduling is that it needs highly accurate synchronization (1µs accuracy) among the nodes and also it is not flexible to add new traffic since the schedule has to be modified at all nodes.

The concept of Flexible Time-Triggered-Switched Ethernet presented in [13] offers flexibility to configure the schedules of the Control Data Traffic dynamically by using a trigger message from a Master Switch in the network. But this concept has not been evaluated for ultra-low latency requirements specified by 802.1TSN. Also, adding this type of Master/Slave configuration in the network for configuring new streams has an impact on the existing sub-standards for Stream Reservation, namely 802.1Qat and 802.1Qcc and this has to be studied separately. For IEEE 802.1TSN compatibility, it is required that the work on traffic shaping should not induce major changes to these sub-standards.

On the other hand, the event-triggered approach from IEEE 802.1 AVB, i.e. the Credit Based shaping technique provisions the prioritized traffic based on the bandwidth reserved for them. This method offers flexibility to add new data traffic dynamically. But the intention of IEEE802.1AVB is to guarantee QoS only for isochronous audio/video streams. It does not include highly time-critical Control Data Traffic in in-vehicle network. The authors in [14] [15] include the time-critical control data traffic in AVB network by considering it as the highest priority traffic and re-arranging the priorities for existing AVB traffic. This method exploits the Credit Based traffic shaper to shape the control data traffic. The authors of [14] achieve a latency of 175 µs over 3 hops for control data traffic with a payload size of 92 bytes. These results show that the Credit Based shaper is not sufficient to guarantee the QoS requirements specified by IEEE802.1TSN [8]. The Burst Limiting shaper introduced in [16] uses the basic principle as that of the Credit Based shaping technique but with certain modifications to include the control data traffic.

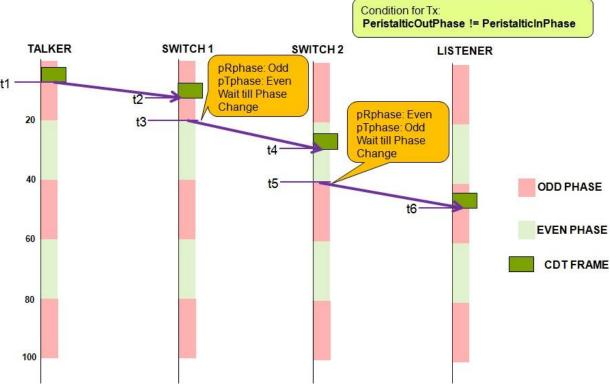

Apart from these two main approaches, there are many other techniques available in the literature which tries to include the real-time data traffic in switched Ethernet networks. A concept called synchronous pacing used in Residential Ethernet [17] and IEEE1394 [18] where the common timeline is divided into

cycles of equal width and the frames are labeled with cycle numbers before transmission. The frame received in one cycle is transmitted in the successive cycle as quickly as possible. This Peristaltic shaper enhances this technique to deliver guaranteed end-to-end latencies for time-critical control data traffic.

The Virtual Clock approach proposed in [19] re-arranges the frames for transmission based on their arrival rate. This mechanism offers flexibility as the incoming frames are dynamically re-arranged. But the work focuses to deliver only average throughput and average queuing delay which is not sufficient for the control data traffic in automotive Ethernet IVN. Other possibilities include the use of real-time scheduling concepts like Earliest Deadline First for the re-ordering of frames in terms of their urgency to be transmitted. This approach called the Urgency based scheduler [20] is another potential traffic shaping technique considered for the IEEE802.1TSN standard. Since there is only very little information available regarding this shaper in the standardization process, it is not considered for this thesis work.

#### 2.2 Related Work

Since all the three traffic shaping mechanisms are still under IEEE standardization, much of the related work deals with proving the performance of each of the shapers theoretically and using simulations. The presentations available from different members of the IEEE standardization committee mostly include theoretical arguments for the comparison of these three traffic shapers.

Boiger in [21] provides a comparative study of the Burst Limiting shaper and the Peristaltic shaper. The work illustrates the working of these two shapers under network overload situations. But it does not really give insights to the end-to-end latencies achieved for the control data traffic. It concludes that the Burst Limiting shaper should block the overload of control data traffic in order to protect the downstream bridges. Also it concludes that the Peristaltic shaper is not backward compatible to the Credit Based shaper in terms of implementation. This theoretical analysis provides sufficient insights for modeling the Burst Limiting shaper and the Peristaltic shaper.

Goetz in [22] compares the simulation results of Burst Limiting shaper and Time Aware shaper using an industrial network use case with eight bridges. The size of the control data traffic is varied and simulations are performed. The results show that for control data traffic with constant frame sizes of 64 bytes, the end-to-end latency in a Burst Limiting shaper varies between 80 µs to 90 µs. On the other hand, the latency remains constant at 80 µs for Time Aware shaper. With random size control data traffic (size varied from 64 bytes to 512 bytes), there was only a minimal difference in latencies between the Burst Limiting shaper (372 µs) and the Time Aware shaper (368 µs). However, this scenario assumed a transmission period of 250 µs for control data with constant frame size and 875 µs for the control data traffic with random frame size. This does not comply with the IEEE802.1TSN standard. Though this work includes only the best effort traffic in addition to the control data traffic for the simulations, it provides sufficient details for the configuration of the Burst Limiting shaper.

The presentations [23][24][25][26][27] provide illustrations and theoretical methods to compute the worst case end-to-end latency for a control data frame. Though these presentations concentrate on different scenarios and variable frame sizes, they offer valuable details for identifying the worst case behavior of each of the traffic shapers. These methods are adapted in computing the theoretical maximum values for end-to-end latencies in the validation phase of this project.

Meyer *et al.* in [10] present a network scenario to analyze the impact of the Time Aware shaper on AVB Class A traffic. The authors present a theoretical analysis for the maximum end-to-end latency of AVB Class A data traffic and compare their simulation results with the theoretical values. The results show that the size of the time slot for control data traffic and the spacing of time slots play a vital role in affecting the end-to-end latency of the AVB Class A data traffic. This work provides the needed the network scenario to simulate the worst case behavior of all the three traffic shapers.

Rahmani *et al.* in [29] propose a novel traffic shaping mechanism called Simple Traffic smoother for video traffic in in-vehicle communication. The goal is to space out the video traffic based on a predefined smoothing interval to avoid traffic bursts and to analyze the resource usage in terms of queue sizes. This work succeeds in achieving efficient resource usage for variable bit rate video traffic in a double star topology. The results prove that smoothing out bursts equally can improve the resource utilization. This work along with the presentation in [28] about performance tradeoffs to achieve end-to-end latency is considered as an input for creating the static schedule for control data traffic in Time Aware shaper.

### 3. Traffic Classification

The selection of particular data traffic for transmission depends on the priority associated with that traffic. So, it is essential to understand how data traffic from different domains is classified and prioritized before describing the traffic shapers for transmission selection. This chapter gives an overview of switched Ethernet specifications for prioritization and classification of different data traffic.

#### 3.1 Prioritization

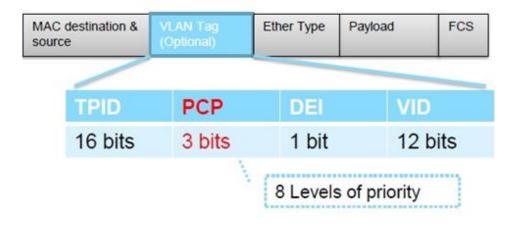

Figure 3.1 illustrates the structure of an Ethernet frame with VLAN tag field. IEEE802.1Q standard specifies VLAN tag as an optional field used to specify the Virtual LAN identification [30]. A VLAN is a logical sub-network defined via the switches. VLAN has properties which allows to

- 1. Limit the number of links used for a broadcast

- 2. Define different priorities to the traffic of different VLANs

- 3. Restrict access to portions of the network

- 4. Define different active topologies

Figure 3.1 Ethernet Frame structure with VLAN Tag

A VLAN Tag is composed of a fixed set of fields as follows (extracted from the IEEE802.1Q standard [30])

TPID: Fixed by the standard, indicates to the switch that this frame has a VLAN tag and the switch has to read further to find the EtherType field

*PCP*: Priority-Code-Point which identifies the priority of the frame (0 to 7 with 0 as the lowest priority)

*DEI:* Drop eligible bit used by input mechanisms at the switches to mark frames that violate the configuration restrictions (e.g. maximum bandwidth allocated for a specific VLAN)

VID: Identifier for a VLAN (upto 4096 values but not all the switches necessarily support the whole range)

The PCP field values can be used to classify different traffic classes based on their QoS needs and map them to different priority levels.

#### 3.2 Traffic Types and Priority mapping

Though it is complex to represent a full description of the QoS needs of the applications and network services with just 8 priority levels using the PCP, IEEE802.1Q gives a pragmatic way of traffic classification. It simplifies the classification requirements and specifies eight different traffic types as shown in the Table 3.1, which can be useful for traffic segregation based on their QoS requirements [30].

| PCP         | Priority    | Acronym | Traffic Types                     |

|-------------|-------------|---------|-----------------------------------|

| 1           | 0 (lowest)  | BK      | Background                        |

| 0 (default) | 1           | BE      | Best Effort                       |

| 2           | 2           | EE      | Excellent Effort                  |

| 3           | 3           | CA      | Critical Applications             |

| 4           | 4           | VI      | Video, < 100ms latency and jitter |

| 5           | 5           | VO      | Voice, < 10ms latency and jitter  |

| 6           | 6           | IC      | Internetwork Control              |

| 7           | 7 (highest) | NC      | Network Control                   |

Table 3.1 Priority mapping of different IEEE802.1Q recommended traffic types

If the network element supports only one output queue, then all the traffic is considered as the Best Effort traffic. So the default traffic is the Best Effort traffic. At the same time, the default PCP used by the nodes to communicate is 0. This is the reason for associating PCP value 0 to Best Effort traffic. But if Background traffic is available, it takes the lowest priority. So, the Best Effort traffic is always transmitted with a PCP value of 0 and it takes a higher priority value than Background traffic if the latter is available in the network.

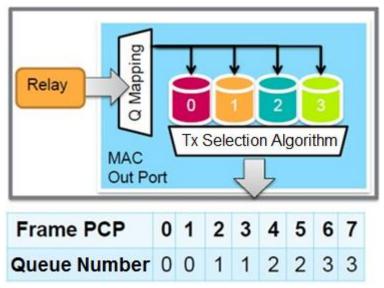

Each output port of a network element (Switch and End nodes) supports a limited number of queues. Different traffic types can be grouped together to match the number of traffic class queues available in a network element. IEEE802.1Q standard suggests a list of group combinations for mapping traffic classes to the queues available [31].

For a better illustration, we assume a scenario where a network element has only four queues and there are 8 different traffic classes available in the network. These eight different traffic classes can be segregated by associating priorities based on the application requirements. Table 3.1 lists the priority and PCP suggestions provided by the IEEE802.1Q standard [31]. These traffic classes can be mapped to the available four queues as illustrated in the Figure 3.2

Figure 3.2 Queue mapping for Traffic Types

This shows that the frames with priority 0 and 1, here the Background traffic type and the Best Effort traffic type are grouped together and mapped to the same queue (Queue 0).

#### 3.3 Traffic Specifications in IEEE802.1AVB and IEEE802.1TSN

Traffic specification is a way to characterize the bandwidth that a data stream with a constant bit-rate can consume. The traffic specification of a data stream is defined by two elements

- 1. Maximum Frame Size: Defines the amount of data that is generated periodically (excluding overhead) by the stream

- 2. Minimum Frame Interval: Defines how often the data is being sent

The IEEE802.1AVB standard provides three different traffic class specifications based on their priorities and interval times namely Class A, Class B and Class BE. Class A has the highest priority, with Class B as the next priority and then followed by Class BE. Class BE has no interval of arrival as it is classified to include the legacy Ethernet traffic which can have random arrival intervals. Also Class BE has no latency constraints. There is no restriction on the maximum frame size of any traffic class. So the frame sizes can be up to the Ethernet standard restriction (MTU of 1500 bytes) for both 100 Mbits/s and 1Gbits/s links. Table 3.2 lists the traffic class specifications in IEEE802.1AVB standard and their QoS constraints in terms of end-to-end latency.

| Traffic Class | Max. Frame Size (MTU) | Min. Frame Interval | Expected end-to-end Latency (7 hops) |

|---------------|-----------------------|---------------------|--------------------------------------|

| ClassA        | 1500 bytes            | 125 µs              | 2 ms                                 |

| Class B       | 1500 bytes            | 250 µs              | 50 ms                                |

| Class BE      | 1500 bytes            | -                   | -                                    |

Table 3.2 Traffic Specifications in IEEE802.1AVB. Class A covers the audio domain and Class B covers the video traffic

Class A traffic specification is intended to classify audio streams in the AVB network. For example, let us assume an audio source generating a 32 bit stereo audio stream at 48 kHz. Accounting for the left and right channel of the stereo, a sample of 64 bits is generated approximately every 20µs. This audio stream can be captured in an AVB Class A stream that generates a frame every 125µs. In this case, a single Class A frame can store 6 left and right audio samples. In a similar fashion, Class B is intended to classify video streams.

Moreover, in the professional live audio scenario, the maximum delay between a live audio source and its destination is limited to 10ms. The processing delays may use up to 8ms and there is only 2ms available for the network to transfer the data from the source to the destination [7] [32]. This explains the latency requirements for the AVB Class A stream.

As the IEEE802.1TSN was intended to service even more time-critical control applications in automotive network, an additional traffic class specification for the control data traffic namely Class CDT was introduced. Also frame size restrictions were imposed for other traffic classes to minimize the effect of their interference with the control data traffic. Class CDT has the highest priority followed by Class A, Class B and Class BE respectively. Table 3.3 lists the modified traffic specifications with their corresponding QoS constraints in terms of end-to-end latency. The frame sizes listed are for 100 Mbits/s links. These specifications are not yet part of the standard as the standard itself is in the process of development and they are only based on the general agreement of the standardization committee during the plenary meetings [8]. However, since they are more likely to get standardized; it serves as an input for this thesis work. The frame sizes are larger for 1Gbits/s links and the complete specification can be found in [8].

| Traffic Class | Max. Frame Size (MTU) | Min. Frame Interval | Expected end-to-end Latency |

|---------------|-----------------------|---------------------|-----------------------------|

| Class CDT     | 128 bytes             | 500 μs              | 100 μs (for 5 hops)         |

| ClassA        | 256 bytes             | 125 µs              | 2 ms (for 7 hops)           |

| Class B       | 256 bytes             | 250 µs              | 50 ms (for 7 hops)          |

| Class BE      | 256 bytes             | -                   | -                           |

Table 3.3 Traffic Specifications in IEEE802.1TSN. A new data traffic class (CDT) for the time critical control data is added

### 4. IEEE 802.1AVB standard

The IEEE802.1AVB is the standard that includes many new protocols to enable switched Ethernet for time sensitive audio and video applications. It forms a base framework for the evolving IEEE802.1TSN standard to target more real-time applications. This chapter gives a brief introduction to the IEEE802.1AVB standard and some of the protocols involved in it.

The IEEE Audio/Video Bridging task group (AVB TG) [33] was created with responsibilities for developing standards to deliver low latency streaming services over IEEE 802 networks. The main goals for AVB TG were as follows [7]

- 1. To provide a network wide precision reference clock

- 2. To restrict the per hop network delays to a known small value

- 3. To limit the interference of the non-time-sensitive traffic for time-sensitive traffic

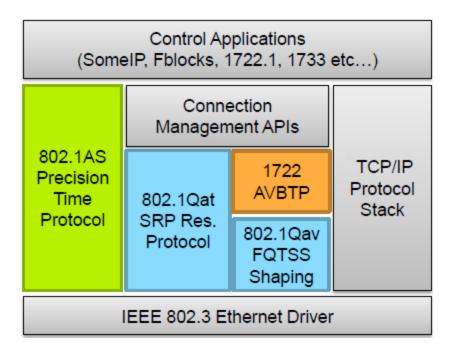

Figure 4.1 Overview of IEEE802.1AVB Standard

Based on the above goals, the task group specified different mechanisms which were based on the Medium Access Control (MAC) Layer to support guaranteed QoS in a switched Ethernet network [7]. The overview of the set of protocols specified in the IEEE802.1AVB standard compared to the legacy protocols is given in the Figure 4.1. These protocols are essential to guarantee a worst case end-to-end latency for audio and video streams. This chapter gives an overview of the different sub-standards which form the IEEE802.1AVB standard and the Chapter 4 explains the traffic classification and the QoS guarantees expected out of the AVB standard.

#### 4.1 IEEE 802.1AS

The IEEE 802.1AS protocol [34] aims to achieve one of the crucial goals for time-sensitive communication which is to deliver precise timing and synchronization over all the nodes in the network. The standard aims to achieve accurate distributed timing with a worst case synchronization error of  $\pm 500$ ns in a seven hop AVB network.

The synchronization process is executed in two steps.

- 1. Selection of a Grand Master (GM) node. The Grand Master is a node with the best available source of time (e.g. atomic clock, GPS, etc.) among all the nodes of the network and is selected using a best master clock algorithm (BMCA). The synchronization of all other nodes is with respect to the Grand Master. The standard also provides plug and play capability with automatic GM selection and automatic reconfiguration in case of GM change or error.

- 2. Synchronization of the distributed nodes. The synchronization information is distributed to the network by using two message types namely the *Sync* and *Follow\_Up* messages. The *Sync* message is synchronization information and the *Follow\_Up* message is the correction value for the previous information to improve accuracy. The correction is performed at all intermediate and the end systems in the network.

IEEE802.1AS requires HW support of the MAC or PHY layers for time-stamping the incoming/outgoing frames but does not require the ability to change the local clock PLL configuration. It specifies the minimum requirements for the local clock of each node in the network. These minimum requirements are listed in the Table 4.1.

| Fractional Frequency offset relative to Timing Application Interface (TAI) | +/- 100PPM         |

|----------------------------------------------------------------------------|--------------------|

| Max Frequency Drift                                                        | 1PPM/sec           |

| Time Measurement Granularity                                               | <= 40ns (25MHz)    |

| Jitter Generation                                                          | < 2ns peak to peak |

Table 4.1 Minimum requirements for local clock

#### 4.2 IEEE 802.1Qat

The IEEE802.1Qat sub-standard of IEEE802.1AVB specifies a signaling protocol named Stream Reservation Protocol (SRP) for end-to-end management of resource reservation in the AVB network [35]. This protocol allows dynamic registration or de-registration of data streams in the whole AVB network to allocate or release the bandwidth associated with that particular stream.

The registration process has two steps. In the first step, the sources of AVB content (Talkers) generate a talker advertisement frame with traffic specifications such as StreamID, MaxFrameSize and MaxIntervalFrames. The talker advertisement is a multicast communication independent of the AVB destination (Listener) and each of the intermediate switches in the network is able calculate the required bandwidth for the stream with this information. If a switch has enough resources, the frame is forwarded

without any modifications. If there are no sufficient resources available at a switch, the advertisement frame is modified to *talker failed frame* with failure information and is forwarded to all the listeners.

When the *talker advertisement frame* is received at the listener, the next step in the registration process begins. If the *talker advertisement* does not contain any failure information, the listener can decide to register and subscribe this particular stream. In this case, the listener generates a *listener ready frame* and transmits it to the talker in order to register to the specific data stream and to inform the intermediate switches along the path to allocate the required bandwidth for the same. If there is no sufficient resource at an intermediate switch, the frame is modified to *listener asking failed* and forwarded to the previous switches to inform about the insufficient bandwidth capacity.

The stream reservation is successful only if the bandwidth requirement of the stream is available on all the switches along the path from the talker to its listeners. The standard also specifies the procedure to handle failed *talker advertisements* and *listener registrations* due to the lack of bandwidth capacity in one or more intermediate switches in the network.

The de-registration of a data stream can be initiated by both talkers and listeners. A talker can de-register a stream at any time by transmitting the *de-register stream frame* and a listener can do this by transmitting a *de-register attach frame* in a similar procedure as that of registration. In this case, the switches along the path releases the bandwidth reserved at the ports for that particular stream.

#### 4.3 IEEE 802.1Qav

The IEEE802.1Qav standard named "Forwarding and Queuing of Time Sensitive Streams" specifies mechanisms to deliver guarantees for real-time audio/video traffic (with bounded latency and jitter) [36]. The standard aims to achieve latency requirements as mentioned in Table 3.2 for both Class A and Class B AVB streams. The two main mechanisms provided by IEEE802.1Qav to achieve guaranteed QoS in a switched Ethernet network are explained in the following sub sections

|          |             |   | Number of Queues or Traffic Classes |   |   |   |   |   |  |

|----------|-------------|---|-------------------------------------|---|---|---|---|---|--|

|          |             | 2 | 3                                   | 4 | 5 | 6 | 7 | 8 |  |

|          | 0 (Default) | 0 | 0                                   | 0 | 0 | 0 | 0 | 1 |  |

|          | 1           | 0 | 0                                   | 0 | 0 | 0 | 0 | 0 |  |

|          | 2 (Class B) | 1 | 1                                   | 2 | 3 | 4 | 5 | 6 |  |

| ξį       | 3 (Class A) | 1 | 2                                   | 3 | 4 | 5 | 6 | 7 |  |

| Priority | 4           | 0 | 0                                   | 1 | 1 | 1 | 1 | 2 |  |

|          | 5           | 0 | 0                                   | 1 | 1 | 1 | 2 | 3 |  |

|          | 6           | 0 | 0                                   | 1 | 2 | 2 | 3 | 4 |  |

|          | 7           | 0 | 0                                   | 1 | 2 | 3 | 4 | 5 |  |

Table 4.2 Recommended Priority mapping for AVB Classes

#### 4.3.1 Priority re-mapping

The IEEE802.1Qav standard extends the priority mapping rules specified by the IEEE802.1Q standard (described in Chapter 3) to accommodate the AVB Class A and Class B traffic classes. Table 4.2 shows the IEEE802.1AVB recommended VLAN priority re-mapping for Class A and Class B with priority values 3 and 2 respectively depending on the total number of queues available. Each entry in the table indicates the queue index allocated to a particular traffic. The modified priority mapping for this thesis work is given in Table 4.3. Since this thesis work uses 8 queues per output port, the corresponding queue indices of Class CDT, Class A and Class B traffic are highlighted. It is to be noted that Class CDT has the highest priority and hence it is assigned the highest queue index. Class A is assigned a queue index of 6 and queue index 5 is assigned to Class B. Class BE with default priority uses the queue with index 1. Class CDT traffic is tagged with PCP value 3, Class A with 5 and Class B with 4.

|          |               |   | Number of Queues or Traffic Classes |   |   |   |   |   |

|----------|---------------|---|-------------------------------------|---|---|---|---|---|

|          |               | 2 | 3                                   | 4 | 5 | 6 | 7 | 8 |

|          | 0 (Default)   | 0 | 0                                   | 0 | 0 | 1 | 1 | 1 |

|          | 1             | 0 | 0                                   | 0 | 0 | 0 | 0 | 0 |

|          | 2             | 1 | 0                                   | 0 | 1 | 2 | 3 | 4 |

| Ę        | 3 (Class CDT) | 1 | 2                                   | 3 | 4 | 5 | 6 | 7 |

| Priority | 4 (Class B)   | 1 | 1                                   | 1 | 2 | 3 | 4 | 5 |

|          | 5 (Class A)   | 0 | 1                                   | 2 | 3 | 4 | 5 | 6 |

|          | 6             | 0 | 0                                   | 0 | 1 | 2 | 2 | 2 |

|          | 7             | 0 | 0                                   | 0 | 1 | 2 | 2 | 3 |

Table 4.3 Priority mapping used this thesis work. Each output port have 8 queues. Table 4.2 is modified to include Class CDT traffic with highest priority. Class CDT, Class A and Class B are allocated to queues 7, 6 and 5 respectively

#### 4.3.2 Transmission Selection Algorithms

IEEE802.1Qav specifies traffic shaping and scheduling mechanisms to enable the transmission of AVB and non-AVB legacy Ethernet frames. These mechanisms play a vital part in delivering guaranteed QoS for the AVB streams.

#### 4.3.2.1 Strict Priority Selection

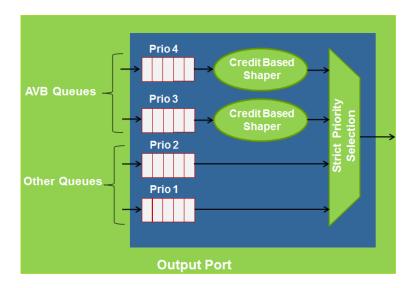

This is the default selection algorithm to select legacy Ethernet frames for transmission. This mechanism is supported by all network elements (Switches and End Nodes) and the frames are selected for transmission based on the priority values of the queues they are in. Figure 4.3 shows the organization of the transmission selection mechanism in an output port of an AVB network element.

Figure 4.3 Transmission Selection at Output Port of a network element

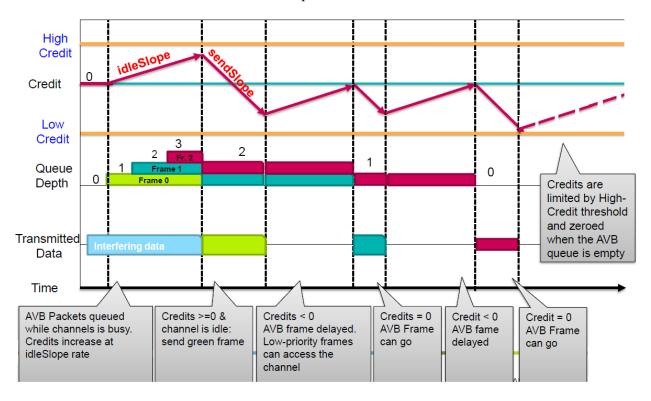

#### 4.3.2.2 Credit Based Shaper Selection

The credit based shaper algorithm is similar to the leaky bucket algorithm. The two AVB traffic classes namely Class A and Class B are organized in two separate queues which are associated with their corresponding VLAN priorities. In this case, Class A queue has higher priority than Class B queue. Each queue is associated with a credit based shaper. The algorithm defines credits in bits to be associated with each of the AVB traffic class queue. The transmission of a frame from an AVB class queue is only allowed when the credits associated with that particular traffic class is greater than or equal to zero, considering there are no conflicting frames. When an AVB frame is removed from the queue and transmitted, the credits associated with this AVB class queue are decreased at a rate called *sendSlope*. If the AVB frame is available in the queue but is waiting for frames from other queues to be transmitted, then the credit associated with this AVB Class queue is increased at a rate *idleSlope*. The algorithm limits the maximum and minimum number of credits that can be accumulated by using parameters *hiCredit* and *loCredit*.

The *idleSlope* for an AVB traffic class at which the credit is accumulated for that traffic class is defined as

*idleSlope* = *reservedBytes/FrameIntervalTime*

The *sendSlope* for an AVB traffic class at which the credit is decreased for that particular traffic class is defined as

sendSlope = idleSlope - portTransmitRate

The rules for calculating the credits are as follows

- 1. If there is positive credit but no AVB stream frame to transmit, the credit is set to zero.

- 2. During the transmission of an AVB stream frame the credit is reduced with the sendSlope

- 3. If the credit is negative and no AVB stream frame is in transmission, credit is accumulated with the *idleSlope* until zero credit is reached.

4. If there is an AVB stream frame in the queue but cannot be transmitted as a non AVB stream frame is in transmission, credit is accumulated with the *idleSlope*. In this case the credit accumulation is not limited to zero, also positive credit can be accumulated.

Figure 4.4 Credit Based Shaper operation for a particular AVB traffic class

The *hiCredit* is the maximum limit which the credit of an AVB traffic class can reach. This is limited by the size of the maximum interference for this traffic class. So *hiCredit* is calculated as follows

$hiCredit = maxInterferenceSize \ x \ (idleSlope/portTransmitRate)$

The *loCredit* is the maximum burst limit that an AVB traffic class can reach once the frame is selected for transmission after it has accumulated credits during the idle time. So loCredit is calculated as

loCredit = maxClassFrameSize x (sendSlope/portTransmitRate)

Figure 4.4 illustrates a scenario for the operation of credit based shaper algorithm. All the frames in the figure correspond to the same AVB traffic class in this example.

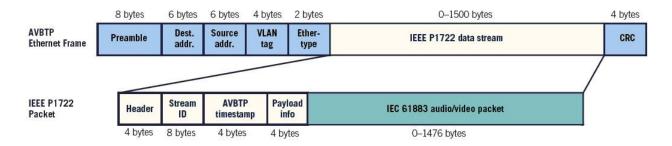

#### 4.4 IEEE1722

IEEE1722 Audio/Video Transport Protocol (AVTP) [37] is a Layer-2 transport protocol for the end nodes in the AVB network with no impact on the switches. This software protocol specifies particular encapsulation of audio and video frames in order to meet the QoS requirements. Also IEEE1722 defines the following

- 1. The media types supported by the protocol (e.g. SD-DVCR, MPEG2 TS, Uncompressed Audio etc.)

- 2. The formats and encapsulations for the supported raw and compressed audio/video formats

- 3. The synchronization mechanisms at the end nodes including clock reconstruction features and latency normalization

- 4. A multicast address assignment protocol (MAAP) to define the ID for new streams

Figure 4.5 1722 AVBTP Ethernet Frame

The standard IEEE1722 frame specified as the AVBTP payload shown in Figure 4.5 is limited to a maximum size of 1476 bytes [37]. In addition to the payload, information like *Header*, *StreamID*, *AVTPTimestamp*, *GatewayInfo* and *PacketInfo* are encapsulated by an Ethernet frame. *StreamID* is used to identify and distinguish different streams. *AVTPTimestamp* contains the presentation time of a frame i.e. the sum of the time when the sample was presented to the AVTP at the talker side and a constant *MaxTransitTime* for the worst case network latency. The *MaxTransitTime* depends on the AVB traffic class of the given stream. The MaxTransitTime of Class A and Class BAVB streams are 2ms and 50ms respectively as derived from their latency constraints. The *PacketInfo* gives information about the payload and the *GatewayInfo* is reserved for the use of AVTP gateways.

# 5. Traffic Shaping Algorithms for Control Data Traffic

The Credit Based traffic shaping mechanism in IEEE802.1AVB needs to be improved to achieve better latencies for time critical Control Data Traffic (refer section 2.1). From Figure 4.4, it can be seen that there are two main methods by which the Credit Based Shaper can be improved.

- 1. Avoiding the spreading out of high priority traffic

- 2. Minimizing or avoiding interference from other traffic

This chapter details three different traffic shaping algorithms namely

- 1. Burst Limiting Shaper

- 2. Time Aware Shaper

- 3. Peristaltic Shaper

These three shapers are under consideration by the IEEE802.1TSN standardization committee to achieve very low latencies (100 µs over 5 hops) for Control Data Traffic. Two of these three algorithms namely Burst Limiting shaper and Time Aware shaper use the above mentioned techniques for minimizing end-to-end latency. The Peristaltic shaper aims to restrict the residence time of the CDT frames in an Ethernet switch to a fixed maximum limit.

#### 5.1 Burst Limiting Shaper

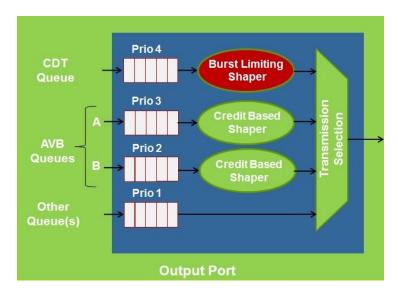

The concept of the Burst Limiting shaper is to allow the high priority Control Data Traffic (CDT) to burst within a certain threshold, thereby avoiding the spreading out of high priority traffic. This algorithm uses similar concepts of credit accumulation and credit reduction techniques as that of the Credit Based shaper but with certain modifications to the rules for selecting a CDT frame for transmission [22]. As shown in Figure 5.1, the traffic classes are organized in separate queues which correspond to their VLAN priorities. Class CDT queue has the highest priority by default and it is associated with the Burst Limiting shaper. However, the priority associated with the CDT queue is changed dynamically by the Burst Limiting shaper. The AVB Class A has the next priority level followed by Class B and other traffic classes. The AVB queues are associated with the Credit Based shapers. The transmission selection mechanism here is a strict priority based transmission selection.

The Burst Limiting shaper algorithm specifies rules for changing the priority of CDT dynamically and for incrementing/decrementing credits to select the next frame to be transmitted.

A CDT frame is selected for transmission only

- 1. If the credit associated with the CDT queue are less than or equal to a maximum value (max\_level)

- 2. If the dynamic priority of the CDT queue is higher than the priorities of all other queues

Figure 5.1 Output port with queue for CDT and Burst Limiting traffic shaper

The rules for incrementing or decrementing the credits are as follows [38]

- 1. The credits associated with the CDT queue are decremented at the rate of *idleslope* only when a frame from a non-CDT queue is selected for transmission or when there is no frame in any of the queues

- 2. The credit associated with the CDT queue are incremented at the rate of *sendslope* only when a CDT frame is being transmitted

- 3. The credit cannot increase more than *max\_level* and cannot decrease below zero

These conditions introduce two new parameters namely *max\_level* and *dynamic priority* for CDT which are to be defined. *max\_level* is the maximum allowed credit limit for the CDT within a transmission period. This implies that *max\_level* is determined by the fraction of total bandwidth allocated for CDT. The rate *idleslope* is a product of the bandwidth fraction for CDT and the transmission rate of the port (*portTxRate*).

$$idleslope = BandwidthFraction \times portTxRate$$

(5.1)

So, the max\_level of the credits can be calculated as

$$max\_level = idleslope \times CTP + SafetyMargin$$

(5.2)

CTP in the above equation 5.2 denotes the Common Transmission Period of the CDT. The Common Transmission Period (CTP) is the minimum interval between successive CDT frames. The term "common" allows the flexibility to have multiple CDT traffic with different transmission periods to be grouped to have the same priority. In this case, the CTP is the "least common multiple" of all the transmission periods. The CTP for CDT according to the IEEE 802.1TSN assumptions is 500 µs [8]. The SafetyMargin is a tolerance limit can be used to increase the max\_level threshold to tolerate overload situations within a transmission period.

The value of the credit determines the priority of the CDT queue. The CDT queue has the highest priority until the credit reaches *max\_level*. The credit is incremented at the rate of *sendslope* as the CDT frames are being sent. The *sendslope* depends on the sum of bandwidth allocated to all traffic other than CDT. So the *sendslope* is given by,

$$sendslope = portTxRate - idleslope$$

(5.3)

When the credit value reaches *max\_level*, the priority of the CDT queue is changed to the lowest of all the queues. This allows the traffic from other queues to be selected for transmission. The credit is decreased when the frames from non-CDT queues are transmitted and as it reaches the *resume\_level*, the priority of the CDT queue is restored to the highest level. The *resume\_level* is a fixed percentage of *max\_level* for e.g. 10%.

$$resume\_level = 0.01 \times max\_level$$

(5.4)

By this mechanism, the CDT traffic is given the highest priority when the amount of CDT traffic is within the limits. At the same time, the bandwidth fraction allocated to a specific data traffic class is also respected.

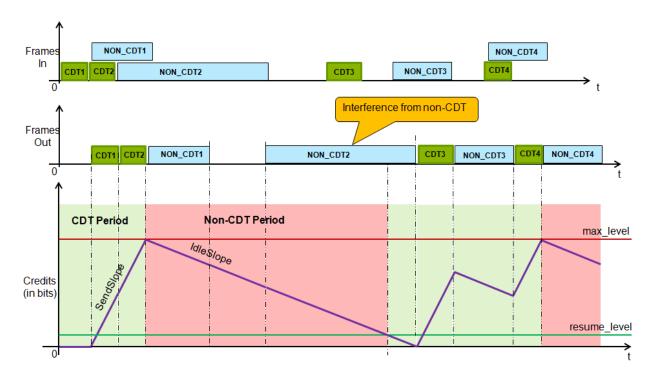

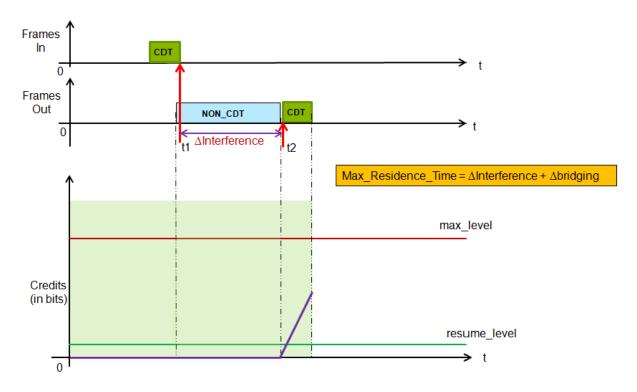

Figure 5.2 Operation of Burst Limiting Traffic Shaping Algorithm in an output port

The Scenario shown in Figure 5.2 illustrates the operation of Burst Limiting shaper in an Ethernet switch. The Frames-In represents the arrival of frames in the input port of the switch targeting the same output port and the Frames-Out represents the frames that are being transmitted in that output port. Frames are numbered in the order they arrive and also named according to their traffic class. It is to be noted that the frames are selected for transmission only if they are completely received. The *CDTPeriod* and *Non-CDTPeriod* shaded regions represent the regions in the timeline where the priority of the CDT queue is

the highest and the lowest respectively. Also it is to be noted that the non-CDT frames can be transmitted in the *CDT-Period* and vice versa if there is no higher priority frame available to be transmitted.

#### **5.2 Time Aware Shaper**

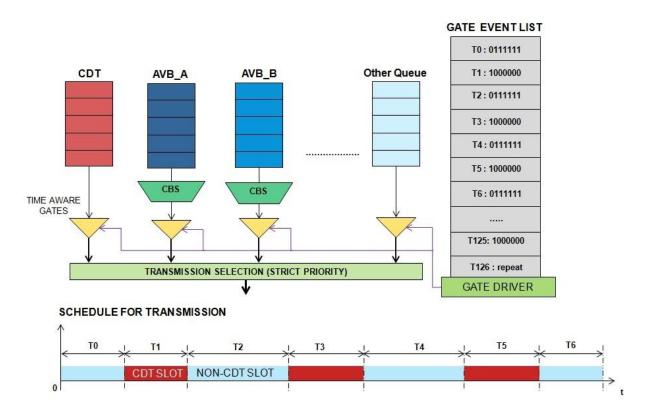

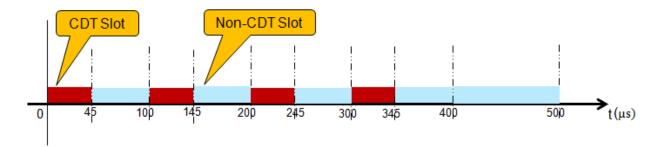

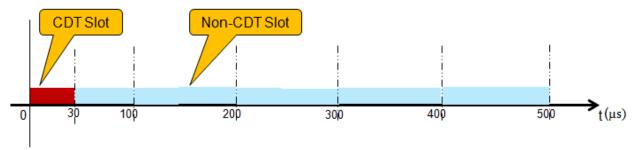

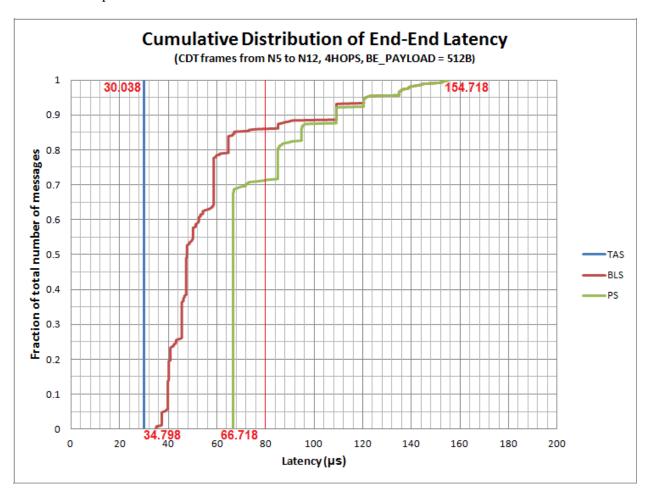

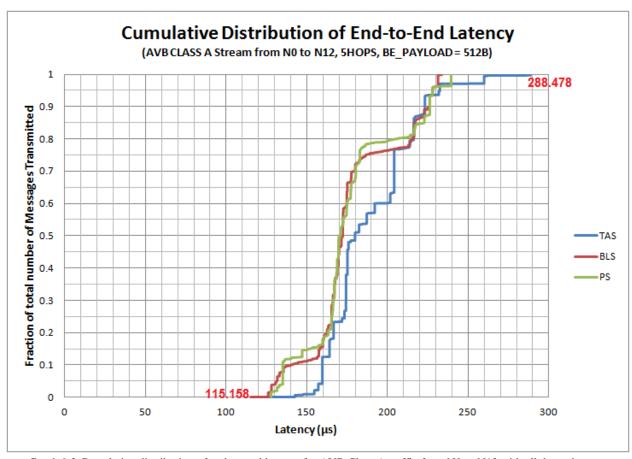

The Time Aware shaper avoids interference from other data traffic to achieve low latency for CDT. The principle is to precisely know the time of arrival of every control data stream and to block the traffic from all other queues during this time to allow the CDT to be selected for transmission [39]. This gives rise to a schedule of time intervals which determines when the CDT queue can be opened or closed for transmission. So the Time Aware shaper is a mechanism which blocks certain queues based on the schedule to allow data traffic from other queues. An example schedule is shown in the bottom of Figure 5.3 with CDT and non-CDT time slots.

The blocking mechanism is implemented by associating each traffic queue of the output port with a time aware transmission gate [39]. These gates are triggered by a gate driver. The gate driver takes the schedule as its input and generates an open or close trigger for all the gates at corresponding time intervals in the schedule. By this, the entire schedule transforms to a *GateEventList*. Each entry in the *GateEventList* is called a *GateListEntry* and has two fields namely

- 1. *timeInterval*: Specifies the width of the time slot

- 2. *gateEvent*: Specifies a set of bits with each bit representing an open or close event for a particular queue (1 for open, 0 for close)

A frame from the CDT queue is selected for transmission only if the transmission gate of the CDT queue is open. On the other hand, a frame in a non-CDT traffic class queue is available for transmission only

- 1. If the transmission gate for that queue is in the open state and

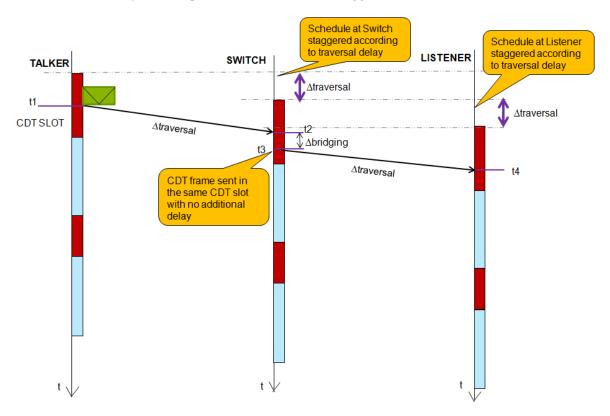

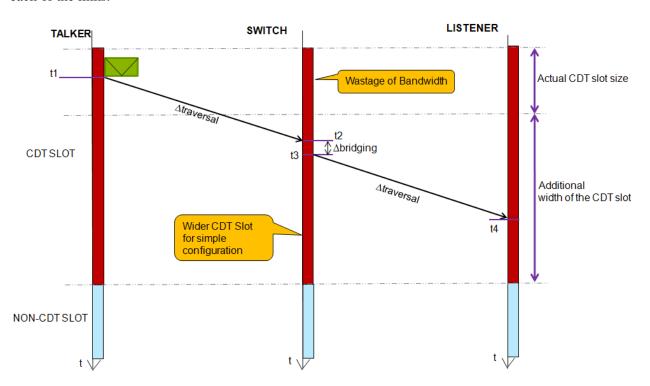

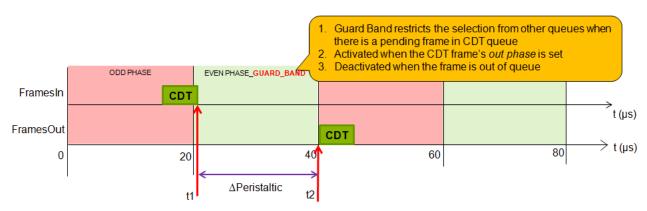

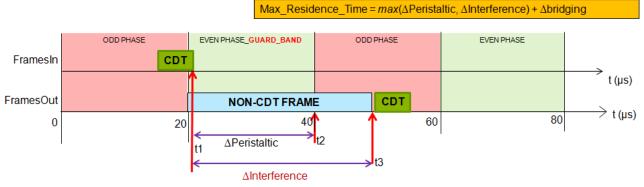

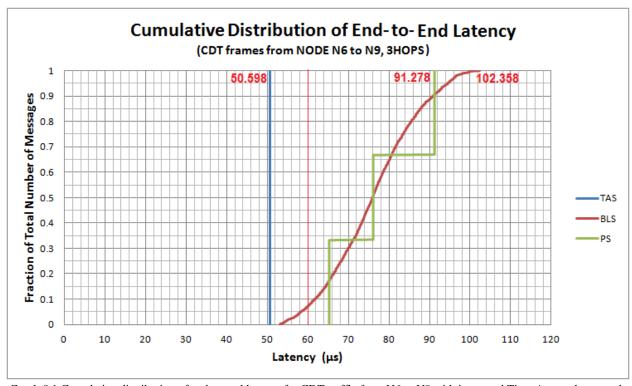

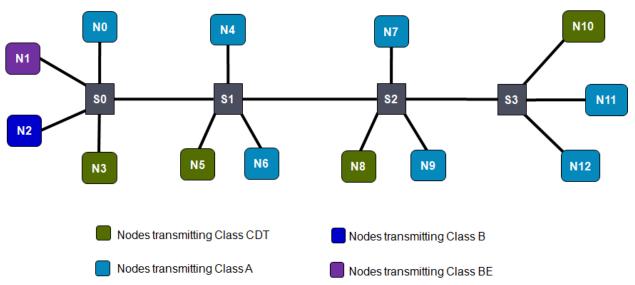

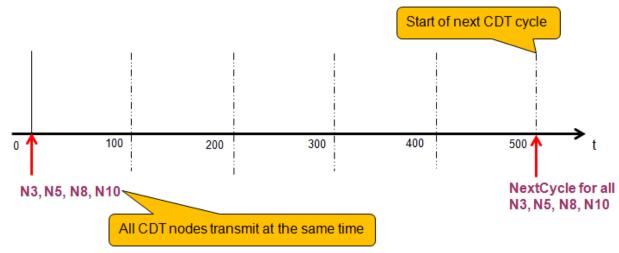

- 2. If there is sufficient time available to transmit the entirety of that frame before the next gate-close event