| MASTER                                                   |

|----------------------------------------------------------|

| Definition and high level description of the C-processor |

|                                                          |

| Withagen, W.J.                                           |

| Award date:<br>1988                                      |

|                                                          |

| Link to publication                                      |

|                                                          |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# Definition and High Level description of the C-processor

Master Thesis of:

Willem Jan Withagen

Departement of Electrical Engineering,

Digital Systems groep.

Eindhoven University of Technology.

November 1987 — December 1988.

The department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsability what so ever for the contents of this thesis.

#### Abstract

In this master thesis is reported on the structured design of a processor which is targetted to execute high level programming languages with more efficiency. The thesis encompasses:

- The definition of an instruction set.

- The developement of a software model that will executed the defined instruction set.

- The developement of a high level decomposition for a choosen architecture. The modules in this high level description are programmed with HHDL. (Silvar-Lisco)

The results of this project give an indication of the problems to be solved in near future before a working system can be created.

It contains two high level models which will execute the defined instruction set. Each of the models is written for a specific task. The software model will execute complete programs to test the performance of the system and its instruction set. The decomposition model will be used as a testing vehicle for future decompositions and possibly gate implementations.

#### Acknowledgements.

A place like a masters thesis report is a too a small place to thank the friends who have helped me during my (long) time at the university.

None the less would I like to say to every one:

# Thank, Thank, Thank for having patience with me! or Dank, Dank, Dank voor al het geduld!

The following is in dutch, since the quotations are typically dutch.

Natuurlijk heeft mijn favoriete schrijver Martin Toonder zijn stripfiguren voor deze gelegenheden wel wat passelijks laten zeggen.

Spreuken die we in het dagelijkse leven ook gebruiken:

- Als je begrijpt wat ik bedoel.... .

- Ik wist niet dat ik het in mij had.

- Had ik maar beter geluisterd.

Maar ook wat diepzinniger:

- Bedrijfsleven.

- 'Recht is is kroms dat verbogen is,' hernam Super na een korte pauze. 'En daar heb ik verstand van, als zakenman zijnde.'

- Communicatie.

- 'Uw antwoord klinkt als een klepel in een gebarsten klok van grote schoonheid,' sprak Ping Po.

- Voor Frank.

- Wanneer men zich in een voertuig zonder bodem bevindt moet men zeer hard lopen wanneer het rijden gaat, en dat deed heer Bommel dan ook.

- Voor de Prof. (onderwijs)

- 'Als het anders niet is,' sprak heer Bommel. 'Mijn goede vader heeft mij tweeënzeventig meter boeken nagelaten. Volg me maar naar de bibliotheek, heer Trot. Er bestaan maar weining dingen waar iemand van mijn stand geen weet van heeft.'

# Contents

| 1 | Intr         | roduction                                                       | 1   |

|---|--------------|-----------------------------------------------------------------|-----|

|   | 1.1          | The history of the project                                      | 1   |

|   | 1.2          | The aspects added in this thesis                                | 2   |

| 2 | Min          | or changes to the registerset and the first level decomposition | 3   |

|   | 2.1          | "C"-processor language background                               | 3   |

|   |              | 2.1.1 A possible memory layout                                  | 3   |

|   |              | 2.1.2 A possible speedup of the architecture                    | 5   |

|   | 2.2          | Changes in the registerset                                      | 5   |

|   | 2.3          | A new level 1 decomposition                                     | 7   |

|   |              | 2.3.1 A means of synchronizing controller(s) and/or slaves      | 8   |

|   | 2.4          | What makes the design testable?                                 | 10  |

|   | 2.5          | What will the next step(s) be?                                  | 11  |

| 3 | The          | e definition of an Instructionset                               | 13  |

|   | 3.1          | The method of constructing the instructionset                   | 13  |

|   |              | 3.1.1 First term objectives                                     | 13  |

|   |              | 3.1.2 First term problems                                       | 15  |

|   | 3.2          | Inventory of operations and functions                           | 16  |

|   |              | 3.2.1 Listing of all possible instructions                      | 16  |

|   |              | 3.2.2 P-type instructions                                       | 19  |

|   |              | 3.2.3 F-instructions                                            | 25  |

|   |              | 3.2.4 M(ixed)-instructions                                      | 31  |

|   | 3.3          | Remarks                                                         | 35  |

| 4 | $\mathbf{A}$ | first model description of the "C"-processor.                   | 38  |

|   | 4.1          | What will the software model not do?                            | 39  |

|   | 4.2          | The modules in the "C"-processor                                | 39  |

|   | 4.3          | Abstractions from the software model.                           | 41  |

|   |              | 4.3.1 Global variables in the C-processor                       | 42  |

|   |              | 4.3.2 Local operations in modules on variables                  | 43  |

|   | 1 1          | B                                                               | 4.9 |

| 5 | A h | igh level implementation in HHDL 4                                           | 6 |

|---|-----|------------------------------------------------------------------------------|---|

|   | 5.1 | The parts to implement on level 1                                            | 7 |

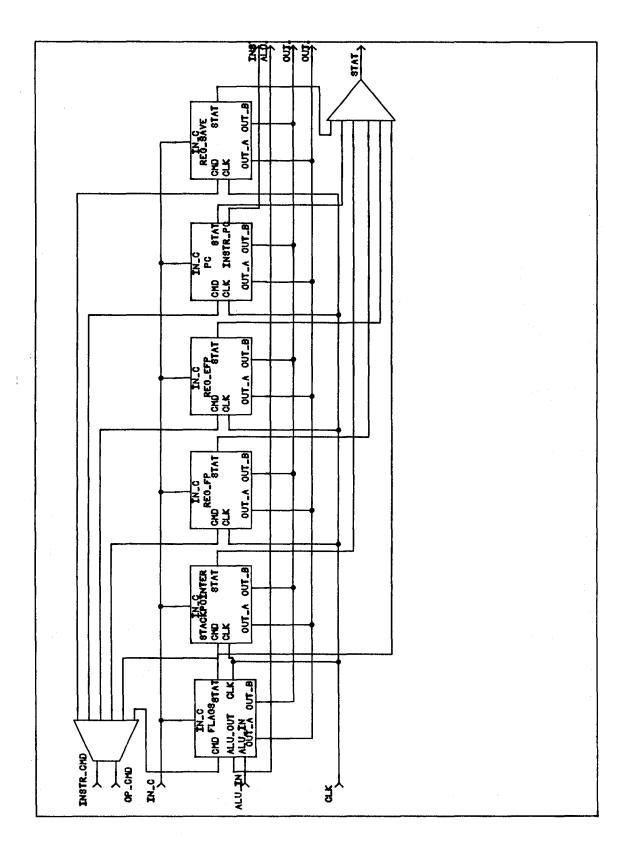

|   | 5.2 | A next decomposition for the Registermodule                                  | 4 |

|   |     | 5.2.1 The stackpointer                                                       | 4 |

|   |     | 5.2.2 The framepointer, external framepointer and temporary save location. 5 | 7 |

|   |     | 5.2.3 The program counter                                                    | 8 |

|   |     | 5.2.4 The Flagsregisters                                                     | 8 |

|   |     | 5.2.5 Command and status translators                                         | 0 |

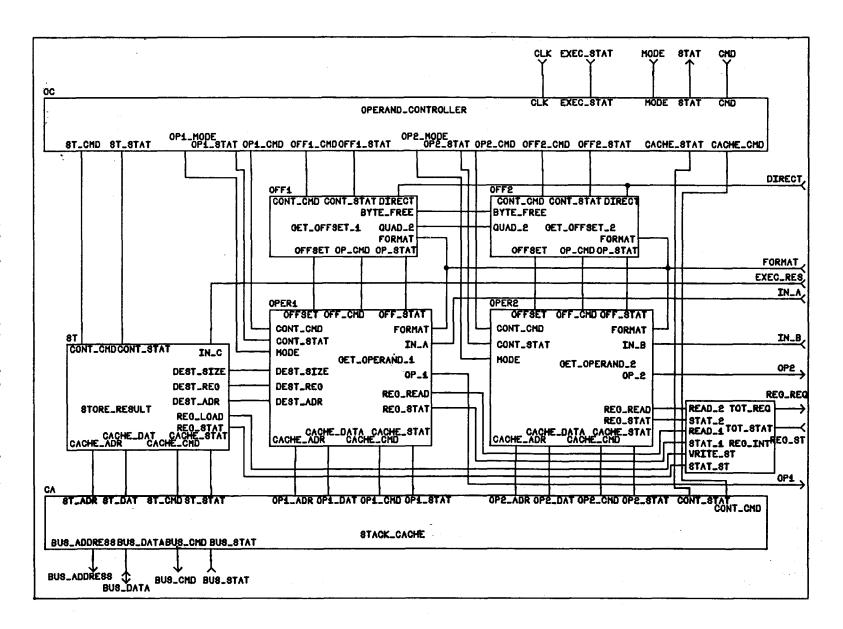

|   | 5.3 | Decomposition of the operand unit                                            | 0 |

|   |     | 5.3.1 The cache window                                                       | 2 |

|   |     | 5.3.2 The operand fetchers                                                   | 4 |

|   |     | 5.3.3 The offset calculation units                                           | 7 |

|   |     | 5.3.4 The store result module                                                | 8 |

|   |     | 5.3.5 The Operand unit controller                                            | 9 |

|   |     | 5.3.6 The interface to the registers module                                  | 0 |

|   | 5.4 | The execution unit                                                           | 1 |

|   | 5.5 | The instruction cache                                                        | 2 |

|   | 5.6 | The bus unit                                                                 | 3 |

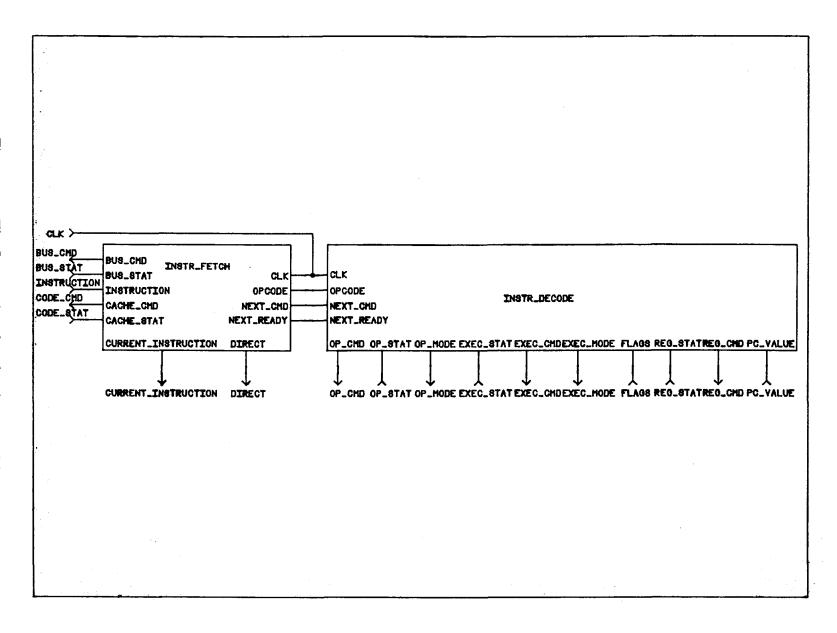

|   | 5.7 | The instruction unit                                                         | 6 |

|   |     | 5.7.1 The instruction fetcher                                                | 8 |

|   |     | 5.7.2 The instruction decoder                                                | 0 |

|   |     | 5.7.3 Conclusions and/or remarks                                             | 2 |

| 6 | Sim | nulation and testing of the HHDL models                                      | 4 |

|   | 6.1 | Testing of the registers and the Register Unit                               | 6 |

|   | 6.2 | Models tested with a driver model                                            | 6 |

|   | 6.3 | The results of the simulations                                               | 7 |

| 7 | Con | nclusions 89                                                                 | റ |

| • | 7.1 | What has been done?                                                          |   |

|   | 7.2 | What is the current status of the project?                                   |   |

|   | 7.3 | Future steps to take                                                         |   |

|   | 7.4 | The ultimate question                                                        |   |

|   |     |                                                                              |   |

| A | Bib | liography 98                                                                 | 5 |

| В | Enu | meration of the "C"-processor instructions.                                  | 6 |

|   | B.1 | Operand formats and their values                                             | 0 |

| C |     | PL/0 compiler for the C-processor                                            | 8 |

|   | C.1 | The lexical scanner                                                          | 8 |

|   | C.2 | , 1                                                                          | 9 |

|   | C.3 | The code generation.                                                         | n |

|   |     | C.3.1  | The instructions generated                                   | 121 |

|---|-----|--------|--------------------------------------------------------------|-----|

|   |     | C.3.2  | CAUTION with addressing of items                             | 124 |

|   | C.4 | Remar  | ks about extensions and improvements to the $PL/0$ -compiler | 124 |

|   |     | C.4.1  | Peephole code optimisation                                   | 124 |

|   |     | C.4.2  | Extending the language                                       | 125 |

|   |     | C.4.3  | Other changes                                                | 125 |

| D | The | UNIX   | I features used during the development of the system         | 126 |

|   | D.1 | Using  | the m4 package                                               | 126 |

|   |     | _      | the SCCS system                                              |     |

|   | D.3 | The us | sed files and directories.                                   | 128 |

# List of Figures

| 2.1        | A possible memory layout used for reference |

|------------|---------------------------------------------|

| 2.2        | A frame on stack                            |

| 2.3        | The processor for programmers               |

| 2.4        | A first decomposition in global blocks      |

| 2.5        | The basic handshake cycle                   |

| 2.6        | An extende handshake cycle                  |

| 3.1        | An example of a two operand P-code          |

| 3.2        | The bit assignment for P-opcodes            |

| 3.3        | The bit assignment for F-opcodes            |

| 3.4        | The bit assignment for F-operands           |

| 5.1        | Level 1 decomposition in smaller blocks     |

| 5.2        | The register module decomposition           |

| <b>5.3</b> | The decomposition of the operand unit       |

| 5.4        | The Instruction decoder decomposition       |

# List of Tables

| 3.1 | Suggestions for Arithmetic and Logic operations       | 17 |

|-----|-------------------------------------------------------|----|

| 3.2 | Flow control operations                               | 18 |

| 3.3 | Processor control operations                          | 18 |

| 3.4 | Several P-opcodes merged into one QUAD                | 25 |

| 3.5 | Layout of 1-operand FM instruction in the code stream | 36 |

| 3.6 | Layout of 2-operand FM instruction in the code stream | 37 |

# Chapter 1

# Introduction

# 1.1 The history of the project.

As part of a project to get a better and more systematic grip on the design aspects of digital systems, a number of "test" design projects have been started at the Digital Systems group of the Department of Electrical Engineering of the Eindhoven University of Technology. The aim is to retrieve common design steps and methods in order to automate, or at least partly automate, these design steps.

The studies are focused on the higher levels of the designs, and do not bother about the last steps of finishing the design, the production of layout and masks. There are two reasons for these limitations. The restriction placed on the projects make them more or less technology independent. At a high level of the design, functional blocks are created which have very little relation yet with their physical implementation.

Current state-of-the-art design systems have speeded up the design process enormously: Time consuming items as drawing, documenting, and testing are already, or will in the near future, be handled in large amount by software systems. What remains for the human designer are the more creative aspects of the design: Developing the specifications and architecture of the circuit. Once the circuit has been broken down into pieces small enough to be handled by software, most of the designers work is done. The software programs can be items such as: State diagram translators, RAM/ROM generators, PLA generators, or even a "silicon compiler".

The design project described in this report is a follow up on the graduation work of F. Budzelaar [Bud88], coached by Prof. M.P.J. Stevens. This thesis involves the design of a microprocessor targeted to execution of high level languages, and in more detail the language "C" [Ker88].

My "inheritance" consisted of a master's thesis which gave a clear analysis of the language items to be implemented in the C-processor, a proposal for the first level of design and the decomposition of the first level into subblocks. Next to this contained the thesis discussions on: Processor design in general, a first global definition of the instructionset, communication between the modules, and low level machine architecture.

# 1.2 The aspects added in this thesis

The assignment for this thesis was to take the work of [Bud88] and check his analysis of the design for flaws ( if there where any ). And from there on continue with the design process starting at the highest level possible. In this thesis are described:

- A minor change in the functionality of the onboard register set. This results in a redraw the highest level of design.

- The bitwise description of the instructionset. The instructionset had to be fully defined before any work of greater detail could be done.

- A software model of the "C"-processor. Due to the complexity of designing the processor a distinction was made in executing mere code, and the functioning of the designed hardware. As a consequence of this divide and conquer methode, the software model would give information about functionality of the given instructionset, usefulness of the first step of decomposition, possible guidelines for future decompositions.

- Another advantage to consider was the possibility to forgo the timing relations and concentrate on the data path and data manipulation. A final profit was constituted by the test files. To test the software model, small code files had to be made, and these code files can also be used during designing and testing of the hardware realization.

- A high level description in HHDL (Silvar Lisco) of the decomposition was an obvious next step following the software model. On this level the software functions and procedures are translated into separate hardware modules. Each of these modules has its interfaces with the "calling" modules and/or a controller. The objective at this stage of implementation is to acquire a HHDL model that will execute the same "C-code" as was executed by the software model. No efforts are made to convert the serial program flow of the software model into parallel execution in hardware. Note that this does not imply that parallelism will not be possible or wanted. But at the current level this is not really considered a valid item.

# Chapter 2

# Minor changes to the registerset and the first level decomposition

# 2.1 "C"-processor language background

The "C"-processor is designed to execute the language "C" more efficiently. To show some of the properties of this concept a short introduction of the background principles is made before the "real" work is started.

### 2.1.1 A possible memory layout.

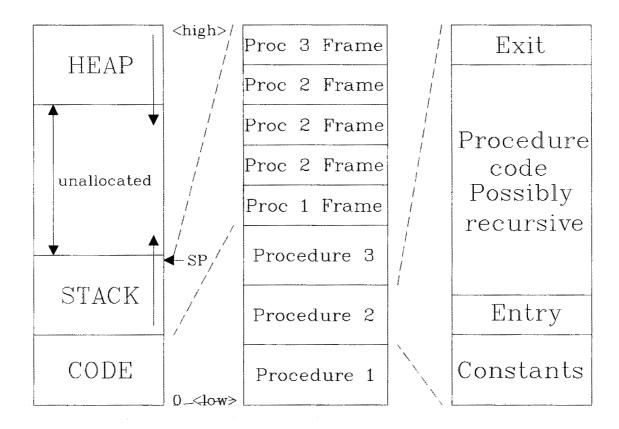

In fig 2.1 a possible subdivision is given. In this are clearly distinguishable:

- The Code space.

- The Stack space

- The Heap

- Unallocated memory.

It is obvious that this subdivision is not the only one possible. But it will serve the purpose of explaining some of the used principles and ideas.

The Code space can be enlarged, in which case the routines comprising the program can be seen. It is possible to look upon the main global body of a program as the first and entrance routine. It is possible for routines to contain a section with constants. These can be either user defined constants, or possibly construct a jump table. It has however to be fixed data.

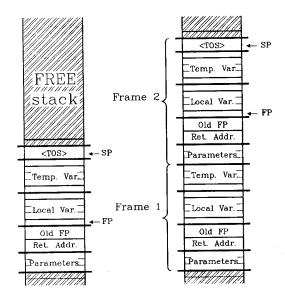

When the execution of a routine is started, the routine will create a stackframe. In this frame (fig. 2.2) are located:

• Parameters

Figure 2.1: A possible memory layout used for reference.

- The status of the previous routine to be saved. ( Here: The return address, and the old frame pointer. )

- Local variables.

- The dynamically used part of the stack, containing < TOS>.

The main routine of the program can be considered as a special type of routine. In the frame of this routine could also the global variables be declared. If a routine calls itself recursively, it will create a new frame for every new entrance of the routine.

Once a routine terminates it returns the Stack space occupied to the unallocated space. ( Or the calling routine will do so. )

If we were to consider frames created by the programming language PASCAL, the above would hold. And the allocation of the parameter and local variable space would be simpler, since this could always be done in the function call of the routine to execute. It is however beyond the scope of this thesis to go too much into detail. For more details of PASCAL program construction we refer to [Pem82].

Although these considerations would give enough reason to call the design a stack-processor design, the name "C"-processor will be kept for historical reason.

Figure 2.2: A frame on stack.

#### 2.1.2 A possible speedup of the architecture.

In our design of the "C"-processor shall the concept of the stack frames (As shown in the above paragraph) be used as the key item of the design philosophy. The instructionset will contain operations which will handle data in the stackframe with optimal speed and with flexibility. The hardware design will facilitate these operations and will make the stack frame fast accessible.

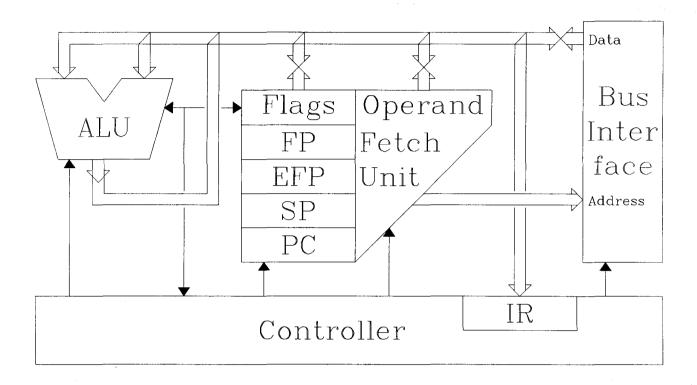

To fulfil the first requirement the instructionset contains a set of P-instructions. (derived from the P(ascal)4 instructions), which are in all kinds of types and machines available) To fulfil the second requirement the hardware will be equipped with a dedicated stack system. This system will manipulate a high speed onboard stack window. This window will always contain the last activated stackframe. As a consequence of the above assumption all operands to the P-instructions are within the system. And thus low access times can be guaranteed. The programmer could view the system as drawn in figure 2.3.

# 2.2 Changes in the registerset.

Although the design in [Bud88] complies with the above assumptions a few changes will be made. Most of these changes are not in the system, but in the functionallity of the designed parts.

The initial design has a TOS (Top of Stack) and a TOPS (Top of Parameter Stack). Both point to the same location, with one exception: When the parameters are loaded on the stack, the stackpointer points in the old frame, while the parameter stackpointer increments with every parameter loaded.

Since it is considered useful to be able to use the stack as a save location for temporary

Figure 2.3: The processor for programmers.

results, and as a consequence of this a chance is made to the functionality of TOS and TOPS.

<TOS >will be a pointer that will always point to the Top of Stack (in future it will be called "SP"), TOPS will point in the current frame to the return address. A negative offset will give access to the parameters, a positive offset will return a value from the local variable space. When examining compiled PASCAL programs it is very often found that one of the general registers serves as a frame pointer. This is also due to the nature of the language PASCAL. The language "C" has the same implications and concerns at this point.

From the same analysis one can deduct that storing large quantities of data on the stack, will defeat the purpose of a cache for the stack. Due to these large quantities, too many reads and writes to main memory will occur and to processor will be slowed down. For these large quantities of data a special frame pointer is added (EFP = External Frame Pointer). This register can be used as an offset register in all addressing modes. But it is the programmers responsibility to maintain a correct value in this pointer. The pointer is not modified by calls or returns. It only changes on a process swap or if the programmer writes into the register.

The consequences of this change are major with respect to the instructionset, but since this was not yet rigidly defined no work is lost.

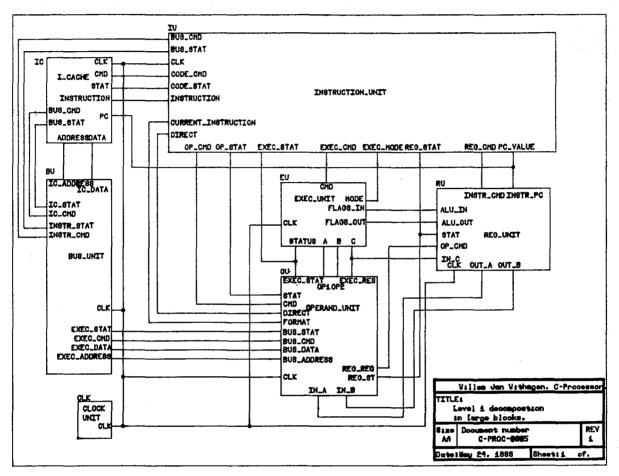

# 2.3 A new level 1 decomposition

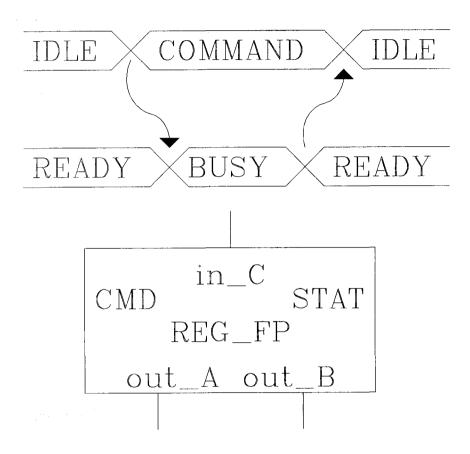

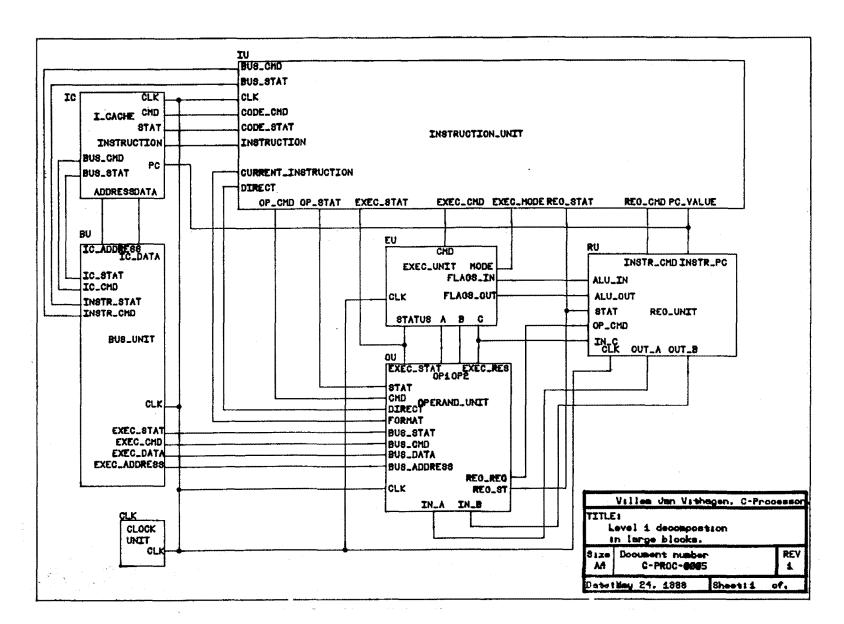

Figure 2.4: A first decomposition in global blocks.

The impacts on the design however are very modest. None the less is a slightly new architecture created. This architecture will make better use of the FP and EFP, see fig. 2.4 If one compares this architecture with the design from [Bud88] on page 41, it is clear that almost all submodules are still there, the names have changed a little. By the new design the data paths and command paths are given in greater detail and have a completely different structure, as are the connections.

#### For instance:

• Since instructions with two operands will be created, a double data path is used to connect all registers and the operand unit. This gives a possibility to calculate the addresses of both operands at the same time, given that other criteria allow for this parallelism.

- The program counter can be used for references during offset calculations, hence the path to the operand-unit.

- But as one can deduct from the design, the paths to and from the execution unit are all uni-directional. The A- and B-bus have six sources, the C-bus or the "result bus" has one master and six slaves. The flags register has two connections to the execution unit, one for either direction. Through these connections the values of the flags will be transported. ( to and from the ALU )

- All modules (on this level) are centrally controlled by the instruction-unit. Every module interfaces with the instruction-unit through a set of handshake signals. These signals contain at least on of the following signals or busses:

- A command bus, with a NOP command as one of the commands. Other commands can be either a plain start command or more complex commands which specify the action to perform.

- A result or status bus. This bus has at least the following values: READY, BUSY. They indicate whether the unit is currently active. Other included commands can be request for the controller. If for instance extra data is required, this can be asked with a status like MORE or NEW\_DATA.

- An exception to the above scheme is the regsiter\_unit This unit can also be controlled directly from the operand\_unit. Although this is clearly an evasion from the "central controller" idea, it prevents extensive amounts of communication between the instruction\_unit and the regsiter\_unit.

# 2.3.1 A means of synchronizing controller(s) and/or slaves.

Since on forehand very little is know about timing and sequence relations, a tight (but flexible) mechanism is needed to keep all modules in synchronization. It would be possible to solve some of these problems, using a central clock, but this would force us to give timing estimates for the modules. In stead of the clocked solution, a choice is made for a completely asynchonous communication. In this way no information concerning timing relations will be left out. In future steps, however, it can prove possible to remove certain constrains in the operations. These decisions should then be made at the appropriate level and not on the current level, in which case they could stress the design to comply with some ad hoc rules.

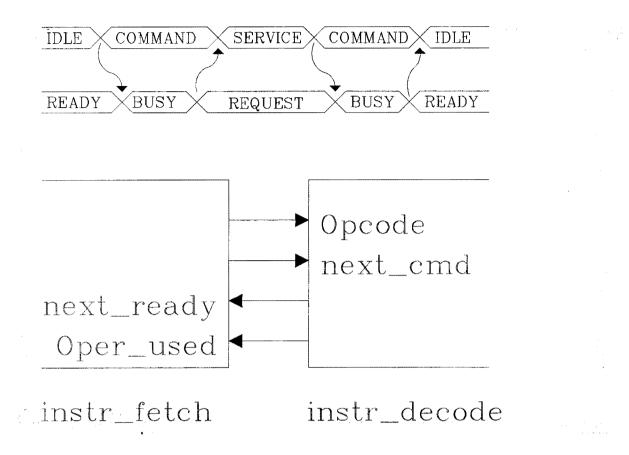

The principal way of handshaking will be:

- 1) The slave unit is READY, and the command is NOP.

- 2) The controller issues a command (COMMAND), and the slave responds with setting it's status to BUSY.

Figure 2.5: The basic handshake cycle.

- 3) The slave carries out the requested task. While in the meantime other modules could be scheduled, either in parallel or upon request of the slave unit currently observed.

- 4) Once the slave is done with its assignment, it clears the status to READY.

- 5) The controller acknowledges the READY by resetting the command to NOP.

#### Compare with figure 2.5.

If the slave module has a "request" for the controller, then the communication could be extended as in figure 2.6:

- 3a) The status changes to REQUEST. The slave could continue its operations, but it is not yet allowed to use the requested item.

- 3b) The controller responds with a NOP on the controlbus. This should be interpreted by the slave as: "The controller is currently not observing the statusbus of this unit".

Figure 2.6: An extende handshake cycle.

- 3c) Once the controller is able to fulfil the request issued by the slave, the controller will change the controller to COMMAND to alert the slave that the operation asked for has been completed.

- 3d) The slave unit will acknowledge the completion of the request by setting its status back to BUSY.

Naturally there are many possible variations on this theme. The two examples above are considered the most elementary ones used in this design. They are, if so needed, adapted for each situation. But on the high level description a strong attempt is made to exercise a complete handshake mechanism on all interfaces.

# 2.4 What makes the design testable?

If testability needs to be considered on this level of the design it would be possible to state: "I'm using a scan-design, so the design will be testable by definition." However, simple observations show that on this level every module can be connected directly to I/O-pins of the chip by switching other modules into a transparent state. In this test state

there will be no changes in the flow of data. Or in other words: no datapath will have to change its direction of flow for the testing.

Switching a module into a transparent state will require a multiplexer and a demultiplexer per datapath, and in the overall design a small controller to perform the testing.

The problem with this approach is that there is no guarantee that the chip will be fully testable. Scan-design however will in its crude form guarantee that all modules are testable. The systems buses are the one exemption from this. Even in the current scan-designs one has to test busses with a different strategy.

The valid question to ask now is: "Which of the two options will be the cheaper one." The answer to this question at the moment is of very little concern, since it was already stated that scan-design is a possibility that is almost always possible, and for the other option the circuit needs no changes at this level of implementation.

# 2.5 What will the next step(s) be?

The decomposition has still left us five large items:

- The bus controller, a circuit which has to arbitrate memory requests from the operand unit, and the instruction cache unit. It also has to manipulate the data to be able to write BYTES, WORDS and QUADS. The complexity of this will be fairly low, the next step will result in a definition of the datapath, registers and controller within the module.

- The instruction cache unit, the unit can have several types of implementation. However, all of these are on a rather primitive level. Hence the next decomposition step for this block will probably be port level.

- The instruction unit, this block is the major controller of the processor. It will consist of a micro programmed controller, or a state machine, or any combination of the two. The design can be straight forward.

- The execution unit, in this unit the actual data manipulation will take place. It will contain all logic to do the needed arithmetic and logic operations, most of these can be done by a "simple" combinatorial network. Multiply, divide, modulo are candidates for serialisation, since a 32/32 divide ain't nothing to program just straight into logic.

- As a consequence of this the execution block will contain a large and complex logic part, next to a simple controller with again a large logic network.

- The operand unit, this unit has to prepare the operands to go along with an instruction. The operands will be used by the execution unit. All different types of addressing modes are implemented in this module. The stack cache could also be fitted into this module. This module has to implement several subprocesses and will be fairly complex. This module will have to perform the actual fetching of the

| Minor | changes to  | the    | registerset | and | the first | level | decom        | position |

|-------|-------------|--------|-------------|-----|-----------|-------|--------------|----------|

|       | 01100110000 | , ,,,, | 0           | ~   | V         |       | OL O O O III | P        |

operands, whether they are in main core or in the stack cache. It has to translate operand sizes to their appropriate formats. It has to convert from signed to unsigned and vice versa.

Before a next decomposition step is taken, it is very desirable to have the instructionset of the "C"-processor available in full detail. It is obvious that the instructions used, and the operand formats possible will have a great impact on the future decompositions. The next chapter will contain a short recapture of the analysis from [Bud88] and then an enumeration of the used instructions and operands will be given.

After this it will be possible to make a new decomposition for the major blocks in the current decomposition, and for this is it advisable to make a complete analyses of the structure and the requirements of the modules that will be sliced up. For this purpose a software model will be created. This model should supply detailed information on the data paths used and manipulations done with this data.

# Chapter 3

# The definition of an Instructionset

For the "C"-processor to function, it is necessary to have an set of instructions which can be executed. ( How very trivial! ) The definition of this instructionset is however not a trivial matter.

# 3.1 The method of constructing the instructionset.

As a guideline for the decisions to be made during the selection of instructions and the subsequent assignment of codes to the instructions, a collection of objectives is generated. The source of these objectives is in the first place the famous big thumb, and secondly there are some indications for selection in the literature. [Das84]

# 3.1.1 First term objectives.

As guideline for the design of the instructionset, the following criteria were taken into account:

- Instructions are aligned at either BYTES (8 bits), WORDS (16 bits) or QUADS. (The term QUAD stands for 32 bits.) A good choice seems to be alignment on WORD basis. Which gives the basic opcode a size of 16 bits.

- The possible operand sizes included in the instruction are BYTE, WORD and QUAD. If an operand is of BYTE size then it might be desirable not to waste any space due to alignments. Not from a next operand, not from a next instruction.

- This would mean that for instructions with BYTE operands the opcodefield is limited to 8 bits.

- Two operand instructions. Most of the arithmetic and some other instructions have two operands, which are both to be included in the instruction.

- If an instruction contains a QUAD immediate operand, then this operand will be aligned on a QUAD boundary. The two lowest address bits are zero. If the alignment

leaves holes in the code space, they will be treated as NOPs, it is up to the executionunit to detect these items in time to ignore them completely.

The coding of the instructions is chosen in such a way that the decoding and/or the interpretation can be done in a straightforward way. Straightforward here means in as little time as possible.

The following addressing modes are candidates for implementation. With these items one has to keep in mind that the processor under design has to be of semi-RISC architecture, and this prohibits the use of complex addressing modes such as base-indexed, indirect-indexed, etc. The reason for this is that in most processors a lot of registers are used in these modes to get a high performance. Since our processor does not stand out in the number of onboard registers these modes are taboo. The emphasis should be on the dedicated stack in the system

The only exemptions from this are the indirect modes, which need one extra cycle to obtain the final result. And the linked-list mode which will access to get next operands, and these might cause extra accesses given their format.

#### • Register.

SP, <TOS>, FP, EFP, Flags, PC.

Although the previous arguments favor a rigid and orthogonal instructionset, not all registers need to be possible in all instructions. (i.e. Flags and PC) For the <TOS > register could using the register mode mean: implementation of autoincrement and autodecrement: POP and PUSH.

#### • Immediate.

Data size: BYTE, WORD, QUAD.

The operand is contained in the instruction.

#### • Direct.

Address size: WORD, QUAD.

( BYTE is possible but gives page ZERO addressing. Which does not seem very important in this design. )

The address of the operand is included in the instruction.

#### • Relative.

Offset size: BYTE, WORD, QUAD.

The address of the operand is found through the addition of the contents of a register and an offset contained in the instruction. The registers used with this mode are mostly SP, FP, EFP, < TOS >. The PC could be used for a, in code included, table of constants.

#### • Indirect.

Address sizes: WORD, QUAD.

( For BYTE indirect addressing can be said exactly the same as with direct addressing.)

The field in the instruction gives the address where the operands address can be found.

• Relative Indirect.

Offset: BYTE, WORD, QUAD.

The offset in the instruction and the indicated register create the address where the address of the operand can be found.

The registers for this mode are again: SP, FP, EFP, <TOS>.

- Next to the previous types of "normal" operands is the linked-list addressing. This kind of addressing is specifically targeted towards high level programming languages.

- To get the value of a variable which is defined on a higher lex-level in PASCAL, a series of static links has to be processed before the required value can be obtained.

- In "C" often variables are referenced with more than one level of indirection. Since the types and repetitions of the indirections are known at compile-time is it possible to create a list of actions to be taken.

- This method does not have a fixed format. It consists of a repeated list of addressing operands with offsets. The offset of a item in the chain is calculated by part of the chain already processed.

- Offsets specified in the instructions are ,where used, of several sizes. BYTE and WORD are valid candidates for this. QUAD would be comfortable if large structures are used on the External Frame. (Large means bigger than 64K)

Literature indicates that a considerable amount of processing power is spent on the transportation of data from one location to the next. (approx. 50%)

Next to these instructions are the arithmetic-instructions (approx. 35%) of which the add instruction is by far out the most used instruction.

Even more difficult is the fact that in most cases of immediate data the size of the data is very small. The instructions ADD 1, LOAD 0, TESTBIT 1 are very common examples of this type.

## 3.1.2 First term problems.

Given the above statements, some of the problems already shine on the horizon.

• If all possibilities are simply coded in the instruction, without regards to compactification, the size of an instruction might well be larger than 32-bits.

- When however all operand formats and opcodes are merged into one large bit field, then the decoding of a instruction will require a large block of logic to decode the exact meaning of the opcode and the operand formats.

- When a two-operand instruction has operands of different sizes, the smaller operand has to be converted to the size of the larger one. This extension can be done by either sign-extension or by logic- extension. Some information regarding the types has to be added in the instruction.

# 3.2 Inventory of operations and functions.

The previous section contains an enumeration of possible operands and their addressing methods. To be able to define an instructionset one needs a list of operations on these operands. Furthermore needed are other instructions. A list is given below which is extracted from: [Bud88], 68000 user manual, am29000 user manual and the P4-code instructions. Note that this list is not the full and complete union of the four mentioned instructionsets. The report [Bud88] and the P4-code were used as prime sources, the other two are "checked" to see if there where any omissions.

## 3.2.1 Listing of all possible instructions.

This is a list with:

- A description of the instruction,

- A mnemonic and

- The number of possible operands.

#### NOTE:

This is not an listing of the instructions in assembler format. It is mere jested as a inventory list for the instructions possibly implemented.

If and when the instruction are going to be used, then a definition of the assembler foramt would be appropriate.

#### End NOTE

The instructions are grouped in appropriate classes:

- Arithmetic, boolean and logic operations. Table 3.1

- Boolean operations can have only two result values. The result is either 1 or 0,

(true or false.) A non boolean value is always considered true if it is not 0.

| Source | Description                       | Mnem. | #operands |

|--------|-----------------------------------|-------|-----------|

| В      | Add.                              | ADD   | 2         |

| В      | Add with Carry.                   | ADDC  | 2         |

| В      | Boolean AND.                      | BAND  | 2         |

| В      | Logical AND.                      | LAND  | 2         |

| В      | Boolean OR.                       | BOR   | 2         |

| В      | Logical OR.                       | LOR   | 2         |

| В      | Logic XOR.                        | XOR   | 2         |

| M      | Check bounds.                     | CHK   | 3         |

| В      | Compare.                          | CMP   | 2         |

| В      | Divide Unsigned.                  | DIVU  | 2         |

| В      | Divide Signed.                    | DIVS  | 2         |

| A      | Extract part of item.             | EXTR  | 2         |

| В      | Modulo Unsigned.                  | MODU  | 2         |

| В      | Modulo Signed.                    | MODS  | 2         |

| В      | Multiply Unsigned                 | MULU  | 2         |

| В      | Multiply Signed                   | MULS  | 2         |

| P      | Boolean Not.                      | BNOT  | 1         |

| P      | Logic Not.                        | LNOT  | 1         |

| В      | Negate                            | NEG   | 1         |

| В      | Move                              | MOVE  | $_2$      |

| В      | Shift left.                       | SHL   | 2         |

| В      | Shift right, arithmetic Signed.   | SARS  | 2         |

| В      | Shift right, arithmetic Unsigned. | SARU  | 2         |

| В      | Subtract.                         | SUB   | 2         |

| В      | Subtract, with Borrow.            | SUBB  | 2         |

| В      | Select operand                    | SEL   | 3         |

Table 3.1: Suggestions for Arithmetic and Logic operations

| Source | Description                        | Mnem.                | #operands |

|--------|------------------------------------|----------------------|-----------|

| В      | Call "high level" Function.        | CALLF                | 2         |

| В      | Call Subroutine                    | CALL                 | 1         |

| В      | Conditional Jump.                  | JMPC                 | 2         |

| В      | Jump, Goto.                        | JMP                  | 1         |

| В      | Return from "high level" Function. | RETF                 | 1         |

| В      | Return from Interrupt.             | IRET                 | 0         |

| В      | Return from Subroutine             | $\operatorname{RET}$ | 0         |

| В      | Swap context.                      | SWAP                 | 2         |

| M      | Test, Decrement and Jump.          | $\mathrm{TDJ}$       | 2         |

| M      | Trap.                              | TRAP                 | 1         |

Table 3.2: Flow control operations

| Source | Description                        | Mnem.  | #operands |

|--------|------------------------------------|--------|-----------|

| В      | Call "high level" Function.        | CALLF  | 2         |

| В      | Clear Instruction Cache            | CIC    | 0         |

| В      | Enable interrupt.                  | ENAINT | 1         |

| В      | Disable interrupt                  | DISINT | 1         |

| A      | Halt.                              | HALT   | 0         |

| A      | Lock.                              | LOCK   | 0         |

| M      | Reset external system.             | RESET  | 0         |

| В      | Update Main Memory with data cache | UPDM   | 0         |

Table 3.3: Processor control operations

- Logic operations are operations which are performed bitwise on all bits of the operands.

- Flow-control instructions. Table 3.2

- Processor-control instructions. Table 3.3

The indications with the instructions, A = am29000, B = [Bud88], M = Motorola 68000, P = P4-code, give an indication where the instruction is first found during the generation of this list. It does not suggest as to which processor knows which instructions.

It is also possible to classify the instructions by the way they handle their operands. In the following paragraphs different types of instructions will be introduced.

## 3.2.2 P-type instructions.

These instructions emphasize the stack oriented character of the processor. On a "regular" processor they are usually very slow and cumbersome. Here this is not the case due to the typical implementation of the stack-cache, or stack-window.

The instructions are targeted at:

• Data manipulation on the stack, in the stack-window.

This gives 42 different types of opcodes to be implemented.

- Use autoincrement and autodecrement modes with the stackpointer, when used as < TOS > operand.

- Are short and compact. (8 or 16 bits)

- Can contain short immediate data.

- Some can take one operand from the local frame using the FP.

In the following description the notation given below is used:

- < TOS > the QUAD pointed at by the stackpointer SP.

- < TOS 1 > is the QUAD just below the stackpointer.

- < TOS 2 > is the QUAD just 2 below the stackpointer.

#### Instructions with implied operands.

These instructions have complete implicit addressing, no operands what so ever are present in the instruction.

#### 1 Operand instructions.

Plnot.

$$< TOS > := lnot < TOS >$$

Logic bitwise complement the top of stack.

Phnot.

$$< TOS > := bnot < TOS >$$

Boolean complement the top of stack.

Pneg.

$$< TOS > := - < TOS >$$

2's-complement the top of stack.

Pdup.

$$< TOS + 1 > := < TOS >$$

$$SP := SP + 1$$

Create a copy of <TOS>on the stack.

#### 2 operand instructions.

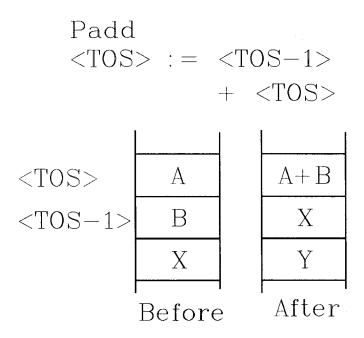

All of the following instructions have the same description except for the ALU-action to be performed:

'code' = Padd, Paddc, Pland, Pband, Plor, Pbor Pxor, Pdivu, Pdivs, Pmodu, Pmods, Pmultu, Pmults, Psub, Psubb, Pshl, Pshrs, Pshru.

Where the sequence of action is given by:

$$:=  'code' < TOS>$$

;SP:= SP - 1

In plain English:

The two top elements of the stack are added and deleted from the stack. The result will be placed back on the stack. This is shown in figure 3.1.

Figure 3.1: An example of a two operand P-code

At first it may seem strange to use < TOS - 1 > as the first operand for the instruction, since < TOS > is ready available. But it is the design target to execute instructions like this in one cycle, and hence both have to be fetched in parallel. And if one considers that statements of the construction "A := A 'code' B " are very common, then the used sequence becomes even more obvious.

In the remaining text of this thesis it will be assumed, unless stated otherwise, that in constructions like the ones discussed here **A** represents operand 1, and **B** represents operand 2.

Pcomp.

$$\begin{aligned} \mathsf{Flags} &:= <\mathsf{TOS} - 1 > \text{-} <\mathsf{TOS} > \\ &; \mathsf{SP} &:= \mathsf{SP} - 2 \end{aligned}$$

Set the flags according the result of a subtraction of the top 2 elements. The elements are removed from the stack. Pswap.

#### 3 Operand instructions.

Pcheck.

Flags or

$$<$$

TRAP $>$  :=  $<$ TOS  $-$  2 $>$ <=  $<$ TOS $>$ <=  $<$ TOS $-$  1 $>$  ( possibly  $<$ TOS $-$  2 $>$ :=  $<$ TOS $>$ ) ;SP:= SP- 3 ( -2??? )

Check the bounds of the top against the two given bounds on the stack. It is either possible to generate a TRAP if the check fails. It is also possible to set flag to indicate a failure.

Psel.

$$<$$

TOS  $- 2>:= (<$ TOS  $- 2>? <$ TOS  $- 1>: <$ TOS $>)$ :SP:= SP-  $2$

Replace the top of stack with either < TOS - 1 > or < TOS > dependant on the value of the selector in <math>< TOS - 2 >.

#### Remarks on P-instructions with implicit operands

All instructions described above have no specified operands, and their mnemonics can be used as is. It is also clear that the majority of the instructions will have two operands, only a few will have 1 operand. Only 2 instructions require three operands, of which the Check instruction also requires two aritmetic actions.

#### Instructions with explicit operands.

In most cases where immediate data is used, the size of the data is small. One of the most common actions is the addition of one, increment, or a subtraction of one, decrement. Another class of instructions with parameters is shifts and rotates. The explicit operands indicate the number of places to be shifted. Also possible is an extract with two operands: They indicate the place of the first bit to be extracted and the length of the string to be extracted.

The size of the operand is made 8 bits in arithmetic and logic operations. This gives a possibility to act on values which are actually 8 bits, characters for instance. For the shifts and the extract an operand size of 5 bits will generate all possible index addresses.

#### Arithmetic and logic instructions

'code' = Paddi, Paddci, Plandi, Pbandi, Plori, Pbori, Pxori, Pdivui, Pdivsi, Pmodui, Pmodsi, Pmultui, Pmultsi, Ppushi, Psubi, Psubbi, Pcompi.

Where the sequence of action is given by:

Next to the 7-bits immediate data included, the data BYTE also contains a bitflag to indicate whether the immediate data is to be logic or sign extended. It is also possible to see the data as an 8 bits signed integer which is always sign extended. The ultimate effect will be the same.

The immediate data will be the second operand during calculations of this type of instruction.

#### Extract.

Pextract.

$$< TOS[0..length]> := < TOS[start..(start+length)]>$$

The bitstring [start..(start+length)] replaces the < TOS > right justified. (if length = 0 exactly **one** bit is extracted!) Since this extraction needs 2 \* 5 bits to identify all extractions possible, 2 bits from the instruction code are used. This gives 4 Pextract opcodes, they all extract a part of the < TOS > value, but dependant on the start value another version of the extract instruction will be used.

#### Instructions with a relative reference to FP.

The instructions with a reference to the FP use the location referred to in the same way as the short P-instructions use < TOS >. As a consequence of this 2-operand P-instructions are the only instructions that are able to use this mode. These instructions were:

Padd, Paddc, Pland, Pband, Plor, Pbor, Pxor, Pdivu, Pdivs, Pmodu, Pmods, Pmultu, Pmults, Ppush, Psub, Psubb, Pcomp.

The index is an offset to the FP and thus are they in "C" or PASCAL references to the local variable space and current parameters from the routine under execution. The size of the index is 8 bits, in signed notation. This makes it possible to address 127 locations in the local frame, and 126 locations in the parameterlist. (The maximum negative number is 128, but the locations -1 and -2 are references to the old FP and return address.)

#### NOTE:

One has to realize that references made with the FP as base register are always to  $\mathbf{QUAD}$  units. Since bits are considered valuable in P-instructions the units of displacement also reference  $\mathbf{QUAD}s$ . This in contrast with F(ull)-operand instructions where the addressing is done in  $\mathbf{BYTE}$  units.

#### **End NOTE**

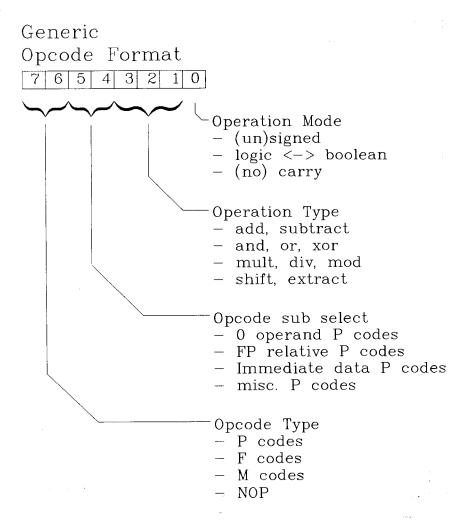

Figure 3.2: The bit assignment for P-opcodes

#### Bit-allocations for the instructions.

There are all in all there 64 instructions in the P-instructionset. This takes 6 bits from the opcode field. If instructions can be aligned on BYTE addresses and opcodes are 8 bits wide then with the remaining 2 bits the indication must be given that the instruction to

## 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

#### P-code instructions

| P-opcode P-opcod | P-opcode | P-opcode |

|------------------|----------|----------|

|------------------|----------|----------|

#### P-code instructions with data field

| Pdata-opcode | Offs. or Imm. |               |               |  |

|--------------|---------------|---------------|---------------|--|

| •••          | Pdata-opcode  | Offs. or Imm. | •••           |  |

|              |               | Pdata-opcode  | Offs. or Imm. |  |

Table 3.4: Several P-opcodes merged into one QUAD.

be used in this opcode is part of the P-instructionset. In figure 3.2 are the bit assignments for the modes depicted, in table 3.4 is show how P-codes are merged into QUADs.

#### 3.2.3 F-instructions.

Are P-instructions targeted towards the optimal use of the onboard stack-cache. The F(ull)-instructionset forms an orthogonal set of instructions with various methods of addressing, referencing and indexing. And this is true for almost all instructions mentioned in the inventory of operations and instructions. The exceptions are those instructions where the operands are of a specific type.

For every operand in an instruction are all possible addressing modes possible, whether this is immediate, indirect or indirect relative.

Relative instructions can use either SP, FP, EFP or < TOS > ( and/or PC ) as the base register.

The registers usable in the register mode are: SP, FP, EFP, PC, < TOS > and Flags. < TOS >, which is not just a short notation for SP[0], gives an automatic update of the stackpointer SP. If the < TOS > operand is used as a operand which is read than the item is popped from the stack. If < TOS > is used as base value in an offset calculation then the base value is left on stack, it has to be removed explicitly. Is the result of the instruction placed in < TOS > then the result is pushed on the stack.

The exception to this rule is a move to < TOS>. In this case there is no operation involved using the first operand, This is the mere destination. The action is corrected and the SP is incremented before the value is loaded on the stack. The old < TOS> value is ,as a consequence of this, kept as < TOS-1>, the new value becomes < TOS>.

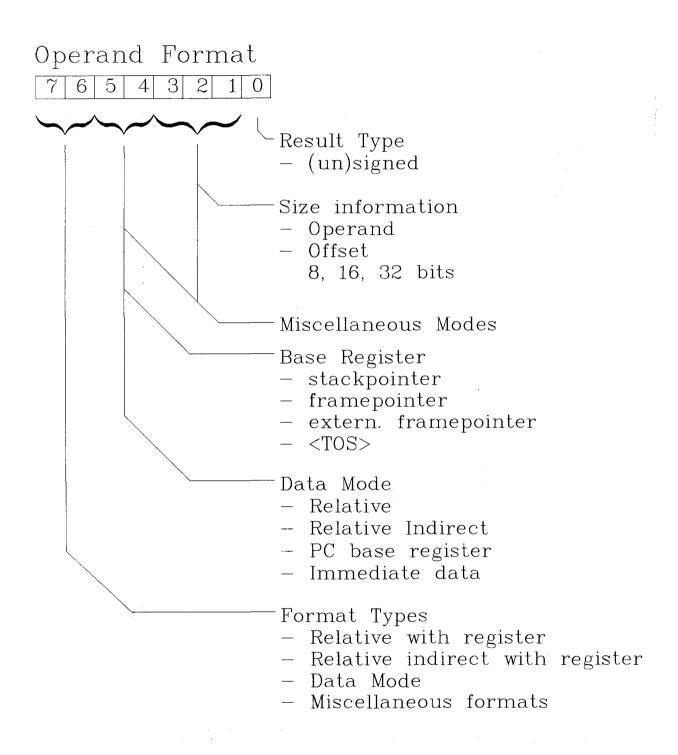

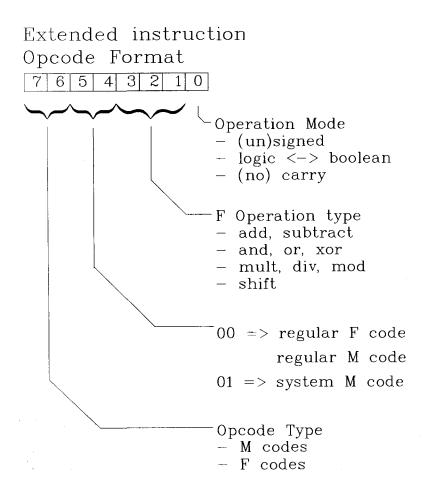

Figure 3.3: The bit assignment for F-operands

#### Opcodes in the F-instructionset.

All F-instructions, arithmetic and logic, can be combined with all variants of the F-operands.

The used arithmetic and logic instructions are:

Fadd, Faddc, Fband, Fland, Fbor, Flor, Fxor, Fcheck, Fcomp, Fdivu, Fdivs, Fmodu, Fmods, Fbnot, Flnot, Fmove, Fshl, Fshrs, Fshs, Fsub, Fsubb, Fselect.

If one visually depicts the bit assignment of an opcode BYTE, it looks like figure 3.3.

Figure 3.4: The bit assignment for F-opcodes

#### F-operands.

The F-instructions are characterized by their large amount of operand types possible. These operands, F-operands, are the key item for the orthogonality of this part of the instructionset.

| The | definition | of an | Instructionset. |

|-----|------------|-------|-----------------|

|     |            |       |                 |

The following section gives a complete list with all possible operands. First are listed all partial components. Next are listed all combinations of the partial components.

#### Addressing modes.

Immediate.

Register.

Direct.

Relative.

Relative Indirect.

#### Result Types.

Signed.

Unsigned.

#### Sizes.

8 bits or BYTE.

16 bits or WORD.

32 bits or QUAD.

#### Combinations of all items.

#### Explanation of the used notation.

"N#IM": $\{s|u\}M$  has the following meaning: an immediate value IM is stored in the codestream, the size of the information is N bits. (N = 8, 16, 32). This value has to be extended to M bits. (signed or unsigned). The resulting value is then used for any operation indicated.

#### NOTE:

Every operation uses a 32-bit intermediate value, this according KER. All operations are converted to 32 bits according to the type of the operand. The resulting value will be truncated in the highest bits to fit into the format of the destination.

#### End NOTE

[\*] is the notation that stands for the contents of memory location \*.

reg[\*] is the memory location addressed by the addition of the register contents and \*.

= Items marked with = are equivalent with another possible format, and are therefor not used.

\* Items marked with \* are not used to keep the number of possibilities with 8 bits.

```

{ Immediate }

"im8":S8

"im8":S16

"im8":S32

"im8":U16

"im8":U8 =

"im8":U32

"im16":S8 =

"im16":S16

"im16":S32

"im16":U8 =

"im16":U16 =

"im16":U32

"im32":S8 =

"im32":S32

"im32":S16 =

"im32":U8 =

"im32":U16 =

"im32":U32

{ Register }

The registers are only usable as a QUAD quantity.

The exception is <TOS> but than this is not a real

register. < TOS> can use all possible formats, but the

results on the stack are always aligned on QUAD addresses.

}

SP:S8 *

SP:S16 *

SP:S32 *

SP:U8 *

SP: U16 *

SP:U32

FP:S8 *

FP:S32 *

FP:S16 *

FP:U8 *

FP:U16 *

FP:U32

EFP:S8 *

EFP:S16 *

EFP:S32 *

EFP: U32

EFP:U8 *

EFP:U16 *

PC:S8 *

PC:S16 *

PC:S32 *

PC:U8 *

PC:U16 *

PC:U32

{ with auto-stack }

<TOS>:S8

<TOS>:S16

<TOS>:S32

<TOS>:08

<TOS>:U32

<TOS>:U16

<flags>:S8 *

<flags>:S16 *

<flags>:S32 *

<flags>:U8 *

<flags>:U16 *

<flags>:U32

{ Direct }

["addr8"]:S8

["addr8"]:S16

["addr8"]:S32

["addr8"]:U8

["addr8"]:U16

["addr8"]:U32

["addr16"]:S8

["addr16"]:S16

["addr16"]:S32

["addr16"]:U8

["addr16"]:U16

["addr16"]:U32

["addr32"]:S8

["addr32"]:S16

["addr32"]:S32

["addr32"]:U8

["addr32"]:U16

["addr32"]:U32

{ Indirect }

[["addr8"]]:S8

[["addr8"]]:S16

[["addr8"]]:S32

[["addr8"]]:U8

[["addr8"]]:U16

[["addr8"]]:U32

[["addr16"]]:S8

[["addr16"]]:S16

[["addr16"]]:S32

[["addr16"]]:U8

[["addr16"]]:U16

[["addr16"]]:U32

[["addr32"]]:S8

[["addr32"]]:S16

[["addr32"]]:S32

[["addr32"]]:U8

[["addr32"]]:U16

[["addr32"]]:U32

{ Relative }

SP["off8"]:S32

SP["off8"]:S8

SP["off8"]:S16

SP["off8"]:U8

SP["off8"]:U16

SP["off8"]:U32

SP["off16"]:S8

SP["off16"]:S16

SP["off16"]:S32

SP["off16"]:U8

SP["off16"]:U16

SP["off16"]:U32

SP["off32"]:S8

SP["off32"]:S16

SP["off32"]:S32

```

```

SP["off32"]:U8

SP["off32"]:U16

SP["off32"]:U32

FP["off8"]:S16

FP["off8"]:S32

FP["off8"]:S8

FP["off8"]:U8

FP["off8"]:U16

FP["off8"]:U32

FP["off16"]:S8

FP["off16"]:S16

FP["off16"]:S32

FP["off16"]:U8

FP["off16"]:U16

FP["off16"]:U32

FP["off32"]:S8

FP["off32"]:S16

FP["off32"]:S32

FP["off32"]:U8

FP["off32"]:U16

FP["off32"]:U32

EFP["off8"]:S8

EFP["off8"]:S16

EFP["off8"]:S32

EFP["off8"]:U8

EFP["off8"]:U16

EFP["off8"]:U32

EFP["off16"]:S8

EFP["off16"]:S16

EFP["off16"]:S32

EFP["off16"]:U16

EFP["off16"]:U32

EFP["off16"]:U8

EFP["off32"]:S16

EFP["off32"]:S32

EFP["off32"]:S8

EFP["off32"]:U32

EFP["off32"]:U8

EFP["off32"]:U16

PC["off8"]:S8

PC["off8"]:S16

PC["off8"]:S32

PC["off8"]:U8

PC["off8"]:U16

PC["off8"]:U32

PC["off16"]:S32

PC["off16"]:S8

PC["off16"]:S16

PC["off16"]:U32

PC["off16"]:U8

PC["off16"]:U16

PC["off32"]:S32

PC["off32"]:S8

PC["off32"]:S16

PC["off32"]:U8

PC["off32"]:U16

PC["off32"]:U32

<TOS>["off8"]:S16

<TOS>["off8"]:S32

<TOS>["off8"]:S8

<TOS>["off8"]:U8

<TOS>["off8"]:U16

<TOS>["off8"]:U32

<TOS>["off16"]:S8

<TOS>["off16"]:S16

<TOS>["off16"]:S32

<TOS>["off16"]:U8

<TOS>["off16"]:U16

<TOS>["off16"]:U32

<TOS>["off32"]:S8

<TOS>["off32"]:S16

<TOS>["off32"]:S32

<TOS>["off32"]:U8

<TOS>["off32"]:U16

<TOS>["off32"]:U32

{ Relative Indirect }

[SP["off8"]]:S32

[SP["off8"]]:S8

[SP["off8"]]:S16

[SP["off8"]]:U8

[SP["off8"]]:U16

[SP["off8"]]:U32

[SP["off16"]]:S8

[SP["off16"]]:S16

[SP["off16"]]:S32

[SP["off16"]]:U8

[SP["off16"]]:U16

[SP["off16"]]:U32

[SP["off32"]]:S8

[SP["off32"]]:S32

[SP["off32"]]:S16

[SP["off32"]]:U8

[SP["off32"]]:U16

[SP["off32"]]:U32

[FP["off8"]]:S8

[FP["off8"]]:S16

[FP["off8"]]:S32

[FP["off8"]]:U8

[FP["off8"]]:U16

[FP["off8"]]:U32

[FP["off16"]]:S8

[FP["off16"]]:S16

[FP["off16"]]:S32

[FP["off16"]]:U8

[FP["off16"]]:U16

[FP["off16"]]:U32

[FP["off32"]]:S32

[FP["off32"]]:S8

[FP["off32"]]:S16

[FP["off32"]]:U8

[FP["off32"]]:U16

[FP["off32"]]:U32

[EFP["off8"]]:S8

[EFP["off8"]]:S16

[EFP["off8"]]:S32

[EFP["off8"]]:U8

[EFP["off8"]]:U16

[EFP["off8"]]:U32

[EFP["off16"]]:S8

[EFP["off16"]]:S16

[EFP["off16"]]:S32

[EFP["off16"]]:U8

[EFP["off16"]]:U16

[EFP["off16"]]:U32

[EFP["off32"]]:S8

[EFP["off32"]]:S16

[EFP["off32"]]:S32

[EFP["off32"]]:U16

[EFP["off32"]]:U32

[EFP["off32"]]:U8

[<TOS>["off8"]]:S8 [<TOS>["off8"]]:S16

[<TOS>["off8"]]:S32

```

```

[<TOS>["off8"]]:U8 [<TOS>["off8"]]:U16 [<TOS>["off8"]]:U32

[<TOS>["off16"]]:S8[<TOS>["off16"]]:S16 [<TOS>["off16"]]:S32

[<TOS>["off16"]]:U8[<TOS>["off16"]]:U16 [<TOS>["off16"]]:U32

[<TOS>["off32"]]:S8[<TOS>["off32"]]:S16 [<TOS>["off32"]]:S32

[<TOS>["off32"]]:U8[<TOS>["off32"]]:U16 [<TOS>["off32"]]:U32

```

For an exact definition of the values assigned to the operand codes, see the appendix with the definition of the instructionset. In this appendix the formats are described as encoded bitfields and a full enumeration of the values and their functionality is given. The figure 3.4 gives however an idea of the bit assignments used for operand formats. In the table 3.5 are examples given of the packing of an F-instruction into the code stream. (This table can be found at the end of the chapter.)

### 3.2.4 M(ixed)-instructions.

A processor needs more instructions types than the instructions explained in detail in the previous sections. This section of the instructionset description covers those instructions that control the flow of the program, maintain the processor status, etc.

The instructions in this collection do not created a neatly organised subset. Every item has its specific operands and operand formats. The only operand format that used more general, is the F-operand. This operand has all the possible forms as given in the section on F-operands.

#### FLOW-CONTROL instructions.

- CALL "high level" function with "C" mechanism.

Instruction format: Mcalle "8U-operand", "F-operand"

The "8U-operand" is a subset of the F-operand, namely all formats which have an 8 bit unsigned integer as a result. (i.e. "im8":U8 or < TOS >:U8). The integer indicates the number of QUADs to be reserved for extra parameter variables on entrance of the function. This space can be used for return values. The local variable space, which is only known inside the function, is created by adding a value to SP. If the value of the second operand is outside its range, this will not result in a system error. One cannot rely on the resulting actions to be reproducible.

The "F-operand" gives the address of the procedure or function to be called.

First the size for the parameter area is added to the SP.

**Next** is the program counter pushed on the stack.

Then the frame pointer is pushed on the stack, and once it is pushed, FP is updated to point to <TOS>. This leaves the framepointer pointing to the first local variable, if needed.

The code in the called routine is now free to reserve any extra space for local variables by adding a value to the SP.

- CALL "high level" function with PASCAL mechanism.

Instruction format: Mcallp "F-operand", "8U-operand"

The "F-operand" gives the address of the procedure or function to be called.

The "8U-operand" is a subset of the F-operand, namely all formats which have a 8 bit unsigned integer as a result. (i.e. "im8":U8 or < TOS >:U8). The integer indicates the number of Quads to be reserved for extra local stack variables on entrance of the function. This space can be used for the local variable space, which is only known inside the function.

First is the program counter pushed on stack.

**Second** is the frame pointer pushed on the stack.

Third is the SP is pushed onto the stack to keep the return address. Parallel with this is the framepointer updated to point to the first entry in the new local variable. Thus under normal operation will FP[0] indicate the first local variable. The last action is the addition of the "8U-operand" to the stackpointer.

- CALL subroutine.

Instruction format: Mcall "F-operand"

This type of call has a strong likeness with the previous calls. The only difference is that no stack-space is allocated for parameter or local variables and thus the FP pointer needs no changes. It is left pointing to the current frame of local variables. Local variables are only created explicitly if the SP is incremented.

- JUMP, GOTO.

Instruction format: Mjmp "F-operand"

The F-operand gives the new address for the program counter to be loaded with.

- Conditional JUMP, GOTO.

Instruction format: Mjmpc "condition", "F-operand"

The flow-control is directed to the address of the F- operand when the given condition shows **TRUE**. Otherwise the instruction following the **jmpc** instruction is executed.

The following conditions can be used:

- Zero.

- Non zero.

- True.

- False.

- Equal.

- Not equal.

- less.

- greater.

- less or equal.

- greater or equal.

- Sign (negative).

- No Sign (positive).

It is not said that all of the above conditions are represented by different flag settings.

- RETURN from "high level" function.

Instruction format: Mretf "8U-operand"

This return can be used for returning from a call in a PASCAL routine and from a call in a "C" routine.

First the 8-bits operand releases the indicated number of QUADs for the local variables.

**Secondly** the FP is restored to the value it had before calling the "high level" function.

Finally program execution is resumed on the address that is found on < TOS>.

These actions leave the stackpointer pointing to the top element in the list with parameters. If these parameters have to be ignored, they have to be removed explicitly by subtraction of the number of nparameters from the stackpointer.

- RETURN from subroutine.

Instruction format: Mret.

Execution proceeds to the address given in < TOS>. The FP remains unchanged.

- RETURN from interrupt.

Instruction format: Mreti.

The execution of an interrupt routine is completed. And the processor returns to the task it was executing when it was interrupted. The stored processor status is retrieved from the stack. - SWAP context.

Instruction format: Mswap "32-address A", "32-address B"

The complete processorstatus is stored in a processorstatus frame given by the absolute address. The new processorstatus is loaded from address B.

- DECRement, TEST and JUMP.

Instruction format: Mdtj "F-operand A", "F-operand B"

De variable addressed by operand A is decremented. If the result of the operation is not zero, control is transferred to the address given by operand B.

- TRAP.

Instruction format: Mtrap "im8" instruction.

Processorstatus is saved on the stack and the interrupt service routine of interrupt "im8" is executed.

#### Processor handling.

- Clear Instruction Cache.

Instruction format: Mcic. Is a valid short instruction.

All valid tags from the instruction cache are cleared.

- Update DATA memory.

Instruction format: Mupm. Is a valid short instruction.

All entry's in the stack-window are flushed to main memory.

- Enable Interrupts.

Instruction format: Menaint "F-operand"

The F-operand contains a mask. All interrupt levels with a 1 in the mask are enabled.

- Disable Interrupts.

Instruction format: Mdisint "F-operand"

The F-operand contains a mask. All interrupt levels with a 1 in the mask are disabled.

- Reset

Instruction format: Mreset. Is a valid short instruction.

The external reset line is asserted by the processor. The internal status of the processor is maintained. Execution continues with the next instruction.

- Halt.

Instruction format: Mhalt. Is a valid short instruction.

The processor ceases to execute the next instruction. All data-, address- and controllines are tri-stated and the HALT line is asserted. The only exit from this state is an external reset or an interrupt on a level that is not masked.

- Lock.

Instruction format: Mlock "count8"

Count8 specifies the number of instructions (or system cycles or clock cycles. This is not yet decided on at this time.) the system busses are locked by the processor. Interrupt handling will also be postponed for this period of time.

For a full description of all instructions and their assigned opcodes is referred to appendix with the instructionset description. Here the complete instructionset is listed with all possible operand values, including the various bitfield assignments.

#### 3.3 Remarks.

Although it was indicated that a more complex type of linked-list operands could prove very useful, this type of operands is currently not implemented. Reasons for this could be the following:

- Definition of the instructionset consumed far more time than expected, and the exact definition of a linked list operand type requires lots of "bit fiddling".

- The linked list operand could be implemented in full extend. This means that all combinations of operands could be possible, and as a consequence of this far to many combinations would be available. However once information is available on indexing methods used or wanted, a more appropriate set of operands could be created.

The currently introduced instructionset has however properties which are not directly obvious at first. For instance the following question ( and answer ) could be discussed: Has the "C"-processor no PC-relative jump?

No! Not in the direct sense that there is an opcode or an operand for this action.

Yes! The instruction Fadd PC, 'operand2' will give a relative branch with the offset given by the value of operand2.

| TO 1 | 1 0        | c     | т .    |           |   |

|------|------------|-------|--------|-----------|---|

| The  | definition | of an | Instri | uctionset | : |

# Table 3.5: Layout of 1-operand FM instruction in the code stream 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

## FM-instruction with 1 Operand

| FM-opcode | Oper1 Format |  | Byte Data |

|-----------|--------------|--|-----------|

|-----------|--------------|--|-----------|

## With 1 Operand of Word Size

|     | FM-opcode | Oper1 Format | <br> |

|-----|-----------|--------------|------|

| ••• |           | Data         |      |

## With 1 Operand of Quad Size

| FM-opcode | Oper1 Format |  |  |  |  |

|-----------|--------------|--|--|--|--|

| Word Data |              |  |  |  |  |

If, however, a relative conditional jump needs to be taken ( or a relative call ), then the matter becomes a little more complex. A construction for this would be to create the new address in < TOS >. And than take the conditional jump with the value in < TOS > as the new address.

It has to be admitted that the last construction is not a very elegant one. But the lacking of this type of operand has become clear only after writing the Software model, and after the implementation of the HHDL models going with the operand unit. If this omission would be considered serious enough, then it could be implemented relatively fast. ( As long as the design is in the High Level design phase ) There are still opcodes and operand formats available. The appropriated codes for these formats have to be inserted in the large case statements in the operand fetchers. ( in the operand unit )

|  | _The | definition | of | an | Instructions | et. |

|--|------|------------|----|----|--------------|-----|

|  |      |            |    |    |              |     |

## Table 3.6: Layout of 2-operand FM instruction in the code stream 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

## 2 Operand FM-instructions

## Without Operand Data

| FM-opcode Operand 1 For | at Operand 2 Format | • • • |

|-------------------------|---------------------|-------|

|-------------------------|---------------------|-------|

## With Operand 1 = Byte, Operand 2 = Byte.

| FM-opcode | Operand 1 Format | Operand 2 Format | Operand 1 Byte |

|-----------|------------------|------------------|----------------|

|           |                  | •••              | Operand 2 Byte |

## With no Operand 1 data, Operand 2 = Byte.

| FM-opcode | Operand 1 Format | Operand 2 Format | Operand 2 Byte |

|-----------|------------------|------------------|----------------|

|-----------|------------------|------------------|----------------|

## With Operand 1 = Word, Operand 2 = Byte.

| FM-opcode | Operand 1 Format | Operand 2 Format | Operand 2 Byte |

|-----------|------------------|------------------|----------------|

| •••       |                  | Operand          | 1 Word         |

## With Operand 1 = Word, Operand 2 = Quad.

| FM-opcode      | Operand 1 Format | Operand 2 Format |        |  |

|----------------|------------------|------------------|--------|--|

| •••            |                  | Operand          | 1 Word |  |

| Operand 2 Quad |                  |                  |        |  |

## With Operand 1 = Quad, Operand 2 = Quad.

| FM-opcode      | Operand 1 Format | Operand 2 Format | • • • |  |  |  |

|----------------|------------------|------------------|-------|--|--|--|

|                | Operand 1 Quad   |                  |       |  |  |  |

| Operand 2 Quad |                  |                  |       |  |  |  |

## Chapter 4

# A first model description of the "C"-processor.

Given the instruction set, defined in the previous chapter, and the first decomposition model, it is possible create a software model. With this software processor model is it possible to:

- Test the designed instruction set and test its functionality. This will give an indication whether the chosen instruction set is applicable for its purpose or not.

- Since this processor is designed to have a data cache of a very special type. The software model would give the possibility of testing the effects of different types of implementation.

Next to these "verification" possibilities the software model also gives information which can be of use in future steps of the design process.

- The software model will give a complete description of the datapath in the processor:

- All operations and manipulations with the variables are clearly visible in the code.

- The parameters communicated between routines give information on variables that are shared between only two routines.

- Global variables are an indication of variables that are used in all routines in the processor and are thus candidates for registers with a separate bus.

- The software model will be able to supply verification material for test runs of the high level implementation of the processor. The software model is currently also able to supply the values that are communicated between the modules. This makes it possible to compare the software modules with the hardware modules on a lower level.

• And as a aid in further designs on the next level, the software design could give guidelines for choosing the decomposition of modules in smaller ones.

#### 4.1 What will the software model not do?

The software model will not, or is not able to:

- Give timing information. None of the actions of the software modules are related to any timing what so ever. As a consequence of this, is it also not possible to detect all action that can be executed in parallel.