| MASTER                                     |

|--------------------------------------------|

| GPU-based rendering to a multiview display |

|                                            |

| Verburg, E.I.                              |

| Award date: 2006                           |

|                                            |

| Link to publication                        |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# TECHNISCHE UNIVERSITEIT EINDHOVEN Department of Mathematics and Computer Science

# GPU-based Rendering to a Multiview Display

By E.I. Verburg

Supervisors:

dr. C. Huizing (TU/e) ir. G.T.G. Volleberg (Philips)

## **Abstract**

This thesis is the result of a project on rendering to a nine-view lenticular display device of two megapixels. We successfully implemented a render engine on a personal computer equipped with a programmable video card.

The render algorithm is based on a technique called micropolygon displacement mapping, which is suitable for generating mutually disparate views. The solution allows for real-time playback of disk-streamed RGBD video sequences. These sources contain both color and depth information at a standard definition resolution.

(This page intentionally contains only one sentence.)

## Summary

This thesis presents a method for real-time rendering to a multiview display device given a 2D video source with depth information. Although the method is suitable for various types of multiview displays, this project specifically targets a nine-view lenticular display. Our implementation uses a personal computer equipped with a programmable graphics programming unit (GPU).

The conversion process from the before mentioned source format to a video sequence that is suitable for a lenticular display can be divided in two steps. First a set of mutually disparate views needs to be generated based on depth, and second, these views have to be merged by multiplexing the appropriate subpixels.

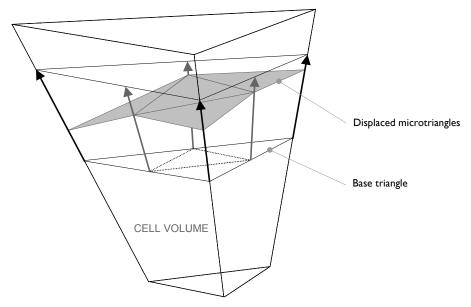

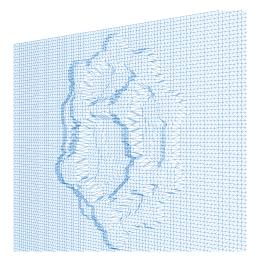

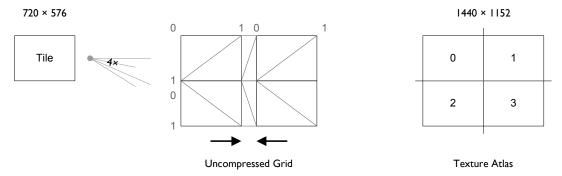

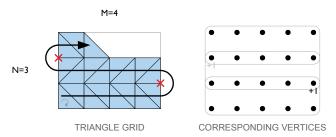

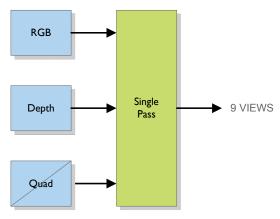

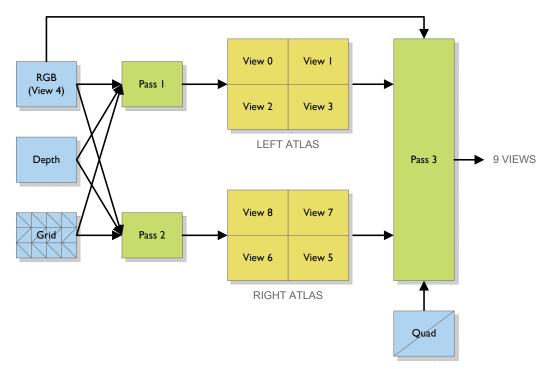

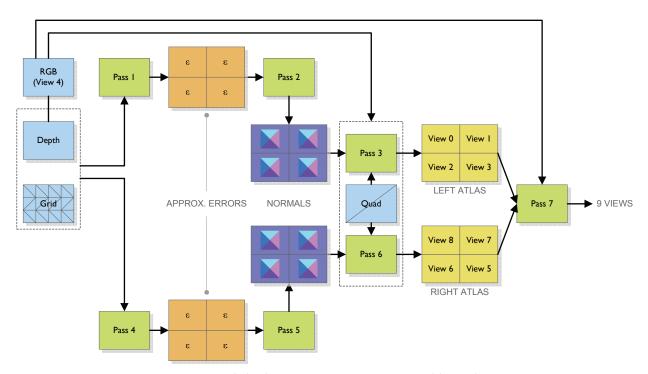

Regarding the first step we adopt a rendering technique called micropolygon displacement mapping to create eight additional views. Traditionally this technique enables feature manipulation of 3D rendered objects. However, we exploit it to generate views which simulate a virtual array of cameras. With respect to the point of view provided by the input video, four cameras represent distinct positions on the left side and the other four represent positions on the right side. The views corresponding to each side are computed in a single rendering pass as follows. First, the vertices of a highly tessellated planar triangle grid are manipulated in z-direction based on the depth map. Each quadrant of this grid is manipulated by a different amount, but receives the same color frame as texture map. A specific orthogonal projection of this textured geometry results in four distinct views with horizontal disparity. This pass mainly involves the vertex shader hardware of a GPU.

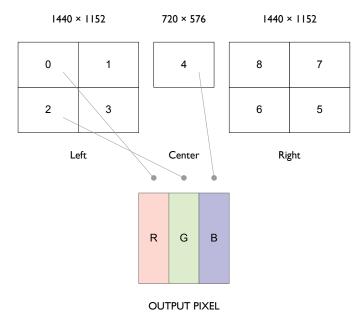

The next step is to multiplex the subpixels of these preprocessed views into a single lenticular image. This step can be mapped conveniently on pixel shader hardware. For each output pixel we determine the view number of the red, the green and the blue subpixel. Given this number we then fetch the appropriate color values from the textures in video memory.

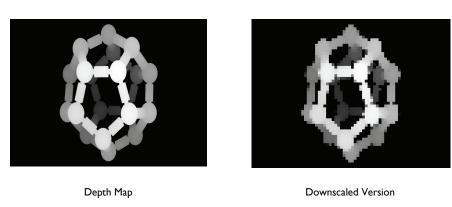

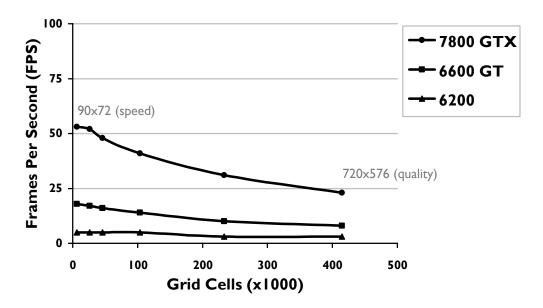

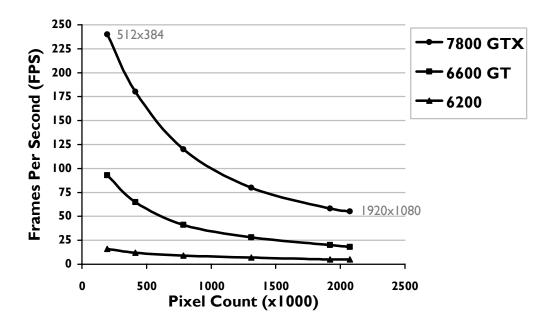

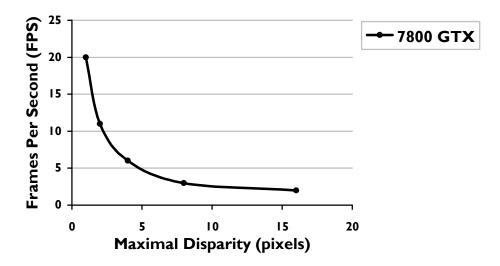

The engine that implements this algorithm for nine-view rendering has been tested on a system with NVIDIA's 7800 GTX graphics processor. It enables a throughput of 25 frames per second at 1920 × 1080 output resolution when using a triangle grid of 692 × 520 cells. The number of cells determines the quality of the perceived depth impression. Ideally this grid would contain twice the number of pixels of an input frame, but the current GPUs are not yet capable of processing larger amounts of data. This undersampling of the depth map does not harm the depth impression much. Occlusions are supported, but de-occlusion areas are only handled by linearly interpolating the colors of the surrounding pixels. Future GPUs will enable higher frame rates or better quality and are likely to support even a higher number of views.

(This page intentionally contains only one sentence.)

# Table of Contents

| Abs | ostract                                                                                                                                                                                                                                                               | 3                                            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Sur | mmary                                                                                                                                                                                                                                                                 | 5                                            |

| Tal | ble of Contents                                                                                                                                                                                                                                                       | 7                                            |

| 1   | Introduction                                                                                                                                                                                                                                                          | 11                                           |

|     | <ul><li>1.1 Project and Assignment</li><li>1.2 Document Structure</li></ul>                                                                                                                                                                                           | 11<br>12                                     |

| 2   | PC and GPU Analysis                                                                                                                                                                                                                                                   | 13                                           |

|     | <ul><li>2.1 PC Architecture</li><li>2.2 Video Cards</li><li>2.3 Brand Specific Technologies</li><li>2.4 Summary</li></ul>                                                                                                                                             | 13<br>20<br>33<br>34                         |

| 3   | Algorithms                                                                                                                                                                                                                                                            | 35                                           |

|     | <ul> <li>3.1 Project Specifics</li> <li>3.2 Overview</li> <li>3.3 Basic Algorithms</li> <li>3.4 Compound Algorithms</li> <li>3.5 Geometry Manipulation and Projections</li> <li>3.6 Lenticular Rendering</li> <li>3.7 Image Filtering</li> <li>3.8 Summary</li> </ul> | 35<br>36<br>37<br>41<br>45<br>51<br>52<br>58 |

| 4   | Concepts and Design                                                                                                                                                                                                                                                   | 59                                           |

|     | <ul> <li>4.1 Introduction</li> <li>4.2 Detailed Design</li> <li>4.3 Ray-Tracing Shader</li> <li>4.4 Micropolygon Based Shader</li> <li>4.5 Improved Displacement Shader</li> </ul>                                                                                    | 59<br>63<br>65<br>67<br>68                   |

| 5   | Implementation                                                                                                                                                                                                                                                        | 70                                           |

|     | <ul><li>5.1 Software Selection</li><li>5.2 Shader Models</li><li>5.3 Shader Languages</li><li>5.4 General Framework</li></ul>                                                                                                                                         | 70<br>71<br>72<br>74                         |

| 6   | Results                                                                                                                                                                                                                                                               | 79                                           |

|     | <ul> <li>6.1 Vertex Processing</li> <li>6.2 Pixel Shading Performance</li> <li>6.3 Image Filtering</li> <li>6.4 Ray-Tracing Results</li> </ul>                                                                                                                        | 79<br>80<br>81<br>82                         |

| 7 | Conclusion               | 83 |

|---|--------------------------|----|

| 8 | Recommendations          | 85 |

| A | ATI Specifications       | 86 |

| В | Matrox Specifications    | 87 |

| C | NVIDIA Specifications    | 88 |

| D | Shader Models            | 89 |

| E | Tabularized Test Results | 90 |

| F | YCbCr to RGB Conversion  | 91 |

| G | References               | 92 |

# Acknowledgement

Hereby, I thank the people who helped me during my graduation in one way or another, especially my mentor Guido Volleberg, who gave me this tremendous opportunity to do a project at Philips Applied Technologies. His continuous enthusiasm and sincerity, I will never forget. I also thank Kees Huizing, Bettina Speckmann and Jack van Wijk from the Eindhoven University of Technology for their time and effort.

And not least of all, let me express my appreciation to my family, friends and colleagues for their support; with whom I got to spend a lovely time and had many invaluable discussions, both professionally and socially. It has been a great experience to work in the field of video processing and even write my first paper in addition to this thesis.

(This page intentionally contains only one sentence.)

### I Introduction

#### 1.1 Project and Assignment

Multiview display devices are emerging, but suitable media sources are still scarce as broadcasters continue to deliver two-dimensional (2D) video. Various conversion algorithms are now being developed in order to provide a three-dimensional (3D) experience from different kinds of media.

On the other hand, programmable graphics processing units (GPUs) have evolved into powerful image processing devices over the last few years. These devices for personal computer (PC) platforms can be used to aid the before mentioned conversion.

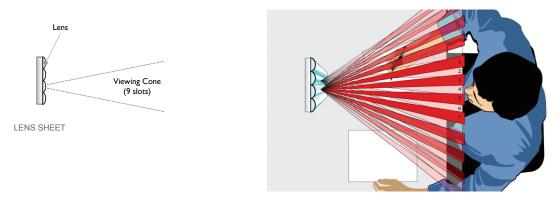

A lenticular display is a specific type of multiview display device. Its name originates from the small lenses contained on the surface of the screen. These lenses redirect each view in such a way that it enables stereoscopic vision without the use of 3D glasses or other headgear.

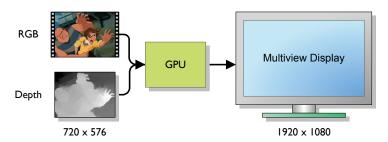

Currently, one operational set-up is built from a personal computer (PC), a Field-Programmable Gate Array (FPGA) and a lenticular display. An FPGA is a programmable logic chip. It is programmed to convert an input signal (RGBD) to an output signal (RGB), which is fed into the lenticular display. RGBD denotes a video stream composed of the colors red, green and blue, and a depth channel. This depth channel stores the relative distances between the camera and the objects being captured, as shown in figure 1.

Due to recent developments in computer graphics hardware the graduation project 'GPU-based rendering to a multiview display' was initiated. A GPU is the primary processor of video cards found in PCs. We designed an algorithm for multiview rendering to a lenticular display and implemented it on such a graphics processor. The resulting application is able to process video in real-time as required. This helps the future development of 2D video to RGBD conversion by enabling faster prototyping of the produced sequences.

**Figure 1.** A programmable GPU processes a video stream containing color and depth information to drive a multiview display device.

#### 1.2 Document Structure

The remainder of this document is organized as follows.

In chapter 2 we describe the parts of the common architecture of both PC and video card that are relevant to our use case. For each component the minimal requirements to sustain real-time video playback are defined.

In chapter 3 we provide an overview of traditional 3D rendering techniques related to texture mapping. The focus is on how these candidate techniques can alter surface details of virtual objects. The discussed techniques form a prerequisite for the design concepts discussed in the next chapter.

Chapter 4 first presents the specifics of multiview rendering. Thereafter two adapted algorithms are presented for multiview rendering; both tailored to the architecture of a programmable GPU. We also propose a method, which enables the detection of the inherent artifacts of the first algorithm.

Chapter 5 discusses topics on GPU programming, such as shader models and shader languages, and describes the software implementation details of our render engine.

The project results are presented in chapter 6 and conclusions are drawn in chapter 7.

Reference material on GPUs, as well as a list of literature, is included in the collection of appendices.

## 2 PC and GPU Analysis

The primary goal of this project is to get a 3D video impression out of a multiview display. Our video sequence only contains frames that describe a single point of view, as captured by a single camera. These input images need to be processed, not just streamed to the display device. This processing results in new images. The creation of such computer images or video frames is commonly called rendering.

This chapter discusses the hardware needed for real-time multiview rendering. Our focus is on personal computers equipped with programmable GPUs.

#### 2.1 PC Architecture

#### 2.1.1 Essential Components

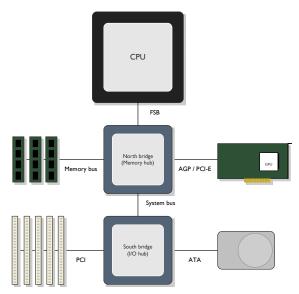

A personal computer (PC) consists of three essential components, which are interconnected as is depicted in figure 2. The essential components are the central processing unit (CPU), volatile memory – also referred to as main memory or system memory – and the video card. The CPU and memory modules are placed on a printed circuit board (PCB) called mainboard or motherboard. Sometimes the video controller is also integrated on this same board.

Computer programs are executed on the CPU and perform calculations on data. Both programs and data are held by main memory. The video card enables visible output. In addition all desktop PCs generally have at least one hard disk, which serves as non-volatile memory. This is where programs and data can be stored (more) permanently.

These PC components are controlled by two additional processors, which are commonly called 'the chipset'. The chipset consists of a Northbridge chip and a Southbridge chip. The Northbridge connects the CPU, main memory and video card(s). The Southbridge masters system input and output (I/O), such as disk drives, and other system buses, for example the Peripheral Component Interconnect (PCI) bus.

Just like the CPU and system memory, the chipset is located on the motherboard. Although playback of video streams involves all of the before mentioned components, we are particularly interested in the data paths between these parts.

**Figure 2.** The architecture of a personal computer consists of functional components and communication buses.

In order to display a video stored on disk, video data must pass various buses and components. During this process video (and audio) data is continuously read from the hard disk. The data passes both South- and Northbridge on its way to main memory.

The CPU generally performs processing on this data. The executed program determines what data is moved to and from the CPU.

Finally, the buffered data is moved from main memory to the video card, which drives a display device. The application software running on the CPU controls the playback process.

Each system part must be able to sustain this relatively large data transfer. The next paragraph defines the bandwidth requirements for playback of such data streams. The subsequent sections discuss the primary tasks and limits of each PC component in detail.

#### 2.1.2 Video Playback Requirements

The playback of video puts a relatively high strain on a computer system. Table 1 summarizes the raw throughput requirements for a few common television standards [1] in megabytes per second (MB/s). The images displayed on a television or computer monitor consist of small colored dots. Such a dot is called a pixel, which is a contraction of the words 'picture element'.

| Active lines | Width | Pixel<br>count | FPS | 4:4:4 | 4:4:4:4 | 4:2:0 | 4:2:0:4<br>(all in MB/s) |

|--------------|-------|----------------|-----|-------|---------|-------|--------------------------|

| 480p (VGA)   | 640   | 307200         | 30  | ~27   | ~36     | ~14   | ~22                      |

| 540p         | 720   | 388800         | 25  | ~28   | ~38     | ~14   | ~24                      |

| 576p         | 720   | 414720         | 25  | ~30   | ~40     | ~15   | ~25                      |

| 720p (HDTV)  | 1280  | 921600         | 25  | ~66   | ~88     | ~33   | ~55                      |

| 1080p (HDTV) | 1920  | 2073600        | 25  | ~149  | ~198    | ~75   | ~124                     |

**Table 1.** The more pixels each video frame hold, the more bandwidth it requires for both storage and transfer. Active lines are the number of visible pixel rows. FPS denotes frames per second, which is the playback rate of motion video.

It is important to distinguish RGB data from RGBD in real-time solutions. The depth channel could be added along the path between disk and video card. It is the responsibility of a component called a depth estimator. Instead, we will be streaming pre-processed video sources that already carry depth information. Our source files use the 720 × 576p format, where 'p' denotes progressive scanning [2]. The final output of the video card is again a RGB signal without a depth channel, though the pixel count likely differs.

In practice video systems always use some form of subsampling. Technicians do not regard subsampling as a compression technique like for example MPEG-1. Over the years various MPEG standards for 'lossy' video compression have been defined by the Moving Picture Experts Group. This project does not consider these compression techniques.

Subsampling saves bandwidth. For example 4:2:2 subsampling packs the luma and chroma channels of each  $2 \times 2$  pixel array into 8 bytes instead of 12 bytes. 4:2:0 uses only 6 bytes for each  $2 \times 2$  array. For subsampled RGBD this results in a lower raw bandwidth requirement of

$$(6 / 12 \times 3) + 1$$

bytes/pixel ×  $(2 \times 10^3)$  pixels × 25 FPS  $\approx 124$  MB/s.

It halves the number of bytes needed for both luma and chroma of the 2D video. The depth information still takes a single byte per pixel. Depth information can be stored in similar way as is often done for the alpha (transparency) channel. In this case the last digit of 4:2:0:4 denotes the sampling of depth in relation to luma sampling instead of alpha.

#### 2.1.3 Hard disk performance

We opt for the highest possible picture quality, thus not using compression or subsampling. Neglecting the fact that we will perform multiview rendering for the moment, a hard disk has to read  $(2 \times 10^3) \times 25 \times 3 \approx 149$  MB/s.

When discussing hard disk performance we need to distinguish internal from external speed. Internal speed is related to physical properties and mechanics of the drive. To be more precise: hard disks read and write using a small local memory buffer to optimize throughput by scheduling. Buffer sizes range from 1 to 8 MB nowadays.

The external speed is subject to the I/O technology used. There exist a few standards on hard disk I/O, which are ATA/ATAPI\*, SCSI† and serial ATA. The interface types determine the maximum throughput between the hard disk cache and system memory. The tables 2 and 3 list the maximum theoretical throughput for existing SCSI interfaces and ATA-varieties.

| Name              | Standard  | Throughput (MB/s) |

|-------------------|-----------|-------------------|

| SCSI              | SCSI-1    | 5                 |

| Fast SCSI         | SCSI-2    | 10                |

| (Fast &)Wide SCSI | SCSI-2    | 20                |

| Ultra SCSI        | SCSI-3    | 40                |

| LVD SCSI          | Ultra-2   | 80                |

| Ultra-160 SCSI    | Ultra-3   | 160               |

| Ultra-320 SCSI    | Ultra-320 | 320               |

| Fast-320 SCSI     | Ultra-640 | 640               |

Table 2. This table lists the maximum theoretical throughputs for existing SCSI interfaces.

\*

<sup>\*</sup> Advanced Technology Attachment Packet Interface

<sup>†</sup> Small Computer System Interface

| Name        | Standard    | Throughput (MB/s) |

|-------------|-------------|-------------------|

| UDMA Mode 0 | ATA/ATAPI-4 | 16.7              |

| UDMA Mode 1 | ATA/ATAPI-4 | 25.0              |

| UDMA Mode 2 | ATA/ATAPI-4 | 33.3              |

| UDMA Mode 3 | ATA/ATAPI-5 | 44.4              |

| UDMA Mode 4 | ATA/ATAPI-5 | 66.7              |

| UDMA Mode 5 | ATA/ATAPI-6 | 100               |

| UDMA Mode 6 | ATA/ATAPI-6 | 133               |

| SATA        | SATA        | 150               |

| SATA        | SATA        | 300               |

**Table 3.** This table lists the maximum theoretical throughputs for existing ATA interfaces. The figure for UDMA Mode 6 was based on a finishing technical standard (see <a href="http://www.serialata.org/">http://www.serialata.org/</a>).

The first serial ATA standard, which is the successor of the (parallel) ATA standard, specifies a maximum theoretical throughput of 150 MB/s. This probably won't suffice for non-subsampled 1080p video streams. However, when settling for less video quality this throughput will do. The same holds for Ultra-160 SCSI.

When video streams are subsampled the bandwidth requirements somewhat lower and some of the picture quality is lost. With a small investment in hardware (e.g. additional drives in a RAID\* configuration) we can overcome the problem of bottlenecking full quality streaming.

For the input stream the PAL standard was suggested. The frame dimensions of PAL video are 720  $\times$  576 pixels. This is sufficient for multiview rendering because  $9 \times 720 \times 576$  is spread over  $1920 \times 1080$ . The purpose of this project is not to investigate how to perform real-time streaming, thus we assume it is possible to stream sequences of this quality, based on the above information. In the FPGA set-up a resolution of  $720 \times 540$  was chosen because height of 540 pixels scales more easily to the 1080 pixels of the lenticular display device.

Our test case will be based on a set of 576p25 source videos. These videos will consume up to 30 MB/s bandwidth, which requires at least UDMA-2. This is no problem because UDMA-5 capable drives are now commonplace. A SCSI-based test system should use at least an Ultra SCSI I/O controller.

It is often suggested that hard disk performance is limited by external factors. It is true that the interface must provide sufficient bandwidth to transfer data to and from the drive. In computer sales the hard disk interface is often stated as ATA/100, ATA/133 or SATA300. These labels are not technically correct according to the specification [3]. ATA (without the number) is the name of the interface standard on parallel communication. The appended number just gives the potential buyer an indication of the maximum throughput. ATA drives are sometimes referred to as EIDE; a term once introduced by hard disk manufacturer Quantum. The specifications are correctly stated as ATA-5, ATA-6 and SATA respectively, but it gives less of a clue. In fact, the external interface does not tell us what the real transfer rates will be. Hard disk performance could as well be limited by internal factors.

For video streams it is important to have seamless playback, e.g. exactly 25 frames per second. This means we are interested in the sustained transfer rate of hard disks. However for desktop systems, which traditionally use less expensive ATA drives, such guarantees cannot be given. Most hard disk manufacturers do provide typical data transfer rates for their ATA products, as is listed in table 4<sup>†</sup>.

A redundant array of independent drives (RAID) improves performance and/or reliability.

<sup>&</sup>lt;sup>†</sup> These lists are compiled from various technical papers and are available upon request.

| Manufacturers   | Model           | Interface | Typical Transfer to/from Media |

|-----------------|-----------------|-----------|--------------------------------|

| Fujitsu         | MPG3204AH       | ATA-5     | 29.6 / 50.8 MB/s               |

| Hitachi/IBM     | HDS725050KLA360 | SATA      | 31 / 64.8 MB/s                 |

| Samsung         | SP2504C         | SATA      | ? / 121 MB/s                   |

| Seagate         | ST-380023AS     | SATA      | 27 / 44 MB/s                   |

| Western Digital | WD2500SK        | SATA      | ≤ 93 MB/s                      |

**Table 4.** This short list shows typical transfer rates for modern hard disks.

More expensive SCSI drive configurations are common in server environments. Drives, like the ones listed in table 5, often perform better and are considered to be more reliable. Because of the differences between SCSI and ATA, the former interface allows multiple drives to operate independently even when connected to the same bus. This improves performance for disk arrays, or state fully redundant array of independent disks (RAIDs). Today, also RAIDs exist based on ATA drives.

| Manufacturers   | Model           | Interface | Sustained Data Rate |

|-----------------|-----------------|-----------|---------------------|

| Fujitsu         | MAU3147NC/NP    | SCSI      | 147 MB/s            |

| Hitachi/IBM     | HUS151414VL3800 | SCSI      | 93.3 MB/s           |

| Maxtor/Quantum  | Atlas 15K II    | SCSI      | 98 MB/s             |

| Seagate         | ST936701        | SCSI      | 63 MB/s             |

| Western Digital | WD740GD         | SATA      | 72 MB/s             |

Table 5. These best-of-class of hard disks are more likely encountered in server environments.

Most ATA-6 drives are able to stream subsampled video at SDTV resolution under optimal conditions. However, operating systems are likely to interrupt disk reading from time to time to allow other processes to access this shared resource. Uninterrupted playback also depends on a streaming-friendly file format, which will keep disk seeks low.

System characteristics such as time sharing and the sharing of hardware resources are not available to the public. This makes it difficult or even impossible to predict whether a system can prevent frame drops while playing a video. An actual PC is needed to prove that a real-time application will perform as expected. Even internal hard disk characteristics matter. By design, not all sectors of a hard disk can be read equally fast. It is wise to use some performance margin. Margins of 25% or 50% are not uncommon.

The listed hard disks read at speeds of at least 27 MB/s. When the system is dedicated to play and process video streams and the operating systems intervenes as little as possible, there's a good chance that the modern PC is able to sustain the playback at 576p (4:2:0 subsampled).

For HDTV most single disk configurations are currently insufficient. A RAID can be used to increase the data throughput. More disks can be added to the communication channel until its bandwidth is saturated. 720p requires two or three disks for both SATA and SCSI systems. Each drive must be able to transfer 17 MB of data per second. 1080p requires at least an array of three fast drives, each of which is able to sustain 25 MB/s. Most drives will be suitable, even with a reasonable performance overhead.

We can play a subsampled 576p video stream using a single drive. This is the configuration that we initially chose. We conclude that it is possible to assemble a disk array, which is able to handle broader streams. It is not our primary concern to put this to the test, as long as we know it does not limit our rendering tests.

#### 2.1.4 System Bus: North- and Southbridge

The Northbridge and Southbridge make up the core logic chipset on the motherboard. The Northbridge chip typically handles communication between CPU, system memory and the video card. Whereas the Southbridge handles the system I/O.

These two chips are separated because of design and fabrication complexity. These two parts could as well be integrated in future designs. For now, the chips are linked by a high-speed interconnect. All video data from disk is passed over this communication path. On older chipsets this link formed a bottleneck, especially in application of high definition video sourced from disk or another PCI peripheral. Today's chipset bandwidth of 1 gigabyte per second (GB/s) exceeds this bandwidth requirement by far.

#### 2.1.5 System Memory Speeds and Bandwidth

The set of available memory types has exploded over the last years. This makes it harder for consumers to select the right parts. Today, DRAM modules exist in various speeds denoted as for example PC2700, PC3200 for SDRAM and PC-800 for RDRAM. The latest memory technologies include double data-rate (DDR) and Rambus\*, the latter that Intel licensed in late 1996 for its motherboards. We won't go into the details of these memory types and technologies, but we are interested in its bandwidth characteristics.

At the moment of investigating the hardware, we did not know exactly what the bandwidth requirements are for depth estimation and its rendering. A precise specification of memory read and writes is needed for that. But we can estimate the order of magnitude for this requirement. Depending on the number of (sequential) processing steps on each video frame, one, two, three or perhaps ten read-writes are needed in system memory, before the data is passed on to the graphics card. Luckily, (cache) memory speeds already go up to about 35 GB/s. However, a relatively high locality or reference is assumed. It means that caches are only suitable in the situation where memory addressing is highly coherent.

Let's assume video processing perform one hundred processing steps on complete high definition video. This will consume a lean  $100 \times 2 \times 2 = 400$  MB/s of bandwidth. The peak bandwidth for the older PC2100 DDR memory is 266 MHz  $\times$  8 bytes = 2.1 GB/s. Thus, very inefficient video processing on the CPU is unlikely to be limited by the speed of system memory. Table 6 lists other relevant memory bandwidths in different parts of computer systems.

| Component                          | Bandwidth |

|------------------------------------|-----------|

| GPU Memory Interface               | 35 GB/s   |

| PCI Express Bus (×16)              | 8 GB/s    |

| CPU Memory Interface (800 MHz FSB) | 6.4 GB/s  |

**Table 6.** This table, taken from GPU Gems 2 by Matt Pharr et al., ch. 30, p. 472, lists typical bandwidths of PC components.

#### 2.1.6 CPU and the FSB

The front side bus (FSB) is the data bus that connects the CPU to the rest of the system. The frequency of the FSB determines the external speed of the CPU. Modern motherboards feature a 166 or 200 MHz FSB and the communication is double or quad pumped. This technique exploits the both rising and falling edges of the base clock signal. The tightened timing allows for twice or four times the data rate.

<sup>\*</sup> More on the memory interfaces of Rambus Inc. is available at http://www.rambus.com/

CPUs often use an internal clock multiplier to run the processor at the right speed. I.e. an Intel P4 660 processor runs at 4 (pumped)  $\times$  200 (FSB)  $\times$  8 (internal clock) = 3,600 MHz.

#### 2.1.7 Video Buses

During playback a video stream is normally passed to a graphics cards once. The data again passes the memory bus twice – the second time in reversed direction – and then passes the video bus. Today, most motherboards either contain an accelerated graphics port (AGP) or PCI Express (PCIe) bus [4]. In case of an older PCI video card the data is passed back over the North- and Southbridge, instead of using the designated video link.

Before dedicated video buses were designed PCs were limited in graphics performance. Buses like VESA\* local bus (VLB) and PCI could not deliver high-resolution video or complex 3D graphics without latency or frame drop. PCI is based on a 66 MHz clock. The inferior VLB was clocked at 33 MHz and 32-bit wide.

Since the Intel Pentium II generation, motherboards were designed with a single accelerated graphics port (AGP). This bus allowed faster reads from and writes to main memory, which was typically exploited to extend the video memory of graphics boards.

PCIe is the successor of the AGP. It is a new serial I/O technology, compatible with the current PCI software environment. The open industry standard exists since 2004 and is managed by the special interest group PCI-SIG<sup>†</sup>, which was formed 1992 and became non-profit in the year 2000. PCI-SIG is also responsible for the conventional PCI and PCI-X standards.

The initial PCIe documentation consisted of two parts; the base specification and the card electromechanical specification. Version 1.0 of these specifications was released in July 2002. In June 2003, after a period of enablement, compliance and PCI-SIG member reviews, the mini card electromechanical specification became available. A low-power addendum was released in September of that year to support the mobile (graphics) industry.

According to the base specification the PCIe (×16) peripheral connector should be colored black or at least a color different from PCI, which should be white. Still, the PCIe slots can be recognized because are positioned farther off the edge of the main board than PCI slots do.

In table 7 and 8, we summarize the bandwidth properties of the AGP and PCI Express interface. All speeds are expressed in MB/s.

| AGP Multiplier | MHz | Theoretical Bandwidth | Actual Peaking |

|----------------|-----|-----------------------|----------------|

| 1×             | 66  | 266                   | 264            |

| 2×             | 133 | 533                   | 528            |

| 4×             | 266 | 1066                  | 1056           |

| 8×             | 533 | 2133                  | 2112           |

**Table 7.** Both the maximum theoretical and the actual bus speeds depend on the AGP multiplier. This multiplier determines the clock frequency of the communication bus.

-

The Video Electronics Standards Association website is located at http://www.vesa.org/

<sup>&</sup>lt;sup>†</sup> The PCI-SIG industry organization website is located at http://www.pcisig.com/

| PCIe Lanes  | Theoretical Bandwidth | Actual Peaking |

|-------------|-----------------------|----------------|

| ×1          | 250                   | 237            |

| ×16         | 4000                  | 3800           |

| <b>×</b> 32 | 8000                  | 7600           |

**Table 8.** PCI Express connections can use one or more lanes. This table lists the bandwidth properties for a few exemplary lanes configurations.

AGP's writing speed was much slower than its reading speed. The newer PCIe architecture features a set of communication lanes. These lanes allow transfers in both directions at similar speed simultaneously. This is the main reason why this new technology is superior to AGP.

PCIe is designed as local point-to-point connection, rather than a shared bus. Its implementation is based on the same programming concepts and communication standards as the vintage PCI. Board manufacturers need only change the physical layer of their cards to make them compatible with PCIe [5]. These devices must support single-lane (×1) links. However, to increase throughput over 237 MB/s the device must transmit its data over multiple lanes.

The PCIe standard defines ×2, ×4, ×8, ×12, ×16 and ×32 lane configurations, which provides up to 8 GB/s theoretical bandwidth. The physical bus sizes for each lane configuration differ. PCIe provides each device with a dedicated data pipeline, unlike PCI devices that shared their communication bus.

PCIe's data transmission is interleaved or what is called striped in the specification, which means that each successive byte is sent down successive lanes. This makes data synchronization more difficult on the receiving end, but increases throughput.

Like other high-speed serial interconnect systems, PCIe does have a significant protocol and processing overhead. Long continuous unidirectional transfers can approach up to 95% of its raw data-rate. The actual peaking column for PCIe bandwidth, shown in table 8, is calculated using this percentage.

We conclude this section with the remark that both AGP and PCIe suffice for our video application. It is unlikely that we need to pass back data from video memory for multiview rendering.

#### 2.2 Video Cards

#### 2.2.1 Overview of Internals and Connectivity

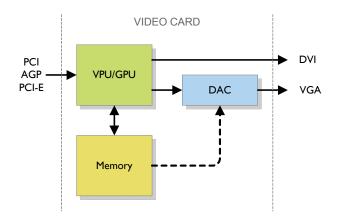

As shown in figure 3, all video cards contain the following essential components: a graphics processing unit (GPU) – sometimes referred to as video processing unit (VPU) – video memory and at least one output port, to which a display device is connected. Some video cards have an analog output such as the analog video graphics array (VGA) output. These require a digital-to-analog converter (DAC), which repeatedly reads the picture, stored in video memory and converts this data to the analog video signal.

**Figure 3.** The video processing unit (VPU) or graphics processing unit (GPU) receives data over a communication bus. This processor interacts with onboard video memory and sends its output to DVI or VGA.

Video cards contain far more features than just writing to video memory and the subsequent 2D output to an analog or digital display device. In fact, we are particularly interested in the details of GPUs and memory of video cards. The following paragraphs give insight in what has changed on these cards over the years.

#### 2.2.2 Graphics Hardware Evolution

Early computer graphics was limited to 2D vector graphics, where lines were drawn one after the other on the screen using coordinates. Later 2D raster graphics hardware emerged. Raster graphics allow each element of the screen (pixel) to be written to individually. Most importantly, this enabled graphical user interfaces.

In the beginning 3D applications used software rendering, which means that all render stages are mapped onto the CPU. Geometry transformations and lighting are computationally expensive. The first 3D graphics boards could handle vertex processing. Later boards accelerated rendering by means of a hardware transform and lighting (T&L) engine. Graphics processing partially moved from the CPU to the GPU [6]. On August 31, 1999 NVIDIA launched world's first programmable graphics unit, the GeForce 256. The GeForce was the first GPU to feature hardware T&L, but processing was still limited to vertex computing. ATI responded at Microsoft's WinHEC\* in April 2000 with their Radeon chip.

New video cards brought a change to the inflexibility of the fixed-function pipe (explained in paragraph 2.2.3). In February 2001, during Intel's Developers Forum in San Jose, NVIDIA introduced the GeForce 3 for the PC platform [7]. The GeForce 3 included the same core technology as used in Microsoft's Xbox game console. It was the first programmable GPU that included a fragment processor [8]. Combined with Microsoft's shader model version 1.1 included in DirectX 8, it allowed customization of the render process by loading small programs – called shader programs – onto the graphics chip. The first programmable GPUs on the market had a separate fixed-function pipe and programmable pipe. The current trend is towards a more integrated solution.

In February 2002 the GeForce 4 was introduced, which added a new anti-aliasing technique<sup>†</sup>, improved occlusion culling, 4:1 Z-buffer compression and better support for multiple displays.

By the end of November 2002, NVIDIA launched the FX series [9]. These GPUs series added vertex and geometry displacement support and 128-bit color precision; being 32-bits for each component of

<sup>\*</sup> WinHEC is Microsoft's annual Windows Hardware Engineering Conference.

<sup>&</sup>lt;sup>†</sup> The 2×, 4×, Quincunx<sup>™</sup> and new 4×S anti-aliasing techniques were marketed as Accuview.

RGBA. The new GPUs were specifically designed for shader model 2.0. Next, the various components found on these video cards are discussed in order of the graphical rendering pipeline.

#### 2.2.3 Rendering Pipeline

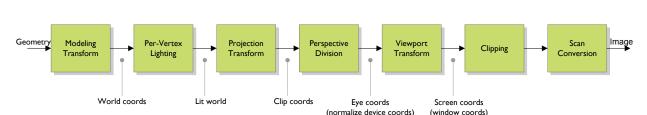

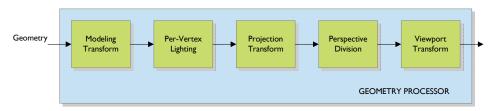

The rendering pipeline is a system that produces computer imagery out of 3D geometry, textures and other data. Computer graphics artists create virtual worlds called scenes. These scenes typically include 3D models, light sources and at least one camera. The calculation of the final image as seen from the camera is a complex task. It is handled by a dedicated system; the rendering pipeline. Figure 4 depicts the various stages of the classic fixed-function rendering pipeline [10].

FIXED-FUNCTION RENDERING PIPELINE

**Figure 4.** The fixed-function rendering pipeline consists of processing stages which convert geometry and other graphics data into output images.

In the rendering pipeline all geometry from the 3D scene is converted from model space to world space, lit, clipped and results in primitives defined by screen coordinates. Objects in 3D scenes are constructed from a set of points in space called vertices. These vertices determine the surface of the object. Most often triangles are used. These primitives interconnect exactly three points.

The modeling transform converts all vertex coordinates from modeling space to world space. For basic illumination one must at least calculate the amount of light that is incident at a triangle. This concept is called flat shading. Another solution is to determine the light at each vertex. This pervertex lighting takes into account the amount of light received from each light source in the scene. It results in a lit world. (More information on rendering algorithms is found in chapter 3.)

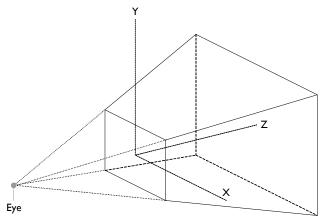

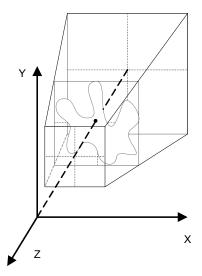

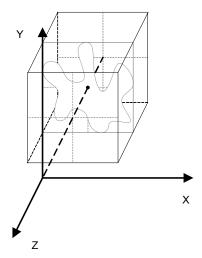

The projection transform limits the 3D space to what is called the viewing frustum. The viewing frustum is a 3D volume that defines which (parts of) polygons are removed and won't be visible in the final 2D picture [11]. The removal is called clipping. Practical bounding volumes are either box-shaped or a truncated pyramid. Figure 5 shows an example of such a volume.

**Figure 5.** The viewing frustum for a perspective projection defines the visible volume of a scene. The viewing direction is along the z-axis.

The pyramid shaped volume represents the part of the scene that is visible from the camera's point of view. The six clipping planes of the volume are called 'left', 'right', 'top', 'bottom', 'hither' and 'yon'. The hither plane is the perpendicular plane closest to the eye. Yon is the farthest perpendicular plane. Often the hither plane corresponds to the viewport plane, but this need not be the case [12].

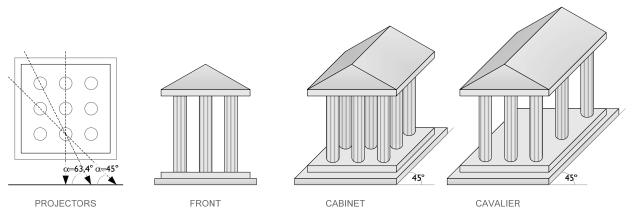

The perspective division makes objects appear smaller when they lie farther away from the viewpoint. It creates the illusion of depth. Stepping over this computational stage creates an orthogonal view. Orthogonal views have no point of view, e.g. when viewing the xy-plane from the front, there is no perspective correction along the z-axis.

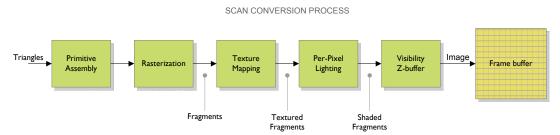

The viewport transform converts eye coordinates to screen coordinates. These coordinates still have a z-component. In the next stage all vertices that lie out of the defined view port are clipped. Clipping uses linear interpolation to break off triangles at the border of the view port. The remaining triangles and other primitives are passed on to the scan converter. Figure 6 shows the stages that are part of the scan conversion process.

**Figure 6.** The stages of the scan conversion process translate triangles and other geometry into an image which is stored in the frame buffer.

The primitive assembly combines the triangles, lines and points of the scene. The rasterizer creates one of more fragments from each primitive. Such a fragment can be regarded as a pixel, but fragment is technically a more correct name as multiple fragments can make up a pixel's color. For example, a red and a green fragment can be blended to make up a yellow pixel of a particular frame.

Triangles can have an associated texture map and texture coordinates. The texture mapping stage performs a texture lookup and assigns the right color in case of such a textured fragment. More realistic illumination models take the amount of light for each pixel into account, and do not just depend on the interpolate vertex values from the rasterizer. In a typical 3D scene some parts of the object's surface could be in shade. The per-pixel lighting stage performs shading calculations for each fragment. The visibility stage uses the depth information stored in the Z-buffer to determine whether or not the fragment must be written to the frame buffer.

In the past these rendering stages were hard-coded. One could send in all data of the 3D scene and the subsequent processing was managed by the pipe itself. Post-processing the rendered images was the only enhancement it allowed. Typical post-processing effects in 3D animation include depth-of-field, glow and motion blur.

#### 2.2.4 Programmable Architecture

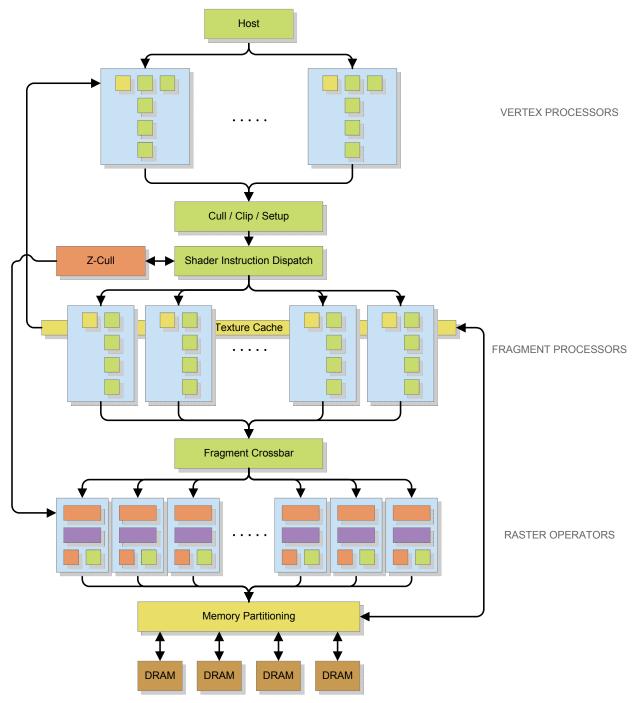

Figure 7 is an example of a modern GPU architecture. It gives an overview of the components that are described next. From top to bottom, it shows the various vertex- and fragment processors, followed by the raster operators, which write the calculated pixel values to video memory.

Figure 7. The processing of modern programmable GPUs can be divided in three stages being vertex processing, fragment processing and raster operations. Each stage consists of multiple pipelines that execute in parallel.

Two of the most important differences among GPUs are the number of vertex- and pixel units. Performance depends on the capabilities of these processing units and also depends to a large extent on processor timings and memory speeds. These units have capabilities conform a specific shader model, although implementations may differ among brands. Details can be found in appendices A through C\*. Shader model requirements are listed in appendix D.

Core and memory speeds are not included in the appendices because they differ among brands.

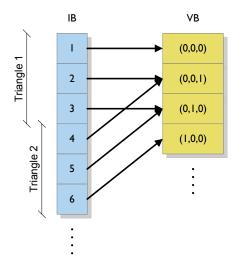

#### 2.2.5 Vertex Buffer

The vertex buffer (VB) stores the geometry of the 3D scene. It holds all 3D coordinates and the index buffer (IB) determines which vertices belong to each polygon. Traditionally video cards process polygons as triangles. Triangles are flat surfaces determined by its three corner vertices. This simplifies design and increases throughput of video cards.

In case more complex geometry is sent down the graphics pipeline, the shape is broken down in appropriate triangles. This process is called tessellation.

The index buffer is used to compress vertex buffer data. As depicted in figure 8, this list holds three pointers to locations in the vertex buffer to make up a specific triangle. Without an index buffer the vertex buffer would have to contain duplicate vertex coordinates for adjacent triangles. This is undesirable, thus indexing is often used in practice [13].

Figure 8. The index buffer (IB) lists pointers to data stored in the vertex buffer (VB).

Vertex- and index buffers can be used on all video cards that perform 3D rendering; regardless of whether it uses a fixed-function or a programmable pipe.

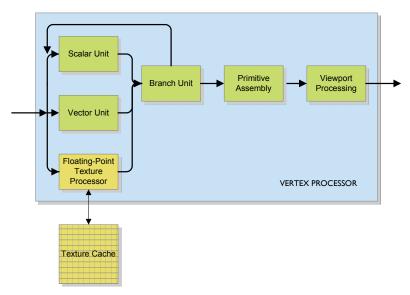

### 2.2.6 Geometry/Vertex Processor

The first stages of the fixed-function pipeline are part of the geometry processor (figure 9), sometimes referred to as vertex processor or vertex shader – as it computes vector coordinates and scalars.

**Figure 9.** The rendering stages of a geometry processor handle various transformations and lighting of vertex data.

The primary task of the geometry processor is transformation and lighting (T&L). The coordinates of the input geometry are expressed in model space. These coordinates need to be converted in several steps into projected 2D screen coordinates. The lighting value at each vertex is also computed during this process. The per-vertex data will be interpolated in the rasterizer stage. The geometry processor passes its output to the scanline converter.

Modern video cards do not use scanline conversion. Instead a vertex processor (or vertex shader) passes its data to a rasterizer. The rasterizer converts all triangles into fragments (pixels). The following list shows the tasks of a vertex processor [14]:

- 1. Vector & scalar processing

- 2. Primitive assembly

- 3. Backface culling

- 4. Clipping

- 5. Perspective division

- 6. Viewport transform

- 7. Triangle setup

The first stage converts all coordinates from model space to world space. Not only 3D models can be sent into the rendering pipeline. Also, basic shapes such as lines and points can be inserted. The primitive assembly combines these different input entities. The following stages are strictly relevant to geometry.

Back face culling is the removal of triangles, of which the surface normal points away from the viewer and need not be rendered. Next, triangles that lie outside of the viewing frustum are clipped.

The viewport transform changes world space coordinates into viewing space coordinates. The triangle setup combines the coordinates to construct triangles according to the information in the index buffer. These geometry processor steps result in a set of the visible and lit triangles, ready to be scanconverted.

Vertex shaders as found on modern GPUs serve the same purpose as the traditional geometry processors, but allow customization of the processing. Vertex shaders can be loaded with vertex programs, which specify how transformation and coloring at vertices is done.

The minimal feature set of shader hardware is specified by a shader model. These shader models are maintained by Microsoft (see appendix D). Newer vertex processors that are 'shader model 3' [15] compliant have the ability to fetch additional data from the texture cache. This feature is called vertex texture fetch. It enables a larger set of shader constants to be loaded in the vertex processor using so-called vertex textures. The operation is considered as rather expensive, but it can be used to implement look-up tables.

Vertex programs of shaders are limited in the number of instructions. Newer GPUs support larger shader programs. Today's vertex hardware can process up to 750 million vertices per second.

Figure 10. Modern vertex processors contain a set of dedicated computational units and have access to video memory via the texture cache. This diagram was based on GPU Gems 2 by Matt Pharr et al., ch. 30, p. 475.

The left-most units, of the vertex processor in figure 10, can perform calculus on specific data types such as scalars, vectors and texture coordinates. Selection instructions are handled by the branch unit. The computation for duplicate vertices is only performed once conform the list held by the vertex buffer. The primitive assembly reconstructs vertices into triangles according to the index buffer. Finally, all coordinates are converted to screen space including its z-component.

The total instruction count supported by GPUs varies. Minimal performance requirements and features are also specified by the shader model documentation, managed by the Microsoft Corporation. For example, GPUs conform shader model 3.0 must support at least 512 instructions. Some video cards already support 65,536 dynamic instructions. This means the hardware is able to determine whether instructions need to be executed to get the correct output. Instruction that do not affect the output will not get executed. This saves resources and time.

#### 2.2.7 Rasterizer

The rasterizer translates triangles into pixel space. The algorithm basically loops over all triangles and determines what pixel on the raster it colors [16]. Traditionally, this raster was either the frame buffer or the back buffer in case of double buffering. On shader hardware the fragments can also be fed to a fragment pipe for further processing.

#### 2.2.8 Shader Instruction Dispatch

On GPUs the rasterizer stage is implemented as a shader instruction dispatch. It manages the instruction decoding and scheduling of the shader at a hardware level and passes the fragments into one of the pixel shaders [17]. The shader instruction dispatch should keep all fragment shaders busy for maximal performance.

The shader instruction dispatch is also responsible for filtering the input by means of a technique named Z-culling. Z-culling excludes each invisible fragment from further processing by one of the fragment shaders. The filtered fragments are not sent further down the graphics pipe.

### 2.2.9 Z-Buffer

On 3D graphics hardware the Z-buffer is used to store per-pixel depth values of the projected scene. The buffer values determine if objects are occluded or visible, from the user's perspective. If occluded, pixels need not be rendered again. This greatly reduces the rendering cost of 3D scenes.

The precision of the Z-buffer is normally 16 or 24 bits. 16 bits granularity can result in visual artifacts when objects are positioned too close to one another. 24 bits provides better scene quality [18]. A stencil buffer often accompanies the Z-buffer.

### 2.2.10 Stencil Buffer

The stencil buffer is a non-displayable bit-plane, similar to the depth buffer. It determines which rasterized fragments must be excluded from a following rendering pass. An engineer can design tests and tag certain areas that need special rendering. This stenciling is an extra per-pixel test and a set of update operations that are closely coupled with the depth test [19].

This technique can be used for masking or rendering shadow volumes and reflections, without referring back to pre-calculated maps [20]. For example, an 8 bit stencil buffer could be exploited to render shadow projections of a scene with eight shadow casting light sources in a secondary pass. One, four and eight bits are the most common stencil buffer configurations.

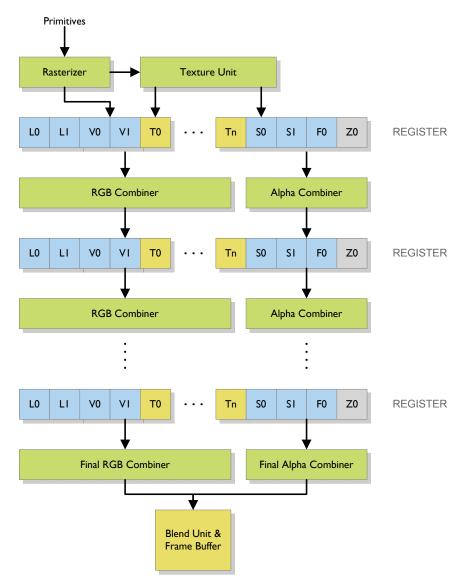

#### 2.2.11 Register-Combiner Architecture

The first programmable video cards featured new vertex processors, which could compute geometry transformations and per-vertex lighting (see paragraph 2.2.2). The rasterizer and scanline stages were left untouched. Initial fragment processing could only be performed conform a rather strict model. Later, pixel shaders evolved from this same model.

Figure 11 describes the structure of what is called the register-combiner architecture. This name stems from the two building blocks that make up the processing pipe. One is the register block. This memory unit stores the values being processed. The other is the combiner, which performs the arithmetic on these values.

**Figure 11.** World's first register-combiner architecture consisted of a rasterizer, texture units followed by two pipelined register~ and combiner stages. The results could be written to the blend unit or frame buffer.

The register element can store vectors, colors and texture coordinates. Each element has an associated name based on the type of information it should hold. For example, v# are input registers, s# are texture samples and t# store texture coordinates. The number of registers available to the programmer increased each generation of GPUs. Now, these registers are exposed as variables in the various high-level shading languages.

The combiner performs mathematical operations. It reads values from several registers, operates on these values and writes the results to the next register-block [21]. Each combiner enables the computation of two dot products, or an add/multiplex operation, and a scale/bias. A combiner contains two dot/multiply units and one add/multiplex unit to accomplish this. Such a unit can be instructed to perform either one of the operations on its input, not both.

The RGB and Alpha combiners operate in parallel. The fragment pipeline consists of one or more register-combiners. The final combiner writes to the frame or back buffer. NVIDIA's first-generation GeForce design allowed two register-to-register instructions. It also featured a read-only register (Z0) and two global constant registers (C0 and C1). As of the GeForce 3 the constant registers were

changed into more flexible per-stage registers (L0 and L1). The register-combiner concept was extended to a programmable fragment processor.

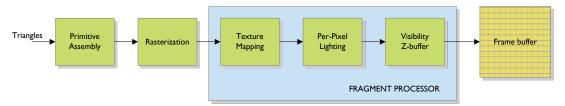

#### 2.2.12 Fragment Processor

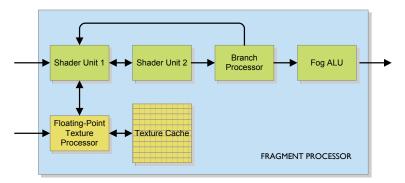

The fragment processor is also named a pixel shader. These processors can be loaded with small programs called pixel shader programs, which are executed in parallel to speed up the process. Each pixel shader receives per-fragment data like color and alpha, processes it and writes the result to the frame buffer or render target. The pixel shader has access to texture memory, but can also perform fogging, stenciling and alpha blending. Figure 12 shows three important stages of the rendering pipeline that can be customized though the use of fragment programs.

**Figure 12.** Pixel processing by the fragment processor encapsulates texture mapping, the per-pixel lighting and a visibility stage.

Not all fragment processors are designed the same, but they do share a few commonalities. Inside a fragment processor one or more shader units execute the instructions of the loaded fragment program. At least one shader unit can perform a texture look up from a local cache or texture memory. An (optional) texture floating-point processor handles the texture-filtering math.

As of shader model 3.0 branching operation are allowed. The branch processor handles this. The Fog ALU can blend per-pixel fog. Figure 13 shows an example of the fragment processor as can be found on NVIDIA's GeForce 6 series GPUs.

**Figure 13.** The fragment processor determines a fragment's color using a set of computational units as well as a texture processor which has access to video memory. This figure is based on GPU Gems 2 by Matt Pharr et al., chapter 30, page 476.

The number of fragment processors determines how many fragments can be processed simultaneously. Because of the parallel execution model, no interdependence of fragments is allowed among output values. Most cards do have multiple texture samplers, so the shader can combine multiple inputs, but such gathering algorithms are potentially slow. One of our experimental algorithms took over 100 samples (e.g. a 10 × 10 kernel) per output pixel. It proved that such an approach severely hampers performance. Similar results were obtained from our ray-tracing shader, which is described in section 4.3.

As mentioned before shader model 3.0 prescribes 512 GPU instructions as a minimum. The previous shader model (2.0) was limited to 96 instructions, being 32 texture plus 64 arithmetic instructions. More details are found in appendix D.

#### 2.2.13 Raster Operators

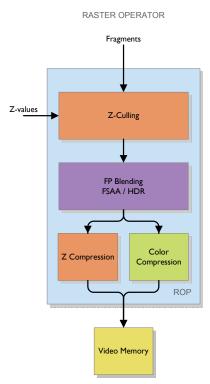

The raster operators (ROPs) are part of the pixel pipeline. The fragment crossbar sits between the pixel shaders and the ROPs, so it can distribute the output of each shader to the appropriate ROP. The ROP itself performs comparison operations – like Z-culling or custom stenciling – and enables (alpha) blending and anti-aliasing of pixels in the frame buffer or render target. Some ROPs feature color and/or Z compression, like the one depicted in figure 14.

Figure 14. Modern raster operators (ROPs) perform culling, blending and anti-aliasing or high dynamic range (HDR) lighting. Some ROPs can do compression to save on video memory.

Certain video cards feature less ROPs than they have pixel shaders. This saves transistors without severely bottlenecking performance [22]. For example, NVIDIA's 6800 has 12 or 16 ROPs, depending on the specific model, whereas the 6600 has 8. The conventional GeForce 6200 has four raster operators and the TurboCache (TC) version of this card has only two.

Current GeForce 6 series video cards can do either full scene anti-aliasing (FSAA) – via multisampling – or high dynamic range (HDR) rendering, but not both. This is because both techniques depend on the floating point blending stage. Multisampling takes samples at two or more locations within each pixel and determines how much of it is covered by the primitive being drawn. If a pixel is only partially covered, the resulting color will be a weighted blend of the primitives' color and the background color.

NVIDIA's GeForce 6200 does not support color compression and Z compression. This will limit performance in cases such as 64-bit or 128-bit textures. The 6200 also lacks OpenEXR\* blending and filtering [23].

-3 Ī-

\_

<sup>\*</sup>OpenEXR is a high dynamic-range image format developed by Industrial Light & Magic.

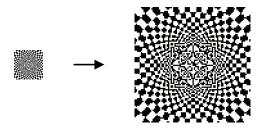

Anti-aliasing and anisotropic filtering technology on ATI cards is named SmoothVision. Anti-aliasing algorithms try to reduce jagged edges often visible in raster images. Version 2.1 of SmoothVision features gamma-corrected multi-sampling that takes up to six samples per pixel to reduce aliasing artifacts. The adaptive anisotropic filter takes up to 16 samples per pixel to sharpen blurry textures.

These filtering techniques are rather expensive and often have a large impact on performance. Most drivers provide control over filter settings to balance rendering speed against image quality.

### 2.2.14 Frame Buffer

The frame buffer, also called front buffer, holds the final picture data, which is displayed on screen. Current consumer displays range from 640 × 480 (VGA) up to 1920 × 1200 (WUXGA) pixels [24]. An appropriate amount of video memory needs to be allocated for the frame buffer.

#### 2.2.15 Back Buffer

This memory also stores a final raster image, just like the frame buffer. The back buffer is useful in a technique called double buffering. Using double buffering the frame buffer holds the active image, which is visible on screen, while the new (next) image is rendered to the back buffer. When all contents are written the back buffer and frame buffer are swapped, so the new image gets exposed on screen.

#### 2.2.16 Multiple Render Targets

Multiple Render Targets (MRTs) provide additional buffer space, to which a pixel shaders can write for storing rendered frames. Output is normally written to the frame or back buffer and is restricted to RGBA coding. The acronym RGB denotes the colors red, green and blue. The RGBA format – sometimes denotes as RGB $\alpha$  – represents three 8-bit colors channels and an 8-bit alpha (transparency) channel.

By using MRTs more than four 8-bit floating-point values can be kept. So, MRTs can be exploited to save on the expensive render loops of multi-pass rendering, but in practice certain restrictions apply to using this technique [25].

One should keep in mind that MRTs have a large associated frame-buffer bandwidth cost. For example, rendering to four A32R32G32B32F surfaces consumes 16 times the frame-buffer bandwidth of rendering to a single A8R8G8B8. These strings denote the format of the data structure stored in the buffer. Again the letters represent the alpha and color channels. The interspersed values indicate the amount of bits used for the coding of the alpha and/or color channels. Modern graphics boards support a specific and rather large set of data formats.

#### 2.2.17 Texture Memory

Texture memory or texture buffer store texture maps, depth maps or other kinds of maps that determine surface properties. These texture mapping techniques are commonly used to reduce modeling complexity. Surface details are often too small and thus expensive and tedious to model explicitly.

Texture reads are relatively expensive. The processing speed of GPUs tends to increase faster than the increase in memory speeds. This also holds for writing to texture memory, but in 3D rendering reads generally occur many more times than writes. Because memory accesses potentially limit performance (graphics) programming should be memory efficient; possibly at the expense of extra processing cycles.

#### 2.3 Brand Specific Technologies

The market leaders on video cards want to differentiate their products from the rest. The following paragraphs focus on a selection of new technologies related to video cards.

#### 2.3.1 Memory Management

ATI's HyperMemory\* technology exploits the PCI Express bus to extend the video memory by utilizing system memory. Because writing to system memory over PCIe is fast – unlike over AGP – this memory expansion is claimed to be without compromise of speed. All computer applications should benefit from this, especially at high display resolutions.

NVIDIA introduced a similar concept and calls it TurboCache<sup>†</sup>. The so-called TurboCache Manager (TCM) allows direct rendering to system memory [26].

#### 2.3.2 Multi-GPU

Both ATI and NVIDIA provide solutions to increase performance and quality of video processing. Selected products can be coupled, but these particular set-ups do require a special main board. These boards typically feature two PCIe (×16) buses.

ATI's CrossFire<sup>‡</sup> workload distribution is based on a checkerboard tiling [27]. Conceptually the screen space is divided in white tiles and black tiles. All white tiles are handled by the first GPU and all black tiles are handled by the second GPU. This super tiling should result in a consistent and efficient load balancing of the GPUs.

CrossFire is designed as an open platform and the two GPU models need not be identical, but some restrictions do apply. For example, when 16-pipe CrossFire Edition card is coupled with a 12-pipe card, the number of active pipes is limited to 12 on both cards. However, individual clock-speeds remain unchanged. All applications will benefit from the dual setup. The following 'CrossFire Ready' Radeon cards can be combined with a CrossFire Edition card of the same series that holds a special co-processor:

- X850 Pro / XT / XT Platinum Edition

- X800 'Vanilla' / Pro / XL / XT / XT Platinum Edition

NVIDIA competes with their scalable link interface (SLI). It requires both GPUs to be of the same model. In Multi-GPU mode only one monitor is supported. SLI is supported on the following GeForce PCIe cards:

- 6600 'Vanilla' / LE / GT

- 6800 'Vanilla' / LE / GT / Ultra

- 7800 GT / GTX

Both ATI's and NVIDIA's implementation differ from the older 3Dfx solution, which was based on a shared PCI bus. 3Dfx increased performance by interleaving the scan lines of the output. Fill rates were improved, but geometry processing however was not. Multi-GPU configurations can also be used for striped or even more generalized processing. Such a custom design need not rely on CrossFire or SLI technology.

-

<sup>\*</sup> HyperMemory is a trademark of ATI Technologies Inc.

<sup>&</sup>lt;sup>†</sup> TurboCache is a trademark of NVIDIA Corp.

<sup>&</sup>lt;sup>‡</sup> CrossFire is a trademark of ATI Technologies Inc.

#### 2.3.3 Video Processing

High Definition video will become available in the near future. New optical disc formats like Blu-ray and HD-DVD and HD broadcasts will bring improved picture quality. Current PCs need some kind of hardware acceleration for smooth playback of this media. Video card manufacturers equip their new products with components to process these high definition streams. These video processors perform decoding of compressed video streams, often accompanied with image filtering.

ATI has implemented hardware acceleration for the H.264 codec and calls it VideoShader [28]. Currently, only the Radeon X700 and newer cards feature the VideoShader technology.

NVIDIA's PureVideo\* accelerates HD video for Microsoft Windows Media files, but it requires a specific software component. It should improve picture clarity and enables high-quality scaling to any view port size. Decoding and spatial-temporal de-interlacing is supported by GeForce 6200 and higher. Hardware accelerated 3:2 or 2:2 pull down is supported as of the GeForce 6600. Certain Quadro FX cards also support this technology.

#### 2.4 Summary

Today's personal computers are well suited for video streaming. Modern video cards with programmable GPUs enable video specialists to develop sophisticated render engines based on image processing algorithms that run in real-time.

We selected NVIDIA's GeForce 7800 GTX graphics card for developing a multiview render engine. This card was the most powerful consumer device available at that time. The 7800 is a PCI Express card. An AGP version would also have sufficed, if one existed, because we will primarily stream data to – and not from – the graphics card for our purpose.

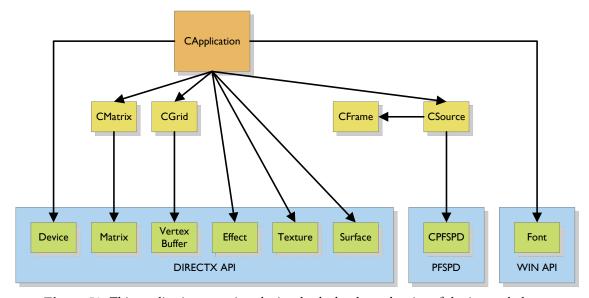

The engine should implement the video processing in terms of vertex and fragment computations of the GPU. An elegant approach is constructing an engine similar to one for traditional 3D rendering, although multiview rendering has a few additional requirements. What these requirements are and our investigation of the related rendering algorithms is presented in the next chapter.

<sup>\*</sup> More information on can be found at http://www.nvidia.com/page/purevideo\_support.html

# 3 Algorithms

This chapter presents our study of rendering algorithms which were considered for the construction of our render engine. Literature provides a rather large collection of image processing algorithms, but not all of them are suitable for a GPU implementation target. We first explain the two specific problems of rendering to a multiview display. This motivates the investigation of certain mapping algorithms and 3D to 2D projections matrices, which are discussed thereafter. Then the layout of our lenticular display is explained. We end this chapter on the topic of image filtering, because all manipulation should preserve the best image quality possible.

### 3.1 Project Specifics

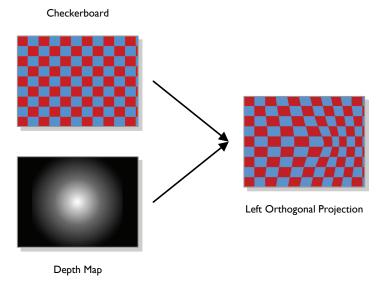

The problem of rendering RGB and depth (RGBD) to a multiview display involves two tasks. The first one is to create disparity from depth information. Once we are able to create such a set of mutually disparate views, we need to merge these views into a single image with the appropriate layout. This is the second task. The specifics of both these tasks are explained next.

### 3.1.1 Disparity from Depth per Pixel

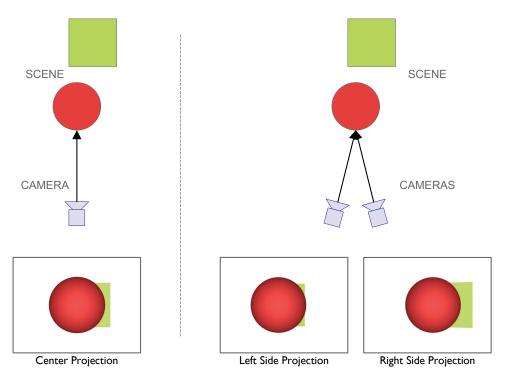

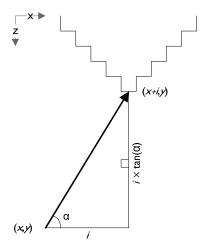

To capture a true stereoscopic image one needs to use a set-up of two cameras that are positioned somewhat apart. Such a set-up is highlighted in figure 15. The resulting camera shots would include all the visual cues, including occlusion and de-occlusion. Our video sources were shot with a monoocular camera, but do contain depth information.

**Figure 15.** Stereoscopic images of (real-life) scenes can be created by using a dual camera set-up. The subtle differences of the resulting projections is what multiview rendering needs to simulate for N camera positions.

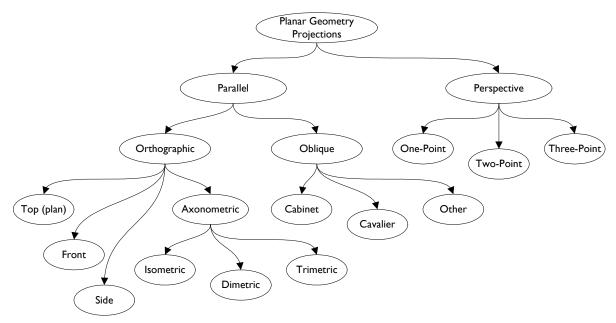

The traditional rendering pipeline for 3D graphics also uses the notion of a camera position and viewing direction. The view of a shot is controlled by one or more projection matrices. It determines what will end up in the final picture. One approach is to create disparity by changing the camera position, but we need more than that to get disparity depending on depth. This motivates our research on the subject of 3D to 2D projections together with a collection of object manipulation algorithms; topics of the upcoming sections.

Programmability of new GPUs allows us to control the rendering process. We could for example change the camera positions one or more times between output frames. Switching cameras is of little use when the scene consists of a flat texture mapped surface. To generate disparity the texture mapped object also needs some manipulation. We could either change the shape of this object or alter the texture on it. Research showed that the micropolygon-based displacement mapping algorithm translates quite nicely to shader hardware. So, the object can be manipulated using a vertex program.

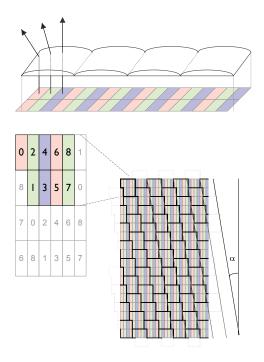

## 3.1.2 Multiple Views per Frame

The simulation of multiple camera positions via displacement mapping results in a set of raster images. Our render engine needs to combine these images into the lenticular output format. One approach is to buffer the nine  $720 \times 576$  RGB frames, and then multiplex the appropriate pixels by copying them to the back buffer. This is somewhat expensive in terms of video memory, because only  $1920 \times 1080$  pixels of the pre-processed  $9 \times 720 \times 576$  pixels are effectively being used per output frame.

A more streamlined approach would not compute redundant intermediate values, but given the architecture of the GPU this is next to impossible. We cannot change the camera position in between fragments, because fragments are computed in parallel. The actual order of computation is hidden from the developer. So, we must keep the view creation and multiplexing in separate passes.

### 3.2 Overview

In order to create disparity we need to manipulate the input frames based on depth. This depth information typically differs per pixel, although it is spatially correlated\* for objects in this picture, still we are in need of an algorithm to process certain details within one frame.

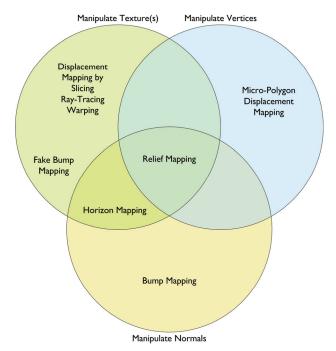

The literature on image processing provides a collection of algorithms on rendering textured surfaces – visualized in figure 16 – which proves to be of value to us. The following sections explain some of these rendering algorithms.

-36-

<sup>\*</sup> We do not consider temporal coherence because of the computational complexity and associated performance penalty.

Figure 16. This Venn diagram shows the properties of a few texture mapping related techniques.

The disparity requirement rules out texture mapping on a flat surface. The derived algorithms shown in the diagram above do enable some form of sub-frame manipulation. The amount and direction of feature manipulation is either controlled by parameters such as normal vectors or vertices, or by directly manipulating the input texture. Some of the techniques combine two or more of these parameters.

## 3.3 Basic Algorithms

## 3.3.1 Texture Mapping

Texture mapping is a basic rendering technique that is used to apply a picture to the surface of a 3D object. The technique was invented by Edwin Catmull in 1974 [29]. Traditionally texture maps were used to add realism to surfaces and are still used in computer modeling and animation today. Sophisticated texturing of 3D objects could mimic real-life materials like marble or wood. Many of the more complex mapping techniques for rendering are based on texture mapping and can provide an even greater surface resemblance.

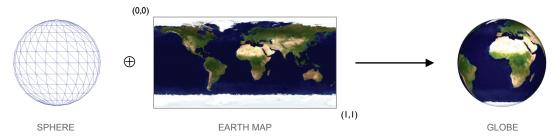

The image in the center of figure 17 is called a texture map. Such a map is coded as a 2D grid and its elements usually store color values. The texture elements (texels) can represent other data, such as height, normal vectors or other parameters [30]. The figure shows how texture mapping can be used to create a globe out of a sphere and a color map of earth.

**Figure 17.** A globe can be rendered by texture mapping a 2D map of earth on a sphere, modeled in 3D. (0, 0) and (1, 1) are texture coordinates for the earth map.

### **Texture Coordinates**

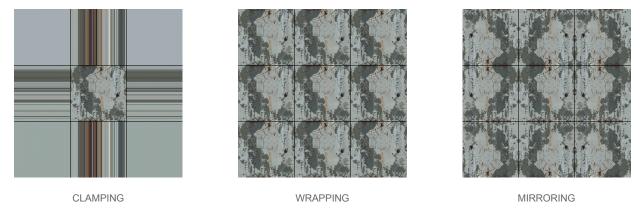

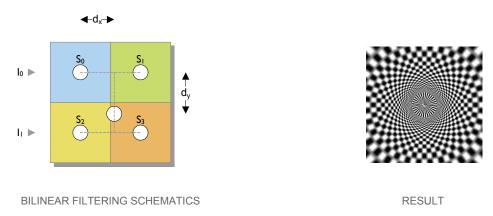

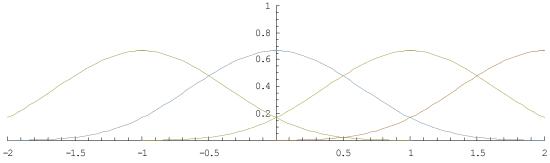

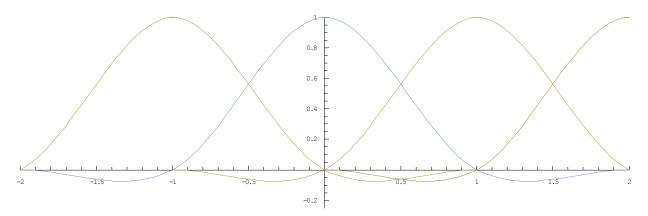

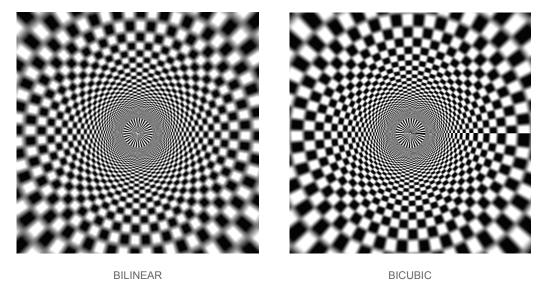

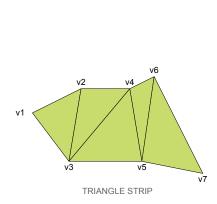

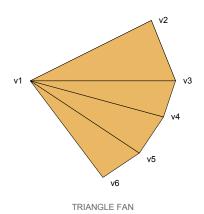

Texture coordinates, often denoted as (u, v), specify which part of the image ends up where on the surface of the object. The coordinates of the texture can be used to crop the edges of the texture map. The texture coordinates of the object define the position of the texture map and also enable texture tiling, where the same texture is repeated to fill a larger part of the surface.