#### MASTER

Emulation flow for designs with large memory requirements

Lammers, K.J.

Award date: 1997

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

tu)

# Master's Thesis

\_

# Emulation flow for designs with large memory requirements

# K.J. Lammers

| Department        | : Design Automation Section,<br>Department of Electrical Engineering,<br>Eindhoven University Of Technology |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| Supervision       | : Prof. Dr. Ing. J.A.G. Jess                                                                                |

| Period            | :01-04-'93 to 18-02-'94                                                                                     |

| Place             | : DVP group,<br>Department PCALE,<br>Philips Semiconductors                                                 |

| Supervision PCALE | : Ir. J.A.A.M. van den Hurk<br>Ing. J. Lakerveld<br>Ir. R.H. van der Wal                                    |

| ID.nr.            | : 270493                                                                                                    |

The Eindhoven University of Technology is not responsible for the contents of thesis reports

# Abstract

During the development of HD-MAC decoder ICs for HDTV, an ASIC design flow was developed: the PCALE Design Flow. Since this design flow does not capture all aspects of system design, a *system* design flow is developed: the Advanced PCALE Design Flow.

Part of the Advanced PCALE Design Flow is *emulation*: the bread board implementation of a design through mapping of the VHDL description of the design to programmable logic devices. One of the steps for deriving this implementation is synthesis by means of synthesis tools. However, synthesis of designs containing large registers with programmable logic devices as back end turns out to be problematic, since very little memory is available in programmable logic devices. This large register problem was solved by using a RAM for implementation of a large register.

The solution consists of a conversion of the VHDL description of a design containing a large register to a VHDL description of a design containing a RAM while preserving design functionality. This conversion is feasible under certain restrictions and a tool was written to automate the conversion. Also, templates that guarantee that the restrictions are met, have been devised. Template checking is incorporated in the tool, prior to design conversion.

So through register replacement emulation of designs with large memory requirements has become possible within the Advanced PCALE Design Flow.

# Summary

During the development of HD-MAC decoder ICs for HDTV, an ASIC design flow was developed: the PCALE Design Flow. Since this design flow does not capture all aspects of system design, a *system* design flow is developed: the Advanced PCALE Design Flow.

One of the new parts in the Advanced PCALE Design Flow is a flexible hardware route. This flexible hardware route has to enable the *quick* development of hardware with the same functionality as the final ASIC before ASIC design has even started. This hardware, also known as bread boards, can then be used for *emulation*: a combination of the advantages of a flexible software simulation with the advantages of real time (and consequently fast) hardware.The reasons for emulation are fourfold:

- 1. Fast-prototyping

- 2. Start-up production

- 3. Field-test

- 4. Real-time simulation

Yet building bread boards in the usual way is time-consuming and not very flexible. Fortunately the *quick* development of bread boards comes within reach due to the emergence of flexible hardware modules.

One of the steps for deriving bread boards is synthesis by means of synthesis tools. However, synthesis of designs containing large registers with programmable logic devices as back end turns out to be problematic, since very little memory is available in programmable logic devices. This large register problem was solved by using a RAM for implementation of a large register.

Two solutions have been investigated, namely:

## 1. Synthesis libraries

The three synthesis tools available at PCALE are reviewed with respect to their ability to add designer defined VHDL descriptions as new building blocks to their synthesis libraries. If it is possible to add a VHDL description of an existing memory IC to the synthesis libraries, then it might be possible to instruct the synthesis tool to automatically use this description instead of synthesizing the register.

However, none of the reviewed synthesis tools support VHDL models as a basis for building blocks. The support that exists is not sufficient for application within the Advanced PCALE Design Flow. Therefore the conclusion is drawn that synthesis libraries cannot solve the large register problem.

## 2. Register replacement

This solution consists of a conversion of the VHDL description of a design containing a large register to a VHDL description of a design containing a RAM while preserving design functionality. As it turns out, this conversion is feasible under certain restrictions.

Hence register replacement is the developed solution to the large register problem. A tool was written to automate the conversion. Also, templates that guarantee that the restrictions are met, have been devised. Template checking is incorporated in the tool, prior to design conversion.

So through register replacement emulation of designs with large memory requirements has become possible within the Advanced PCALE Design Flow.

# **Table of Contents**

| 8.2.1. Structure of the library              | 63  |

|----------------------------------------------|-----|

| 8.2.2. Automatic selection from the library  | 65  |

| 8.3. Template checking                       | 66  |

| 8.4. Error checking                          | 66  |

| 8.5. Transcript file                         | 68  |

| 9. Conclusions and recommendations           | 71  |

| Appendix A. List of References               | 75  |

| Appendix B. List of Figures                  | 77  |

| Appendix C. Framework of definitions package | 79  |

| Appendix D. Example of definitions package   | 81  |

| Appendix E. VHDL model of memory             | 83  |

| Appendix F. VHDL models of addressgenerator  | 85  |

| Appendix G. Listing of simple testcase       | 87  |

| Appendix H. Example of control file          | 95  |

| Appendix I. Example of files file            | 97  |

| Appendix J. Example of RAM library           |     |

| Appendix K. Glossary                         | 101 |

# **1. Introduction**

When developing new systems, it is necessary to verify their performance prior to implementation in <u>Application Specific Integrated Circuits (ASICs)</u>. For instance, in the case of digital video applications, simulations can be used to inspect and evaluate video images before such a digital video application is implemented in an Integrated <u>Circuit (IC)</u>. This offers the possibility to critically evaluate systems prior to their implementation. In this stage of system design changes in system specifications can still be easily made since software can be adapted quickly, while changes in dedicated ICs (ASICs) are costly and much more time-consuming. This strategy is incorporated in the ASIC design flow currently at use at the <u>Product Concept and Application Laboratory Eindhoven (PCALE)</u>. This ASIC design flow is called the PCALE Design Flow.

The PCALE Design Flow prescribes the consecutive steps to be taken in dedicated IC design. However, system design involves more than the development of dedicated hard-ware only. For instance, most systems consist of both hardware and software. Also missing in the PCALE Design Flow is a flexible hardware route. This flexible hardware route has to enable the *quick* development of hardware with the same functionality as the final ASIC before ASIC design has even started. This hardware, also known as bread boards, can then be used for *emulation*: a combination of the advantages of a flexible software simulation with the advantages of real time (and consequently fast) hardware. In fact, the reasons for integrating hardware emulation in the PCALE Design Flow are fourfold:

### 1. Fast-prototyping

Through emulation a customer can quickly be provided with a "prototype" of the final ASIC (in fact emulation does not provide a prototype but a bread board with the same functionality as the final ASIC). The availability of a prototype enables the customer to verify his specification through testing the functionality of the bread board. This allows tracing desirable changes in the specification in an early stage of the ASIC design. Furthermore, the customer can start writing software for his application (in case software is part of the system) and build a prototype-system. In general, a total of some tens of prototype copies can be expected since prototypes are usually small in number.

## 2. Production

A second possibility is to map a description of the design to gate arrays in order to use these gate arrays in the beginning of system production. Gate arrays are half-fabricated ICs: the logic cells are already fabricated but the interconnections (wiring) still have to be made through two final IC masks.

The use of gate arrays in start-up production is faster and less expensive and therefore more desirable than fabricating a dedicated IC. In this case less than a 100,000 gate array copies can be expected. Later on, an optimal and more expensive dedicated IC can be designed for mass production.

#### 3. Field-test

The prototype can be used for a so-called field-test. This means that incomplete parts of the specification can be tested by the designer and that some parts can be evaluated with

respect to their functionality. The incomplete parts of the specification can usually be completed after such a field-test.

#### 4. Real-time simulation

Through emulation, the designer has the opportunity for real-time simulation. This way "simulations" (by means of emulations) can be carried out much faster than traditional simulations. In particular for simulations at system level, a large reduction in simulation time is to be expected. Emulation does not mean that simulation has become outdated: through simulation a description of a design must be checked for correctness; after that, by emulation, the design becomes rapidly available in hardware without having to wait until the ASIC design has been completed.

Yet building bread boards in the usual way is time-consuming and not very flexible. Fortunately the *quick* development of bread boards comes within reach due to the emergence of flexible hardware modules. But the bread board development speed is not the only requirement that is imposed on a flexible hardware route (emulation flow).

Another requirement is that the emulation flow starts with a description of a design in a <u>H</u>ardware <u>D</u>escription <u>L</u>anguage (HDL), a language especially developed and suited for the description of hardware designs. Several of such HDLs exist, but the HDL that is used for this purpose at PCALE is the <u>VHSIC Hardware D</u>escription <u>L</u>anguage (VHDL). This HDL is defined by the <u>Institute of Electrical and Electronics Engineers (IEEE)</u> and is used in the industry for the description of designs during development (see [2]). This requirement is imposed on the emulation flow, since the basis of the dedicated hardware route, an HDL design description, must be the basis of the flexible hardware route also, in order to ensure identical functional behaviour of the ASIC and bread board.

Furthermore the emulation flow must fit into the PCALE Design Flow. This means that the mandatory functional verification at all levels of the PCALE Design Flow must also be applicable to the levels of the emulation flow.

A fourth requirement on the emulation flow is that the application of the emulation flow has to be kept in mind: the emulation flow is to be used for designs that involve video applications, so very stringent speed requirements have to be taken into account.

Finally, a choice has to be made what flexible hardware modules to use. There are several choices for flexible hardware modules since a number of such devices are available on the market: gate arrays from different vendors (Altera, Xilinx, Actel, etcetera) and Erasable Programmable Logic Devices (EPLDs) from Altera. The Digital Video Processing (DVP) group at PCALE has chosen to use EPLDs from Altera as their flexible hardware modules for several reasons:

1. Only for large amounts of bread boards (for instance when emulation is to be applied for production start), gate arrays are cheaper than EPLDs. Since the first applications of the emulation flow apply to fast-prototyping and field-testing (hence a small amount of bread boards), EPLDs are considered as back end of the emulation flow.

- 2. EPLDs are reprogrammable while gate arrays can only be given a certain logic function once. With EPLDs as flexible hardware, this flexible hardware is re-usable when a bread board is no longer needed. But the fact that EPLDs can be quickly reprogrammed has an additional advantage. As with all developments, the emulation flow too has to be tested several times during its development. Using gate arrays for such tests is too expensive and takes too much time. EPLDs on the other hand can be used for several tests and their programming takes little time. On top of that, the EPLDs can even be used for a bread board after the emulation flow has been developed: when testing the emulation flow with EPLDs, no money is lost on flexible hardware. Of course, after the emulation flow has been developed, the extension to gate arrays can then still be made.

- 3. Altera EPLDs are the fastest devices according to comparisons with other flexible hardware modules. These comparisons are based on benchmarks (well-known and welldefined designs used as standard testcase) and have been performed by the <u>Programmable Electronic Performance Corporation (PREP)</u>, a consortium of 13 prominent suppliers of programmable logic and tools.

- 4. Altera EPLDs have been used before by the DVP group. Very satisfactory performance was experienced on those occasions. So there is no reason for changing to new and unknown devices unless they prove to be better.

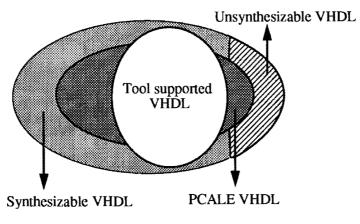

The development of a standard emulation flow is the subject of the Master's Thesis of L.P.M. van Lieshout (see [16]). He encountered several synthesis problems in the synthesis tools that can be used in the emulation flow for synthesizing a VHDL design description. Most of these problems were solved by defining a VHDL subset that is included in the (synthesizable) tool supported VHDL subset. But this subset could not solve all synthesis problems. One synthesis problem, the problem of large registers in the description of a design, still remained.

The reason that this synthesis problem cannot be solved by defining a VHDL subset is that this problem is not a question of "bad" VHDL statements but merely a question of register size. The size of a register becomes a problem when it exceeds the memory capacity of an EPLD: preferably the design is mapped into one EPLD and when more EPLDs have to be used, it is desirable in terms of timing not to divide the register amongst several EPLDs. Since the memory capacity of an EPLD is in the order of magnitude of 200 flip-flops, any register of that size or larger is a candidate problem register.

Therefore another solution has to be found for this synthesis problem. Hence the subject of this Master's Thesis, the development of an emulation flow for designs with large memory requirements.

Basic idea behind this emulation flow is the use of an existing memory IC (RAM) for the implementation of the large register. Then the large register no longer has to be implemented in flexible hardware; only the rest of the design has to be implemented in flexible hardware. This way the need for large memory capacity in flexible hardware would be taken care of.

The only way to solve the large register problem is to change the input for the synthesis tool, since the synthesis tool itself cannot be altered. The input for a synthesis tool are the description of the design that is synthesized and the synthesis libraries. Synthesis libraries provide the synthesis tool with the building blocks needed to synthesize the design. Both inputs are investigated in this Master's Thesis as possible solutions:

- First the possibilities to change the synthesis libraries of synthesis tools are evaluated. The three synthesis tools available at PCALE are reviewed with respect to their ability to add designer defined VHDL descriptions as new building blocks to their synthesis libraries. If it is possible to add a VHDL description of an existing memory IC to the synthesis libraries, it might be possible to instruct the synthesis tool to automatically use this description instead of synthesizing the register. Since the memory IC does not have to be synthesized (remember that it is an existing IC), only the rest of the design has to be implemented in flexible hardware.

- Secondly, the possibilities to change the VHDL description of the design are evaluated. It might be possible to change the VHDL description of a design in such a way that the register is replaced by (a VHDL model of) a memory IC, while preserving design functionality. In that case the standard emulation flow would have to be adapted in a way that the design itself is synthesized while the memory IC is not synthesized. The memory requirements imposed by the register are then no longer a problem. Of course the conditions under which the replacement can take place have to be investigated and preferably a tool is developed for this replacement.

The next chapter discusses the PCALE Design Flow in its present form (the Existing PCALE Design Flow) and in its successor form (the Advanced PCALE Design Flow), followed by an elaboration of the standard emulation flow. Chapters 3 and 4 involve the development of the emulation flow for designs with large memory requirements itself: chapter 3 is about three synthesis tools and their synthesis libraries and chapter 4 reviews the conversion of a design with a register to a design with a memory IC. The templates that guarantee successful register replacement are discussed in chapter 5. Readers unfamiliar with the syntax and semantics of VHDL may experience some difficulties reading chapters 4 and 5. They are referred to the IEEE Standard VHDL Language Reference Manual (see [2]). The testcase and the tests that have been performed are the subjects of chapters 6 and 7. The features of the tool that performs the register replacement are also reviewed in chapter 8. The final chapter is concerned with conclusions regarding the development of an emulation flow for designs with large memory requirements.

# 2. The PCALE Design Flow

As already stated in the introduction, the PCALE Design Flow in its present form does not capture all elements of system design. The DVP group has set out to extend this design flow to a design flow that covers more and hopefully all aspects involved in system design. One of the extensions is the emulation of designs, including the emulation of designs with large memory requirements. However, before the emulation flow for designs with large memory requirements is developed, it is important to have a good notion of the PCALE Design Flow in its present and in its envisioned form and of the standard emulation flow developed for designs in general. They are discussed in this chapter.

# 2.1. Existing PCALE Design Flow

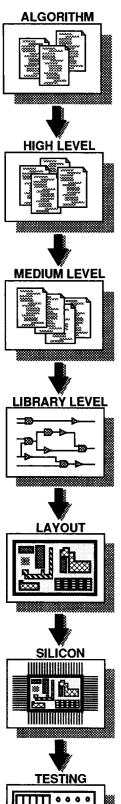

The PCALE Design Flow, depicted in figure 1 on page 6, is a *top-down* hierarchical design flow. It prescribes a trajectory from algorithm to evaluated silicon and is based on two basic principles: specification and verification. As for the first principle, the paper specification of a design is the input for the design flow and must be very accurate since the functionality of the flow input highly determines the functionality of the flow output, the final ASIC. The second basic principle, the functional verification at all levels of the flow, is to ensure design correctness at every moment during design development including the flow output. The combination of the two basic principles is the philosophy behind the PCALE Design Flow, which yields a lot of advantages over non-hierarchical design flows. The most important advantages are:

• A reduced risk of functional design errors

This is the most important benefit of *mandatory* functional verification at all levels in the flow.

• An integrated design environment for system development

This allows for straightforward data exchange between tool sets and between consecutive design levels.

• A short throughput time

A direct result of a short throughput time is a short Time-To-Market.

- The possibility to join forces of multiple design teams in the development of a chip-set

- The possibility to limit simulation run times

Through abstract functional descriptions of individual ICs system behaviour is matched with the algorithm specification and simulation at high abstraction levels becomes possible, resulting in limited simulation run times.

The PCALE Design Flow has been successfully applied during the development of the first generation of HD-MAC <u>B</u>andwidth <u>R</u>estoration <u>D</u>ecoders (BRDs) in the Eureka-95 project, which involved the development of <u>High D</u>efinition <u>Television</u> (HDTV). It proved to be very effective and is now being used for digital design at PCALE. For a more extensive description on this design flow, see [1].

The PCALE Design Flow starts at the <u>Algorithm Level</u> (AL). In this stage of the design flow a system's functional behaviour is recorded in an abstract software description. This description is known as the reference software, or algorithm. An algorithm is the principal functional reference for the development of a system in the PCALE Design Flow.

Once an algorithm has been frozen, IC-partitioning is performed. For each IC in an IC-partitioning, its behaviour is described in a High Level (HL) description. An HL is used as functional reference for the development of an individual IC. IC interfaces and functional behaviour must be in exact accordance with the HL. The combined behaviours of all HLs must be equivalent to the algorithm's behaviour.

To capture an IC's proposed interior architecture and hierarchy, a Medium Level(ML) description can be written which is less abstract than an HL. Functional correctness of an ML is verified through bitby-bit comparison with the HL description; bit-by-bit comparison is performed through simulations. An ML is written in a Hardware Description Language (HDL) at Register Transfer Level (RTL).

The lowest level symbolic description of an IC, the Library Level (LL) description, is created by implementing the ML by means of library elements. Such an LL contains both symbolic representations of VLSI library blocks and their symbolic interconnections. Functional correctness of an LL is verified through bit-by-bit comparison with (parts of) the ML. Timing verification is performed also.

Through placement and routing, the IC layout is generated from an LL description. This layout is checked during factory finishing, for instance to find possible design rule errors.

In this stage of the PCALE Design Flow, the IC layout is transferred to a foundry. At the foundry the design is implemented on silicon wafers and the first IC prototypes are delivered to the design team for testing.

When the first IC prototypes return from the foundry, silicon evaluation can start. Silicon evaluation includes both functional and electrical evaluation. In addition to IC-only evaluation, (sub)system evaluation, including other ICs in the chip-set, is performed.

**FIGURE 1. Existing PCALE Design Flow**

# 2.2. Advanced PCALE Design Flow

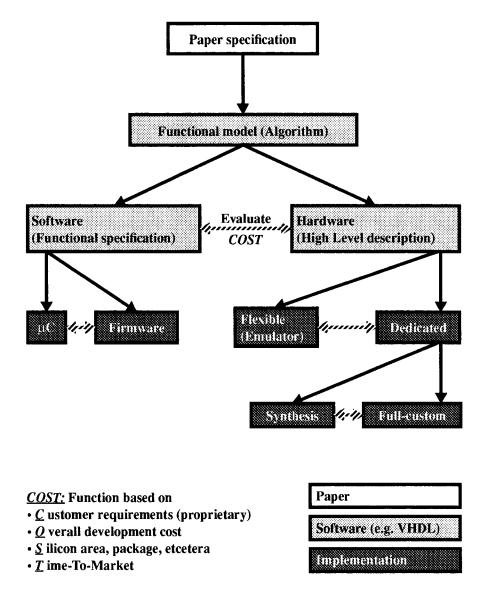

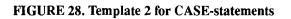

Until now system development has been separated into the development of the hardware part of the system, followed by the development of the software part (provided that the system incorporates both hardware and software); on top of that the two developments were cast in a different mould. The PCALE Design Flow in its present form as described in the preceding section, prescribes the consecutive design steps to take in dedicated hardware design. However, due to a growing understanding of system design and all the aspects of system design over the years, the idea was formed that a complete design flow should cover all the aspects of designing and not merely dedicated hardware design. Hence, the DVP group at PCALE set out to extend the Existing PCALE Design Flow. The PCALE Design Flow in its envisioned extended form, called the Advanced PCALE Design Flow, is shown in figure 2.

FIGURE 2. Advanced PCALE Design Flow

It is important to realize that the philosophy behind the Existing PCALE Design Flow remains intact in the Advanced PCALE Design Flow. The difference is that this philosophy is applied to other aspects of system design also (for example to the development of a system's software). Another important notice is that the Existing PCALE Design Flow in figure 1 is really a design flow in the sense that it identifies the various levels and the consecutive steps involved in dedicated hardware design. The diagram of the Advanced PCALE Design Flow in figure 2 is conceptually different since it merely identifies possible target implementations. The concept of different levels during system development still applies although these levels are not depicted in figure 2.

The blocks in the Advanced PCALE Design Flow are:

#### • Paper specification

Completely analogue to the Existing PCALE Design Flow, the Advanced PCALE Design Flow starts with the paper specification of the system. Based on this specification, the system is developed. A system can consist of both hardware and software. Instead of separating the development of a system's hardware and software in two consecutive and conceptual different steps, the co-design of the two has a lot of advantages, namely:

- 1. The hardware-software combination can be tested in an early stage of system development. This in turn offers the possibility to check the specification of the complete system at an early hour against customer wishes. This system evaluation can then be used to adjust or complete the specification. Most likely this leads to better designs and largely reduces the possibility of redesigns.

- 2. Furthermore, simultaneous hardware and software design decreases the total Time-To-Market. The total Time-To-Market is IC development time plus software development time. The Time-To-Market (IC development time) in the Existing PCALE Design Flow is already much shorter than the Time-To-Market of non-hierarchical design flows. However, if a system also incorporates software, then the software development time is not accounted for in this Time-To-Market. The total Time-To-Market decreases due to the co-design of hardware and software in the Advanced PCALE Design Flow.

- 3. At some stage in system design, the system has to be partitioned in hardware and software. With a growing knowledge of the system during development, this partitioning can be adjusted on the basis of an estimation of costs. This estimation can be thought of as a function taking into account <u>Customer requirements</u>, <u>Overall development cost</u>, <u>Silicon area & package and Time-To-Market (COST)</u>. The partitioning adjustment can be made in almost every stage of the design flow since both hardware and software are described in the same description language, for example VHDL.

The combination of hardware and software development, Hardware-Software Codesign, is therefore captured in the Advanced PCALE Design Flow, starting with the paper specification. It is important to observe that both hardware and software are based on VHDL descriptions. VHDL was developed for the description of hardware as the name already suggests, <u>VHSIC Hardware Description Language</u>. But taking a closer look at VHDL, it is observed that it incorporates certain constructs that can be used for the description of software also. This in fact makes the smooth hardware-software integration feasible and worthwhile; otherwise Hardware-Software Co-design becomes much more complex and perhaps not even feasible within the PCALE Design Flow.

#### Functional model

Also completely analogue to the Existing PCALE Design Flow is recording a system's behaviour in an abstract software description. Again this description (or algorithm) is the principal functional reference for the development of a system. The only difference with the Existing PCALE Design Flow is that a system involves both system hardware and system software in the Advanced PCALE Design Flow. Therefore the algorithm incorporates the combined functionality of a system's hardware and software.

#### Software

Based on the evaluation of the COST function, some parts of the system are selected to be implemented in software. A distinction can be made between firmware and microcontroller ( $\mu$ C) software. Firmware is fixed software, which means that this software possesses little or no flexibility (for instance software in a ROM). Software implemented on a micro-controller is much more flexible, but on the other hand takes more chip area. For some designs firmware suffices while other designs need the micro-controller implementation; sometimes even, the designer has to evaluate the pros and cons of the two before making a choice.

#### • Micro-controller (µC) software

Just like all target implementations, the final implementation in micro-controller software is based on a VHDL description. But VHDL is not suited for programming a micro-controller. Hence a translation from VHDL to some programming language is necessary for implementation in a micro-controller: a tool translating sequential VHDL to the C programming language has already been developed at PCALE.

#### • Firmware

Firmware, being the fixed implementation of software, is already indicated as part of the Advanced PCALE Design Flow. Yet the design flow for firmware is still to be developed.

#### Hardware

Based on the evaluation of the COST function, some parts of the system are selected to be implemented in hardware. Final implementation usually means development of dedicated hardware (implementation in ASICs). However, besides dedicated hardware also the implementation in flexible hardware is possible. This implementation is usually of a more temporary nature since it is used for emulation purposes. The fact that both dedicated as well as flexible implementations can be derived for hardware, has an additional advantage. It is possible to implement ICs from a chip-set via the dedicated route one by one. The others can be emulated until an IC has been implemented in dedicated hardware. Then another IC follows the dedicated path until the whole chip-set is available in dedicated hardware.

• Flexible hardware

As mentioned in the introduction, emulation can be very useful. The block called flexible hardware indicates the route that leads to emulation boards (bread boards). A flexible hardware route for designs in general has been developed by L.P.M. van Lieshout. However, designs with large memory requirements cannot be emulated with that flexible hardware route. Hence this Master's Thesis subject of a flexible hardware route for such designs.

### Dedicated hardware

Dedicated hardware is the development of ASICs: selecting the dedicated path for parts of the system means that these parts are implemented in ASICs. The path Paper specification – Functional model – Hardware – Dedicated in the Advanced PCALE Design Flow indicates the target technologies of the Existing PCALE Design Flow. This means that all dedicated hardware is developed according to the Existing PCALE Design Flow. For dedicated hardware, two blocks in the Advanced PCALE Design Flow are distinguished: full-custom and synthesis.

### • Full-custom

Dedicated full-custom hardware design means development of ASICs that are as optimal as can be. The design team exerts itself to the utmost to optimize the final ASICs. The consecutive steps to take in full-custom hardware design are prescribed by the Existing PCALE Design Flow.

## • Synthesis

The block synthesis in the Advanced PCALE Design Flow indicates the development of all dedicated hardware except full-custom hardware design. Final target implementations are standard cell or datapath designs. The derivation of these implementations is prescribed by the Existing PCALE Design Flow.

# 2.3. Standard emulation flow

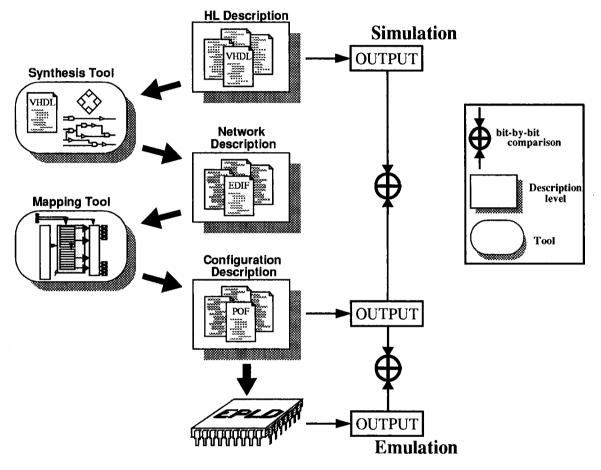

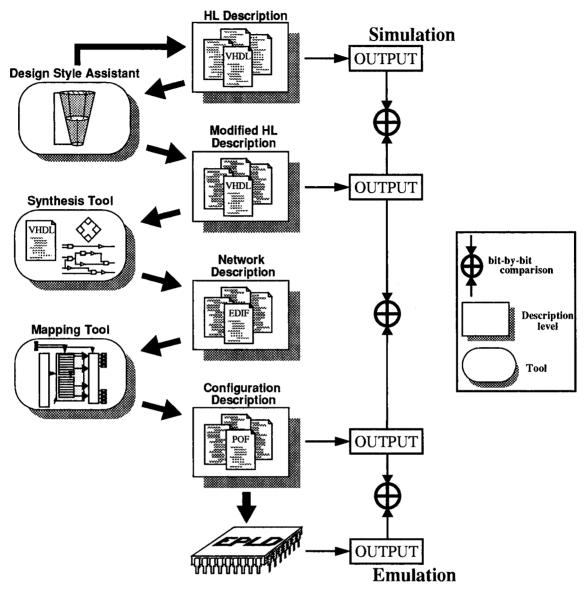

Now that the reasons for emulation and the place of emulation in the PCALE Design Flow have been determined, it is time to take a closer look at the emulation flow itself. As mentioned in section 2.2, emulation is the implementation of an HL description of an IC in flexible hardware. This implementation is of use when the final ASIC has not yet been developed through dedicated design. Only by using synthesis tools the flexible hardware implementation can be generated *quickly* (which is an essential demand on the emulation flow). After synthesis, a mapping has to be generated by a mapping tool and finally the generated mapping can be transferred to flexible hardware. These are the main steps in the emulation flow.

However, emulation is to be part of the PCALE Design Flow and must therefore comply with the philosophy behind the PCALE Design Flow. So every next step in the emulation flow can only be taken if the functional correctness of the preceding step has been established. In figure 3 the concept emulation flow is illustrated along with the three bit-by-bit comparisons that have to be performed to verify functional correctness. The first two are based on simulation results; establishment of functional correctness of the programmed flexible hardware is in fact bit-by-bit comparison of simulation results with emulation results.

FIGURE 3. Concept emulation flow

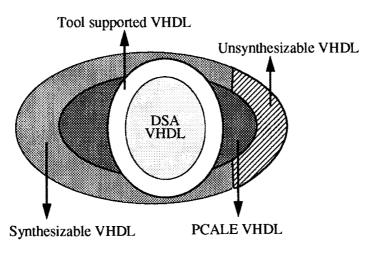

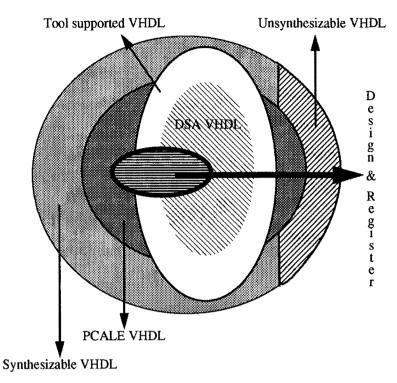

However, the synthesis of a design by means of a synthesis tool turns out to be the most critical step in the emulation flow due to the fact that the available synthesis tools demonstrate several problems when synthesizing an HL description written in VHDL. These problems have been thoroughly described by L.P.M. van Lieshout in his Master's Thesis (see [16]). He describes various subsets of the VHDL language (see figure 4) and concludes that many of the synthesis problems stem from the fact that these subsets have non-overlapping parts and that even VHDL descriptions written according to the tool supported subset are possibly synthesized inefficiently.

FIGURE 4. VHDL subsets

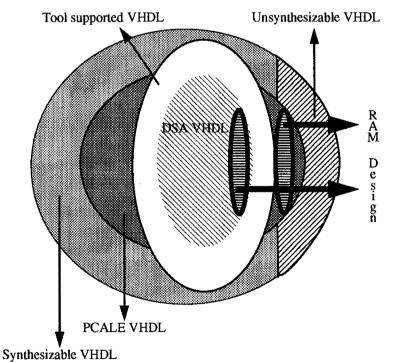

As a solution to the synthesis problems he defines the <u>Design Style Assistant</u> (DSA) VHDL subset, a VHDL subset that contains those VHDL statements of the tool supported VHDL subset that are synthesized in a satisfactory way. Figure 5 illustrates the position of the DSA VHDL subset with respect to the other VHDL subsets.

FIGURE 5. DSA VHDL subset

By making sure that an HL description not only complies with the PCALE design VHDL subset but also with the DSA VHDL subset, most of the synthesis problems can be solved except for the large register problem, since this problem is not a question of "bad" VHDL statements (registers are allowed within the DSA VHDL subset) but merely a question of memory size.

A DSA tool has been developed by L.P.M. van Lieshout to help the designer to ensure that an HL complies with the DSA VHDL subset. This DSA tool can be used to aid in translating VHDL constructs in the PCALE design VHDL subset, but not in the DSA VHDL subset to equivalent VHDL constructs in the DSA VHDL subset. This DSA tool is to be applied before synthesis is attempted. The emulation flow incorporating this tool is depicted in figure 6.

FIGURE 6. Standard emulation flow

This emulation flow is called the standard emulation flow since it applies to almost every design and concerns most of the synthesis problems. Whether or not this emulation flow also holds for designs with large registers, is to be investigated.

# 3. Synthesis libraries

When synthesizing an IC description, synthesis tools use so-called synthesis libraries to map the description to a technology. These synthesis libraries provide the synthesis tool with the building blocks and their characteristics needed to perform synthesis and to be able to meet constraints. Constraints may have been imposed on the design in order to achieve speed or memory requirements. For every technology another synthesis library is available since building blocks and their characteristics can differ from technology to technology.

When synthesis libraries can be expanded with designer defined building blocks, this provides a powerful way to perform more efficient mapping. Since the synthesis tool can choose between the original building blocks and added optimized building blocks, the mapping is likely to improve: inefficient mappings can be avoided and previously impossible mappings become available. In fact, effort that has previously been invested into certain designs, is not lost. Also, if existing ICs are added as building blocks, implementation of a building block by an existing IC and copying (parts of) layouts of existing ICs are possibilities that come within reach. So chip design becomes more efficient and faster.

But the fact that (parts of) designs can be mapped to added building blocks offers the possibility to emulate designs containing one or more large registers. If a RAM is added as building block to the synthesis libraries and if the synthesis tool can map a register to such a RAM, then the register can be implemented by a RAM instead of by flexible hardware. This way the emulation flow can be extended to cover designs with large registers.

In the next sections three synthesis tools are discussed. They are evaluated in terms of their ability to add designer defined building blocks to their synthesis libraries. The evaluation concerns designer defined building blocks in general. This is done because a general solution not only enables emulation of designs with large registers but also upgrades chip design. A solution merely aimed at the addition of a RAM as building block would only enable the emulation and would not improve chip design. Since all design descriptions at PCALE are written in VHDL, the synthesis tools are evaluated on their possibility to add VHDL descriptions of building blocks to their synthesis libraries; descriptions that are written in a format other than VHDL are not of interest. And, of course, all results must fit into and comply with the Advanced PCALE Design Flow and especially the Flexible Hardware route, since the synthesis tools are applied in that context.

# 3.1. Autologic

The synthesis tool from the Mentor Graphics Corporation is called Autologic. It is the first synthesis tool that has been evaluated with respect to its ability to add designer defined building blocks to its synthesis library. The manuals that go along with the synthesis tool (see [6] and [7]) form the basis of this evaluation.

An Autologic synthesis library can be developed through a library development process. This development process involves a number of steps, starting with the creation of a socalled AMP-library. Only from such an AMP-library, Autologic synthesis libraries can be developed.

The only way to add a component to an AMP-library is to provide a functional model of that component. Three AMP functional model types are supported:

#### 1. AMP built-in model

An AMP built-in model is a logical model that operates with simulators and synthesis tools and provides good run time performance and high memory capacity in the tools.

#### 2. QuickPart table model

A QuickPart table model is a formatted table description of a functional model which offers specification flexibility for the creation of accurate models.

### 3. Schematic model

A schematic model is a collection of smaller models (such as built-in models and QuickPart Table models) which accurately represents the internal composition of the model.

VHDL models, however, are not supported, so an alternate model must be provided for such VHDL models or the unsupported VHDL models must be marked as "blackbox".

#### A. Providing an alternate model for the VHDL model

This means that the designer has to supply an extra model for synthesis with the same functionality as the original VHDL model. This means that the same objective can be achieved with the alternate model; the VHDL model is superfluous. Moreover, "model-ling the VHDL model" is not wanted: you are performing the same task, namely describing the functionality of a design, twice. The only remaining possibility is generating a schematic from the VHDL model. Then this schematic could be used as a functional model for the AMP-library. However, schematics that can be used as a functional model for the AMP-library are restricted:

- Schematics can only consist of built-in models, QuickPart Table models or other schematic models. VHDL models cannot be part of schematics.

- Asynchronous feedback cannot be included in a schematic model.

- Restrictions are present for the components that can and/or should be used in a schematic model. That is: some components are not supported and some components are mapped in a logically correct, but inefficient manner. Since there is no guarantee that such unwanted components are introduced when generating the schematic, there is also no guarantee that the schematic can be used as a functional model for the AMPlibrary.

Looking at the above restrictions, it is evident that no guarantee can be given in advance whether or not a schematic generated from a VHDL model can be used as a functional model for the AMP-library. Therefore schematics do not qualify as a possible solution.

#### B. Marking the VHDL model as blackbox

Marking the VHDL model as blackbox means that no logic is generated during synthesis. The designer or the library developer must create a replacement rule to map the blackbox cell to a target library. By means of a replacement rule Autologic can be instructed to use a specific building block from the library for implementation of a certain component.

In case of VHDL models of existing ICs, no optimization should be performed, so marking of the blackbox cell with Syn\_donttouch or Syn\_dontuse is necessary.

- Syn\_donttouch: Autologic does not remove or introduce this component during optimization, but it can still be replaced by means of a replacement rule.

- Syn\_dontuse: Autologic does not introduce this cell during optimization, but it can be introduced by means of a replacement rule.

So marking the VHDL model as blackbox and replacing it through a replacement rule boils down to instantiating a netlist from the synthesis library. Since timing is not included in the netlist, the timing of the total IC can only be synthesized and optimized correctly if the designer tells Autologic what the timing of the blackbox is. On top of that, in the case of EPLDs as back end synthesis tools cannot guarantee that the timing will be correct after synthesis and mapping.

This is not a straightforward and transparent use of synthesis libraries since nothing is done by the synthesis tool: what to replace, how to replace it and the timing have to be entered by the designer. So marking the VHDL model as blackbox is useless.

Since there is no way to use VHDL models in the envisaged fashion as a basis for components of the synthesis libraries of Autologic, the Autologic synthesis libraries cannot solve the problem of large registers in a design.

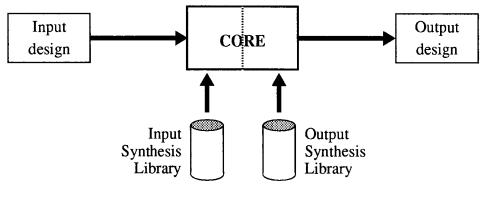

# **3.2. CORE**

Another synthesis tool is the <u>Complete Optimization and Retargeting Environment</u> (CORE) from Exemplar Logic. It is the second synthesis tool that was reviewed. In CORE there is a distinction between input synthesis libraries and output synthesis libraries. Figure 7 illustrates this distinction.

FIGURE 7. CORE and synthesis libraries

CORE uses input synthesis libraries to allow mapping out of a technology, that is to provide an input for CORE. Output synthesis libraries are used for mapping into a technology.

Concerning synthesis libraries, CORE has two tools available for the creation of synthesis libraries: *lBuild* for the creation of libraries that are used for input synthesis only and *lGen* for the creation of libraries that are used for input and output synthesis. The restrictions of these tools and particularly the restrictions on the synthesis libraries are listed below. Note that on top of these restrictions, every library element has to be described by hand. Automatic creation of library elements is not supported so VHDL models cannot be automatically transformed to library elements.

## lBuild:

If a library is built for input synthesis only, the area and electrical properties of the gates are not needed, and the global library properties are also not needed. Only gate functionality descriptions are required. Gate functionality can be described as a set of boolean equations, as a set of predefined primitives or a combination of both. The following restrictions for input synthesis libraries are listed in the *lBuild* manual (see [9]):

- Supply voltage with the name VCC and ground with the name GND are added when the synthesis library is built, unless those functions are specified with other names.

- Gate and pin names are case insensitive.

- No loops in combinatorial logic are allowed. Most loop situations can be specified by using one of the predefined primitives.

- Gate, pin and node names which are also keywords or contain non-alphanumeric characters, should be quoted. For example: gate "DELAY".

#### <u>lGen:</u>

lGen is the tool to use for libraries that are built for output synthesis also.

In addition to the restrictions for input synthesis libraries listed in the *lBuild* manual, the *lGen* manual (see [10]) lists the following restrictions for output synthesis libraries:

- *lGen* requires at least a 2-input NAND-gate and an inverter to be included in the library.

- Complex combinatorial cells with more than one output are allowed for input only. Therefore these cells must be designated as NOMAP when the library is used for output synthesis also.

- For mappable gates, *lGen* supports at most a single predefined primitive (such as flipflops, latches, tri-states) per gate. There is no limitation to the combinatorial logic that can accompany that primitive.

- When mapping into a technology, CORE performs automatic selection of gates in a class to get the best performance out of the circuit. Gates are members of the same class if they have the same functionality and the same pin names.

The synthesis libraries are used as output synthesis libraries in the PCALE Design Flow. Since it is far from realistic that library elements (and in particular RAMs) contain at the most one primitive and have only one output, and since VHDL models cannot be used as a basis for library elements, the CORE synthesis tool is unfit as a solution to the memory problem that large registers cause in the flexible hardware route.

# 3.3. VHDLSyn

The last synthesis tool that was evaluated, is VHDLSyn from Philips Electronic Design & Tools. According to the VHDLSyn manual (see [11]), it is possible to add your own parametrized VHDL models to the synthesis library. Since VHDLSyn can produce output in the <u>Sprite Input Language</u> (SIL) format, the SIL-format of the library is not a problem.

VHDLSyn uses an implementation from the synthesis library whenever a VHDL operation is translated or when an entity or subprogram is instantiated that has the so-called *lv\_primitive* attribute (see [11]). This means that by giving an entity or a subprogram the *lv\_primitive* attribute, VHDLSyn can be told to skip the architecture/subprogram body and to use a predefined implementation from the synthesis library.

Automatic selection of an implementation is only possible for standard building blocks (such as AND-gates, flip-flops, etcetera) or for standard operations (such as counters, shifters, etcetera). This means that you can add your own components to the synthesis library without any problem, but the automatic selection only takes place if the added component is an alternative for already existing standard building blocks or standard operations.

Combining the memory problem with the possibilities of VHDLSyn, two problems are noticed:

- 1. RAMs and registers are completely different hardware components. A RAM does not qualify as an alternative for a register. That makes automatic selection impossible in VHDLSyn.

- 2. A register can be modelled in VHDL as a VARIABLE or as a SIGNAL. VARIABLES and SIGNALS are *part* of an entity or subprogram. So the *lv\_primitive* attribute is also useless since that attribute can only be applied to entities or subprograms as a whole.

Apparently VHDLSyn does not incorporate capabilities that allow automatic implementation of a register by a RAM. Therefore it is evident that the memory problem cannot be solved by the synthesis libraries of VHDLSyn.

# 3.4. Conclusions

A large register in a design requires a large memory capacity to be available in flexible hardware when a bread board is developed for the design. Flexible hardware elements in contrast have very little memory capacity. Therefore synthesis tools have to use a lot of flexible hardware elements when mapping a design which contains large registers to flexible hardware. This means that a design has to be partitioned among multiple elements.

Partitioning implies an increase in wiring and in wiring complexity, which leads to inefficient mappings, which in turn cause a decrease in clock frequency. Remember that for video applications the speed requirements are very stringent. Also it is preferred to keep the number of flexible hardware elements as small as possible in order to keep the bread board simple, small and as cheap as possible. Besides this, the synthesis tools crash during synthesis of such designs, probably because such large registers cause an overflow in the internal format used by the synthesis tools.

To overcome the memory problem, several synthesis tools have been reviewed on their synthesis libraries. The idea behind the use of synthesis libraries is quite simple: if it is possible to add a VHDL model of a RAM to these libraries as new building block, then it might be possible that the synthesis tool can perform an automatic mapping of the register to this new building block.

But the reviewed synthesis tools have either no support for VHDL models as a basis for their synthesis libraries, or such support has too many and too severe restrictions. Hence none of the reviewed synthesis tools can provide a solution to the memory problem in terms of synthesis libraries.

# 4. Changing the design description

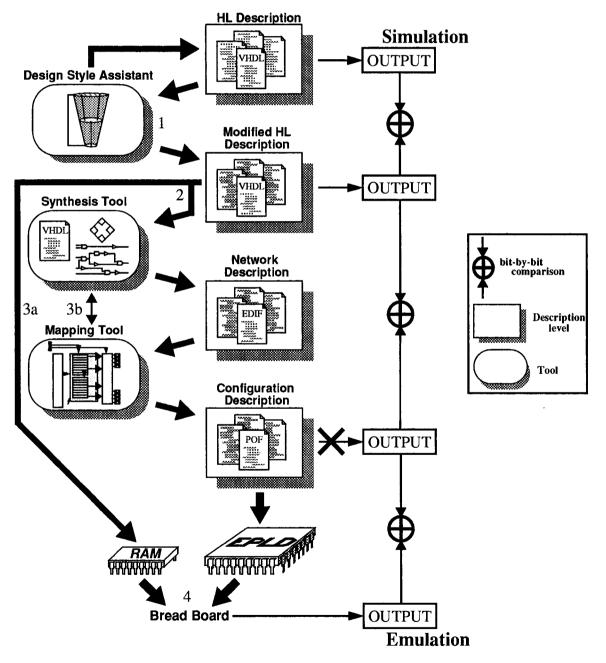

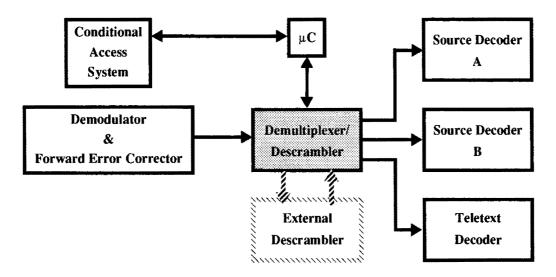

Besides the synthesis libraries of synthesis tools, another solution is looked into: perhaps the description of a design containing a large register can be altered in such a way that the large register problem can be overcome. The basic idea is still that the large register is implemented in an existing RAM IC while the rest of the design is implemented in flexible hardware. The bread board for emulation can thus be built from this RAM and flexible hardware. The emulation flow describing the approach of this solution is shown in figure 8.

FIGURE 8. Emulation flow for designs with large memory requirements

In this emulation flow the consecutive steps to take, starting with an HL description of a design, are:

# 1. Conversion of the design description

The first step in the emulation flow is the conversion of the HL description of the design to a new HL description. During this conversion the large register has to be completely replaced by a RAM. The tool that performs the replacement is part of the <u>Design Style Assistant (DSA)</u> tool that already was present in the standard emulation flow of figure 6.

The new description still has to be simulatable of course for functional verification of the design after conversion. Recall that functional verification is an essential part of the PCALE Design Flow and that the emulation flow must comply with the PCALE Design Flow.

However, the new design description does not have to be synthesizable. The RAM, actually a VHDL model of the RAM, only has to be simulatable since it is not synthesized. The rest of the design description on the other hand must be completely synthesizable since it has to be synthesized by means of a synthesis tool.

# 2. Splitting the design description

The second step is splitting up the new HL description into a part containing the RAM and a part containing the rest of the design. This has to be done since the RAM is not synthesized.

## **3a. Acquisition of a suitable RAM**

Evidently, a suitable RAM must be acquired for implementation of the register unless it is available. A suitable RAM is a RAM that suffices the speed, memory and voltage requirements.

# 3b. Synthesis and mapping

Parallel to the acquisition of a suitable RAM is synthesis. Synthesis is performed on the new HL description without the part that describes the RAM. After synthesis, mapping on flexible hardware (EPLDs) is performed by means of a mapping tool.

# 4. Bread board building

After RAM acquisition and synthesis, it is time to build the bread board. On this bread board the flexible hardware and the RAM are connected. Finally the bread board is emulated and the emulation results are verified through bit-by-bit comparison with the simulation results that are obtained after conversion of the design description.

The first two steps in this emulation flow still have to be developed; the other steps can already be performed. But before these two steps can be developed, the differences between registers and RAMs must be inventorised. Since RAMs and registers differ in behaviour, it is very likely that there are some restrictions on the conversion of the design description. After these restrictions have been determined, conversion and splitting of the design can be developed, thus completing the emulation flow for designs with large memory requirements.

# 4.1. Differences between RAMs and registers

For the replacement of a register by a RAM the most general case is considered: registers with full random access and assignment. Afterwards it is always possible to investigate the replacement of other registers such as shift registers. Perhaps the restrictions for replacement and the replacement itself are different for such other registers.

Preferably there are no restrictions for the register replacement, of course. This means that full random register access and assignment have to be replaced by full random RAM access and assignment. But that is an illusion since the behaviour of a RAM is very different from the behaviour of a register. Due to the differences between RAMs and registers there are most likely some restrictions for describing a register in a design when such a register is to be replaced by a RAM. The main differences between RAMs and registers are:

## 1. Response time

Every operation on a RAM takes a certain amount of time namely the response time of that RAM. A register in contrast has no response time. The time needed to perform a register operation is negligible compared with the time needed for a RAM operation.

### 2. Accessible amount of data

Only one word at a time can be read from a RAM or written to a RAM. This means that for a RAM the accessible amount of data is equal to the wordlength of the words of the RAM. The accessible amount of data for the register on the other hand is equal to the registersize since the register is completely accessible.

## 3. Control signals

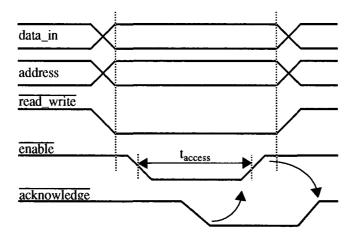

Besides the clock signal the register does not need any control signals for its operation. A RAM however does not need a clock signal but some other control signals, namely a read\_write signal, an enable signal and an acknowledge signal.

The read\_write signal indicates the RAM what kind of operation it has to perform: a read operation or a write operation. With the enabling signal the RAM can be turned on and off. Usually turning the RAM off results in a low power consumption. The RAM has to be enabled before data is read from the RAM or written to the RAM. The third control signal, the acknowledge signal, is used by the RAM to indicate that an operation is completed.

These differences clearly indicate that the conversion of the HL description is not trivial. But besides the differences between registers and RAMs, there are more aspects involved in the conversion. For instance, the HL description has to be simulatable after the conversion and the design without the RAM has to be synthesizable.

The complexity of the conversion is depicted in figures 9 and 10. In figure 9 the position of the design in the various VHDL subsets before replacement is reflected.

FIGURE 9. Place of design description in VHDL subsets before conversion

Figure 10 shows the position of the design with the RAM in the VHDL subsets after the replacement.

FIGURE 10. Place of design description in VHDL subsets after conversion

As figure 10 clearly shows, the RAM is in the PCALE VHDL subset but is not synthesizable. The rest of the design is in the DSA VHDL subset after treatment by the DSA tool.

# 4.2. Replacement restrictions

As stated in the previous section it is most likely that the replacement of a register by a RAM is restricted. Before the restrictions for replacement can be stated there are a number of considerations that must be paid attention to. These considerations that are listed below lead to the restrictions under which the replacement can take place and thus they lead to the VHDL model of the RAM.

Considerations:

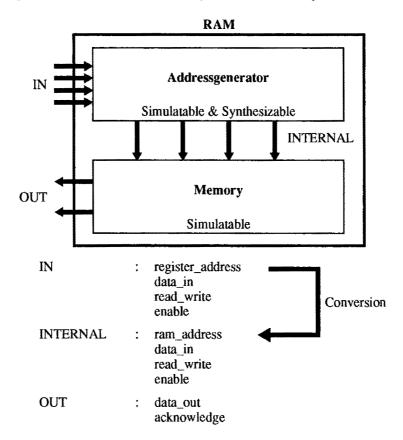

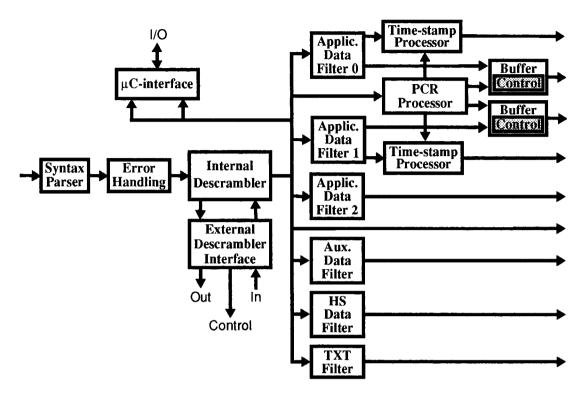

1. A RAM consists of two parts: the memory itself and an addressgenerator which is used to address the RAM correctly. This is illustrated in figure 11. Also indicated in the figure are the signals that control the memory and the addressgenerator.

FIGURE 11. Schematic model of a RAM

The memory consists of a certain number of words, each with the same wordlength. The total memory capacity of the RAM is the wordlength multiplied with the number of words.

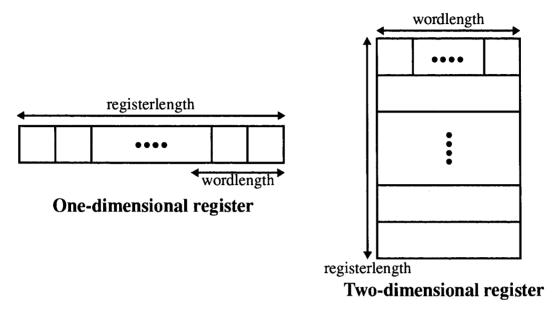

A register can be modelled as a one-dimensional and as a two-dimensional array as shown in figure 12. More dimensional arrays are not supported by synthesis tools. Therefore registers are assumed to be one-dimensional or two-dimensional since the result of a replacement of a more dimensional register cannot be verified.

FIGURE 12. Schematic models of a one-dimensional and a two-dimensional register

Registers are indexed with integer values. In contrast, RAMs are addressed with socalled std\_(u)logic\_vectors. Hence type conversion is necessary. This type conversion has to take place in the addressgenerator. Note that the memory of a RAM is always two-dimensional. A different dimensionality between the register and the memory requires a more complex address conversion of course.

- 2. For the memory of the RAM an existing IC is used while on the other hand the addressgenerator has to be synthesized. Therefore it is necessary that they have separate VHDL models. The VHDL model of the *addressgenerator* must be both *simulatable and synthesizable* whereas the VHDL model of the *memory* only needs to be *simulatable*.

- 3. In the design various parts of the register (slices) can be indexed. It is possible that these slices vary in size or differ from the wordlength of the memory. This has to be accounted for in the addressgenerator also. For simplicity only *slices of a size equal to the wordlength* are considered (see figure 12). Afterwards extensions can be added.

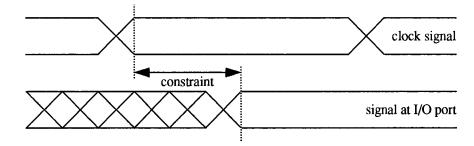

- 4. Another consideration is that *constraints* have to be put on the various signals. Every RAM has its own specific response time: every read-operation and every write-operation takes this time to complete. This time can be accounted for in the simulatable model of the RAM memory; however, this time is not accounted for when synthesizing the design and the addressgenerator. Therefore constraints have to be put on various signals (such as the read\_write signal, the data signal, etcetera), in order to synthesize a functionally correct design and addressgenerator. These constraints are parameters for the synthesis tool when it performs synthesis.

There are two types of constraints: input constraints and output constraints:

• With input constraints the arrival times at input ports can be defined. An arrival time for an input port defines the maximum delay relative to the clock to that input through logic external to the synthesized design.

• With output constraints the required times at output ports can be defined. The required time for an output port defines the longest allowable path from any input port to the output port. Paths start at primary inputs and at register outputs. Paths end at primary outputs and at register inputs.

Constraints are relative to the last or to the next active clock edge (see figures 13 and 14).

FIGURE 13. Constraint relative to last active clock edge

FIGURE 14. Constraint relative to next active clock edge

Note that when signals are constrained, there is no guarantee that the synthesis tool is able to synthesize a network that meets the constraints imposed on the input/output signals of the design and addressgenerator. Even if the synthesis tool reports successful synthesis, it is still not guaranteed that the constraints are indeed met, since the exact timing of the final EPLD(s) is not known before the mapping is completed (see [16]).

5. In VHDL the signals that control the RAM can be modelled as VARIABLES or as SIG-NALS. Preferably the RAM that replaces a large register has the same possibilities that the register has: full random access for write and for read operations. This implies the use of VARIABLES.

It is already established that the signals have to be constrained. Since only SIGNALS can be constrained, the use of VARIABLES is impossible. A direct consequence of the use of SIGNALS is that *the number of operations per clock cycle is limited to the maximum of one*. This is due to the fact that SIGNALS can only be updated once per clock cycle in VHDL.

Another consequence of the usage of SIGNALS is that *read operations have to be anticipated at least one clock cycle*. Suppose some data is needed in the *middle* of a PROC-ESS. That implies that the signals have to be updated in the *middle* of the PROCESS. On the contrary, during simulation SIGNALS are updated at the *end* of a PROCESS. The only way in VHDL to update SIGNALS in the middle of a PROCESS is by using a WAIT-statement. However, WAIT-statements are not synthesizable. So when data is needed in a clock cycle, the data has to be retrieved before that clock cycle.

6. The replacement of a register by a RAM alone is complex enough, so the tool that eventually has to carry out the replacement does not try to ensure that the register complies with the restrictions for replacement. Instead, the restrictions under which the replacement can be done are captured in templates (see chapter 5) and the tool checks the design before replacement for compliance with these templates.

If the templates are violated, the replacement is not guaranteed to be correct. In that case interaction with the designer rules the decision whether or not a register has to be replaced by a RAM. This means that the designer takes responsibility for the restriction that the register complies with the restrictions.

7. Another important aspect is the *timing*. The timing of a RAM is shown in the diagram of figure 15. Normally when addressing a RAM, all the needed signals (read\_write, data, address) are made valid. After that the RAM is enabled by means of an enable signal. When the read or write operation has completed, the RAM sends an acknowledge signal to indicate this completion. Next the enable signal is disabled. In case of a read operation data is not sent to the RAM but data is received from the RAM, of course.

FIGURE 15. Timing diagram of a RAM

The VHDL code that corresponds with the above timing diagram and that handles the acknowledge correctly, is:

valid\_data\_in; -- in case of a write operation valid\_address; valid\_read\_write; enable\_ram; WAIT UNTIL ram\_acknowledge; disable\_ram;

Yet such a construct, to be implemented in the addressgenerator, is not synthesizable due to the fact that the WAIT UNTIL statement is not synthesizable for signals other than the clock signal (see [16]).

Another solution one might think of is to use a WAIT FOR statement in the VHDL model of the memory:

WAIT FOR access\_time; disable\_ram;

Since the memory is not synthesized, the unsynthesizability of this statement is not a problem. But the enabling and disabling of the enable signal is a problem. Because the addressgenerator "knows" when the various signals are valid, the enabling has to be done by the addressgenerator. Disabling on the other hand is done by the memory, since only the memory can determine when the operation has been completed.

However, there are three reasons why this approach cannot be applied.

- 1. It is functionally incorrect that a RAM disables itself. The RAM is controlled by the addressgenerator so the addressgenerator has to enable and disable the RAM.

- 2. The logic needed to disable the RAM is not synthesized since the memory of the RAM is not synthesized.

- 3. The enable signal now has multiple drivers: both the memory and the addressgenerator assign the enable signal. Multiple drivers imply a WIRED\_OR or a WIRED\_AND in hardware and such hardware elements are not present in EPLDs. A separate process for disabling the RAM, triggered by an EVENT on the acknowledge signal, is also impossible due to multiple drivers.

The only remaining possibility is that an enable VARIABLE is used instead of an enable SIGNAL, but since constraints cannot be applied to VARIABLES, this cannot be correct either.

Apparently *the enable signal must always be enabled*, since there is no way of implementing correct disabling.

- 8. Since the RAM is always enabled, the RAM is continuously working. However, the design does not continuously access the RAM, and the data and/or address signal may change after an access. In case the last performed operation was a read operation, a change in the data and/or address signal does not matter. But if the last performed action was a write operation, any change in the data and/or address signal has a disastrous effect: the RAM contents are unintentionally overwritten. The only way to avoid this effect is to be *always reading the RAM, unless explicitly a write operation has to be carried out.* So after a write operation, the read\_write signal is immediately adjusted so that the writing of the RAM only takes place when correct data and address signals are present.

- 9. Let us consider the read operation. Several cases can be distinguished for the read operation:

- Only a read operation is performed.

- The read operation is performed after certain conditions have been met. The determination of these conditions is implemented in hardware as a boolean network. This network evidently takes some amount of time before the read operation can start.

- Furthermore, it is possible that a decision is made on which data is read, whereas every read operation can be preceded by some decision. Since every decision implies another boolean network, it is most likely that the read-operations are preceded by different amounts of time.

- It is also not unlikely that a read operation is followed by some sort of calculation on the read data. This calculation also takes time in hardware and again different amounts of time can be expected.

Now two problems arise:

- 1. There is no way of predicting the amount of time a synthesized network (boolean network, network for calculation) takes.

- 2. Every signal (read\_write, data, address, enable) can have only one constraint, while the preceding indicates that all the different cases ask for different constraints (meeting one constraint most likely violates other constraints).

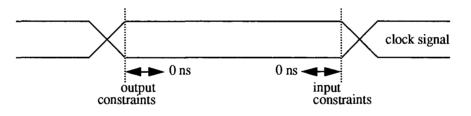

To solve these problems, the constraints could be determined iteratively. This iterative determination starts by giving the various output signals an output constraint of 0 ns after the last active edge of the clock; the input signal (data coming from the RAM) is given an input constraint of 0 ns before the next active edge of the clock. In fact this means that the determination starts with the assumption that there is no preceding boolean network before a read operation and no following calculation after the read operation. The start of the constraint determination is depicted in figure 16.

FIGURE 16. Start of iterative constraint determination

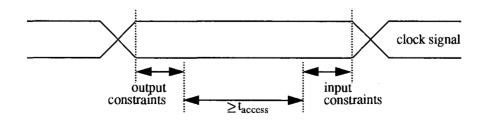

Starting with constraints of 0 ns, the synthesis tool could issue an error about the times minimally needed for the boolean network and for the calculation. These times are then the new constraints in the iterative process of constraint determination. The correct constraints can thus be found. Note that the time between the output constraints and the input constraints must be at least equal to the response time of the RAM, otherwise there is not enough time to perform an operation on the RAM. The end of the constraint determination is shown in figure 17.

FIGURE 17. End of iterative constraint determination

It is not known whether there is a synthesis tool that reports such a warning. It is also unknown whether the synthesis tools report the time minimally needed for each and every read operation or only for the first read operation that cannot be successfully implemented with the given constraint. This could mean that the designer is *iteratively determining the constraints*, while in the end the conclusion might be that the needed input and output constraints cannot be met.

Note that the constraints on the signals for write operations coincide with the constraints for read operations; the constraints would have been adversary if the read operation is implemented in the same clock cycle when it is needed. Actually this is another reason for anticipating the read operations.

10. The memory part of the RAM has to modelled but is not synthesized. However, there must be an EVENT that triggers the VHDL model of the memory during simulation. (Actually, this is another reason for using SIGNALS and not VARIABLES since only SIGNALS have EVENTS defined on them in VHDL.)

Normally the EVENT to use as a trigger would be an EVENT on the enable signal (see also [14] and [15]):

IF enable'EVENT AND enable = '0' THEN

..... -- memory model

END IF;

Since the enable signal is always enabled, this can no longer be the case. An EVENT on another signal must be the triggering EVENT for the memory. Let us review all other possibilities:

### • Read\_write signal

For this signal EVENTS take place when no operation on the RAM is needed (see consideration 9). Also, more seriously, there could be a need for a new operation on the RAM when no EVENT occurs on the read\_write signal. For instance, when during some subsequent clock cycles the design is continuously reading (writing). Therefore the read\_write signal cannot be used for triggering the memory.

### Data signal

Data is only offered to the RAM in case of a write operation. Using the data signal as trigger makes read operations unsimulatable. So the data signal cannot be used for triggering also.

### • Address signal

Using the address signal for triggering implies a restriction: an *operation on the* same position in the register (and thus in the RAM) can only be implemented when at least one operation on another position is in between the two operations. This however does not present the behaviour of a real RAM. So the address signal can be used for triggering as long as the design does not violate the restriction.

### • A combination of signals

A combination of several of the above signals could be used for triggering the memory. All these signals are simultaneously updated during simulation. Since there is no guarantee about the order of updating, there is no way to predict the order of the EVENTS. Since there is no way to predict the order of the EVENTS, the simulation order of processes is undetermined. Simulations consequently become unreliable. This violates the PCALE Design Flow philosophy severely and is therefore useless.

Clocked RAM

Another possibility is the use of a clocked RAM instead of an asynchronous RAM. Here the problem arises that data is sampled at the active edge of the clock, which means that it is not possible to generate a write or read operation halfway the clock cycle in order to write data into the RAM or read data from the RAM in that clock cycle. When an operation is needed, the read\_write (and data signal possibly) must be generated so that the clocked RAM copies or delivers the data in the *next* clock cycle. This implies two restrictions.

- 1. Since every read operation already had to be anticipated one clock cycle, every write operation followed by a read operation must a least be separated by three clock cycles in order to perform the operations.

- 2. Write operations must be delayed one clock cycle. Read operations must be completed one extra clock cycle earlier to a total of two clock cycles.

As both restrictions are unacceptable, the RAM cannot be modelled as a clocked RAM.

Apparently, the only useful solution is the use of the *EVENTS on the address signal as the triggering EVENTS* for the memory model during simulation. This means that the design must comply with the restriction for separating operations on the same position.

However, this restriction can be relaxed a little. Since data is read before the clock cycle in which the data is needed, this data has to be retained during the active edge of the clock. This is done by sampling the data in a sampling register. This register has a size equal to the wordlength of the RAM. This sampling register allows for two read operations on the same address after each other. No EVENT occurs for the address signal, but the needed value is still present in the sampling register.

From the above considerations, the following restrictions are deducted:

- The number of operations per clock cycle is limited to one.

- Read operations are anticipated one clock cycle at least. Write operations are not anticipated.

- A read (write) operation after a write (read) operation or vice versa or two write operations after each other on the same address, are separated by at least one operation on another address. Two read operations after each other on the same address are allowed.

These restrictions are further referred to as the *replacement restrictions*. Only if a design complies with these replacement restrictions, can the design be converted while preserving design functionality.

The considerations of this chapter form the basis for the VHDL models of the memory and the addressgenerator. The VHDL model of the memory is listed in appendix E. An *example* of the VHDL model of the addressgenerator is listed in appendix F since the addressgenerator is different for every design and RAM.

## 4.3. Adjustments for simulation

When the replacement tool performs the register replacement, the HL VHDL description has to be changed in several ways. The following adjustments are needed to obtain the descriptions that can be simulated to verify functional correctness after replacement:

### • Insertion of package declaration and package creation

Type conversion functions from integer to std\_(u)logic and vice versa are needed for the replacement. These conversion functions are defined in a package. Some symbolic constants also are defined in this package; the constants are used in the inserted VHDL code because they enhance readability. This package has to be made "visible" to the entity in which the register has been replaced through a package declaration. The package itself has to be created with the correct contents, for instance the correct constant value for the response time of the RAM has to be defined in the package.

### • Insertion of component declarations and configurations

The VHDL descriptions of the RAM and of the addressgenerator are defined in a separate file. Since these descriptions are referred to as components in the new HL description, both declaration and configuration of these components have to be inserted at the correct position in the altered entity.

### • Insertion of signals for communication with RAM

The signals that stem from the design and that control the RAM (which is added as a component in the design), must be declared inside the entity.