#### **MASTER**

A small digital signal processor for Philips from specification via IDaSS and VHDL to silicon

Oerlemans, R.V.M.

Award date: 1994

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Eindhoven University of Technology Department of Electrical Engineering Digital Information Systems Group

Master thesis report September 1993 - March 1994

# A small Digital Signal Processor for PHILIPS

From specification via IDaSS and VHDL to silicon

By ing. R.V.M. Oerlemans

Supervisor prof. ir. M.P.J. Stevens Coach dr. ir. A.C. Verschueren

The department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of student projects and graduation reports.

#### **Abstract**

The Digital Information Systems group of the Eindhoven University of Technology has developed an Interactive Design an Simulation System (IDaSS) for Ultra Large Scale Integration (ULSI) of digital circuits. With this tool it is possible to design and simulate a microcontroller on a very high level. Philips wanted to verify the use of IDaSS as a design tool. This has been done through designing and simulating the microcontroller MicroDsp with IDaSS after the functional specification of this chip had been approved. Then an implementation of the microcontroller in VHDL had to be made. This VHDL implementation will be used to create the MicroDsp chip layout using a silicon compiler. The size and performance of this chip give an indication of the benefits and disadvantages of IDaSS as a design tool. This report describes the design of the microcontroller MicroDsp. It is a chip with an 8-bit reduced instruction set microprocessor combined with an arithmetic accelerator unit, a timer unit, a serial interface and internal program and data memory. It provides a controller function and includes low-end digital signal processing capability for special applications. The chip is being developed in cooperation with Philips Semiconductors in Eindhoven. The Eindhoven University of Technology (TUE) is a partner in the development of this chip.

Philips has made a specification [MDSP93] of the MicroDsp. This specification is used for the design of the MicroDsp in IDaSS. During the design phase I have made modifications on the specification, erased errors and added new features. A new specification [MDSP94] was made that will be used to design the chip.

The MicroDsp microcontroller with the following elements:

- Peripheral Controller Cell (PCC)

- Arithmetic Accelerator Unit (AAU)

- PCC program memory of 4096+64 words of 16 bits

- PCC data RAM of 256 bytes

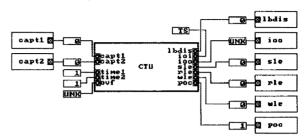

- 16 bit Capture Timer Unit (CTU)

- 10 I/O ports

- I<sup>2</sup>C bus interface and monitor control unit (IICC)

In this report the design in IDaSS and VHDL of the Capture Timer Unit and the I<sup>2</sup>C bus interface and monitor control unit are described.

An I<sup>2</sup>C bus interface and monitor control unit is used to control the MicroDsp with a "host" computer (PC). Communication is done via a serial two wire link. This means that a monitor program that is running on the PC can influence the progress of the program running on the MicroDsp. For example, the monitor program can start and stop the MicroDsp or read IO bus information or read the contents of a register of the PCC.

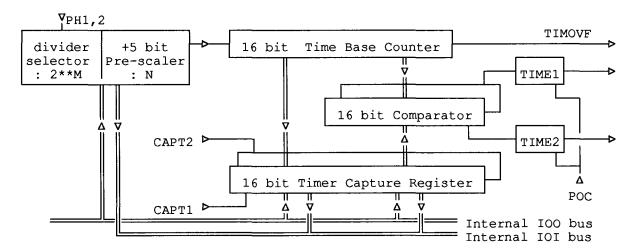

A capture-timer unit (CTU) is a combination of a capture unit and a timer unit. A timer unit is a time-base counter that counts a predefined number of clocks and then gives an interrupt. A capture unit is an element that can read and store the time in the time-base counter on the moment that a capture command is given.

All parts of the MicroDsp have been designed in IDaSS by the Eindhoven University of

Technology. The PCC processor and the program RAM have been made by Simons and Vostermans, the AAU coprocessor and the data RAM have been created by Verschueren while the Capture Timer Unit, I<sup>2</sup>C and Control, IO ports and MicroDsp toplevel have been build by me.

It was also the intention to describe all parts of the MicroDsp in VHDL. Therefore Simons and Vostermans have converted their IDaSS PCC to VHDL. The VHDL AAU has been made by Brand from Microtel. The Capture Timer unit and I<sup>2</sup>C and Control unit have been translated into VHDL by me. A VHDL description of the IO ports has not yet been made. For the program RAM and data RAM simple VHDL modules are used.

Designing with IDaSS has been done fast compared to the time necessary to develop such a processor immediately in VHDL or in a lower level description language. With a tool like IDaSS the efficiency and quality of the definition of new IC's can be improved considerably. If IDaSS is going to be used by Philips as a design tool it has to be accepted by a tool support group such as for example ED&T. A lot of disadvantages then have to be improved.

# Table of contents

| 1 Introduction                                 | 7   |

|------------------------------------------------|-----|

| 2 IDaSS                                        | 11  |

| 3 MicroDsp                                     | 15  |

| Peripheral Controller Cell (PCC)               |     |

| Arithmetic Accelerator Unit (AAU)              |     |

| I <sup>2</sup> C interface and Control (IICC)  |     |

| Inter-IC (IIC)                                 |     |

| Program memory access ports (MADT)             |     |

| External signal override controls (FCTL)       |     |

| Program address register (PAD)                 |     |

| IO-bus select address and data capture (IOBUS) |     |

| Execution start control (XCTL)                 |     |

| System status register (STAT)                  |     |

| Mail port (MAIL)                               |     |

| Program type control (PRGTYPE)                 |     |

| Monitor control (MONCTRL)                      |     |

| Stop control (STOPCTRL)                        |     |

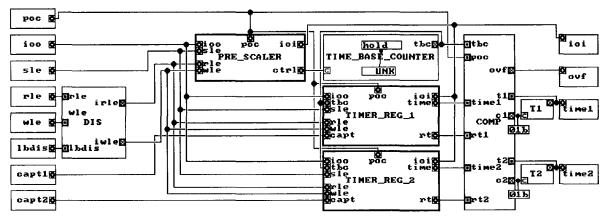

| Capture Timer Unit (CTU)                       |     |

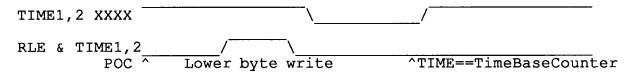

| Time-base counter (TIME_BASE_COUNTER)          |     |

| Prescaler (PRESCALER)                          |     |

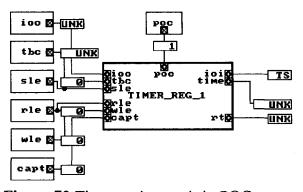

| Timer-register unit (TIMER_REG)                |     |

| Dual comparator (COMP)                         |     |

| Time output registers (T)                      |     |

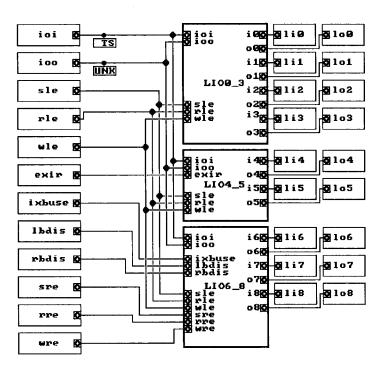

| I/O ports (LIO)                                |     |

| Data RAM (DRAM)                                |     |

| Program RAM (PRAM)                             |     |

|                                                |     |

| 4 VHDL                                         | 87  |

| IICC and CTU                                   |     |

| 2200 and 020                                   | / 2 |

| 5 Results                                      | 93  |

| 6 Conclusions                                  | 95  |

| Literature                                     | 98  |

| EJENJERENEN                                    | /(  |

### 1 Introduction

Philips wants to verify the use of IDaSS as design tool for their intergrated cirquits. A microprocessor is one kind of chip that Philips makes. Designing a new type of microprocessor is something that is only done by few because the world simply doesn't need many different microprocessors. Most designers try to speed up existing microprocessors. Only for a special kind of application a new type of microprocessor will have to be designed.

In one of the laboratories of Philips Semiconductors, such a special application is being developed. It is the controlling of a electric motor that is used in video recorders and disk drives. The controlling of the speed of such a motor has to be very accurate. Therefore a very fast but small and cheap microprocessor is needed to compute the speed and acceleration of the motor and to control the current that drives the motor. Very fast but small and cheap seem contradictive, but if the microprocessor only needs to perform a limited set of instructions this looks possible.

#### Developing a chip

In this document, you will find a report of the design of a microcontroller called the MicroDsp. The MicroDsp is a microcontroller with an 8-bit reduced instruction set microprocessor combined with an arithmetic accelerator unit, a timer unit, a serial interface and internal program and data memory. It provides a controller function and includes low-end digital signal processing capability for special applications. The chip is being developed in cooperation with Philips Semiconductors in Eindhoven. This is done at the Product Concept and Application Laboratory in Eindhoven (PCALE). The laboratory has several groups such as a group for telecommunication systems, a television group and an industrial group. The industrial group has a subgroup called Motor Control. For this group, J. den Ouden has made a functional specification of the MicroDsp.

The Eindhoven University of Technology (TUE) is a partner in the development of this chip. The Digital Information Systems group has developed an Interactive Design an Simulation System (IDaSS) for Ultra Large Scale Integration (ULSI) of digital circuits. The designer of this tool IDaSS is Ad Verschueren. With IDaSS it is possible to design and simulate a microcontroller on a very high level. Philips wants to use IDaSS for the verification of the functional specification of the MicroDsp. This will be done through simulation of an IDaSS implementation of the MicroDsp. If the functional specification is approved, an implementation of the microcontroller in VHDL must be made. This VHDL implementation can be used to create the MicroDsp chip layout using a silicon compiler. The size and performance of this chip give an indication of the benefits and disadvantages of IDaSS as a design tool.

#### Project team

At the TUE, the Digital Information Systems group has formed a MicroDsp project-team under leadership of professor Stevens. This team exists of Ad Verschueren, Wido Kruijtzer, Bart Vostermans, Peter Simons and myself.

Philips has two divisions working on the MicroDsp: PCALE and MicroTel. At PCALE Jos den Ouden, Roland Broekman, Ewout Rotte and Edwin Warrens work on the MicroDsp. The MicroTel team consists of Ronald Kemp and Hjalmar Brand.

In Tabel I a task overview is given of the people that are involved in the development of the MicroDsp:

Table I Relation between project items and designers

| Item Person          | AV | wĸ | BV  | PS  | во    | JdO | RB | ER | EW | RK | нв |

|----------------------|----|----|-----|-----|-------|-----|----|----|----|----|----|

| Toplevel             |    |    |     |     | s/i   | s   |    |    |    | v  |    |

| PCC                  |    |    | i/v | i/v |       | s/h |    |    |    |    |    |

| AAU                  | i  |    |     |     |       | s/h |    |    |    |    | v  |

| CTU                  |    |    |     |     | s/i/v | s   |    |    |    |    |    |

| I2C                  |    |    |     |     | s/i/v | s   |    |    |    |    |    |

| I/O ports            |    |    |     |     | s/i   | s   |    |    |    |    |    |

| Program RAM          |    |    | i   | i   | s     | s   |    |    |    |    |    |

| Data RAM             | i  |    |     |     | s     | s   |    |    |    |    |    |

| IDaSS Tool           | đ  |    |     |     |       |     |    |    |    |    |    |

| IDaSS->VHDL Compiler |    | đ  |     |     |       |     |    |    |    |    |    |

| PCC C Compiler       |    |    |     |     |       |     |    |    | đ  |    |    |

| PCC Assembler        |    |    |     |     |       |     |    |    | đ  |    |    |

| PCC Simulator        |    |    |     |     |       |     | đ  |    |    |    |    |

| Applications         |    |    |     |     |       |     |    | m  |    |    |    |

#### Abbreviations:

RK

HB

| AV  | = | Ad Verschueren       | d | = | design        |

|-----|---|----------------------|---|---|---------------|

| WK  | = | Wido Kruijtzer       | h | = | hand layout   |

| BV  | = | Bart Vostermans      | i | = | idass         |

| PS  | = | Peter Simons         | m | = | motor control |

| BO  | = | <b>Bob Oerlemans</b> | S | = | specification |

| JdO | = | Jos den Ouden        | v | = | vhdl          |

| RB  | = | Roland Broekman      |   |   |               |

| ER  | = | <b>Ewout Rotte</b>   |   |   |               |

| EW  | = | Edwin Warrens        |   |   |               |

Ronald Kemp

Hjalmar Brand

As can be seen in Tabel I, my part of the development of the MicroDsp is the rewriting of the specification of the MicroDsp toplevel, I<sup>2</sup>C, CTU, RAMs and IO. Furthermore the IDaSS design and simulation of these blocks and the VHDL generation of the I<sup>2</sup>C and CTU blocks.

#### About this report

The next chapters will explain how the MicroDsp has been developed. In chapter 2 is explained how IDaSS can be used for the design of a microcontroller. In chapter 3 the development of the parts of the MicroDsp that have been designed by me will be described in detail. Other parts of the MicroDsp are described globally. In this chapter the paragraph numbering refers to the hierarchy of the MicroDsp design. For example, if a schematic is described at paragraph 3.1, a subschematic will be described at paragraph 3.1.1, etc. A paragraph is partitioned in three sections that represent three developing steps: specification, design and simulation. An example of a paragraph that describes the capture timer unit is:

```

3.1 Capture Timer Unit (CTU)

CTU specification

CTU design

3.1.1 Prescaler Unit (PRESCALER)

PRESCALER specification

PRESCALER design

...

PRESCALER simulation

3.1.2 Timer Register Unit (TIMER_REG)

...

CTU simulation

3.2

```

Chapter 4 describes the VHDL code generation of the CTU and the I<sup>2</sup>C units. Finally, the last chapter will describe the results and give conclusions of my part of the developing of the MicroDsp.

#### 2 IDaSS

The MicroDsp has been designed in IDaSS. IDaSS is an interactive design and simulation environment for digital circuits. It is targeted towards VLSI and ULSI designs of complex data processing hardware (microprocessors, coprocessors and signalprocessors of all kinds). It can also be used for simpler designs, as long as the complete design is a synchronous machine (a single clock source for all clocked elements in the design). Simulating asynchronous logic with internal feedbacks is impossible with IDaSS, because the built-in simulator is not designed to do so (the results will not mirror actual hardware behaviour).

IDaSS describes a design as a tree-like hierarchy of schematics. The schematics contain elements like registers, ALU's, memories, state machine controllers and the like, and are entered graphically. Rectangles (called 'blocks') represent all schematic elements, which are connected by lines representing the (bidirectional) buses. Small squares at the boundaries of the rectangles represent the input and (three-state) output ports of the elements, these are called 'connectors'. The connectors come in several shapes to make a distinction between input, (disabled) output, bidirectional and control connectors.

A controller can test and control the elements of the schematic it is placed in, and can change it's state based upon test results. Controllers can be placed in a schematic just like all other blocks. There operational characteristics are entered in textual form, describing a state machine. The language used can describe microprogrammed controllers (including a subroutine stack) and Moore state machines. Tests done by the controller can only be based upon directly clocked elements in the schematic.

Elements in a schematic can also be controlled by adding a 'control connector'. This connector can be connected to any bus in the system, the value of which will determine the functions of that block. A textual PLA-like specification 'couples' the values on the bus with the functions to be executed.

IDaSS is targeted towards ULSI by allowing multiple schematics and controllers to be present in a single design. This is done by allowing 'lower level' schematics to be placed in a schematic as a single element, thus forming a hierarchical 'tree' of schematics.

Controllers can test and control blocks placed in schematics at lower levels in the hierarchy. Controllers can also (to some extent) control other controllers in their own or lower level schematics. Synchronisation of controllers is simplified by the use of special 'semaphore' bits in registers and a user-defined set of 'signals' which can be used for system-wide communication between controllers.

#### IDaSS connector symbols

IDaSS uses different symbols for connectors, as shown in Figure 1:

Figure 1 Connectors

For a continuous output, the symbol for an enabled output is used. Three-state outputs show their state by toggling between the symbols for enabled and disabled outputs.

#### **IDaSS** elements

IDaSS only knows a few basic elements. With these elements a complete schematic can be build. The elements are:

- Register

- Buffer

- Constant

- Operator

- Memory

- Schematic

- State controller

A register is a block that contains a number of clocked memory elements. The width of the register determines the number of elements used. An IDaSS register can hold, load, reset, set, increment or decrement. The register's function is controlled by a state controller or by a special connector at the register. A buffer is block that has an input, an output and an optional control connector. This control connecter determines if the buffers output is equal to the input (enabled) or if the output is floating (tree-state). A constant is a block which contains a constant value, but looses that value if a clock tick passes. An operator is a block that may contain one ore more functions. A function is a relation between an output and one ore more input connectors of the operator. An operator can be seen as a combinatorial network with AND's OR's etc. A memory is a block that may contain data. It can be RAM, ROM, FIFO, LIFO, etc. A schematic is a block that may contain several subblocks. In this way a hierarchical structure can be brought into the design. A state controller is a special block that is a combination of a state-register and a combinatorial network which determines the next

state. In every state, the controller controls other blocks to execute a function that is specified in that state. The next state is actually controlled by the contents of the registers in this schematic or lower level schematics. There are no wires connected on the state controller: test and control lines are hidden.

#### **IDaSS** busses

Busses are used to connect blocks. A bus is a line that is connected to one or more connectors of blocks in the schematic. A bus can be several bits wide. The width of a bus is always the same as the width of the connectors the bus is connected to.

#### **IDaSS** viewers

In order to have a continuous display of a register's contents or bus value, we can place a 'value viewer' on the schematic. A value viewer is a box that is connected to a register or a bus and displays its value. A 'function viewer' indicates the function a block is performing, for example: the function viewer of a register could indicate 'load' or 'reset'.

#### **IDaSS borders**

Every block in an IDaSS schematic has a border. The border is thin if this block is the lowest level in the schematic. A thick border indicates that the block consists of more elements. This is a so called lower level schematic. A grey border is used to indicate a state controller.

#### IDaSS automatic document generation

IDaSS can automatically generate a text containing documentation for almost any block in the system. It is also possible to generate documentation for the complete set of signals, any schematic (with all blocks below it in the hierarchy) or the complete system at once. The text only contains actual design information, no graphical (schematics) or current state information. Comments appended to the design elements by the designer are included. Because the documentation system extracts actual information from the design, the comments need only clarify the intended function of the design elements -what they are used for, not what they are. The text is in a 'flat' ASCII format, and is intended to be reworked with a suitable word processor.

#### IDaSS filing and library management system

All files used to store blocks and/or signals are text files in a flexible and compact format. They contain not only the design, but also the state of the simulation at the time the file was created and any documentation attached to the system.

## 3 MicroDsp

The MicroDsp is a microcontroller with a 8-bit RISC microprocessor named Peripheral Controller Cell (PCC) combined with an Arithmetic Accelerator Unit (AAU), a Timer Unit (CTU), an I<sup>2</sup>C serial bus interface and internal program and data RAM. It should provide a controller function and should include low-end DSP capability for a wide range of applications. The MicroDsp is intended to be a solution suited to many problems as it should provide just the amount of performance required using minimum silicon and supply current. This is, for example, important for portable applications.

A MicroDsp test chip of the Peripheral Controller Cell (PCC) together with the Arithmetic Accelerator Unit (AAU) is to be designed to verify correct implementation of the PCC and AAU blocks, to develop and debug PCC systems and programs and to set up working prototypes of applications implemented with the PCC/AAU combination.

Philips employee J. den Ouden has written the specification [MDSP93] of the MicroDsp. The title of this specification is 'MicroDSP: PCC plus AAU test chip specification 1.1', and it is dated 15 Sept. 1993. This specification is used for the first design of the MicroDsp in IDaSS. During the design phase, modifications have been made on this specification, errors have been erased and new features have been added. This is done by me in cooperation with J. den Ouden. A new specification [MDSP94] was made and it has been used for my final design of the MicroDsp. This specification has version 1.2 and is dated 18 Jan. 1994.

#### MicroDsp specification

The MicroDsp is a microcontroller with the following elements:

- Peripheral Controller Cell (PCC)

- Arithmetic Accelerator Unit (AAU)

- PCC program memory of 4096+64 words of 16 bits

- PCC data RAM of 256 bytes

- 16 bit Capture Timer Unit (CTU)

- 10 I/O ports

- I<sup>2</sup>C bus interface and monitor control hardware (IICC)

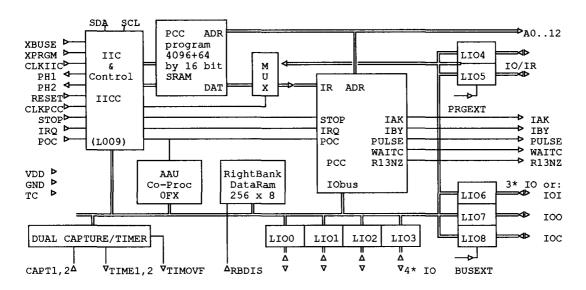

In Figure 2 the functional block diagram of the MicroDsp emulator/test chip is given.

The 8-bit RISC microprocessor called PCC is the centre block of the MicroDsp. This PCC has an address bus called ADR and a instruction bus called IR. Via these busses the program memory is connected to the PCC. This memory provides the PCC instructions needed to run. Via the IObus the peripherals Arithmetic Accelerator Unit (AAU), Capture Timer Unit (CTU), Inter IC bus interface and Control unit (IICC), and internal data memory (DATARAM) and 9 I/O ports (LIO) are connected. The input and output pins of the chip are given according to the specification in the pinning list below:

Figure 2 Functional block diagram of the MicroDsp

### MicroDsp test chip pinning:

| #4     | pin name               | <u>type</u> | description                                                                      |

|--------|------------------------|-------------|----------------------------------------------------------------------------------|

|        | VDD, GND               | pwr         | Minimum number of power pins                                                     |

| 1      | TC<br>CLKIIC           | in<br>in    | Test chain Control input<br>I <sup>2</sup> C controller clock                    |

|        | CLKPCC                 | in          | PCC/AAU system clock                                                             |

| 1<br>2 | PH1, PH2               | out         | internal generated PCC system phase clocks                                       |

| 1      | RESET                  | in          | initialize monitor I <sup>2</sup> C and control hardware                         |

| 1      | XPRGM                  | in          | external program enable                                                          |

| ī      | XBUSE                  | in          | external IO bus enable                                                           |

| 1      | POC                    | in          | PCC Power On Clear                                                               |

| 1      | IRQ/TCI1               | in          | PCC Interrupt Request / Test Chain In                                            |

| 1      | IAK/TCO1               | out         | PCC Interrupt Request / Test Chain In PCC Interrupt Acknowledge / Test Chain Out |

| 1      | IBY                    | out         | PCC Interrupt Busy                                                               |

| i      | SDA                    | in/out      | I <sup>2</sup> C data                                                            |

| 1      | SCL                    | in/out      | I'C clock                                                                        |

| 1      | STOP                   | in          | PCC STOP control                                                                 |

| 1      | WAITC                  | out         | PCC WAIT Cycle indicator                                                         |

| i      | PULSE                  | out         | PCC PULSE enable signal                                                          |

| 1      | R13NZ                  | out         | PCC R13 Not Zero indicator                                                       |

| 8      | LIO0[07]               | in/out      | Left Bank Port 0                                                                 |

| 8      | LIO1[07]               | in/out      | Left Bank Port 1                                                                 |

| 8      | LIO1[07]<br>LIO2[07]   | in/out      | Left Bank Port 2                                                                 |

| 8      | LIO2[07]               | in/out      | Left Bank Port 3                                                                 |

| 8      | LIO3[07] IR[07]        | in/out      | Left Bank Port 4 / instruction input                                             |

| 8      | LIO5[07] IR[815]       | in/out      | Left Bank Port 5 / instruction input                                             |

| 8      | LIO5[07] IR[813]       | in/out      | Left Bank Port 6 / IO data in bus                                                |

| 8      |                        | in/out      | Left Bank Port 7 / IO data in bus                                                |

| 8      | LIO7[07] IOO[07]       | in/out      | Left Bank Port 8 / IO bus control                                                |

| 8      | LIO8[07] IOC:<br>0 SRE | out         | Select Right bank address Enable                                                 |

|        | 1 SLE                  |             | Select Left bank address Enable                                                  |

|        | 2 RRE                  | out         | Read Right bank data Enable                                                      |

|        |                        | out         | Read Left bank data Enable                                                       |

|        | 3 RLE                  | out         | Write Right bank data Enable                                                     |

|        | 4 WRE                  | out         | Write Left bank data Enable                                                      |

|        | 5 WLE                  | out         | Left Bank Disable for internal IO                                                |

|        | 6 LBDIS                | in          | <del></del>                                                                      |

| 1 2    | 7 RBDIS                | in          | Right Bank Disable for internal IO                                               |

|        | AOA12                  | out         | PCC Address                                                                      |

| 1      | TIMEOVF                | out         | TIME base counter OVerFlow                                                       |

| 2      | CAPT1,2/TCI2           | in          | Capture inputs, separate test chain inputs                                       |

| 2      | TIME1,2/TCO2           | out         | Timer outputs, separate test chain outputs                                       |

The MicroDsp is provided with Test Chain (TC) inputs and outputs. With this, almost all internal flip-flops can be tested. The flip-flops are chained, and the contents is serially transferred to the TCO pins. The MicroDsp has two Test Chain Inputs (TCI1,2) and two Test Chain Outputs (TCO1,2).

The internal and external IO transfers are done via two IO busses, IOI and IOO. The IOC bus is used to control the IO transfers. IO has been partitioned into two banks: Left Bank IO and Right Bank IO. If an IO device should be accessed, first the IO device should be selected with SLE or SRE combined with an IO address. Later data can be transferred using RLE, RRE, WLE or WRE. LBDIS and RBDIS are used to disable the internal IO. In this way external IO can be put on the same address as internal IO devices.

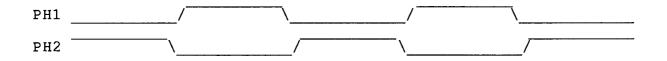

Clock timing for the MicroDsp is specified in the PCC specification [PCC93]. There are two non-overlapping clocks used: PH1 for the input phase and PH2 for the output phase. In the IDaSS design it was not possible to use seperate input and output phases because IDaSS only has one synchronisation point for both transactions.

Figure 3 Two non-overlapping clocks PH1 and PH2

The MicroDsp is provided with two reset pins: RESET and Power On Clear (POC). The RESET pin is used for the reset of the I<sup>2</sup>C and control part of the MicroDsp. The POC is used to reset the PCC, AAU and Timer and to Initialize the RAMs and IO.

For the communication with a remote PC, two serial IO pins are provided: SDA and SCL. These pins are specified in the I<sup>2</sup>C specification [I<sup>2</sup>C92]. SDA is the I<sup>2</sup>C serial data line, SCL is the I<sup>2</sup>C clock line.

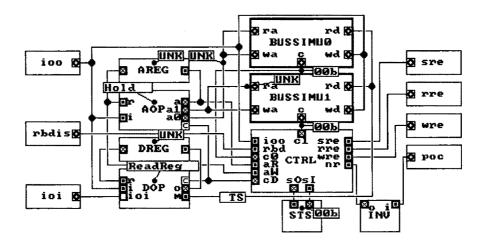

#### MicroDsp design

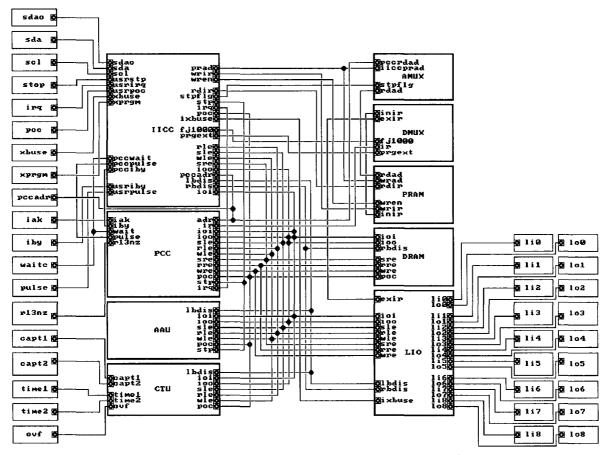

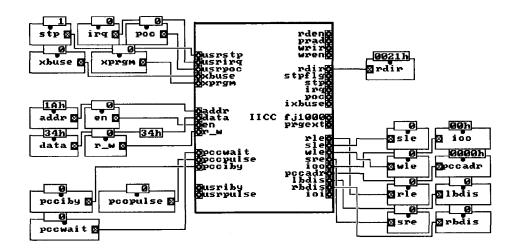

Designing the MicroDsp toplevel in IDaSS is done after the design of the elements of the MicroDsp was completed. Because a lot of connectors and signals were already specified, it was simple to connect the blocks. In Figure 4 the IDaSS design of the MicroDsp toplevel is given. In this figure, you will find the following elements:

- IICC PCC

- AAU • CTU

- AMUX DMUX

- PRAM DRAM

- LIO

The most important internal signals used to connect these blocks are:

| <u>name</u> | <u>bits</u> | description              |

|-------------|-------------|--------------------------|

| • sle       | 1           | select left bank enable  |

| • wle       | 1           | write left bank enable   |

| • rle       | 1           | read left bank enable    |

| • sre       | 1           | select right bank enable |

| • wre       | 1           | write right bank enable  |

| • rre       | 1           | read right bank enable   |

| • ioo       | 8           | io output bus            |

| • ioi       | 8           | io input bus             |

| • lbdis     | 1           | left bank disable        |

| • rbdis     | 1           | right bank disable       |

| • poc       | 1           | power on clear           |

| • irq       | 1           | interrupt request        |

| • stp       | 1           | stop                     |

There are more signals necessary to connect all blocks. In the next paragraphs these signals and blocks will be described in detail.

Figure 4 MicroDsp

#### 3.1 Peripheral Controller Cell (PCC)

The Peripheral Controller Cell (PCC) provides a very fast processor function optimised for bit field handling and quick event response. The PCC is based on the 8X305 RISC architecture, which is a proven concept for fast bit oriented control. Low transistor count makes a very small core design possible. Harvard structure, execution of most instructions in a single cycle of the two phase non-overlapping clock and keeping program memory, data and I/O accesses on-chip, mean that performance can be very high, mainly limited by program memory speed. A full custom design in C200DM technology has been realised (size: 1.06 mm2, worst case performance of 16 MIPS at 5 Volt, full static design, suitable for low voltage operation). An IDaSS design has to be made to be able to simulate the PCC with peripherals on a high level. A VHDL implementation has to be made to be able to synthesize the PCC with the use of a silicon compiler.

The basic architecture has been extended with an interrupt facility that has a one clock cycle interrupt latency and performs some context switching. Conditional jump execution is delayed by one clock wait cycle to allow use of relatively slow program memory. An accessory ROM generator is also available. PCC assembler and simulator are running on IBM-PC and Apollo.

PCC Features according to the Philips specification:

- Fetch, decode, execute 16 bit instructions in single 2 phase clock cycle

- Bit oriented instruction set (addressable single/multiple bit sub-fields)

- Separate busses for instruction, instruction address and 3-state IO

- Thirteen 8 bit general purpose working registers

- Source/destination architecture

- Single clock latency for interrupt, including context switching

- Wait cycle for conditional jumps (relaxed program memory spec)

- 8 kword (16 kbyte) program memory space

- Full static CMOS implementation

- Very small processor block size

- Very low supply current per MIPS

- Designed for testability (minimal)

#### **PCC** specification

The PCC is a high speed full static CMOS 8 bit micro-control RISC with a bit-oriented instruction set. The PCC has a Harvard structure and can fetch, decode and execute a 16 bit instruction in a single clock cycle (PH1,PH2).

Within one instruction cycle the 8 bit data processing path can be programmed to rotate, mask, shift and/or merge single or multiple bit sub-fields and, in addition, perform an ALU operation; in the same instruction an external data field can be input, processed and output to a specified destination. Likewise, single or multiple bit sub-fields can be moved from a given source to a given destination. To summarize: fixed or variable length data fields can be fetched, processed, operated on by the ALU and moved to a different location, all in a single two phase clock cycle.

To enable fast response on asynchronous hardware events without loss of performance an interrupt facility is provided which has a single clock response latency and which includes a context switch. Program memory receives a 13 bit address to access 16 bit instructions allowing a program of up to 16 kbyte. Data I/O is done via a separate 8 bit bi-directional three-state bus that multiplexes I/O data and addresses under control of 6 I/O control enables. The I/O bus also can be split in two separate busses, one for input and one for output. In-line PULSE instructions and the PULSE output provide an extra facility for fast control of user hardware without affecting program context.

When calculating a conditional program jump address (instructions XEC and NZT) the PCC inserts a wait cycle so that the program address can always be provided early in the memory access cycle. This allows use of relatively slow program memory. (This mode can be omitted for slower clocks).

#### Internal data registers

The PCC has 18 internal data registers, nine 8-bit registers can freely be used and nine others have (also) a special purpose. All register names are pre-declared assembler variables.

R0|R0I=AUX implicit second argument for ALU operations (ADD, AND, XOR)

R1..R6 6 general purpose 8-bit data registers

R7=IOL 8-bit register, copies Left Bank IO address in main program context. R7 is

automatically re-transmitted on interrupt return.

R10=OVF carry of the last add operation. OVF cannot be destination. OVF uses a

separate flag in interrupt context.

R11 used by the PCC assembler for subroutine return table index

R12,R13 general purpose 8-bit data registers.

XMIT to R12, R13 sends a data byte to the Left and Right Bank ports, not to

the register. (see XML, XMR instructions)

R14..R16 3 general purpose 8-bit data registers

R17=IOR 8-bit register, copies Right Bank IO select address in main program context

AUX has a separate interrupt context register and for both normal and interrupt context there is a shadow register in the ALU. The shadow register data is used as implicit data for ADD, AND and XOR operations. Both AUX registers and their ALU shadow registers are cleared at POC. The interrupt context AUX contents, but not its ALU shadow register, can be modified by moving data to R0I "MOVE Rn,R0I" (Note that this data only is used in interrupt context if AUX is specified as source data).

In main program context R7 and R17 are automatically written if IO addresses are selected, in interrupt context a SELect of IO does not affect R7 or R17. On interrupt return R7 is automatically re-transmitted to restore the main context Left Bank select address. If IOR is changed by the interrupt routine R17 has to be restored using MOVE R17,IOL before executing interrupt return.

R12 and R13 are used for the XML and XMR special XMIT instructions that send an 8 bit data byte to Left and Right bank IO ports. Internal registers R12 and R13 therefore cannot be loaded directly using XMIT.

If R13 contains a non-zero value the R13NZ output goes HIGH. This feature can be used to speed up and reduce code in "compare-and-set bit" operations with data and IO flags.

#### IO data bus

IO bus ports and/or data RAM are connected to the 8 bit 3-state user bus. A RAM block is commonly addressed via the Right Bank, while single ports reside on the Left Bank. To enable access of a RAM location or a port it can be selected by sending the port address on the bus using XMIT, MOVE, etc to IOR=R17 or IOL=R7 or the assembler directive SEL with an RIO or LIO address. These instructions put the 8 bit address value on the bus and assert the Right or Left Bank select enable. A RAM block latches the complete Right Bank select address, while a port that detects its address sets its select flag. A bank address or port select flag is valid until a new address is transmitted on the Bank it is assigned to. Port 000X on the Left Bank is automatically selected on reset (POC='1') and on interrupt acknowledge (IAK='1'), so it can be used for very quick interrupt service and/or as interrupt vector address.

Reading port data takes place in the PCC input phase (PH1), while address selects and data (re-)writes are done on the output phase (PH2). When accessing data on the IO bus, a bit field can be defined with a length of 1 to 8 bits and a LSBit position from 0 to 7. (If Length plus LSB position overflows the byte size, the bit field is truncated).

Note that the whole byte of an IO port is read in the input phase (PH1) and copied, even if only a part of the port bits is affected by the instruction, so that the modified bit field can be merged in the PCC and the complete byte can be written back in the output phase (PH2).

Port registers can be simple latches as the PCC performs the master flip-flop function (on PH1). Port latches are written on PH2, so port output latches can change during PH2.

#### PCC Instruction set

The PCC is a highly Reduced Instruction Set Controller (RISC) having only 8 basic 16 bit instructions most of which can be executed with a single clock. Four instructions operate on data (MOVE, ADD, AND and XOR), two conditional jumps (XEC, NZT) are available for program control and table handling, one instruction provides data constants (XMIT) and one makes jumps over the whole address range (JMP).

#### Data operation instructions

ALU data operation instructions MOVE, ADD, AND and XOR specify source and destination, rotation, or bit field position and length. Within one data operation instruction cycle, the 8 bit data processing path can be programmed to rotate, mask, shift and/or merge single or multiple bit sub-fields, and perform an ALU operation. AUX is implied argument for ADD, AND, OR and XOR operations. Increment (INC), complement (NOT) and inclusive or (OR) are single argument instructions: specified data source (register or IO bit field) is also destination. INC, NOT, OR, the four instructions for interrupt control and the PULSE instruction, all indicated with '+', are modified basic instructions that use OVF (not writable) as dummy destination for their code. MOVE Rn,R0I from register Rn other then R7 writes to the AUX register of the interrupt context, using OVF as destination code.

| 0 MOVE                           | Source to Destination used for data transport between register(s) and IO p                                                                                  | port(s)                                                                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| + DSI<br>+ ENI<br>+ RTI<br>+ RTE | clears interrupt enable flag<br>set interrupt enable flag (cleared at POC, IAK)<br>return from interrupt<br>return from interrupt set interrupt enable flag | (MOVE R7(0),OVF)<br>(MOVE R7(1),OVF)<br>(MOVE R7(2),OVF)<br>(MOVE R7(2),OVF) |

| 1 ADD                            | Source + AUX> Destination, update OVF provides arithmetic.                                                                                                  |                                                                              |

| + INC                            | Source/Destination + 1> Source/Destination increments data without using AUX or OVF                                                                         | (ADD Rx(R),OVF)<br>(ADD IOx(L),OVF)                                          |

| 2 AND<br>+ OR                    | Source .and. AUX> Destination can be used to isolate data bits and evaluate logic f Source/Destor. AUX> Source/Destination inclusive or of S/D with AUX     | Functions.  (AND Rx(R),OVF)  (AND IOx(L),OVF)                                |

| 3 XOR                            | Source .exor. AUX> Destination contributes to logic evaluations and arithmetic                                                                              |                                                                              |

| + NOT                            | Source/Destexor. FF> Source/Destination Complements data without using AUX.                                                                                 | (XOR Rx(R),OVF)<br>(XOR IOx(L),OVF)                                          |

#### Conditional jump instructions XEC and NZT

"Conditional" jump instructions XEC and NZT calculate a jump address on basis of a data source field. As source data access starts at the beginning of the instruction cycle a new address would be valid much later than for other instructions (sequential instructions start address increment in the previous cycle, JMP provides the full new address in the instruction). To prevent that XEC and NZT instructions reduce maximum operating speed a wait cycle is inserted, so that new addresses are valid early in a program memory access cycle for all instructions allowing relatively slow ROMs or long address setup times.

Conditional jump instructions XEC and NZT calculate new address bits to replace the lower 8 bits if source is register, or 5 bits if source is IO, of the program counter. For correct operation the target address must therefore be in the current 5 or 8 bit page. The PCC assembler ORG directive supports conditional page alignment.

4 XEC execute in page at (Displacement + SRC)

XEC provides indexed execution (on register or IO port), it is very powerful for constant table access and for indexed jump tables useful for subroutine return, vectored interrupt handling as well as state machine service. XEC replaces 8 bits or 5 bits in the program counter (before increment) and executes the instruction at the calculated address. If this instruction is not an accepted jump only one instruction is done and the program continues with the instruction following the XEC. If the XEC executes a JMP or a NZT (source non zero) the program continues at the jump address. XEC instructions may execute chained XEC instructions. If an instruction executed by a XEC is aborted by an interrupt the XEC itself will also be reexecuted after interrupt return. XEC instructions always insert a wait cycle.

5 NZT jump in page if Source not zero

Non-Zero-Transfer is used for program flow control and signal polling. If the source data is non-zero the NZT instruction replaces 8 bits (if source is register) or 5 bits (if source is IO bit field) in the program counter after incrementing. If the NZT source data is zero the program counter is simply incremented. NZT instructions always insert a wait cycle.

#### Load literal instruction XMIT

| 6 XMIT                    | Constant> Destination loads data into specified destination if register: 8 bit literal, if IO bit field: 5 bit literal                                                                 |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + XML<br>+ XMR<br>+ PULSE | send 8 bit literal to IO Left Bank (uses R12 as dummy destination) send 8 bit literal to IO Right Bank (uses R13 as dummy destination) send 8 bit literal to IO bus, assert PULSE line |

#### Unconditional branch instruction JMP

The unconditional JMP instruction enables jumps over the full address range.

7 JMP jump to Address

#### PCC design

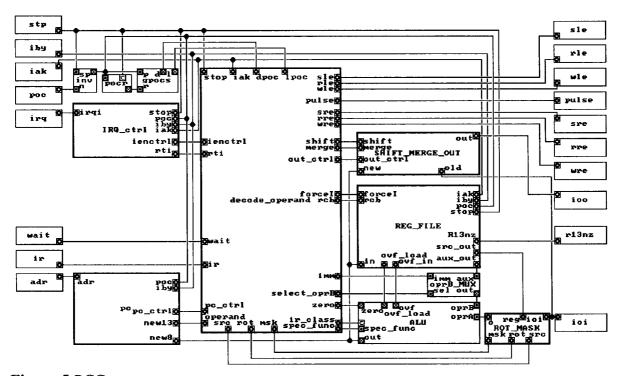

The PCC has been designed in IDaSS by B. Vostermans and P. Simons. They are employees of the Eindhoven University of Technology. Their design is given in Figure 5.

Figure 5 PCC

#### **PCC** simulation

The IDaSS PCC has been simulated by B. Vostermans and P. Simons. According to them the IDaSS implementation is corresponding the specification [PCC93] of the PCC. However, this has not been verified with the special PCCTEST program. The IDaSS PCC (version 2) is used in the MicroDsp toplevel schematic.

#### 3.2 Arithmetic Accelerator Unit (AAU)

The Arithmetic Accelerator Unit (AAU), a coprocessor for the PCC, is designed to speed up otherwise tedious byte-wise multiply/divide and shift operations for calculations with signed or unsigned integers in floating or fixed point data formats.

The AAU features signed (four-quadrant) and un-signed multiplication, division, normalise and adjust, in short format (both operandi 16 bits) and long format (operandi 16 and 32 bits). Short integer (16 bit) signed and unsigned multiplication also can be done while accumulating with previous result(s). In this mode overflow and underflow are detected and resulting values are clipped automatically to their appropriate maximums to prevent control calamities without any software overhead. The multiply-accumulate feature is very powerful for digital signal processing in control loops. Normalise and shift facilities of the AAU enable to implement relative fast floating point calculation routines.

#### **AAU** specification

AAU data registers X, Y, Z, CMD and STA are located in PCC IO 0xF0..0xFF. Starting access on addresses 0xF0 or >0xFA provides Burst Mode Access incrementing IO addresses automatically at consecutive accesses. The AAU allows "chained operations": intermediate results of formula evaluation may be left in AAU accumulator registers for re-use in next operations. Both features increase performance while reducing PCC code required.

Operations basically require one clock for initialise, 16 or 32 AAU clocks for execution and one to four AAU clocks for finishing. The PCC program may continue with other business while the AAU is BUSY.

| operation | clocks for word | for long  |

|-----------|-----------------|-----------|

| Multiply  | 18              | 34        |

| Divide    | 19              | 36        |

| shift     | n+1,<=17        | n+1, <=33 |

Together with the PCC the AAU provides a capability to do low end DSP calculations like about 640.000 digital filter stage calculations (multiply/accumulate/clip) per second (for C3DM: at 16 MHz clock).

Features:

- . multiply 16\*16 and 16\*32 bits

- . divide 16:16 and 32:16 bits (with overflow detection)

- . multiply 16\*16 accumulate (32 bits) with overflow clipping

- . Normalise (16/32 bit) for floating point operations

- . Shift left/right (16/32 bits) over 0..15/31 bits

- . All operations un-signed and signed, four quadrants

- . Results within 19 (short) or 36 (long) PCC clock cycles (worst case)

- . Chained operations may be used to reduce data moves

- . Burst Mode Access for optimal performance and reduced code

- . PCC may proceed during AAU operation

#### AAU design

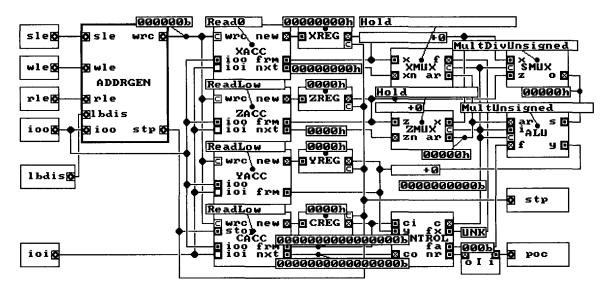

The AAU has been designed in IDaSS by A. Verschueren. This AAU is different from the handcraft AAU. In the IDaSS design most calculations are computed 2 cycles faster. Another difference is that the IDaSS AAU has a POC input while in the original design the POC line has to be connected to the STOP input. Furthermore, the handcraft AAU also provides a BUSY output while the IDaSS AAU does not have that output. The IDaSS design is given in Figure 6.

Figure 6 AAU

#### **AAU** simulation

The IDaSS AAU has been simulated by A. Verschueren. The first simulation gave an error for the division -18/3. This gave quotient -5 with remainder -3, witch is of course the same as quotient -6 with remainder 0, what should have been the answer. This error was a result of a wrong algorithm that was used for the divide action. This algorithm was also used for the handcraft AAU that was already implemented. In both designs this error then had to be erased. According to Verschueren the IDaSS implementation is not exactly corresponding the specification [AAU93] of the AAU because of differences in timing and pinning. On the other hand, the functional behaviour is according to the specification. This AAU is used in the MicroDsp toplevel schematic.

## 3.3 I<sup>2</sup>C interface and Control (IICC)

The MicroDsp can be controlled by a "host" computer like a Personal Computer (PC) via an on chip  $I^2C$  interface ( $I^2C$  = Inter-IC). Communication is done via a serial two wire link. This means that a monitor program that is running on the PC can influence the progress of the program running on the MicroDsp. For example, the monitor program can start and stop the MicroDsp or read IO bus information or read the contents of a register of the PCC. The  $I^2C$  device in the PC is called the master, and the  $I^2C$  device on the MicroDsp is called the slave.

The MicroDsp has to have the possibility to download PCC instructions into the program memory. For small PCC monitor programs an additional memory segment is available. Via I<sup>2</sup>C control the PC can start and stop PCC program execution and access control and status ports. In this way the PCC emulator running on the PC can access the PCC. All system information can be displayed on the screen and all writable ports can be modified from the keyboard.

Control hardware on the MicroDsp chip is kept to a minimum by locating most of the "intelligence" in the controlling monitor program of the PC, this in order to reduce design complexity and design risk while preserving maximum flexibility.

#### **IICC** specification

For the MicroDsp I<sup>2</sup>C interface a number of I<sup>2</sup>C addresses is reserved without looking at eventual conflicts with existing I<sup>2</sup>C devices. These are used to address MicroDsp control ports. The following ports are provided:

| <u>addr</u> | name | R/W | functional description                  |

|-------------|------|-----|-----------------------------------------|

| 10          | FCTL | R&W | External signal override controls       |

| 11          | PADH | R   | PCC ADR[812] state on last instruction  |

| 12          | PADL | R   | PCC ADR[07] state on last instruction   |

| 13          | LBAD | R   | PCC IO last Left Bank address           |

| 14          | RBAD | R   | PCC IO last Right Bank address          |

| 15          | IODT | R   | PCC IO last IOO data                    |

| 16          | MADH | R&W | PCC program memory address 5 upper bits |

| 17          | MADL | R&W | PCC program memory address 8 lower bits |

| 18          | MDTH | R&W | PCC program memory data 8 upper bits    |

| 19          | MDTL | R&W | PCC program memory data 8 lower bits    |

| 1 <b>A</b>  | XCTL | R&W | MicroDsp start control                  |

| 1B          | STAT | R   | MicroDsp status                         |

| 1C          | MAIL | R&W | MicroDsp debug port                     |

The following PCC system data access and control functions must be available from the hardware for the PC monitoring/debugging program:

| <u>unit</u>      |

|------------------|

| MADH/L, MDTH/L   |

| FCTL, XCTL       |

| FCTL, XCTL       |

| IODT             |

| PADH/L           |

| LBAD,RBAD        |

| IODT             |

| STAT             |

| FCTL, XCTL, IODT |

| FCTL, XCTL, IODT |

| MAIL             |

|                  |

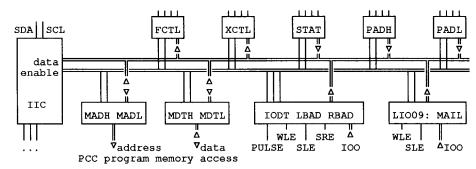

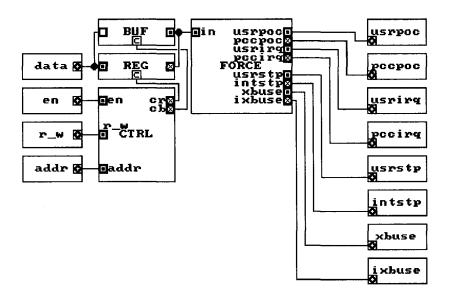

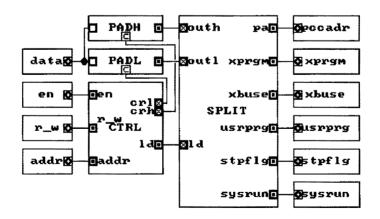

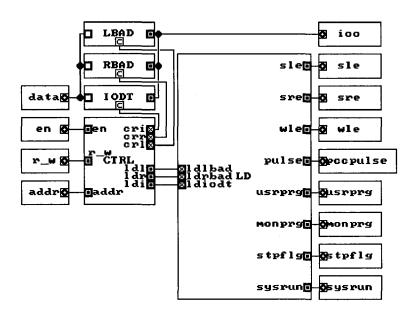

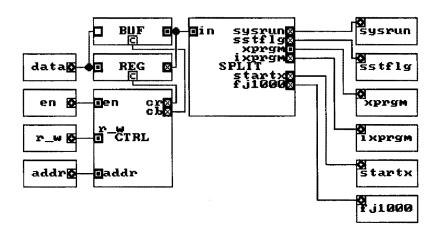

A functional block diagram of the IICC is given in Figure 7.

Figure 7 Functional block diagram of IICC

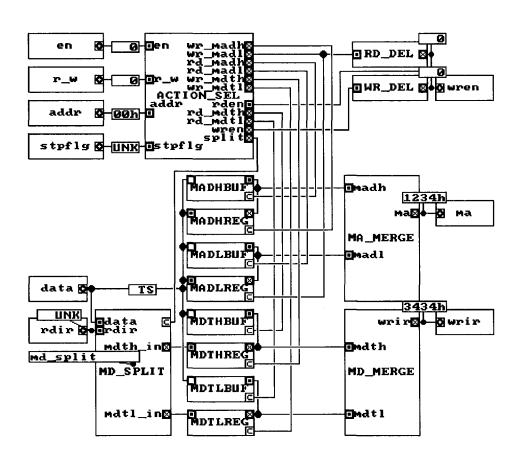

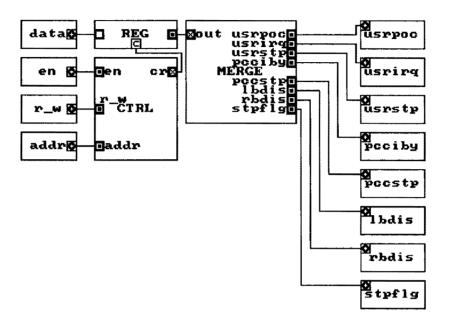

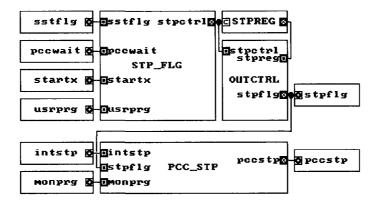

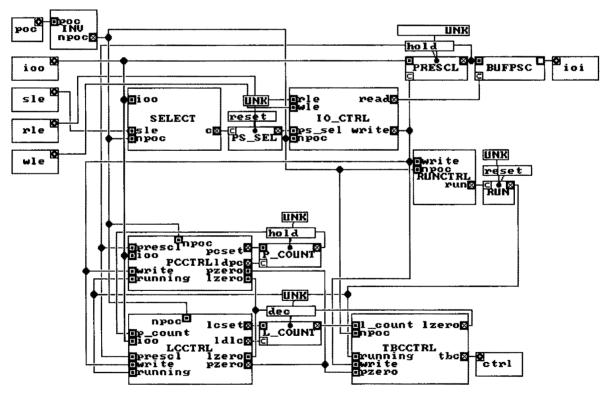

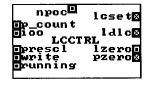

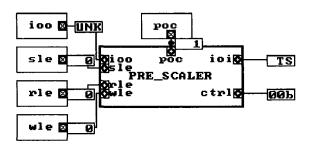

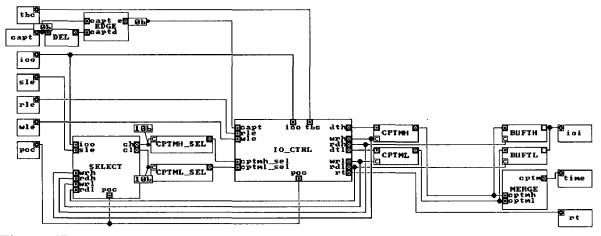

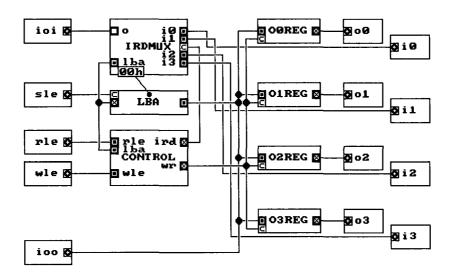

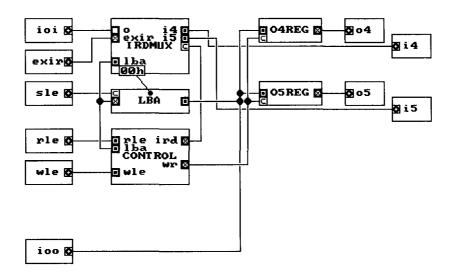

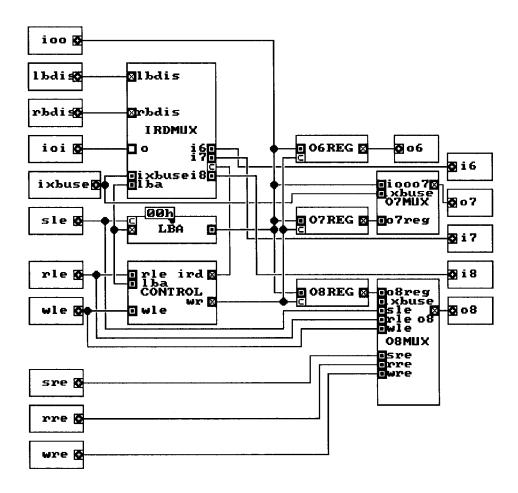

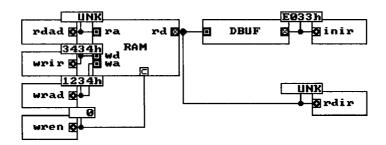

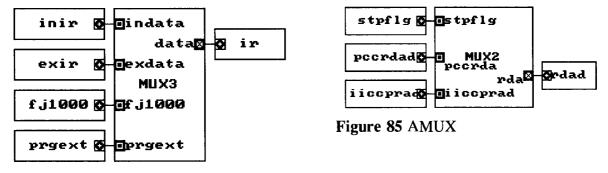

#### **IICC** design

In the IDaSS design of the IICC unit, we find the following elements:

- inter IC control unit (IIC)

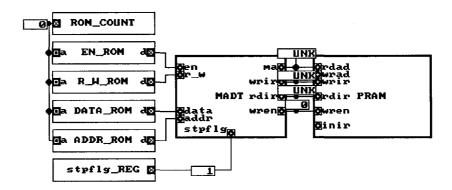

- program memory access unit (MADT)

- force control unit (FCTL)

- address state unit (PAD)

- IO view unit (IOBUS)

- start control unit (XCTL)

- status unit (STAT)

- mail unit (MAIL)

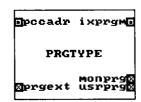

- program type determination unit (PRGTYPE)

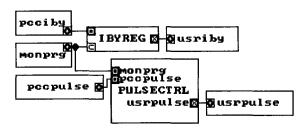

- monitor control unit (MONCTRL)

- stop control unit (STOPCTRL)

The IIC unit is the centre of the total IICC design. Globally, this block is a serial to parallel converter. It converts the serial information that is received from a PC host into bytes that can be read by the surrounding blocks such as MADT, FCTL etc. On the other hand if the PC

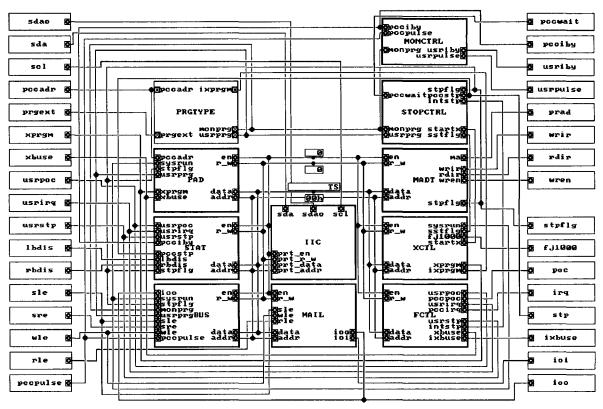

Figure 8 IICC

host has to read something from one of the IICC subblocks, these bytes will be coded into a serial bit stream, that will be transferred to the PC host. In the list below all signals are described.

#### External signals:

| name sda sdao scl                                                          | <u>bits</u><br>1<br>1                | description<br>serial data in<br>serial data out<br>serial clock                                                                                              |

|----------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • ioi • ioo • sle • wle • rle • sre • lbdis • rbdis                        | 8<br>8<br>1<br>1<br>1<br>1<br>1<br>1 | io input bus io output bus select left bank enable write left bank enable read left bank enable select right bank enable left bank disable right bank disable |

| <ul><li>rden</li><li>wren</li><li>prad</li><li>rdir</li><li>wrir</li></ul> | 1<br>1<br>13<br>16<br>1              | read program ram enable write program ram enable program ram address read instruction bus write instruction bus                                               |

| <ul><li>pccwait</li><li>pccadr</li><li>fj1000</li></ul>                    | 1<br>13<br>1                         | pcc wait<br>pcc address bus<br>force jump to 1000h                                                                                                            |

| <ul><li>stpflg</li><li>stp</li><li>usrstp</li></ul>                        | 1<br>1<br>1                          | stop flag<br>stop<br>user stop                                                                                                                                |

| <ul><li>poc</li><li>usrpoc</li></ul>                                       | 1<br>1                               | power on clear<br>user driven poc                                                                                                                             |

| <ul><li>irq</li><li>usrirq</li></ul>                                       | 1<br>1                               | interrupt request<br>user interrupt request                                                                                                                   |

| <ul><li>usrpulse</li><li>pccpulse</li></ul>                         | 1<br>1           | user pulse<br>pcc pulse                                                                                            |

|---------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| <ul><li>usriby</li><li>pcciby</li></ul>                             | 1                | user interrupt busy pcc interrupt busy                                                                             |

| <ul><li>prgext</li><li>xprgm</li><li>ixbuse</li><li>xbuse</li></ul> | 1<br>1<br>1      | external program user external program external bus enable user external bus enable                                |

| Internal signals:                                                   |                  |                                                                                                                    |

| <ul><li>addr</li><li>en</li><li>r_w</li><li>data</li></ul>          | 8<br>1<br>1<br>8 | <pre>internal address bus internal enable signal internal read/!write signal internal bidirectional data bus</pre> |

The sda and sdao lines have to be connected to each other, but because some additional logic is necessary to prevent metastability, these signals are separated input and output ports. The metastability circuit will be described in VHDL.

In the next paragraphs all IICC elements will be described in detail.

#### **3.3.1 Inter-IC (IIC)**

Philips PCALE employee H. Schutte has developed a simple bidirectional 2-wire bus for efficient inter-IC control. This bus is called the Inter IC or I<sup>2</sup>C-bus. An I<sup>2</sup>C-bus compatible device incorporates an on-chip interface which allows it to communicate directly with every other device on the I<sup>2</sup>C-bus. Some features of the I<sup>2</sup>C-bus are:

- Two bus lines are required; a serial data line (SDA) and a serial clock line (SCL)

- Each device connected to the bus is software addressable by a unique address

- Serial, 8-bit oriented, bidirectional data transfers can be made at up to 100 kbit/s in the standard mode or up to 400 kbit/s in the fast mode

- On chip filtering rejects spikes on the bus data line to preserve data integrity

The I<sup>2</sup>C-bus supports any IC fabrication process (NMOS, CMOS, bipolar). Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognised by a unique address and can operate either as transmitter or receiver, depending on the function of the device.

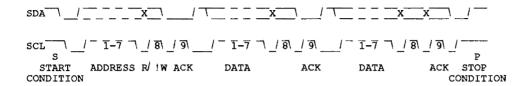

#### **IIC Data validity**

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW.

#### **IIC START and STOP conditions**

Within the procedure of the I<sup>2</sup>C-bus, unique situations arise which are defined as START and STOP conditions. A HIGH to LOW transition on the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. Detection of START and STOP conditions by devices connected to the bus is easy if they incorporate the necessary interfacing hardware. However, microcontrollers with no such interface have to sample the SDA line at least twice per clock period in order to sense the transition.

#### **IIC Transferring data**

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. If a receiver can't receive another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the transmitter into a wait state. Data transfer then continues when the receiver is ready for another clock line SCL.

Data transfer with acknowledge is obligatory. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse. Set-up and hold times must also be taken into account. Usually, a receiver which has been addressed is obliged to generate an acknowledge after each byte has been received. When a slave-receiver doesn't acknowledge the slave address (for example, it's unable to receive because it's performing some real-time function), the data line must be left HIGH by the slave. The master can then generate a STOP condition to abort the transfer.

If a slave-receiver does acknowledge the slave address but, some time later in the transfer cannot receive any more data bytes, the master must again abort the transfer. This is indicated by the slave generating the not acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates a STOP condition.

If a master receiver is involved in a transfer, it must signal the end of data to the slave-transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate the STOP condition.

#### IIC Formats with 7-bit addresses

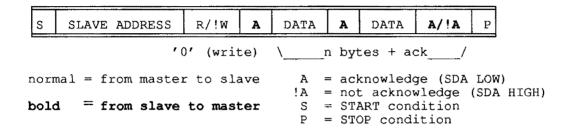

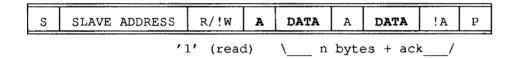

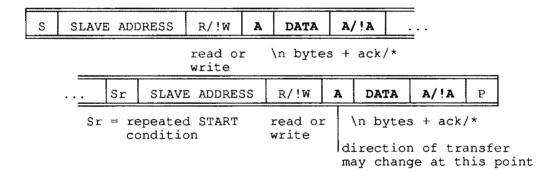

Data transfers follow the format shown in Figure 9. After the start condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/!W) -a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a stop condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer. Possible data transfer formats are:

- Master-transmitter transmits to slave-receiver. The transfer direction is not changed (Figure 10).

- Master reads slave immediately after first byte (Figure 11). At the moment of the first acknowledge, the master-transmitter becomes a master receiver and the slave-receiver becomes a slave transmitter. This acknowledge is still generated by the slave. The STOP condition is generated by the master

- Combined format (Figure 12). During a change of direction within a transfer, the START condition and the slave address are both repeated, but with the R/W bit reversed.

Figure 9 A complete data transfer

Figure 10 A master-transmitter addresses a slave receiver with a 7-bit address. The transfer direction is not changed

Figure 11 A master reads a slave immediately after the first byte

Figure 12 Combined format

#### **IIC** specification

It is advised that the PC to MicroDsp interface is a point to point interface that exists of a single master located in the PC and a single slave located on the MicroDsp. For a convenient program trace mode or commands like "step n instructions" I<sup>2</sup>C data transfers must be done as quickly as possible, so the 400 kbit/s I<sup>2</sup>C specification is preferred.

The PC I<sup>2</sup>C master issues all START and STOP conditions, generates the I<sup>2</sup>C clock SCL and

sends I<sup>2</sup>C address bytes including the Read/Write control bit. At the end of byte output the master can check reception of the acknowledge to ensure that the connected MicroDsp slave is responding. On reading I<sup>2</sup>C data the master will also provide an acknowledge according to the I<sup>2</sup>C specification. This acknowledge will be ignored by the slave. As most MicroDsp registers are writable and readable a more extensive I<sup>2</sup>C interface test can be done at the start of the PC monitor program.

Host computer program command sequences start by sending an I<sup>2</sup>C start (S) condition and a new I<sup>2</sup>C address that points to the MicroDsp port which is the first source or destination for I<sup>2</sup>C data byte. The MicroDsp Control hardware automatically advances to the next I<sup>2</sup>C port addresses. Data transfers can be ended at any time with an I<sup>2</sup>C stop condition (P) from the PC master I<sup>2</sup>C driver. While the PCC is running I<sup>2</sup>C control is only practical to read the MicroDsp status (from STAT port), debug data (from MAIL port) and to control write (to port FCTL) to stop the PCC. While in stop mode all I<sup>2</sup>C actions described below can be used. I<sup>2</sup>C sequences as transmitted by the PC controlling program will be described here using the following conventions, appearance and order:

|       | 1. S                         | force I <sup>2</sup> C start condition           |

|-------|------------------------------|--------------------------------------------------|

|       | 2. portname                  | I <sup>2</sup> C port address (7 bits)           |

|       | 3. +R or +W                  | read / write control bit in the address byte     |

|       | 4. (A) or (!A)               | address acknowledge level resp. ACK or NAK       |

|       |                              | from MicroDsp                                    |

| for N | 5. [data] or [ <i>data</i> ] | data transfer (8 bits) resp. to or from MicroDsp |

| bytes | 6. (A) or (!A) or (A) or (A) | data acknowledge level resp. ACK or NAK resp. to |

|       |                              | or from MicroDsp                                 |

|       | 7. P                         | force I <sup>2</sup> C stop condition            |

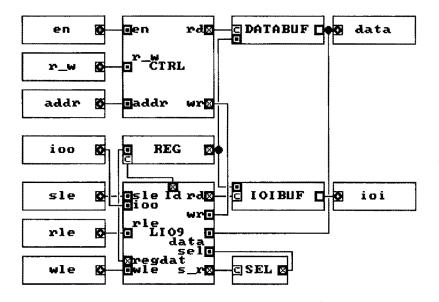

#### IIC design

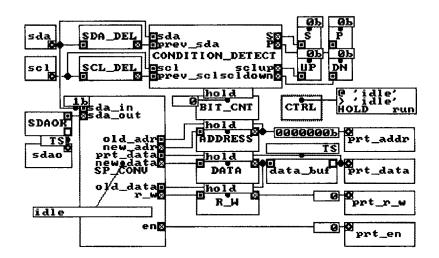

The IIC unit is the connection between the host computer and the MicroDsp. All inside information that is captured in the IICC register units can be transferred to the host computer via the serial SDA and SCL lines. Therefore the IIC unit has to be able to read and write these registers. A special internal data bus DATA and address bus ADDR have been made to perform these transfers. A read/write line R\_W indicates if such a register has to be read or written. An enable line EN determines if the busses are valid.

The IIC unit has four registers that indicate the condition of the data transfer. The registers S and P indicate the START and STOP conditions and the registers UP and DN indicate the state of the SCL line, thus the validity of the SDA data. This information is used by a state-controller CTRL which controls the serial-parallel converter SP\_CONV and the registers BIT CNT, ADDRESS, DATA and R W.

The SDA\_DEL and SCL\_DEL registers are used to delay the SCL and SDA signal one bit in order to detect if the SDA and SCL lines change from '1' to '0' or from '0' to '1'. (In the final VHDL design 3 or more clocks delay are necessary to avoid metastability but for the functional simulation this delay is not needed).

#### Figure 13 IIC

```

'SDA_DEL' is a register.

SDA_DEI

This register is 1 bit wide. The default function is 'load'. This register is loaded with value 0 following system reset.

Figure 14

The value loaded for the 'reset' command is 0.

SDA DEL

register

'SCL_DEL' is a register.

SCL_DEL

This register is 1 bit wide.

The default function is 'load'.

This register is loaded with value 0 following system reset.

Figure 15

The value loaded for the 'reset' command is 0.

SCL_DEL

register

The CONDITION_DETECT operator is used to determine the next state of

```

The CONDITION\_DETECT operator is used to determine the next state of the state-controller. Every next state depends on the behaviour of the SDA and SCL lines. The condition detect operator can detect the specified START and STOP conditions and the state of the SCL line (HIGH or LOW).

```

'CONDITION_DETECT' is an operator.

This operator has 1 function.

The default function is 'S_P_det'.

Text for function 'S_P_det' of 'CONDITION_DETECT':

S := prev_sda /\ prev_scl /\ (sda not) /\ scl.

P := (prev_sda not) /\ prev_scl /\ sda /\ scl.

sclup := (prev_scl not) /\ scl.

scldown := prev_scl /\ (scl not).

```

Isda SE Iprev\_sda P∑ CONDITION\_DETECT Iscl sclup⊠ Iprev\_sclscldown⊠

Figure 16 CONDITION DETECT operator

A state controller CTRL is used to control the serial parallel converter SP\_CONV and to control the registers ADDRESS, DATA and R\_W. In this way serial bits received at the SDA

input line will be shifted in the DATA and ADDRESS registers. If these registers are valid and the transfer direction has been set in the R\_W register, the enable signal EN will be made HIGH.

```

'CTRL' is a state machine controller.

This state machine controller has 12 states.

No stack is available for 'subroutine' calls.

This controller is enabled following system reset.

This state machine controller has no connectors.

Text for state number 1 (reset state) of 'CTRL':

sp_conv idle;

| 1 bit_cnt reset;

address reset;

data reset;

r_w reset;

-> receive_addr_bit

| 0 << ]

Text for state number 2 of 'CTRL':

----v---

receive_addr_bit:

[ bit_cnt < 7

| 1 [ up = 1

| 1 sp conv addr sp;

address load;

bit_cnt inc;

| 0 -> receive_direction ]

Text for state number 3 of 'CTRL':

receive direction:

[ up = 1

| 1 sp_conv set_dir;

r_w load;

-> prepare_addr_ack

Text for state number 4 of 'CTRL':

prepare_addr ack:

[ dn = 1 | 1 sp_conv send_ack;

sdaor load;

-> send_addr_ack

0 << ]

Text for state number 5 of 'CTRL':

send addr ack: [ \overline{dn} = \overline{1}

1 bit_cnt reset;

[r_w = 1

| 1 sp_conv read_prt_data;

data load;

-> get_data_bit

| 0 -> receive_data_bit ]

| 0 sdaor enable; "keep_sending_ack"

Text for state number 6 of 'CTRL':

----v---

get data bit:

\overline{bit} \overline{cnt} < 8

| 1 sp_conv data_ps;

data load;

sdaor load;

sdaor enable;

```

bit\_cnt inc;

CTRL

Figure 17 CTRL

```

-> send_data_bit

| 0 bit_cnt_reset;

[address < 1Bh</pre>

| 1 address inc ];

->receive_data_ack ]

Text for state number 7 of 'CTRL':

send data bit:

[ dn = T

| 1 sdaor enable;

-> get data bit

| 0 sdaor enable; "keep sending ack"

Text for state number 8 of 'CTRL':

receive_data_ack:

[dn = 1

data load;

-> get_data_bit]

Text for state number 9 of 'CTRL':

| 0 << ]

Text for state number 10 of 'CTRL':

| 1 -> receive_addr_bit

| 0 -> idle |

| 0 [ bit_cnt < 8

| 1 [ up = 1

| 1 sp_conv data_sp;

data load;

bit_cnt inc;

<< <sup>-</sup>

| 0 sp_conv write_prt_data;

data_buf enable;

-> prepare_data_ack ]]

Text for state number 11 of 'CTRL':

prepare_data_ack:

[ dn = 1

| 1 data_buf enable;

sp_conv send_ack;

sdaor load;

-> send data_ack

| 0 data_buf enable;

<< ]<sup>_</sup>

Text for state number 12 of 'CTRL':

----v--

send_data_ack:

[ dn = 1

| 1 bit_cnt reset;

data reset;

[ address < 1Bh

| 1 address inc ];

-> receive_data_bit

| 0 sdaor enable;

<< ]

```

End of state descriptions.

The SP\_CONV operator is used to shift the information bits received from the SDA line into the DATA and ADDRESS registers or to shift the information byte in the DATA register out of this register to drive the SDA line.

```

'SP_CONV' is an operator.

This operator has 8 functions. The default function is 'idle'.

Text for function 'addr_sp' of 'SP_CONV':

new adr := (old adr shl: 1) \/ (sda in width: 7).

Text for function 'data_ps' of 'SP_CONV':

sda out:=old data at: 7.

new_data:=(old_data shl: 1).

en:=0.

Text for function 'data_sp' of 'SP_CONV':

new_data:=(old_data shl: 1) \/ (sda_in width: 8).

Text for function 'idle' of 'SP_CONV':

Text for function 'read_prt_data' of 'SP_CONV':

en:=1.

new data:=prt data.

Text for function 'send_ack' of 'SP_CONV':

sda out := 0.

en := 0.

Text for function 'set_dir' of 'SP_CONV':

r_w := sda_in. "O indicates a write from the master"

Text for function 'write_prt data' of 'SP_CONV':

en:=1.

```

End of function descriptions.

Figure 18 SP\_CONV

The BIT\_CNT register is used to count the number of bits that are shifted in or out the DATA or ADDRESS register. This information is used by the state controller.

```

'BIT_CNT' is a register.

This register is 4 bits wide.

The default function is 'hold'.

This register is loaded with value 0 following system reset.

The value loaded for the 'reset' command is 0.

```

BIT\_CNT

Figure 19 BIT\_CNT register

'ADDRESS' is a register.

This register is 7 bits wide.

The default function is 'hold'.

This register is loaded with value 0 following system reset.

The value loaded for the 'reset' command is 0.

Figure 20 ADDRESS register

'DATA' is a register.

This register is 8 bits wide.

The default function is 'hold'.

This register is loaded with value 0 following system reset.

The value loaded for the 'reset' command is 0.

Figure 21 DATA register

'R\_W' is a register.

This register is 1 bit wide. The default function is 'hold'. This register is loaded with value 0 following system reset.

The value loaded for the 'reset' command is 0.

Figure 22 R\_W register

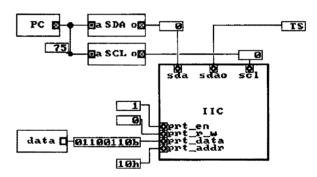

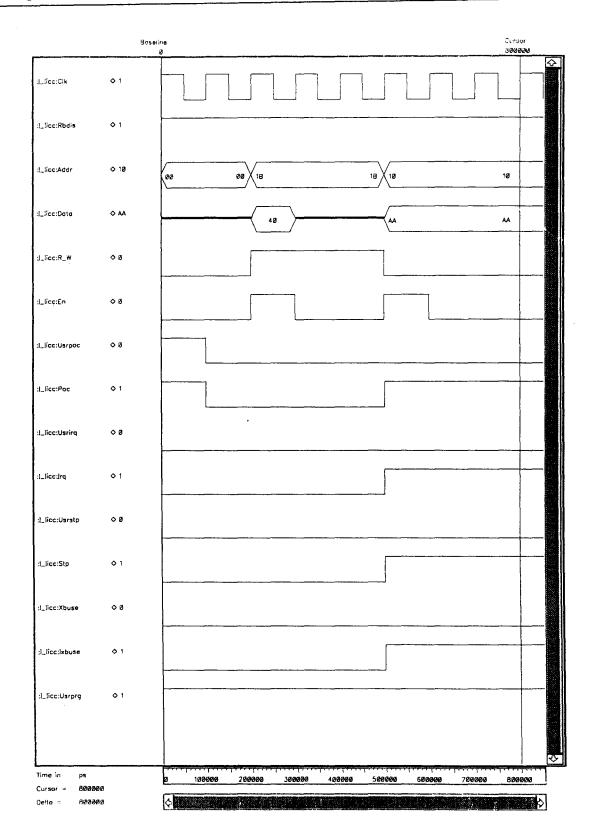

#### **IIC** simulation

When we are going to simulate the IIC unit we need input for the SDA and SCL lines. This has to be a serial input which means that every clock pulse the SDA and SCL lines are sampled. Therefore we connect to ROM units to these pins. The ROM units contain serial bit information that is read by the IIC unit.

Suppose we want to load the FCTL register with value 01100110b. Then we have to

Figure 23 IIC simulation

send a serial code to the IIC unit that addresses the FCTL register and writes the value into it. This code looks like:

S;FCTL;+W;(A);[data];(A);P

with FCTL = 10h

and [data] = 01100110b

The SCL signal in the ROM is described as 001100110011... . So every  $I^2C$  bit transfer takes four IIC clock pulses. In this case it will take 75 clock pulses until the data appears on the data bus and the enable signal becomes valid.

If we want to read the contents of the STAT register we have to send:

S;STAT;+R;(A);[data];(!A);P

with STAT = 1Bh