| MASTER                                                 |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|

| Design of a RSA crypto-processor using a systolic arra |  |  |  |  |  |

|                                                        |  |  |  |  |  |

|                                                        |  |  |  |  |  |

| Kuipers, E.A.M.                                        |  |  |  |  |  |

| Award date:<br>1996                                    |  |  |  |  |  |

|                                                        |  |  |  |  |  |

|                                                        |  |  |  |  |  |

| Link to publication                                    |  |  |  |  |  |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

### Faculty of Electrical Engineering Section Information and Communication Systems

# Design of an RSA crypto-processor using a systolic array

#### Graduation report

Author

: E.A.M. Kuipers

Coach

: R. Joosten

Supervisor

: Prof. Ir. M.P.J. Stevens

Date

: June 1996

Betreft: Geheimhouding van afstudeerverslag

Geachte heer Stevens,

Vanwege het feit dat het afstudeerproject betreffende het ontwerp van een RSA cryptie-processor heeft plaatsgevonden in het bedrijf Pijnenburg Custom chips B.V., wordt verzocht het verslag betreffende dit afstudeerproject niet openbaar te maken voor het jaar 2001.

Hartelijk dank voor de medewerking.

Met vriendelijke groet,

Erwin Kuipers

## Abstract

This report describes the design of a scalable RSA device, which is suited for public-key encryption and decryption according to the Rivest, Shamir and Adleman method [Riv77]. This design has been developed in the context of a graduation assignment at the section Information and Communication Systems of the faculty Electrical Engineering of the Eindhoven University of Technology. This assignment is characterized as follows:

Design a parameterizable RSA cryption-processor, which can be optimized on either chipsize or cryption speed. The goal is to achieve maximum flexibility, which allows the processor to be used in any environment using an optimal configuration.

The RSA design is based on a modular multiplication core, which executes the Montgomery algorithm [Mon85]. This algorithm requires conversions to and from an *N*-residue domain, but it is faster than the conventional 'paper & pencil' method and is easier to implement in hardware.

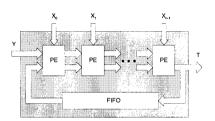

The multiplication core (MMM) is a systolic array, which consists of a number of processing elements (PE's), which can be varied in number and size. The number and size of the PE's are parameters which can be used to configure the RSA design to optimally perform in it's environment.

For this purpose the Montgomery algorithm has been adapted for systolic arrays, which results in a PE design which is proposed by Iwamura et al. [Iwa94]. In this report the steps are described, which are required to adapt the Montgomery algorithm to an efficient algorithm suited for systolic arrays. All conditions, which are required for this algorithm in order to prevent overflow or underflow are described. Further a schematic of the systolic array is presented, which shows the data flow in the PE's. Finally a schematic of an RSA processor is presented, which is based on the MMM-core.

The MMM-core has been simulated and functionally tested, from which can be concluded that the adapted Montgomery algorithm is working correctly. The PE's of the MMM-core have been described in VHDL and compiled to hardware-design. These compilations show, that using mimimal hardware optimization of the PE's, a (best case) cryption speed of 80 cryptions (1024 bits) per second can be achieved at a clock frequency of 66 MHz using a datapath of about 70 Kgates. When small chip size is required, the RSA design can be adapted to perform at 27 MHz using 6 Kgates. Using this configuration the RSA device can calculate about 5 cryptions of 1024 bits per second.

## Table of contents

| ı | Inti                              | roauctio                        | <b>n</b>                                         |  |  |     | 1        |  |

|---|-----------------------------------|---------------------------------|--------------------------------------------------|--|--|-----|----------|--|

|   | 1.1                               | Public-l                        | key cryptography                                 |  |  |     | 1        |  |

|   | 1.2                               | A scala                         | able hardware RSA cryption-device                |  |  |     | 3        |  |

|   |                                   |                                 |                                                  |  |  |     |          |  |

| 2 | RS                                | A expon                         | nentiation                                       |  |  |     | 5        |  |

|   |                                   |                                 | s RSA?                                           |  |  |     |          |  |

|   | 2.2                               | An RSA                          | A exponentiation algorithm                       |  |  |     | 6        |  |

| 3 | Modular Multiplication            |                                 |                                                  |  |  |     |          |  |

|   | 3.1 The 'paper & pencil' method   |                                 |                                                  |  |  |     |          |  |

|   |                                   | -                               | ontgomery algorithm                              |  |  |     |          |  |

|   | 3.4                               | 3.2.1                           | Adjustment of the modular multiplication result  |  |  |     |          |  |

|   |                                   | 3.2.1                           | The Montgomery multiprecision algorithm          |  |  |     |          |  |

|   |                                   |                                 |                                                  |  |  |     |          |  |

|   |                                   | 3.2.3                           | Scaling the Montgomery multiprecision algorithm  |  |  |     | 14       |  |

| 4 | Montgomery in Systolic Arrays     |                                 |                                                  |  |  |     |          |  |

|   | 4.1                               | Reducin                         | ing the internal bus width                       |  |  |     | 18       |  |

|   | 4.2                               | The Mo                          | ontgomery algorithm adapted for systolic arrays  |  |  |     | 23       |  |

|   | 4.3                               | The fin                         | nal delta correction                             |  |  |     | 27       |  |

|   |                                   |                                 | ary of the adapted algorithm for systolic arrays |  |  |     | 28       |  |

| 5 | Hardware Design of the RSA-device |                                 |                                                  |  |  |     |          |  |

| 3 |                                   |                                 |                                                  |  |  |     |          |  |

|   |                                   | •                               |                                                  |  |  |     | 30<br>32 |  |

|   | 3.4                               | -                               | of the MMM                                       |  |  |     |          |  |

|   |                                   | 5.2.1                           | Delta-correction                                 |  |  |     | 32       |  |

|   |                                   | 5.2.2                           | Pipelined multiplication in the MMM              |  |  |     | 33       |  |

|   |                                   | 5.2.3                           | Reducing the number of PE's                      |  |  |     | 35       |  |

|   |                                   | 5.2.4                           | Control of the MMM                               |  |  |     | 37       |  |

|   | 5.3                               | Design                          | of the RSA processor                             |  |  |     | 40       |  |

| 6 | Performance of the RSA core       |                                 |                                                  |  |  |     |          |  |

|   | 6.1                               | Number                          | er of clock cycles of an MMM                     |  |  |     | 43       |  |

|   | 6.2                               | 6.2 Performance of PE type 1 44 |                                                  |  |  |     |          |  |

|   |                                   | 6.3 Performance of PE type 2    |                                                  |  |  |     |          |  |

|   |                                   |                                 | ization of the PE's                              |  |  |     | 48       |  |

|   |                                   | 6.4.1                           | Optimization of the $m_i$ calculation            |  |  |     | 48       |  |

|   |                                   | 6.4.2                           | Optimization of the adders                       |  |  |     | 52       |  |

|   |                                   | U. 1.4                          | opinization of the address                       |  |  | • • | مے ب     |  |

| 7 Conclusions and Recommendations         | 4 | 53 |

|-------------------------------------------|---|----|

| Literature references                     | 4 | 55 |

| Appendix A: MMM controller functions      |   | 57 |

| Appendix B: VHDL description of PE type 2 |   | 59 |

## 1 Introduction

In this chapter public-key crypto-systems are explained, and the encryption/authentication methods are described. Then the need for a flexible RSA cryption-device is explained, from which the graduation assignment can be characterized. Finally a number of situations are described which this device is suitable for.

#### 1.1 Public-key cryptography

Today's communication is largely based on production and transport of digital information. The largest part of this information consists of private data, which may not be read or changed by unauthorized persons. This requires the application of safety measures, like isolated communication channels or data encryption. Because the latter is far more inexpensive, many crypto-systems have been developed to secure communication channels.

One crypto-system which has been in use for over 10 years now, is the DES-algorithm. DES is still commonly used, for it allows data blocks to be encrypted and decrypted fast and easily (over 20 Mbit/s in hardware), and still has withstood cryptanalysis attacks successfully. However, to decrypt a message, DES requires that both sender and receiver possess the cryption-key, which must be transferred using a safe communication channel.

The necessity for safe key-transfer can be avoided by using a public-key cryption method like RSA instead. Public-key cryptography, and RSA in particular, has no need for transmitting keys, for it is based on key-pairs: each sender/receiver has it's own public and private (secret) key. Because of the use of key-pairs, an identical algorithm can be used for both encryption and decryption. A message which has been *encrypted* using the public key, can be *decrypted* using the private key if and only if the private and public keys form a key-pair. This can be illustrated using the following example:

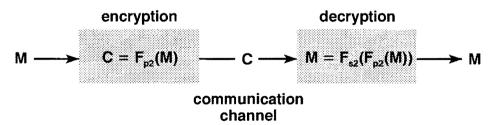

Sender 1 would like to send message M to receiver 2 using public-key cryptography. Sender 1 has key pair (p1, s1), receiver 2 has key pair (p2, s2) for public and secret keys. Using encryption/decryption function  $F_{key}(data)$ , the data transfer can be illustrated using figure 1.1.

figure 1.1: Encryption/decryption using a public-key crypto-system

Because the cyphertext C has been encrypted using the public key p2, it can only be decrypted using the secret key s2, which is only known by receiver 2. Therefore, receiver 2 is the only person who can decrypt cyphertext C to message M.

Public-key cryption implies that, using the cryption function F and the correct keypair, encryption and decryption should be calculated relatively easy. However, breaking the crypto-system by finding the inverse function  $F_{p2}^{-1}(C) = F_{p2}^{-1}(F_{p2}(M)) = M$  (which means uncovering secret key s2) should require more time than the expiration date of the message (after which encryption is no longer necessary). More about the cryption function F is explained in chapter 2.

Because of the large digits used by the cryption function F (over 1024 bits), public-key encryption and decryption take too long for large messages. Therefore this cryption method is generally used in combination with DES: messages are encrypted fast using DES, and are sent to the receiver with the DES-key, which has been encrypted using a public-key encryption method. This allows the sender to safely send the DES-key with the DES-encrypted message using the same (unsafe) communication channel.

Besides encryption and decryption, public-key crypto-systems can also be used for authentication and verification of the sender's identity. The sender can send his signature by first encrypting a message using his own private key (authentication). Then the encryption using the receiver's public key is executed. On the receiver's side, the original message can be retrieved by decryption using the receiver's own private key, followed by verification using the sender's public key. The transferred message M can only be retrieved correctly if the public key p1 matches the secret key s1. Because sender 1 is the only person who could have encrypted M using secret key s1, the identity of the sender of message M has been verified (see figure 1.2).

figure 1.2: Authentication/verification using a public-key crypto-system

Today's most popular public-key system is RSA, because for many years now it has withstood numerous attempts to break this system, and it allows authentication and verification easily.

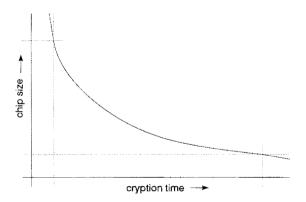

#### 1.2 A scalable hardware RSA cryption-device

The last few years the RSA crypto-system has become more popular than ever, strongly encouraged by the increasing demand for data security on the Internet. Because of it's considerable amount of arithmetic operations and it's demand for still larger digits, software RSA cryption has proven to be too slow for many applications. The increasing demand for high-speed RSA cryption however requires custom hardware devices, which are suitable for fast arithmetic operations on digits of width 1024 bits and larger. These high-speed hardware devices are mainly designed to perform at maximum cryption speed at the cost of a large chip size. Other RSA applications however impose less severe restrictions on cryption speed; but demand small chip size. The following two examples illustrate this:

Network server:

- Cryption-time less than 10 ms.

- Chip size approximately 200 Kgates.

- · Maximum clock frequency.

Chip-card:

- Cryption time approximately 0.5 seconds.

- Chip size less than 10 Kgates.

- Clock frequency 5 20 MHz.

Because usually DES and RSA are used together, for security reasons it is preferred to place hardware for both encryption methods, including memory, on one chip, which constrains available space. Other applications (e.g. cryptography in portable devices) constrain the operating frequency of the RSA device. These conditions require a flexible hardware design, which provides a trade-off of chip size against cryption speed. Now the graduation assignment, as described in this report, can be characterized as follows:

Design a parameterizable RSA cryption-processor, which can be optimized on either chipsize or cryption speed. The goal is to achieve maximum flexibility, which allows the processor to be used in any environment using an optimal configuration.

To achieve flexibility in both time and space, the RSA cryption-device should be designed using a systolic array, which consists of a number of identical processing elements (PE's). The number and size of these PE's are parameters which directly relate to the number of clockcycles required for an RSA-cryption, the maximum clock-frequency, and the chip-size. These parameters can be adjusted to meet the requirements imposed by the hardware environment.

The scalable RSA cryption-device is applicable in the following situations:

#### • When chip size is constrained: Optimization on cryption time.

In the case of several hardware-devices on one chip (e.g. DES, RSA, memory, control, security hardware) only limited space is left for the RSA cryption part. Also, the maximum clock-frequency can be constrained by the processing speed of the environment.

The clock-frequency determines the *size* of the PE's; the chip space determines the *number* of PE's. When both parameters are fixed, the maximum cryption speed for these parameters is achieved.

#### • When a reduced cryption speed is sufficient: Optimization on chip size.

In this case a minimum chip size can be obtained by adjusting the parameters (size and number of PE's) and clock-frequency. Because this application does not require high-speed RSA cryption, the internal bus-width can be made significantly smaller than the full cryption-width (>1024 bits), which reduces chip size considerably.

#### When RSA-cryption is applied using variable cryption widths.

When using *smaller* cryption widths, less PE's can be activated, which reduces the number of clock-cycles, resulting in less cryption time.

Using *larger* cryption widths (>1024 bits) can easily be achieved by increasing the number of PE's or connecting multiple RSA cryption-devices in cascade.

To find the optimal RSA cryption-device for any environment, it is desirable to make use of a graph which indicates the optimal size and number of PE's, given a specific chip size or cryption speed, as indicated in figure 1.3.

figure 1.3: Trade-off of the optimal parameters of the RSA cryption-device

This report describes the design of such a flexible RSA cryption-device, using PE's which have been designed to execute a modular multiplication algorithm in a pipeline structure.

### 2

### RSA exponentiation

In this chapter the RSA public-key crypto-system is explained, and how the public and private keys are used in RSA calculations. An algorithm is presented, which can execute RSA exponentiation fast, using only modular multiplications.

#### 2.1 What is RSA?

RSA is a public-key crypto-system for both cryption and authentication, introduced in 1977 by Rivest, Shamir and Adleman [Riv77]. RSA uses public key (N, e) and private key (N, d), where N, d, e are positive integers, N is odd and d, e < N. The cryption function  $F_{key}(M)$  is defined as  $M^{key} \mod N$  (M < N), so the data must be 'chopped' into digits smaller than N. Using the keys (N, e) and (N, d), RSA cryption operates as follows:

- Encryption of message M to cyphertext C:

- $C = F_{e}(M) = M^{e} \bmod N$

- Decryption of cyphertext C to message M:  $M = F_d(C) = C^d \mod N = M^{ed} \mod N$

The decryption of C using private key d returns the original message M if e, d and N are defined according to a set of rules. The modulus N is the product of two large primes, say p and q. Choose a private key d < N, which is relatively prime to (p-1)(q-1). The public key e is defined as the multiplicative inverse of  $d \mod (p-1)(q-1)$ , which means, that

*ed* mod

$$(p-1)(q-1) = 1$$

, so  $ed \equiv 1 + k \cdot (p-1)(q-1)$ ,  $k \in \mathbb{N}$ .

According to Euler and Fermat [Niv72], for any integer M relatively prime to N=pq goes:  $M^{k(p-1)(q-1)} = 1 \mod pq$

Now the decrypted message  $F_d(C)$  can be written as:

$$F_{d}(C) = M^{ed} \mod N$$

$$= M^{1+k(p-1)(q-1)} \mod pq$$

$$= M \mod pq \cdot 1 \mod pq$$

$$= M \mod N$$

$$= M \qquad \forall_{0 \le M < N}$$

Which proves that decryption of C (using the private key d) results in the original message M.

RSA security is based on the assumption that factorization of large digits into prime numbers is very difficult (see [Pol74], [Dix92]). When the modulus N is factorized in the two primes p and q, the private key d can be revealed easily by calculating the multiplicative inverse (mod (p-1)(q-1)) of public key e. If however N is chosen large enough, the factorization problem is too complex to solve within the expiration time of the encrypted message. Currently an RSA modulus N of 130 decimal digits (432 bits) has been factorized with great effort.

An other way to uncover the private key d is exhaustive search. However, also this technique to break the RSA-code requires too much calculation effort if N is chosen large enough.

In today's RSA cryptography a modulus of 1024 bits or larger is recommended.

#### 2.2 An RSA exponentiation algorithm

As mentioned before, RSA encryption calculates  $M^e \mod N$ , RSA decryption calculates  $C^d \mod N$ . Because both calculations are equivalent  $(M, C < N \mod d, e < N)$ , let's focus on the modular exponentiation  $C = M^e \mod N$ .

Define  $n=\lceil 2\log N \rceil$ , so *n* is the number of bits of the RSA modulus. Because e < N, this exponent can be represented using binary digits:

$$e = \sum_{i=0}^{n-1} 2^{i} e_{i} = (e_{n-1} \dots e_{1} e_{0})$$

(1)

Using this notation, C can be written as:

$$C = M^{2^{n-1}e_{n-1} + \dots + 2e_1 + e_0} \mod N$$

$$= \left( \left( (1 \cdot M^{e_{n-1}})^2 \cdot M^{e_{n-2}} \right)^2 \cdot \dots \cdot M^{e_1} \right)^2 \cdot M^{e_0} \mod N$$

(2)

So M can be exponentiated using n-1 squarings and n multiplications. However, in many cases the number of multiplications can be reduced, because if the exponent bit  $e_i$  is zero, the multiplication by  $M^{e_i}$  can be skipped.

The exponentiation algorithm for calculating C according to equation (2) now is as follows:

```

{input M, e, N}

C := 1

for i = (n-1) downto 0 do

begin

if e<sub>i</sub>=1 then C := C ⋅ M mod N

if i>0 then C := C ⋅ C mod N

end

{output C = M<sup>e</sup> mod N}

```

Note that during this algorithm the intermediate result C never exceeds N.

All most significant zero bits of exponent e, which precede the most significant '1'-bit, can be skipped, because for each of these zero exponent bits the algorithm will square the initial '1'.

Let  $\varepsilon$  be the number of bits required to represent e binary, so  $\varepsilon = \lceil 2\log e \rceil \le n$ . Now  $\varepsilon$  indicates the number of mod N-squarings executed by the exponentiation algorithm. Let  $\eta$  be the number of '1'-bits of exponent e, so  $\eta \le \varepsilon$ . Now  $\eta$  indicates the number of mod N-multiplications executed by the algorithm, and  $\varepsilon + \eta$  modular multiplications are required to calculate  $M^e$  mod N.

The upper bound of the required number of modular multiplications thus is 2n, which can be reduced to  $1\frac{1}{2}n$  using the following exponentiation method, based on [Bri82]:

• if  $\eta \le \frac{1}{2}\epsilon$ , e contains at most  $\frac{1}{2}\epsilon$  '1'-bits, so use the algorithm as presented before:

```

{input M, e, N}

C := 1

for i = (ε-1) downto 0 do

begin

if e<sub>i</sub>=1 then C := C ⋅ M mod N

if i>0 then C := C ⋅ C mod N

end

{output C = M<sup>e</sup> mod N}

```

• if  $\eta > \frac{1}{2}\epsilon$ , e contains less than  $\frac{1}{2}\epsilon$  '0'-bits, so the inverse of e contains at most  $\frac{1}{2}\epsilon$  '1'-bits. Now the following algorithm can be applied using the precomputed value  $M^{-1}$  mod N:

```

{input M, e, N, M^{-1} \mod N}

e' := 2^{\varepsilon} - e

C := M

for i = (\varepsilon - 1) downto 0 do

begin

C := C \cdot C \mod N

if e_i' = 1 then C := C \cdot M^{-1} \mod N

end

{output C = M^e \mod N}

```

Both algorithms require at most  $\varepsilon + \frac{1}{2}\varepsilon \le \frac{1}{2}n$  modular multiplications.

Using the presented exponentiation method, RSA exponentiation boils down to repeated calculation of  $C = A \cdot B \mod N$ , where A, B, C < N (so all can be represented using n bits). Other, more efficient exponentiation algorithms are presented in [Knu69], [Zha93], [Dim95] and [Kaw93], but all are based on repeated modular multiplications.

In the next chapters the design of a modular multiplier is described, which is particularly suited for RSA-exponentiation.

## $\frac{3}{M_{\text{odular}}}$

### **Modular Multiplication**

This chapter describes how two digits of width n bits can be multiplied modulo N. First a 'paper & pencil' method is explained, which requires large bit comparisons. Then an alternative algorithm is presented, which has no need for bit comparisons, at the cost of necessary transformations to and from an N-residue domain. Finally some modifications are described which improve the performance of this alternative algorithm.

#### 3.1 The 'paper & pencil' method

The modular multiplication  $C = A \cdot B \mod N$  (A, B < N) can be calculated straightforward by first multiplying A and B, and then reducing the product by a multiple of N such that the result does not exceed N. This method is known as the 'paper & pencil' method and can be applied using the following algorithm:

$$C = A \cdot B \mod N = A \cdot B - q \cdot N \qquad (A, B < N)$$

- Multiplication: Calculate  $A \cdot B$

- Trial division: Find q with  $0 \le q < N$  such that  $0 \le C < N$

If n (the width of modulus N in bits) is large, the calculation of the full product  $A \cdot B$  of width 2n should be avoided. This can be done by splitting both A and q in k digits of width  $\alpha$  bits:

$$k = \left\lceil \frac{n}{\alpha} \right\rceil \tag{3}$$

$$A = \sum_{i=0}^{k-1} 2^{\alpha i} a_i = (a_{k-1} \dots a_1 a_0)$$

$$q = \sum_{i=0}^{k-1} 2^{\alpha i} q_i = (q_{k-1} \dots q_1 q_0)$$

(4)

Now C can be calculated by multiplying each digit  $a_i$  by B, and by immediately reducing the result modulo N:

$$C = \sum_{i=0}^{k-1} (a_i B - q_i N) 2^{\alpha i}$$

(5)

The product  $a_i B$  has only width  $n+\alpha$  bits instead of 2n, which reduces the multiplier size considerably if k is large.

This 'paper & pencil' method requires that for each product term  $a_iB$  a  $q_i$  is found in order to reduce it modulo N (trial division). The number of comparisons and subtractions can be reduced by skipping the modulo reduction (subtraction of  $q_i N$ ) several multiplication steps and subtracting a larger multiple of N. This method however increases the size of the q-digits, which requires much additional hardware and a longer critical path. This issue returns in many hardware designs which are based on optimized 'paper & pencil' methods, as presented in [Bri82], [Mor90], [Wal93] or [Iwa93].

In [Mon85] an alternative algorithm is presented, which is based on transformations to and from an *N*-residue domain. In [Eld93], optimized 'paper & pencil' methods are compared to this Montgomery algorithm. It is concluded that the Montgomery algorithm can achieve twice the speed of the optimized 'paper & pencil' method described in [Bri82], at the cost of two extra registers. The operation and advantages of the Montgomery algorithm are shown in the next paragraph.

#### 3.2 The Montgomery algorithm

Peter L. Montgomery has developed a method for calculating  $C = A \cdot B \mod N$  without the need for trial division. In [Mon85] he shows that the modulo reduction factor q does not have to be found using bit comparison, but can be calculated. This requires however conversion of A and B to an N-residue domain and conversion of the calculation result back to C in the integer domain. The Montgomery method for modular multiplication can be described as follows:

1 Let N be a positive odd integer such that  $2^{n-1} < N < 2^n$ .

Choose an  $R = 2^r$ , r a positive integer, which satisfies

- R > N  $(r \ge n)$

- gcd(R,N)=1 (R is coprime to N, which is satisfied by N being odd).

- 2 Find integers  $R^{-1}$  and N' satisfying  $0 < R^{-1} < N$  and 0 < N' < R,

such that  $RR^{-1} - NN' = 1$ , so

- $RR^{-1} \mod N = 1$   $(R^{-1} \text{ is the multiplicative inverse of } R \mod N)$

- $N' = (RR^{-1} 1) \text{ div } N$

- 3 Let A, B, C be integers,  $0 \le A$ , B, C < N.

- 4 Let X, Y, T be integers,  $0 \le X$ , Y < N and  $0 \le T < 2N$ .

- 5 Let  $\lambda$  and  $\mu$  be integers,  $0 \le \lambda$ ,  $\mu < N$

- 6 Define function MMM( $\lambda,\mu$ ) =  $\lambda \mu \cdot R^{-1} \mod N$ .

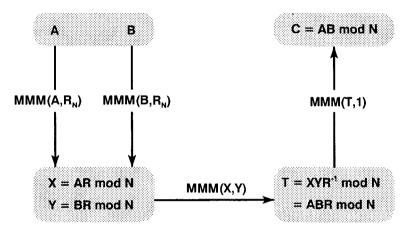

Using the function MMM( $\lambda,\mu$ ) and a precalculated value  $R_N=R^2 \mod N$ , the modular multiplication  $C=A\cdot B \mod N$  can be calculated as follows:

• Convert the integers A and B to the N-residue domain using  $MMM(..,R_N)$ :

$$X = MMM(A, R_N) = A \cdot R^2 \cdot R^{-1} \mod N = AR \mod N$$

$Y = MMM(B,R_N) = B \cdot R^2 \cdot R^{-1} \mod N = BR \mod N$

- Calculate in the N-residue domain the modular multiplication MMM(..,..):  $T = MMM(X,Y) = ABR^{2} \cdot R^{-1} \mod N = ABR \mod N$

- Convert T from the N-residue domain to C in the integer domain using MMM(..,1):  $C = MMM(T,1) = ABR \cdot R^{-1} \mod N = AB \mod N$

The N-residue transformations are illustrated in figure 3.1.

figure 3.1: Montgomery transformations to and from the N-residue domain

Montgomery defines the function MMM(X,Y) as:

$$T = MMM(X,Y) = \frac{XY + mN}{R} = XY \cdot R^{-1} \mod N$$

(6)

The factor m is defined as:

$$m = (X \cdot Y \mod R) \cdot N' \mod R$$

$$= XY \cdot N' \mod R \equiv XY \cdot N' + k \cdot R \qquad (k \in \mathbb{I})$$

(7)

So  $0 \le m < R$ .

Equation (6) can be proven by simply substituting (7):

$$T = \frac{XY + XY \cdot NN' + k \cdot NR}{R}$$

$$= \frac{XY(1 + NN') + k \cdot NR}{R}$$

(8)

Using the Montgomery property  $RR^{-1} - NN' = 1$ , T can be written as:

$$T = \frac{XY \cdot RR^{-1} + k \cdot NR}{R} = XY \cdot R^{-1} + k \cdot N \equiv XY \cdot R^{-1} \mod N$$

(9)

which proves that  $T = MMM(X, Y) = XY \cdot R^{-1} \mod N$ .

Because XY, N and  $R^{-1}$  are integers, T can be shown to be an integer by calculating:

$$mN = XYNN' + kNR = XY(RR^{-1} - 1) + kNR$$

=  $-XY + (XYR^{-1} + kN)R = -XY + l \cdot R$  (10)

Since  $l = (XYR^{-1} + kN) \in \mathbb{I}$ , the numerator of T is a multiple of R, which proves that T is an integer.

#### 3.2.1 Adjustment of the modular multiplication result

The Montgomery algorithm shows that the product  $X \cdot Y$  can be reduced modulo N using a division by  $R = 2^r$ , with R > N and N is odd (so  $r \ge n$ ). This integer division is allowed, for the lower r bits of the product XY are set to zero by adding an m-multiple of N, which does not affect the final result in the N-residue domain. This concept is illustrated in figure 3.2.

figure 3.2: Principle of the Montgomery algorithm

However, the MMM(X,Y) output can be equal to  $XY \cdot R^{-1} \mod N + N$  instead of the desired  $XY \cdot R^{-1} \mod N$ . This can be demonstrated as follows:

Using X, Y < N and m, N < R, an upper bound of T = MMM(X, Y) can be determined using equation (6) and the conditions imposed at X, Y and M:

$$T = \frac{XY + mN}{R} < \frac{N \cdot N + R \cdot N}{R} < \frac{R \cdot N + R \cdot N}{R} = 2N$$

(11)

So if the MMM result T equals or exceeds N, T should be adjusted to T - N. After this adjustment T is an N-residue value smaller than N, so it satisfies the input conditions imposed at he input multiplicands X and Y. This means that (after this N-adjustment) MMM output values can be used as input values of a new MMM.

The necessity for N-adjustment of the Montgomery multiplication result (subtraction of N if  $MMM(X,Y) \ge N$ ) can be avoided by choosing R large enough. Because it is desired to use the MMM-output T (< 2N) directly for input to a new MMM(X,Y), the input conditions for X and Y should become  $0 \le X, Y < 2N$ . With  $R = 2^r$ , the new condition for r can be found as follows:

1

$$2^{n-1} < N < 2^n, n \ge 1$$

$\Rightarrow N \le 2^n - 1$

2  $0 \le X, Y < 2N$   $\Rightarrow X, Y \le 2^{n+1} - 3$

3  $R = 2^r, r = n + d$   $(d \in \mathbb{N})$

4  $m < R = 2^{n+d}$   $\Leftarrow m \le 2^{n+d}$

Find a minimal d, such that T = MMM(X, Y) < 2N for all X, Y < 2N.

$$T = \frac{XY + mN}{R} \le \frac{(2^{n+1}-3) \cdot (2^{n+1}-3) + 2^{n+d} \cdot (2^n-1)}{2^{n+d}} < 2(2^n-1)$$

(12)

This can be rewritten as:

$$2^{2n+2} - 6 \cdot 2^{n+1} + 9 < 2^{2n+d} - 2^{n+d} \Rightarrow$$

$$2^{2n}(4 - 2^d) - 2^n(12 - 2^d) + 9 < 0$$

$$(13)$$

This condition is satisfied for all  $n \ge 1$  and  $d \ge 2$ . This means, that if  $R = 2^r$ ,  $r \ge n+2$  and X, Y < 2N, the calculated T = MMM(X,Y) < 2N. The MMM-function now can be applied for repeated modular multiplications (as in exponentiation algorithms) without N-adjustment. However, the final result C after conversion back to the integer domain using C = MMM(T,1) may not exceed N. This modular multiplication requires adjustment only if C = N, for backward conversion of N-residue values <2N always returns integers  $\le N$ , which can be shown as follows:

1

$$2^{n-1} < N < 2^n, n \ge 1$$

$\Rightarrow N \le 2^n - 1$

2  $0 \le T < 2N$   $\Rightarrow T \le 2^{n+1} - 3$

3  $R = 2^r, r = n + d$   $(d \in \mathbb{N})$

4  $m < R = 2^{n+d}$   $\Rightarrow m \le 2^{n+d} - 1$

If C is the integer after conversion of T from the N-residue domain, so C = MMM(T,1), the upper bound of C can be determined as follows:

$$C = \frac{T \cdot 1 + mN}{R} \le \frac{(2^{n+1} - 3) \cdot 1 + (2^{n+d} - 1) \cdot (2^n - 1)}{2^{n+d}}$$

(14)

This can be rewritten as:

$$C \leq \frac{(2 \cdot 2^n - 3) + 2^{2n+d} - 2^{n+d} - 2^n + 1}{2^{n+d}} = 2^n - 1 + \left(\frac{2^n - 2}{2^{n+d}}\right) < 2^n$$

(15)

So  $C<2^n$  for all  $n\ge 1$ , implying that C can be at most equal to N after conversion of T back to the integer domain. Only then C must be set to zero in order to reduce C modulo N.

#### 3.2.2 The Montgomery multiprecision algorithm

Because  $R = 2^r$ ,  $r \ge n+2$ , the maximum m < R is represented by at least n+2 bits. To avoid the calculation of the full-width product XY during a Montgomery modular multiplication (MMM), both X and m are split into k digits of width  $\alpha$  bits, with  $0 < \alpha$ ,  $k \le n+2$ , so

$$k = \left\lceil \frac{n+2}{\alpha} \right\rceil \tag{16}$$

Now let  $r = k\alpha$ , so r is the smallest multiple of  $\alpha$  which equals or exceeds n+2, indicating the number of bits which are used to represent X and m. These values can be written using base  $2^{\alpha}$  as

$$X = \sum_{i=0}^{k-1} 2^{\alpha i} x_i = (x_{k-1} \dots x_1 x_0)$$

$$m = \sum_{i=0}^{k-1} 2^{\alpha i} m_i = (m_{k-1} \dots m_1 m_0)$$

(17)

under the condition that  $x_i$  and  $m_i < 2^{\alpha}$ .

Using equations (7) and (18), the Montgomery algorithm becomes:

$$R \cdot T = \sum_{l=0}^{k-1} (x_l Y + m_l N) 2^{\alpha l}$$

(18)

Division by  $R = 2^{\alpha k}$  yields:

$$T = \sum_{l=0}^{k-1} (x_l Y + m_l N) 2^{-\alpha(k-l)}$$

(19)

Now the partial sum T(i) can be defined using index i = 0, 1, ..., k-1:

$$T(i) = \sum_{l=0}^{i} (x_l Y + m_l N) 2^{-\alpha((i+1)-l)}$$

(20)

so  $T(k-1) = T = XY R^{-1} \mod N$ .

If the last sum term is extracted from the entire sum of equation (21), T(i) can be written as:

$$T(i) = \sum_{l=0}^{i-1} (x_l Y + m_l N) 2^{-\alpha((i+1)-l)} + (x_i Y + m_i N) 2^{-\alpha}$$

$$= 2^{-\alpha} \sum_{l=0}^{i-1} (x_l Y + m_l N) 2^{-\alpha(i-l)} + (x_i Y + m_i N) 2^{-\alpha}$$

$$= (T(i-1) + x_i Y + m_i N) 2^{-\alpha}$$

(21)

So instead of dividing the sum of products xY + mN once by  $R = 2^{\alpha k}$ , now during k iteration steps the partial sum is divided by  $2^{\alpha}$ . This division is only permitted if the division result is an integer, so if the  $\alpha$  least significant bits (LSB's) of the numerator of T(i) are zero. Therefore  $m_i$  is defined as:

$$m_i = (T(i-1) + x_i Y) N' \mod 2^{\alpha}$$

(22)

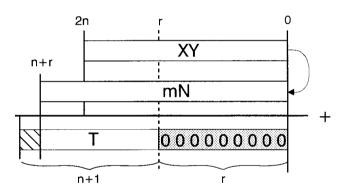

The principle of the Montgomery multiprecision case can be illustrated using figure 3.3, which shows two consecutive iteration steps.

figure 3.3: The Montgomery multiprecision case

Notice that each intermediate result T(i) has maximum width n+2 bits, for  $x_iY$  has width  $\alpha+n+1$  bits, and  $m_iN$  has width  $\alpha+n$  bits. The final result T(k-1) = MMM(X,Y) however has width n+1 bits, for equation (12) shows that  $T = \text{MMM}(X,Y) < 2N < 2^{n+1}$ .

#### 3.2.3 Scaling the Montgomery multiprecision algorithm

As just has been shown, an MMM can be calculated using k iteration steps. In each step a digit of X is multiplied by Y, the result is added with the result of the previous iteration step and the whole is divided by  $2^{\alpha}$ . This division is only allowed if the numerator of T(i) is a multiple of  $2^{\alpha}$ . For this purpose an  $m_i$ -multiple of N is added to this numerator, which is calculated using equation (22). However, this  $m_i$  cannot be calculated until the product  $x_i Y$  is available, so the product  $m_i N$  can only be calculated afterwards.

The calculation of  $m_i$  can be simplified by shifting each product  $x_i Y$  over  $\alpha$  bits to the left, out of the grey area of figure 3.3. The scaled multiprecision Montgomery algorithm can be determined as follows:

If digits  $x_k$  and  $m_{ij}$  are set to zero, it follows from equation (18) that

$$R \cdot T = \sum_{l=0}^{k-1} x_l Y \, 2^{\alpha l} + \sum_{l=1}^{k} m_{l-1} N \, 2^{\alpha (l-1)}$$

$$= \sum_{l=0}^{k} (2^{\alpha} x_l Y) \, 2^{\alpha (l-1)} + \sum_{l=0}^{k} m_{l-1} N \, 2^{\alpha (l-1)}$$

(23)

Left and right division by  $R = 2^{\alpha k}$  yields:

$$T = \sum_{l=0}^{k} \left( 2^{\alpha} \cdot x_{l} Y + m_{l-1} N \right) 2^{-\alpha(k-l+1)}$$

(24)

Now the partial sum T(i) is redefined using index i = 0, 1, ..., k:

$$T(i) = \sum_{l=0}^{i} \left( 2^{\alpha} \cdot x_{l} Y + m_{l-1} N \right) 2^{-\alpha(i-l+1)}$$

(25)

so  $T(k) = T = XY R^{-1} \mod N$ .

By separating the last term of the entire sum of equation (26), T(i) can be written as:

$$T(i) = 2^{-\alpha} \sum_{l=0}^{i-1} (2^{\alpha} \cdot x_{l}Y + m_{l-1}N) 2^{-\alpha((i-1)-l+1)} + (2^{\alpha} \cdot x_{i}Y + m_{i-1}N) 2^{-\alpha}$$

$$= (T(i-1) + 2^{\alpha}x_{i}Y + m_{i-1}N) 2^{-\alpha}$$

(26)

Now the lower  $\alpha$  bits of the *numerator* of T(i) depend only on the lower  $\alpha$  bits of T(i-1), which simplifies the calculation of  $m_{i-1}$ :

$$m_{i-1} = T(i-1) \cdot N' \mod 2^{\alpha}$$

(27)

These results are also presented in [Iwa94] and [Dus90].

The multiprecision Montgomery algorithm scaled over  $\alpha$  bits can be illustrated by figure 3.4, which shows two successive iteration steps.

figure 3.4: The Montgomery multiprecision case scaled over  $\alpha$  bits

Notice that the scaled Montgomery algorithm produces intermediate results T(i) of width  $n+2+\alpha$  bits, for the MSB of the product  $2^{\alpha}x_iY$  is located at bit position  $n+1+2\alpha$ . Again, by equation (12) the final result T(k) = T < 2N has maximum width n+1 bits.

The Montgomery multiprecision algorithm scaled over  $\alpha$  bits can be described as follows:

Montgomery conditions:

```

1

n \ge 1

2^{n-1} < N < 2^n, N is odd

2

0 \le X, Y, T < 2N

3

1 \le \alpha \le n+2

5

k=\lceil (n+2)/\alpha \rceil

6

r = k\alpha \ge n+2

R=2^r=2^{k\alpha}

7

RR^{-1} - NN' = 1

\{input X, Y, N\}

T(-1) = 0

= 0

m_{-1}

= 0

x_k

for i = 0 to k do

begin

T(i) = (T(i-1) + 2^{\alpha} x_i Y + m_{i-1} N) \operatorname{div} 2^{\alpha}

m_i = T(i) \cdot N' \mod 2^{\alpha}

end

{output T = T(k) = MMM(X,Y) = XYR^{-1} \mod N}

```

Each  $m_i$  is the product of the lower  $\alpha$  bits of the currently calculated T(i) and the lower  $\alpha$  bits of the precalculated constant N'. For example, if  $\alpha=1$ ,  $m_i$  is the product of the LSB of T(i) and N'. Because N' is always odd (see paragraph 6.4.1), it's LSB is always '1', so  $m_i$  can be retrieved straight from T(i) without any calculation!

By choosing small values for  $\alpha$ ,  $m_i$  is calculated using a simple  $\alpha$  x  $\alpha$  multiplier, which can start multiplying while the higher order bits of T(i) are calculated. This parallel arithmetic gives great benefit over the 'paper & pencil' method, which cannot start the  $q_i$ -determination until a great number of bits of the product  $a_iB$  has been calculated.

4

### **Montgomery in Systolic Arrays**

In this chapter is described how the multiprecision Montgomery algorithm can be applied for systolic arrays. To reduce the internal bus width, the algorithm is adapted, which provides a new parameter which relates to the PE size. Although this adapted algorithm cannot be realized directly, after some modifications a flexible design is obtained which is suitable for systolic arrays.

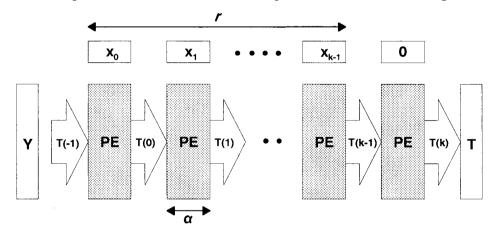

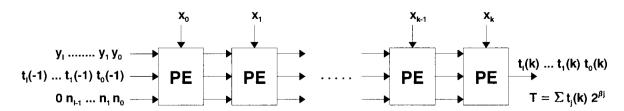

As described in chapter 1, a flexible RSA cryption-device can be obtained by hardware design using a systolic array. The array consists of identical processing elements (PE's), of which the number and size can be adjusted in order to optimally perform in the environment. The multiprecision case of Montgomery's algorithm is well suited for hardware design using systolic arrays, for each iteration step can be calculated by one PE. If each PE processes a digit of X of width  $\alpha$  bits, k+1 PE's would be required to execute a modular multiplication, as illustrated in figure 4.1.

figure 4.1: MMM iteration steps in a systolic array

The size of the PE's is defined by  $\alpha$ , and the number of PE's can be decreased. If less than k+1 PE's are used, the intermediate result T(i) (i < k) on the output of the last PE must be stored in a register (width  $n+2+\alpha$  bits). The register contents can be loaded in the first PE, which then will calculate T(i+1) using digit  $x_{i+1}$ . So if p is the number of PE's  $(1 \le p \le k+1)$ ,  $\lceil (k+1) \mid p \rceil$  MMM-cycles are required.

#### 4.1 Reducing the internal bus width

Although  $\alpha$  provides some flexibility for the size of a PE, still  $(n+2+\alpha)$  bits are processed each iteration step. This width may be too large for applications which require a small internal bus width. Therefore it is desired to split T, Y and N into smaller digits of width  $\beta$  bits.

If  $\beta$  is constrained to  $\beta \le n$ , integer l can be defined as

$$l = \left[ \frac{n}{\beta} \right]$$

(28)

Now let  $s = l\beta$ , so s is the smallest multiple of  $\beta$  which equals or exceeds n. Then  $n \le s < n+\beta$  and  $N < 2^n$  can be represented binary using l digits of width  $\beta$  bits.

If also  $\beta \ge \alpha+2$ , both T(i) and Y can be represented binary using l+1 digits of  $\beta$  bits:

$$T(i) = \sum_{j=0}^{l} t_{j}(i) 2^{\beta j}$$

$$Y = \sum_{j=0}^{l} y_{j} 2^{\beta j}$$

$$N = \sum_{j=0}^{l-1} n_{j} 2^{\beta j}$$

(29)

under the condition that  $t_i(i)$ ,  $y_i$  and  $n_i < 2^{\beta}$ .

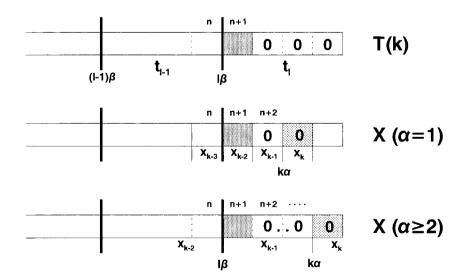

The most significant digits  $t_l(i)$  contain the calculation overflow bits generated during the Montgomery modular multiplication. The digits  $t_l(k)$  and  $y_k$  have at most bit n+1 of T(k) and Y placed at the least significant bit position (only if  $n=l\beta$ ), for both T(k) and  $Y < 2N < 2^{n+1}$ .

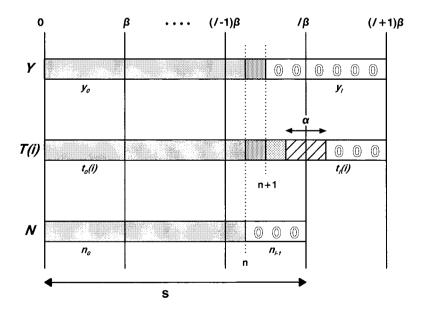

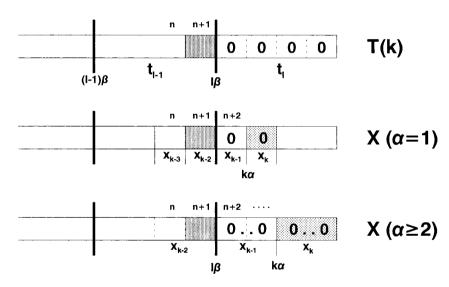

The contents of the digits of Y, T(i) and N are illustrated in figure 4.2.

figure 4.2: Contents of digits Y, T(i) and N

The purpose of splitting Y, T(i) and N into digits of  $\beta$  bits is to calculate one digit  $t_j(i)$  of  $\beta$  bits in each PE. Now also  $\beta$  provides a parameter which directly relates to the PE size.

From equations (26) and (29) follows, that

$$T(i) = \sum_{j=0}^{l} t_{j}(i) \ 2^{\beta j} = \sum_{j=0}^{l} \frac{t_{j}(i-1) + 2^{\alpha} x_{i} y_{j} + m_{i-1} n_{j}}{2^{\alpha}} \ 2^{\beta j}$$

(30)

Notice that the total summations are equal, which does *not* imply that all individual sum terms are equal (each  $t_i(i) < 2^{\beta}$ , while the fraction on the right side of equation (30) is smaller than  $2^{\alpha+\beta+1}$ ).

To determine how each  $t_i(i) < 2^{\beta}$  can be calculated in one PE, we define:

$$U'(i) = 2^{\alpha}T(i) \tag{31}$$

Write U'(i) redundant using l+1 digits of width  $2\alpha+\beta+1$ :

$$U'(i) = \sum_{j=0}^{l} u_j'(i) 2^{\beta j} = 2^{\alpha} T(i) = \sum_{j=0}^{l} \left( t_j(i-1) + 2^{\alpha} x_i y_j + m_{i-1} n_j \right) 2^{\beta j}$$

(32)

The summation term  $u'_{i}(i)$  is defined by

$$u_j'(i) = t_j(i-1) + 2^{\alpha}x_iy_j + m_{i-1}n_j < 2^{2\alpha+\beta+1}$$

(33)

The upper bound for  $u_j'(i)$  is justified by  $t_j(i-1) < 2^{\beta}$ , by  $2^{\alpha}x_iy_j < 2^{2\alpha+\beta}$  and by  $m_{i-j}n_j < 2^{\alpha+\beta}$ .

Now if  $u'_{i}(i)$  is split in three parts:

$$\delta_i(i) = u_i'(i) \mod 2^{\alpha}$$

$$t_i'(i) = (u_i'(i) \operatorname{div} 2^{\alpha}) \mod 2^{\beta}$$

(34)

$$\gamma_j(i) = u_j'(i) \operatorname{div} 2^{\beta+\alpha}$$

this value can be written as:

$$u_{j}'(i) = 2^{\beta+\alpha}\gamma_{j}(i) + 2^{\alpha}t_{j}'(i) + \delta_{j}(i)$$

(35)

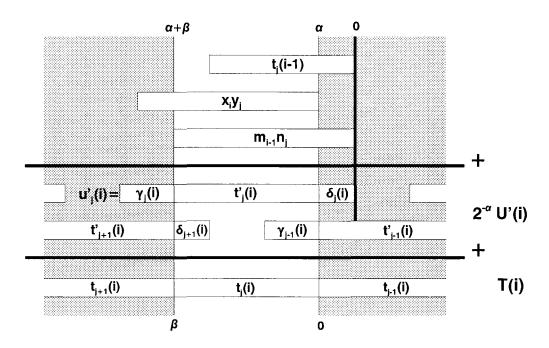

The use of U'(i) can be illustrated using figure 4.3.

figure 4.3: Calculation of adjacent digits of T(i)

Using equations (30), (32) and (33), T(i) can be written as:

$$T(i) = \sum_{j=0}^{l} t_{j}(i)2^{\beta j} = 2^{-\alpha} \sum_{j=0}^{l} u_{j}'(i)2^{\beta j}$$

$$= 2^{-\alpha} \sum_{j=0}^{l} \left(2^{\beta+\alpha} \gamma_{j}(i) + 2^{\alpha} t_{j}'(i) + \delta_{j}(i)\right) 2^{\beta j}$$

$$= \sum_{j=0}^{l} \gamma_{j}(i)2^{\beta(j+1)} + \sum_{j=0}^{l} t_{j}'(i)2^{\beta j} + \sum_{j=0}^{l} 2^{-\alpha} \delta_{j}(i)2^{\beta j}$$

$$= \sum_{j=1}^{l+1} \gamma_{j-1}(i)2^{\beta j} + \sum_{j=0}^{l} t_{j}'(i)2^{\beta j} + \sum_{j=-1}^{l-1} 2^{-\alpha} \delta_{j+1}(i)2^{\beta(j+1)}$$

$$= \sum_{j=0}^{l} \gamma_{j-1}(i)2^{\beta j} + \left(\gamma_{l}(i)2^{\beta(l+1)} - \gamma_{-1}(i)\right) + \sum_{j=0}^{l} t_{j}'(i)2^{\beta j} + 2^{\beta-\alpha} \sum_{j=0}^{l} \delta_{j+1}(i)2^{\beta j} + \left(\delta_{0}(i) - \delta_{l+1}(i)2^{\beta(l+1)}\right)$$

$$(36)$$

Now both  $\gamma_1(i)$  and  $\delta_{l+1}(i)$  are 0 by definition, for both values are out of the digit index range j=0 ... l. Because  $T(i)=2^{-\alpha}U'(i)$  is an integer, U'(i) mod  $2^{\alpha}=0$  for all i=0 ... k, which implies by equation (34) that  $\delta_0(i)=0$ . Also,  $\gamma_l(i)=0$ , for this digit is located at bit position  $n+\beta$  of  $T(i)=2^{-\alpha}U'(i)<2^{n+\alpha+2}<2^{n+\beta}$ . So no more than the lower  $\alpha+2$  bits of digit  $t_l(i)$  are used.

According to equations (34) and (36), T(i) can be written as:

$$T(i) = \sum_{j=0}^{l} t_j(i) 2^{\beta j} = \sum_{j=0}^{l} \left( \gamma_{j-1}(i) + (u_j'(i) \operatorname{div} 2^{\alpha}) \operatorname{mod} 2^{\beta} + 2^{\beta-\alpha} \delta_{j+1}(i) \right) 2^{\beta j}$$

(37)

Now the complete sumterm can be constrained modulo  $2^{\beta}$ , for all addition overflow bits will ripple into  $\gamma_i(i)$ , which is processed in the next digit  $t_{i+1}(i)$ .

Using the definition of u'(i) in equation (33), T(i) can be written as

$$\sum_{j=0}^{l} t_{j}(i) 2^{\beta j} = \sum_{j=0}^{l} \left( \frac{u_{j}'(i) + 2^{\beta} \delta_{j+1}(i) + 2^{\alpha} \gamma_{j-1}(i)}{2^{\alpha}} \right) \operatorname{mod} 2^{\beta} \cdot 2^{\beta j}$$

$$= \sum_{j=0}^{l} \left( \frac{t_{j}(i-1) + 2^{\alpha} x_{i} y_{j} + m_{i-1} n_{j} + 2^{\beta} \delta_{j+1}(i) + 2^{\alpha} \gamma_{j-1}(i)}{2^{\alpha}} \right) \operatorname{mod} 2^{\beta} \cdot 2^{\beta j} \tag{38}$$

The fraction represents an integer division (the lower  $\alpha$  bits of the addition of the numerator can be ignored, for they are processed as  $\delta_{j-1}(i)$  in the previous digit  $t_{j-1}(i)$ ). If finally the numerator of the fraction of equation (38) is defined as:

$$u_{j}(i) = t_{j}(i-1) + 2^{\alpha}x_{i}y_{j} + m_{i-1}n_{j} + 2^{\beta}\delta_{j+1}(i) + 2^{\alpha}\gamma_{j-1}(i)$$

(39)

with j = 0 .. l and i = 0 .. k, the required digits can be calculated as follows:

$$\delta_{j}(i) = u_{j}(i) \mod 2^{\alpha}$$

$$t_{j}(i) = (u_{j}(i) \operatorname{div} 2^{\alpha}) \mod 2^{\beta}$$

$$\gamma_{j}(i) = u_{j}(i) \operatorname{div} 2^{\alpha+\beta}$$

$$(40)$$

Because  $T = T(k) = \sum_{j=0}^{l} t_j(k) \ 2^{\beta j}$ , and all digits  $t_j(k) < 2^{\beta}$ , the Montgomery modular multiplication result is obtained by concatenation of all digits  $t_j(k)$ , so no post-processing (extra addition) is required.

The expression of equation (39) can be illustrated using figure 4.4.

figure 4.4: Calculation of digit t<sub>i</sub>(i)

In order not to lose any information bits during the division of U(i) by  $2^{\alpha}$ , the lower  $\alpha$  bits of the numerator of  $t_0(i)$  are set to zero by adding  $m_{i-1}N$ , which corresponds to adding  $m_{i-1}n_j$  to each digit  $t_j(i)$ . Because  $t_0(i-1)$  is the only value which has effect on these lower  $\alpha$  bits,  $m_{i-1}$  is defined as:

$$m_{i-1} = t_0(i-1) \cdot N' \mod 2^{\alpha}$$

(41)

The expressions (39), (40) and (41) provide an adapted algorithm of the Montgomery method for modular multiplication. The next step is to implement it in a systolic array.

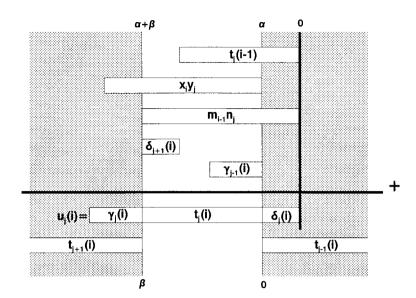

#### 4.2 The Montgomery algorithm adapted for systolic arrays

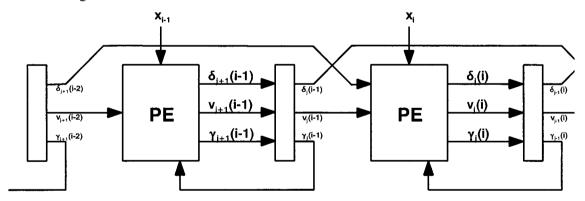

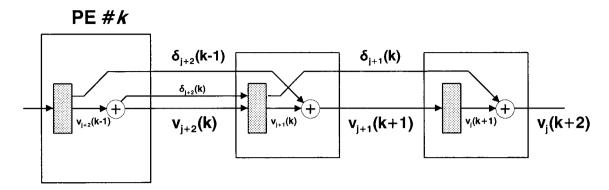

The MMM-result T(k) can be retrieved by concatenation of all digits  $t_0(k)$  to  $t_1(k)$ . The adapted algorithm of expression (39) can be implemented in a systolic array by loading  $x_0$  to  $x_k$  in the consecutive PE's of the array, and inputting the digits of T(-1), Y and N from least to most significant digit in the first PE serially. Each PE now has a set of registers, in which the input digits and temporary result are stored and passed on to the next PE. Each clock cycle PE number i calculates  $t_j(i)$  using  $t_j(i-1)$  from the preceding PE. The systolic array looks like the schematic of figure 4.5.

figure 4.5: Systolic array which calculates MMM(X,Y) using digits of X, Y, N and T

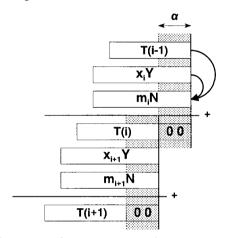

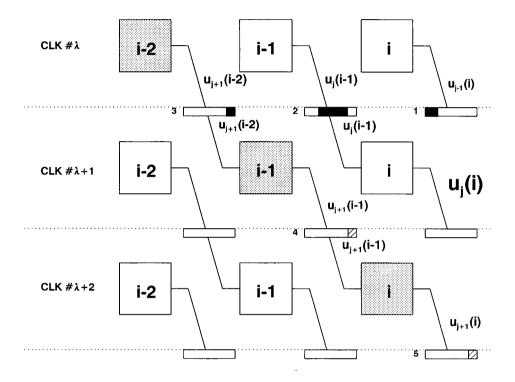

The data-flow in the systolic array can be illustrated by taking a 'snapshot' of a number of PE's for several clock cycles, as in figure 4.6.

figure 4.6: 'Snapshots' of the systolic array

This figure shows the input and output values of PE nrs. *i*-2 to *i* during three clock cycles. So each horizontal row shows what the three consecutive PE's are calculating simultaneously.

The dotted horizontal lines indicate a clock edge on which the input values of the PE input registers (placed on the dotted lines) are loaded. The grey marked PE's indicate the datapath of digit  $u_{i+1}$ .

Notice that the sum of the digit index j and the iteration step index i is the same for all output values  $u_j(i)$  of the PE's in the systolic array at a certain clock cycle. This sum, which is referred to as *time-index*, increases by one each next clock cycle. The time-indices of figure 4.6 thus are respectively i+j-1, i+j and i+j+1

By expression (40)  $u_j(i)$  can be written as binary vector ( $\gamma_j(i):t_j(i):\delta_j(i)$ ). PE #i calculates in clock cycles  $\lambda$  to ( $\lambda$ +2) digits  $u_{j-1}(i)$ ,  $u_j(i)$  and  $u_{j+1}(i)$ . To calculate  $u_j(i)$  in clock cycle  $\lambda$ +1, PE #i needs the following input parameters:

•  $t_i(i-1)$  : Can be loaded directly from register #2 (the input register of the current PE)

•  $m_{i-1}$  : Can be calculated directly using  $t_i(i-1)$  and constant N'

x<sub>i</sub>, y<sub>j</sub> and n<sub>j</sub>: Can be loaded directly from external memory or internal shift registers

γ<sub>i-1</sub>(i): Can be loaded directly from register #1 (the input register of the next PE)

•  $\delta_{i+1}(i)$  : Cannot be loaded from register #5 until clock cycle  $\lambda+3$

There seems to be a problem calculating  $u_j(i)$ , for the required  $\delta_{j+1}(i)$  can only be read from register #5 after two clock cycles. However, this  $\delta_{j+1}(i)$  can be added in PE's which are placed further in the systolic array (PE numbers i+1 ... k).

PE #i cannot read  $\delta_{j+1}(i-1)$  from register #4 until the next clock cycle  $\lambda+2$ . However,  $\delta_{j+1}(i-2)$  is available in the current clock cycle  $(\lambda+1)$  and can be read directly from register #3 (the input register of the previous PE). So if  $\delta_{j+1}(i-2)$  is used for calculation of  $u_j(i)$ , all input parameters are available and  $t_i(i)$  can be output by PE #i.

In order to find out which modifications to the Montgomery algorithm have to be made to add  $\delta_{j+1}(i-2)$  instead of  $\delta_{j+1}(i)$ , digit  $t_j(i)$  in expression (40) is reduced to  $t_j(-1)$ . This is done using a temporary identifier D(i), defined as:

$$D(i) = 2^{\alpha} x_{i} y_{i} + m_{i-1} n_{i} + 2^{\beta} \delta_{i+1}(i) + 2^{\alpha} \gamma_{i-1}(i)$$

(42)

Using this definition and applying integer division, from equation (40)  $t_i(i)$  can be written as:

$$t_{j}(i) = 2^{-\alpha} \left( t_{j}(i-1) + D(i) \right) \mod 2^{\beta}$$

$$= 2^{-\alpha} \left( 2^{-\alpha} \left( t_{j}(i-2) + D(i-1) \right) + D(i) \right) \mod 2^{\beta}$$

$$= 2^{-\alpha} \left( 2^{-\alpha i} t_{j}(-1) + \sum_{l=0}^{i} D(l) 2^{\alpha(l-i)} \right) \mod 2^{\beta}$$

(43)

By the Montgomery algorithm, T(-1) is set to zero, which implies that  $t_j(-1) = 0$  for  $j = 0 \dots l$ . Using this property and substituting D(l), we obtain:

$$t_{j}(i) = 2^{-\alpha} \left( 2^{-\alpha i} \sum_{l=0}^{i} \left( 2^{\alpha} x_{l} y_{j} + m_{l-1} n_{j} + 2^{\beta} \delta_{j+1}(l) + 2^{\alpha} \gamma_{j-1}(l) \right) 2^{\alpha l} \right) \mod 2^{\beta}$$

$$= 2^{-\alpha(i+1)} \left( \sum_{l=0}^{i} \left( 2^{\alpha} x_{l} y_{j} + m_{l-1} n_{j} + 2^{\alpha} \gamma_{j-1}(l) \right) 2^{\alpha l} + \sum_{l=2}^{i+2} 2^{\beta} \delta_{j+1}(l-2) 2^{\alpha(l-2)} \right) \mod 2^{\beta}$$

$$(44)$$

The last summation of  $\delta$ 's can be rewritten as:

$$\sum_{l=2}^{i+2} 2^{\beta} \delta_{j+1}(l-2) \ 2^{\alpha(l-2)} = \sum_{l=0}^{i} 2^{\beta-2\alpha} \delta_{j+1}(l-2) \ 2^{\alpha l} + 2^{\alpha i} \left( 2^{\beta-\alpha} \delta_{j+1}(i-1) + 2^{\beta} \delta_{j+1}(i) \right)$$

(45)

under the condition that both  $\delta_{i+1}(-2)$  and  $\delta_{i+1}(-1)$  are zero.

This 'rescaling' of  $\delta$  over two iteration steps results in the following  $t_i(i)$ :

$$t_{j}(i) = \left(2^{-\alpha} \sum_{l=0}^{i} \left(2^{\alpha} x_{l} y_{j} + m_{l-1} n_{j} + 2^{\alpha} \gamma_{j-1}(l) + 2^{\beta-2\alpha} \delta_{j+1}(l-2)\right) 2^{\alpha(l-i)} + \left(2^{\beta-2\alpha} \delta_{j+1}(i-1) + 2^{\beta-\alpha} \delta_{j+1}(i)\right) \mod 2^{\beta}$$

$$(46)$$

Instead of calculating  $t_j(i)$ , it is possible to calculate in each PE a digit  $v_i(i) < 2^{\beta}$ , defined as:

$$v_{j}(i) = 2^{-\alpha} \sum_{l=0}^{i} \left( 2^{\alpha} x_{l} y_{j} + m_{l-1} n_{j} + 2^{\alpha} \gamma_{j-1}(l) + 2^{\beta-2\alpha} \delta_{j+1}(l-2) \right) 2^{\alpha(l-i)} \mod 2^{\beta}$$

(47)

By splitting the expression above in a sum from l = 0 ... i-1 and l = i (as in expression (22)),  $v_j(i)$  can be calculated recursively by:

$$v_{j}(i) = \frac{v_{j}(i-1) + 2^{\alpha}x_{i}y_{j} + m_{i-1}n_{j} + 2^{\alpha}\gamma_{j-1}(i) + 2^{\beta-2\alpha}\delta_{j+1}(i-2)}{2^{\alpha}} \mod 2^{\beta}$$

(48)

In order not to lose any information bits after the integer division by  $2^{\alpha}$ , the lower  $\alpha$  bits of the numerator of  $v_0(i)$  are set to zero by adding  $m_{i-1}N$ , which corresponds to adding  $m_{i-1}n_j$  to the numerator of each digit  $v_i(i)$ . Analogous to equation (41),  $m_{i-1}$  can be calculated as:

$$m_{i-1} = v_0(i-1) \cdot N^{T} \mod 2^{\alpha}$$

(49)

only if the data bits of  $2^{\beta-2\alpha}$   $\delta_{j+1}(i-2)$  are located outside the  $\alpha$  least significant bits of the numerator of  $v_0(i)$ , thus if  $2^{\beta-2\alpha} \ge 2^{\alpha}$ , or  $\beta \ge 3\alpha$ . This is a stronger condition than the earlier imposed  $\beta \ge \alpha+2$ , but it is essential for preventing underflow while calculating digits  $v_0(i)$ .

If the numerator  $w_i(i)$  of the integer division of (48) is defined as:

$$w_{j}(i) = v_{j}(i-1) + 2^{\alpha}x_{i}y_{j} + m_{i-1}n_{j} + 2^{\alpha}\gamma_{j-1}(i) + 2^{\beta-2\alpha}\delta_{j+1}(i-2)$$

(50)

the digits  $v_i(i)$ ,  $\delta_i(i)$  and  $\gamma_i(i)$  can be defined as follows:

$$\delta_{j}(i) = w_{j}(i) \mod 2^{\alpha}$$

$$v_{j}(i) = (w_{j}(i) \operatorname{div} 2^{\alpha}) \mod 2^{\beta}$$

$$\gamma_{j}(i) = w_{j}(i) \operatorname{div} 2^{\beta+\alpha}$$

(51)

The expressions (49) to (51) provide a modified Montgomery algorithm which is suitable for execution in a dedicated systolic array, which we call MMM (Montgomery Modular Multiplier). However, the final result needs some  $\delta$ -correction, for we wish to calculate  $t_i(i)$  instead of  $v_i(i)$ .

#### 4.3 The final delta correction

After the digits  $v_j(k)$  have been calculated in the PE's, according to (46) all digits  $t_j(k)$  of T(k) = MMM(X,Y) are calculated as

$$t_{j}(k) = (v_{j}(k) + (2^{\beta-2\alpha}\delta_{j+1}(k-1) + 2^{\beta-\alpha}\delta_{j+1}(k))) \mod 2^{\beta}$$

(52)

In the systolic array this corresponds to adding the  $\delta$ 's, which are generated in the last two PE's, to the addition result of the last PE. For this purpose two extra (small) PE's are required, which add these  $\delta$ 's at the right place at the proper moment.

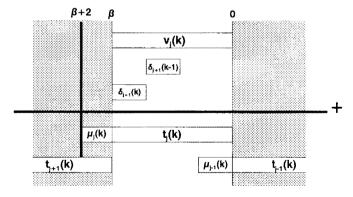

As  $t_j(k)$  contains only the lower  $\beta$  bits of the addition of (52), the overflow bits should be added to the next (more significant) digit  $t_{j+1}(k)$ . If this overflow is defined as  $\mu_j(k)$ , the final  $\delta$ -correction is executed as shown in figure 4.7.

figure 4.7: Final delta-correction

If  $\mu_{-1}(k)$  is set to zero, the calculation of  $t_i(k)$  can be rewritten as:

$$t_{j}(k) = \left( v_{j}(k) + \left( 2^{\beta-2\alpha} \delta_{j+1}(k-1) + 2^{\beta-\alpha} \delta_{j+1}(k) \right) + \mu_{j-1}(k) \right) \mod 2^{\beta}$$

(53)

by which the addition overflow is defined as:

$$\mu_{j}(k) = (v_{j}(k) + (2^{\beta-2\alpha}\delta_{j+1}(k-1) + 2^{\beta-\alpha}\delta_{j+1}(k)) + \mu_{j-1}(k)) div 2^{\beta}$$

(54)

Using equations (53) and (54), the output digits  $v_j(k)$  of the last PE can be corrected by adding the  $\delta$ -values, generated in the last two PE's. After this correction the desired Montgomery result  $t_j(i)$  is obtained.

#### 4.4 Summary of the adapted algorithm for systolic arrays

We have seen that the multiprecision case of Montgomery's algorithm can be executed by a systolic array using large PE's. To reduce the PE size, the T, Y and N values have been split in digits of  $\beta$  bits, which results in PE's of size  $\alpha$  x  $\beta$  bits (indicated as PE( $\alpha$ , $\beta$ )).

However, digit  $t_j(i)$  cannot be calculated directly in a systolic array, for the required  $\delta_{j+1}(i)$  is not yet available at the time of calculation. Instead digit  $v_j(i)$  is calculated using  $\delta_{j+1}(i-2)$ , which is stored in the input register of the previous PE at the time of calculation. This method however requires two extra (small) PE's, which add the last digits  $\delta_{j+1}(k-1)$  and  $\delta_{j+1}(k)$  to  $v_j(k)$  in order to obtain the desired digit  $t_j(k)$ .

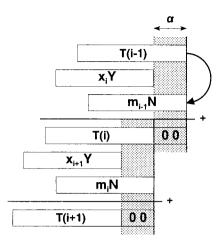

Figure 4.6 shows, that the required  $\gamma_{j-1}(i)$  which is necessary to calculate  $v_j(i)$  can be loaded from the input register of the next PE, and the required  $\delta_{j+1}(i-2)$  can be loaded from the input register of the preceding PE. The data flow during the calculation of  $v_{j+1}(i-1)$  and  $v_j(i)$  in two consecutive PE's is shown in figure 4.8.

figure 4.8: Register and PE output digits of two consecutive PE's

The Montgomery algorithm which is suitable for PE's of size  $\alpha \times \beta$  is as follows:

Montgomery conditions:

1

$n \ge 1$

$R=2^r=2^{k\alpha}$

7

```

2

2^{n-1} < N < 2^n, N is odd

8

RR^{-1} - NN' = 1

0 \le X, Y, T < 2N

3

9

3\alpha \le \beta \le n

1 \le \alpha \le n+2

4

10 l=\lceil n/\beta \rceil

5

s = l\beta \ge n

k=\lceil (n+2)/\alpha \rceil

11

r = k\alpha \ge n+2

\{input X, Y, N\}

m_{-1} = 0

for i = 0 to k do

begin

\gamma_{-1}(i) = 0

\delta_{l+1}(i) = 0

for j = 0 to l do

begin

{initialize input digits of first PE(i=0)}

v_i(-1) = 0

\delta_{j+1}(-2)=0

\delta_{i+1}(-1) = 0

w_i(i) = v_i(i-1) + 2^{\alpha}x_i y_i + m_{i-1} n_i + 2^{\alpha}\gamma_{i-1}(i) + 2^{\beta-2\alpha}\delta_{i+1}(i-2)

\delta_i(i) = w_i(i) \mod 2^{\alpha}

v_i(i) = (w_i(i) \operatorname{div} 2^{\alpha}) \operatorname{mod} 2^{\beta}

\gamma_i(i) = (w_i(i) \operatorname{div} 2^{\alpha+\beta}) \operatorname{mod} 2^{\alpha+1}

end \{for j\}

m_i = v_0(i) \cdot N' \mod 2^{\alpha}

end \{for i\}

{execute final delta-correction}

\mu_{-1}(k) = 0

for j = 0 to l do

begin

t_i(k) = (v_i(k) + 2^{\beta - 2\alpha} \delta_{i+1}(k-1) + 2^{\beta - \alpha} \delta_{i+1}(k) + \mu_{i-1}(k)) \mod 2^{\beta}

\mu_i(k) = (v_i(k) + 2^{\beta - 2\alpha} \delta_{i+1}(k-1) + 2^{\beta - \alpha} \delta_{i+1}(k) + \mu_{i-1}(k)) \text{ div } 2^{\beta}

end \{for j\}

\{T = T(k) = \sum_{i} t_i(k) \cdot 2^{\beta j} = MMM(X, Y) = XYR^{-1} \bmod N\}

```

## 5

## Hardware Design of the RSA-device

In the previous chapter it has been shown, that the Montgomery algorithm after some transformations can be executed by a dedicated systolic array (MMM) using a number of identical PE's which can process  $\alpha$  bits of X and  $\beta$  bits of Y within one clock cycle. The next step is to create a hardware design of a PE which executes the adapted Montgomery algorithm. Then an MMM-design is presented which consists of a cascade of these PE's. Finally an RSA chip design is proposed, which executes an exponentiation algorithm adapted for the MMM.

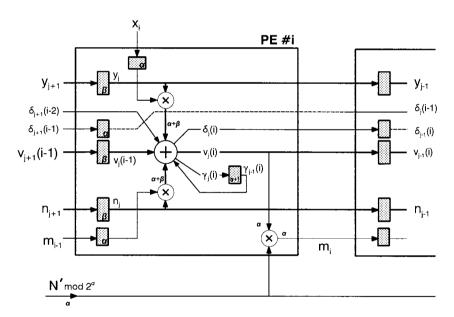

#### 5.1 Design of a PE

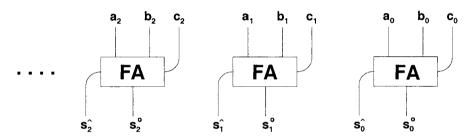

Before proceeding, the choice of  $\alpha$  and  $\beta$  is constrained to powers of 2, for this simplifies the hardware implementation of the integer division and multiplications significantly. Therefore, the constraint of  $\beta \geq 3\alpha$  implies that  $\beta \geq 4\alpha$  when the MMM is implemented in hardware.

To determine the size of the PE register for storage of  $\gamma_j(i)$ , we need to define an upper bound for digit  $w_j(i)$ . Because in equation (50) the summation term  $2^{\alpha}x_iy_j < 2^{2\alpha+\beta}$  and at least *one* addition carry bit is generated, it is stated that this upper bound is  $2^{2\alpha+\beta+1}$ .

#### **Proof:**

Assume that  $w_i(i) < 2^{2\alpha+\beta+1}$ , then by expression (51)  $\gamma_i(i) < 2^{\alpha+1}$ . Then by (50)  $w_i(i)$  is bounded by:

$$w_i(i) < 2^{\beta} + 2^{\alpha} \cdot 2^{\alpha+\beta} + 2^{\alpha+\beta} + 2^{\alpha+\beta} + 2^{\alpha} \cdot 2^{\alpha+1} + 2^{\beta-2\alpha} \cdot 2^{\alpha} = 2^{2\alpha+\beta+1} \left( 2^{-2\alpha-1} + 2^{-1} + 2^{-\alpha-1} + 2^{-\beta} + 2^{-3\alpha-1} \right)$$

To make an upper boundary estimate of the expression between parenthesis, the minimum value  $\beta = 4\alpha$  is used:

$$w_i(i) < 2^{2\alpha+\beta+1} (2^{-2\alpha-1} + 2^{-1} + 2^{-\alpha-1} + 2^{-4\alpha} + 2^{-3\alpha-1}) \le 2^{2\alpha+\beta+1}$$

for all  $\alpha \ge 1, \beta \ge 4\alpha$ .

(the expression between parenthesis equals 1 for  $\alpha = 1$ ).

So the assumption is true, and  $\gamma(i)$  can be stored in a register of width  $\alpha+1$  bits.

Now expression (54) implies, that  $w_j(i)$  is a binary vector of  $\delta_j(i)$  ( $\alpha$  LSB's),  $v_j(i)$  (bits  $\alpha$  to  $\alpha+\beta-1$ ), and  $\gamma_j(i)$  ( $\alpha+1$  MSB's).

Next to these values an  $m_i$  must be calculated, which will be used in the next PE. Equation (49) shows, that  $m_i$  can be calculated according to:

$$m_i = v_0(i) \cdot N^{\prime} \bmod 2^{\alpha} \tag{55}$$

This means, that a PE only needs to calculate a new  $m_i$  if it is calculating the first digit  $w_0(i)$  using  $x_i$ ,  $v_0(i-1)$ ,  $y_0$  and  $n_0$ , so when the PE is starting a new modular multiplication.

Additionally, because  $m_i$  has width  $\alpha$  bits, only the *lower*  $\alpha$  bits of  $v_o(i)$  and constant N' are required for the  $m_i$  calculation. The fact that carries propagate away from this  $m_i$  makes this Montgomery algorithm superior to the paper & pencil method.

For the calculation of  $w_j(i)$  digits  $y_j$  and  $n_j$  are required, which are loaded from the previous PE and passed on to the next PE each clock cycle. Digit  $x_i$  is loaded in PE #i (together with  $m_{i-1}$ ) each time a new modular multiplication is started, and remains there until all digits  $y_j$ ,  $n_j$  and  $v_j(i-1)$  have been loaded and processed in this PE (until  $w_l(i)$  has been calculated and a new modular multiplication can be started).

Furthermore it has been shown that the required  $\delta_{j+1}(i-2)$  can be loaded from the input register of the preceding PE, and  $\gamma_{j-1}(i)$  can be loaded from the input register of the next PE.

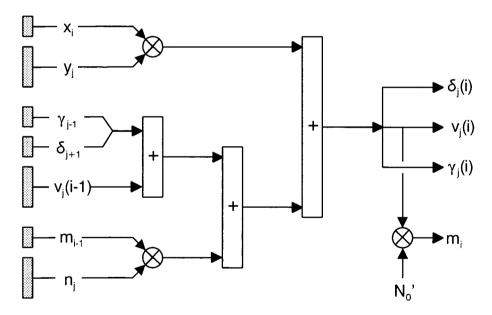

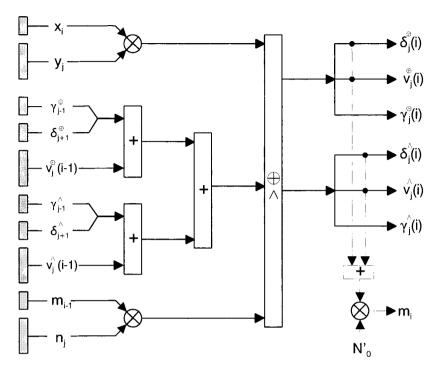

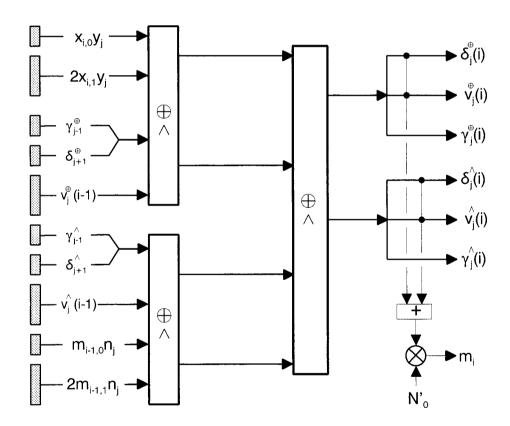

Using this description, the PE's of the MMM can be outlined as in figure 5.1.

figure 5.1: Outline of the PE's of the MMM

The 5-input adder, which is the core of the PE, adds the input values according to equation (50), which by expression (51) results in the desired  $\delta_j(i)$ ,  $v_j(i)$  and  $\gamma_j(i)$ .

The schematic shows that  $x_i$ ,  $m_{i-1}$  and  $\gamma_{j-1}(i)$  are local values which belong to PE #i. All other values are passed on to the next PE.

#### 5.2 Design of the MMM

As has been shown in the previous chapter, the MMM is a dedicated systolic array, consisting of a number of identical PE's which each execute part of an adapted version of the Montgomery algorithm. Because most exponentiation algorithms are based on repeated modular multiplications, the MMM provides a powerful core for a scalable RSA device. However, the MMM is not entirely compatible with RSA exponentiation because of two reasons:

- Two conversions to the *N*-residue domain and one conversion back to the integer-domain are required at the start and ending of an exponentiation, for all modular multiplications are executed in the *N*-residue domain.

- N-residue values have width n+1 bits, while RSA values all have width n bits.

The required conversions have little impact on the exponentiation performance, for exponentiation needs at most 1.5n modular multiplications (see paragraph 2.2). Because RSA security is based on a large value of n (1024 bits), the conversions take about 0.2% of the whole exponentiation time. However, these conversions still need precalculation of the constant  $R^2$  mod N.

The second drawback can be minimized by feeding back bit n+1 of the MMM-result internally, so only digits  $t_0(i)$  to  $t_{l-1}(i)$  (containing n databits) will be stored in memory for storage of intermediate results. Equation (15) shows that the final conversion back to the integer domain reduces the n+1 bit N-residue value to an n-bit integer value. In this way the user does not have to concern about the Montgomery algorithm, except for providing the constant  $R^2 \mod N$ .

#### 5.2.1 Delta-correction

Figure 4.8 shows how the PE's of the MMM are mutually connected. This PE interconnection can also be used for the final  $\delta$ -adjustment, which adds the  $\delta$ -digits generated in the last two PE's of the MMM to digit  $v_i(i)$  (equation (52)). If this addition is split into:

$$t_{j}(k) = \left( \left( v_{j}(k) + 2^{\beta-2\alpha} \delta_{j+1}(k-1) \right) \mod 2^{\beta} + 2^{\beta-\alpha} \delta_{j+1}(k) \right) \mod 2^{\beta}$$

$$= \left( v_{j}(k+1) + 2^{\beta-\alpha} \delta_{j+1}(k) \right) \mod 2^{\beta}$$

$$= v_{j}(k+2) \mod 2^{\beta}$$

(56)

digits  $v_j(k+2)$  and  $v_{j+1}(k+1)$  can be calculated by two extra (smaller) PE's in cascade, placed behind the last PE of the MMM. This principle is shown in the schematic of figure 5.2.

figure 5.2: δ-correction using two small dedicated PE's

Using these two dedicated PE's for  $\delta$ -correction at the end of the last PE, digits  $v_j(k+2)$  are calculated  $(j = 0 \dots l)$  which by (56) are equal to the Montgomery output digits  $t_j(k)$ .

#### 5.2.2 Pipelined multiplication in the MMM

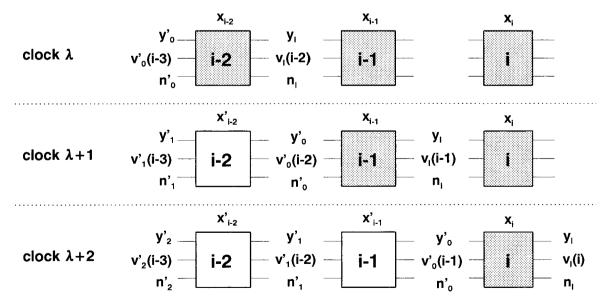

If a PE has processed all l+1 digits of one modular multiplication, it is ready and can start a new calculation by loading the first digit  $v_0'(i)$  of the next modular multiplication. This pipelining can be illustrated by figure 5.3, which shows the transition of two consecutive multiplications. In this figure the grey PE's are calculating digits of the first modular multiplication, the white PE's

are calculating the next multiplication. If all digits  $y_j$ ,  $n_j$  and  $v_j(-1)$  (j = 0 ... l) have been loaded in a PE of the MMM, this PE is ready and can start loading the first digits of the next modular multiplication.

figure 5.3: Data flow of two consecutive modular multiplications in the MMM

Two consecutive multiplications in the MMM do not mutually interfere:

• In figure 5.3, in clock cycle  $\lambda+2$  PE #i calculates the last digit  $v_1(i)$  of the first multiplication, and should add  $\delta_{l+1}(i-2)$ , which is zero by definition (there are only l digits of  $\delta_j(i)$ ). However, instead  $\delta'_0(i-2)$  which has been calculated in PE #i-2 in clock cycle  $\lambda+1$  (and loaded in PE #i-1 in clock cycle  $\lambda+2$ ) is added! This is allowed, for all  $\delta_0(i)$  digits which are calculated starting a new modular multiplication are zero. The proof for this is as follows:

By equations (51) and (50) and  $\beta \ge 4\alpha$  the following applies:

$$\delta_0(i) = w_j(i) \mod 2^{\alpha} =$$

$$= \left( v_0(i-1) + 2^{\alpha} x_i y_0 + m_{i-1} n_0 + 2^{\alpha} \gamma_{-1}(i) + 2^{\beta-2\alpha} \delta_1(i-2) \right) \mod 2^{\alpha}$$

$$= \left( v_0(i-1) + m_{i-1} n_0 \right) \mod 2^{\alpha}$$

(57)

Equation (49) shows that:

$$m_{i-1}n_0 = v_0(i-1) \cdot N'n_0 \mod 2^{\alpha}$$

(58)

Using this equation and that  $N'n_0 \mod 2^{\alpha} = -1$  (see paragraph 6.4.1),  $\delta_0(i)$  can be written as:

$$\delta_0(i) = (v_0(i-1) + (v_0(i-1)N'n_0) \mod 2^{\alpha}) \mod 2^{\alpha} = 0$$

(59)

which shows that all digits  $\delta_0(i)$  are zero and will not interfere with the calculation of the last digit of the preceding modular multiplication.

The PE which calculates the last digit of the preceding multiplication, stores the overflow bits in the γ-register (α+1 bits). The next clock cycle, when this PE starts to calculate the first digit of the next modular multiplication, the contents of this γ-register will be added. Therefore digit γ<sub>i</sub>(i) must be zero (for all i = 0 ... k) in order not to interfere with the next multiplication. This can be shown using equation (50):

$$w_{l}(i) = v_{l}(i-1) + 2^{\alpha}x_{i}y_{l} + m_{i-1}n_{l} + 2^{\alpha}\gamma_{l-1}(i) + 2^{\beta-2\alpha}\delta_{l+1}(i-2)$$

$$= v_{l}(i-1) + 2^{\alpha}x_{i}y_{l} + 2^{\alpha}\gamma_{l-1}(i)$$

(60)

Because digits  $y_0 \dots y_{l-1}$  contain at least n bits of  $Y(l = \lceil n/\beta \rceil)$ , digit  $y_l$  can contain at most bit n+1, which implies that  $2^{\alpha}x_iy_l < 2^{2\alpha}$ . Now  $w_l(i)$  can be bounded by:

$$w_I(i) < 2^{\beta} + 2^{2\alpha} + 2^{2\alpha+1} < 2^{\beta+1}$$

(61)

By expression (51),  $\gamma_l(i) = w_l(i)$  div  $2^{\beta+\alpha} = 0$  for all  $i = 0 \dots k$ , which proves that the  $\gamma$ -register only contains zeroes when the PE starts a new modular multiplication.

So because both  $\delta_0(i)$  and  $\gamma_i(i)$  are zero for each i, two multiplications in the MMM can be executed after each other without interference. However, each PE which starts a new modular multiplication must be initialized by loading the new  $x_i$  and  $m_{i-1}$  digits and resetting the  $\gamma$ -register (contents are undefined after a chip reset, and must be set to zero).

#### 5.2.3 Reducing the number of PE's

For purpose of scalability it is desired to change the number of PE's to optimally fit the environment in which the RSA device is used. We have seen before:

- $k = \lceil (n+2)/\alpha \rceil$ : There are k+1 digits of X to be loaded in the MMM, so k+1 PE's are used during one modular multiplication.

- $l = \lceil n/\beta \rceil$ : There are l+1 digits of Y, T and N to be loaded in the MMM, so each PE must process l+1 digits during one modular multiplication.

Because  $\beta \ge 4\alpha$ , k > l. This means, that there are more PE's to be used (X-digits to be loaded) than Y, N and T digits to be loaded by each PE.

Choosing p = k+1 provides just enough PE's to load all X-digits, but because l+1 (the number of digits running through the MMM) is smaller than k+1, there are p - (l+1) PE's not active. These non-active PE's cannot already start a new multiplication, for this requires the output digits of the current multiplication.

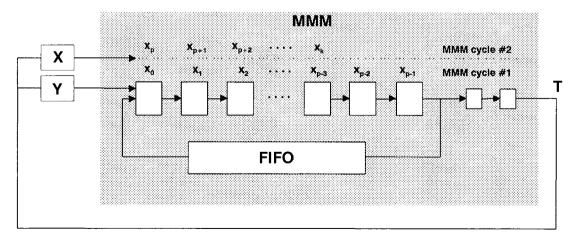

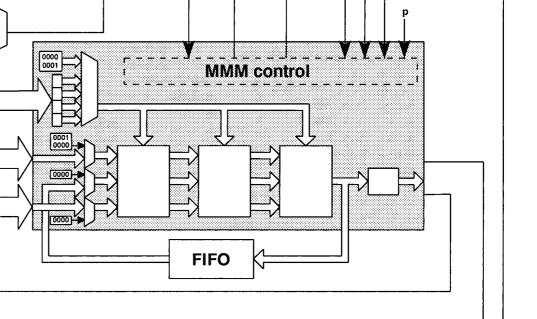

In order to keep all PE's of the MMM active all the time, at most l+1 PE's should be used and the intermediate results are fed back into the first PE internally. In this case data would run through the same PE multiple times (MMM cycles) during one modular multiplication, each time processing a new digit of X. Because the MMM must be able to contain all intermediate results (all  $v_j(i)$ 's), a FIFO buffer of depth (l+1) - p is required (l+1) digits, of which p are stored in the PE registers). This would yield an MMM which looks like figure 5.4.

figure 5.4: MMM configuration with internal feedback

The first MMM cycle digits  $x_0 ext{...} x_{p-1}$  are loaded in the PE's. The first PE in the MMM is ready for a new MMM cycle if it has calculated the last digit  $v_l(0)$ . At that time the next digit  $x_p$  can be loaded to calculate  $v_0(p)$ , which starts the second MMM cycle. One modular multiplication requires  $\lceil (k+1)/p \rceil$  MMM cycles. As we have seen before, in two successive PE's the first digit of a new MMM cycle does not affect the calculation of the last digit of the preceding MMM cycle.

All digits  $v_j(p-1)$  which leave the last PE of the MMM while the first PE is not ready yet (p < l+1) are stored in the FIFO buffer until the second MMM cycle can start. Because PE #i needs both  $\delta_{j+1}(i-2)$  and  $\delta_{j+1}(i-1)$  and the intermediate result  $v_j(i)$  from the preceding PE, all must be stored in the FIFO. This FIFO therefore will have (l+1) - p levels of width  $\beta+2\alpha$  bits.

When the last MMM cycle (in which  $v_j(k)$  is calculated) has been completed, after  $\delta$ -correction the final digits  $t_j(k)$  with j=0 ... l-1 are written to external memory and input to the MMM for the next modular multiplication. Digit  $t_i(k)$ , which contains at most bit n+1 of T (if n is a multiple of  $\beta$ , see figure 4.2) can be stored internally and fed back to one of the MMM inputs (multiply) or both inputs (squaring) for the next modular multiplication of the exponentiation algorithm. In this way in the external memory at most  $s=l\beta$  bits (s is the smallest multiple of  $\beta$  larger than n,  $s < n+\beta$ ) have to be stored, and the user will not be confronted with extra memory space for storage of the overflow digit  $t_i(k)$  of the Montgomery algorithm.

A new modular multiplication can start as soon as the first PE of the MMM has calculated it's last digit in the last MMM cycle, so when the FIFO is empty.

Because the number of PE's p can be chosen arbitrarily, it is possible that the final  $v_j(k)$  digits are calculated by a PE in the middle of the MMM. All next PE's must then be set in a 'bypass mode', which forces them to pass on the input result to the output without any modification.