| MASTER                                                                     |

|----------------------------------------------------------------------------|

| Optimization of inter processor buffers using regular location assignment. |

|                                                                            |

|                                                                            |

| van Bladel, F.M.A.M.                                                       |

| Award date:<br>1993                                                        |

|                                                                            |

| Link to publication                                                        |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# Optimization of inter processor buffers using regular location assignment

By: F.M.A.M van Bladel

Master thesis on a project at the Philips Research Laboratories in Eindhoven under supervision of:

Prof. dr. ing J.A.G. Jess

Coach (university): Dr. ir. J. van Eijndhoven Coach (Philips) : Dr. ir. J.L. van Meerbergen Coach (Philips) : Ir. P. Lippens

The department of electrical engineering of the Eindhoven university of technology does not accept any responsibility for the contents of student reports and master theses.

#### Abstract

Looking at a VLSI chip one can distinguish different kinds of recourses. There are arithmetic-buffer- and control units and interconnection. The arithmetic units can be designed in a very short time with the use of a silicon compiler like PIRAMID or PHIDEO. During the design of these units little attention is payed to the communication problems that may arise between different arithmetic units. To solve these problems inter processor buffers (IPBs) are used. These IPBs can be designed with tools like ESPA or MATCHBOX. This report focuses on the techniques used by the tool MATCHBOX.

The techniques used by MATCHBOX are presented and compared with a new technique called regular placement. This regular placement technique aims at reducing the area used for address generation in the IPB. This is done by assigning locations to samples is such a way that the address sequences become regular.

For different kind of applications IPBs are generated with regular placement and the techniques from MATCHBOX. It appeared that regular placement did not result in a significant reduction in area costs, when the IPB was designed for only one application. For these IPBs the techniques and target architectures of MATCHBOX will cover the design space very well. But when IPBs are designed to handle more than one application regular placement is a good technique for reducing the size of this merged IPB.

# Contents

| 1 | Intr | roduction                                           | 3          |

|---|------|-----------------------------------------------------|------------|

| 2 | MA   | тснвох                                              | 7          |

|   | 2.1  | Absolute location assignment                        | 9          |

|   | 2.2  | Counter addressing                                  | 12         |

|   | 2.3  | Relative location assignment                        | 14         |

|   | 2.4  | Target architectures                                | 16         |

|   |      | 2.4.1 The counter architecture                      | 16         |

|   |      | 2.4.2 The address table architecture                | 17         |

|   |      | 2.4.3 The delta table architecture                  | 18         |

|   |      | 2.4.4 The run length delta table architecture       | 20         |

| 3 | Reg  | gular placement                                     | 23         |

|   | 3.1  | The solution space of regular placement             | 25         |

|   |      | 3.1.1 Solution space exploration                    | 27         |

| 4 | Tes  | t applications                                      | 35         |

|   | 4.1  | Matrix transposition                                | 35         |

|   | 4.2  | Zig-zag transformation                              | 36         |

|   | 4.3  | Spiral left turning                                 | 37         |

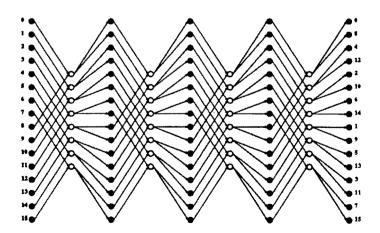

|   | 4.4  | Radix 2 Fast Fourier Transformation                 | 37         |

|   | 4.5  | Radix 4 Fast Fourier Transformation                 | <b>3</b> 8 |

| 5 | Res  | sulting IPBs                                        | 39         |

|   | 5.1  | Results Matchbox                                    | 39         |

|   |      | 5.1.1 The memory sizes                              | 39         |

|   |      | 5.1.2 The address generators                        | <b>3</b> 9 |

|   |      | 5.1.3 The total cost of the inter processor buffers | <b>4</b> 0 |

|   | 5.2  | Results regular placement                           | 41         |

| 6 | Me   | rging of IPBs                                       | 45         |

|   | 6.1  | Results MATCHBOX and regular placement              | 45         |

|   | 6.2  | Merging of N applications                           | 47         |

| 7 | Cor  | nclusions and recommendations                       | 51         |

|   | • |          |

|---|---|----------|

| 2 |   | CONTENTS |

| A | PIF                                                | 53 |  |  |  |  |

|---|----------------------------------------------------|----|--|--|--|--|

|   | A.1 PIF description of matrix transposition        | 53 |  |  |  |  |

|   | A.2 PIF descrition of 8 × 8 zig-zag transformation | 54 |  |  |  |  |

|   | A.3 PIF description of 4 × 4 left turning spiral   | 56 |  |  |  |  |

|   | A.4 PIF description of radix 2 FFT                 | 57 |  |  |  |  |

|   | A.5 PIF description of radix 4 FFT                 | 58 |  |  |  |  |

| В | Regular placement program                          | 59 |  |  |  |  |

| C | C Matchbox memory sizes                            |    |  |  |  |  |

| D | Matchbox address generator sizes                   | 65 |  |  |  |  |

| E | Result regular placement                           | 69 |  |  |  |  |

| F | archtecture merged IPB                             | 71 |  |  |  |  |

| G | Unix script                                        | 73 |  |  |  |  |

# Chapter 1

# Introduction

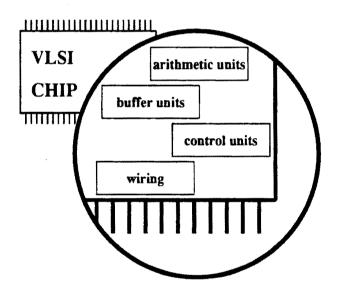

Looking at a VLSI chip different units which perform different tasks can be distinguished.

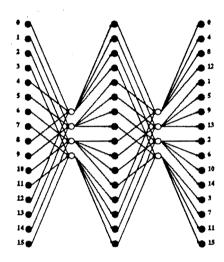

Figure 1.1: The different units on a VLSI chip

The arithmetic units together with the buffer units make up the data path which is controlled by the control units. The wiring is used to connect the different units together. The arithmetic units are the producers and consumers of the data. With the use of a silicon compiler arithmetic units can be designed in a very short time. For applications with a clock to sample rate ratio between 1 and 20 (high throughput) the silicon compiler PHIDEO [2] is used. For applications with such a ratio of 1000 or more (low throughput) PIRAMID [10] is used. Complex systems however need more than one of these arithmetic units on one chip. During the design of these units, PHIDEO and PIRAMID pay little or no attention to the communication problems that may arise between these different arithmetic units. To make the communication between two arithmetic units or between arithmetic units and outside world possible, inter processor buffers (IPBs) are used. These

IPBs can be designed with tools like ESPA and MATCHBOX. ESPA is used to design IPBs for arithmetic units which are designed with PIRAMID. MATCHBOX is used for the design of IPBs which have to solve the communication problems between arithmetic units of PHIDEO.

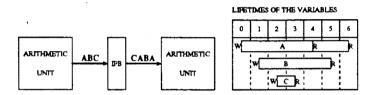

Because the arithmetic units are designed before the IPBs are designed it is known in what order and on which timepoints data is produced or consumed. An IPB can be seen as a black box between two arithmetic units which input is a certain stream of data (samples) and which output is delayed version of that input. Where each sample can have a different delay.

Figure 1.2: The inter processor buffer with its in and outputs

A sample can only be produced once but can be consumed multiple times. The lifetime of a sample is the time between its production and its last consumption. During this lifetime it has to be stored in the memory of the inter processor buffer.

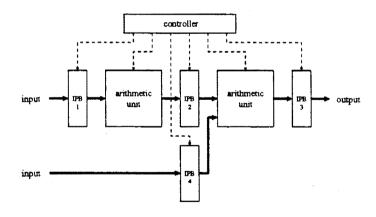

Figure 1.3 shows an example of an architecture at the chip level.

Figure 1.3: multi arithmetic unit overview

As can be seen in Figure 1.3, IPBs can be needed quite often on a chip. That is why it is relevant to reduce the size of these individual IPBs [3] [4] [5] [8] [9]. When a arithmetic unit is capable of executing different applications, a different IPB is necessary for each application. Therefore merging different IPBs to one IPB which is capable of coping with different applications is also an issue which needs attention.

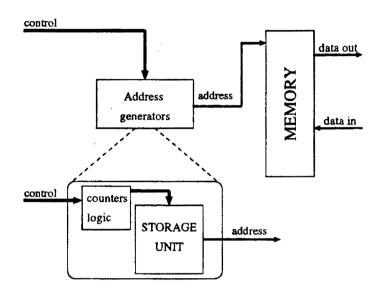

An inter processor buffer consists of a memory block and address generators (Figure 1.4). In most of the cases two address generators are needed, one for

the read accesses and one for write accesses. But in some cases these two address generators can be merged together to one address generator which generates the addresses both for the read and write accesses.

Figure 1.4: The inter processor buffer

The address generators consist of counters, some logic and a storage unit. This storage unit can be a PLA a ROM or a standard cell implementation. In this storage unit the information of which address has to be generated is stored. Several different strategies exist to store this information. One can store the actual addresses, the differences between consecutive addresses, or the runlength of rows of the same deltas and the delta size. Which way of storing the addresses, and what kind of storage unit is used, will be determined by the resulting size of the address generator. The smallest solution will be selected.

But before the problem of address generation is under discussion we first have to determine a place for all the samples in the memory in such a way that no samples with overlapping lifetimes are stored in the same memory location.

The research has been focused primary on MATCHBOX. All the techniques of MATCHBOX optimize either the memory cost or the addressing hardware cost. But as a result of optimizing the one, the other has unpredictable cost. These unpredictable cost turns out to be very high in some cases. The goal is, to find a technique which makes a good trade off between memory cost and addressing cost. An address generator will be relatively small when the addresses it has to generate are in some way regular. To achieve that the samples have to be placed in the memory in a regular way. This has to be done without to much extra memory cost, otherwise the cost of the total IPB will be too high.

The search for regularity in a address sequence can be done at different levels. For example one can try to find regularity at the bit level of the address words and aim to generate these bits with a counter, and try to re-use the bits of this counter as much as possible [6]. Or one can try to find regularity at the word

level and try to generate the entire address word with a counter or an other architecture. Both techniques are a subject of research at the Philips Nat. Lab. This paper will deal with the search for regularity at the word level, and with the consequences for memory and address generator size.

Another goal of the research was to develop a flexible address generator. The ultimate flexible solution is a programmable solution. In this way the behaviour of the inter processor buffer can be changed by changing the program. The other extreme in this view is the dedicated single application IPB. In between these two extremes lies merging the IPB for a few applications. By making it possible to use an inter processor buffer for multiple problems the chip area that is used by these buffers can decrease because of the reuse of hardware resources. All these different IPB have been subject of investigation.

In chapter 2 the techniques of MATCHBOX will be discussed. In chapter 3 the technique of regular placement will be explained and the different techniques which are used to increase the quality of the results are discussed. Also some techniques to reduce the computation time are presented here. In chapter 4 the applications which are use in the tests are presented. In chapter 5 the results of MATCHBOX and regular placement will be presented and the solutions will be compared. In chapter 6 the merging of different application into one IPB will be discussed. In chapter 7 conclusions will be drawn and some recommendations will be provided.

# Chapter 2

# **MATCHBOX**

PHIDEO is a silicon compiler targeted at the design of high performance real time systems with high sampling frequencies such as HDTV. It supports the complete design trajectory starting from a high level specification all the way down to layout. At a certain point in this design traject the production and consumption time points of samples and their source and destination arithmetic units are known. The problem is now to synthesize an architecture so that the area of memories, address generators and interconnection hardware is minimized. This task can be divided into two sub-tasks.

- 1. memory allocation ⇒ MEDEA.

- 2. location assignment and address generation  $\Rightarrow$  MATCHBOX.

The first step is memory allocation. Here the decision is made which samples share the same memory. After this step it is exactly known how many memories will be used and how the memories are connected to the arithmetic units. The remaining problem is now to store the samples in the memories in such a way that the size of the IPBs is minimized. The place of the samples in the memory and the timepoints at which they are produced and consumed determine the sequence of addresses that has to be generated. The list of timepoints and addresses is called an address schedule. To determine an address schedule the data schedule is used. A data schedule is a list of read and write timepoints of the different samples.

| Framelength $= 5$                        |   |   |  |  |  |  |  |  |  |

|------------------------------------------|---|---|--|--|--|--|--|--|--|

| sample   Write timepoint   Read timepoin |   |   |  |  |  |  |  |  |  |

| A                                        | 0 | 6 |  |  |  |  |  |  |  |

| В                                        | 1 | 5 |  |  |  |  |  |  |  |

| C                                        | 2 | 9 |  |  |  |  |  |  |  |

| D                                        | 3 | 8 |  |  |  |  |  |  |  |

| E                                        | 4 | 7 |  |  |  |  |  |  |  |

Table 2.1: A data schedule

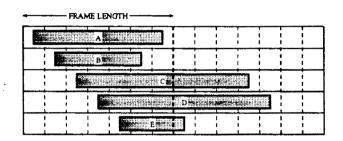

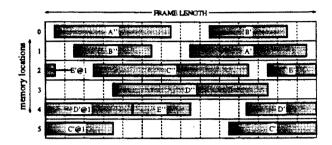

All applications which are used during Digital Signal Processing (DSP) have a repetitive nature. That means that the data schedule repeats after a certain time. One repetition of the data schedule is called a *frame*. The time one repetition takes is called the *frame length*. It is possible that a sample is read in a later frame than the one in which it is written. Than it is said that the sample crosses the *frame boundary*. With the use of the information from the data schedule a lifetime diagram of the samples can be constructed. The lifetime diagram of the samples for one repetition derived from the data schedule in Table 2.1 is shown in Figure 2.1.

Figure 2.1: Lifetime diagram for one repetition

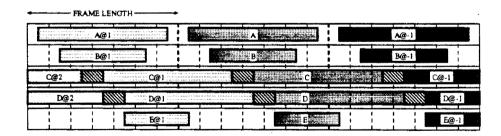

But the data schedule in Table 2.1 is repetitive and it also contains samples which cross the frame boundary. That means that during one frame not only the samples of the current frame can be alive but also samples from previous frames. The samples from previous frames are called *delayed versions* of the current samples. This is indicated with a '@1' suffix. The number in this suffix indicates how many frames ago the sample started living. Figure 2.2 shows the lifetimes during several frames.

Figure 2.2: Lifetimes of the samples during several frames

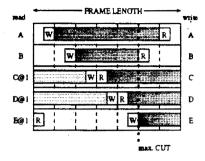

It can be seen that the pattern of lifetimes is the same every frame. So to characterise the application it is enough to know the lifetimes during one frame. The lifetimes during one frame can be seen in Figure 2.3.

Figure 2.3: Lifetimes of the samples during one frame

This lifetime diagram is used to determine the address schedule. When two samples are never alive at the same time they can share the same memory location. For the lifetime diagram that means that samples with non-overlapping lifetimes can share the same location. When it is tried to store two samples with overlapping lifetimes in the same location a lifetime clash occurs. An address schedule which contains lifetime clashes is called 'not valid'. From the lifetime diagram the minimum memory size which is necessary to store all the samples can be derived. The minimum memory size equals the maximum cut of alive samples in the life time diagram. This can be explained as follows. At the timepoint where the cut is maximal, there are for example 'X' samples alive. Because all are alive at this timepoint they can not share the same memory location. So at this point in time 'X' memory locations are necessary. This lower bound of the memory size will be called  $M_{lowb}$ . For the lifetime diagram from Figure 2.3 the maximum number of samples which are alive simultaneously is five. A maximum cut is indicated with the dotted line.

In the search for a valid address schedule which is cheap in area costs PHIDEO evaluates three different techniques. These three techniques will be explained in the following sections.

# 2.1 Absolute location assignment

Absolute location assignment is an assignment of memory locations to the samples of a data schedule in such a way that each version of a sample is written into the same memory location every frame. So after applying absolute location assignment every sample has its own absolute address which stays the same every frame. That is the reason why this technique is called absolute location assignment. The location of a sample is independent of the frame. This is indicated in Equation 2.1 where location(s,f) represents a function which assigns a location to sample s during frame f. L(s) represents a location assignment function which only depends on s.

$$location(s, f) = L(s)$$

(2.1)

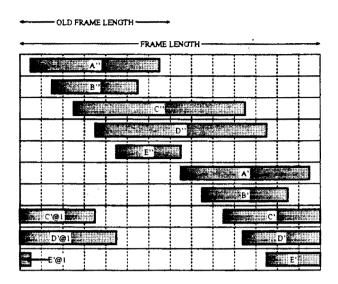

Problems occur when there are samples which lifetime is longer than the framelength. For example samples 'C', 'D' in Figure 2.1. In this case it is impossible to come up with a valid schedule. This is because of the restriction that a sample has to be written to the same memory location every frame. Using this restriction, sample C and its delayed version C@1 have to be stored in the same location, the same yields for sample D. But sample 'C@1' and 'D@1' are not read yet when 'C' and 'D' have to be stored again. A lifetime clash exists between 'C' and 'C@1' and between 'D' and 'D@1'. So it is not possible to store 'C@1' and 'C' or 'D@1' and 'D' in the same location. To solve this problem the frame length is expanded. By expanding the frame length the new framelength becomes an integer times the old framelength. The samples which are starting to live during this new frame will be treated as different samples. So before expansion 'A' and 'A@1' where the same samples only A@1 is a delayed version of A. After expansion they are treated as different samples. This is indicated by changing the names. For sample A this is shown in Table 2.2 for an expansion of two.

| old sample name | new sample name |

|-----------------|-----------------|

| A               | A'              |

| A@1             | A''             |

| A@2             | A'@1            |

| A@3             | A"@1            |

Table 2.2: Sample names before and after expansion

The number of expansions necessary equals the number of frames in which the longest living sample is alive. This is shown in Equation 2.2.

$$Number of expansions = \lceil \frac{longest \ lifetime}{framelength} \rceil$$

(2.2)

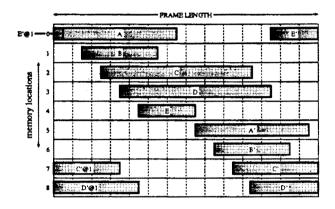

For our example from Figure 2.3 an expansion of two will be enough. The resulting data schedule after expansion can be seen in fig 2.4.

Figure 2.4: Frame expansion for absolute location assignment

By expanding the frame length the characteristics of the application are not changed. Only the constraint that the address sequence has to be repetitive after one frame is relaxed by increasing the framelength. Now the address sequence only has to be repetitive after N old frames, with N the number of expansions. With this new lifetime diagram it is possible to find a valid schedule. The problem that samples clash with their delayed versions is solved now, because there are no samples left which lifetime is longer than the framelength. PHIDEO uses graph colouring techniques to solve the problem of placing the samples without life time clashes in an as small as possible memory. The graph that has to be coloured is called a conflict graph. In this graph the different vertices are the samples. An edge between two vertices exists, when the two samples have overlapping life times. When the resulting graph is an interval graph, than the left edge algorithm will be used, which runs in  $O(n \log n)$  time [7] for n samples. This will result in a minimal number of colours thus a memory size equal to  $M_{lowb}$ . When the graph is not an interval graph but a circular arc graph left edge cannot be used. Colouring a circular arc graph is known to be a NP-complete problem [11]. Consequently no polynomial time algorithm is known that solves this problem. Furthermore Tucker [12] proved that an optimal result  $M_{circ}$ , found by an exhaustive algorithm for example can be far from the lower bound  $M_{lowb}$ . In [12] Tucker shows circular arc graphs for which

$$M_{circ} = 2 \times M_{lowb} - 1 \tag{2.3}$$

From the lifetime diagram can be derived whether the conflict graph will be an interval graph or a circular arc graph. If there is a timepoint during a frame at which no sample is alive than the resulting graph will be an interval graph and the left edge algorithm will be used to colour the graph. In the life time diagram of Figure 2.4 there is no timepoint on which no sample is alive so graph colouring with heuristics is used. This leads to a placement like in Figure 2.5.

Figure 2.5: absolute location assignment resulting from graph colouring

The schedule is valid now but the complexity of the address sequence is not taken into account. The resulting addressing sequences can be seen in Table 2.3

| Time          | Write    | Read     |

|---------------|----------|----------|

| (clock cycle) | location | location |

| 0             | 0        | 2        |

| 1             | 1        | X        |

| 2             | 2        | X        |

| 3             | 3        | 5        |

| 4             | 4        | 4        |

| 5             | Х        | 1        |

| 6             | X        | 0        |

| 7             | 1        | 4        |

| 8             | 0        | X        |

| 9             | 5        | X        |

| 10            | 4        | 2        |

| 11            | 2        | 3        |

| 12            | X        | 0        |

| 13            | X        | 1        |

Table 2.3: Addressing sequences absolute location assignment

In Table 2.3 the address sequences for one frame are shown. These are the only sequences which have to be generated. The address sequences during the other frames are a repetition of these sequences. The memory needed in this case is larger than the minimum. When the frame has to be expanded the addressing sequences are longer than the number of samples. Also by using graph colouring no attention is payed to how difficult it will be to generate these sequences. So although absolute location assignment aims at an as small as possible memory the cost of the total inter processor buffer can turn out to be high because of excessive cost of address generation.

### 2.2 Counter addressing

Counter addressing is a kind of absolute location assignment. So the restriction that the delayed versions of a sample are stored in the same memory location every frame still holds. The difference is that the samples are not placed with graph colouring techniques but in such a way that the write address sequence can

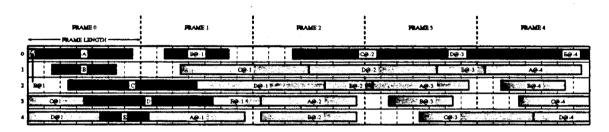

be generated with a counter. Because counter addressing is based on absolute addressing it is possible that the frame has to be expanded. Aiming at a counter solution can sometimes result in a large memory, as shown in Figure 2.6 for the application from Figure 2.2.

Figure 2.6: absolute location assignment for counter addressing

From Table 2.4 it follows that the write addressing sequence can be generated with a counter which is very cheap. But the read sequence is still as hard to generate as with absolute location assignment.

| Time          | Write<br>location | Read<br>location |

|---------------|-------------------|------------------|

| (clock cycle) | location          | location         |

| 0             | 0                 | 0                |

| 1             | 1                 | X                |

| 2             | 2                 | X                |

| 3             | 3                 | 7                |

| 4             | 4                 | 8                |

| 5             | Χ                 | 1                |

| 6             | X                 | 0                |

| 7             | 5                 | 4                |

| . 8           | 6                 | X                |

| 9             | 7                 | X                |

| 10            | 8                 | 2                |

| 11            | 0                 | 3                |

| 12            | X                 | 6                |

| 13            | X                 | 5                |

Table 2.4: Addressing sequences counter addressing

Because the lifetime diagram consist of a two times expanded frame, the address sequence will still be twice as long as the number of samples. For the write address generator this is not really a problem because the counter address generator will stay quite cheap. But for the read address generator holds the same as for the address generators following from absolute location assignment. The addressing hardware of the inter processor buffer generated with counter addressing will consist of a cheap write address generator and a read address generator

which has cost comparable to the one generated with absolute addressing. But because the memory needed for this counter technique is large in a lot of cases, the total cost of the inter processor buffer can be high due to large memory cost.

# 2.3 Relative location assignment

In this case a pointer technique is used. This pointer is incremented every frame. Relative to this pointer position the location of the different samples is the same. This means that the absolute location of a sample in the memory is dependent on the frame. This technique is only possible if the location calculations are executed using modulo arithmetic. The absolute location of a sample s in frame f is defined as:

$$location(s, f) = (P(f) + R(s)) mod M$$

(2.4)

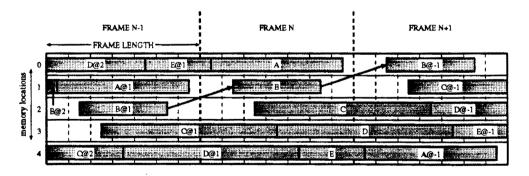

In this equation P(f) stands for the base location (pointer) which is updated every frame. R(s) stands for the relative location of the sample. This location is relative to the base location and is independent of the frame. M is the size of the memory. The pointer mechanism solves the problem that samples clash with their own delayed versions, because in every frame the samples will be stored in different absolute locations. In Figure 2.7 the result of relative location assignment for the application of Figure 2.3 can be seen. To illustrate the principle three frames are shown. One can see in Figure 2.7 that because of the changing base pointer the samples rotate through the memory.

Figure 2.7: Result of relative location assignment

An interesting property is that it can be proven that a memory size of at most  $M_{lowb} + 1$  is necessary. To see this, one has to realize that there are two equivalent ways to look at the problem. Assuming that M memory locations are available.

Select one frame (e.g frame 0) and discuss the location that is assigned to every sample. • Select on location (e.g location 0) and look over M frames to discuss the frame at which every sample is stored.

The role of time and place in the two cases is interchanged. These two points of view contain the same information because the base location is updated (decremented) every frame. When it is determined in which frame a sample is assigned to location zero than the location of that same sample in frame zero can be calculated. To demonstrate this the place of the samples in the memory during several frames is shown in Figure 2.8

Figure 2.8: Result of relative location assignment for several frames

From Figure 2.8 it can be concluded that the two viewpoints are indeed identical. So it is enough to concentrate on location zero and schedule the samples in a efficient way in this location. This can be done by using the first fit algorithm. The first fit technique tries to place the samples as close as possible together in memory location zero. So the minimum amount of frames (memory locations) is needed to store the samples. To come up with a placement with the variables as close together as possible the algorithm starts with the sample with the earliest write timepoint (sample A) followed by the sample with a write timepoint the closest to the read timepoint of sample A in this case sample B and so on until all samples are placed. More information about relative location assignment can be found in [1]. The advantage of relative location assignment is that the memory cost will be low, as the memory needed is at most  $M_{lowb} + 1$ . Also the address sequences that have to be generated during one frame are never longer than the number of variables as is shown in Table 2.5. The address sequences during other frames can easily be derived from these sequences, because they are just shifted one or more places.

| Time<br>clock cycle | Write<br>location | Read<br>location |

|---------------------|-------------------|------------------|

| 0                   | 0                 | 0                |

| 1                   | 1                 | X                |

| 2                   | 2                 | Х                |

| 3                   | 3                 | 3                |

| 4                   | 4                 | 4                |

| 5                   | X                 | 1                |

| 6                   | X                 | 0                |

Table 2.5: Addressing sequences relative location assignment for frame 0

On the other hand it is possible that the address sequence is so complex and irregular that it leads to expensive address generators. Also, extra cost (in comparison to absolute and counter addressing) will be introduced by the modulo hardware. Due to this, the overall cost of the IPB with relative location assignment can be higher than when using counter or absolute location assignment.

The kind of architecture which is used for address generation can also influence the size of the address generators. Therefore the target architectures of MATCHBOX will be discussed.

## 2.4 Target architectures

To generate the different address sequences MATCHBOX has certain target architectures at its disposal. These architectures are:

- counter

- address table

- delta table

- run-length delta table

Each of these architectures has its own way of storing the information which is necessary to generate the address sequence. Only the counter architecture has no storage, it can only generate consecutive addresses like 0,1,2,3,4,5 etc. The address table architecture has all the actual addresses stored in its storage unit. This storage unit is addressed with a counter. The Delta table architecture has only the differences between the different addresses stored in its storage unit. The actual addresses are calculated from the previous address and the delta. In the run length delta architecture the storage unit is used to store the number of the same consecutive deltas (the run length) and the size of the delta. The actual addresses are again calculated from the previous addresses and the deltas. In the following sections the different architectures will be discussed in more detail.

#### 2.4.1 The counter architecture

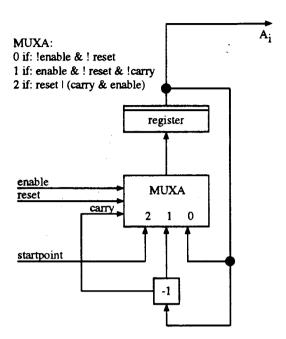

The counter architecture can only be used when the samples are placed in the memory in such a way that they can be addressed with a counter. So when the goal is to use a counter architecture as an address generator, it should be taken into account during the assigning of locations to the different samples. It is always possible to place the samples in such a way in the memory that the write address generator can be realized by a counter. The counter architecture is not complex and therefore very cheap and can be seen in Figure 2.9

Figure 2.9: counter architecture

The architecture shown here is a down counter, it counts like:

$$M-1$$

,  $M-2$ , ....,  $0$ ,  $M-1$ ,  $M-2$ ...

The architecture consists of a decrementor, a block with switch logic and a register. The quantity start point, which is equal to the memory size minus one, is known at compile time and can thus be stored locally. So the only control signals which have to be generated by the controller, are reset and enable. The down counter is preset every time address zero is generated. This can be easily implemented using the carry flag of the decrementor. The enable signal is used to obtain the next address. If the enable signal is low the register will hold.

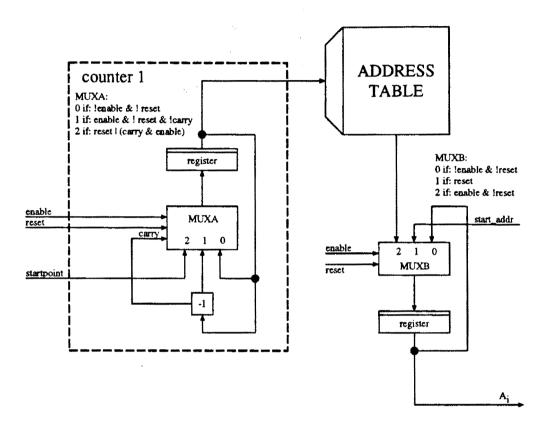

#### 2.4.2 The address table architecture

When the samples are placed in the memory and the address sequences show no regularity at the word level, than MATCHBOX will choose for an address look up table. This method also uses a counter, but the output of this counter is now used as the entry of a table in which the addresses are stored. The hardware is shown in Figure 2.10. The table can be implemented with a ROM but when the addresses show some modulo two regularity, at the bit level, it may be cheaper to replace the ROM with a PLA. Because it than possible that the PLA can be reduced at lot. The counter is the same as used with counter addressing. The output of the table is latched in a register. The hardwired signal start point determines the address of the first table entry. This architecture can only be used for absolute location assignment because for relative location assignment the actual addresses

will be different every frame. For small examples the address table may be a cheap solution but when the problems become larger the address look up table can become large and expensive. In that case the other architectures may offer a cheaper solution.

Figure 2.10: Address table architecture

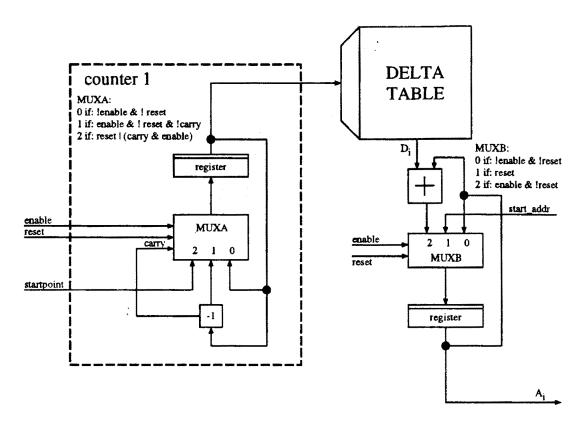

#### 2.4.3 The delta table architecture

Another way to generate addresses is to store only the differences between two subsequent addresses. The advantage of this is that the word width of the largest delta will be smaller than the word width of the largest address. So the storage unit requires a smaller word with. The number of entries in the PLA will be one less than in an address table. On the other hand the hardware that is needed to calculate the addresses will introduce extra costs.

The architecture in case no modulo hardware is necessary (absolute location assignment) is shown in Figure 2.11.

Figure 2.11: Delta table address generator without modulo hardware

An adder is needed to add the difference to the previous address. This result is stored in a register. The enable signal is used to step to the next address. A reset is given at least once to synchronize the read and write address generator. The delta table architecture can also be used to generate the addresses which result from relative location assignment. The architecture has to be modified slightly for it. The differences (D<sub>i</sub>) between the subsequent addresses can be calculated as follows:

$$D_i = (loc(s_i, f) - loc(s_{i-1}), f) mod M$$

(2.5)

In this equation f is the frame number,  $s_i$  is a sample that has to written or read at timepoint i,  $s_{i-1}$  is a sample that has to be written or read on timepoint i-1. loc is a function which assigns a location to a sample in a particular frame. So  $loc(s_i, f)$  and  $loc(s_{i-1}, f)$  are two consecutive addresses in time. The value M equals the memory size, this modulo memory size operation is needed to exclude negative deltas.

By using Equation 2.3 it follows

$$D_{i} = ((P(f) + R(v_{i})) mod M - (P(f) + R(v_{i-1})) mod M) mod M$$

(2.6)

$$D_{i} = (R(v_{i}) - R(v_{i-1})) mod M$$

(2.7)

In Equation 2.7 can be seen that because of the pointer mechanism  $D_i$  is independent of the frame number. From equation 2.7 it also follows that modulo hardware is needed to calculate the differences. So to calculate an address from a delta and a previous address it will also be necessary to use a modulo operation. This modulo architecture can be seen in fig 2.12. The cost of this modulo hardware is an extra cost which can be saved by using absolute location assignment. It depends on the problem what turns out to be cheaper, the modulo hardware or the frame expansion.

Figure 2.12: Modulo hardware for relative location assignment

The implementation of the pointer mechanism can be done in two ways. The first is to implement the last delta one smaller than it actually should be. In this case it not allowed to give more than one reset. The reset is only used to synchronize the read and write address generator. The other way is to change the start address every frame. In this case every frame a reset should be given. Changing the start address every frame will be expensive in hardware, but implementing a smaller last delta can lead to synchronisation problems between read and write address generator.

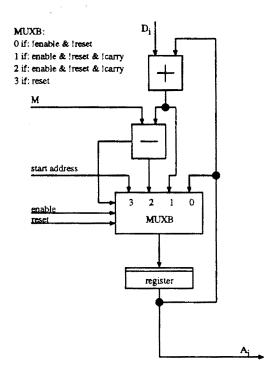

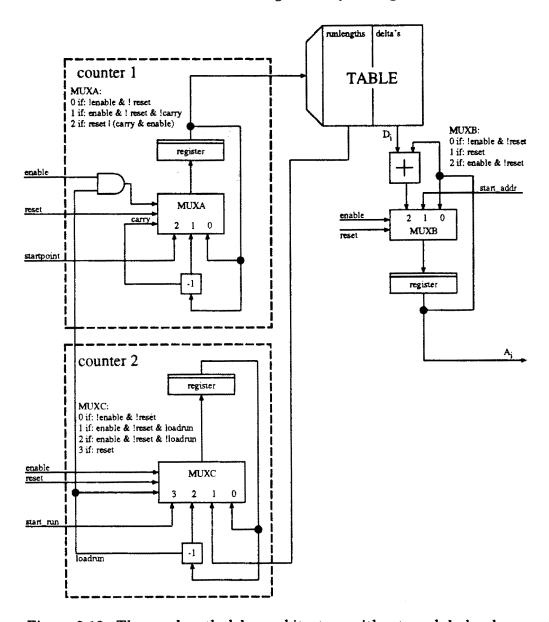

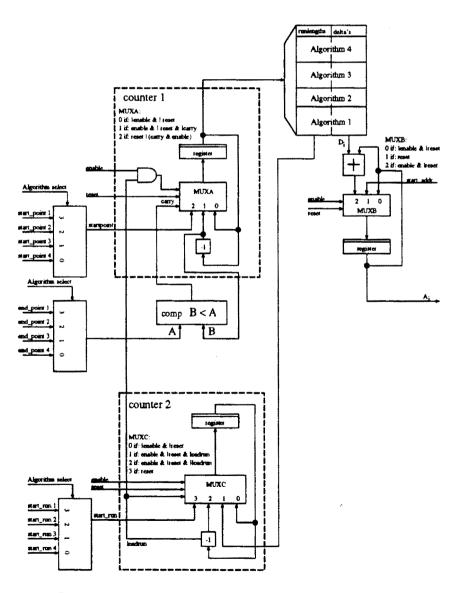

### 2.4.4 The run length delta table architecture

When the delta sequence contains a long series of constant delta's the possibility exists to store the runlength and the delta. This can be achieved with the architecture shown in Figure 2.13. For this architecture holds the same as for the

delta table address generator. It is shown for absolute location assignment but it can also be used for relative location assignment by adding the modulo hardware.

Figure 2.13: The run length delta architecture without modulo hardware

This architecture needs some explanation because its operation is not as obvious as it seems. Counter two counts down the run length for every difference. When the carry out of this counter becomes active counter one is decremented and the next run length is loaded into counter two. Start\_run is a hard wired signal which determines the first run length. This signal is necessary because the first run length from the table is loaded into counter two only after the first difference has been counted down. So the first run length in the table belongs to the second difference. This means that run length and difference are shifted one place in the table. The carry from counter two is generated with a delay of one

runlength. That is why all the run lengths in the table are one smaller than their actual value. Further should be mentioned that this architecture has a very large overhead of hardware. So will this run length delta architecture be the smallest and thus the cheapest solution the storage unit must be very small in comparison to the storage units in the other architectures.

# Chapter 3

# Regular placement

Looking at the methods MATCHBOX uses for location assignment, one can see that the used techniques aim at minimizing either the memory cost or the addressing cost. The counter technique which tries to minimize the addressing cost, sometimes turns out to be very expensive in memory cost. The other techniques, absolute location assignment and relative location assignment, which aim at small memory costs have unpredictable address generator costs. The total costs of an inter processor buffer can be separated into three parts, Equation 3.1.

$$Read \ Address \ generator \ cost \\ Write \ Address \ generator \ cost \\ + \ Memory \ cost \\ \hline Total \ cost$$

(3.1)

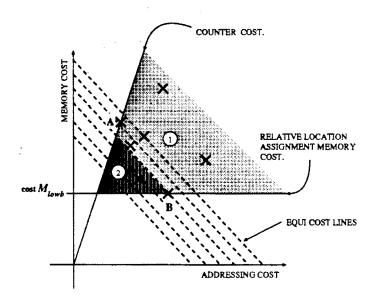

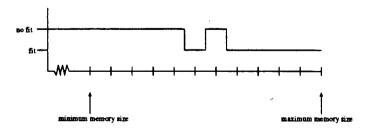

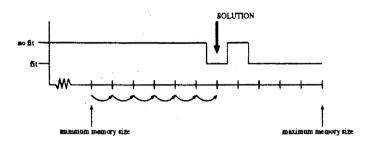

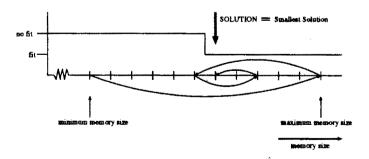

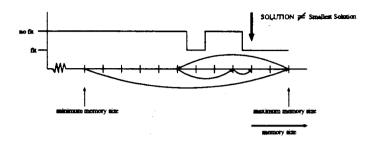

Predicting the total costs of the inter processor buffers resulting from the different techniques appeared to be very hard. There are only a few things which are predictable and which are not problem dependent. For relative location assignment it is known that the memory cost will be close to the minimum ( $M_{lowb}$ or  $M_{lowb} + 1$ ). On the other hand the costs of the address generators can not be estimated accurately a priori. This addressing cost is dependent on the application for which the IPB is designed, but is also strongly influenced by the unpredictable effect of the minimization of the storage unit. It is known that the cost of the address generators will be larger than the cost of counter architecture. By using the counter technique there is chosen for minimal cost for one address generator (the write address generator). The memory size which is necessary for realizing counter addressing is dependent of the application for which the IPB is designed. But even when the application is known it is not possible to make a good estimation of the memory size that is needed to realize counter addressing. Although only a few things are known about the design space it is still possible to draw an address generator- memory- cost graph. This graph contains the cost of the write address generator, on the X-axis, and the cost of the memory size. on the Y-axis. The reason why only one address generator is taken into account for the design space cost graph is that when one address generator is defined, the other address generator will be the logical consequence of the defined address generator and the application. So when there is something to gain in total cost it has to be done by decreasing the cost one of the two address generators while keeping the memory as small as possible. Minimizing both address generators is impossible. The graph shown in Figure 3.1 is a representation of the costs of one address generator and the required memory cost for one application.

Figure 3.1: Design cost space

The line which represents the cost of a counter in Figure 3.1 is slanted, this is because a larger memory needs a larger counter to address it. By increasing the size of the counter the area cost will also increase. The "counter addressing line" also represents the absolute minimum costs for which it is possible to realize an address generator. So on the left hand side of this line there exist no address generator. The minimum memory line is constant in the entire solution space. This minimum is application dependent, and can be calculated when the lifetimes of the samples are known. Below this line there exist no memory size in which it is possible to store all the samples. The marks represent the cost of the address generator and the memory as a result of using different kind of techniques for memory allocation. Mark A represents the cost of a counter solution and mark B represents the cost of a relative solution. The memory cost of relative addressing is placed on the cost of  $M_{lowb}$  but in reality the memory needed with relative location assignment can be one more than  $M_{lowb}$  so the cost can be a little higher. Absolute location assignment with graph colouring can be represented by one of the other marks somewhere in the two grey areas. The question whether absolute location assignment is cheaper than the cheapest of one of the two extremes (in area two in Figure 3.1) or more expensive (in area one in Figure 3.1) is impossible to answer a priori because this is dependent on many factors, like the heuristic of the graph colouring algorithm, the application for which the IPB has to be

designed and the unpredictable effect of the minimisation of the storage unit of the address generator. In developing a technique for location assignment the goal was to find another technique which results in a inter processor buffer with low costs. So the cost should be somewhere in area two of Figure 3.1. On the other hand the flexibility should be kept in mind. Knowing all this it is tried to optimize the address generator size within such limits that the memory would not grow too much. Minimizing the address generator costs is done by assigning memory locations to samples in such a way that the addressing sequence will become regular. This is called regular placement.

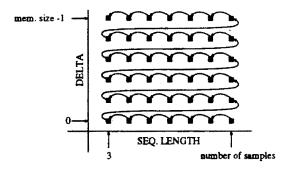

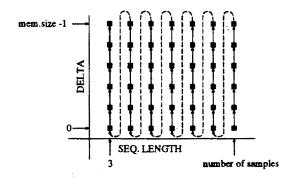

The architecture which is best suited to generate these regular sequences is the run length delta architecture. For the address table and the delta table architecture, the storage pattern of the samples will not have a predictable influence on the size of the address generator. The number of entries in the storage unit, in which the addresses or the deltas are stored, stays the same, so a big difference was not expected. In practice it appeared that the size of these address generators did differ a lot between one storage pattern and the other. This was due to the fact that with one storage pattern the storage unit can be reduced more than with another, but the amount of reduction is unpredictable. On the other hand the number of entries in the storage unit of the run length delta architecture will decrease when the sequence becomes more regular. So the address generator may become smaller when the address sequence becomes more regular. But the costs of an inter processor buffer consist of more than the cost of one address generator. The cost of the other address generator is unpredictable and the cost of the memory is an uncertain factor too. The question now is, will this method result in a inter processor buffer which is smaller than the other techniques and is it possible to turn the resulting IPB into a flexible one. Before answering these questions let us first look into the method of regular placement.

# 3.1 The solution space of regular placement

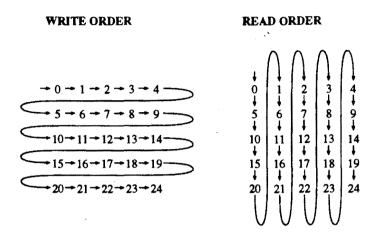

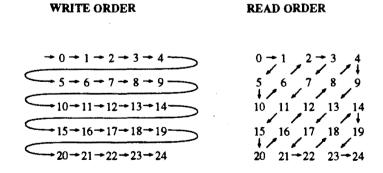

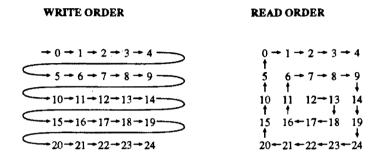

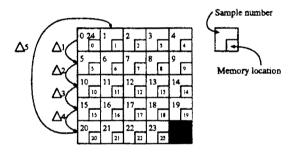

The definition of a regular addressing sequence is an important issue. Because regularity can have many different forms. In the previous section it is already mentioned that the size of the run length delta architecture will decrease when the address schedule is more regular. That is why this architecture is used to determine a measure for regularity. There are numerous solutions which can have the label regular solution. Three examples of a regular solution for 25 samples can be seen in Figure 3.2.

| SOLUTION 1<br>#mem=23 (rel) |                                              |               | TION 2<br>28 (rel.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                   | ~                  | = Regular delta seque |

|-----------------------------|----------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------------------|-----------------------|

| DDRESS                      | DELTA                                        | ADDRESS       | DELTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADDRESS. | DELTA             | <i>'1111111111</i> | = Start addres        |

| 111101111                   | 345]                                         | 0             | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29       | S COLUMN TO LINES |                    |                       |

| 3                           | 200000                                       | 5             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29       | 29                |                    |                       |

| 6                           | 3                                            | 10            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25       |                   |                    |                       |

| 9                           | 3.3                                          | 15            | 3 3 444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21       | 29                |                    |                       |

| 12                          | 3 (2)                                        | 20            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17       | 29                |                    |                       |

| 15                          | 3                                            | 25            | <b>38.5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13       | 29                |                    |                       |

|                             | 3 3 6 111                                    |               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 29                |                    |                       |

| 18                          | 3288                                         | <u> </u>      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9        | 299               |                    |                       |

| 21                          | 120                                          | 7             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 29                |                    |                       |

| _1                          | - 3                                          | 12            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1        | 29                |                    |                       |

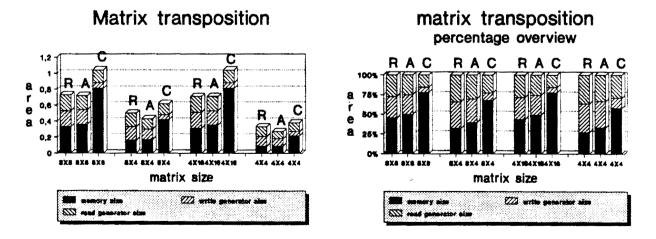

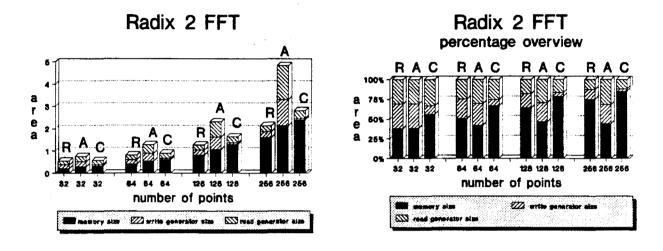

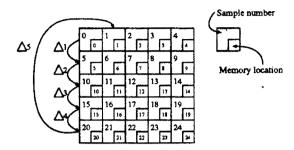

| _4                          | 3                                            | 17            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30       | 29                |                    |                       |