| R A | A C | т     | -0 |

|-----|-----|-------|----|

| М   |     | . I F | -ĸ |

|     |     |       |    |

A miniaturized 5.2 Watt battery charger

Schetters, C.J.A.

Award date: 1998

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

#### Faculteit Elektrotechniek

Vakgroep Elektromechanica en Vermogenselektronica

Afstudeerverslag

A Miniaturized 5.2 Watt Battery Charger.

EMV 98-09

C.J.A. Schetters

Hoogleraar:

Prof. ir. J. Rozenboom

Mentor(en):

Ir. P.J.M. Smidt

Prof. ir. J. Rozenboom

Eindhoven, 15 oktober 1998.

De Faculteit der Elektrotechniek van de Technische Universiteit Eindhoven aanvaardt geen verantwoordelijkheid voor de inhoud van stage- en afstudeerverslagen.

#### **Abstract**

In the present report a complete theoretical analysis and practical design of a miniaturized 20cc, 5.2 Watt battery charger will be given. A standard flyback topology is chosen, theoretically analyzed and implemented. The need to reduce the number of components resulted in an integrated flyback solution, the VIPer20 of SGS-Thomson. A novel frequency reduction technique is introduced to prevent the battery charger to operate in burst mode at low output loads and high input voltages, followed by a practical implementation. The electrical losses in the converter are identified, calculated and successfully verified by measurement. The feedback loop is theoretically analyzed using the state space averaging method, which results in a dynamic small signal (AC) and steady state (DC) model of the converter operating in current and voltage regulation mode. From these models the Bode plots are calculated and successfully verified by a closed loop gain measurement. The electrical volume of the prototype battery charger is 25cc due to the chosen transformer. When using flying leads 20cc is possible.

## **Table of Contents**

| 1. INTRODUCTION                                                                                                                                                         |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1 FORMULATION OF THE PROBLEM  1.2 DESCRIPTION OF ASSIGNMENT  1.3 REPORT DESCRIPTION                                                                                   |                |

| 2. TOPOLOGY AND CONVERTER CHOICE                                                                                                                                        |                |

| 2.1 TOPOLOGY CHOICE                                                                                                                                                     |                |

| 3. DESIGN OF THE CONVERTER                                                                                                                                              | 13             |

| 3.1 DESIGN OF THE INPUT CIRCUIT 3.2 TRANSFORMER DESIGN 3.3 DESIGN OF THE OUTPUT FILTER 3.4 DESIGN OF THE VOLTAGE REGULATION CIRCUITRY                                   | 14<br>17<br>19 |

| 3.5 DESIGN OF THE CURRENT REGULATION CIRCUITRY 3.6 DESIGN OF THE FREQUENCY CONTROL CIRCUITRY 3.7 DESIGN OF THE BIAS VOLTAGE REGULATION 3.8 PRINTED CIRCUIT BOARD DESIGN | 22             |

| 4. CONTROL LOOP CALCULATIONS AND MEASUREMENTS                                                                                                                           |                |

| 4.1 STABILITY MARGINS  4.2 THE STATE SPACE AVERAGING METHOD APPLIED TO A FLYBACK CONVERT OUTPUT FILTER                                                                  | ER WITH CLC30  |

| 4.3 SIMULATIONS  4.3.1 Simulations of the Voltage Regulation Feedback Loop                                                                                              |                |

| 5. ELECTRICAL LOSSES IN THE CONVERTER                                                                                                                                   |                |

| 5.1 LOSSES IN THE TRANSFORMER  5.1.1 DC Losses  5.1.2 Skin Effect Losses  5.1.3 Proximity Losses  5.1.4 Core Losses                                                     | 43<br>43<br>44 |

| Losses in the VIPer20  Losses in the Input Circuit  Losses in the Output Circuit  Losses in the Current Sense Resistor  Losses in the Additional Electronics            | 50<br>50<br>51 |

| Total Losses in the Converter<br>Efficiency Measurements                                                                                                                | 51             |

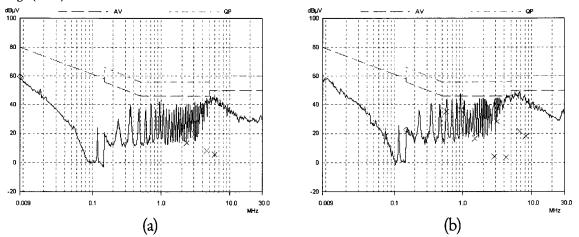

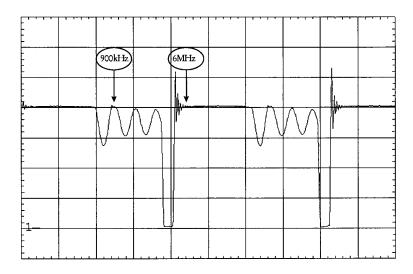

| 6. ELECTRO MAGNETIC INTERFERENCE                                                                                                                                        | 53             |

| 6.1 Measurement Setup                                                                                                                                                   |                |

|    | 6.3 Measurements                                          | 54 |

|----|-----------------------------------------------------------|----|

| 7. | GENERAL MEASUREMENTS                                      | 57 |

|    | 7.1 LOAD CURVE                                            | 57 |

|    | 7.2 SWITCHING FREQUENCY                                   | 58 |

|    | 7.3 STANDBY POWER                                         | 58 |

|    | 7.4 LOAD REGULATION                                       | 58 |

|    | 7.5 TEMPERATURE DEPENDENT MEASUREMENTS                    |    |

|    | 7.6 OUTPUT RIPPLE AND NOISE                               | 60 |

|    | 7.7 SHORT CIRCUIT OUTPUT CURRENT                          | 60 |

|    | 7.8 ELECTRICAL VOLUME                                     |    |

| 8. | CONCLUSIONS AND RECOMMENDATIONS                           | 61 |

| 9. | BIBLIOGRAPHY                                              | 63 |

| A  | PPENDIX A FOURIER TRANSFORM OF A TRIANGULAR SHAPED SIGNAL | 65 |

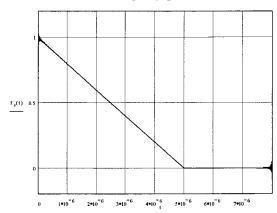

| A  | PPENDIX B CIRCUIT DIAGRAM                                 | 67 |

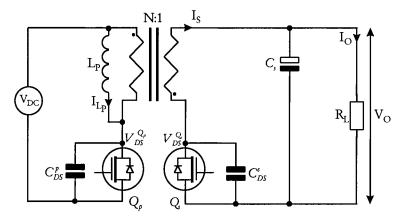

| A  | PPENDIX C BIDIRECTIONAL FLYBACK CONVERTER                 | 68 |

|    | 1. WORKING OF OPERATION                                   | 68 |

|    | A CONTENT OF CHAPTER                                      |    |

#### 1. Introduction

#### 1.1 Formulation of the Problem

To obtain more freedom in the mechanical construction and casing design of power supplies used for charging battery packs of cellular phones, one needs to reduce the electrical volume by using smaller and/or less components. Here a contradiction occurs, since the customer is nowadays interested in features like fast charging, which more or less implies that high charging currents should be used, and low standby losses. This does not automatically result in smaller and/or less components. By decreasing the casing dimensions, we also decrease the overall convection area. As a result the internal losses of the power supply should be kept as low as possible in order to maintain the temperature of the power supply at an acceptable level. The price of the power supply should also be considered from a cost-saving point of view. The bill of material should be kept as low as possible.

#### 1.2 Description of Assignment

The assignment of my graduation project was to develop a small battery charger, which can be used to charge NiCd, NiMH and Li-Ion batteries. The output specifications are a regulated continuous output current of  $800 \, \text{mA} \pm 10\%$  at an output voltage of  $6.5 \, \text{V} \pm 10\%$  for NiCd and NiMH and  $4.1 \, \text{V} \pm 1\%$  for Li-Ion. While operating in current regulation an output voltage down to  $3 \, \text{V}$  must be guaranteed. Below  $3 \, \text{V}$  current foldback should occur. The power supply is not allowed to operate in burst mode at the minimum output current of  $50 \, \text{mA}$ . The input voltage is universal mains, which is an input voltage of  $85 \, \text{V}$  up to  $265 \, \text{V}$ . The power supply should meet the EMI and safety regulations. These specifications must be achieved in a volume of  $\pm 20 \, \text{cc}$ . For a better understanding of the battery charger output voltage and current, we will give a full explanation below.

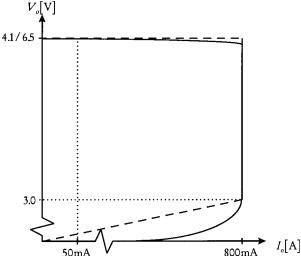

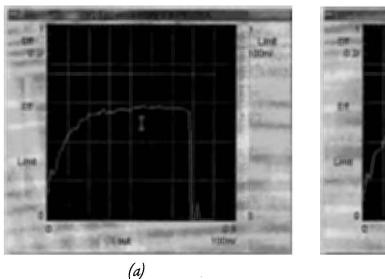

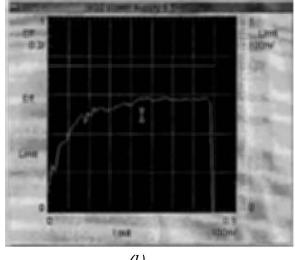

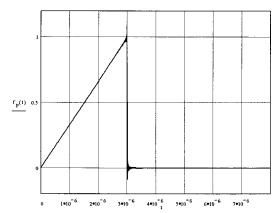

The battery charger output voltage and current are given in Fig. (1.1). This graph depicts the complete charge cycle of an entirely discharged battery pack. The ideal situation is represented by the dashed lines, the drawn curve is normally measured.

Fig. (1.1) Ideal and normally measured output voltage and current of the battery charger

When the charger is connected to the cellular phone it will first operate in voltage regulation mode. A series resistance in the cellular phone with the impedance of the battery pack will limit the precharge current to 50mA. During pre-charge the voltage of the battery pack will rise up till 3V and at that point the charging control of the cellular phone is activated. The series resistance is short circuited by a MOSFet internally in the cellular phone, causing the battery charger to operate in

current regulation mode. In this stage the battery pack is charged at the maximum current of 800mA. We are now at the vertical line in the graph. The battery voltage will increase to the nominal battery pack voltage. At this point we are in the "knee" of the  $V_o - I_o$  curve, and the charger will change from current to voltage regulation mode. The charge control circuit in the cellular phone will identify a completely charged battery pack at the horizontal part of the  $V_o - I_o$  curve and will shut down.

#### 1.3 Report Description

A first step in the development of the power supply is choosing the right topology. Since lots of combinations are possible with the topologies which are nowadays available, we reduced the possibilities to the ones which were actual at EPM in the period I started my graduation project. After a short comparison, given in Chapter 2, between different topologies, we have chosen one topology to be studied. In Chapter 3 a complete theoretical analysis and design will be given. A power supply is, like a lot of electronics, a controlled system and it uses a feedback loop to increase system performance. The improper closing of such a loop may result in overshoot, instabilities or even worse system performance as without a closed feedback loop. In Chapter 4 a equivalent Steady-State (DC) model and a Dynamic (AC) Small Signal Model of the converter including its current and voltage feedback system will be derived. By using these models we can predict the behavior of the converter and this will be verified by measurements. Minimizing the volume was one of the main targets of this project. This implies less convection area and therefore the electrical losses must be kept below an acceptable level. A detailed analyses and calculation of the electrical losses is given in Chapter 5 followed by a verification by measuring the efficiency of the converter. Meeting the EMI level can be a problem due to the switching behavior of the converter. Chapter 6 is devoted to the EMI behavior of the converter, EMI measurement setup and EMI levels. Since the measurements already done do not cover all the specifications of the battery charger, we describe several general measurements in Chapter 7. A summary of the conclusions in this report and recommendations are given in Chapter 8, followed by some additional derivations and explanations in the Appendices

In this Chapter we have set out the object of this project. In the next Chapter we will decide which topology is the best choice for this application.

### 2. Topology and Converter Choice

#### 2.1 Topology Choice

The first and rather important decision in this project is choosing the right topology, which roughly fixes the electrical structure and the setup of the power supply. In order to choose the best converter topology for this application, we have made a comparison of several topologies which were actual at EPM in the period I started my graduation project. See Table (2.1) for a short overview.

|                              | Resonant LLC converter                                                                               | Resonant LLC converter<br>with input voltage pre-<br>conditioner                                  | Conventional fly-back converter                                                               | Bi-directional fly-back<br>converter                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| transformer                  | E16                                                                                                  | E13                                                                                               | E13                                                                                           | E13                                                                                                       |

| input filter                 | CLC filter                                                                                           | CLC-filter                                                                                        | CLC-filter                                                                                    | CLC filter                                                                                                |

| output filter                | low pass filter                                                                                      | low pass filter                                                                                   | low pass filter                                                                               | low pass filter                                                                                           |

| switches                     | primary two MOS-Fets,<br>secondary two diodes                                                        | primary two MOS-Fets, secondary two diodes                                                        | primary a MOS-Fet,<br>secondary a diode                                                       | primary and secondary a<br>MOS-Fet                                                                        |

| switching frequency          | 75-105kHz                                                                                            | 35-45kHz                                                                                          | 100kHz                                                                                        | 100kHz                                                                                                    |

| primary peak current         | $\frac{\pi P_{o} / \gamma_{\eta}}{V_{DC_{\min}} \cos(\mathcal{G}_{f_{\min}})} = 338 \text{mA}$       | $\frac{\pi P_o \frac{1}{\eta}}{V_{DC_{\min}} \cos(\theta_{f_{\min}})} = 338 \text{mA}$            | $\sqrt{\frac{2P_o}{\eta L_p f_s}} = 430 \text{mA}$                                            | $\sqrt{\frac{2P_o}{\eta L_P f_s}} = 430 \mathrm{mA}$                                                      |

| primary maximum<br>voltage   | V <sub>DC</sub>                                                                                      | V <sub>DC</sub>                                                                                   | V <sub>DC</sub> +NV <sub>o</sub>                                                              | V <sub>DC</sub> +Nv <sub>o</sub>                                                                          |

| complexity control<br>system | half bridge driver,<br>VCO, voltage reference                                                        | half bridge driver,<br>VCO, voltage reference                                                     | PWM, voltage<br>reference                                                                     | two control loops,<br>consisting of two<br>accurate voltage sensing<br>circuits, primary a PWM<br>circuit |

| ЕМІ                          | ++                                                                                                   | ++                                                                                                | 0                                                                                             | +                                                                                                         |

| efficiency                   | 65-70%                                                                                               | 70-75%                                                                                            | 60-65%                                                                                        | 65-70%                                                                                                    |

| volume                       | •                                                                                                    | -                                                                                                 | 0                                                                                             | +                                                                                                         |

| result                       | Universal input<br>increases the<br>transformer size and<br>therefore is this<br>topology not useful | Input voltage control<br>increases the total size<br>and therefore is this<br>topology not useful | Although not original,<br>due to the small<br>amount of components<br>is this topology useful | control circuits are not<br>yet integrated and<br>therefore too<br>complicated to build<br>discrete       |

Table (2.1) A comparison between different topologies

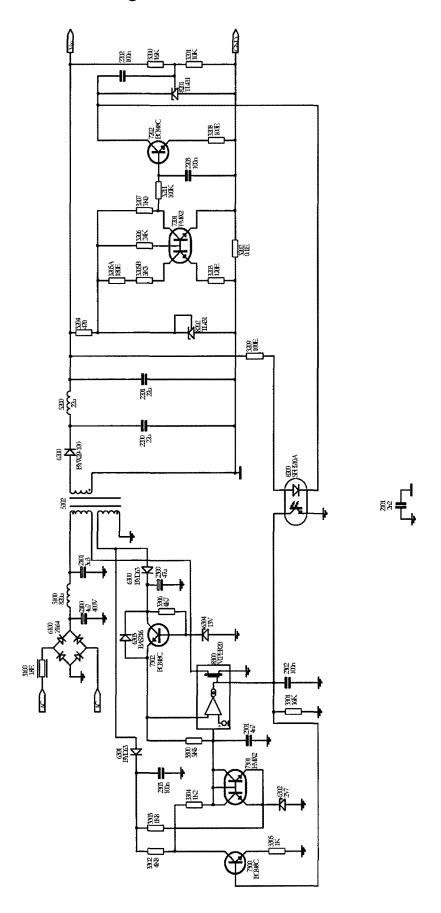

The final choice is more or less based on the number and the size of the components, especially the transformer, necessary to build the converter. Table (2.1) shows that the conventional fly-back converter is the best choice when considering size and the number of components. When considering EMI, a LLC based converter is more applicable, but the universal mains aim increases the size of the transformer. This can be overcome by using an input voltage pre-conditioner and therefore by increasing the number of components. The bi-directional flyback converter is interesting because of the low switching losses. A problem using this topology is the complexity of the primary and secondary control circuits, which are not yet integrated at the present moment. Because of the fact that the topology as such is rather interesting for miniaturisation aims, we have included a small description of a possible implementation of a bi-directional flyback converter in Appendix D. Every topology has it's own merits and demerits, but since miniaturisation is the most important aim in this project we therefore have chosen for the conventional flyback converter. A next step in the decrease of the number of components is integration and therefore we will now investigate several integrated flyback solutions.

#### 2.2 VIPer20 Integrated Flyback Solution

At the beginning of this project we have made a short inventory of the integrated control circuits which include a high voltage MOSFet and are easy available. We came up with the next three integrated circuits,

- TEA1401T from Philips,

- TOP221 from Power Integrations,

- VIPer20 from SGS-Thomson.

In order to make a choice between one of the listed i.c.'s, we made a comparison using the following considerations,

- flexibility of the integrated circuit in, for example, adjustable switching frequency, control loop gain and phase correction,

- voltage or current mode control,

- package layout,

- price,

- knowledge of the integrated circuit already at EPM.

See Table (2.2) for a summary of the results.

|                                 | TEA 1401T | TOP221      | VIPer20    |

|---------------------------------|-----------|-------------|------------|

| flexibility                     | ++        | -           | ++         |

| voltage/current mode<br>control | current   | voltage     | current    |

| package layout                  | SO20      | DIL-8/TO220 | PowerSO-10 |

| price                           | Fl 2.10   | Fl 1.20     | Fl1.20     |

| knowledge at EPM                | +         | +           | -          |

Table (2.2) Results of the comparison of the three integrated flyback solutions

The VIPer20 is chosen since it is flexible, has a current mode control strategy, the package layout can easily use the printed circuit board as a heat spreader, it is not as expensive as the TEA1401T and EPM's knowledge concerning the VIPer20 can be extended, since it has never been used in one of EPM's power supplies.

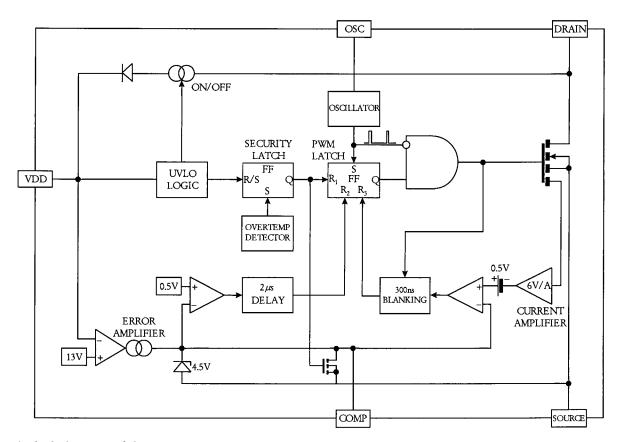

The Viper20 is a combination of a current mode controller, protection circuit, start-up power supply and a high voltage MOSFet in one integrated circuit, as shown in Fig. (2.1). This integrated combination is ideal in our case, since we are aiming at a minimal electrical volume.

Fig. (2.1) Block diagram of the VIPer20

First we will shortly explain the operation of the VIPer20. The MOSFet is switched off during startup and at this time the high voltage current source is charging a capacitor which is connected to the  $V_{DD}$  pin. As a consequence the voltage at the  $V_{DD}$  will increase until the voltage reaches 11V . At this point, the internal high voltage current source is switched off and the control logic is activated causing the converter to start switching. The level of  $V_{DD}$  is decisive for the operation mode of the converter. If  $V_{DD} \leq 8 \, \text{V} \vee V_{DD} \geq 13 \, \text{V}$  then the converter is shut down. If  $8 \, \text{V} < V_{DD} \leq 12.5 \, \text{V}$  then the converter is operating in secondary sensing mode and uses the information of the comp pin. If  $12.5 \, \text{V} < V_{DD} < 13 \, \text{V}$  then the converter is operating in primary sensing mode and uses an internal voltage reference to control the  $V_{DD}$  voltage, which is directly coupled to the output voltage.

The most important features of the VIPer20 are listed below,

- I. adjustable switching frequency up to 200kHz,

- II. current mode control,

- III. under voltage lock-out with hysteresis,

- IV. integrated start-up supply,

- V. over temperature protection,

- VI. PowerSO-10 casing.

- Ad I. The switching frequency will be determined externally by a capacitor and resistor combination and because of that it is possible to adjust the switching frequency, which will be shown in the present report. The fact that the switching frequency is not internally determined creates more design possibilities.

- Ad II. The internal controller is a current mode controller, which has the advantage of complete rejection of the 100Hz input ripple at the output. This means that no 100Hz ripple will be

- present in the output and therefore the cut off frequency of the control loop can be beneath 100Hz, which results in an easy to stabilise control system.

- Ad III. The under voltage lockout will be used to create a foldback function at the output. Since the output voltage and the supply voltage are directly coupled, it is possible to switch the converter of whenever the output voltage drops below a stated level.

- Ad IV. The integrated start up supply, which is switched off during normal operation, reduces the losses which are normally produced in the start up resistors.

- Ad V. No external circuit is needed to protect the VIPer20 for over temperature

- Ad VI. The PowerSO-10 casing has the advantage to conduct the heat to the printed circuit board and will therefore be used as a heat spreader. The mechanical layout of the PowerSO-10 casing is depicted in Fig. (2.2).

Fig. (2.2) PowerSO-10 casing of the VIPer20

The VIPer20 is an interesting circuit to make a power supply with, however it does have some serious disadvantages. First of all the heat spreader connected to the PowerSO-10 casing is electrical connected to the drain of the internal MOSFet. Since the drain voltage contains very high (600V) and very steep flanks, is this a disadvantage from an EMI point of view. Another disadvantage is the fact that the VIPer20 can handle up to 20W mono input and 10W universal mains, which is approximately twice the power we need. The area of the internal MOSFet could have been smaller, resulting in a smaller  $C_{DS}$ . This would have been interesting from an efficiency point of view, since the switching losses are proportional to  $\frac{1}{2}C_{DS}V_{DS}^2$ . The last disadvantage, which can be directly concluded from the data-sheets is the minimum on time of the MOSFet, which is  $0.3\mu s$ . This minimum will cause the power supply to operate in burst mode at low output power. A way to overcome this problem will be shown in the present report.

In this chapter we have made two decisions, i.e. the use of a conventional flyback topology and the use of the VIPer20. In the next chapter we will design a flyback converter when using the VIPer20.

### 3. Design of the Flyback Converter

#### 3.1 Design of the Input Circuit

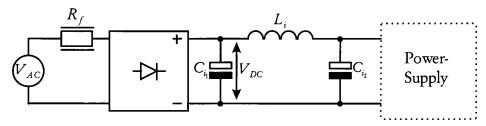

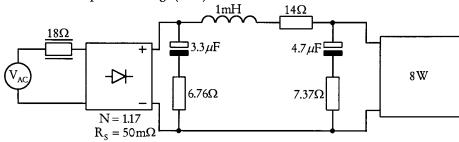

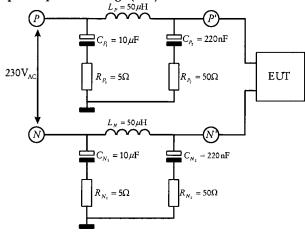

The input circuit used in this power supply is depicted in. Fig. (3.1).

Fig. (3.1) The input filter section.

The input filter has two functions, namely preventing the input voltage to drop below a stated level of 70V, it's energy buffer function, and EMI suppression, it's filter function. For calculating the minimum capacitance, which should be available to guarantee the minimum input voltage level, we invoked the principle of conservation of energy. The minimum amount of energy, which should be stored in the capacitors and the inductor during the on time of the diode bridge, is equal to the energy which is transferred to the output divided by the efficiency of the remaining circuit, minus the energy taken directly from the mains, whenever the diode bridge is conducting, thus

$$E_C = \frac{E_o}{\eta} - E_{mains} .$$

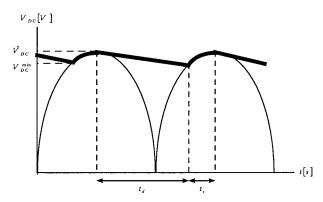

Since the load, and therefore the output power is constant, we can calculate the charging and discharging times of the capacitors by applying some basic trigonometrics to the graph depicted in Fig. (3.2).

Fig. (3.2) Rectified voltage after the diode bridge.

Solving for the charging and discharging times respectively, we obtain

$$t_{c} = \frac{\cos^{-1}\left(\frac{V_{DC}^{\min}}{\hat{V}_{DC}}\right)}{4\pi f_{L}} = \frac{\cos^{-1}\left(\frac{70\text{V}}{\sqrt{2} \cdot 85\text{V}}\right)}{4 \cdot \pi \cdot 50\text{Hz}} = 1.51\text{ms},$$

$$t_{d} = \frac{1}{2f_{L}} - t_{c} = 8.49\text{ms}.$$

As a consequence, we have for the stored energy in the capacitor

$$E_C = \frac{2t_d f_L P_{out}}{\eta 2 f_I} = \frac{2 \cdot 8.49 \,\text{ms} \cdot 50 \,\text{Hz} \cdot 5.2 \,\text{W}}{0.75 \cdot 2 \cdot 50 \,\text{Hz}} = 58.86 \,\text{mJ}.$$

This energy, if we neglect the energy which is stored in the inductor, is equal to

$$E_C = \frac{1}{2}(C_{i1} + C_{i2})V^2 = \frac{1}{2}(C_{i1} + C_{i2})(V_{DC}^2 - V_{DC_{\min}}^2),$$

which results in an input capacitance of

$$C_{i1} + C_{i2} = \frac{2E_C}{V_{DC}^2 - V_{DC_{min}}^2} = \frac{2 \cdot 58.86 \text{mJ}}{\left(\sqrt{2} \cdot 85 \text{V}\right)^2 - 70 \text{V}^2} = 12.33 \,\mu\text{F}.$$

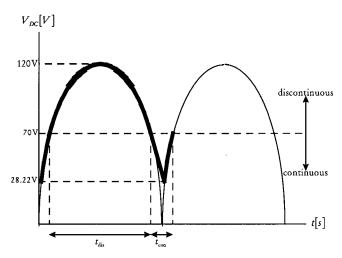

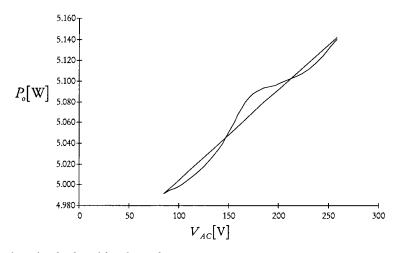

The other function of the input circuit is to suppress the disturbances which are produced by the triangular formed current shapes at switching frequency. One way to attenuate these disturbances, is to create a low pass filter, which is already present in the form of  $C_{i_1}$  and  $L_i$ . Taking the maximum current of the inductor in consideration and choosing components in regular series we find  $C_{i_1} = 4.7\,\mu\text{F}$  and  $L_i = 820\,\mu\text{H}$ , resulting in a cut off frequency of 2564Hz, which is the lowest cut off frequency possible in this situation to have maximum attenuation at the switching frequency. The remaining capacitor,  $C_{i_2}$ , can be calculated and results in  $7.6\,\mu\text{F}$ . This is a rather big capacitor and it is impossible to fit this casing size on our printed circuit board. The maximum input capacitance we can create, considering the printed circuit board space, is equal to  $3.3\,\mu\text{F} + 4.7\,\mu\text{F} = 8\,\mu\text{F}$ , resulting in  $V_{DC} = 28.22\,\text{V}$  at  $V_{AC} = 85\,\text{V}$ . This causes the converter to operate shortly in continuous mode at  $V_{AC} = 85\,\text{V}$ , as shown in Fig. (3.3). The minimum input voltage to guarantee discontinuous mode is in our case  $V_{AC} = 98.69\,\text{V}$  in stead of  $V_{AC} = 85\,\text{V}$ .

Fig. (3.3) The actual rectified input voltage

Resistor  $R_f$  is added to limit the inrush current to approximately 20A and can be calculated using Ohm's law

$$R_f = \frac{\hat{V}_{AC}^{\text{max}}}{I_{\text{in}}^{\text{max}}} = \frac{\sqrt{2} \cdot 265 \text{V}}{20 \text{A}} = 18.74 \Omega.$$

Choosing this resistor in regular series, we find  $R_f = 18\Omega$ .

#### 3.2 Transformer Design

The principle we use for dimensioning the flyback transformer is based on comparing the magnetic energy stored in the air gap of the flyback transformer during the on time of the MOSFet to the energy transferred to the output during the off time of the MOSFet [12]. The magnetic energy stored in the air gap of the primary inductance is equal to

$$E_m = \frac{1}{2} L_p I_p^2.$$

The power, drawn from the output in discontinuous mode, is equal to

$$P_o = E_m f_s \eta = \frac{L_p I_p^2 f_s \eta}{2}.$$

(3.1)

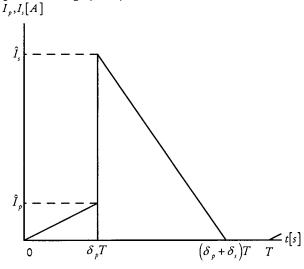

In Eq. (3.1)  $\eta$  represents the efficiency of the transformer and the secondary circuit,  $f_s$  is the switching frequency and  $I_p$  the primary current. The primary peak current is calculated using the

basic inductor equation  $V = L \frac{di}{dt}$ , which reads in our case

$$\hat{I}_{p} = \frac{1}{L_{p}} \int_{0}^{\delta_{p}T} V_{DC} dt = \frac{V_{DC} \delta_{p}T}{L_{p}}.$$

(3.2)

Solving for  $L_p$  by substitution of Eq. (3.2) in Eq. (3.1) results in

$$L_p = \frac{V_{DC}^2 \delta_p^2 \eta}{2P_o f}.$$

(3.3)

The number of primary turns and the ratio between the primary and the secondary number of turns can be calculated invoking Maxwell's second law

$$V_{DC} = \oint E ds = N_P \frac{\mathrm{d}}{\mathrm{d}t} \iint_{A_s} B dA .$$

Since  $A_e$  is constant and B starts at zero, due to using half the B-H curve, this equation reduces to  $V_{DC}\delta_{p}T = N_{p}BA_{e}$ .

Solving for the number of primary windings,  $N_n$ , we obtain

$$N_p = \frac{V_{DC} \delta_p T}{B A_a}.$$

For calculating the minimum number of primary windings we evaluate

$$N_{P_{\min}} = \frac{V_{DC_{\min}} \mathcal{S}_{P_{\max}}}{f_{e} B_{\max} A_{e}}, \tag{3.4}$$

in which  $\delta_{p_{\max}}$  is the start up duty cycle of the VIPer20 and from the data-sheets we have  $\delta_{p_{\max}}=$  0.13 .

From the ratio between the primary and secondary peak currents we have

$$\frac{\hat{I}_p}{\hat{I}_s} = N = \frac{\frac{V_{DC}\delta_p}{L_p}}{\frac{V_o\delta_s}{L_s}} = \frac{V_{DC}\delta_p}{V_o\delta_s N^2},$$

and with  $\delta_p + \delta_s = 1$  at the minimum input voltage, this results in

$$N = \frac{V_{DC}\delta_p}{V_o(1-\delta_p)}.$$

(3.5)

The losses in the VIPer20 are mainly switching losses and not conduction losses, in perticular at high input voltages. The losses in the secondary diode are mainly conduction losses and therefore it is recommendable to choose N as small as possible. Table (3.1) lists several different N values including the primary and secondary peak currents, which are calculated using Eqs. (3.2), (3.3) and (3.5).

| N | $\delta_p$ | $L_p[\mu H]$ | $\hat{I}_p[mA]$ | $\hat{I}_s[mA]$ |

|---|------------|--------------|-----------------|-----------------|

| 4 | 0.271      | 221          | 687             | 2747            |

| 5 | 0.317      | 303          | 586             | 2928            |

| 6 | 0.358      | 386          | 519             | 3116            |

| 7 | 0.393      | 458          | 476             | 3333            |

| 8 | 0.426      | 548          | 435             | 3484            |

Table (3.1) Possible transformer transfer ratios including the resulting  $L_p$ ,  $\hat{I}_p$  and  $\hat{I}_s$

The maximum rated  $I_{ds}$  of the VIPer20 is 500mA resulting in N=7.

From Eq. (3.5) we have  $\delta_p = 0.39$  and  $\delta_s = 0.61$ . Now we are able to calculate the primary inductance,  $L_p$ , by using Eq. (3.3)

$$L_p = \frac{(70\text{V})^2 \cdot 0.39^2 \cdot 0.8}{2 \cdot 5.2 \text{W} \cdot 125 \cdot 10^3 \text{Hz}} = 458.64 \,\mu\text{H}.$$

The design of the transformer is based on a E13/6/6 transformer of which we use the physical dimensions in the next calculations. The parameters used in the calculations below are the effective area,  $A_e = 20.2\,\mathrm{mm}^2$  and the nominal winding width,  $l_b = 6.5\,\mathrm{mm}$  . The minimum number of primary windings can be calculated using Eq. (3.4)  $N_{p_{\text{min}}} = \frac{375 \text{V} \cdot 0.13}{125 \text{kHz} \cdot 375 \text{mT} \cdot 20.2 \cdot 10^{-6} \text{m}^2} = 51.46.$

$$N_{p_{\min}} = \frac{375 \text{V} \cdot 0.13}{125 \text{kHz} \cdot 375 \text{mT} \cdot 20.2 \cdot 10^{-6} \text{m}^2} = 51.46.$$

Thin wire causes an increase of the copper losses in the transformer. On the other hand, thick wire expands the number of winding layers and results therefore in an increase of the proximity losses. Because of that, we aim at completely filled layers. From this we obtain  $N_p = 60$ , which results in, when using 0.16mm wire and a filling constant of 1.3, two filled layers of 30 windings. The number of secondary windings,  $N_s$ , can be calculated using

$$N_S = \frac{N_P}{N} = 8.57 \rightarrow 9.$$

Since  $N_s = 9$  we can use 0.4mm triso wire to obtain one filled layer. Two benefits of triso wire are the galvanic isolation between the primary and secondary side of the transformer and the good coupling between the primary and the secondary layer. The bias winding, necessary for the power supply of VIPer20 is chosen with due observance of the next consideration. One requirement of the converter when operating in current mode is that the output voltage must be defined from 6.5V down to 3V. Since the output voltage  $V_{\rho}$  and the bias voltage  $V_{b}$  are directly coupled by the ratio of  $N_s$  and  $N_b$  we have

$$\frac{V_o^{\min}}{V_b^{\min}} = \frac{N_s}{N_b},$$

$$N_b = N_s \frac{V_b^{\min}}{V_o^{\min}} = 9 \cdot \frac{8.5 \text{V}}{3 \text{V}} = 25.5 \rightarrow 26.$$

Due to peak rectification in the bias circuit, we have chosen, after some experiments,  $N_h = 20$ . To more or less create a filled layer we have chosen 0.28mm<sup>2</sup> wire, which is rather thick in this case, but we use the bias winding as a shield between primary and secondary side.

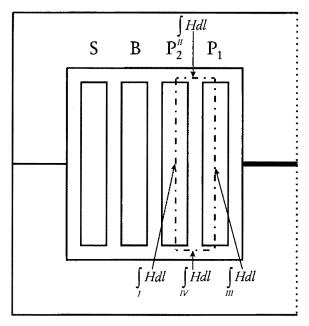

The airgap in the core can be calculated by invoking Maxwell's first law

$$\oint H \mathrm{dl} = i_{\mathrm{air}} .$$

Since  $\mu_{r_{1C85}} >> 1$  we can make a approximation

$$\oint H dl = N_p I_p = \int_{l_p} \frac{B}{\mu_0 \mu_{r_{1008}}} dl + \int_{l_p} \frac{B}{\mu_0} dl \approx \frac{B l_g}{\mu_0}.$$

Solving for the magnetic field, we obtain

$$B = \frac{N_p I_p \mu_0}{l_p}.$$

Using the relations  $\phi = BN_p A_e$ ,  $\phi = L_p I_p$  and after solving for  $l_g$ , we find

$$l_g = \frac{N_p^2 \mu_0 A_e}{L_p}.$$

Substitution of the known values results in

$$l_g = \frac{60^2 \cdot 4 \cdot \pi \cdot 10^{-7} \,\mathrm{Hm}^{-1} \cdot 20.2 \cdot 10^{-6} \,\mathrm{m}^2}{458.64 \,\mu\mathrm{H}} = 0.199 \,\mathrm{mm}\,.$$

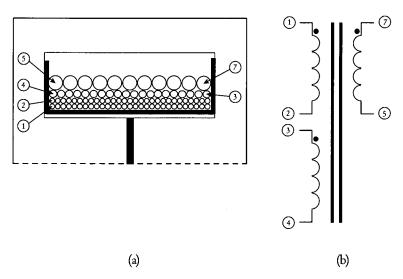

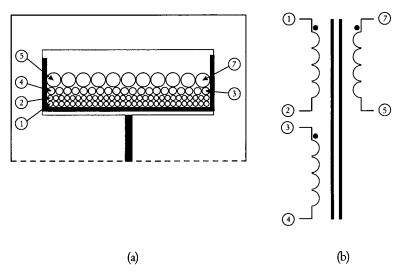

The windings of the transformer are constructed as depicted in Fig. (3.4).

Fig. (3.4) (a) Layout of the transformer (b) Electrical connections

This layout [Afstudeerverslag Patrick en Dion] is chosen because of the EMI friendly behavior, since the voltage difference between the secondary and primary windings is minimal, due to the bias winding. Important is that the two grounds, points 3 and 7, are at the same side of the bobbin. Most ideal, but rather impractical for this transformer, is to choose  $N_b=N_s$ . The capacitance between primary and secondary, the so called crosstalk capacitance, is low, whenever this condition is met. The EMI behavior of this converter benefits from this effect, as will be shown in Chapter 6.

#### 3.3 Design of the Output Filter

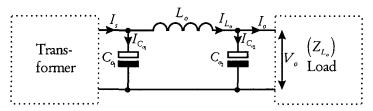

Normally the output filter is designed by taking the lifetime or maximum ripple current of the capacitor in consideration. This results usually in a rather big capacitor casing and since miniaturization is the aim, this is a disadvantage. If we had chosen for the traditional solution we needed a  $470\mu\text{F}/25\text{V}$  capacitor. Size  $10.2\text{mm}\varnothing x$  13.5mm. A way to avoid this is using Ceramic Multilayer Capacitors because of the low Equivalent Series Resistance. A second step in miniaturization is building a higher order low-pass filter with smaller components in stead of a first order filter with a rather big capacitor. We used a  $\pi$ -section as depicted in Fig. (3.5).

Fig. (3.5) Output filter.

Total size 4.3mmØx14mm and two 1206 SMD capacitors, which can be placed on the bottom side of the printed circuit board under the inductor.

The voltage ripple superimposed on the DC output voltage must be less then  $\pm 1\%$ . Calculating this ripple can not be done straightforward using the complex calculation method as in basic network theory, since the secondary current is triangular shaped. As explained in Appendix A we can decompose this triangular shaped signal into it's harmonics, calculate the voltage ripple at the output for all the harmonics and after summation we find the total voltage ripple at the output.

In this system we can distinguish the next transfer functions

$$\begin{split} H_{1}(f) &= \frac{I_{s}(f)}{I_{C_{o_{1}}}(f)} = \frac{Z_{L_{o}}(Z_{C_{o_{2}}} + Z_{L_{o}}) + Z_{C_{o_{2}}}Z_{L_{o}}}{(Z_{C_{o_{1}}} + Z_{L_{o}})(Z_{C_{2}} + Z_{L_{o}}) + Z_{C_{o_{2}}}Z_{L_{o}}}, \\ H_{2}(f) &= \frac{I_{s}(f)}{I_{L_{o}}(f)} = \frac{Z_{C_{o_{1}}}(Z_{C_{o_{1}}} + Z_{L_{o}})(Z_{C_{o_{2}}} + Z_{L_{o}})}{(Z_{C_{o_{1}}} + Z_{L_{o}})(Z_{C_{o_{2}}} + Z_{L_{o}}) + Z_{C_{o_{2}}}Z_{L_{o}}}, \\ H_{3}(f) &= \frac{I_{s}(f)}{I_{C_{o_{2}}}(f)} = \frac{Z_{C_{o_{1}}}Z_{L_{o}}}{(Z_{C_{o_{1}}} + Z_{L_{o}})(Z_{C_{o_{2}}} + Z_{L_{o}}) + Z_{C_{o_{2}}}Z_{L_{o}}}, \\ H_{4}(f) &= \frac{I_{s}(f)}{I_{o}(f)} = \frac{Z_{C_{o_{1}}}Z_{C_{o_{2}}}}{(Z_{C_{o_{1}}} + Z_{L_{o}})(Z_{C_{o_{2}}} + Z_{L_{o}}) + Z_{C_{o_{2}}}Z_{L_{o}}}, \\ H_{5}(f) &= \frac{I_{s}(f)}{V_{o}(f)} = H_{4}(f)Z_{L_{o}}. \end{split}$$

Solving  $I_{C_a}(t)$  by substitution and transforming the result back to time domain yields

$$I_{C_{q_1}}(t) = a_0^s |H_1(f)| + \sum_{n=1}^m |H_1(f)| a_n^s \cos \left( \frac{2\pi nt}{T} + \arg(H_1(f)) \right) + |H_1(f)| b_n^s \sin \left( \frac{2\pi nt}{T} + \arg(H_1(f)) \right)$$

Using the same procedure we can calculate the remaining wave forms,  $I_{L_o}(t)$ ,  $I_{C_o}(t)$ ,  $I_o(t)$  and  $V_o(t)$ . We used the Ceramic Multilayer Capacitors of  $22\,\mu\mathrm{F}$  with an ESR of  $200\mathrm{m}\Omega$ . By trial and error we found  $L_o=22\,\mu\mathrm{H}$  with an ESR of  $1\Omega$  in order to obtain a output voltage ripple of less then  $\pm 1\%$ . We calculated the output voltage and current ripple with a resistive load of

$$R_L = \frac{\left(V_o^2\right)}{P_o} = \frac{\left(6.5\mathrm{V}\right)^2}{5.2\mathrm{W}} = 8.125\Omega$$

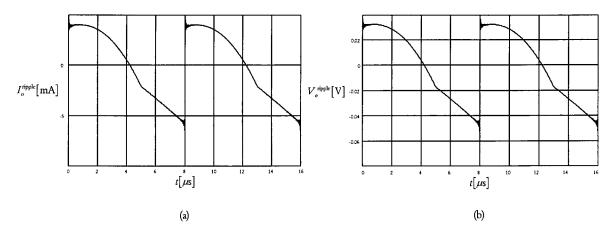

. The calculated output voltage and current are depicted in Fig. (3.6).

Fig. (3.6) (a) Output ripple current (b) Output ripple voltage (n = 150).

#### 3.4 Design of the Voltage Regulation Circuitry

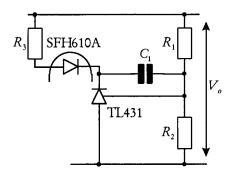

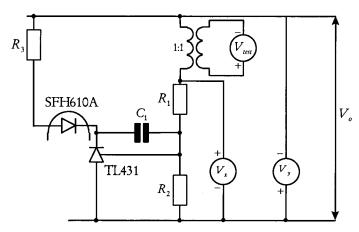

For the voltage regulation circuit we have made use of a programmable shunt regulator diode, which has the advantages to create a precision reference voltage, in order to guarantee the  $\pm 1\%$ output voltage. The schematic used for the voltage regulation is depicted in Fig. ( 3.7 ).

Fig. (3.7) Circuit of the voltage regulation circuitry.

This circuit is built around a typical application of the TL431, a precision voltage reference. The reference pin of the TL431 is internally fixed at precisely 2.5V. The voltage divider, consistent out of resistor  $R_1$  and  $R_2$  should fulfill this condition, when  $V_{\scriptscriptstyle o} = 6.5 \mathrm{V}$  . From this we have

$$V_{r} = V_{o} \frac{R_{2}}{R_{1} + R_{2}},$$

$$R_1 = R_2 \left( \frac{V_0}{V_r} - 1 \right),$$

in which we choose

$$R_2=10 \mathrm{k}\Omega$$

, which results in  $R_1=16 \mathrm{k}\Omega$ . The current in these resistors is

$$I=\frac{V_o}{R_1+R_2}=\frac{6.5 \mathrm{V}}{16 \mathrm{k}\Omega+10 \mathrm{k}\Omega}=250 \mu \mathrm{A},$$

which is much more then the reference input current of  $4\mu$ A. In other words, the reference input current will hardly influence the voltage divider. Capacitor  $C_1$  will be explained in Chapter 4.

Since the tolerance in the output voltage is limited to  $\pm 1\%$  , we calculate the tolerance in the output voltage given the tolerances of the components used in Fig. (3.7). From the same figure we have

$$V_{o} = V_{r} \frac{R_{1} + R_{2}}{R_{2}} \,.$$

We expect the tolerance to increase linear from it's minimum to it's maximum and therefore we can write for the absolute tolerance in the output voltage

$$\begin{split} \left| \frac{\Delta V_o}{V_o} \right| &= \left| \frac{1}{V_o} \left| \left( \frac{\partial V_o}{\partial V_r} \middle| \Delta V_r \middle| + \left| \frac{\partial V_o}{\partial R_1} \middle| \Delta R_1 \middle| + \left| \frac{\partial V_o}{\partial R_2} \middle| \Delta R_2 \middle| \right) \right| = \left| \frac{1}{V_o} \left| \left( \frac{R_1 + R_2}{R_2} \middle| \Delta V_r \middle| + \frac{V_r}{R_2} \middle| \Delta R_1 \middle| + \frac{V_r R_1}{R_2^2} \middle| \Delta R_2 \middle| \right) \right| \\ &= \left| \frac{1}{6.5 \text{V}} \left| \left( 2.5 \text{V} \middle| \Delta V_r \middle| + 2.5 \cdot 10^{-4} \text{A} \middle| \Delta R_1 \middle| + 4 \cdot 10^{-4} \text{A} \middle| \Delta R_2 \middle| \right). \end{split}$$

Substituting  $\Delta V_r = 10 \,\text{mV}$ ,  $\Delta R_1 = 800\Omega$  and  $\Delta R_2 = 500\Omega$  results in  $\frac{\Delta V_o}{V_o} = 6.54\%$ , which is not surprisingly since we are using 5% resistors. Using 1% resistors we have  $\frac{\Delta V_o}{V_o} = 1.62\%$  and using

0.1% resistors we have  $\frac{\Delta V_o}{V_o}$  = 0.51% which is within the specifications. We will use the resistors

which are available at EPM causing, due to 5% tolerance, an error in the output voltage of at most  $\pm 6.54\%$ , which is equal to  $\pm 425 \text{mV}$ .

#### 3.5 Design of the Current Regulation Circuitry

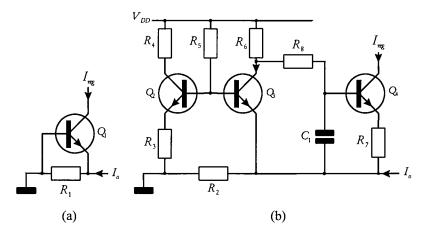

Since we are aiming at minimum losses in the converter, it is appreciable to reduce the losses in the resistors. Especially the current sense resistor is normally dissipating a lot. See Fig. (3.8 a) for a conventional setup.

Fig. (3.8) (a) Conventional current measuring circuit (b) Current measuring circuit with minimalised losses.

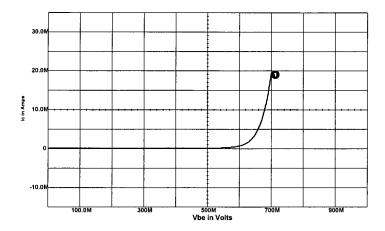

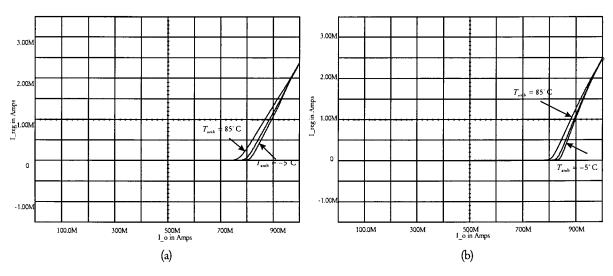

From this figure we have for the current sense resistor losses  $P_L = I_O R_1$ . When using a BC848C transistor for  $Q_1$ , the bases-emitter-voltage needs to be approximately 650mV to turn the transistor in a on state. The current regulation must be activated at  $I_o = 800 \, \mathrm{mA}$ . Using this we can calculate the value of  $R_1$ , and obtain  $R_1 = 812 \, \mathrm{m}\Omega$ . The resulting losses in the resistor are  $I_O^2 R_1 = 520 \, \mathrm{mW}$ . Reducing these losses can be accomplished by having a closer look at the  $V_{le} - I_c$  curve of a transistor, of which an example is given in Fig. (3.9).

Fig. (3.9)  $V_{be}$  versus  $I_C$  curve of the BC848C transistor.

Up till 550mV, the collector current hardly changes due to a change in the base-emitter voltage. A voltage drop of 550mV across the current sense resistor  $R_1$  does not contribute to an increase in the collector current, but does generate losses in the resistor. A way to avoid this is creating an offset voltage of 550mV in series with the base-emitter. The current sense resistor now only adds a small voltage to increase the collector current. This means that the resistor value of the current sense resistor can be chosen smaller, and as a consequence the losses reduce.

This offset voltage idea can be used the other way around as depicted in Fig. (3.8.b). Transistor  $Q_2$  is operating in saturation, in order to create a constant current source. This to create a defined voltage across  $R_3$  and  $V_{le_{Q_2}}$ , which is just enough to turn a BC848C in an on state. The current sense resistor now decreases the  $V_{le_{Q_2}}$  to turn  $Q_3$  in a nearly off state. From this circuit we have

$$I_{e_{Q_2}}R_3 + V_{be_{Q_2}} = (I_O + I_{e_{Q_3}})R_2 + V_{be_{Q_3}}.$$

(3.6)

Solving Eq. (3.6) for  $V_{k_{O_1}}$  yields

$$V_{be_{Q_3}} = I_{e_{Q_2}} R_3 + V_{be_{Q_2}} - (I_O + I_{e_{Q_3}}) R_2.$$

Transistor  $Q_3$  is in the on state when  $I_O < 800 \, \mathrm{mA}$  and in an off state when  $I_O \ge 800 \, \mathrm{mA}$ . We can choose an operating point at  $I_o = 800 \, \mathrm{mA}$ , at which the emitter voltages are chosen equal resulting in  $V_{e_{Q_2}} = V_{e_{Q_3}} = I_o R_2 = 800 \, \mathrm{mA} \cdot 0.1 \Omega = 80 \, \mathrm{mV}$  ( $Q_2$  and  $Q_3$  have the same  $V_e$  voltage at this point). Since the bases of the transistors are connected, we have, with neglecting  $I_{e_{Q_3}}$ ,

$$\frac{I_{e_{Q_1}}}{I_{e_{Q_1}} + I_O} \approx \frac{I_{e_{Q_2}}}{I_O} = \frac{R_2}{R_3}.$$

(3.7)

Applying Kirchhoff's current law to Q2, results in after neglecting the base current,

$$\frac{V_{DD} - V_{e_{Q_1}} - V_{ce(sat)}}{R_4} = \frac{V_{e_{Q_2}}}{R_3} = I_O \frac{R_2}{R_3}.$$

(3.8)

Since  $Q_2$  is operating in saturation we have

$$V_{b_{Q_2}} = 500 \text{mV} + I_{o}R_2 = V_{DD} - \frac{I_{e_{Q_2}}}{\beta_{SAT}} R_5.$$

(3.9)

Solving Eq. (3.6), Eq. (3.8) and (3.9) after taking  $R_2=0.1\Omega$ ,  $R_3=120\Omega$  and  $\beta_{\rm SAT}=8.33$ , results in  $R_4=3.48{\rm k}\Omega$  and  $R_5=24{\rm k}\Omega$ . Low-pass filter  $R_8$ / $C_1$  is added for gain correction at higher frequencies and will explained in Chapter 4.

Transistor  $Q_4$  is added because the signal  $I_{\rm reg}$  is inverted. In this configuration  $Q_3$  is forced to operate in saturation mode if  $I_{\rm O}$  < 800 mA, since  $Q_4$  is off. We limit the  $I_{\rm e_Q}$  to 2mA by choosing  $R_6$

$$R_6 = \frac{V_{\rm DD} - V_{be4}}{I_{c3}} = \frac{2.5 \text{V} - 0.5 \text{V}}{2 \text{mA}} = 1 \text{k}\Omega.$$

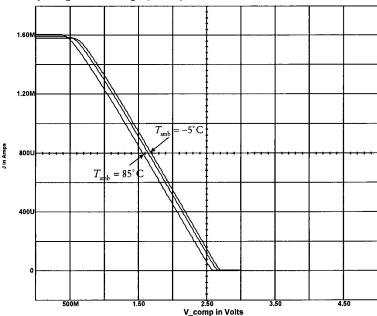

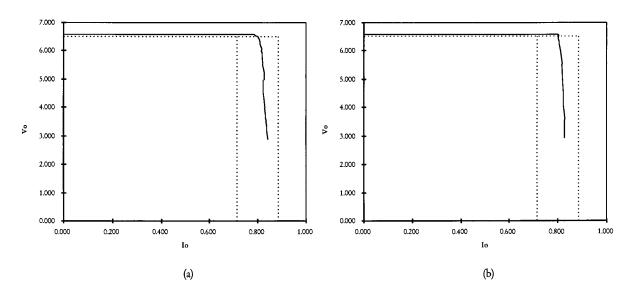

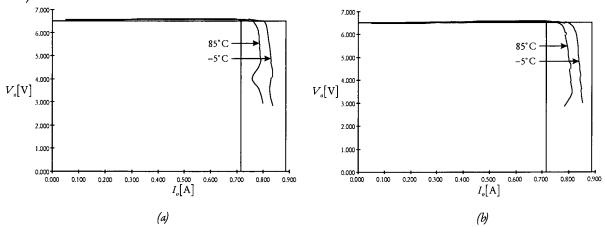

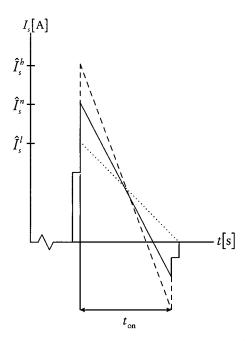

We used ICAPS/4 to run a simulation of the current control circuit at three ambient temperatures,  $T_{anb} = 27^{\circ} \text{C}$ ,  $T_{anb} = -5^{\circ} \text{C}$  and  $T_{anb} = 85^{\circ} \text{C}$ , to verify the proper working of the circuit. The results are depicted in .Fig. (3.10)

Fig. (3.10) Simulation results of the current control circuit, (a)  $V_o = 3V$  (b)  $V_o = 6.5V$

#### 3.6 Design of the Frequency Control Circuitry

One disadvantage of the VIPer20 is the minimum on time, which is limited to  $0.3\mu s$ . This limit results in a restriction for the switching frequency and the primary duty cycle

$$\delta_p \frac{1}{f_s} \ge 0.3 \,\mu\text{s} \to f_s \le 3.33 \cdot 10^6 \,\delta_p \text{Hz} \,. \tag{3.10}$$

Consider the next two situations

$$\delta_{p}^{\text{max}} = \sqrt{\frac{2L_{p}P_{o}^{\text{max}}f_{s}}{\left(V_{DC}^{\text{min}}\right)^{2}\eta}} = \sqrt{\frac{2\cdot458.64\,\mu\text{H}\cdot5.2\text{W}\cdot125\text{kHz}}{\left(70\text{V}\right)^{2}\cdot0.8}} = 0.39 \rightarrow \delta_{p}\frac{1}{f_{s}} = 3.12\,\mu\text{s},$$

$$\delta_{p}^{\text{min}} = \sqrt{\frac{2L_{p}P_{o}^{\text{min}}f_{s}}{\left(V_{DC}^{\text{max}}\right)^{2}\eta}} = \sqrt{\frac{2\cdot458.64\,\mu\text{H}\cdot325\text{mW}\cdot125\text{kHz}}{\left(375\text{V}\right)^{2}\cdot0.8}} = 0.02 \rightarrow \delta_{p}\frac{1}{f_{s}} = 0.16\,\mu\text{s}.$$

The power supply will operate in burst mode at minimum load and maximum input voltage. A way to avoid this problem is to make the switching frequency a function of the input voltage and the output load, resulting in a mechanism which reduces the switching frequency whenever the primary on time becomes too small. The maximum switching frequency is

$$f_s^{\text{max}} = \frac{\left(V_{DC}^{\text{min}}\right)^2 \left(\delta_p^{\text{max}}\right)^2 \eta}{2P_o^{\text{max}} L_p} = \frac{\left(70\text{V}\right)^2 \cdot 0.39^2 \cdot 0.8}{2 \cdot 5.2 \text{W} \cdot 458.64 \,\mu\text{H}} = 125 \text{kHz}.$$

The minimum primary duty cycle can be calculated using Eq. (3.10)

$$L_{p} = \frac{\left(V_{DC}^{\text{max}}\right)^{2} \delta_{p} \eta}{2P_{o}^{\text{min}} \left(3.33 \cdot 10^{6} \delta_{p}\right)} = 458.64 \,\mu\text{H} = \frac{\left(375\text{V}\right)^{2} \cdot \delta_{p} \cdot 0.8}{2 \cdot 235 \text{mW} \cdot \left(3.33 \cdot 10^{6} \cdot \delta_{p}\right)} \rightarrow \delta_{p} = 0.088 \,,$$

which results in a minimum switching frequency of  $f_s = 3.33 \cdot 10^6 \delta_p = 29.38 \text{kHz}$ .

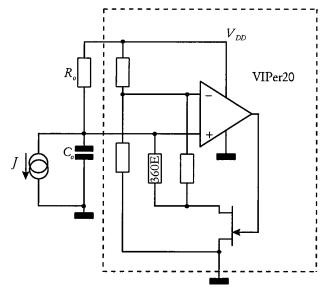

The internal oscillator of the VIPer20 and the external components are depicted in Fig. (3.11).

Fig. (3.11) The oscillator of the VIPer20 and external components

This oscillator is based on charging and discharging capacitor  $C_o$  between it's two threshold voltages, oscillator valley  $(V_{\rm osc}^{\rm valley})$  and oscillator peak voltage  $(V_{\rm osc}^{\rm peak})$ . From the data sheets we have  $V_{\rm osc}^{\rm valley} = 3.7 \, {\rm V}$  and  $V_{\rm osc}^{\rm peak} = 7.1 \, {\rm V}$ . The current source J is not standard, but an extension of the oscillator to control the frequency externally. In the calculations below  $R_D$  is the  $360\Omega$  resistor. We will first derive the oscillator frequency as function of the current J. During charging of the capacitor  $C_o$  the system is governed by the next first order differential equation

$$\frac{V_{DD} - V_{C_o}}{R_o} + J + C_o \frac{d(-V_{C_o})}{dt} = 0,$$

$$R_o C_o \frac{dV_{C_o}}{dt} + V_{C_o} = R_o J + V_{DD}.$$

(3.11)

Solving Eq. (3.11) for the capacitor voltage  $V_{C_o}$  and after substitution of the boundary conditions  $V_{C_o}|_{t=t_0} = 3.7 \text{V}$  and  $V_{C_o}|_{t=t_1} = 7.1 \text{V}$  in the general solution, we find for the capacitor voltage

$$V_{C_o}^{(1)}(t) = (3.7 - V_{DD} - R_o J)e^{-\frac{t}{R_o C_o}} + V_{DD} + R_o J,$$

and for the time  $t = t_1$

$$t_1(V_{DD}, J) = R_o C_o \ln \left( \frac{3.7 - V_{DD} - R_o J}{7.1 - V_{DD} - R_o J} \right).$$

During discharging of capacitor C<sub>o</sub> the system is governed by the next first order differential equation

$$\frac{V_{DD} - V_{C_o}}{R_o} + J + \frac{V_{C_o}}{R_D} + C_o \frac{d(-V_{C_o})}{dt},$$

$$\frac{R_D R_o C_o}{R_D + R_o} \frac{dV_{C_o}}{dt} + V_{C_o} = \frac{R_D}{R_D + R_o} V_{DD} + \frac{R_D R_o}{R_D + R_o} J.$$

(3.12)

Solving Eq. (3.12) for the capacitor voltage  $V_{C_o}$  and after substitution of the boundary conditions  $V_{C_o}|_{t=t_1} = 7.1 \text{V}$  and  $V_{C_o}|_{t=t_2} = 3.7 \text{V}$  in the general solution, we find for the capacitor voltage

$$V_{C_o}^{(2)}(t) = \left(7.1 - \frac{R_D}{R_D + R_o} V_{DD} - \frac{R_D R_o}{R_D + R_o} J\right) e^{-\frac{R_D + R_o}{R_D R_o C_o} t} + \frac{R_D}{R_D + R_o} V_{DD} + \frac{R_D R_o}{R_D + R_o} J,$$

and for the time  $t = t_2$

$$t_{2}(V_{DD}, J) = \frac{R_{D}R_{o}C_{o}}{R_{D} + R_{o}} \ln \left( \frac{7.1 - \frac{R_{D}}{R_{D} + R_{o}}V_{DD} - \frac{R_{D}R_{o}}{R_{D} + R_{o}}J}{3.7 - \frac{R_{D}}{R_{D} + R_{o}}V_{DD} - \frac{R_{D}R_{o}}{R_{D} + R_{o}}J} \right).$$

By definition is the switching frequency equal to

$$f_s(V_{DD}, J) = \frac{1}{t_1(V_{DD}, J) + t_2(V_{DD}, J)}$$

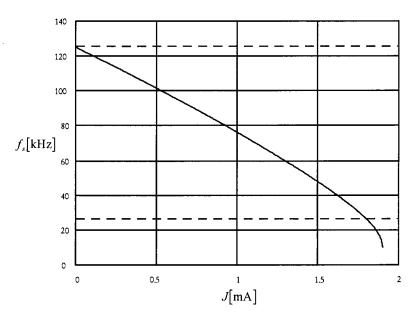

A plot of the switching frequency as function of the current J and  $V_{DD}=13\mathrm{V}$ ,  $R_o=3.1\mathrm{k}\Omega$ ,  $C_o=4.7\mathrm{nF}$  is given in Fig. (3.12).

Fig. (3.12) The switching frequency versus the control current J at  $V_{DD} = 13 \, \mathrm{V}$ .

The dotted lines are presenting the minimum and maximum switching frequency.

The voltage  $V_{comp}$  is joined with the duty cycle  $\delta_p$  as  $0.5 \text{V} \leq V_{comp} \leq 2.5 \text{V} \rightarrow 0.05 \leq \delta_p \leq 0.39$ . Because of this the current source J will be implemented as a voltage controlled current source which joins the voltage  $V_{comp}$  and the current J as  $0.5 \text{V} \leq V_{comp} \leq 2.5 \text{V} \rightarrow 1.6 \text{mA} \geq J \geq 0 \text{mA}$ .

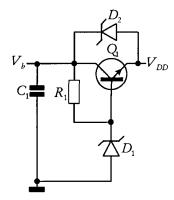

Fig. (3.13) Voltage controlled current source used in frequency control

The voltage regulator diode,  $D_1$ , is added to prevent  $Q_1$  from saturating. At J=0mA the collector voltage of  $Q_1$  could become approximately 700mV, which causes  $Q_1$  to saturate. The diode is chosen 3V because of the oscillator valley voltage of 3.1V. Otherwise  $Q_2$  would saturate. Because of the diode, the minimum collector voltage of  $Q_2$  is 3V, which is more than the maximum base voltage of 2.5V. We will now derive a relationship between the current J and the input voltage  $V_{corp}$ . The output current is equal to

$$J = \frac{V_{C_{Q_1}} - V_{C_{Q_2}}}{R_{A}} = \frac{V_{C_{Q_1}} - \left(V_{D_1} + V_{b_{Q_2}}\right)}{R_{A}} = \frac{V_{DD} - I_{c_{Q_1}} R_1 - J R_1 - \left(V_{D_1} + V_{b_{Q_2}}\right)}{R_{A}}.$$

If we neglect the base current of transistor  $Q_1$  and therefore assume  $I_{c_Q} = I_{e_Q}$  we find

$$J = -V_{comp} \frac{R_1}{R_1 R_2 + R_2 R_4} + \frac{V_{DD}}{R_1 + R_4} + \frac{V_{bc_Q} R_1}{R_1 + R_2} - \frac{V_{D_1} + V_{bc_Q}}{R_1 + R_4}, \tag{3.13}$$

and

$$\left| \frac{\Delta J}{\Delta V_{comp}} \right| = \frac{R_1}{R_1 R_2 + R_2 R_4},\tag{3.14}$$

and as a consequence

$$R_{4} = \frac{\left(\boldsymbol{V}_{le_{Q_{1}}} - \boldsymbol{V}_{comp} + \boldsymbol{V}_{DD} - \boldsymbol{V}_{D_{1}} - \boldsymbol{V}_{le_{Q_{2}}}\right) \left(1 - \left|\frac{\Delta \boldsymbol{J}}{\Delta \boldsymbol{V}_{comp}}\right| R_{2}\right)}{\boldsymbol{J}},$$

From Eqs. (3.13) and (3.14) we find by substitution of  $V_{DD}=13{\rm V}$ ,  $V_{le_Q}=V_{le_Q}=700{\rm mV}$  and  $V_{D_1}=3{\rm V}$  for the resistors  $R_1=4.8{\rm k}\Omega$ ,  $R_2=1{\rm k}\Omega$  and  $R_4=1.2{\rm k}\Omega$ .

We might seem to have a problem with this solution for the current source, since it is very dependend of the supply voltage  $V_{DD}$ . However,  $V_{DD}$  is directly coupled to  $V_o$  and therefore constant whenever the converter is operating in voltage mode. Is the converter operating in current mode, then  $V_o$  will decrease and as a consequence  $V_{DD}$  will also decrease. Because of this, the current source will sink less current from the oscillator causing the switching frequency to increase. This is not a problem for the minimum primary on time  $T_{on}=0.3\mu s$ . The minimum load in current mode is  $P_o=V_o^{\min}I_o=3V\cdot800 \text{mA}=2.4 \text{W}$ . In this situation  $V_{DD}=8.5 \text{V}$  resulting the

current source to sink 0.95mA. The switching frequency versus the shunted current is shown in Fig. (3.12) and is at 0.95mA equal to 75kHz. The minimum duty cycle will be reached at maximum input voltage and is equal to

$$\delta_{p}^{\min} = \sqrt{\frac{2L_{p}P_{o}^{\min}f_{s}}{\left(V_{DC}^{\max}\right)^{2}\eta}} = \sqrt{\frac{2\cdot458.64\mu\text{H}\cdot2.4\text{W}\cdot75\text{kHz}}{\left(375\text{V}\right)^{2}\cdot0.8}} = 0.038 \rightarrow \delta_{p}\frac{1}{f_{s}} = 0.51\mu\text{s}.$$

Even in a situation when the current source is not working at all we have

$$\delta_{p}^{\min} = \sqrt{\frac{2L_{p}P_{o}^{\min}f_{s}^{\max}}{\left(V_{DC}^{\max}\right)^{2}\eta}} = \sqrt{\frac{2\cdot458.64\,\mu\text{H}\cdot2.4\text{W}\cdot125\text{kHz}}{\left(375\text{V}\right)^{2}\cdot0.8}} = 0.049 \rightarrow \delta_{p}\frac{1}{f_{s}} = 0.40\,\mu\text{s},$$

which is more than the minimum on time.

We used ICAPS/4 to simulate the current source at three ambient temperatures,  $T_{anb} = 27^{\circ}$  C,  $T_{anb} = -5^{\circ}$  C and  $T_{anb} = 85^{\circ}$  C, to verify the proper working of the circuit. A graph of the voltage  $V_{comp}$  versus the current J is given in Fig. (3.14).

Fig. (3.14) Results of the simulations of the voltage controlled current source.

#### 3.7 Design of the Bias Voltage Regulation

As pointed out in the paragraph of the transformer design, we have chosen  $\frac{N_b}{N_c} = 2.22$ , to

guarantee a minimum output voltage of 3V . This results in a guaranteed bias voltage of minimal 8.5V. However the maximum bias voltage is in the ideal case  $V_b^{\rm max} = 2.22 \cdot 6.5 {\rm V} = 14.43 {\rm V}$ , but with peak rectification 18V. The VIPer20 will work in primary sense mode if  $12.5 {\rm V} \leq V_{DD} \leq 13 {\rm V}$  and will shut down if  $V_D \geq 13 {\rm V}$ . A solution is to reduce the voltage with a linear regulator as depicted in Fig. (3.15).

Fig. (3.15) Linear regulation circuit used in the bias circuit.

As pointed out  $V_{DD}$  must be below 12.5V for secondary sensing. If we choose the voltage regulator diode voltage 13V then  $V_{DD} = V_{D_1} - V_{le_{Q_1}} = 13\text{V} - 0.7\text{V} = 12.3\text{V}$ . The resistor is added to limit the current in the voltage regulator diode and is equal to

$$R_1 = \frac{V_b^{\text{max}} - V_{D_1}}{I_{D_2}} = \frac{18\text{V} - 13\text{V}}{1\text{mA}} = 5\text{k}\Omega$$

.

We have chosen the current rather low to decrease the losses in the resistor. No problem occurs if  $V_b \le V_{D_1}$ , because the transistor will work as an ordinary diode and  $V_{DD} = V_b - 0.7 \text{V}$ . Diode  $D_2$  is added to charge the capacitor during the startup using the high voltage current source of the VIPer20.

A disadvantage of this method is that we disable the overvoltage protection of the VIPer20. One way to overcome this problem is using voltage regulator diode  $D_2$  as depicted in Fig. (3.15). If the collector voltage of the transistor increases beyond 20V then a fault has appeared and the power supply should be shut down. For example if the opto coupler is not functioning. Choosing  $D_2 = 7 \text{V}$  will force the power supply to shut down if the collector voltage is 20V, because the VIPer20 will shut down if  $V_{DD} \geq 13 \text{V}$ .

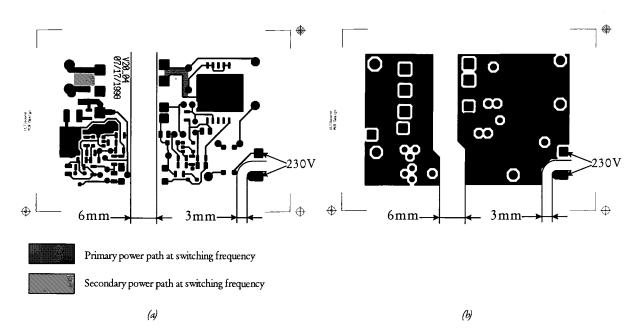

#### 3.8 Printed Circuit Board Design

The printed circuit board is designed by taking safety rules in consideration. We have kept 6mm creep distance between the "hot" and "cold" side of the battery charger and 3mm creep distance between the fused and the net side of the battery charger. From an EMI point of view we have kept the electrical loops as small as possible. The final printed circuit board is depicted in Fig. (3.16).

Fig. (3.16) The (a) bottom and (b) the top side of the printed circuit board

We used a bi-layer printed circuit board to decrease the capacitive coupling with the environment. This was necessary since the drain is electrically connected with the PowerSO-10 casing.

#### 4. Control Loop Calculations and Measurements

In order to predict the behaviour of the converter in voltage and current mode regulation, we have computed the Bode plots of the open loop transfer function, which are needed to determine stability. To do so, we need a small signal (AC) model of the converter in each working mode (voltage or current regulation). These models will be derived using the State-Space Averaging Method and simple network analysis. We will first give some theoretical background information concerning the used stability margins. Then the needed transfer functions will be calculated and analysed. Afterwards we will measure the transfer functions with a gain/phase analyser to verify the calculated transfer functions.

#### 4.1 Stability Margins

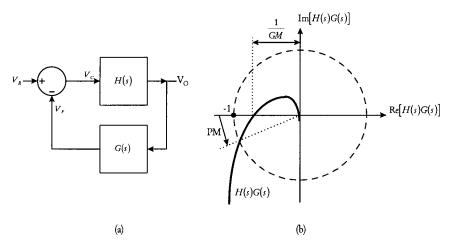

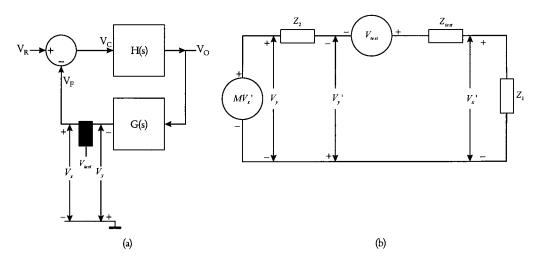

Most power supplies behave roughly similar to that of the system which is depicted in Fig. (4.1.a).

Fig. (4.1) (a) A typical controlled system (b) Nyquist plot for defining gain margin (GM) and phase margin (PM).

The closed loop transfer function of this system is

$$\frac{V_O(s)}{V_R(s)} = \frac{H(s)}{1 + G(s)H(s)}.$$

(4.1)

The open loop transfer function can be measured by injecting a test signal into the closed loop of a system as depicted in Fig. (4.1.a). We can use the closed loop to predict the stability of the system. For systems which can be described by Eq. (4.1) this can be done by making use of the argument principle [8]. From Eq. (4.1) we find that the closed loop roots are solutions of 1+G(s)H(s)=0. Therefore we are interested in the Nyquist plot of H(s)G(s) near -1 on the real axis, since the plot is not allowed to encircle this point in a clockwise or counterclockwise direction for a stable system. This as a direct result of the argument principle and the fact that poles and zeros are not allowed in the right half plane. Clockwise encircling indicates a zero in the right half plane and counterclockwise encircling indicates a pole in the right half plane. From this we can define a phase margin and a gain margin as depicted in Fig. (4.1.b). These definitions can also be used in Bode plots of H(s)G(s) and are stated as,

GAIN MARGIN (GM) is the factor by which the gain is less than the neutral stability value,

PHASE MARGIN (PM) is the amount by which the phase of H(s)G(s) exceeds -180° when |H(s)G(s)| = 1.

This results in simple restrictions to the Bode plots of H(s)G(s) in order to guarantee system stability.

# 4.2 The State-Space Averaging Method applied to a Flyback Converter with CLC output Filter

The use of the State-Space Averaging Method as will be presented here is taken from [Barzegar, F, et al].

#### 4.2.1 Equivalent Steady-State (DC) Model and Dynamic (AC) Small Signal Model

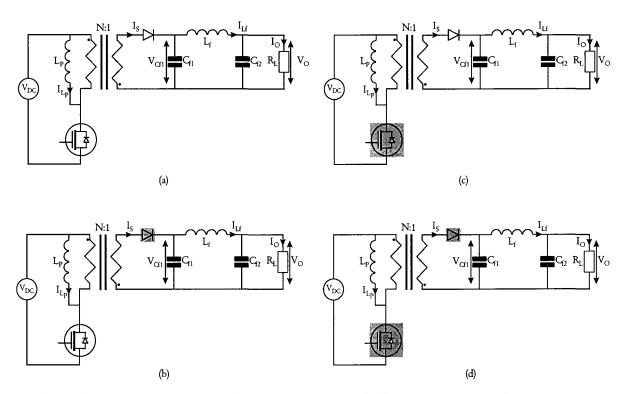

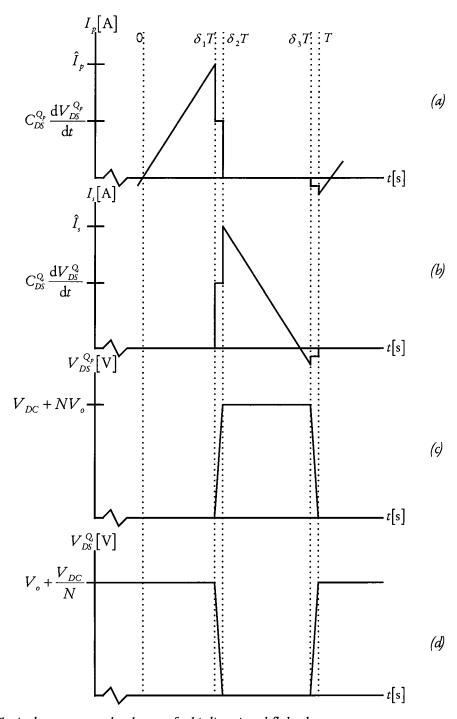

The equivalent circuit models for the power path of a flyback converter in discontinuous mode are presented in Fig. (4.2).

Fig. (4.2) The equivalent circuit models for the power path of a flyback converter in discontinuous mode.

Fig. (4.2.a) shows the complete circuit of the flyback converter as used. In the remaining figures striped components denote components in "off" state, representing the situations in the stages  $0 < t \le \delta_1 T$ ,  $\delta_1 T < t \le \delta_2 T$  and  $\delta_2 T < t \le T$  respectively. Several simplifications are made in this model to make a pencil and paper calculation possible. The first simplification is the absence of ESR in the output capacitors and the inductor. This is allowed, since we are using Ceramic Multilayer Capacitors, which have an ESR of only  $200 \text{m}\Omega$ . The series resistance of the inductor is not this low, but for simplicity neglected. The second simplification is the absence of parasitic components like the resistance and inductance of the printed circuit board traces. In this system the state-space vector  $\mathbf{x}(t)$ , which contains the state variables of the system, and the source vector  $\mathbf{u}(t)$  are defined according to

$$\mathbf{x}(t) = \begin{pmatrix} I_{L_p}(t) \\ I_{L_f}(t) \\ V_{C_{f1}}(t) \\ V_o(t) \end{pmatrix}, \quad \mathbf{u}(t) = V_{DC}.$$

The next step in the state-space averaging method is to define the system equations in three stages, since the converter is working in discontinuous mode. For stage one,  $0 < t \le \delta_1 T$ , the next set of equations is governing the state variables

$$L_{p} \frac{dI_{p}}{dt} = V_{DC},$$

$$L_{f} \frac{dI_{L_{f}}}{dt} = V_{C_{f1}} - V_{o},$$

$$C_{f1} \frac{dV_{C_{f1}}}{dt} = I_{L_{f}},$$

$$C_{f2} \frac{dV_{0}}{dt} = I_{L_{f}} - \frac{V_{o}}{R_{I}},$$

or written in matrix form,

$$\dot{\mathbf{x}}(t) = \mathbf{A}_{1}\mathbf{x}(t) + \mathbf{B}_{1}\mathbf{u}(t) = \begin{pmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & \frac{1}{L_{f}} & -\frac{1}{L_{f}} \\ 0 & \frac{1}{C_{f1}} & 0 & 0 \\ 0 & \frac{1}{C_{f2}} & 0 & -\frac{1}{C_{f2}R_{L}} \end{pmatrix} \mathbf{x}(t) + \begin{pmatrix} \frac{1}{L_{p}} \\ 0 \\ 0 \\ 0 \end{pmatrix} \mathbf{u}(t). \tag{4.2}$$

For the second stage ,  $\delta_1 T < t \le \delta_2 T$  , the next set of equations is governing the state variables,

$$\begin{split} L_{p} \frac{\mathrm{d}I_{p}}{\mathrm{d}t} &= -NV_{DC}, \\ L_{f} \frac{\mathrm{d}I_{L_{f}}}{\mathrm{d}t} &= V_{C_{f1}} - V_{o}, \\ C_{f1} \frac{\mathrm{d}V_{C_{f1}}}{\mathrm{d}t} &= NI_{p} - I_{L_{f}}, \\ C_{f2} \frac{\mathrm{d}V_{0}}{\mathrm{d}t} &= I_{L_{f}} - \frac{V_{o}}{R_{L}}, \end{split}$$

or written in matrix form,

$$\dot{\mathbf{x}}(t) = \mathbf{A}_{1}\mathbf{x}(t) + \mathbf{B}_{1}\mathbf{u}(t) = \begin{pmatrix} 0 & 0 & -\frac{N}{L_{p}} & 0 \\ 0 & 0 & \frac{1}{L_{f}} & -\frac{1}{L_{f}} \\ \frac{N}{C_{f1}} & -\frac{1}{C_{f1}} & 0 & 0 \\ 0 & \frac{1}{C_{f2}} & 0 & -\frac{1}{C_{f2}R_{L}} \end{pmatrix} \mathbf{x}(t) + \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \end{pmatrix} \mathbf{u}(t). \tag{4.3}$$

For the last stage,  $\,\delta_2 T < t \leq T$  , the next set of equations is governing the state variables,

$$L_{p} \frac{dI_{p}}{dt} = 0,$$

$$L_{f} \frac{dI_{L_{f}}}{dt} = V_{C_{f1}} - V_{o},$$

$$C_{f1} \frac{dV_{C_{f1}}}{dt} = I_{L_{f}},$$

$$C_{f2} \frac{dV_{0}}{dt} = I_{L_{f}} - \frac{V_{o}}{R_{I}},$$

or written in matrix form,

$$\dot{\mathbf{x}}(t) = \mathbf{A}_{1}\mathbf{x}(t) + \mathbf{B}_{1}\mathbf{u}(t) = \begin{pmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & \frac{1}{L_{f}} & -\frac{1}{L_{f}} \\ 0 & \frac{1}{C_{f1}} & 0 & 0 \\ 0 & \frac{1}{C_{f2}} & 0 & -\frac{1}{C_{f2}R_{L}} \end{pmatrix} \mathbf{x}(t) + \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \end{pmatrix} \mathbf{u}(t). \tag{4.4}$$

Since the derivatives are taken along linear ramp slopes, we can replace the derivatives by differences without creating any computational rounding errors. Applying this to Eq. (4.2) to Eq. (4.4) yields

$$\begin{split} \frac{\mathbf{x}(\delta_1 T) - \mathbf{x}(0)}{\delta_1 T} &= \mathbf{A}_1 \mathbf{x}(t) + \mathbf{B}_1 \mathbf{u}(t), \\ \frac{\mathbf{x}(\delta_2 T) - \mathbf{x}(\delta_1 T)}{\delta_2 T} &= \mathbf{A}_2 \mathbf{x}(t) + \mathbf{B}_2 \mathbf{u}(t), \\ \frac{\mathbf{x}(T) - \mathbf{x}(\delta_2 T)}{(1 - \delta_1 - \delta_2) T} &= \mathbf{A}_3 \mathbf{x}(t) + \mathbf{B}_3 \mathbf{u}(t). \end{split}$$

Elimination of the  $\mathbf{x}(\delta_1 T)$  and  $\mathbf{x}(\delta_2 T)$  terms by substitution results in

$$\dot{\mathbf{x}}(t) = \mathbf{A}\mathbf{x}(t) + \mathbf{B}\mathbf{u}(t) = \left(\delta_1 \mathbf{A}_1 + \delta_2 \mathbf{A}_2 + \left(1 - \delta_1 - \delta_2\right) \mathbf{A}_3\right) \mathbf{x}(t) + \left(\delta_1 \mathbf{B}_1 + \delta_2 \mathbf{B}_2 + \left(1 - \delta_1 - \delta_2\right) \mathbf{B}_3\right) \mathbf{u}(t). \tag{4.5}$$

Rewriting this result in matrix form and using the relation  $\delta_2 = (\delta_1 V_{DC})/(NV_O)$ , which can be derived for a flyback converter in discontinuous mode, we obtain

$$\dot{\mathbf{x}}(t) = \begin{pmatrix} 0 & 0 & -\frac{V_{DC}\delta_1}{L_pV_o} & 0 \\ 0 & 0 & \frac{1}{L_f} & -\frac{1}{L_f} \\ \frac{V_{DC}\delta_1}{C_{f1}V_o} & \frac{NV_o - V_i\delta_1}{C_{f1}NV_o} - \frac{V_{DC}\delta_1}{C_{f1}NV_o} & 0 & 0 \\ 0 & \frac{1}{C_{f2}} & 0 & -\frac{1}{C_{f2}R_L} \end{pmatrix} \mathbf{x}(t) + \begin{pmatrix} \frac{\delta_1}{L_p} \\ 0 \\ 0 \\ 0 \end{pmatrix} \mathbf{u}(t).$$

We are now able to create disturbances in the input variables  $V_{DC}$ ,  $\delta_1$  and  $\mathbf{x}$ ,

$$V_{DC} = \bar{v}_{DC} + \tilde{v}_{DC},$$

$$x = \bar{x} + \tilde{x},$$

$$\delta_{1} = \bar{\delta}_{1} + \tilde{\delta}_{1},$$

$$(4.6)$$

in order to derive a steady-state (DC) model and a dynamic (AC) model. Substitution of Eq. (4.6) in Eq. (4.5) results in

$$\dot{\overline{\mathbf{x}}} + \tilde{\mathbf{x}} = \left( \mathbf{A}_{2} \left( \overline{\delta}_{1} + \tilde{\delta}_{1} \right) \frac{\overline{v}_{DC}}{NV_{0}} + \mathbf{A}_{3} \left( 1 - \overline{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{0}} - \tilde{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{0}} \right) \right) \left( \overline{\mathbf{x}} + \tilde{\mathbf{x}} \right) + \mathbf{B}_{1} \left( \overline{\delta}_{1} + \tilde{\delta}_{1} \right) \left( \overline{v}_{DC} + \tilde{v}_{DC} \right).$$

$$(4.7)$$

We are now able to separate Eq. (4.7) in a steady state (DC) model and a dynamic (AC) small signal model. We will first obtain the DC model. If the system is in steady state then the derivative of the state vector  $\mathbf{x}$  is zero. As a consequence and after neglecting the AC terms, (4.7) reduces to

$$\dot{\overline{\mathbf{x}}} = \overline{\mathbf{0}} = \left( \mathbf{A}_2 \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_o} + \mathbf{A}_3 \left( 1 - \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_o} \right) \right) \overline{x} + \mathbf{B}_1 \overline{\delta}_1 \overline{v}_{DC}.$$

Solving for the state vector  $\mathbf{x}$  we obtain the DC model

$$\overline{\mathbf{x}} = - \left( \mathbf{A}_2 \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_a} + \mathbf{A}_3 \left( 1 - \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_a} \right) \right)^{-1} \mathbf{B}_1 \overline{\delta}_1 \overline{v}_{DC}.$$

Substitution of the known component values,  $V_{DC} = 375 \text{V}$  and  $\frac{P_o}{I_o^2} = R_L = 8.125 \Omega$  results in

$$\overline{\mathbf{x}} = \begin{pmatrix} 0.192A \\ 0.8A \\ 6.5V \\ 6.5V \end{pmatrix},$$

which was to be expected.

The AC model is obtained using a similar approach. If we neglect second order terms in (4.7) and drop the DC terms, then (4.7) can be written as

$$\tilde{\mathbf{x}} = \left(\mathbf{A}_{2}\overline{\mathbf{x}}\frac{V_{DC}}{NV_{o}} - \mathbf{A}_{3}\overline{\mathbf{x}}\frac{V_{DC}}{NV_{o}} + \mathbf{B}_{1}\overline{V}_{DC}\right)\tilde{\delta}_{1} + \left(\mathbf{A}_{2}\delta_{1}\frac{V_{DC}}{NV_{o}} + \mathbf{A}_{3} - \mathbf{A}_{3}\overline{\delta}\frac{V_{DC}}{NV_{o}}\right)\tilde{\mathbf{x}} + \mathbf{B}_{1}\overline{\delta}_{1}\tilde{V}_{DC}.$$

$$(4.8)$$

For our own ease we drop the tilde. As an intermediate step towards the derivation of the AC model we apply a Laplace transformation with respect to time. The Laplace transform domain

quantities are indicated by a diacritical hat. For example, the Laplace transform domain counterpart of x is defined as  $\hat{x} = \int_{-\infty}^{\infty} \exp(-st)xdt$ .

As a consequence of the Laplace transformation and the vanishing initial conditions we have  $\partial t \rightarrow s$ . Subjecting Eq. (4.8) to the Laplace transformation results in

$$s\hat{\mathbf{x}} = \left(\mathbf{A}_{2}\overline{\mathbf{x}}\frac{\overline{v}_{DC}}{NV_{o}} - \mathbf{A}_{3}\overline{\mathbf{x}}\frac{\overline{v}_{DC}}{NV_{o}} + \mathbf{B}_{1}\overline{v}_{DC}\right)\hat{\delta}_{1} + \left(\mathbf{A}_{2}\delta_{1}\frac{\overline{v}_{DC}}{NV_{o}} + \mathbf{A}_{3} - \mathbf{A}_{3}\overline{\delta}\frac{\overline{v}_{DC}}{NV_{o}}\right)\hat{\mathbf{x}} + \mathbf{B}_{1}\overline{\delta}_{1}\hat{v}_{DC}.$$

$$(4.9)$$

Solving Eq. (4.9) for the state space vector  $\hat{\mathbf{x}}$  yields

$$\hat{\mathbf{x}} = \left( \mathbf{s} \mathbf{I} - \mathbf{A}_{2} \overline{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{o}} - \mathbf{A}_{3} + \mathbf{A}_{3} \overline{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{o}} \right)^{-1} \left( \mathbf{A}_{2} \overline{\mathbf{x}} \frac{\overline{v}_{DC}}{NV_{o}} - \mathbf{A}_{3} \overline{\mathbf{x}} \frac{\overline{v}_{DC}}{NV_{o}} + \mathbf{B}_{1} \overline{v}_{DC} \right) \hat{\delta}_{1} + \left( \mathbf{s} \mathbf{I} - \mathbf{A}_{2} \overline{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{o}} - \mathbf{A}_{3} + \mathbf{A}_{3} \overline{\delta}_{1} \frac{\overline{v}_{DC}}{NV_{o}} \right)^{-1} B_{1} \overline{\delta}_{1} \hat{v}_{DC}$$

$$(4.10)$$

in which I is the unit matrix. Eq. (4.10) is the AC model in the Laplace s-domain. We are now able to study the behaviour of the power path of the flyback converter in discontinuous mode up till frequencies of one tenth of the switching frequency.

#### 4.2.2 Dynamic (AC) Small Signal Model of the Voltage Regulation Feedback Loop.

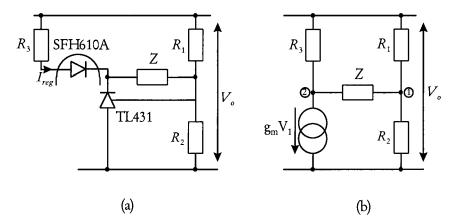

The voltage feedback circuitry including it's small signal equivalent is depicted in Fig. (4.3).

Fig. (4.3) Voltage feedback circuitry and it's small signal equivalent.

We will now apply Kirchhoff's current law on the marked nodes  $\mathbb O$  and  $\mathbb O$  to obtain the transfer function  $\frac{i_{\rm eg}(s)}{\tilde{v}_o(s)}$ . Solving for the opto-coupler led current as a consequence of the voltage  $V_o$  results

$$I_{reg} = \frac{g_{m}ZR_{2} + g_{m}R_{1}R_{2} + R_{1}}{Z(R_{1} + R_{2}) + g_{m}R_{1}R_{2}R_{3} + R_{1}R_{2} + R_{1}R_{3} + R_{2}R_{3}}V_{o},$$

in which  $g_m = 1.1 \mathrm{AV}^{-1}$ , according the data sheets of the TL431. Substituting a capacitor for the complex impedance Z leads to a led current

in

$$I_{reg}(s) = \frac{sC(g_m R_1 R_2 + R_1) + R_2 g_m}{sC(g_m R_1 R_2 R_3 + R_1 R_2 + R_1 R_3 + R_2 R_3) + R_1 + R_2} V_o.$$

(4.11)

Because of the absence of any DC-component in this transfer function we have for the AC-model

$$\frac{i_{reg}(s)}{\tilde{v}_o(s)} = \frac{sC(g_m R_1 R_2 + R_1) + R_2 g_m}{sC(g_m R_1 R_2 R_3 + R_1 R_2 + R_1 R_3 + R_2 R_3) + R_1 + R_2},$$

with resulting pole and zero,

$$n = -\frac{R_2 g_m}{C(g_m R_1 R_2 + R_1)},$$

$$p = -\frac{R_1 + R_2}{C(R_1 R_2 R_3 + R_1 R_2 + R_1 R_3 + R_2 R_3)},$$

and DC-gain

$$K_{DC} = \frac{R_2 g_m}{R_1 + R_2} \ .$$

For the component choice we have to take the parallel RC network attached to the comp pin in consideration. See Appendix C for the circuit diagram (components 3301 and 2302). The transfer function is

$$\frac{V_{comp}}{I_{reg}} = \frac{R_c}{sR_cC_c + 1},$$

with resulting pole

$$p = -\frac{1}{R_c C_c}.$$

Obtaining an overall low pass characteristic results in

$$\frac{R_{2}g_{m}}{C(g_{m}R_{1}R_{2}+R_{1})} = \frac{1}{R_{c}C_{c}},$$

$$R_{c} = \frac{g_{m}R_{1}R_{2}+R_{1}}{R_{2}g_{m}} = 16k\Omega, \quad \text{if } C_{c} = C.$$

The overall system pole is chosen as low as possible, because the switching frequency of this converter can decrease to  $29.38 \, \text{kHz}$ .  $C = 100 \, \text{nF}$  results in a cut-off frequency of  $2.56 \, \text{Hz}$ .

### 4.2.3 Dynamic (AC) Small Signal Model of the Current Regulation Feedback Loop.

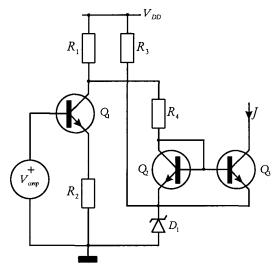

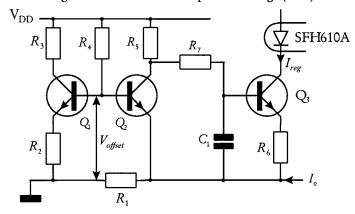

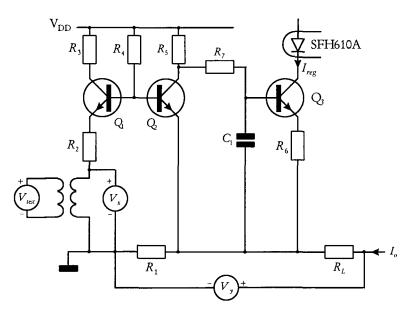

The circuit used for current regulation feedback is depicted in Fig. (4.4).

Fig. (4.4) Current control circuitry

We will derive  $I_{mg}$  as function of  $I_o$ . For this circuit we can derive the next set of equations

Substitution of these equations results in

$$I_{rg}(s) = \frac{S_{Q_1} V_{DD} - V_{offset} S_{Q_2} S_{Q_1} R_5}{1 + s R_7 C_1} + I_o \frac{S_{Q_2} S_{Q_3} R_5 R_1}{1 + s R_7 C_1}.$$

(4.12)

Creating disturbances in  $I_o = \bar{i}_o + \hat{i}_o$  and drop the DC-terms in Eq. (4.12) results in the AC-model of the current control circuitry

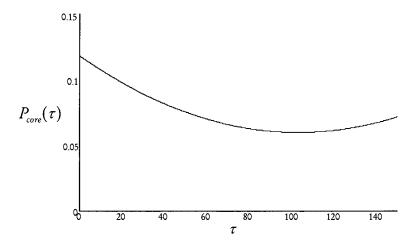

$$\tilde{i}_{reg}(s) = \tilde{i}_0 \frac{S_{Q_0} S_{Q_0} R_5 R_1}{1 + s R_7 C_1},$$

(4.13)

with pole

$$p = -\frac{1}{R_2 C_1}.$$

Choosing  $R_7 = 100 \text{k}\Omega$  and  $C_1 = 100 \text{nF}$  results in a cut-off frequency of 15.92Hz.

#### 4.3 Simulations

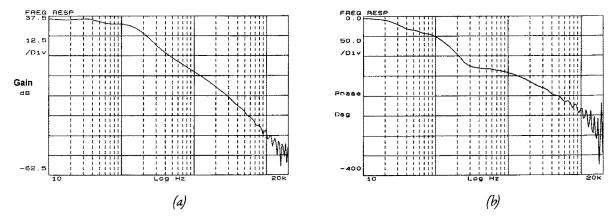

#### 4.3.1 Simulations of the Voltage Regulation Feedback Loop.

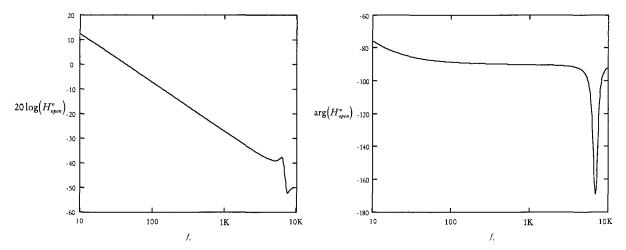

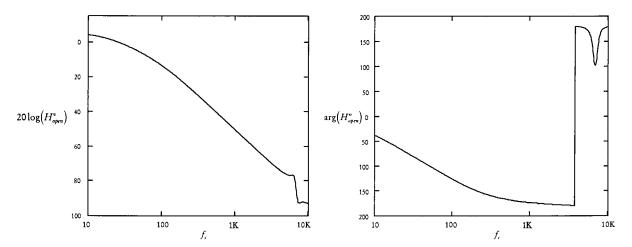

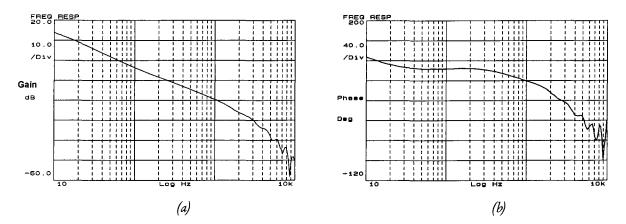

We will now calculate the Bode and phase plots of the transfer function, derived in Section (4.2), using the mathematical package Mathcad. Since we are using a DC power supply we have no disturbances in the input voltage resulting in  $\hat{v}_{DC} = 0\text{V}$ . Therefore the state space vector of Eq. (4.10) changes to

$$\hat{\mathbf{x}} = \left( s\mathbf{I} - \mathbf{A}_2 \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_o} - \mathbf{A}_3 + \mathbf{A}_3 \overline{\delta}_1 \frac{\overline{v}_{DC}}{NV_o} \right)^{-1} \left( \mathbf{A}_2 \overline{\mathbf{x}} \frac{\overline{v}_{DC}}{NV_o} - \mathbf{A}_3 \overline{\mathbf{x}} \frac{\overline{v}_{DC}}{NV_o} + \mathbf{B}_1 \overline{v}_{DC} \right) \hat{\delta}, \quad (4.14)$$

creating a relationship between disturbances in the output voltage, the last element of the state vector, and disturbances in the primary duty cycle,  $G_0(s) = \hat{\mathbf{x}}(s)/\hat{\delta}(s)$ . Rewriting (4.11) results in the transfer function  $G_1(s) = \hat{i}_{reg}(s)/\hat{v}_o(s)$ . For the voltage at the comp pin of the VIPer20, we can write

$$\hat{v}_{comp}(s) = \hat{i}_{reg}(s) \cdot CTR \cdot \frac{R_c}{sR_cC_c + 1},$$

resulting in the transfer function

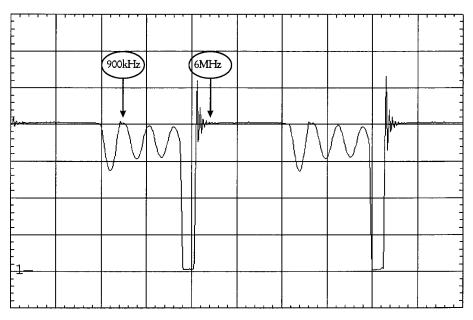

$$G_2(s) = \frac{\hat{v}_{comp}(s)}{\hat{i}_{reg}(s)} = CTR \cdot \frac{R_c}{sR_cC_c + 1},$$