| MASTER                                                          |  |

|-----------------------------------------------------------------|--|

| Parallel code generation for non-preemptively scheduled systems |  |

|                                                                 |  |

| John, S.                                                        |  |

| Award date:<br>2012                                             |  |

|                                                                 |  |

| Link to publication                                             |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

ELECTRONIC SYSTEMS, DEPARTMENT OF ELECTRICAL ENGINEERING

### Master's Thesis

## Parallel Code Generation for Non-Preemptively Scheduled Multiprocessor Systems

Author: Sunil John 0755704 Supervisors:

Prof. Dr. Henk Corporaal Prof. Dr. ir. Marco Bekooij

ir. Stefan Geuns

### **Abstract**

Streaming applications often have real-time constraints like throughput. In order to meet these real-time constraints, task-level parallelism is exploited. However, manual partitioning of sequential code to parallel tasks is time-consuming and error prone. Therefore it is beneficial to automatically generate parallel code from a sequential description of the application, while guaranteeing the same functional behavior. The automatic parallelization tool Omphale, extracts a parallel task graph from a sequential nested loop program, which can then be executed on a multiprocessor platform. Non-preemptive scheduling is beneficial as it enables fast context-switching, and is essential in processors that do not support preemption. In this thesis, we introduce techniques in Omphale to generate code for a shared-memory multiprocessor platform, which uses non-preemptive scheduling and a communication library with buffers supporting only a single producer and consumer.

Streaming applications often contain if or switch statements. These statements can contain multiple assignment statements in different branches, writing to the same variable. After parallelization, such a variable corresponds to a buffer having multiple producers. Also, certain variables can be read multiple times. These variables correspond to buffers having multiple consumers. A method to transform such buffers having multiple producers and consumers, to buffers with only a single producer and consumer is introduced. Streaming applications can also contain arrays wherein the different elements in an array are read and written in a different order. The order in which a producer task writes data into a circular buffer, may not be the order in which the consumer task reads data from the buffer. This leads to a reordering problem. A modified sliding windows approach is presented to solve this issue, when only buffers with a single producer and consumer are supported.

In order to prevent race conditions between tasks and deadlock, synchronization is done by means of acquire and release statements. The acquire statements are blocking whereas the release statements are non-blocking. Acquire statements check for availability of space or data in a buffer. When a blocking acquire call in a task fails due to lack of space or data, it must return control back to the non-preemptive scheduler. On the next execution of this task, it begins execution from the first statement in the task and not at the point at which it was blocked. This happens because the state of the task is not saved. It is shown that not saving the state of the task, can lead to erroneous functional behavior of the application and even a deadlock. Therefore, this thesis also introduces a method to save the state of the task by means of a finite state machine (FSM). Automatic parallelization approaches presented in literature, have not yet addressed these issues, when generating code for

multiprocessor systems using non-preemptive schedulers and blocking synchronization statements.

If variables are accessed across states in a FSM, they are stored statically in the task-state. This prevents the value from being lost, when control is returned to the scheduler on a blocking acquire call. Such variables potentially increase the memory usage, which is limited in an embedded system. The presence of a large number of states in the FSM leads to an increase in code size, and may lead to a decrease in throughput. Optimization techniques to reduce the number of states and the size of the task-state are developed. In order to reduce the number of states and task-state, acquire statements are moved or combined. Fine-grained synchronization on circular buffers can lead to a high synchronization overhead. By reordering the acquire calls in a task, the synchronization overhead in acquiring data in a buffer can be reduced. An attempt at a formal proof, showing that these transformations involving moving acquire statements over release statements or non-synchronization statements, and reordering acquires preserves deadlock-freedom, is presented.

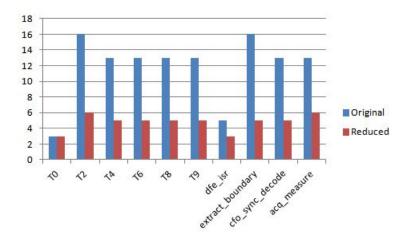

A Digital Video Broadcast - Terrestrial (DVB-T) Decoder is used as a case-study. Parallel tasks are extracted from a sequential description of a DVB-T decoder. These parallel tasks are executed on the NXP MARS multiprocessor platform. By moving acquire calls, the number of states in the tasks of the DVB-T decoder are reduced by 60%. The size of the task-state is reduced by moving or combining acquires. The number of synchronization statements acquiring data in buffers is reduced by 30% by reordering the acquire calls in tasks.

### **Acknowledgements**

I would like to express my gratitude for the people who offered me guidance and support during the course of my graduation project at NXP Semiconductors. Firstly, I wish to thank my supervisors, Prof.Henk Corporaal and Prof.Marco Bekooij for their guidance and constructive recommendations during the course of this project.

Prof. Henk Corporaal was my supervisor at Eindhoven University of Technology. He motivated me to think of alternate approaches at solving the various sub-problems in the project. I appreciate his valuable feedback to improve my presentations.

Prof. Marco Bekooij was my supervisor at NXP Semiconductors. I am grateful to him for offering the opportunity to work on this project. I would like to express my appreciation for the valuable time that he spent patiently, in explaining concepts and clarifying doubts. His insights in the subject played a role in guiding me towards interesting problems related to my project, that could be addressed.

I thank Dr. Pieter Cuijpers, for showing interest in my project and being part of the assessment committee.

I am deeply grateful to Stefan Geuns, who was also my supervisor at NXP Semiconductors. I appreciate the valuable feedback that he gave for this thesis, which has helped improve its quality. I thank him for all the guidance that he provided through the course of the project. I also wish to thank Joost Hausmans for his valuable time and efforts in clarifying doubts regarding related topics.

I wish to acknowledge the various suggestions provided by Umar Waqas during the course of the project and also for the thesis. I appreciate Sohan Walimbe for the inputs he provided during our discussions. I wish to thank my friends Siddharth Chunduri and Bhargava Puvvula for their help in proof-reading parts of the thesis. I am grateful to my friends from church, Jubin Jacob and Jonathan Vasu for their help and encouragement. Last, but not the least, I thank my parents and grandparents for their love and support. Above all, I thank and praise God Almighty, for His sustained grace and mercy, during the course of this project and in my life.

# Contents

| 1 | Intr | roduction                                     | 1  |

|---|------|-----------------------------------------------|----|

|   | 1.1  | Streaming Applications                        | 1  |

|   | 1.2  | Architecture                                  | 3  |

|   | 1.3  | Automatic Parallelization                     | 3  |

|   | 1.4  | Problem Statement                             | 4  |

|   | 1.5  | Contributions                                 | 5  |

|   | 1.6  | Outline                                       | 6  |

| 2 | Om   | phale                                         | 7  |

|   | 2.1  | Motivation                                    | 7  |

|   | 2.2  | Tool Flow                                     | 8  |

|   |      | 2.2.1 Parallelization                         | 8  |

|   | 2.3  | Scope                                         | 10 |

| 3 | Tar  | get Platform                                  | 13 |

|   | 3.1  | Architecture                                  | 13 |

|   | 3.2  | Communication/Scheduling Infrastructure       | 14 |

|   |      | 3.2.1 Components                              | 15 |

| 4 | Pro  | blem Description                              | 17 |

|   | 4.1  | Inter-task communication via circular buffers | 17 |

|   |      | 4.1.1 Reordering Problem                      | 18 |

|   |      | 4.1.2 Multiple Producers                      | 18 |

|   |      | 4.1.3 Multiple Consumers                      | 19 |

|   | 4.2  | Non-Preemptive Scheduling                     | 20 |

| 5 | Inte | er-Task Communication via Circular Buffers    | 23 |

|   | 5.1  | Reordering Problem                            | 23 |

|   |      | 5.1.1 Related Work                            | 23 |

| CONTENTS | CONTENTS |

|----------|----------|

|          |          |

| Bi | bliog | raphy         |                                                   | <b>7</b> 5 |  |

|----|-------|---------------|---------------------------------------------------|------------|--|

| 9  | Con   | clusion       | 1                                                 | 71         |  |

| 8  | Case  | e Stud        | y                                                 | 63         |  |

|    |       | 7.3.1         | Reordering Acquires                               | 58         |  |

|    | 7.3   |               | ing Synchronization Overhead                      | 57         |  |

|    | 7.2   |               | ing Task-State                                    | 56         |  |

|    | 7.0   | 7.1.2         | Combining Acquires                                | 49         |  |

|    |       | 7.1.1         | Moving Acquire/Release outside if-else statements | 47         |  |

|    | 7.1   |               | tion of States in FSM of tasks                    | 47         |  |

| 7  | -     | Optimizations |                                                   |            |  |

|    | 6.8   |               | l If-Else Statements                              | 43         |  |

|    | 6.7   |               | Statement                                         | 41         |  |

|    | 6.6   | _             | ment Statement                                    | 41         |  |

|    | 6.5   |               | on Statement                                      | 41         |  |

|    | 6.4   |               | op                                                | 40         |  |

|    | 6.3   |               | While Loop                                        | 39         |  |

|    | 6.2   |               | sional While Loop                                 | 38         |  |

|    | 6.1   |               | e While Loop                                      | 37         |  |

| 6  |       |               | mptive Scheduling                                 | 35         |  |

|    |       | 5.3.3         | Implementation in Omphale                         | 33         |  |

|    |       | 5.3.2         | Proposed Solution                                 | 33         |  |

|    |       | 5.3.1         | Related Work                                      | 32         |  |

|    | 5.3   | •             | lle Consumers                                     | 32         |  |

|    |       | 5.2.3         | Implementation in Omphale                         | 31         |  |

|    |       | 5.2.2         | Proposed Solution                                 | 29         |  |

|    |       | 5.2.1         | Related Work                                      | 28         |  |

|    | 5.2   | Multip        | le Producers                                      | 27         |  |

|    |       | 5.1.2         | Proposed Solution                                 | 25         |  |

|    |       |               |                                                   |            |  |

## Chapter 1

### Introduction

In recent years, there has been a surge of embedded applications that employ digital signal processing. These range from miniature wireless sensors, cellular phones, to rockets being sent to space. A notable property of these applications is that they are centered around streams of data; involving real-time acquisition, processing and subsequent output of data. These applications are commonly referred to as streaming applications, which is the application domain under consideration in this work. This thesis is concerned with enhancement of the scope of the multiprocessor compiler, Omphale. It performs automatic parallelization of a sequential description of a real-time streaming application such that it can be executed on an embedded multiprocessor system. Omphale currently supports kernels with preemptive scheduling and a communication library which supports buffers with multiple producers and consumers.

In this thesis, the scope of Omphale is enhanced to target commercial kernels employing non-preemptive scheduling and buffers with only a single producer and consumer. The following section describes streaming applications in more detail. Section 1.2 describes an architecture onto which such streaming applications are mapped. Section 1.3 presents the motivation for automatic parallelization and how it is applicable to this work. Section 1.4 gives a brief description of the problems addressed in this thesis. Section 1.6 gives an overview of the remaining chapters in this thesis.

### 1.1 Streaming Applications

Streaming applications are characterized by an infinite stream of input data [1]. They can be found on embedded devices, desktops and servers with high computing power. They are applicable in the domains of digital signal processing, networking, encryption etc. More specifically, they are used in wireless baseband processing (DVB-T, DAB, DRM), medical image processing, sensor processing and phased array radar systems [2]. In the remainder of this thesis, references to streaming applications and stream processing applications are used interchangeably.

Streaming applications have certain properties [2] which characterize their behavior. They perform relatively simple local processing of a large amount of data. So usually, the energy costs for data communication dominate the energy cost of processing. Data arrives at the incoming nodes at a fixed rate. The communication bandwidth is application dependent and so a large variety in communication bandwidth is required. The size of the data items and the data rates are also application dependent.

Streaming applications exhibit input-data dependent behavior. They can contain ifstatements or while-loops where the condition depends upon input data values from the stream. Also, the result of an index-expression used to access array elements may depend upon input data values. At compile time, the value of such a condition or index-expression cannot be evaluated. Such statements are referred to as *non-manifest* [3] statements.

These applications usually have strict real-time constraints such as throughput and end-to-end latency which have to be met. In addition, embedded devices have concerns like minimizing energy consumption to increase their battery life. Since the memory available on such devices is limited, the architecture on which such streaming applications are mapped, should be capable of handling these concerns.

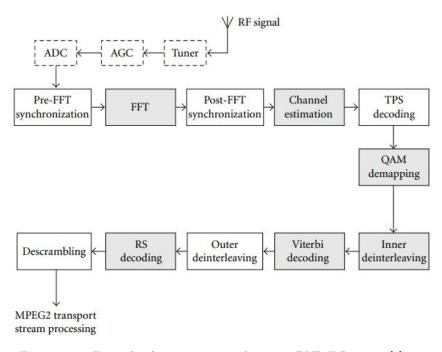

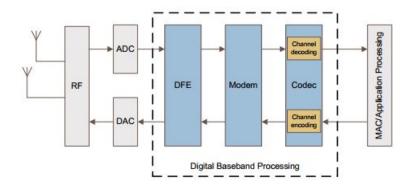

A block diagram of a streaming application, namely a Digital Video Broadcast - Terrestrial (DVB-T) receiver, can be seen in Figure 1.1. As can be seen, a stream of data (RF signal) is obtained from an external source such as a wireless receiver. In each stage, the data items are processed for a limited amount of time. The independent processing stages can be executed on multiple processors in parallel.

Figure 1.1: Example of a streaming application - DVB-T Receiver [4]

#### 1.2 Architecture

A streaming application needs to be mapped on to a suitable architecture which can satisfy its performance requirements. This section describes an architecture which can meet these requirements. In order to meet the high throughput requirements of these applications on a single processor, it has to be clocked at a high frequency. However, this leads to high energy consumption, resulting in a low battery life. An alternative is to increase the number of processors, and reduce the frequency, thereby obtaining the same performance at a lower energy consumption. This has led to the use of multiprocessors in modern day systems. Most of the processor vendors are now moving towards multiprocessors [5]. As scaling technologies have improved, it facilitates the integration of multiprocessors on a single silicon chip, known as a Multiprocessor System-on-Chip (MPSoC). This aids in reducing the chip area. Most embedded systems have requirements of high computational power and low power consumption, which can be met efficiently by using MPSoCs. They are widely used in networking, communications, signal processing and multimedia applications [6]. At NXP, such an MPSoC namely, Multi Application Radio System (MARS) has been developed, targeting Software Defined Radio (SDR) applications. It has been chosen as the target platform to be used in this work. The MARS MPSoC has been described in detail in Chapter 3.

The tasks running on an MPSoC have to be scheduled for execution on the multiple processors. Non-preemptive scheduling is beneficial as it enables fast context-switching as compared to preemptive schedulers. It is essential if the processors do not support preemption. It is desired that our automatic parallelization tool Omphale, is able to support non-preemptive scheduling. Therefore, we consider an architecture which employs non-preemptive scheduling.

An MPSoC has a lot of potential in terms of the parallel processing that it can offer. However, in order to utilize it efficiently, the application has to be parallelized. This means that the following issues have to be solved to map the application on the available resources [7],

- 1. Dividing a program consisting of a single task into one with multiple balanced and communicating tasks. This process should also take the properties of the target platform into account.

- Managing inter-task communication and synchronization. This needs to be considered carefully in order to avoid serialization of the parallel program and the occurrence of race conditions. Furthermore, it can introduce the risk of deadlocks.

Solving these issues manually is a time-consuming, labor-intensive and error-prone process. Therefore it is beneficial to address these issues through automatic parallelization.

### 1.3 Automatic Parallelization

Automatic parallelization involves automated partitioning of a sequential application to parallel tasks. This section motivates the need for automatic parallelization and how it is beneficial to include it in a multiprocessor compiler. A multiprocessor compiler

creates an executable of an application, which can be executed on a multiprocessor system. It maps parallel tasks onto the processors of the MPSoC in such a way that the temporal requirements of the application are met. It also ensures that inter-task communication and synchronization are handled correctly.

As described in section 1.1, streaming applications exhibit stages while processing the streaming data. This renders them a suitable candidate for function or task-level parallelism (TLP). These applications are usually described in sequential programming languages such as C and C++. In order to execute such an application on an MPSoC, it has to be partitioned into tasks that can run in parallel on the MPSoC.

A multiprocessor compiler maps the parallel tasks onto different processors of an MPSoC. It could obtain the parallel partitioned tasks of the application as input or obtain a sequential description of the application and perform the partitioning itself. If the partitioned tasks are obtained as input, it is difficult to guarantee deadlock freedom. In this case, the process of partitioning and inserting appropriate communication and synchronization statements would have been done manually by the system designer or application developer. In this approach, it is also possible to do optimizations manually and exploit the architecture available. Also, the granularity of the tasks can be decided in an optimized manner [3]. These optimizations require the system designer or application developer to have a thorough understanding of the application. The downside of this approach is that it is time-consuming and error-prone. Thereby, it will increase the time-to-market of the application.

On the other hand, if a sequential description is taken as an input, the partitioning of tasks can be done by the compiler. By starting with a sequential description of the application, the advantage is that it is deadlock-free, deterministic and free of race conditions. The input description of the application should be in a manner that the data dependencies in the application are analyzable [3]. This would enable the partitioning of the application into parallel tasks. Also, the inter-task communication and synchronization statements can be inserted automatically by the compiler, such that there is no deadlock. Deadlock-freedom can be checked if the multiprocessor compiler is able to generate a suitable model of the input application which supports this check. This also enables temporal analysis of the application for throughput requirements.

The multiprocessor compiler Omphale, is a research tool currently under development by PhD students at NXP. Given a sequential description of a streaming application, it carries out automatic parallelization, generates an analysis model and produces an executable for a target multiprocessor system. The aim of this work is to enhance the scope of Omphale to be able to target a wider class of multiprocessor systems with non-preemptive scheduling and communication libraries having buffers with only a single producer and consumer. This is further discussed in the next section.

### 1.4 Problem Statement

The problems addressed in this thesis are described briefly in this section. A detailed problem description is given in Chapter 4.

The automatic parallelization tool Omphale generates parallel code for a multiprocessor system, from a sequential description of a streaming application. However, it currently supports multiprocessor systems with only preemptive schedulers and a communication library built in-house, with buffers supporting

multiple producers and multiple consumers. It is desired that Omphale can target the NXP MARS multiprocessor platform. The problem is that MARS uses a non-preemptive scheduler and a communication library having buffers, with only a single producer and consumer, which are not supported by Omphale. Each of these sub-problems is described briefly in the following paragraphs.

Non-preemptive scheduling is beneficial as it enables fast context-switching in comparison to preemptive schedulers. It is essential if the processors do not support preemption. However, Omphale does not support non-preemptive schedulers. When a non-preemptive scheduler is used and a task blocks due to a blocking synchronization call, it must return control back to the scheduler to prevent indefinite blocking and allow other tasks to execute. When the task executes again, it starts from the beginning of the task and not at the point, where it had yielded control back to the scheduler. This could lead to erroneous functional behavior of the application and even deadlock.

The sequential description of a streaming application taken as input by Omphale, can contain multiple assignment statements writing to a single variable. It can also contain multiple statements reading from a variable. These would correspond to buffers with multiple producers and consumers. However, the communication library used on MARS does not support such buffers. It only supports buffers with a single producer and consumer. Omphale is unable to handle such input applications to generate code for multiprocessor systems, which use a communication library with buffers having only a single producer and consumer.

### 1.5 Contributions

This project aims at augmenting the usability of the multiprocessor compiler Omphale, to target multiprocessor systems utilizing communication and scheduling frameworks with certain properties. These properties include the use of circular buffers having only a single producer and consumer and non-preemptive scheduling. The Multi Application Radio System (MARS) MPSoC, developed at NXP, is the chosen target platform which utilizes such a communication and scheduling framework. The contributions of this thesis are as follows.

- Developed a wrapper synchronization library, containing a modified sliding windows buffer implementation, to handle circular buffers with producers and consumers having different access patterns in an array.

- Developed methods in Omphale to transform circular buffers with multiple producers and consumers to buffers with only a single producer and consumer

- Developed a mechanism to save the state of the task in non-preemptively scheduled multiprocessor systems, to prevent erroneous functional behavior of an application when using blocking synchronization statements

- Proposed optimizations to reduce the number of states in the generated FSMs in tasks, the size of the task-state and the number of synchronization statements.

- Implemented the proposed solutions in Omphale, and evaluated them on the MARS multiprocessor platform using DVB-T decoder as a case-study.

### 1.6 Outline

An outline of the remainder of the thesis is presented in this section. Chapter 2 describes the tool flow used in Omphale, starting from a sequential description of a streaming application, and obtaining an executable as an output. Chapter 3 highlights the features of the NXP MARS MPSoC which is used as the target platform. Chapter 4 presents a detailed problem description. Chapter 5 describes the proposed solutions to the issues concerned with inter-task communication via circular buffers. These issues include the reordering problem and the handling of buffers with multiple producers and multiple consumers. In Chapter 6, the problem of explicit state management for tasks when using non-preemptive scheduling and means of solving it are discussed. In Chapter 7, optimizations are proposed to reduce the static memory requirements in tasks and improve the performance of streaming applications on a target architecture. A case-study which illustrates the use of the proposed solutions is presented in Chapter 8. Finally, Chapter 9 concludes the thesis and presents future work.

## Chapter 2

## **Omphale**

A multiprocessor compiler takes a streaming application as input and produces an executable which can run on a multiprocessor system. In this chapter, the multiprocessor compiler Omphale is described in detail. Omphale, currently under development at NXP, takes a sequential description of a streaming application along with its real-time constraints such as throughput and produces an executable that can be executed on a target multiprocessor system. The advantages of starting with a sequential description of the streaming application have been highlighted in section 1.3. The various phases that are followed in transforming a sequential streaming application to a parallel task graph, which is executable on a multiprocessor system, are described in this chapter.

### 2.1 Motivation

This section provides the motivation for using Omphale over other multiprocessor compilers. By starting with a sequential description of a streaming application, it relieves the programmer of the burden of manual insertion of communication and synchronization statements in the parallel tasks. The semantics of Omphale Input Language (OIL) are such that the data dependencies can be extracted [3]. Omphale also supports non-manifest statements in the NLP, which correspond to input-data dependent behavior. A parallel task graph can be extracted by analyzing the data dependencies. A task graph comprises of a dependency graph with inter-task communication and synchronization statements inserted into the tasks. A dataflow model is extracted from the input streaming application such that temporal requirements can be analyzed. Thereby, on providing the temporal requirements of the application as input, sufficient buffer capacities can be computed if the temporal requirements can be met.

Omphale 2.2. Tool Flow

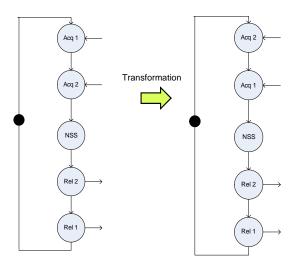

#### 2.2 Tool Flow

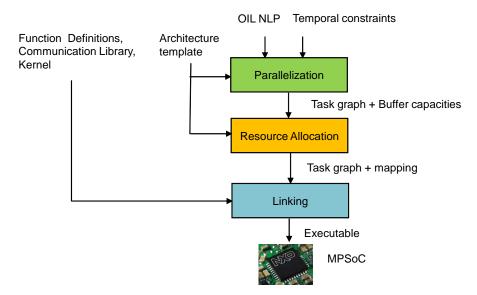

Omphale takes a sequential description of a streaming application as input. This is expressed as a nested loop program (NLP) in OIL. The temporal constraints of the application are also provided as input along with the NLP using OIL. The compiler operates on these inputs and produces an executable targeting a multiprocessor system as an output. This process is carried out in three phases [3], as shown in Figure 2.1. In the parallelization phase, the data dependencies in the input NLP are analyzed to create a parallel task graph. A dataflow model, corresponding to this task graph is extracted in this phase. This dataflow model is used to calculate sufficient buffer capacities such that the temporal requirements of the application are met [8]. Following this, the resource allocation phase assigns the parallel tasks to processors. Buffers are then allocated in memory according to the buffer sizes obtained from the parallelization phase. In the linking phase, the parallel tasks are linked with the communication library and the kernel. In the following subsection, a detailed description of the parallelization phase is furnished.

Figure 2.1: Omphale Tool Flow

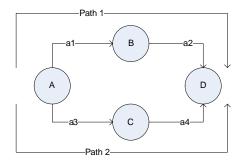

### 2.2.1 Parallelization

In the parallelization phase, a task graph along with its corresponding Cyclo-static Synchronous Dataflow (CSDF) graph are extracted from the input NLP. This process is carried out in three sub-phases [3]. In the first sub-phase, a dependency graph is extracted from the input NLP, highlighting the data dependencies between tasks. Then inter-task communication and synchronization statements are inserted into the tasks, thereby forming a task graph in the second sub-phase. Subsequently, based on the inserted synchronization statements, a CSDF model is extracted in the third sub-phase. The first sub-phase is described in more detail. For more details about the other sub-phases, the reader is referred to [3].

Omphale 2.2. Tool Flow

#### 2.2.1.1 Extraction of Dependency Graph

The extraction of a dependency graph requires the identification of tasks that can be executed in parallel. The assignment statements and function calls in the input NLP are made into parallel tasks. In case of sequential execution, the order of execution of the statements in the NLP guarantees functional correctness. After parallelization, the dependencies have to be maintained, to guarantee the same functional behavior as the sequential application. The data dependencies can be found if the statements in the NLP satisfy single assignment (SA) [9].

Single Assignment Single assignment means that a scalar or a element in an array is written only once. There are two forms of single assignment, static single assignment (SSA) and dynamic single assignment (DSA). SSA [10] requires that there is at most one statement that writes to a scalar or array. DSA requires that a scalar or an element of an array is written only once during the entire execution of a program [11]. A program that satisfies SSA need not satisfy DSA or vice-versa.

For while loops with an unknown iteration bound, both SSA and DSA may not be satisfied [12]. SSA requires that a variable is written only once. However, in streaming applications, there can be several writes to the same variable in the branches of an if statement or a switch statement. Therefore, SSA is not satisfied. In different iterations of a while loop, a variable may be written more than once. Therefore DSA is not satisfied. If automatic renaming is done, and a corresponding array is made to store the values of every iteration, it would require an array of infinite size. Hence a new form of single assignment, namely single assignment section (SAS) [12] is introduced. During the execution of a SAS, each scalar and array element can be written at most once. In the NLP, multiple SASs may exist and each scalar or array can have multiple SASs. At the end of a SAS, the value of the variable in the SAS is lost. The reader is referred to [13] for further description about SASs.

Omphale Input Language (OIL) In order to extract a dependency graph, the data dependencies in the input NLP must be analyzed. To analyze the data dependencies, the input language OIL requires that they must be made explicit. Therefore OIL does not support pointers. An NLP expressed in OIL must also satisfy the notion of single assignment specified by SAS. For the first iteration of a while loop, the SAS also includes the statements prior to the loop in the NLP.

OIL permits the use of external C-functions thereby enabling re-use of existing function implementations. The requirement is that these C-functions should be side-effect free [3]. This implies that the functions do not have any implicit data dependencies. OIL supports the use of the following statements in a NLP, namely assignments, functions, if-else, while loops and for-loops. It also supports non-manifest if statements and while loops. For the examples shown in this thesis, the symbol '~' is used to represent code that has been omitted for clarity. It also includes code that is non-manifest.

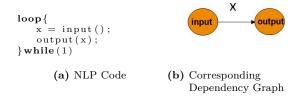

An example of the extraction of a dependency graph is shown in Figure 2.2. An example NLP is shown in Figure 2.2a, where a variable x is the data dependency between two functions *input* and *output*. In the corresponding dependency graph in Figure 2.2b, it is illustrated how assignment statements and function calls become tasks, sharing the data dependency.

After a dependency graph has been extracted, inter-task communication and

Figure 2.2: Extraction of Dependency Graph

synchronization statements have to be inserted into the tasks. Here the shared variables (data dependencies) between tasks are replaced by circular buffers. Figure 2.3c shows the task graph corresponding to the dependency graph in Figure 2.2. Here, the variable x has been replaced by a circular buffer. The inter-task communication and synchronization statements for the input and output tasks are inserted as shown in Figure 2.3a and Figure 2.3b respectively. The communication statements pertain to obtaining a reference to the circular buffer using getWriteAddressCB and writing to it. The synchronization statements acquireSpace and acquireData are used to check the availability of space and data respectively in the buffer. Similarly releaseData indicates that the data has been written to and is available for reading, and releaseSpace indicates that data has been read and is now available for writing.

```

int *xWrite;

int *xRead;

CB *xCB;

CB *xCB;

xCB = openCB(CBNumber);

xCB = openCB(CBNumber);

acquireSpace(xCB);

acquireData(xCB);

xWrite = getWriteAddress(xCB); xRead = getReadAddress(xCB);

*xWrite = input();

output (*xRead);

releaseData(xCB);

releaseSpace(xCB);

(a) Task_input

(b) Task_output

(c) Task Graph

```

Figure 2.3: Extraction of Task Graph

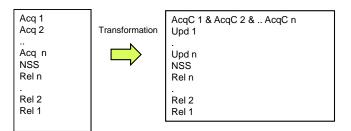

An example of a channel decoding application and its corresponding task graph are shown in Figure 2.4. From the NLP code in Figure 2.4a, it can be seen that the application can either be in the acquisition (acq) phase or the decoding phase depending on the variable state. The decode phase can have several stages forming a pipeline, as shown by the functions decode1, decode2 and output. The keyword out is used to represent the output of a function. In this example,  $out\ state$  refers to a write to the variable state in the next iteration of the while loop. From Figure 2.4a, it can be seen that circular buffers can have multiple producers and multiple consumers. The buffer s has multiple consumers and the buffer s has multiple producers and consumers. The fact that multiple producers are mutually exclusive is no longer visible in the task graph, but can only be seen in the input NLP.

### 2.3 Scope

In the multiprocessor platforms that Omphale currently supports, the communication library and the kernel have been developed in-house for the target platform. In being

```

state = 0;

loop{

x = input();

switch(state){

case 0 : {

acq (x, out state');

}

case 1: {

y = decode1(x, out state');

z = decode2(y);

output(z);

}

} while (1)

(a) NLP Code

(b) Task Graph

```

Figure 2.4: Extraction of Task Graph

able to use commercial kernels and communication libraries, a wrapper has to be generated around the commercial communication library so as to support the required communication and synchronization behavior. Such a wrapper generation is essential in the work carried out in this project. The kernels supported currently by Omphale are developed in-house and they use preemptive schedulers such as Time Division Multiplexing (TDM) schedulers, which belong to the category of budget schedulers. Budget schedulers provide tasks with a minimum budget for every shared resource such that real-time guarantees can be given.

## Chapter 3

## Target Platform

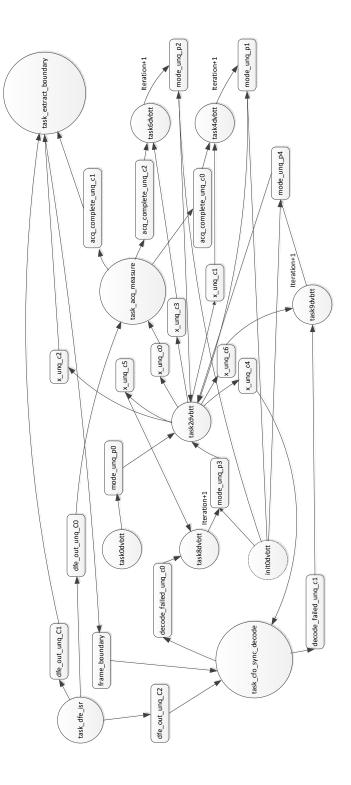

The Multi Application Radio System(MARS) MPSoC, developed at NXP, is the target platform used in this work. It uses the Sea-of-DSP (SoD) infrastructure which has a streaming kernel with non-preemptive scheduling. The communication library offered by SoD supports only buffers with a single producer and consumer. MARS facilitates the implementation of software defined radios (SDR).

#### Software Defined Radio

A software-defined radio system, or SDR, is a radio communication system where components that have been typically implemented in hardware like mixers, filters, amplifiers, modem and detectors are instead implemented by means of software on a personal computer or embedded system [14].

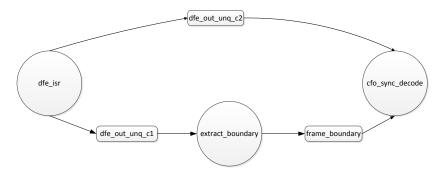

The processing stages in a typical SDR transceiver [15] are shown in Figure 3.1. In the case of an SDR receiver, the first stage is the RF block. The incoming signal is sampled by an analog-to-digital (ADC) converter. The digitized signal is passed to the baseband processing section which consists of the digital front end (DFE), Modem and Codec blocks. The output from this section is passed to the application layer for further processing. The digital front-end consists of filters that are used to remove the unwanted frequencies and suppress the noise present in the signal. The modem block performs the demodulation followed by decoding, which is done by the codec block. In the case of a transmitter, the data flows in the reverse direction starting from the application layer towards the transmitter RF block.

#### 3.1 Architecture

MARS facilitates the implementation of SDRs. The architecture of the MARS platform is shown in Figure 3.2. It consists of a Digital Front End (DFE) which receives the data provided by the transmitter. There are two Vector Digital Signal Processors (VDSPs) which execute the filtering and demodulation operations in the baseband processing. A

Figure 3.1: SDR Transceiver [16]

hardware accelerator, FLORA implements the decoding functions. In order to configure the VDSPs and the FLORA , a general purpose processor namely the ARM is used. There are two Static random access memories (SRAMs) to store data. An external SDRAM is also present in case storage space is not sufficient in the other memories. The various processors and memories in the MARS are interconnected by a high speed Arm Extensible Interface (AXI) bus. The processed output data from the MARS is available to a host system through a USB connection.

Figure 3.2: MARS

### 3.2 Communication/Scheduling Infrastructure

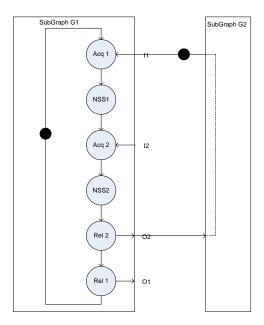

Sea-of-DSP (SoD) is the communication and scheduling infrastructure used by the ARM and VDSPs in the MARS platform. It facilitates the creation and modification of signal processing task graphs during run-time of the application. It efficiently dispatches the signal processing tasks onto the different processors.

### 3.2.1 Components

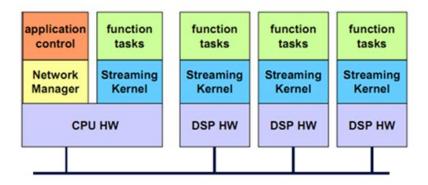

To facilitate creation, modification and dispatch of the signal processing tasks on different processors, SoD has two components namely the network manager and a streaming kernel. Figure 3.3 shows the block diagram of the components in SoD and their presence on the different processors. The network manager is present on the general purpose CPU, which is ARM in case of the MARS. The streaming kernels are present on all the processors and manage the function tasks that are executed on these processors. The DSP hardware corresponds to the VDSPs present in the MARS. The functions of these SoD components are described below.

Figure 3.3: Sea-of-DSP (SoD)

### 3.2.1.1 Network Manager

The Network Manager provides an API for managing the signal processing tasks running on different processors. It provides the following facilities to the user.

- Create, delete processing tasks

- Setting up task graph by connecting or disconnecting tasks via communication channels

- Suspend, resume tasks

- Exchange of commands and status information with tasks

### 3.2.1.2 Streaming Kernel

The streaming kernel is responsible for dispatching the signal processing tasks onto the various processors. It uses a non-preemptive round robin scheduler. It executes the task schedule and supports the data communication required by the tasks. The data exchange between tasks is done through software buffers. It provides a communication library with API calls to facilitate exchange of data between tasks.

**Communication Library** The communication library provides buffers and API calls to check the availability of data or space in the buffer and to read/write data from/to

the buffer. Every task has a port which is its point of access to a channel. A single task may have multiple ports. A unidirectional channel is created by connecting two ports of tasks together. Every channel can have only a single producer and consumer.

### Chapter 4

## **Problem Description**

This thesis is concerned with the enhancement of the scope of the multiprocessor compiler Omphale, which performs automatic parallelization. Omphale takes a sequential description of a real-time streaming application as input and parallelizes it, such that it can be executed on an embedded multiprocessor system. Omphale currently supports kernels with preemptive scheduling and a communication library with buffers supporting multiple producers and consumers. The scope of Omphale is now enhanced to target commercial kernels employing non-preemptive scheduling and buffers with only a single producer and consumer. The MARS multiprocessor platform, developed at NXP, is a target platform which uses such a commercial kernel. A parallel task graph of a stream processing application needs to be generated such that it can be executed on MARS.

### 4.1 Inter-task communication via circular buffers

#### Motivation

Parallel tasks are extracted from a sequential description of streaming application expressed in OIL [3][12]. These tasks communicate via circular buffers. As shown previously in Figure 2.4, these circular buffers can have multiple producers and consumers. Also, in the case of reading and writing to arrays, the producer task could write to the circular buffer corresponding to the array in a particular order and the consumer task could read from the buffer in a different order. The array index could also be non-manifest, i.e. it is dependent on the input data and therefore not known at compile time. Therefore the order of access in the array is not known at compile time.

In the above cases, the communication library on the multiprocessor system should be capable of handling buffers with multiple producers and consumers and also provide a means for out-of-order accesses for arrays. However, the communication library used on our target platform MARS, supports only buffers with a single producer and consumer. A possible approach to solving this incompatibility is to change the existing communication library and replace it with a new one. This would be challenging as

(b) Corresponding Task Graph

Figure 4.1: Illustration of Reordering Problem

(a) NLP Code Snippet

applications using these libraries would contain legacy code and would require a lot of effort to change it. The alternative is to build a wrapper around the existing library. This is the approach followed in this work. Moreover, building a wrapper makes it easier to target other commercial kernels which have their own communication libraries. The following subsections discuss each of the sub-problems in more detail.

### 4.1.1 Reordering Problem

The reordering problem occurs when a producer and consumer of an array have different access patterns, when accessing a circular buffer. This is illustrated with an example shown in Figure 4.1. Figure 4.1a shows a code snippet of a nested loop program (NLP). Here it can be seen that the array x is written to inside the first for loop and corresponds to the producer task (P). The array x is read inside the second for loop and this corresponds to the consumer task (C). The corresponding task graph showing the data dependencies between the two tasks is shown in figure 4.1b. It can be seen that the first element that the producer task would write to the buffer is the array index of 0, whereas the consumer task reads an array index of 5.

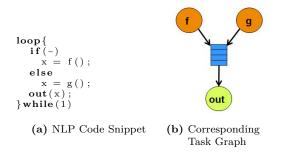

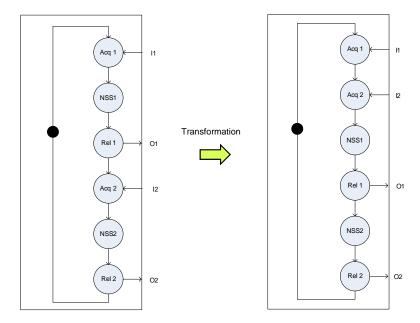

### 4.1.2 Multiple Producers

The multiple producers problem is encountered when there are two tasks which write to the same buffer. OIL supports if and switch statements which leads to the possibility of having multiple mutual exclusive producers to a buffer. The problem is illustrated with an example shown in Figure 4.2. It can be seen from the code snippet of the NLP in Figure 4.2a that there is a mutual exclusive write to the variable x, depending on the if condition. After parallelization, each of the reading and writing statements correspond to different tasks as seen in Figure 4.2b. The producer tasks f and g write to the buffer and the consumer task out reads from the buffer. The issues of concern are listed below.

Figure 4.2: Illustration of Multiple Producers Problem

- The communication library in the target platform does not support buffers with multiple producers. Buffers having multiple producers should be transformed such that buffers with a single producer and consumer are used.

- On using buffers with a single producer and consumer, the consumer task is unable to identify which of the producers wrote to its corresponding buffer. As can be seen from Figure 4.3, task out is unable to identify whether task f or task g wrote to their corresponding buffers.

Figure 4.3: Multiple Producers Problem - Separate buffers

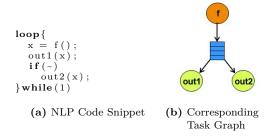

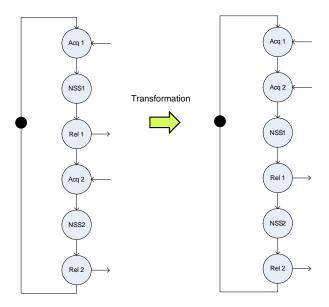

### 4.1.3 Multiple Consumers

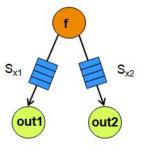

The problem with multiple consumers occurs when there are two tasks which need to read from the same buffer. This is illustrated in the example in Figure 4.4. It can be seen from the code snippet of the NLP in Figure 4.4a that the variable x is written once and read twice. The second read of the variable x is a conditional read. After parallelization, each of the reading and writing statements correspond to different tasks as seen in Figure 4.4b. The producer task f writes to the buffer and the consumer tasks out1 and out2 read from the buffer. The issues of concern are listed below.

Figure 4.4: Illustration of Multiple Consumers Problem

- The communication library in the target platform does not support buffers with multiple consumers. Buffers having multiple producers should be transformed such that buffers with a single producer and consumer are used.

- On using buffers with a single producer and consumer, if at least one of the tasks

conditionally reads its corresponding buffer, there is an accumulation of data in

that buffer. This would lead to the need for infinite size buffers. This is illustrated in Figure 4.5. The task f writes data to the buffers corresponding to the producer-consumer pairs (f, out1) and (f, out2). However, if the condition in task out2 is not satisfied, it would not read from its corresponding buffer. Therefore, there would be an accumulation of data in this buffer, which means an infinite size buffer is required.

.

Figure 4.5: Multiple Consumers Problem - Separate buffers

### 4.2 Non-Preemptive Scheduling

Omphale currently supports preemptive schedulers. It is desired to extend Omphale to support non-preemptive schedulers. Non-preemptive schedulers enable fast context-switching and are needed in cases when the processors do not support preemption.

When a non-preemptive scheduler is used and any of the generated parallel tasks blocks on encountering a blocking synchronization call, the task returns control back to the scheduler so that other tasks can execute. When the task is executed again, it executes from the beginning because the state of the task was not saved. This could lead to an erroneous functional behavior of the application.

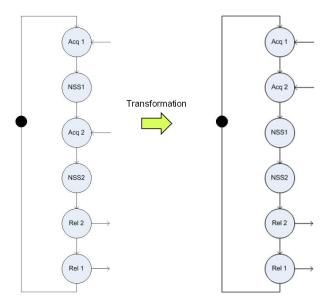

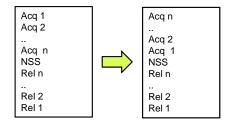

The blocking calls found in the generated tasks are the acquire statements namely, acqSpace and acqData which check for the availability of space or data respectively in a circular buffer. When there is no space or data available in the buffer, these calls return control back to the scheduler. Consider a task containing an acqData statement followed by another acquire statement, with a release Space in between. If this task blocks on execution of the second acquire statement, the data corresponding to the first acquire statement, is already removed from the buffer. This data cannot be obtained on the next execution of the task. This is illustrated in the example shown in Figure 4.6. The input NLP is shown in Figure 4.6a. After parallelization, two tasks, namely task\_f and  $task\_g$  are generated. A snippet of  $task\_g$  is shown in Figure 4.6b. In  $task\_g$ , the value of x is read into a variable condition. On executing  $task\_g$ , if condition is true and the acgSpace call fails due to lack of space, then task\_g returns control back to the scheduler. On the next execution of task\_g, it executes from the beginning and not at the point where the task had got blocked. When task\_g executes from the beginning, a new value of x is read from xCB and the function g() is conditionally executed based on this value of x. This is erroneous as the execution of the function q() should depend on the previous value of x which was read from xCB. However, the previous value of x was lost as it was removed from the buffer.

```

do{

acqData(xCB);

read (xCB, condition);

relSpace(xCB);

if (condition)

acgSpace(vCB):

write (yCB, g());

relData(yCB);

\mathbf{loop}\,\{

x=f();

acqSpace(yCB);

i\,f\,(\,\mathrm{x}\,)

relData(yCB);

} while (1)

(a) Example NLP

(b) Task_g corresponding to the

statement y=g() in the example

NLP

```

Figure 4.6: Non-Preemptive Scheduling

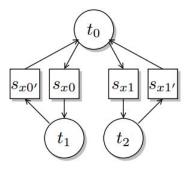

If the state of the task is not saved, it could even lead to a deadlock. This is illustrated by an example in Figure 4.7. The input NLP shown in Figure 4.7a consists of two functions f and g, with two data dependencies between them. After parallelization, two tasks  $task\_f$  and  $task\_g$  are obtained and their corresponding task graph is shown in Figure 4.7c. When sliding window [3] buffers are used for inter-task communication, a read window (RW) and a write window (WW) determine which locations of the buffers are accessible. The read window is defined by r at the head and r at the tail. Similarly, a write window is defined by  $w^{\hat{}}$  at the head and r at the tail. A snippet of the code in  $task\_f$  and  $task\_g$  are shown in Figure 4.7b. When acqData(xCB) is called in  $task\_g$ , if there is data in the location after r, r is moved forward by one location. When executing task\_g, if acqData(xCB) succeeds and acqData(yCB) fails, then  $task\_g$  is blocked and returns control back to the scheduler. On the subsequent executions of  $task\_g$ , if the same scenario repeats, then r coincides with w and  $task\_g$ cannot proceed as there is no new data written that is available for reading. Similarly,  $w^{\hat{}}$  coincides with r and cannot proceed. This leads to a deadlock as the read window and the write window occupy the entire buffer and both cannot advance. The deadlock occurs as some locations in the buffer are acquired by the acqData statement but not released by the corresponding relSpace statement. This occurs because on subsequent executions of the task after being blocked, it resumes execution from the beginning and not from the point where it had got blocked.

```

Task\_f

\mathbf{do}\{

do{

acqSpace(xCB);

acqSpace(yCB);

write(xCB, x_out);

write(yCB, y_out);

relData(xCB);

relData(yCB);

} while(1)

xCB

←ww-

Task\_g

\mathbf{do}\{

\leftarrowRW\rightarrow

do{

acqData(xCB);

acqData(yCB);

read(xCB,temp_x);

read(yCB,temp_y);

relSpace(xCB);

relSpace(yCB);

}

⊱ww->

f(out x,out y);

w

g(x,y);

} while (1)

уСВ

(a) Example NLP

(b) Output Tasks

(c) Corresponding Task Graph with Sliding Window

```

Figure 4.7: Illustration of Deadlock with Non-preemptive scheduling

### Chapter 5

# Inter-Task Communication via Circular Buffers

In this chapter, the various issues in dealing with inter-task communication via circular buffers and the solutions proposed to solve them are discussed. The solutions proposed in literature in dealing with these issues are described in corresponding sections. Section 5.1 discusses the reordering problem and the generation of a wrapper synchronization library. In Section 5.2, the multiple producers problem and proposed solutions are described. Section 5.3 contains a description about the issues with multiple consumers and proposed solutions to solve them.

### 5.1 Reordering Problem

The producer and consumer of an array can have different access patterns while accessing the array, thereby leading to the reordering problem. A sequential NLP can contain statements reading and writing to an array, which after parallelization, correspond to parallel tasks reading and writing to a buffer corresponding to the array. It is noteworthy to mention that if the order in which the different elements in the array are read and written is the same, then the reordering problem does not occur. This is because the elements of the array are written and read in FIFO order and the FIFO buffer present in the communication library supports this behavior.

### 5.1.1 Related Work

To solve the reordering problem, FIFO buffers in combination with a reordering task and reordering memory can be used [3]. This is illustrated in Figure 5.1. The producer task writes the values in the order it produces, to a FIFO buffer. Then the reordering task which has the knowledge of both the write access pattern and the read access pattern of the array writes them to a reordering memory. From the reordering memory, the reordering task writes to another FIFO buffer following the read access pattern of the array. In this case, the producer task and the reordering task execute sequentially as the elements of the entire array have to be written into the reordering memory before the

reordering task can reorder them. This approach has the disadvantage that it prevents parallel execution of both the tasks. Also there is the overhead of the reordering task and reordering memory. Furthermore, two FIFO buffers are required.

Figure 5.1: Reordering task with reordering memory [3]

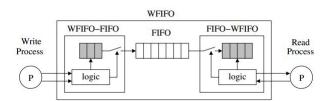

Another method using FIFO buffers has been proposed in [17] by Turjan et al. A special controller unit is designed that takes care of restoring the order of the tokens. Also additional memory is required in the consumer task. Though in this case, no reordering task is required, it faces the overhead of a complex controller unit and also reading from the reordering memory. In [18], Huang et al. propose the concept of a windowed FIFO. A windowed FIFO requires local buffers or containers in the reading and writing tasks. Dedicated logic is used to control the writing of elements of the array into the local container on the producer side, after which the contents of the container are transferred to the FIFO between the producer and consumer tasks. Similarly, dedicated logic is used to control the writing to the container on the consumer side, after which the consumer task can read from it. This has been illustrated in Figure 5.2. In this approach, there is the overhead of the local containers which can be likened to reordering memory.

Figure 5.2: Windowed FIFO [18]

A buffer which supports out-of-order access can also be used to solve the reordering problem. Such a buffer enables reading and writing to any location in the buffer. Synchronization is needed to prevent locations in the buffer being read, before they have been written [3]. Bijlsma et al. developed two such buffers, namely *Sliding windows* [19] and *Overlapping windows* [20]. Sliding windows consist of a read window for every reading task and a write window for every writing task. The read windows are not allowed to overlap with the write windows. However, sliding windows cannot be applied always for cyclic data dependencies as it can cause a deadlock. Overlapping windows can be used even for latency critical cyclic data dependencies [3]. In the case of overlapping windows, a location is removed from the window as soon as it has been accessed.

### 5.1.2 Proposed Solution

The reordering problem occurs due to different access patterns in an array by the producer and consumer tasks. The solutions proposed in literature as shown in section 5.1.1 used FIFO buffers with the overhead of additional control logic and reordering memory. By using buffers permitting out of order access, the reordering problem was solved using sliding windows. The SoD communication library, used in our target platform permits out of order access. Therefore, the approach using sliding windows [20] seems applicable. However, due to certain issues which are described subsequently the sliding windows buffer is not directly applicable. Therefore, a modified version of sliding windows is developed.

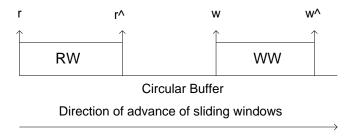

Sliding windows consist of a read window and a write window in a circular buffer as shown in Figure 5.3. The read window (RW) is formed by the r pointer at the head and the r pointer at the tail. Similarly, a write window (WW) is formed by the w pointer at the head and the w pointer at the tail. These windows advance when a task calls the appropriate synchronization statements, which are described subsequently.

Figure 5.3: Sliding windows Buffer

Tasks executing on different processors and communicating via shared memory need a memory consistency model to prevent the reading of a location before it is written [3]. The memory consistency model defines the order in which write accesses complete. The sliding windows approach employs a streaming consistency model [21], wherein shared memory accesses can be reordered so that they can be pipelined for better performance. In order to prevent race conditions between the read and write accesses to shared memory, synchronization has to be performed. The synchronization ensures that a shared location is read only after it has been written. Similarly, synchronization ensures that a shared location has been read before it is overwritten. In the streaming consistency model, synchronization is performed using acquire and release statements.

An acquire statement precedes the access to a shared location and blocks until the location becomes available. A release statement is inserted after the access to a shared location, indicating that it is now available. An empty location in the buffer is referred to as space and a location filled with data is referred to as data. Before writing data to an empty location, a producer acquires it by a acquireSpace call. After data has been written to this location, the producer executes a releaseData call signaling that the location is now available for reading by the consumer. Subsequently, the consumer can acquire the location with a acquireData call. Once the data has been read, the consumer releases the location with a releaseSpace call.

The acquire and release synchronization statements advance the read and write windows in the buffer. The write window should always be ahead of the read window in order to prevent the reading of a location that has not been written. The advancement of the

windows by the producer and consumer are described below.

The following synchronization statements are employed by the producer task.

- acquireSpace(n) increments  $w^{\hat{}}$  by n locations

- releaseData(n) increments w by n locations

The acquireSpace synchronization statement moves the head of WW forward by acquiring a space in the buffer. The corresponding releaseData call moves the tail of WW forward after having written a value in the corresponding location(s), implying that the data can now be read.

The following synchronization statements are employed by the consumer task.

- acquireData(n) increments  $r^{\circ}$  by n locations

- releaseSpace(n) increments r by n locations

The acquireData synchronization statement moves the head of RW forward by acquiring n locations in the buffer. The corresponding releaseSpace call moves the tail of RW forward after having read the value from the corresponding location(s), implying that it can now be written.

In the sliding windows buffer, the buffer administration stores the four pointers for the RW and WW [3]. This is the case when using the buffer implementation and communication library built in-house for Omphale. However, implementations supporting a single producer and consumer have no notion of the head pointers,  $r^{\hat{}}$  and  $w^{\hat{}}$  pointers. Their buffer administration would store only a r and a w pointer. The SoD buffers used in our target platform also do not store the head pointers in the buffer administration. Due to this issue, the sliding windows approach cannot be used directly.

The lack of the head pointers poses a second issue when acquiring locations in the sliding windows buffer. When an acquire statement is executed, it checks for the availability of space or data in the buffer from the current head pointer of WW or RW. However, the SoD buffers do not contain the head pointers. The SoD API provides functions namely checkWrite and checkRead which can check for the availability of space or data respectively from the current w and r pointers only. These functions have to be used in such a manner as to provide the ability to check for space or data from the head pointers of WW or RW. A mechanism is derived to account for the lack of these head pointers in the buffer administration while still being able to provide the required synchronization. This is explained in the following section.

### Wrapper Generation

The synchronization statements use SoD API to implement their functionality. Hence a wrapper library has been built which makes use of the required SoD API. The lack of head pointers in the buffer administration is accounted for in the modified sliding windows buffer. The following listing gives a basic idea about the synchronization statements used in the modified sliding windows approach.

### • AcquireSpace(n, countSpace)

Check for 'n + countSpace' available spaces from w If available, countSpace is incremented by n

### • ReleaseData(n, countSpace)

Decrement countSpace by n Increment w by n

### • AcquireData(n, countData)

Check for n' + countData available data from r If available, countData is incremented by n

### • ReleaseSpace(n, countData)

Decrement countData by n Increment r by n

On executing AcquireSpace, it checks for the availability of n + CountSpace spaces in the buffer. If spaces are available, it increments countSpace by n. countSpace is a counter which maintains the number of spaces that have been acquired in the buffer. On a subsequent releaseData call, it decrements countSpace. Similarly on executing AcquireData, it checks for the availability of n + CountData data in the buffer. If data are available, it increments countData by n. countData is a counter which maintains the number of data that have been acquired in the buffer. On a subsequent releaseSpace call, it decrements countSpace.

The implementation of the synchronization wrapper library functions are shown in Figure 5.4a. Here, it can be seen that all the functions also take port as a parameter. The port refers to SoD ports that are part of SoD tasks. An SoD buffer is formed by the channel connecting two ports. CheckRead is a SoD API function that enables to check that there are n filled data locations from the current r pointer. Similarly, CheckWrite is a SoD API function that enables to check that there are n empty locations from the current w pointer. UpdateWrite and UpdateRead are SoD API functions that increment the w and r pointers respectively. It can be seen here that the acquire synchronization calls return control to the scheduler immediately, when there is not enough space or data available in the buffer.

A sample sequence of operations is shown in Figure 5.4 to illustrate the use of r and w pointers and the counters countSpace and countData when the synchronization calls are encountered. The value of the head pointers can be obtained by summing the corresponding tail pointers and counters as shown in Figure 5.4. The values that change on every step are shown in red. On executing acqS twice, a space is acquired and the values of  $cnt\_S$  and the w pointers are incremented by one each time. After a write is done, then an execution of relD increments the w pointer and  $cnt\_S$  is decremented. In this case, the head of the write window has not moved and this is shown by w retaining a value of 2.

### 5.2 Multiple Producers

Two tasks writing to the same buffer leads to the multiple producers problem. However, if the underlying communication library does not support a buffer with multiple producers, then two separate buffers need to be used. On using separate buffers, the consumer task does not know which of the two producers wrote to its corresponding buffer.

```

acquireDataSod(port,nrData,countData){

if (OK!= CheckRead(port, nrData + countData)

return BLOCKED;

else {

if(countData + nrData >= buf_size)

coundData \, = \, (\, countData \, + \, nrData \, \dot{)} \, \, \% \, \, (\, buf\_size \, )

countData = countData + nrData;

}

}

releaseSpaceSod (port, nrData, countData) {

countData = countData + nrData;

updateRead(port, nrData);

acquireSpaceSod(port, nrSpace, countSpace) {

if( OK != CheckWrite(port, nrSpace + countSpace)

return BLOCKED;

if(countSpace + nrSpace >= buf_size)

countSpace = (countSpace + nrSpace) % (buf_size)

countSpace = countSpace + nrSpace;

}

releaseDataSod (port, nrSpace, countSpace) {

countSpace = countSpace + nrSpace;

updateRead (port, nrSpace);

```

#### (a) Wrapper Synchronization Library

| Sequence of operations | W | cnt_S | r | cnt_D | Space/Data available | w^=w+<br>cnt_S | r^=r+<br>cnt_D |

|------------------------|---|-------|---|-------|----------------------|----------------|----------------|

| Initial                | 0 | 0     | 0 | 0     | NA                   | 0              | 0              |

| acq_S(1,cnt_S)         | 0 | 1     | 0 | 0     | Yes                  | 1              | 0              |

| acq_S(1,cnt_S)         | 0 | 2     | 0 | 0     | Yes                  | 2              | 0              |

| Write 1 value          |   |       |   |       |                      |                |                |

| reID(1,cnt_S)          | 1 | 1     | 0 | 0     | NA                   | 2              | 0              |

Figure 5.4: Example

#### 5.2.1 Related Work

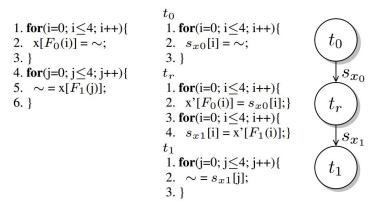

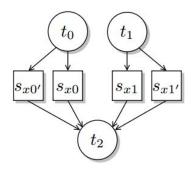

An approach using additional buffers [3] was described to solve the issue with multiple producers in an array. This shown in Figure 5.5. As can be seen, apart from the FIFO buffers  $s_{x0}$  and  $s_{x1}$ , two additional buffers  $s_{x0}$  and  $s_{x1}$  are added. The producer tasks write a value to these additional buffers indicating the indexes of the array which they have written to in the corresponding buffers. The consumer task checks the indexes in these additional buffers and compares it with the index that it needs to read, and reads the corresponding buffer. However, this approach cannot handle the case where there are multiple producers to the same array index.

Turjan et al. [22] propose a method to solve a similar issue as the previous one with

Figure 5.5: Addition of Additional buffers

multiple producers to an array. It is applicable only to NLPs with affine index-expressions. Affine expressions are a linear combination of loop parameters and a constant. By using affine index-expressions, exact data dependencies can be calculated and so the additional buffers are not needed. However, as in the previous approach, multiple producers to the same array index is not handled. Also, streaming applications contain non-manifest statements which cannot be handled by this approach.

In [23], Gangwal et al. propose a synchronization protocol which uses point-to-point FIFOs for communicating between tasks. However, they do not solve the multiple producers problem. Also in [24], a Task Transation Level (TTL) interface is provided to facilitate inter-task communication and synchronization. However, even in this case, the multiple producers problem is not solved.

Bijlsma et al. [3] solve the multiple producers problem by using a single buffer capable of having multiple producers. Multiple sliding windows are used per producer, and a consumer cannot read until all the multiple producers have indicated that the location which has multiple producers is not needed by all of them. However, in our case, the communication library supports only buffers with a single producer and consumer. Hence this approach is not applicable.

An approach that is directly applicable to solve the multiple producers problem could not be found.

# 5.2.2 Proposed Solution

To solve the multiple producers problem several approaches were proposed as discussed in section 4.1.2. However, these approaches address a related issue and not the exact problem that we would like to address. When separate buffers are used in the case of multiple producers, the problem is that the consumer task needs to identify which of the multiple producers wrote a value to its corresponding buffer. Due to single assignment requirement on the NLP it is known that these writes are mutually exclusive. Two approaches to solve the multiple producers problem are shown in the subsequent sections.

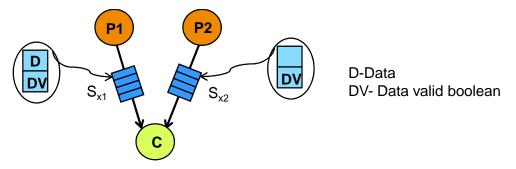

#### 5.2.2.1 Data Valid Boolean

The consumer task has to identify which of the two producers wrote a value to its corresponding buffer. A data structure can be created encompassing a data valid boolean and the actual data to be passed in the buffer. This data structure is henceforth referred to as a container that is passed through the buffer. illustrated in Figure 5.6. Here the producer tasks are P1 and P2, and the consumer task is denoted as C. The producer task (P1) which actually writes a value sets the data valid boolean to true and writes the data into the container. The other producer task (P2) which does not write actual data to the container sets the data valid boolean to false. The consumer task extracts the data valid boolean from the containers in both the buffers. It reads the data from the buffer which has the data valid boolean set to true. In this approach, an empty data structure has to be passed through the buffers, corresponding to producers that do not need to write a value. If these buffers are located on the local memories of other processors, they could use up unwarranted bandwidth on the interconnect. The amount of bandwidth used depends on the size of the data that needs to be passed. Also, the overhead of the data valid boolean is smaller if bigger data structures need to be passed through the buffer as compared to smaller ones. This approach can be used for both shared memory and distributed memory systems.

Figure 5.6: Multiple Producers - Data Valid Boolean

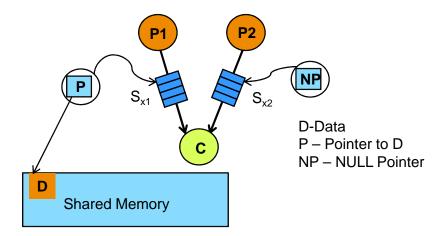

#### 5.2.2.2 Valid / NULL Pointer

In order to identify which of the two producers wrote a value to its corresponding buffer, a valid/NULL pointer can be used. This is shown in Figure 5.7. The producer task which actually writes a value, passes a pointer to the data that has to be passed through the buffer. The data is stored in a shared memory which is accessible by the consumer task. The other producer tasks which do not need to write a value to the buffer, write a NULL value into the buffer. The consumer task reads the buffers corresponding to the different producer tasks, and checks which of them contain a valid pointer. Then the valid pointer is dereferenced to obtain the data stored in the shared memory. This approach can be used only for shared memory systems and not distributed memory systems. This is because, in distributed memory systems a pointer to a local memory location is not accessible remotely.

Figure 5.7: Multiple Producers - Valid/NULL Pointer

# 5.2.3 Implementation in Omphale

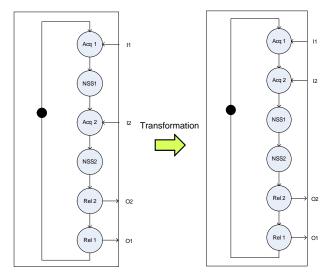

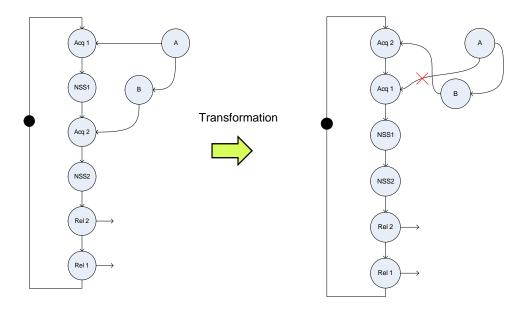

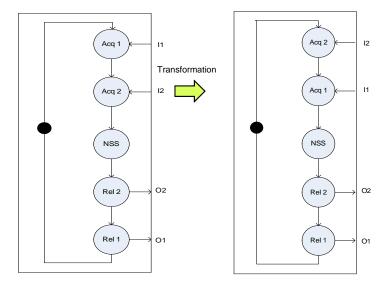

The proposed solution with NULL pointers has been implemented in Omphale. The existing implementation of Omphale is changed to obtain separate buffers for every producer. Figure 5.8 shows how a task is transformed so that multiple buffers can be generated per producer. The variable x is written twice, thereby making it a multiple producer. We create two new unique pointers  $x\_unq\_p0$  and  $x\_unq\_p1$  which replace the first and second occurrences of x where they are being written respectively. A conditional assignment statement is used in a seq block along with the statement that reads x. It assigns the value of x based on whether  $x\_unq\_p0$  or  $x\_unq\_p1$  has a valid address assigned to it. A seq block ensures that the statements in that block are made into a single task. As discussed earlier, it is known that only of the two producers would write a valid pointer pointing to data value, into its corresponding buffer. The other producer would write a NULL pointer to the buffer. The function isValid checks for the valid pointer and assigns x by dereferencing the pointer.

```

loop {

if (~)

*x_unq_p0 = f();

else

loop {

if(~)

x = f();

x = g();

output(x);

} while (1)

loop {

if(~)

*x_unq_p1 = g();

seq {

x = isValid(x_unq_p0) ?

*x_unq_p0 : *x_unq_p1;

output(x);

}

} while (1)

(a) Input Task

(b) Transformed Task

```

${\bf Figure~5.8:~Multiple~Producers~-~Task~Transformation}$

After parallelization, three tasks are obtained as seen in Figure 5.9. It can be observed that a NULL pointer is written into the buffer in task\_f and task\_g when a valid data value is not being written into the buffer.

```

do{

if (~)

*x_unq_p0 = f();

else

x_unq_p1 = NULL;

else

x_unq_p0 = NULL;

} while (1)

do{

x = is Valid (x_unq_p0) ?

x =

```

Figure 5.9: Parallel Tasks

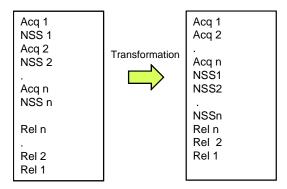

## 5.3 Multiple Consumers

A buffer having multiple consumers leads to a multiple consumers problem. Separate buffers can be used for each consumer if the underlying communication library does not support buffers with multiple consumers. If one of the consumers does a conditional read, then the producer has to decide which of the two buffers should be written to and when it should be written.

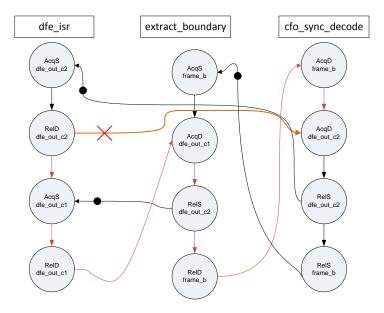

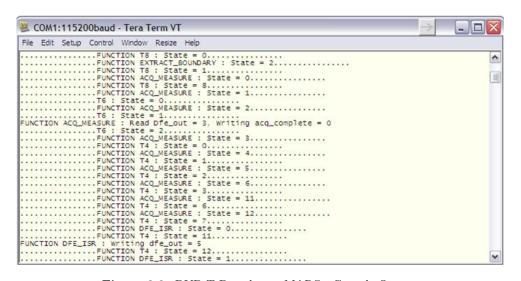

# 5.3.1 Related Work