| MASTER                                                      |

|-------------------------------------------------------------|

|                                                             |

| Diagnosing yield loss using specially designed random logic |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

| Mels, A.                                                    |

|                                                             |

| Award date: 2000                                            |

|                                                             |

|                                                             |

|                                                             |

| Link to publication                                         |

|                                                             |

|                                                             |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# TU/e

# technische universiteit eindhoven

Section of Information and Communication Systems (ICS/EB) Faculty of Electrical Engineering ICS/EB 746

Master's Thesis

Diagnosing Yield Loss using Specially Designed Random Logic

Arjan Mels

Coaches:

ir. K. Veelenturf (Philips Semiconductors B.V.)

Supervisor:

prof.ir. M.T.M. Segers

Date:

November 2000

Semiconductors - Nijmegen - MOS4YOU

# Diagnosing Yield Loss using Specially Designed Random Logic

Arjan Mels

Supervisor: prof. ir. M.T.M. Segers (Eindhoven University of Technology)

Coach: ir. K. Veelenturf (Philips Semiconductors B.V.)

February - November 2000

# Contents

| mma   | ry                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ntent | is                                                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Intro | oduction                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •     |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.3   | Structure of this Report                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The   | Veqtor & Random Logic                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1   | Concept                                                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2   | Versions                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3   | Random Logic                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.3.1 Definition of Random Logic                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.3.2 Testing Random Logic                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.3.3 Localising Defects                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Desi  | gn of the RDMC Module                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1   | Concept                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2   | Design                                                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3   | Variants                                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.4   | Area Considerations                                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Test  | ing the RDMC module                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T.£   |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | ·                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.3   |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.4   |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _     |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | •                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.4   |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | •                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5.4.2 Counting the Failures                                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 5.40 Basing Bananata Education                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

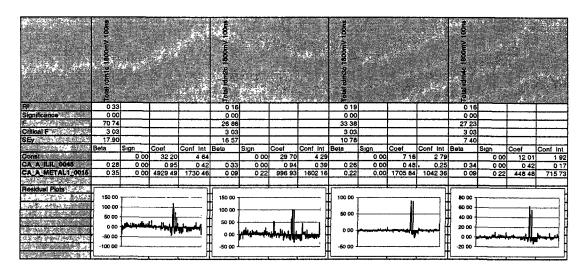

|       | 5.4.3 Design Parameter Extraction                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 5.4.4 Yield Model for the Standard Library Cells                              | 24<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 5.4.4 Yield Model for the Standard Library Cells                              | 24<br>24<br>25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.4.4 Yield Model for the Standard Library Cells                              | 24<br>24<br>25<br>27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | Intro 1.1 1.2 1.3 The 2.1 2.2 2.3  Desi 3.1 3.2 3.3 3.4 Test 4.1 4.2  4.3 4.4 | 1.2 Project Description 1.3 Structure of this Report.  The Veqtor & Random Logic 2.1 Concept 2.2 Versions 2.3 Random Logic 2.3.1 Definition of Random Logic 2.3.2 Testing Random Logic 2.3.3 Localising Defects  Design of the RDMC Module 3.1 Concept 3.2 Design 3.3 Variants 3.4 Area Considerations  Testing the RDMC module 4.1 The Tester 4.2 Test Pattern Considerations 4.2.1 Compact Test Pattern Generation 4.2.2 Test Pattern Verification 4.2.3 Logging 4.4 Conclusions  Diagnosis Methodology 5.1 Outline 5.2 Yield Modelling 5.3 Yield Differences between Modules |

|     | 5.5   | Additional Analysis Instruments29                          |

|-----|-------|------------------------------------------------------------|

|     |       | 5.5.1 Wafermaps30                                          |

|     |       | 5.5.2 Bitmaps                                              |

|     |       | 5.5.3 Pattern Failure Information31                        |

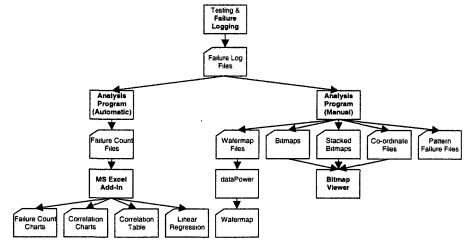

|     | 5.6   | Tools                                                      |

|     | 5.7   | Conclusions                                                |

| 6   | Rec   | ommendations for Test Methods34                            |

|     | 6.1   | Additional Static Patterns34                               |

|     | 6.2   | Current-Based Methods35                                    |

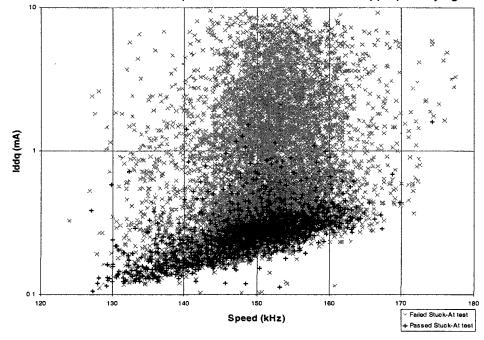

|     | 6.3   | Timing-based Methods                                       |

|     | 6.4   | Conclusions                                                |

| 7   | Rec   | ommendations for Changes to the Design38                   |

|     | 7.1   | Detection Capability for Opens                             |

|     | 7.2   | Area overhead of Flip-Flops                                |

|     | 7.3   | Denser Routing40                                           |

|     | 7.4   | Area Considerations and Multiple Instances of the Cells41  |

|     | 7.5   | Separate Testability of the Sub-modules                    |

|     | 7.6   | Optimal Variants                                           |

|     | 7.7   | Conclusions                                                |

| 8   | Con   | clusions44                                                 |

|     | 8.1   | Test Patterns and Failure Logging44                        |

|     | 8.2   | Diagnosis Methodology44                                    |

|     | 8.3   | Changes and Additions to the Test Methods and the Design45 |

|     | 8.4   | Overall Conclusions                                        |

| Ac  | know  | rledgements                                                |

| Lit | eratu | re48                                                       |

|     |       | ix A Extracted Design Attributes49                         |

| 74  |       | Front-end and Metal 1 attributes                           |

|     |       | Metal 2-6 and Via attributes                               |

| _   |       |                                                            |

| Ap  | -     | ix B Results of RDMC analysis50                            |

|     |       | Lot CZ970050                                               |

|     |       | Lot CZ970150                                               |

|     | B.3.  | Lot CZ989350                                               |

|     | B.4.  | Lot CZ842251                                               |

|     | B.5.  | Lot CA060251                                               |

.

# 1 Introduction

### 1.1 Context

At MOS4YOU (a Philips' Semiconductors IC Foundry in Nijmegen) a specially designed chip is used for speeding up the introduction of new IC production processes and for monitoring running processes. This dedicated chip is used for two reasons:

- Often no commercial products are available in the early stages of the process introduction.

- A dedicated chip can be designed to suit the specific needs of process introduction and monitoring, like size requirements and analysability.

The Veqtor (<u>ve</u>hicle for process <u>qualification</u> and moni<u>toring</u>), as the chip is called, has to be representative for normal products to cover all types of problems that might arise during production. It therefore contains all types of commonly used modules: RAM's, ROM's, analogue circuitry and random logic (also called standard cell logic).

The chip also has to be easily analysable in order to find the cause of problems as quickly as possible. To be able to do this it has to be possible to zoom in on separate modules and even further into these modules. Therefore, the modules are separately accessible from the outside.

For diagnosing the cause of problems in the production process, the use of RAM and ROM is well established: their regular structure and the possibility to access every memory cell separately makes them relatively easy to analyse. However, it is also important to be able to analyse random logic, as this exhibits problems that do not exist for RAM and ROM.

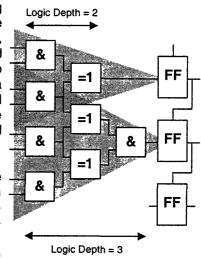

Random logic as applied in normal applications is difficult to analyse because it is hard to pinpoint specific failing cells. This is due to the fact, that normal random logic has a logic depth (the number of logic cells between two externally accessible points) that is quite large. With a given set of test patterns, it is only possible to determine a list of cells that are the most likely cause of a failure.

To overcome the low analysability of normal random logic, a special type of random logic module (further called RDMC) was added to the Veqtor chip. This type of module contains random logic with a logic depth of one. As a result, all in- and outputs of the logic cells are externally accessible, which makes it possible to directly attribute an electrical failure to a specific cell or its interconnect.

Although the design of these modules and a basic test program for them were finished at the beginning of this project, the diagnosis methodology necessary to make good use of them did not exist.

# 1.2 Project Description

The development of such a methodology was the main subject of the graduation project described in this report. However, the project as it was defined consisted of two closely related sub-projects. The first sub-project consisted of devising a diagnosis methodology for the RDMC modules. The second sub-project consisted of proposing changes to the test methods or the design that improve the usefulness of the RDMC modules.

The diagnosis methodology would need to be able to relate the test results to process problems. The problems should be identified as precise as possible. It

was suggested that it might be possible to determine the process layer (or the layout structure) that was causing problems by analysing statistical data. Also it was considered interesting to determine the location of a failure as precise as possible.

The deliverables for the first sub-project not only included the devising of the diagnosis methodology, but also the development of the supporting (software) tools.

In the second stage of the project, improvements to the test methods and / or the design of the module had to be developed. It was known that the current module design and test methods are not sensitive to certain categories of defects (resistive shorts and opens etc.), while these types of defects are expected to become increasingly important. Also some possibilities for enhancements might present themselves during the work on the first sub-project.

The deliverable for the second sub-project was a proposal for a new test approach or for an enhanced design.

MOS4YOU was in the first phases of introducing a new, 0.18µm process when work on this project started. The first Veqtor chips with the RDMC modules were just starting to come out of the line. Therefore the results of the first sub-project could immediately be tested and used. If it was found that additional or different test methods were needed, these could also be used immediately. Changes to the design would of course have to wait for a redesign of the entire Veqtor. This would most likely occur for the next process after the 0.18µm process.

# 1.3 Structure of this Report

Before going into the actual work on the project, the next two sections will provide necessary background information on the Veqtor chip, the RDMC modules and on the testing of random logic.

It was considered necessary to make some changes to the tests used before the work on the diagnosis methodology could start. This is described in Section 4. Also described in this section is the way in which detailed results about these tests can be logged.

Section 5 describes the diagnosis methodology that was devised together with the considerations leading to it. Also included in this section are some examples of the application of the methodology and a short description of the tools that were implemented to support the methodology.

Changes to the test methods and to the design are considered in Section 6 and Section 7 respectively. The chapter on test methods contains sub-sections on additional static patterns, current-based testing and timing-based testing. The chapter on the design considers a number of changes that would make the RDMC modules more suitable for their purpose.

To finish, Section 8 provides a summary of the conclusions of the separate sections and the overall conclusions and recommendations.

# The Veqtor & Random Logic

Before a detailed description of the RDMC module can be given in the next section, it is necessary to briefly look at the overall structure of the Vegtor chip. Details about the latest generation of Vegtor chips, which is used with the 0.18µm process, can be found in [Lit. 1]. This section also provides a basic explanation about random logic and how it can be tested and analysed.

### 2.1 Concept

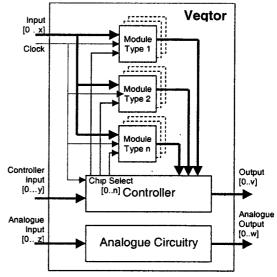

The design of the Vegtor follows a modular approach (see the simplified structure in Figure 1). Consequently, different Vegtors can have different amounts and different types of modules. At the top level a controller switches the in- and outputs between multiple modules. In this way, the number of modules can vary while the number of in- and outputs can stay the same. The analogue circuitry is handled separately and it does not share its in- and outputs with the rest of the chip.

The contents of a module can be freely chosen, as long as the in- and outputs of a module adhere to the specification [Lit. 1]. Examples of module types that • Figure 1 Overview of the Vegtor are used, are RAM, ROM and random

logic. Multiple instances of each module are sometimes placed to increase the area (in order to increase the sensitivity for defects).

### 2.2 **Versions**

Currently, there are four generations of Veqtor chips. Each generation is targeted at a specific process. Within each generation, multiple versions of a Vegtor can exist. The different versions target different process options (for example with different amounts of metal layers) or contain different types and amounts of modules (because some were not available when the initial version was developed for example).

Because it is the first (and for now only) generation that contains the RDMC modules, the Vegtor4 is the only generation of interest for this report. The Vegtor4 is targeted at Philips' CMOS18 process (0.18µm and a maximum of 6 metal layers) and is used both for the start-up of this process and for the ramping of the yield.

Although, the Vegtor4 is the first generation to contain the RDMC modules, random logic was already present on the earlier generations in the form of the socalled RDMR modules. These modules are derived from a 16-bit Digital Signal Processor. All RAM's and ROM's were stripped from the original design and all inand outputs were made accessible via a scan-chain. The module is representative for a normal product, but difficult to analyse. Because it is so very representative, it is still maintained on the Vegtor4. More information about this module can be found in [Lit. 2].

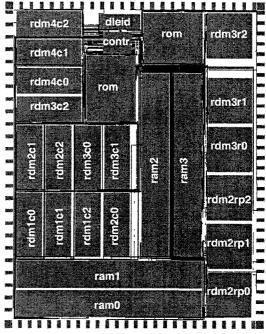

All results used in this report are from three versions of the chip: the Vegtor4 Pinot, the Vegtor4 Flash and the Vegtor4 Steen. The Pinot and Flash differ only a little: the Flash is used for a process option with only five metal layers, so all modules with more than five layers are replaced with other variants. The Steen is a larger version, with more instances of each module type and in addition four RAM modules (these were not yet included on the Pinot and the Flash).

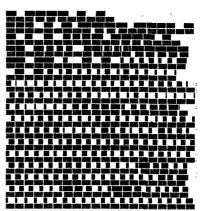

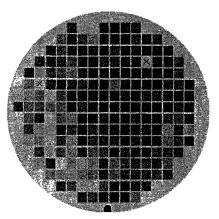

To get a feeling for the complexity of the chip, the layout of the Vegtor4 Steen is shown in Figure 2. The Vegtor4 Steen occupies an area of 31.5 mm<sup>2</sup> and contains about 12 million transistors.

### 2.3 Random Logic

Before starting to discuss the random logic contained on the Vegtor chip, it is important to define what is understood by random logic. In ad- • Figure 2 The layout of the Veqtor4 Steen

dition, it is important to understand the basics of the testing of random logic because this clearly shows the problems in analysing it.

### 2.3.1 **Definition of Random Logic**

The random in the name random logic, comes from the fact that it does not have a structure as regular as a RAM or a ROM. Random logic is -as already mentioned--- also called standard cell logic. From this name, it can be implied that it is logic, built from standard cells, like AND-gates, OR-gates and flip-flops.

These standard cells are organised in what is called a standard cell library. (Therefore, the cells are sometimes also called library cells.) All cells in a library are designed in such a way that all their heights are equal and therefore they are easy to place in long rows. In addition, they are designed in such a way, that they only use the bottom one or two metal layers.

To define the logic functionality of a circuit, the standard cells are connected in the remaining metal layers according to the design. The way in which cells are connected, using the different layers of metal, is called the routing (also the name of the process of determining how the connections can be made). The more layers of metals available the more freedom available for the routing and the "easier" it

### 2.3.2 **Testing Random Logic**

In the introduction, it has already been postulated that it is difficult to isolate failures in normal random logic. This has to do with the way such a circuit can be tested, which will be briefly explained in this sub-section.

To determine if a chip functions according to the design, it has to be tested. A basic test strategy would be to insert the circuit into its final application and see if it functions. This of course is the ultimate test. Yet, this kind of test has a number of major drawbacks, not the least that it is very time-consuming and therefore costly.

The test method that is used most often in practise only tests the logic functionality of a chip; all other aspects (for example speed) are left out of consideration and therefore are not covered. For older processes, this proved to be no problem as short circuits are the predominant failure mechanism in this case. However, other types of defects (for example resistive shorts and opens) become increasingly important as feature sizes keep decreasing. These types of defects are not, covered by the tests for logic functionality. Therefore additional test methods have been developed. Some of these are considered in Section 6.

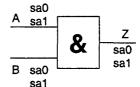

Even when only the logic functionality of a chip is tested, it can become very timeconsuming. In the case of a combinatorial circuit with N inputs, it would require 2<sup>N</sup> test patterns to exhaustively test it. The test time can be strongly reduced by using the socalled stuck-at fault model. A stuck-at fault means that a certain net (connection between cells) is fixed to a certain logical value (either zero or one). On silicon, this would for example mean a short circuit between a net and ground. Two assumptions are introduced, which make the test time reduction possible:

- The only faults that can occur are stuckat faults.

- Only one fault can occur in the circuit.

| Tes | t Patt | ern | Stuck | -At Fa | ıults |

|-----|--------|-----|-------|--------|-------|

| Α   | В      | Z   | Α     | В      | Z     |

| 0   | 0      | 0   |       | -      | sa1   |

| 0   | 1      | 0   | sa1   |        | sal   |

| 1   | 0      | 0   |       | sa1    | sa1   |

| 1   | 1      |     | sa0   | sa0    | sa0   |

(The grey rows indicate the patterns needed to cover all stuck-at faults)

Figure 3 Stuck-at faults for a AND-gate

For example: for a 2-input AND-gate only three patterns are necessary (instead of four) to detect all possible single stuck-at faults (see Figure 3).

The additional assumptions make that shorts between two nets (also called bridges) are not necessarily detected. This is caused by the fact that adjacent nets could have the same value during the entire test. However, it turns out that in practise the majority of the possible bridges is covered.

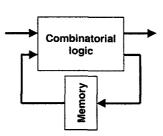

For sequential logic an additional problem occurs. Since the outputs of the memory (consisting of flipflops) can be considered as additional inputs to the • Figure 4 Sequential logic combinatorial logic (see Figure 4), the content of the memory has to be set to a specific state to test the logic. When the inputs of the memory are not directly connected to external pins, it might be impossible (or at least very difficult) to set it up in the correct way. In addition, it is also impossible to check all outputs of the combinatorial logic, when the memory cannot be read from the outside.

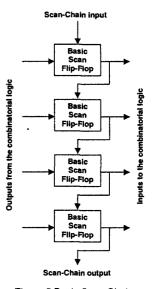

To overcome this problem, so-called scanable flipflops (or just scan flip-flops) can be used. These flipflops can have their value set via a dedicated input and they can be connected together into long chains (called scan-chains). These scan-chains actually form long shift registers, which makes it possible to set and read their content in a serial fashion (see Figure 5).

The use of scanable flip-flops reduces the testing to a combinatorial problem again. The price is a small increase in area because of the more complex nature of these flip-flops. The extra area needed is typically in • Figure 5 Basic Scan-Chain the order of a few percents.

The use of scan flip-flops is a technique that is used industry wide and is an intrinsic part of the design flow used within Philips. Tools are available for the inclusion in the design of scan flip-flops and also for the generation of test patterns (Amsal). Amsal normally minimises the number of test patterns based on the stuck-at fault model.

### 2.3.3 **Localising Defects**

The testing of a circuit can tell if it is working properly. For real products, this is usually the only thing of interest. For diagnostical purposes, the cause of a failure has to be determined however. While testing a circuit, it is possible to pinpoint a specific scan flip-flop that contains a faulty value. However, the defect can be in all logic connected to the input of this flip-flop (see also Figure 6). Thus the fault is not localised precise enough yet.

It is possible to determine the location of the defect more precisely by combining data from multiple failing flip-flops and multiple test patterns, but usually this is still not enough to unambiguously pinpoint the location of a defect. See for example Figure 6. If the defect lies in the AND-gate that lies in the intersection of the • Figure 6 Example of defect localisation two grey cones, then both flip-flops involved will

indicate a failure (and therefore the failing gate can be pinpointed). However, in all other cases, only one flip-flop will fail and to establish the precise location of the defect, data from multiple patterns will have to be combined.

However, the normal procedure is to minimise the number of test patterns used, to keep the testing time low. It will thus not always be possible to pinpoint a single cell as the cause of a failure. Instead it might only be possible to give a list of potential defect locations. A tool (called faloc) is available within Philips to produce this list, but it does not provide very reliable results and work is in progress to improve the localisation capability.

# Design of the RDMC Module

As already stated, it is very important to have random logic that is also analysable. It is simply a must-have to be able to solve process problems related to failures of the random logic. The RDMC module provides in this need. Although all details about the module can be found in [Lit. 1] and [Lit. 2], the most important points are summarised in this section.

### 3.1 Concept

The RDMC module was specifically designed to be analysable. The need for this high analysability became apparent from previous versions of the Vegtor, which only contained the RDMR modules. Although these RDMR blocks had some features added to make them easier to diagnose, it proved (almost) impossible to trace back the cause of failures.

In the first place, the analysability of the RDMC modules is achieved by using logic with a depth of only one level. As could be seen in the previous section, this allows direct localisation of a defect given a failing scan flip-flop.

A second method, with which the analysability of the RDMC modules is increased, is using a couple of different variants. These variants have different amounts of routing in different metal layers. This should make it possible to determine if there are problems with a specific metal layer by analysing the differences in yield.

Although the RDMC module is not as representative for normal logic as the RDMR modules, it is still far more representative for normal logic than special test structures. Test structures are designed in such a way, that they are very sensitive to specific potential problems; they are of no use to detect unexpected problems.

### 3.2 Design

The logical function of the RDMC module could be freely chosen as long as the logic was one level deep. The obvious choice is to include one instance of each library cell. In this way, all possible configurations of the layers used in the cells are present. Therefore at least the front-end (in this report the front-end includes all layers unto and including metal1) is representative for normal random logic. Consequently, the module can also be used for the (partial) qualification of the standard cell library.

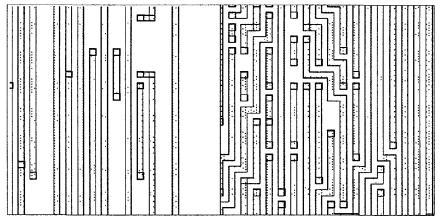

For each output of the standard library cells, a scan-chain flip-flop was added to the circuit: the inputs of the standard cells were connected to the closest scan flip-flop. The circuit was laid out with alternating rows of standard cells and scan-chain flip-flops (see Figure 7). Some buffers were added to provide sufficient drive-strength for the global nets.

The inclusion of non-combinatorial cells, like flip-flops and bus-keepers, causes a problem however: they not only have to be tested for their combinatorial behaviour but also for their ability to retain data. If all inputs (including Dark grey cells are standard library cells are scandard library cells special ones like the clock input) of these cells

Light grey cells are auxiliary cells

Light grey cells are auxiliary cells would be connected to the outputs of the . Figure 7 Layout of the RDMC module

scan-chain flip-flops, it would be impossible to change these inputs independently. This would make it impossible to test all the functionality of these cells. Therefore, a couple of global nets are introduced (clock2, reset, preset and trig). The resulting circuit has 6 inputs (scan-in, clock, clock2, reset, preset, trig), and 1 output (scan-out).

### 3.3 **Variants**

Four different variants of the RDMC module were produced. The library cells are arranged the same, but the modules are routed differently.

The first variant uses the shortestpossible routing. This is the reference variant. Problems in the metal layers should only have a very small impact on this type. This makes it possible to determine if there are any front-end (including metal 1) problems.

The other variants have as much routing as possible in two of the metal layers (the layers differ for each of the variants). Thus problems with a specific layer have an impact that is as large as possible • Figure 8 A routed RDMC module (RDM4C) on the variant that uses this layer.

The variants in layers 2 and 3 respectively in layers 4 and 5 minimise the number of vias in all layers except between 2 and 3 respectively 4 and 5. The variant with routing in layers 2 and 6 was intended to create a maximum amount of vias in all layers.

The characteristics of the different modules can be seen in Table 1. The longer routing for variants 2, 3 and 4 was obtained by shifting all scanchain flip-flops by two places in their respective rows (the last two ones were placed in front). This strategy gives routing that is about twice as long, but with a specific pattern of a couple of cells with very long wires and the rest with shorter wires (but still longer than in the original).

• Table 1 Routing Characteristics of the different RDMC's

|           | rdm1c | rdm2c | rdm3c | rdm4c |

|-----------|-------|-------|-------|-------|

| metal2*   | 16.6  | 20.5  | 2.2   | 2.6   |

| metal3*   | 8.5   | 26.2  | 2.6   | 23.9  |

| metal4*   | 0.4   | 0.4   | 23.9  | 1.6   |

| metal5*   | -     | • ,   | 20.1  | 1.3   |

| metal6*   | -     | -     | -     | 17.8  |

| # of via1 | 3038  | 3059  | 3030  | 3075  |

| # of via2 | 1424  | 2212  | 3013  | 3141  |

| # of via3 | 69    | 74    | 3792  | 1920  |

| # of via4 | -     | -     | 2728  | 822   |

| # of via5 | -     | -     | _     | 951   |

(\* metal lengths in mm)

### 3.4 Area Considerations

The area of all these variants is the same and about 0.05mm<sup>2</sup> ( $220\mu$ m<sup>2</sup> x 220µm²). Because this area is too small to be effective, ten modules (of the same type) are placed together, with their inputs connected in parallel (see Figure 9). This has the additional benefit that the 10 modules can be tested in parallel, while keeping the number of necessary pins low. The resulting block will be called an RDMC module in the rest of this report and the composing blocks sub-modules. The area of the entire RDMC block (including some overhead for power connections etc.) is about  $0.6 \text{mm}^2$ . To increase the area even further multiple instances of each type are placed on the Veqtor.

• Figure 9 An RDMC module containing 10 sub-modules

# 4 Testing the RDMC module

During the testing of the Veqtor chip, data about the RDMC modules is collected. The diagnosis methodology that was developed and which will be explained in the next section, relies on this data. Although a test was implemented for the modules, this had to be improved to reduce the testing time. This section explains how this new test was constructed and how logging of detailed information is implemented.

### 4.1 The Tester

Most Veqtor chips are not packaged because they are not commercial products. So testing of the Veqtor is done on the wafers. The testing is done on a Schlumberger SX100 tester. This tester has strong failure logging capabilities, which makes it suitable to produce memory bitmaps and to log failures in random logic (see also Section 0).

All logic on the Veqtor is first tested for scan continuity. This test proves that the scan-chains are working properly by shifting a certain pattern through the chains and checking if this pattern comes out at the other side. After the scan-continuity test, the RDMC modules are tested with stuck-at patterns. All these tests are done under four conditions: 1800mV and 100ns cycle time (nominal), 1800mV and 50ns, 1950mV and 100ns, and 1650mV and 100ns.

### 4.2 Test Pattern Considerations

The RDMC modules are tested with stuck-at test patterns that test each cell exhaustively to have a coverage that is as high as possible. The presence of the non-combinatorial cells is a complication for the test pattern generation because it is necessary to test these cells for their data retention capability. This can only be tested by using two test patterns. The first pattern loads the data into the cell and the second pattern checks if the data is retained. This is not supported by the standard test pattern generation tool (Amsal) and therefore other ways to generate the patterns had to be explored.

Before the start of this project, a dedicated tool was chosen as the solution [Lit. 3]. The tool was implemented and patterns were generated with this tool. The drawback of this tool is that it tests the library cell sequentially. Therefore, the number of test patterns needed was very large and consequently the test time was very long.

The tool reads (a special version of) the netlist and a file with the test patterns for each cell. It combines the information from these two files and produces a file with the test patterns. The tool also generates a file which contains information about which cell is tested in which cycle. The information from this file can be used to determine the failing cell once the tester indicates that a module fails in a certain cycle.

### 4.2.1 Compact Test Pattern Generation

Although the pattern file generated with the tool is usable, it was decided that the number of resulting test patterns was unacceptably large. The testing of the RDMC modules took half of the total testing time for the Veqtor for example. Three possibilities for the reduction of the amount of patterns were identified:

- Enhance the custom pattern generation program to combine patterns where possible:

- + Exact control over generated patterns

- +/- Reasonable implementation time (1 to 2 weeks)

- +/- Reasonably small pattern set

- Use Amsal after remodelling the non-combinatorial cells:

- + Potentially the largest reduction in the number of patterns

- Correct testing of non-combinatorial elements uncertain, but is might be possible using delay fault patterns

- Implementation time unknown

- +/- Use of standard tools (like aplot/faloc). However, delay fault patterns are not yet supported by these tools

- Use a combination of patterns generated by Amsal (for the combinatorial cells) and existing version of the pattern generation tool (other cells):

- + Small amount of time needed for the implementation (1 to 2 days)

- Only the patterns for the combinatorial cells are reduced (estimated reduction to about 1/2)

- Combination of tools might give problems for the fault localisation

The enhanced custom program was reckoned the best option. This program has to combine the test patterns for multiple cells. The complicating factor is that the patterns for the non-combinatorial elements have to stay in the same order. This decreases the possible combinations of patterns. An additional optimisation with a factor two can be easily reached because the original program does not shift the data out and in simultaneously, but first shifts the data out (while shifting in zeroes) and only then shifts the data in. The program was implemented in the expected time span. More information about the program can be found in [Lit. 4].

### 4.2.2 Test Pattern Verification

The new pattern set that was generated with the tool is about 60 times smaller than the original set. To verify this new pattern set, it was used in parallel with the original set. The yield (ratio of failing to passing modules) was expected to be about the same for the two sets as they have the same coverage (for stuck-at faults).

However, the yield for the new set was about 1% to 1.5% higher than for the old set. This means that the coverage for the new set is lower. This yield difference was judged too large to use the new set. Three effects that could possibly cause the yield difference were identified:

- 1) The large pattern set should be better at detecting bridges because the environment of the cell that is being tested always has the same state. A bridge (a short between two signal nets) can only be detected if the two involved nets have opposite values. If the environment is always the same, the nets have opposite values in at least one situation; this is not necessarily the case with the smaller pattern set.

- 2) The activity level in the circuit is higher with the small pattern set because more cells change states simultaneously. This results in higher currents, which might cause other defects to be detected.

- 3) The shifting out and shifting in of the data is separated in the large pattern set, while this is done simultaneously for the small set. Although it is not directly obvious that this has an impact on the coverage, it is a difference between the two sets.

To establish whether the first two effects combined or the third effect caused the difference, additional pattern sets were generated. To test for the first two effects a set in which adjacent cells are not tested simultaneously was generated. To test for the third effect, sets with a different interval between shift out and shift in were used.

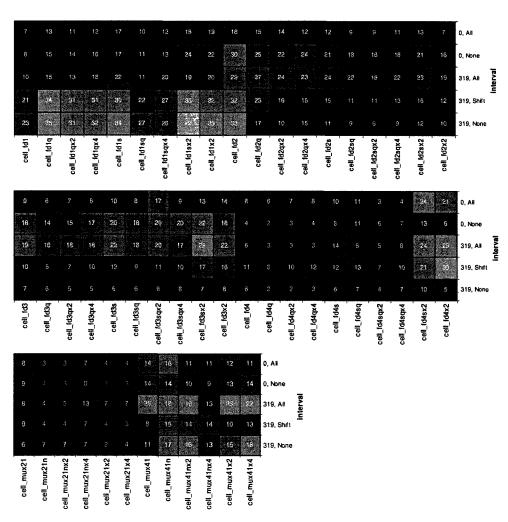

The results from all these tests can be seen in Table 2. The set with 3441 patterns is the original set, the sets with 99 patterns are the small sets and the sets with 408 patterns are the sets in which adjacent cells are not tested simultane-

ously. The number of zeroes used between shift out and shift in is the interval. The patterns with 0 interval simultaneously shift the data out and new data in; the scan-chain is 319 flipflops long and thus the set with 319 interval successively shifts the data out and in. The others use half respectively double the interval. Only an indi-

Table 2 Indicative relative yields of pattern sets

|       |     | Patterns |       |       |  |  |  |  |  |

|-------|-----|----------|-------|-------|--|--|--|--|--|

|       | -   | 3441     | 408   | 99    |  |  |  |  |  |

| _     | 0   |          | +1.3% | +1.3% |  |  |  |  |  |

| rval  | 160 |          |       | +0.6% |  |  |  |  |  |

| Intel | 319 | 0.0%     | ±0.0% | ±0.0% |  |  |  |  |  |

|       | 638 |          |       | -0.5% |  |  |  |  |  |

cation of the yield differences is shown because the absolute yield differs between different RDMC modules and measurements from two separate runs are used. The yield of the original set was chosen as reference and set to 0.0%.

It can be seen from Table 2 that the number of patterns has a relatively small influence. This seems to indicate that the activity level (effect 2) and the bridging defects (effect 1) have no impact at all or an equal (but opposite) impact. However, the simultaneous or successive shift out and shift in has a large impact and concurs with the original 1% to 1.5% difference. To study this effect in more detail additional pattern sets were generated with variations for overlap of shift out and shift in (which use the smallest pattern set). The results from these tests can also be seen in Table 2.

To check, whether the content of the padding between shift out and shift in has any influence on the coverage, additional pattern sets with random instead of zero padding were generated. Two levels of random padding were tried. The first level only replaces the zeroes between shift out and shift in with random data. The second level also replaces the undefined values in the patterns themselves with random instead of zero data. Only the small sets with 99 patterns were modified.

The coverage never is higher than with zeroes as padding, as can be seen in Table 3. For the simultaneous shift out and shift in no effect of the random padding can be detected. For the successive variant only a small

• Table 3 Indicative relative yields of pattern sets

| None Shift All           |        |     | Random padding |       |       |  |  |  |  |

|--------------------------|--------|-----|----------------|-------|-------|--|--|--|--|

| Inter- 0 +1.2% +1.29     |        | ·   | None           | Shift | All   |  |  |  |  |

| 11.270                   | Inter- | 0   | +1.2%          |       | +1.2% |  |  |  |  |

| val 319 0.0% +0.2% +1.0% | val    | 319 | 0.0%           | +0.2% | +1.0% |  |  |  |  |

difference is found when only the shifting is stuffed with random data, but a significantly larger effect is found when the patterns themselves are also stuffed. No explanation for this effect is obvious (as it does not occur with the simultaneous shift out and shift in).

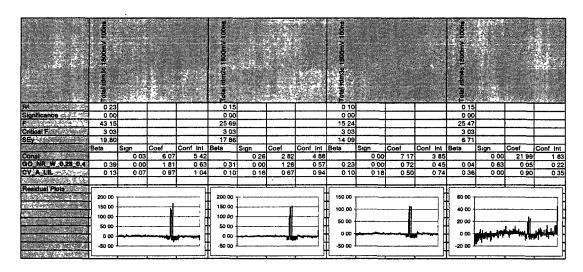

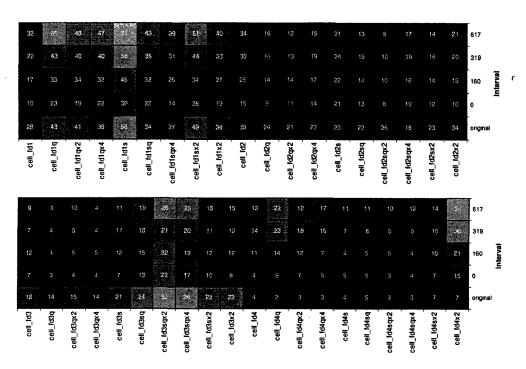

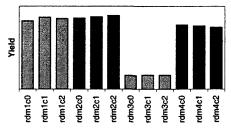

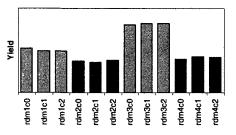

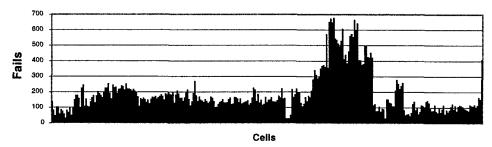

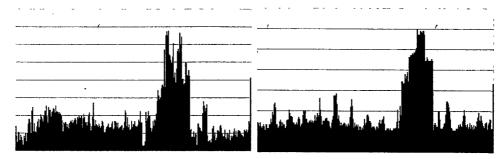

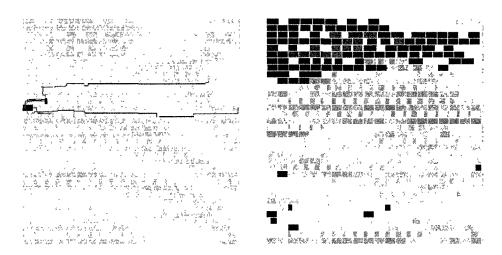

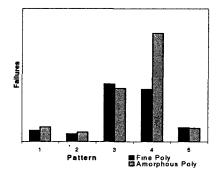

With the tools described elsewhere in this report, it was possible to establish which cells caused the yield differences. Figure 10 and Figure 11 (on the next page) show the number of failures per cell type for the different pattern sets. The number of failures is also indicated graphically by the intensity of the squares. (The cells that are not included in the figure have about equal failure counts for all pattern sets.)

From Figure 10 it can be seen that certain types of flip-flops are responsible for the yield differences between the sets with different amounts of padding. For the insertion of random data, the results can be seen in Figure 11. The picture is not as clear as for the interval variation. Not only the flip-flops seem to play a roll in the yield differences, but also the multiplexers. Moreover, the patterns with successive shifting and no random padding and the patterns with padding in only the shifting, resemble each other. On the other hand, the one with successive shifting and complete random padding and the one with simultaneous shifting and no padding also resemble each other.

• Figure 10 Influence of different intervals on the amount of failures of flip-flops

Figure 11 Influence of random padding on the amount of failures of flip-flops

# 4.3 Logging

The process of storing the results of the tests is called logging. For commercial products, it is only logged if a module passes or fails. To gather data that is more detailed, it should also be logged which test vectors failed. From this data, it can be determined which scan-chain flip-flops contained faulty results. For the RDMC modules, this also directly indicates which standard library cell is involved (see Section 5.3).

The Schlumberger SX100 tester stores the cycle number of the vectors that fail into a special memory during testing. This memory also contains information about the pins that failed, which is used to determine which sub-module failed. The standard software of the tester offers an easy way to log which vectors fail via its data logging options. This option could not be used because it is neither stable nor fast enough to handle the large amounts of data involved.

To circumvent these problems custom logging routines were written; details about these routines can be found in [Lit. 4]. The logging routines are written in such a way that they can also be used for other types of random logic modules (like the RDMR). The custom routines are not only more stable and faster, but they also reduce the amount of data that needs to be written in a number of ways:

- The log is compressed as it is written to disk.

- Only the results from the modules, which pass the scan-continuity testing are logged.

- The results of a module are not logged if there are more than 1853 failing vectors. (There are 1854 failing vectors if the module has floating outputs.)

The stated measures not only reduce the necessary disk space, but also reduce the testing time. (The disk accesses to write the logs cost more time than the actual testing.) The total test time of the Veqtor chip is only increased by approximately 15%.

Over the last couple of months, about 30 lots were tested and the detailed failure data logged. However, because of some test problems (that are unrelated to the logging), not all these results are usable.

### 4.4 Conclusions

Because of the excessive test time required by the original test pattern set, a new set was produced. The results of the set with 99 patterns and successive shift out and shift in (interval of 319) without random padding are close enough to the original set. Therefore, this set replaces the original one for all testing of the RDMC modules.

The RDMC modules are quite sensitive to slight pattern variations. This is mainly because of the presence of flip-flops. It seems to be a problem with the retention of the data because longer intervals cause more failures. The values that are used for padding also seem to play a roll, but this interaction is not clear from the data presented here.

The pattern dependencies probably do not occur in the same way for normal random logic because no flip-flops are present outside the scan-chain. The problem with the data retention probably does occur however (see also [Lit. 5]) and therefore it is worthwhile investigating it on normal random logic.

The logging could be implemented in such a form that the data from all the devices that are tested could be logged. This was actually done for almost all lots from the time that the logging was implemented.

# 5 Diagnosis Methodology

After the preliminaries of the previous couple of sections, it is now time to really look at the problem at hand. For the first part of the project, a diagnosis methodology for the RDMC modules had to be devised. This section will describe the methodology that is developed and also —though briefly—the tools that are necessary to support it.

# 5.1 Outline

For the start-up of IC production processes and improving the quality of the processes, it is necessary to be able to find the causes of problems in random logic. Problems in the production process out themselves as devices that fail some tests. The fraction of devices that pass all tests is called the yield. Due to the complexity of the production process and the impossibility of maintaining an absolutely particle-free environment, the yield will never be 100%, although the goal is to come as close as possible of course.

The purpose of the diagnosis methodology that is described in this section is to identify process problems as precise as possible with the help of the data that is gathered from the RDMC modules. The diagnosis methodology will of course rely heavily upon the special characteristics of the RDMC modules: first, there are the four different routing variants and, second, there is the capability to easily establish which library cell is failing.

During the design of the RDMC modules, two ways of diagnosing problems were identified [Lit. 2]:

- Analysis of the yield differences between different variants.

- Failure analysis (which is the process of finding the cause of a specific defect by physical inspection).

Failure analysis is a very time-consuming procedure. Therefore, it should only be used as a last resort, when all statistical analysis methods have been tried. However, when failure analysis has become inevitable, it has to be facilitated as well as possible. This can be done by determining the most likely location of the defects as precise as possible based on the test data.

A method of analysis that was not considered during the design was using the information about failing cells in a statistical way. It requires the availability of a large amount of data, but it is possible to obtain this (as was seen in Section 0). The analysis of the cell level data can give very detailed and useful information and the methodology described further on in this section relies heavily on this data.

The next sub-section handles about the modelling of the relationship between process problems and the yield. The sections after this go into the diagnosis methodology: first about using yield differences between the different variants, next about relating the cell level data to process problems and finally about some additional analysis instruments. Section 5.6 briefly describes the tools that make the usage of the methodology possible.

# 5.2 Yield Modelling

The yield model that is described in this sub-section has a number of limitations. An important assumption for the model is that defects are randomly and uniformly distributed. This assumption does not necessarily hold for IC production process, especially not for new processes. While the largest problems with mature process

are particle-related defects, new process also suffer from systematic and parametric problems. It is however, a model that is simple enough to be usable and it has proven to be sufficiently precise for most purposes.

The yield of a device can be estimated by multiplying the yields of its constituent blocks. This is true because the yield can be interpreted as the probability that a randomly selected block is functioning properly and for a device to work all the blocks have to work. The estimation can be expressed as:

$$Y_{\text{total}} = Y_{\text{block 1}} \cdot Y_{\text{block 2}} \cdot \dots \cdot Y_{\text{block n}} = \prod_{\text{all blocks}} Y$$

The same sort of relationship is true for all the separate processing steps. For a device to work properly all processing steps have to be flawless. Therefore, the total yield can again be expressed as the product of the constituent yields:

$$Y_{\text{total}} = Y_{\text{step 1}} \cdot Y_{\text{step 2}} \cdot \dots \cdot Y_{\text{step n}} = \prod_{\text{all steps}} Y$$

If it is assumed that yield loss is caused by defects, it is possible to model the yield as the probability that a certain device contains no defects. If the defects are distributed randomly and uniformly, the probability that a chip contains a certain number of defects can be modelled by the binomial distribution [Lit. 6]. If there are n defects distributed amongst N devices, the probability  $P_k$  that a certain device contains k defects is:

$$P_k = \frac{n!}{k!(n-k)!} \cdot \left(\frac{1}{N}\right)^k \left(1 - \frac{1}{N}\right)^{n-k}$$

If n and N are large, it is possible to approximate this equation by the Poisson distribution (for proof see for example [Lit. 8]):

$$P_k \cong e^{-n/N} \frac{(n/N)^k}{k!}$$

If A is the area of the device and  $D_0$  the defect density, the number of defects can be calculated as:

$$n = N \cdot A \cdot D_0$$

The probability that a device contains no defects, which is the yield, can be expressed as:

$$Y = P_0 = e^{-n/N} = e^{-AD_0}$$

This model is called the Poisson model and has the following limitations:

Only random defects are accounted for: systematic and parametric yield losses are not modelled.

A uniform distribution of the defects over the wafer is assumed, so clustering of defects is not taken into account. (For models that do take this into account, see [Lit. 6].)

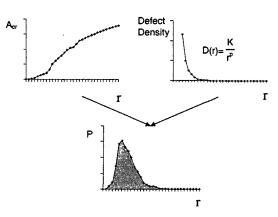

It is assumed that every defect actually causes a failure: this is not the case, but depends on both the size of the defect and the actual layout of the device (see Figure 12 for an example).

Killing Defects

(Connect two metal lines)

Acr for circular defects of size r

Metal Line

Non Killing Defect

(Does not connect

metal lines)

Figure 12 Critical area and (non-)killing defects

An important extension to the Poisson model compensates for the fact that not all defects are killing. Extra material only causes a short if it connects two adjacent

nets; missing material only causes a problem if the electrical connectivity is compromised. For current processes the two most important failure mechanisms (which therefore need to be modelled) are identified as:

- Shorts caused by extra material in layers with conducting lines:

- Opens caused by missing or bad vias and contacts.

In case of shorts, the Poisson model can be enhanced by using the so-called critical area model. The critical area of a chip is the area that is susceptible to a certain type of defect of a certain size (see again Figure 12). This means that the critical area is different for defects of different sizes. Therefore, the average number of defects per device (AD<sub>0</sub>) is replaced by an integral over the defect size of the product of the critical area and the defect size distribution (see Figure 13 for a graphical ex- • Figure 13 Critical area and defect density distribution ample):

$$Y = e^{-\int_{0}^{\infty} A_{Cr}(r)D(r)dr}$$

The defect density curve D(r) is never exactly known. Only the values at a limited number of sample points can be obtained. However, according to [Lit. 7] it is possible to model D(r) using:

$$D(r) = \frac{K}{r^p}$$

In this equation, K describes the defect density level and p is a measure for the form of the distribution of the defect sizes.

The critical area A<sub>cr</sub>(r) is also only known at a couple of points. No simple model can be used in this case, so the curve is approximated with a piecewise-linear function. If r<sub>1</sub>...r<sub>N</sub> are the radii at which A<sub>cr</sub>(r) is sampled, the entire function can now be approximated as:

$$Y = e^{-\sum_{n=1}^{N-1} \frac{D(r_n) A_{cr}(r_n) + D(r_{n+1}) A_{cr}(r_{n+1})}{2} (r_{n+1} - r_n)}$$

For evaluating the effect of open vias and contacts a simple equation can be used, in which N<sub>via</sub> is the number of vias in the device and P<sub>fail</sub> is the chance that a certain via is open:

$$Y = e^{-N_{via}P_{fail}}$$

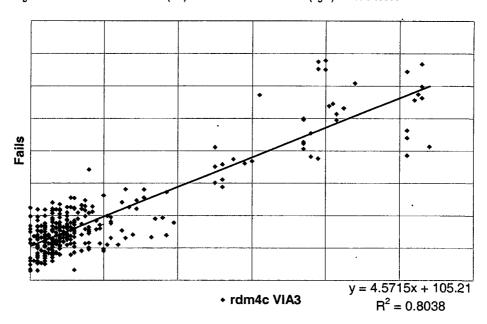

With these equations the total yield can be modelled as: